|

|

|

AIDA

GELINA

BRIKEN

nToF

CRIB

ISOLDE

CIRCE

nTOFCapture

DESPEC

DTAS

EDI_PSA

179Ta

CARME

StellarModelling

DCF

K40

|

| DESPEC |

|

|

|

|

Message ID: 186

Entry time: Tue Mar 9 23:12:17 2021

|

| Author: |

CA |

| Subject: |

March 10th 00:00 - 08:00 |

|

|

00:13 beam back, but some spills 'missing'

DESPEC keeping beam as is, but may stop later if it worsens

00:15 DAQ continues OK - file R20_622

ASIC settings 2019Dec19-16.19.51

DSSSD#1 slow comparator 0xa

DSSSD#2 slow comparator 0xa

DSSSD#3 slow comparator 0xd

BNC PB-5 Pulser

Amplitude1.0V

Attenuation x1

Frequency 2Hz

tau_d 1ms

- polarity

Delay 250ns, tail pulse

00:20 System wide checks all OK *except*

ADC Calibration

FEE64 module aida07 failed

FEE64 module aida10 failed

Calibration test result: Passed 10, Failed 2

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

Check FPGA Timestamp Errors

Base Current Difference

aida12 fault 0x0 : 0x1 : 1

FPGA Timestamp error counter test result: Passed 11, Failed 1

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

00:24 still no bad timestamp errors in NewMerger since 16:30 UTC

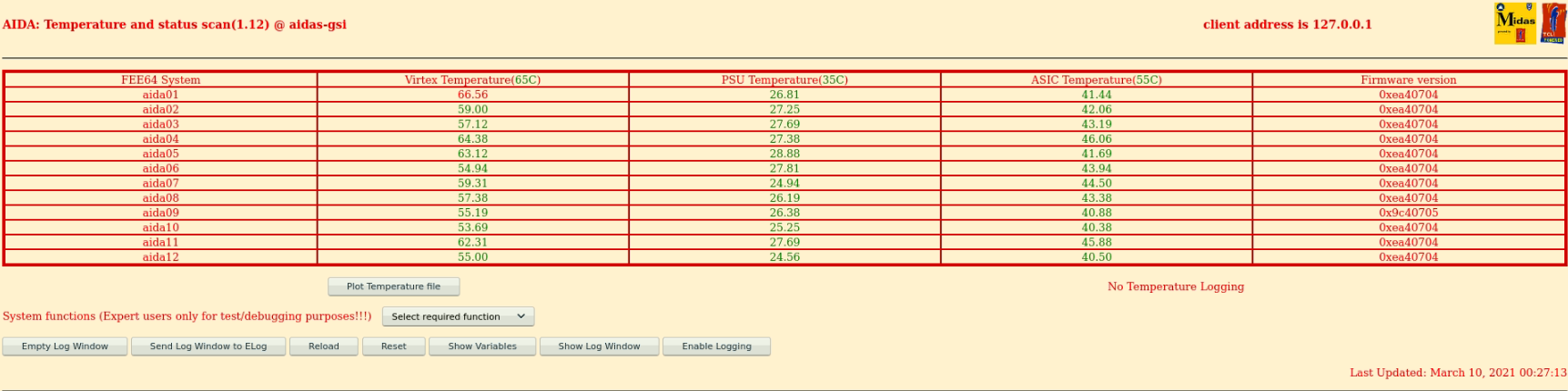

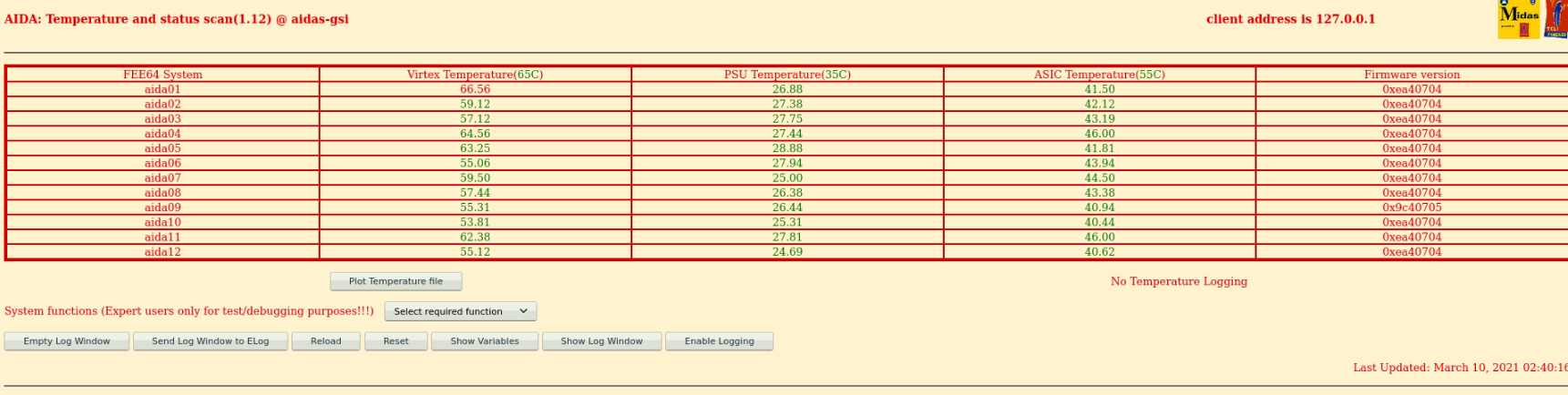

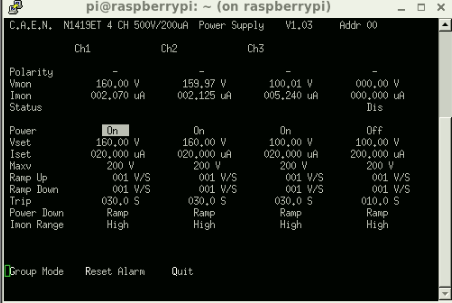

00:30 FEE64 Temperatures OK - attachment 1

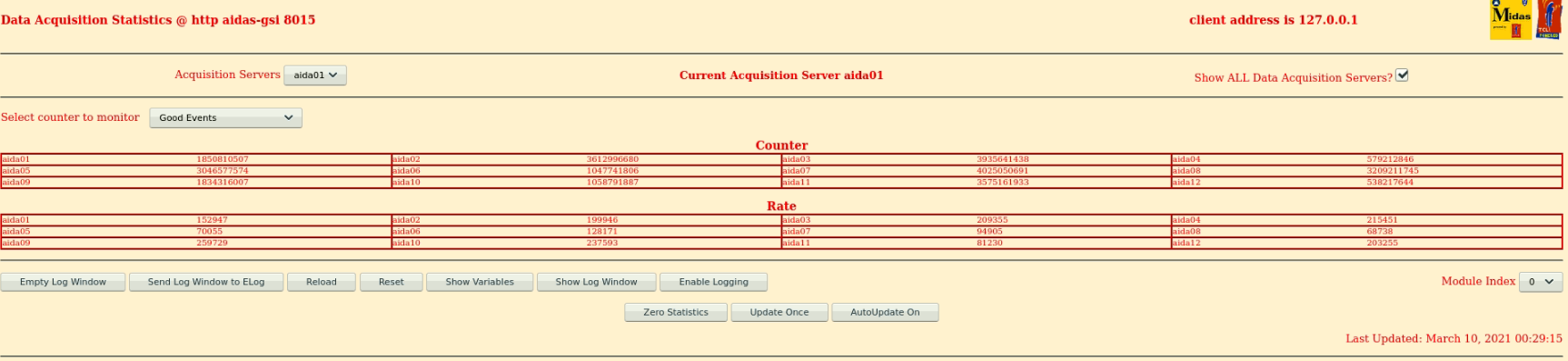

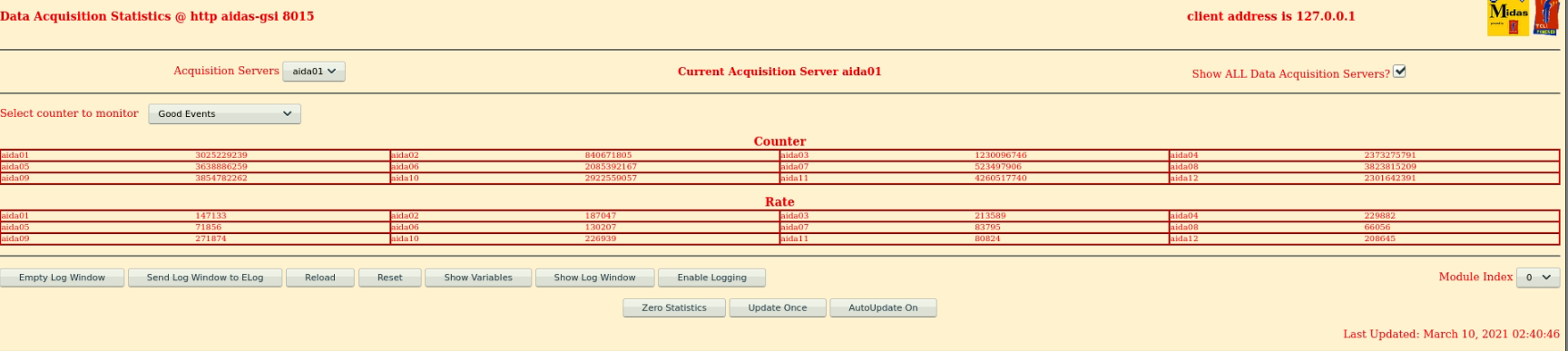

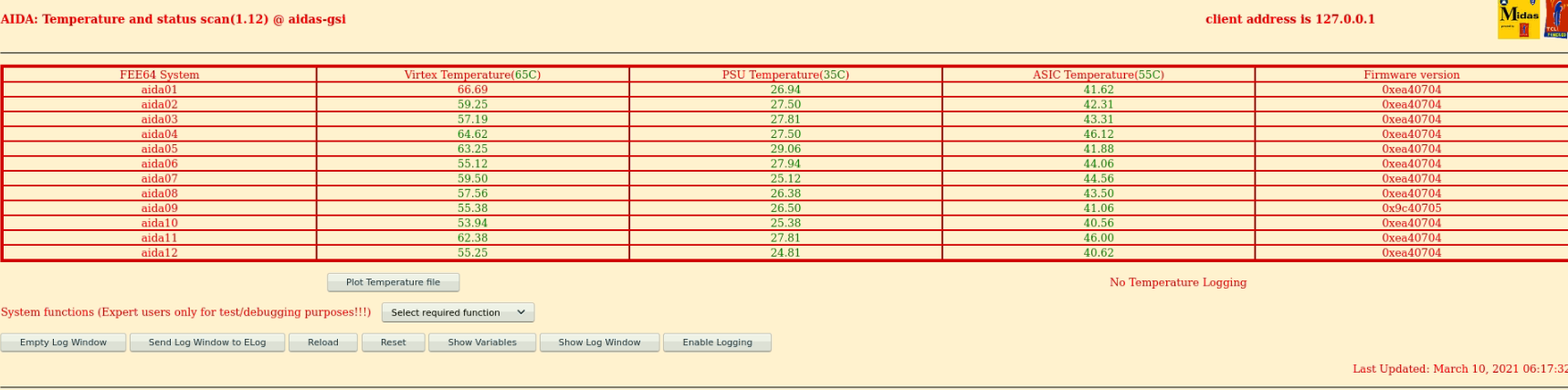

Good event statistics OK - attachment 2

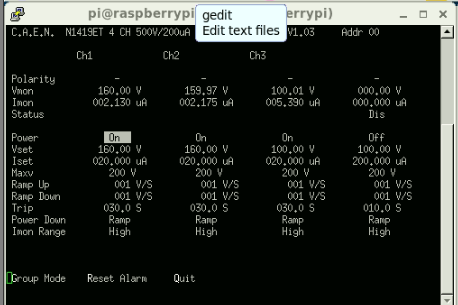

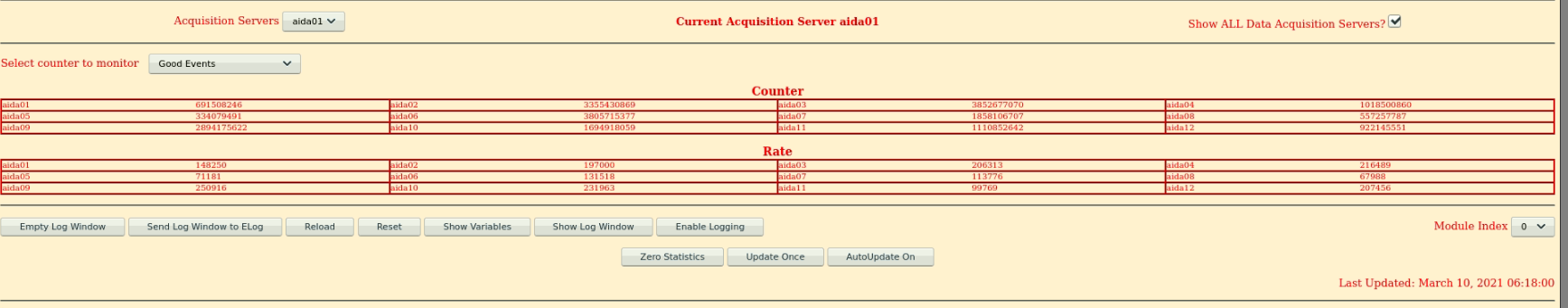

Detector bias & leakage currents OK - attachment 3

Merger OK - 4.2M data items/s

TapeServer OK - 45 Mb/s

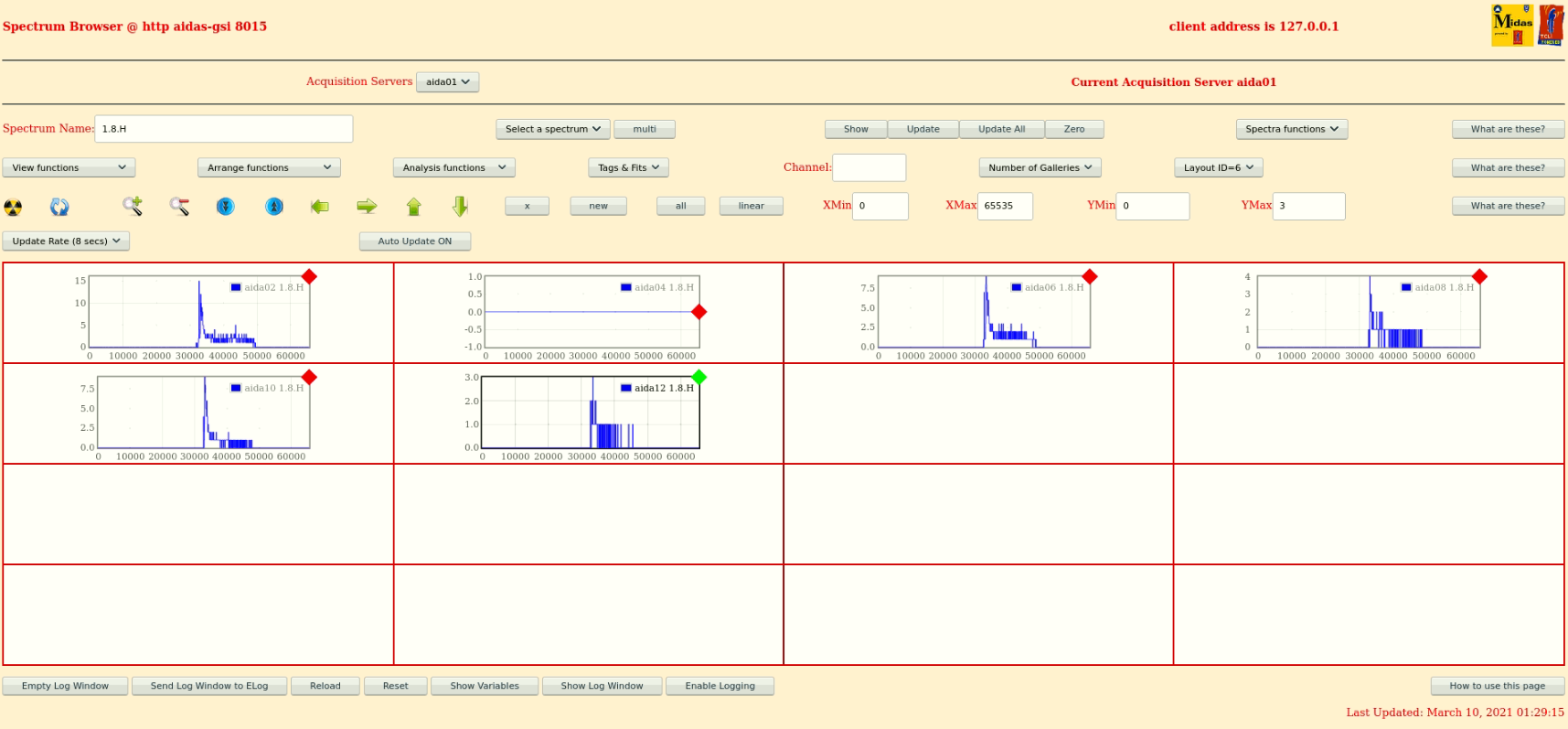

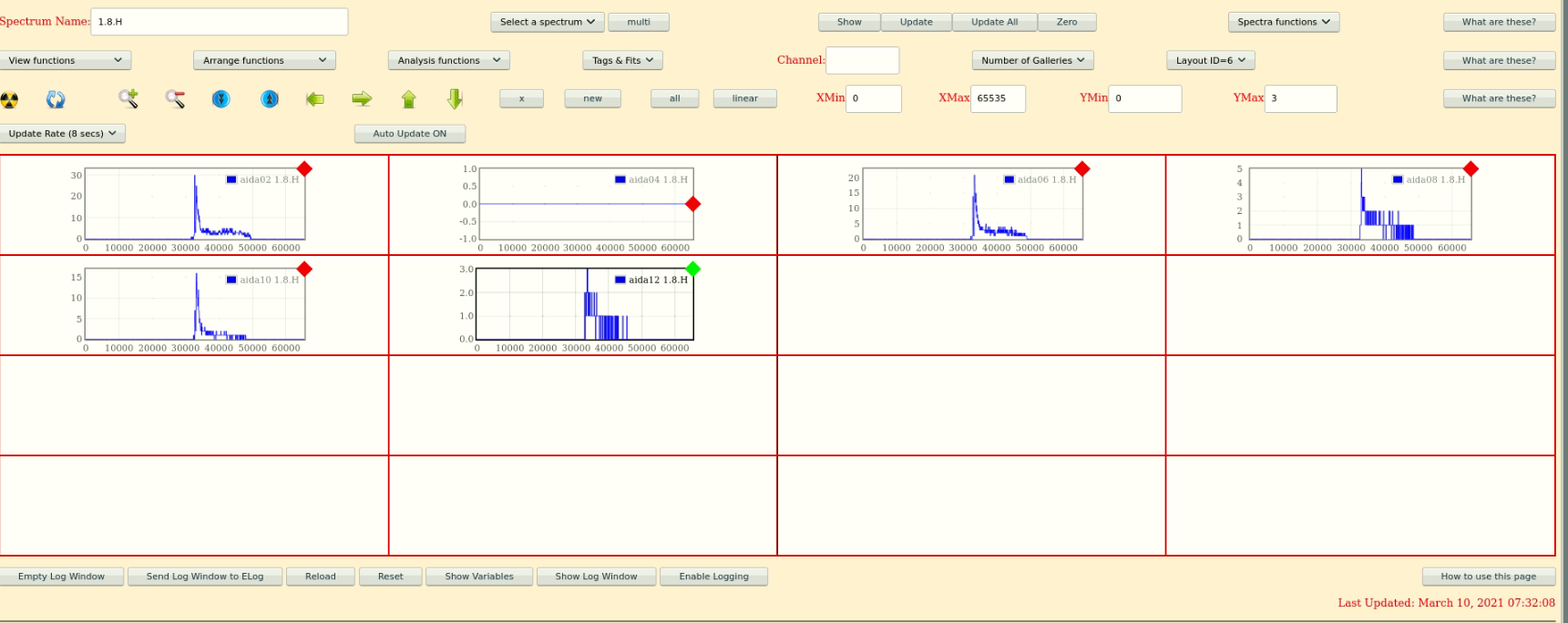

01:30 rate spectra - attachment 4

HEC spectra - attachment 5 & 6

note aida04 spectrum still not showing

02:07 beam off - file R20_760

02:11 beam back - file R20_764

02:44 System wide checks all OK *except*

ADC Calibration

FEE64 module aida07 failed

FEE64 module aida10 failed

Calibration test result: Passed 10, Failed 2

Check FPGA Timestamp Errors

Base Current Difference

aida12 fault 0x0 : 0x1 : 1

FPGA Timestamp error counter test result: Passed 11, Failed 1

still no bad timestamp errors in NewMerger since 16:30 UTC

FEE64 Temperatures OK - attachment 7

Good event statistics OK - attachment 8

Detector bias & leakage currents OK - attachment 9

Merger OK - 4.2M data items/s

TapeServer OK - 44 Mb/s

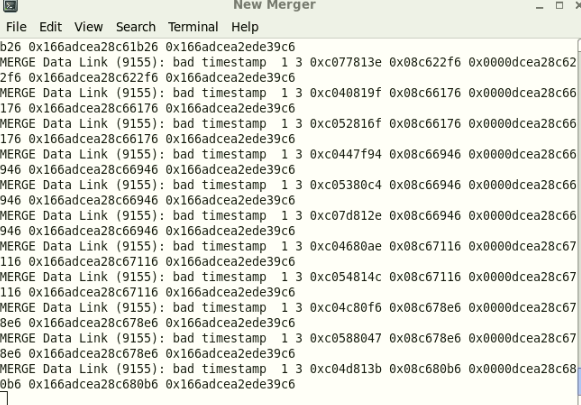

04:16 bad timestamp errors in NewMerger terminal, first since 16:30 UTC - attachment 10

System wide checks all OK *except*

ADC Calibration

FEE64 module aida07 failed

FEE64 module aida10 failed

Calibration test result: Passed 10, Failed 2

Check FPGA Timestamp Errors

Base Current Difference

aida12 fault 0x0 : 0x1 : 1

FPGA Timestamp error counter test result: Passed 11, Failed 1

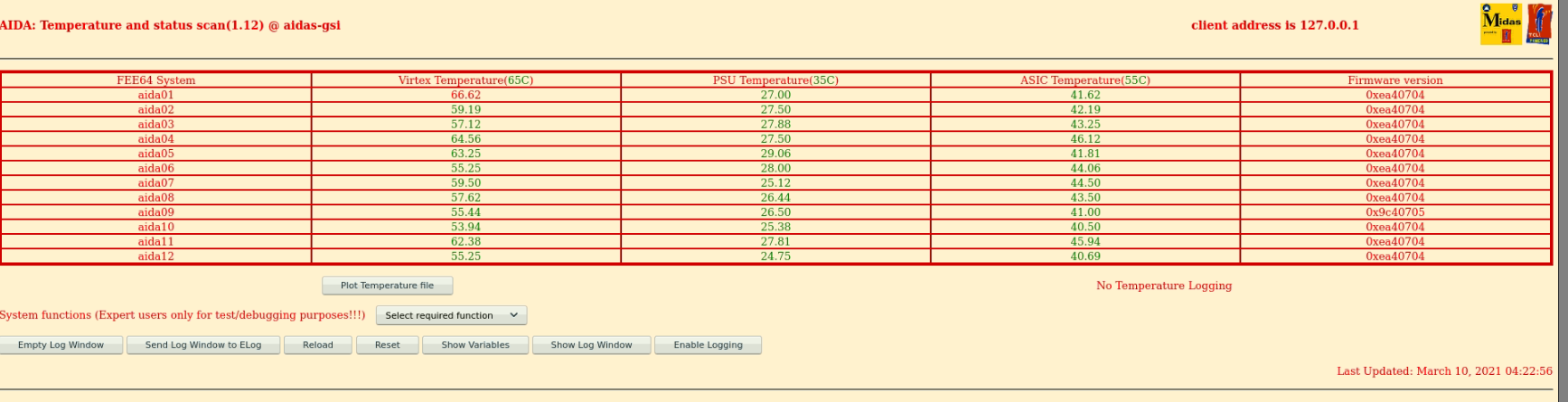

FEE64 Temperatures OK - attachment 11

Good event statistics OK - attachment 12

Detector bias & leakage currents OK - attachment 13

05:03 Merger OK - 4.5M data items/s

TapeServer OK - 43 Mb/s

no bad timestamp errors for ~40 mins, data forwarding to MBS ok at usual rate

06:11 rates spectra - attachment 14

06:14 System wide checks

ADC Calibration

FEE64 module aida07 failed

FEE64 module aida10 failed

Calibration test result: Passed 10, Failed 2

Check WR decoder status

Base Current Difference

aida05 fault 0x1591 : 0x1593 : 2

aida06 fault 0xe23c : 0xe23e : 2

aida07 fault 0x743 : 0x745 : 2

aida08 fault 0xf84e : 0xf850 : 2

aida09 fault 0x5449 : 0x544a : 1

White Rabbit error counter test result: Passed 7, Failed 5

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

Check FPGA Timestamp Errors

Base Current Difference

aida12 fault 0x0 : 0x1 : 1

FPGA Timestamp error counter test result: Passed 11, Failed 1

still no further bad timestamp errors in NewMerger terminal

collected all WR and FPGA errors from baseline, system wide checks ok

FEE64 Temperatures OK - attachment 15

Good event statistics OK - attachment 16

Detector bias & leakage currents OK - attachment 17

06:24 AIDA writing to file R20_1080

Merger OK - 4.5M data items/s

TapeServer OK - 46 Mb/s

06:26 another burst of bad timestamp errors - attachment 18

performed system wide checks again - all ok aside from aida07/aida10 calibration

07:32 HEC spectra - attachments 19/20

07:35 no beam

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|