|

|

|

AIDA

GELINA

BRIKEN

nToF

CRIB

ISOLDE

CIRCE

nTOFCapture

DESPEC

DTAS

EDI_PSA

179Ta

CARME

StellarModelling

DCF

K40

MONNET

|

| DESPEC |

|

|

|

|

Message ID: 407

Entry time: Sat Apr 2 10:42:49 2022

|

| Author: |

TD |

| Subject: |

Saturday 2 April |

|

|

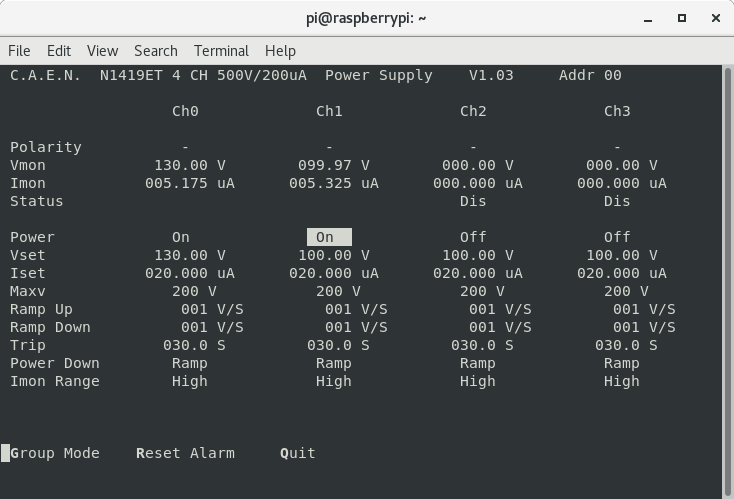

11.10 Found aida08 not running - merger/TapeServer stalled

Restart required power cycle of all FEE64s

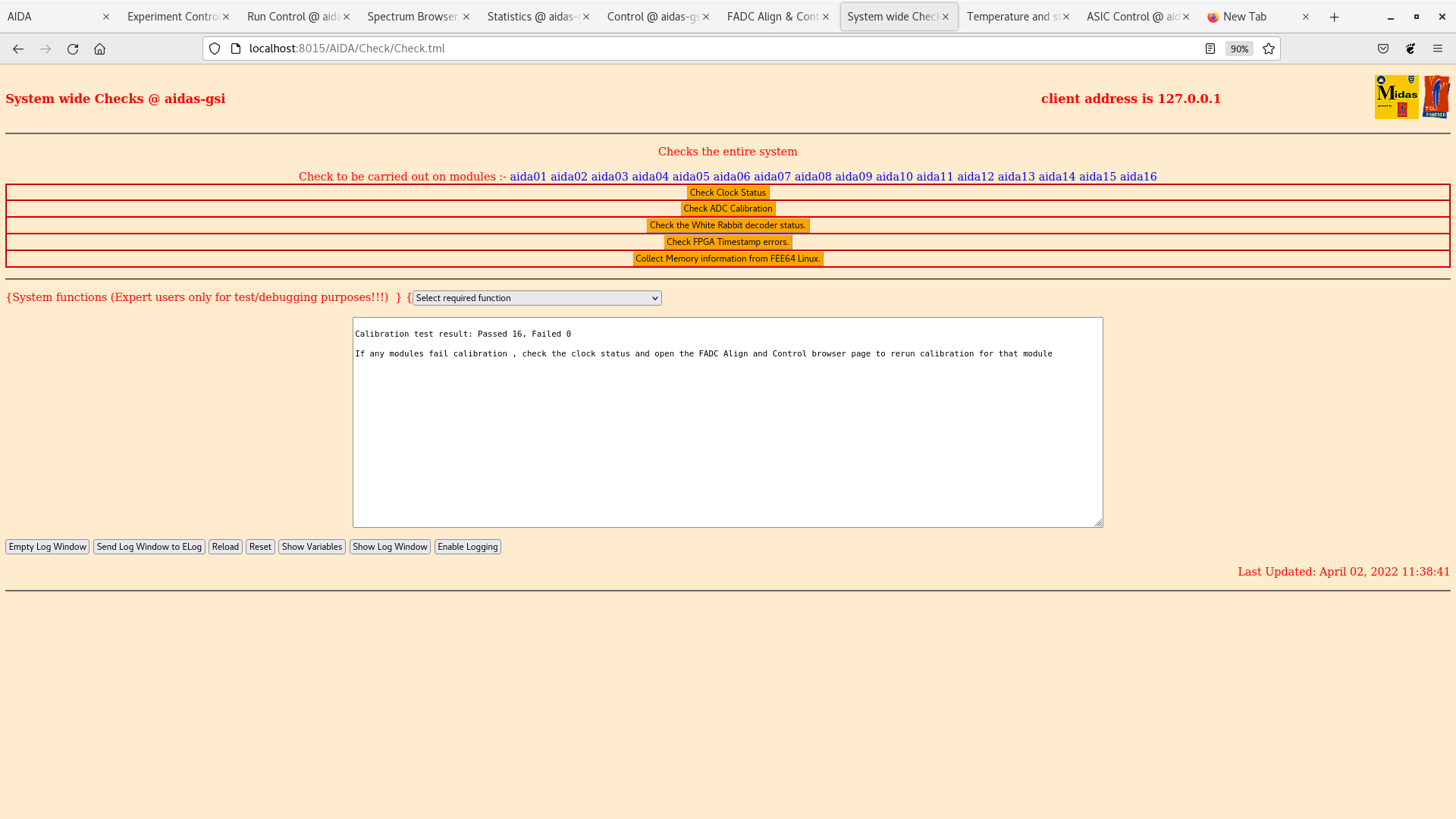

*all* ADC calibrations failed during system wide checks it was necessary to use FADC align & control (act on all FEE64 modules selected) to calibrate - first pass

12/16 calibrated, successive individual re-calibrations calibrated remaining FEE64s

ASIC settings 2021Apr29-13-16-00

slow comparator 0x2f

BNC PB-5

amplitude 1.0V

attenuation x1

polarity +

tail pulse

tau_d 1ms

rate 25Hz

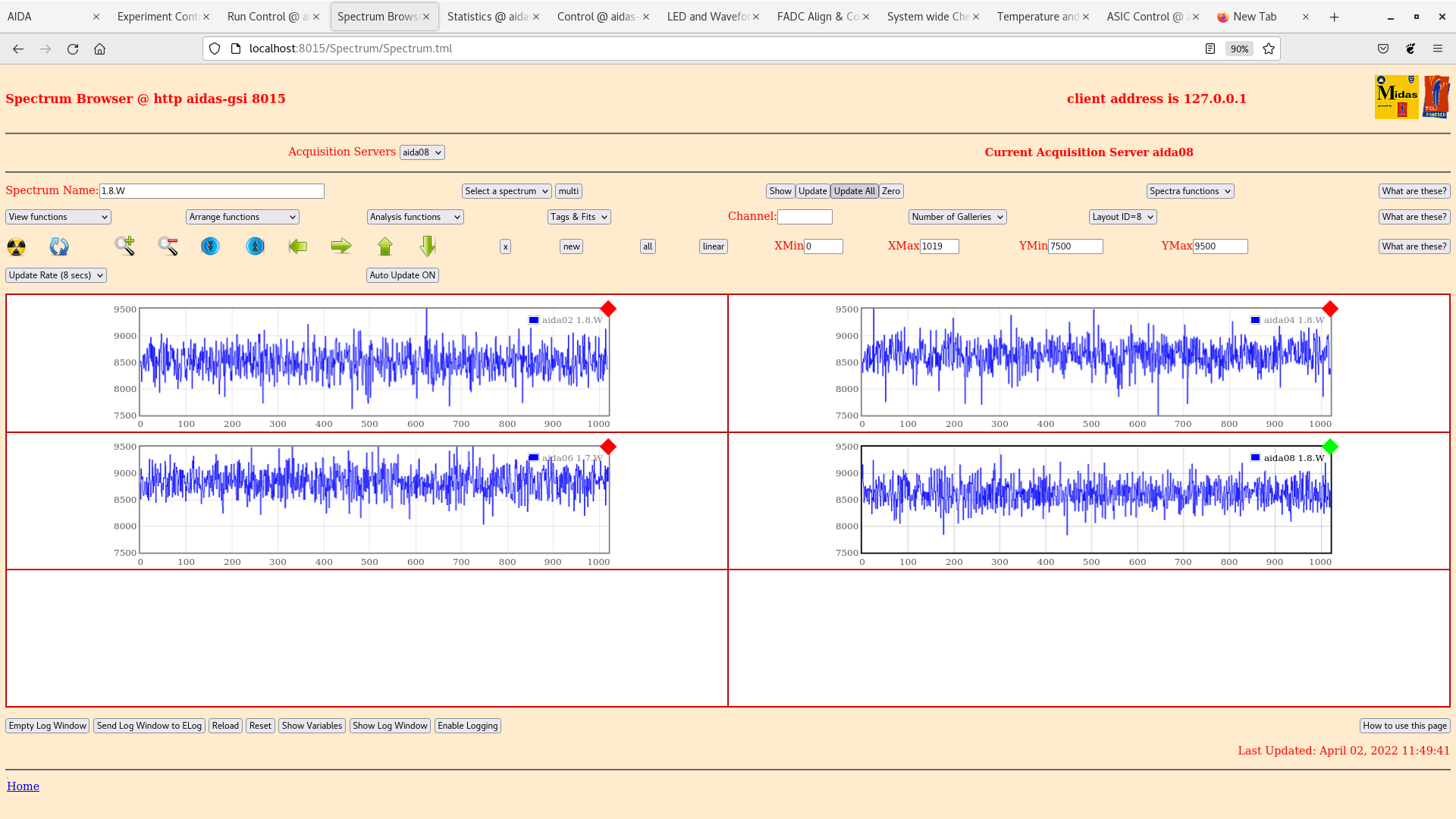

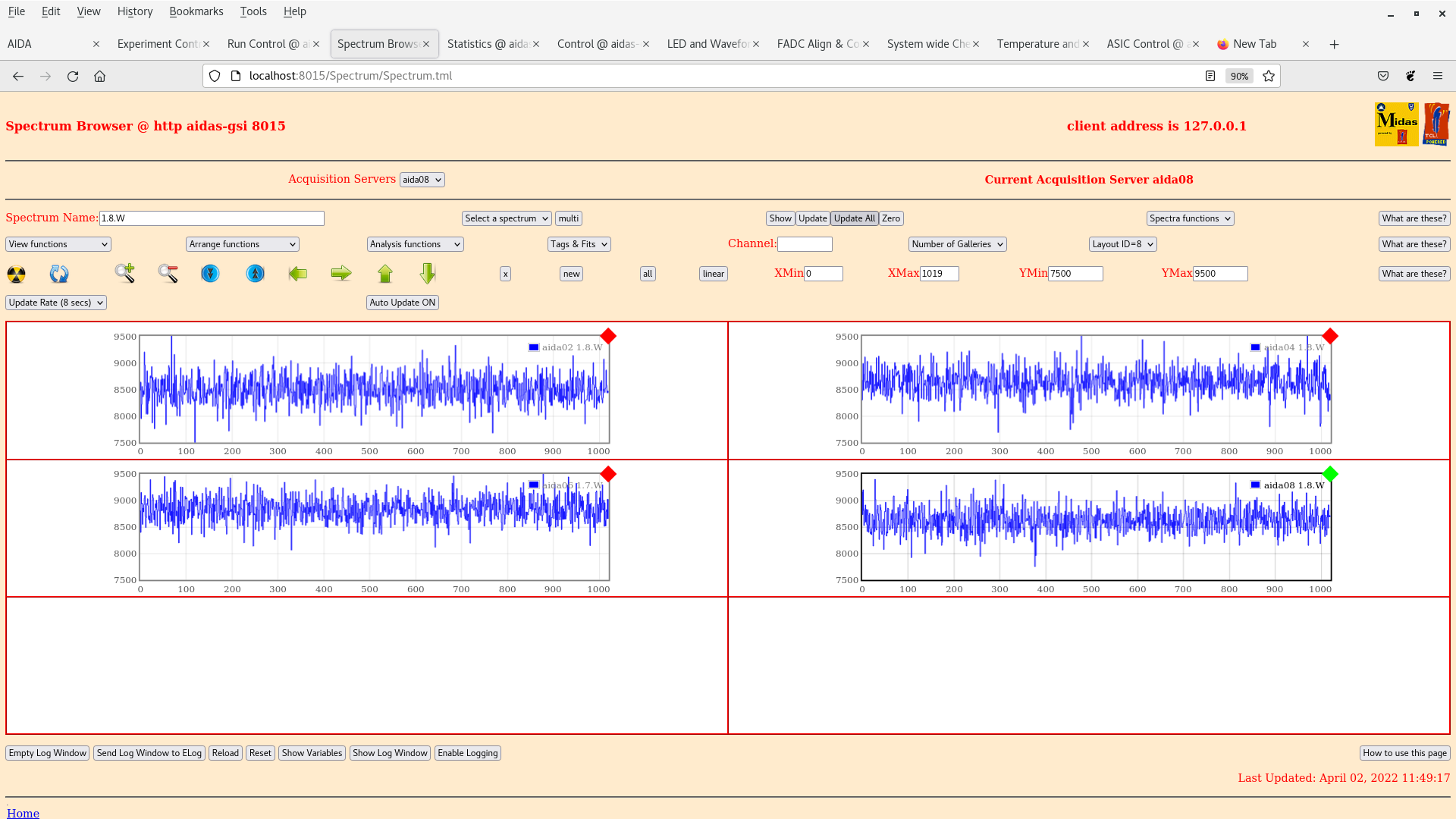

Attachments 1-4 1.8.W n+n spectra 20us, 200us, 2ms, 20ms FSR

Attachments 5-8 1.8.W p+n spectra 20ms, 2ms, 200us, 20us FSR

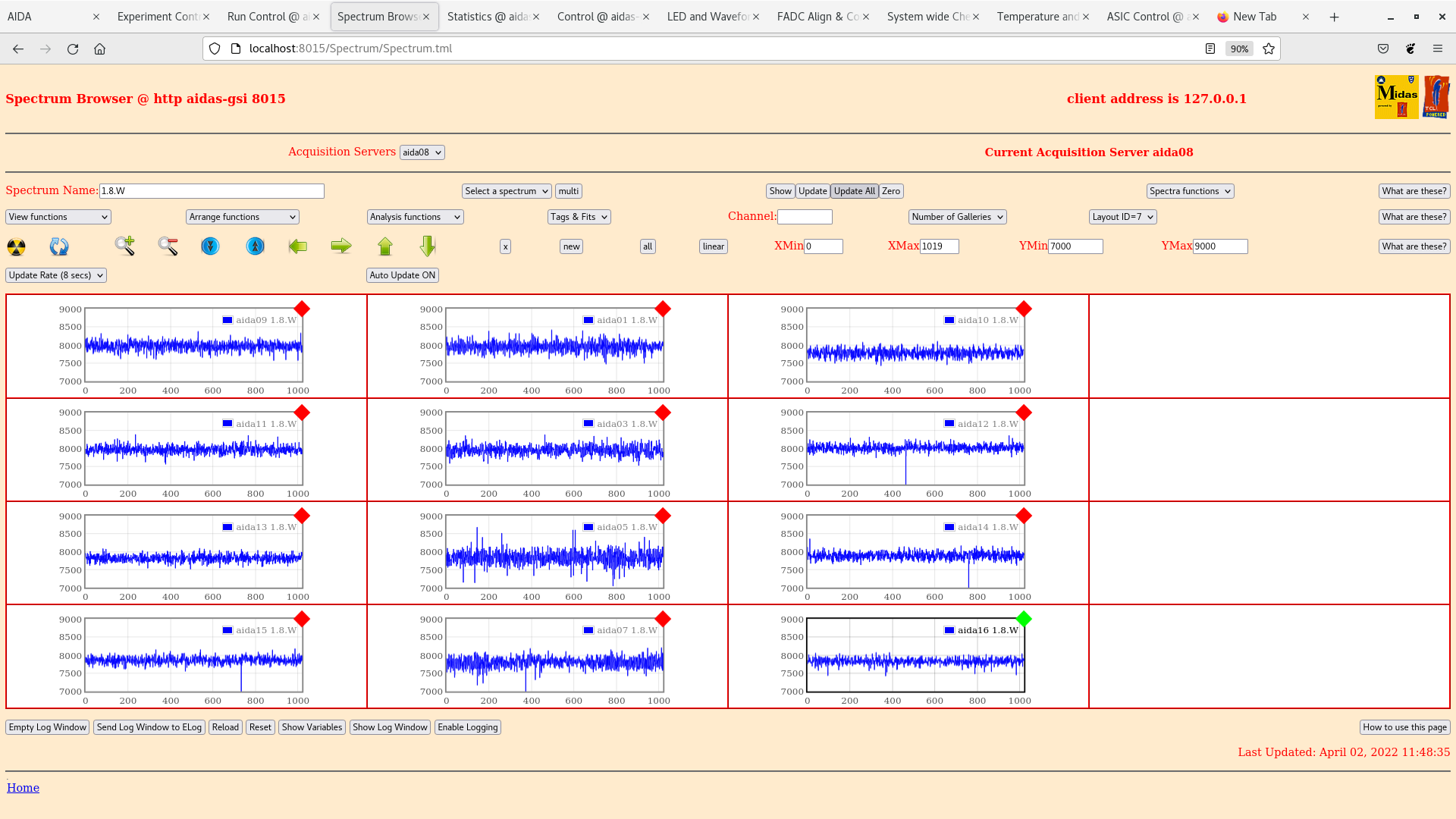

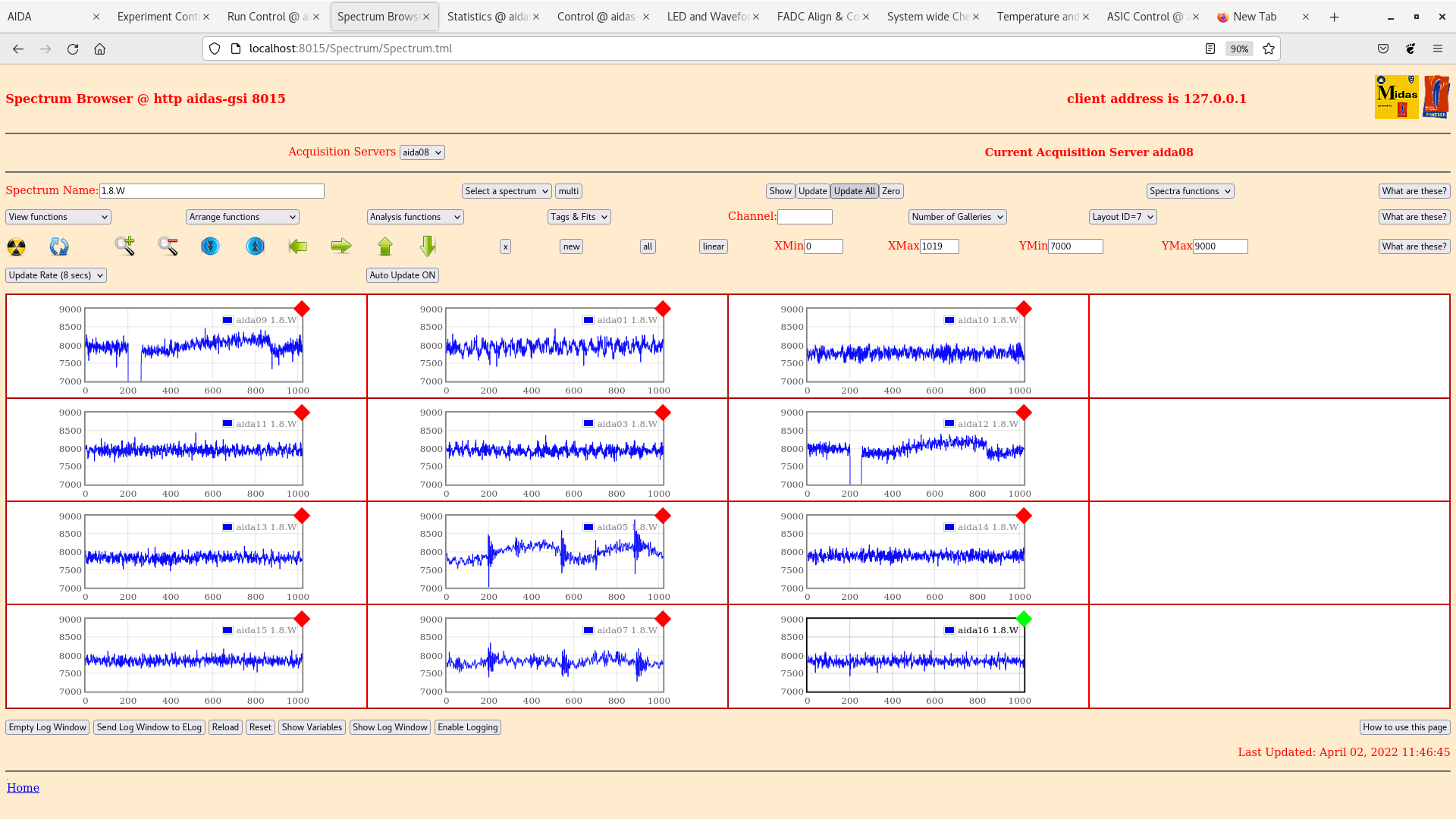

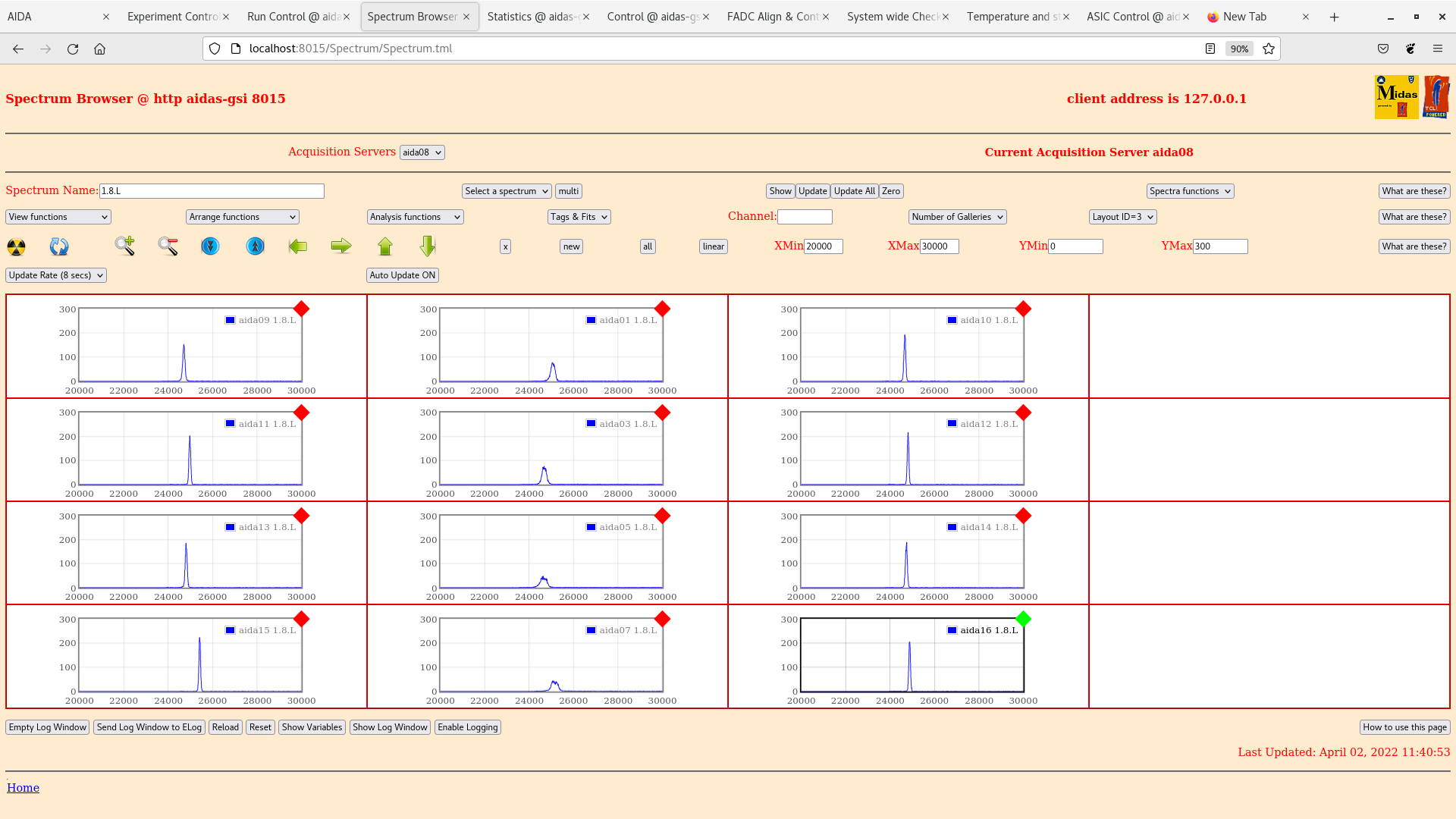

Attachment 9 per FEE64 1.8.L spectra n+n strips

aida04 pulser peak width 387 ch FWHM

Attachment 10 per FEE64 1.8.L spectra p+n strips

aida10 pulser peak width 93 ch FWHM

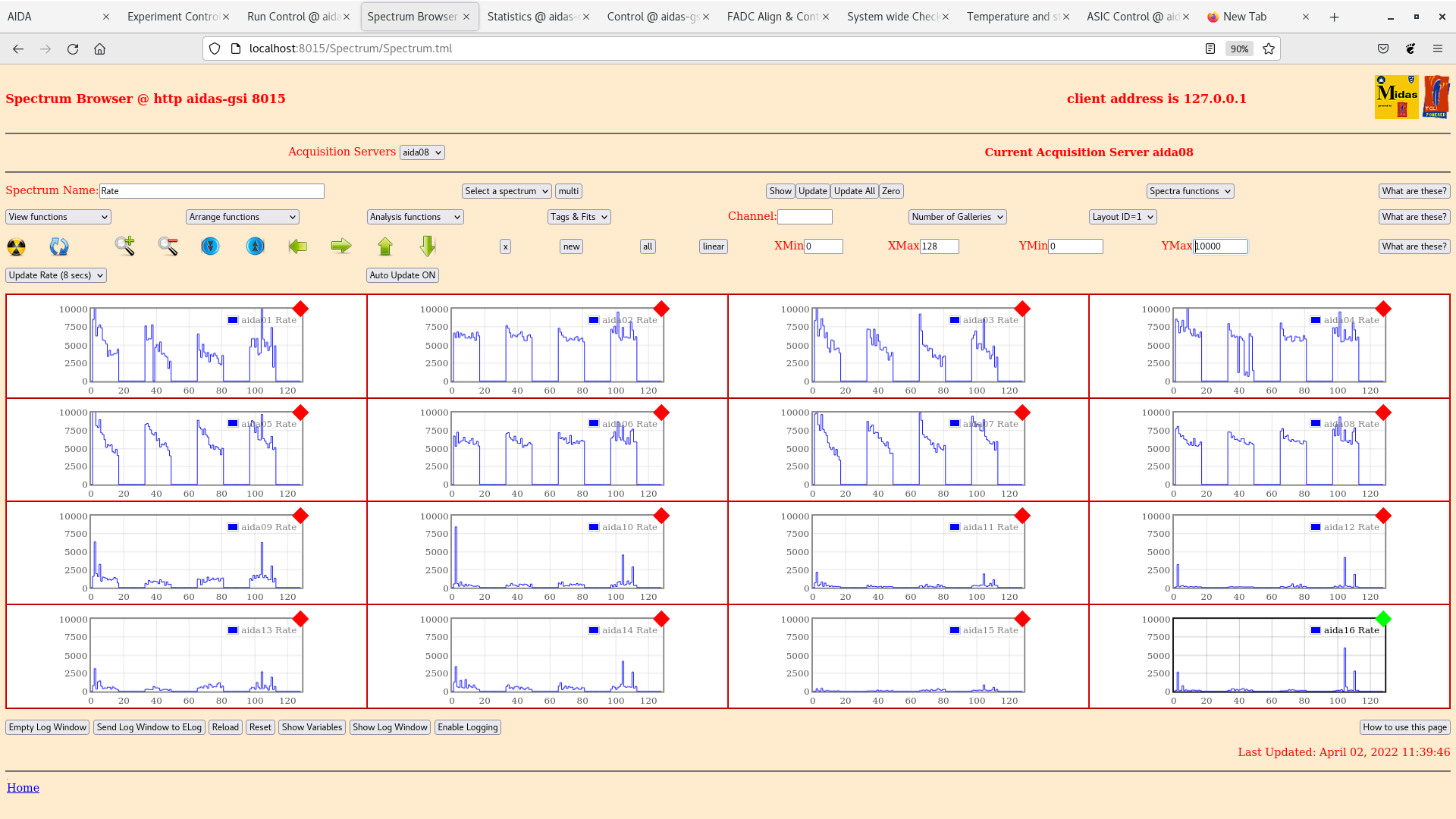

Attachment 11 per FEE64 Rate spectra

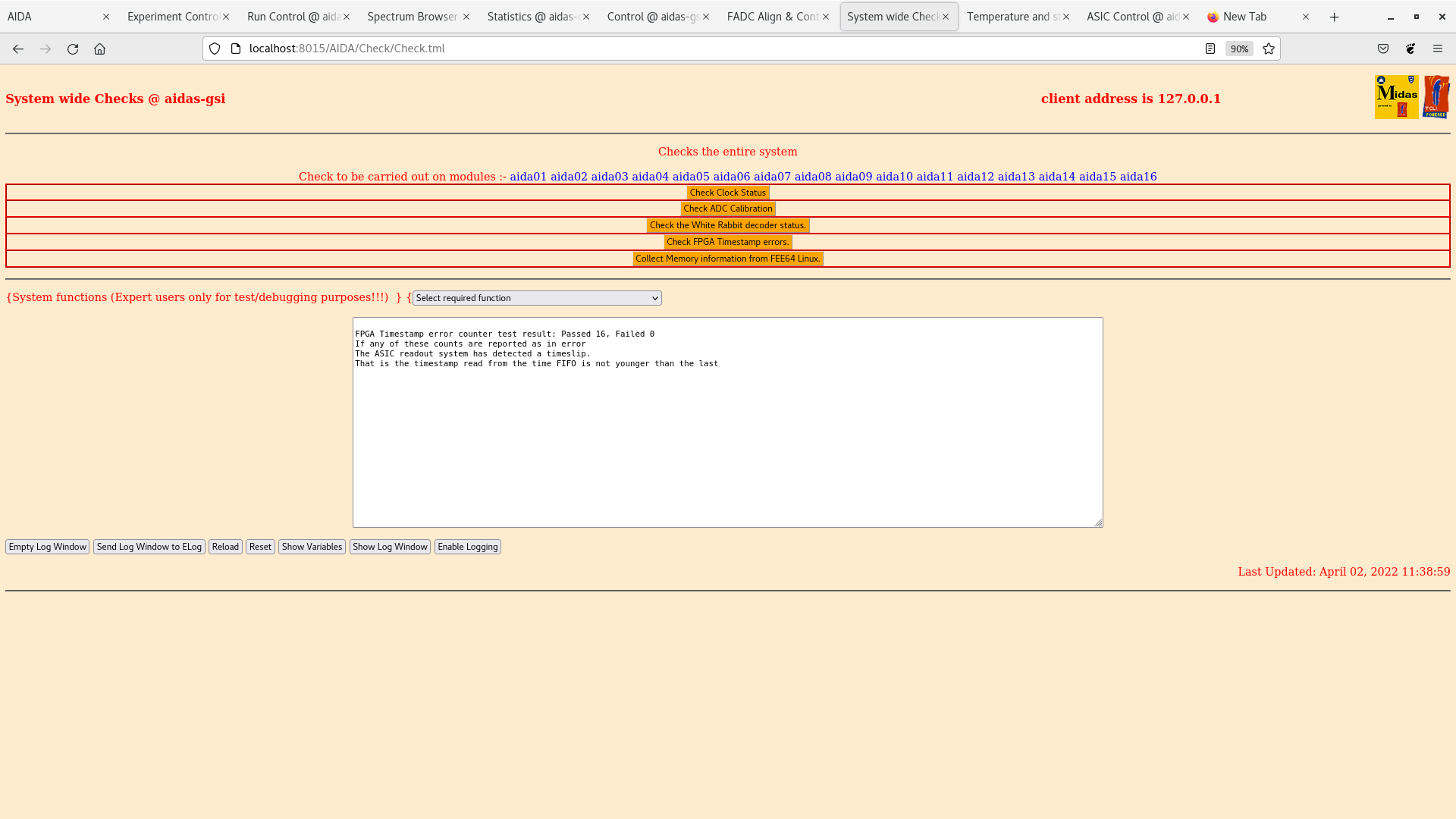

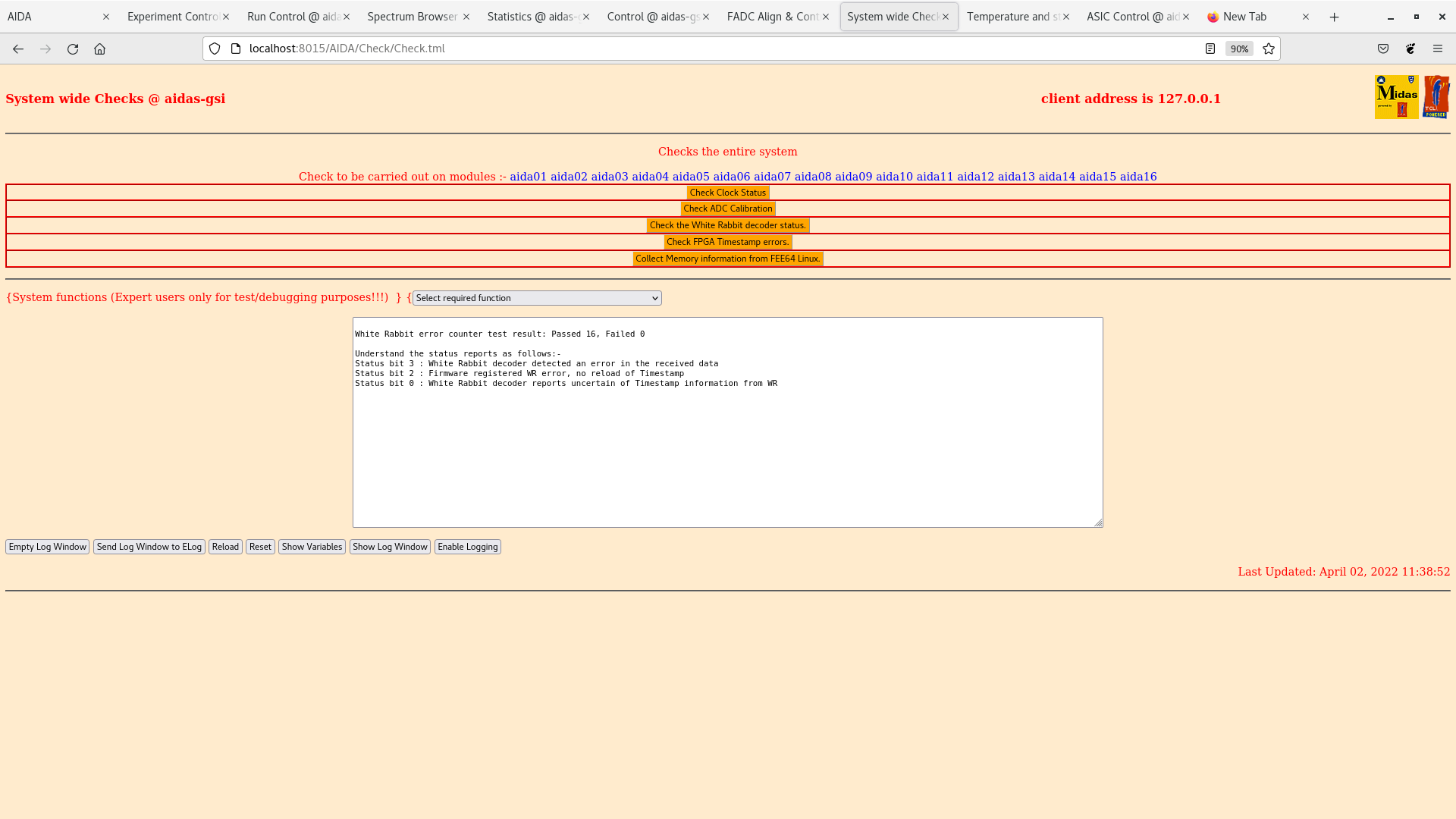

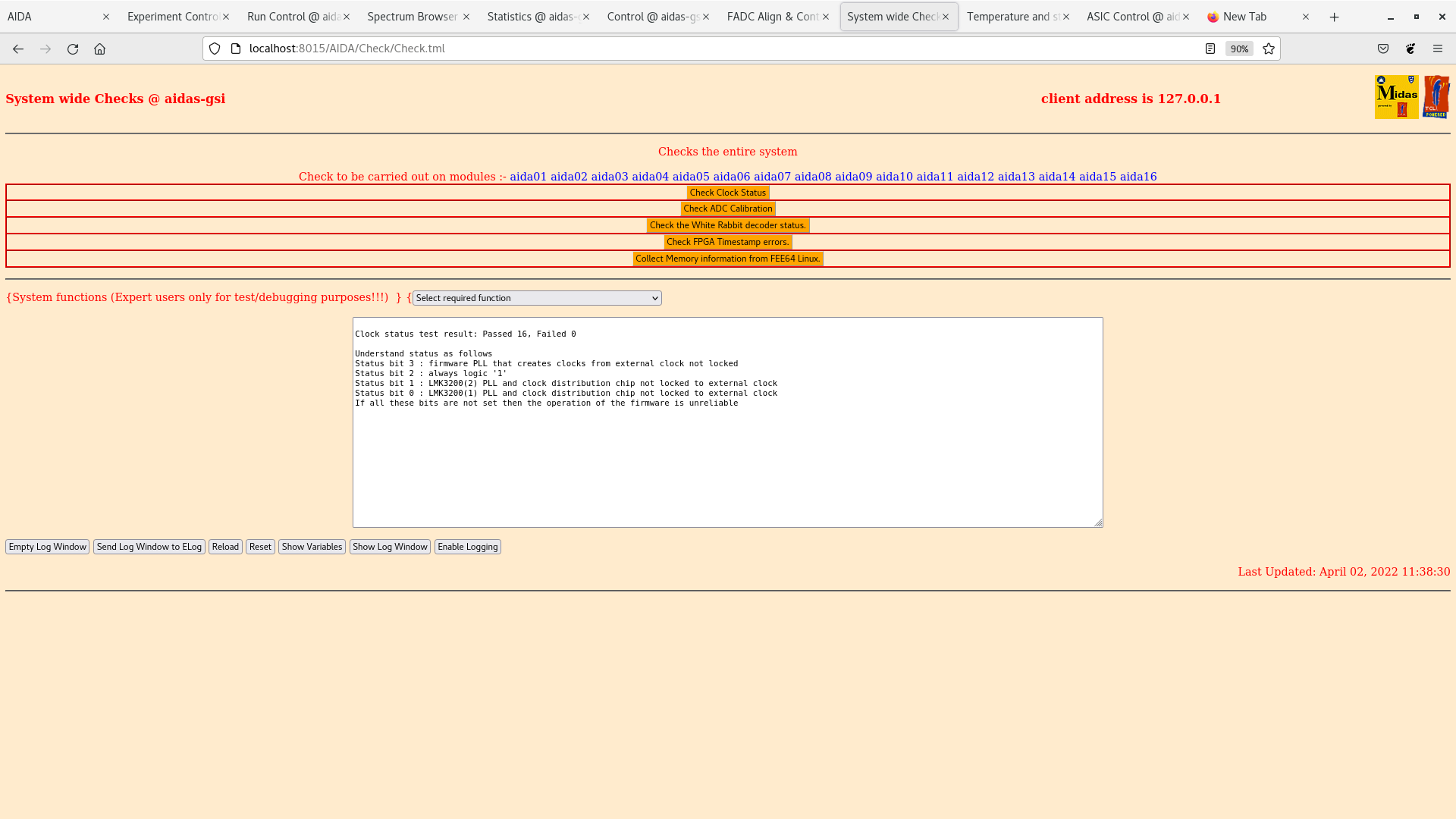

Attachments 12-15 all system wide checks OK

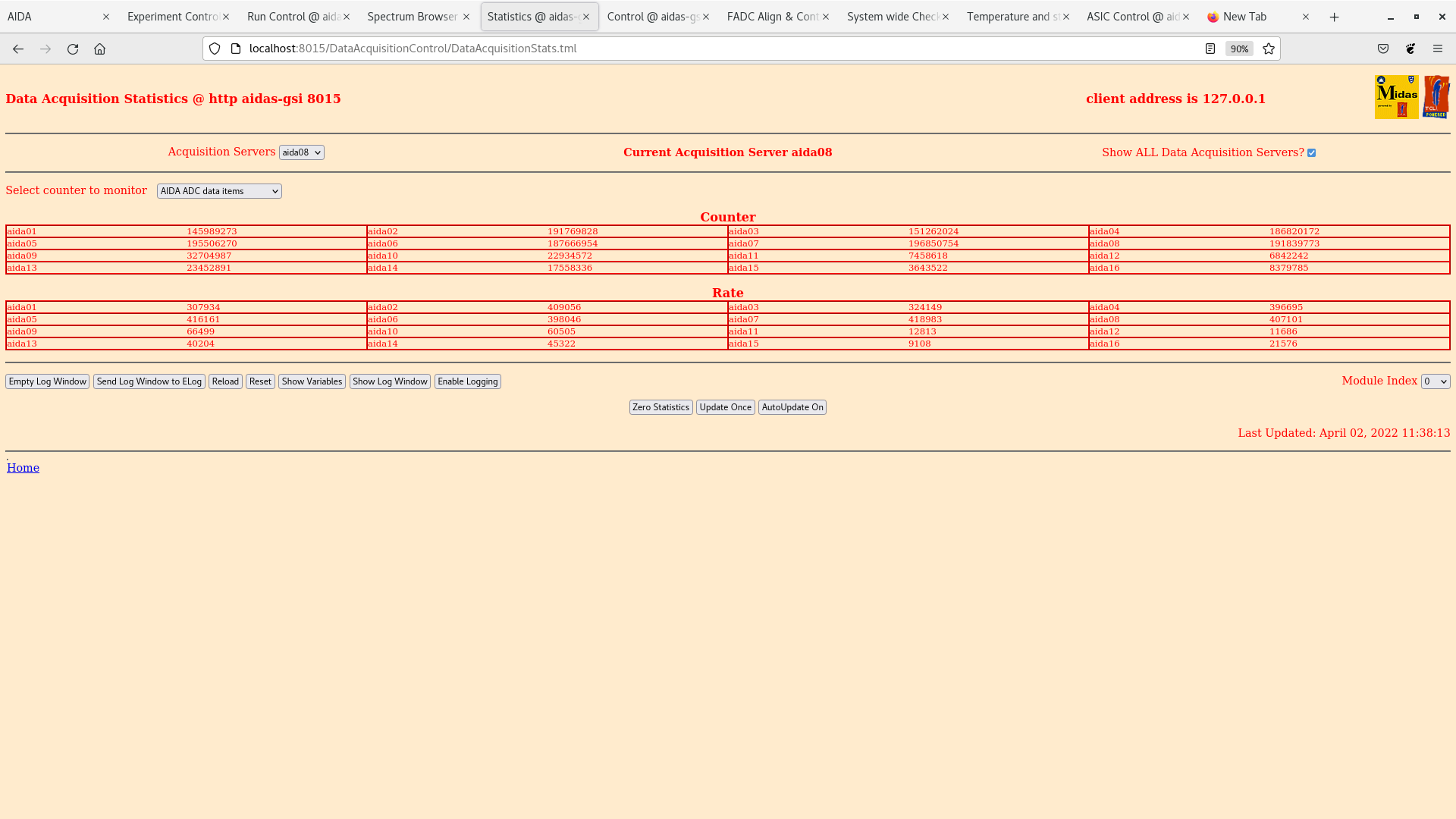

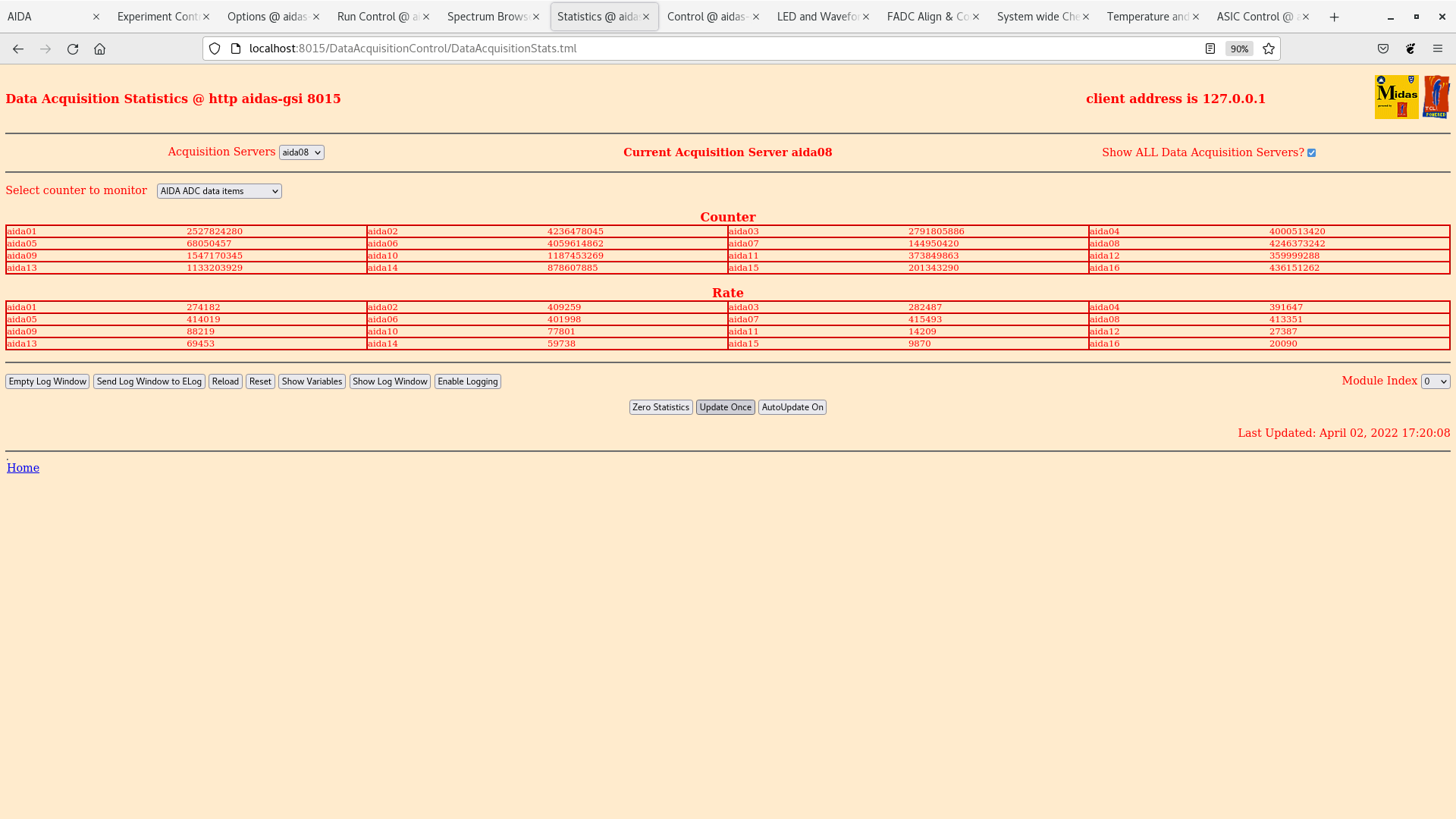

Attachment 16 ADC data item stats

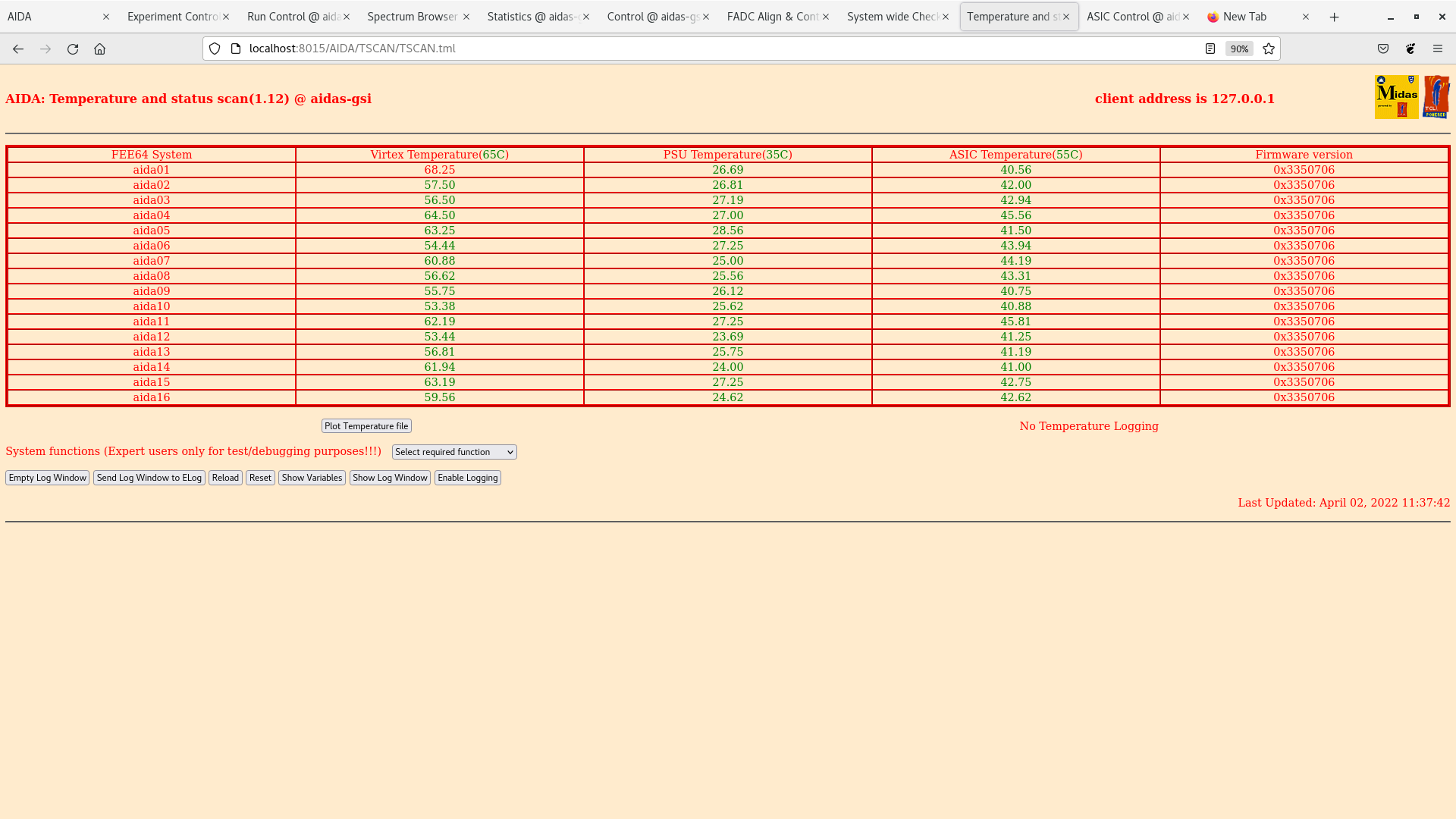

Attachment 17 FEE64 temps OK

Attachment 18 DSSSD bias & leakage currents OK

15.45 check of ASIC settings cf. https://www2.ph.ed.ac.uk/~td/AIDA/Information/Default%20AIDA%20ASIC%20Parameters.txt

Differences from default AIDA ASIC parameters

---------------------------------------------

Input Polarity

Offset Title Positive Negative Notes

12 slow comparator threshold 0x2f->0xa 100keV nominal

14 fast comparator threshold HEC 0xf->0x02 200MeV nominal

15 fast comparator threshold LEC/MEC 0xf->0xff > LEC/MEC nominal FSR

18 preAmp reference 0xb2 0x20->0x30

21 Ibias LF feedback 0x08 0xb->0xf

26 diode link threshold 0xca->0xbf 0x11->0x23 decrease switch threshold

(front) p+n junction strips - positive input polarity

(back) n+n ohmic strips - negative input polarity

All looks OK - variations from default settings are those used at RIKEN

16:45 FEE64 adaptor PCB config

LK1 LK2 LK3 LK4

p+n n/c o * o

n+n o o n/c o

o = jumper fitted

n/c = jumper not fitted

* = top, middle FEE64s - n+n bias ring ground for Si wafer #2

bottom, middle FEE64s - DSSSD PCB gnd

DSSSD#1 & #2 bias via standard coaxial cable to top p+n FEE64 adaptor PCBs

17.05 aida09 or aida13 cable braid not secured to ground - cable tag dia too large - now sandwiched between correctly sized cable tags

no obvious difference to adc data item rates

17.20 LK1 removed for all n+n PCBs

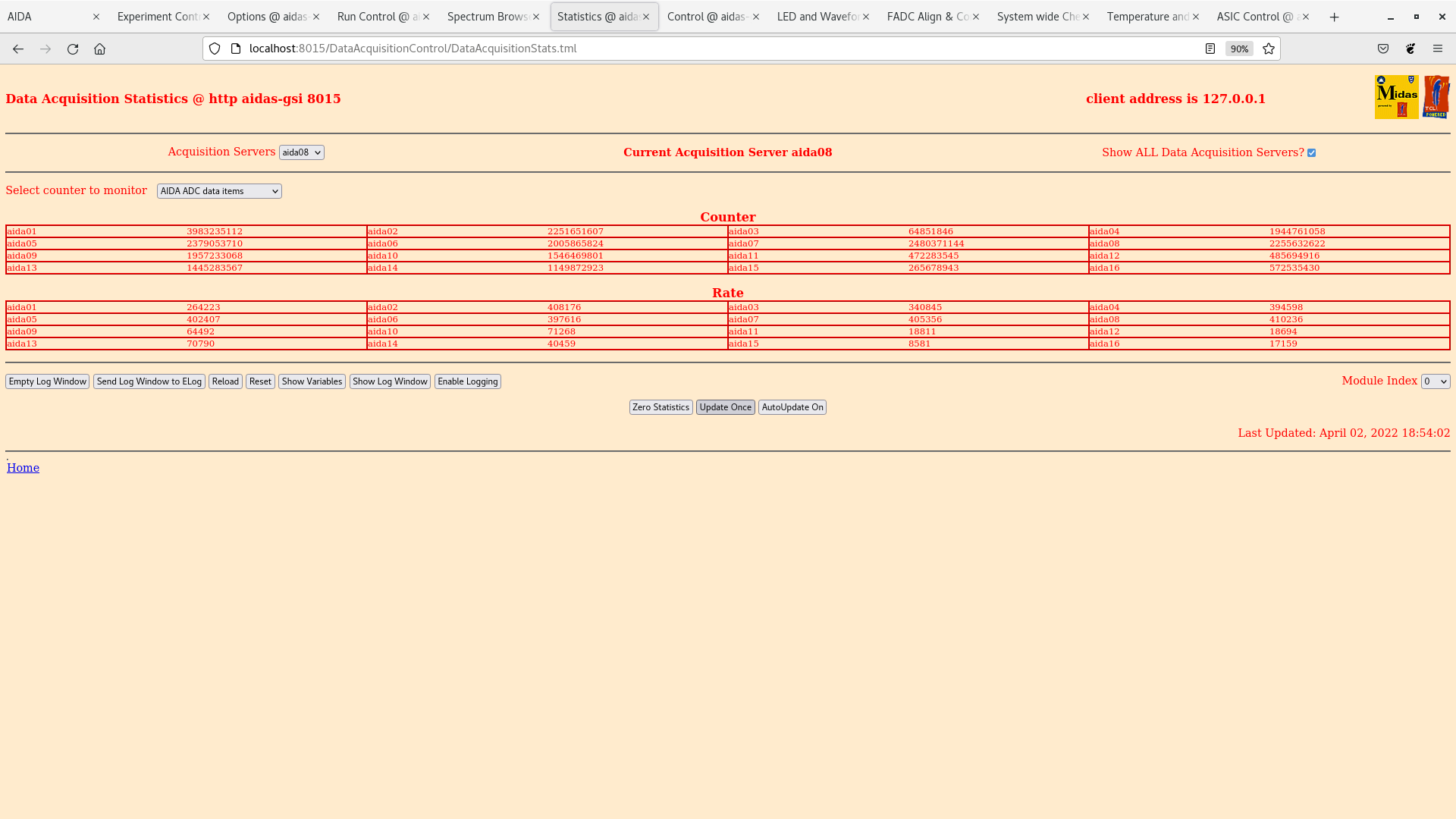

attachment 19 - adc data item stats

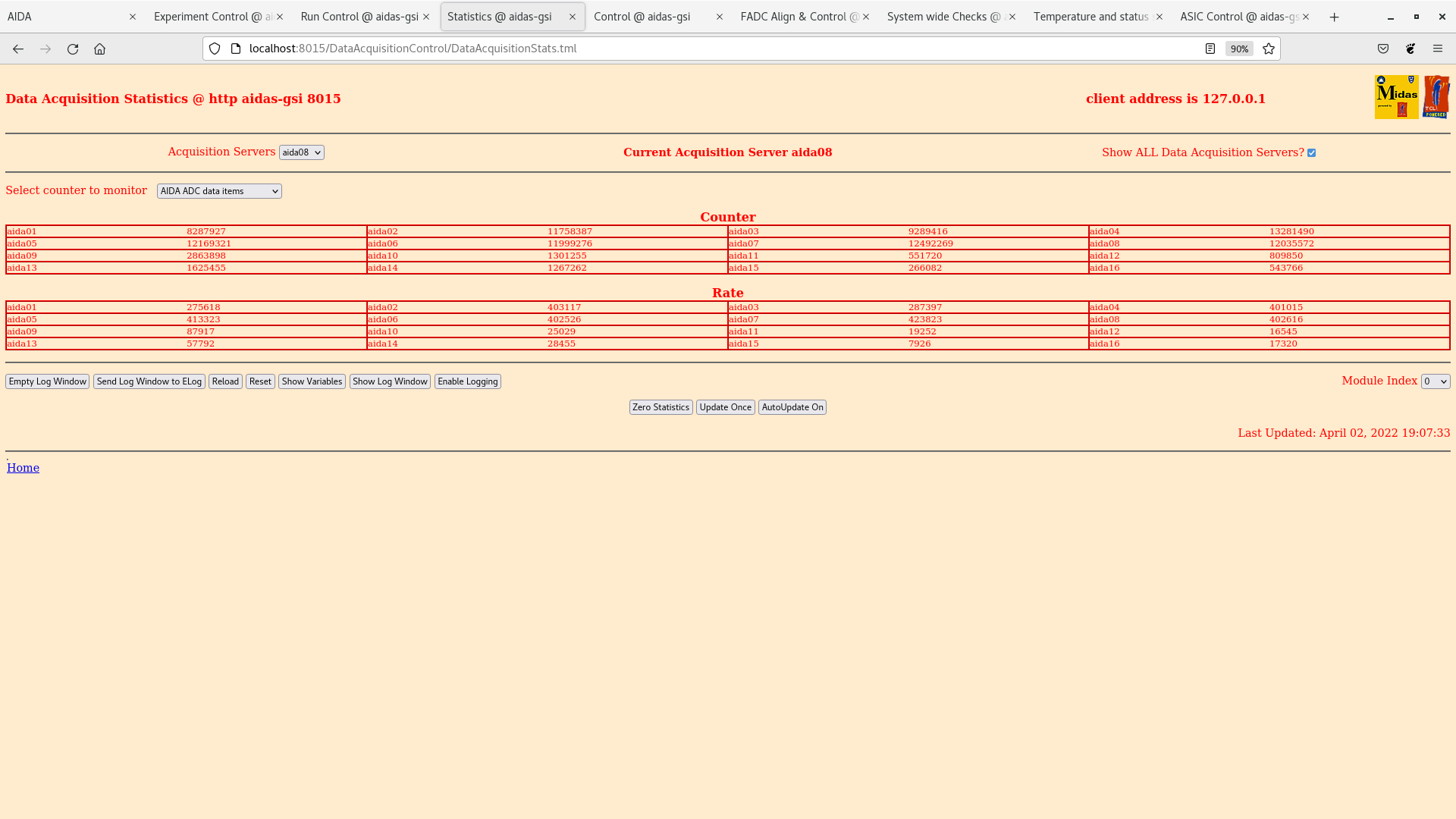

18.55 LK2/LK4 removed for all n+n PCBs

attachment 20 - adc data item stats

19.10 power cycle FEE64s

attachment 21 - adc data item stats |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|