|

|

|

AIDA

GELINA

BRIKEN

nToF

CRIB

ISOLDE

CIRCE

nTOFCapture

DESPEC

DTAS

EDI_PSA

179Ta

CARME

StellarModelling

DCF

K40

MONNET

|

| DESPEC |

|

|

|

|

Message ID: 408

Entry time: Sun Apr 3 10:56:11 2022

|

| Author: |

TD |

| Subject: |

Sunday 3 April |

|

|

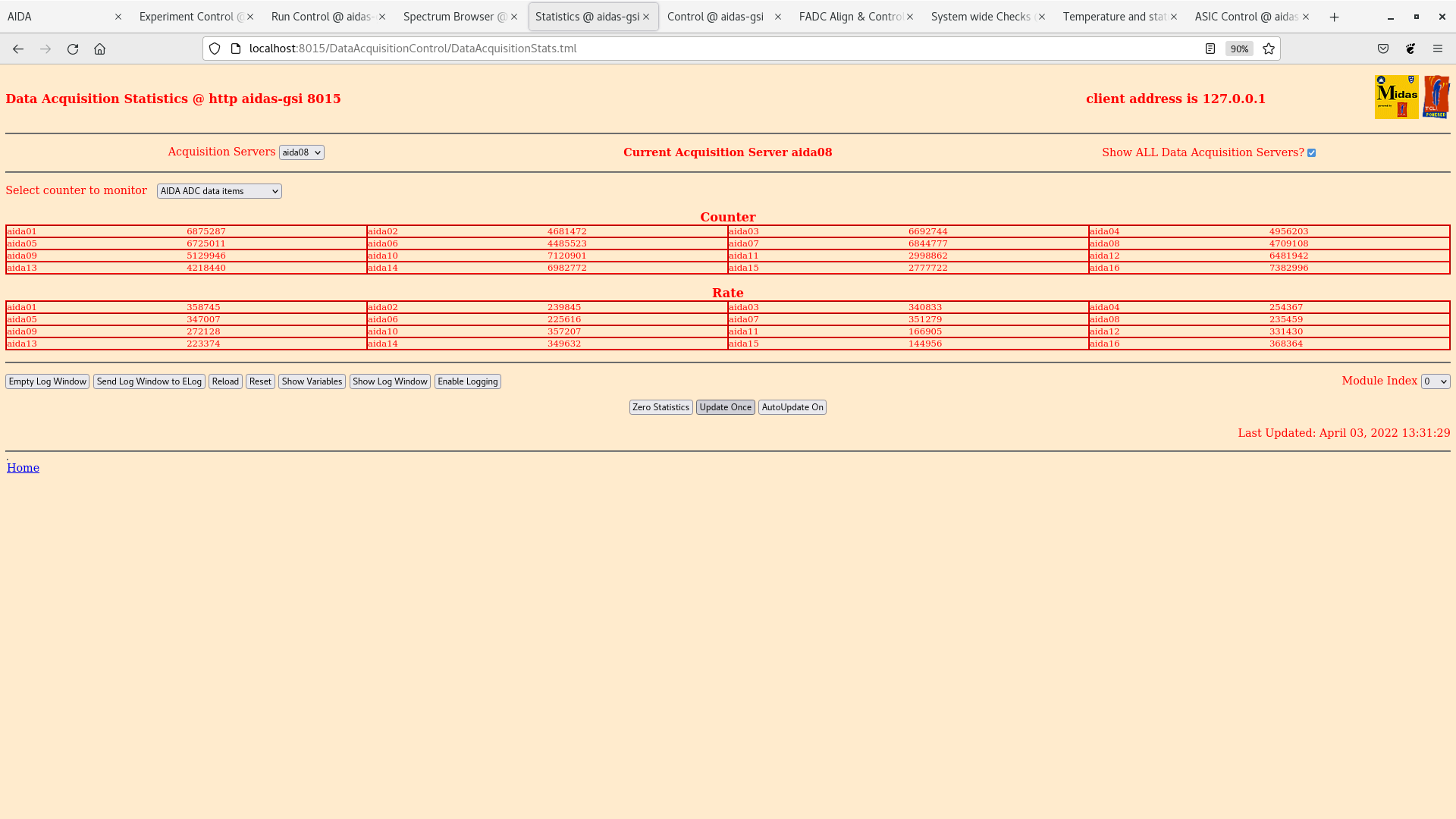

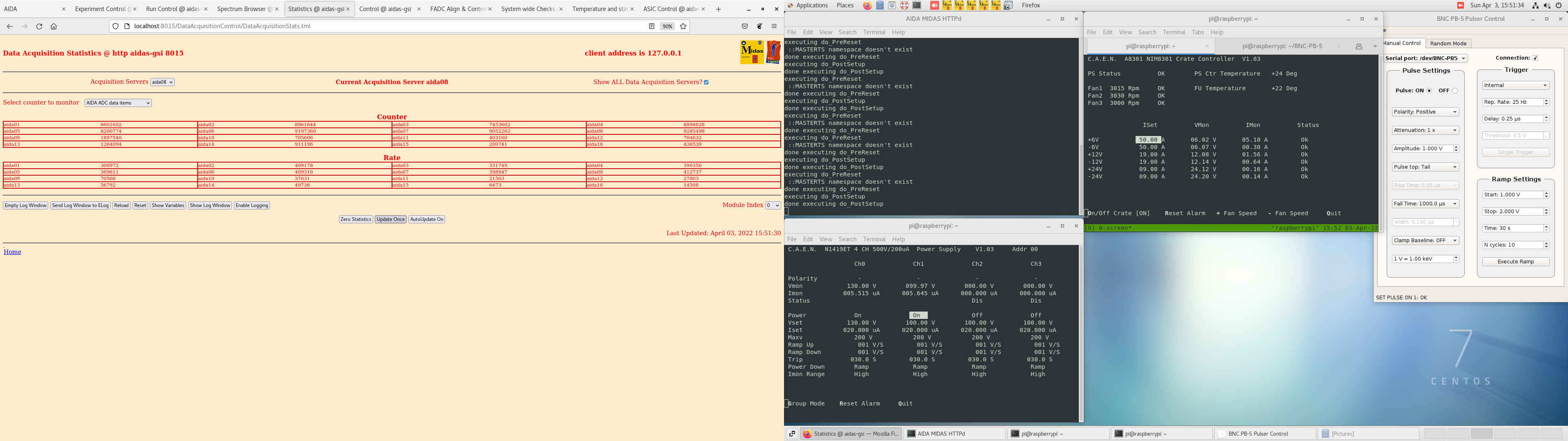

all system wide checks OK *except* aida10 failed ADC calibration

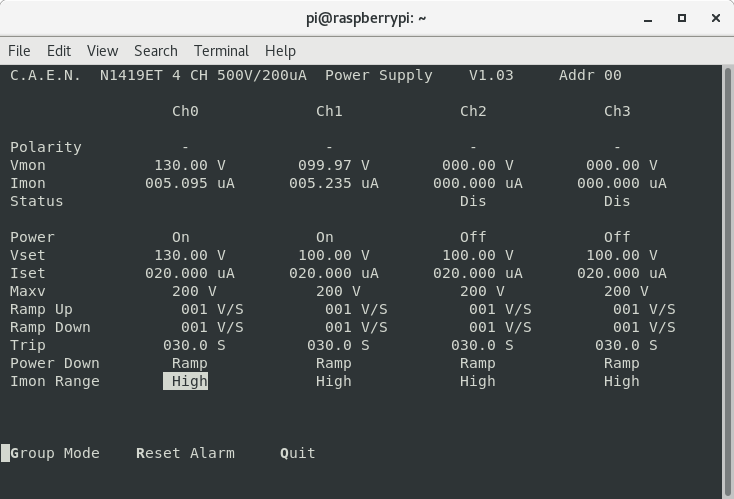

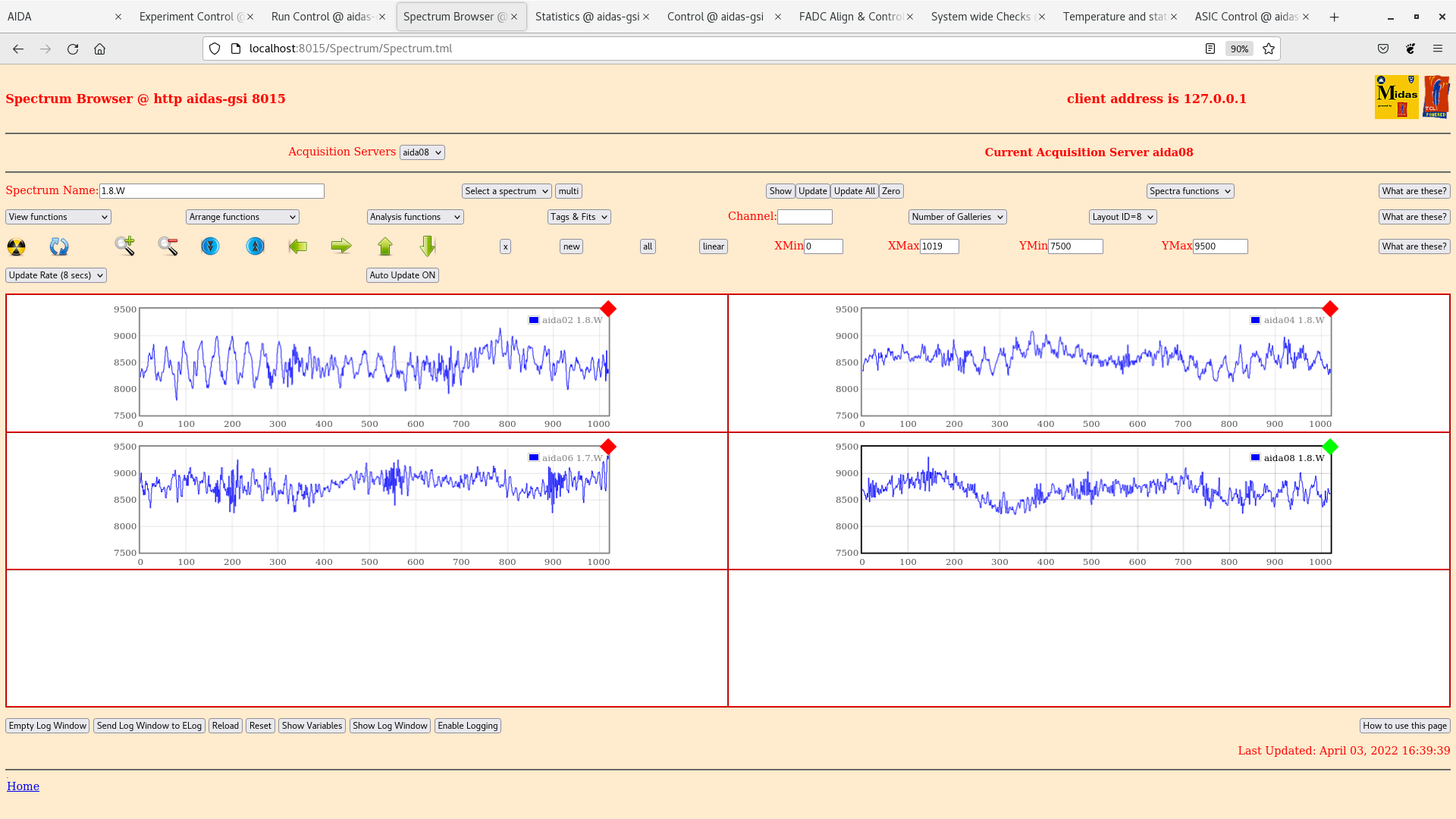

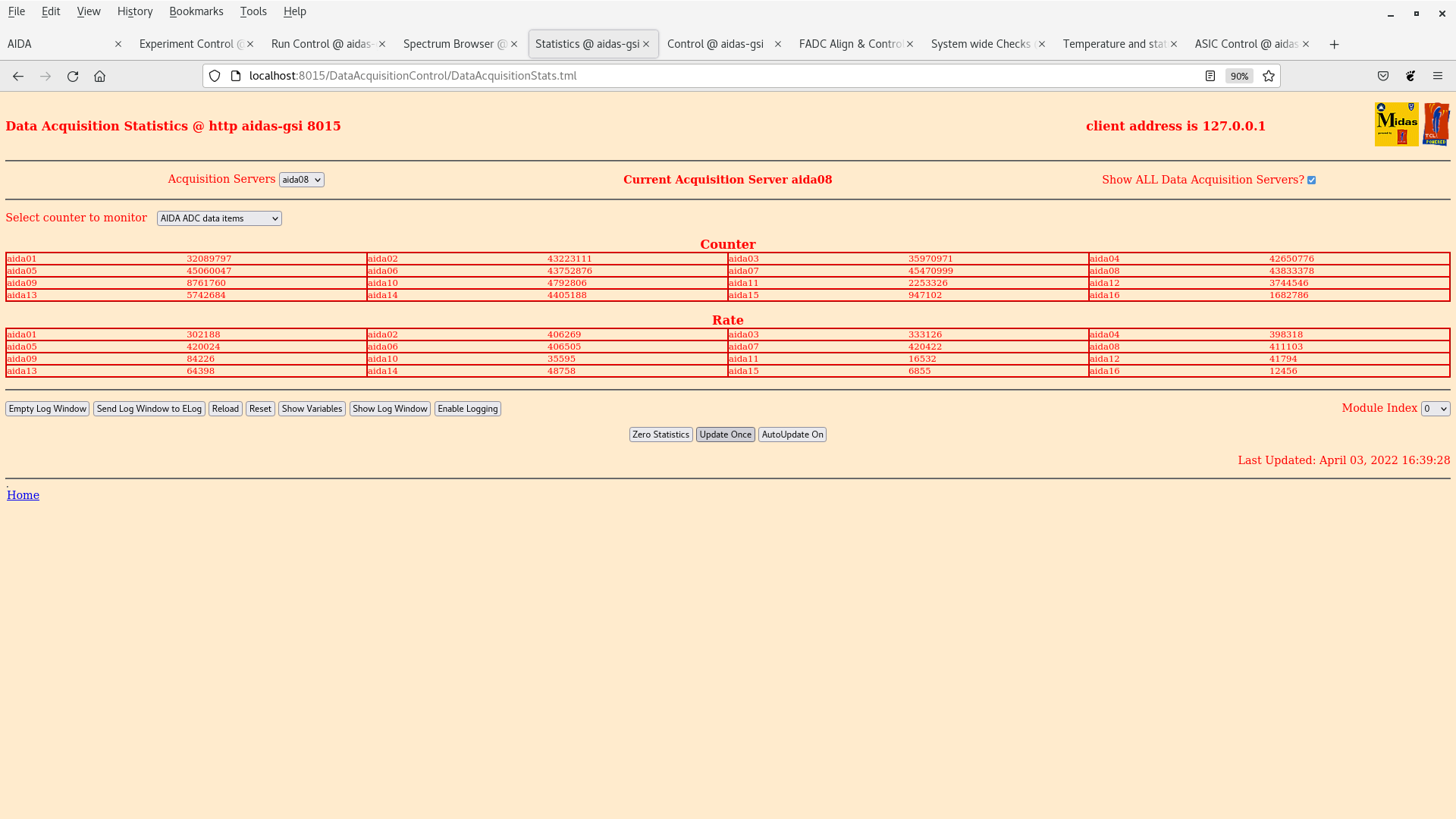

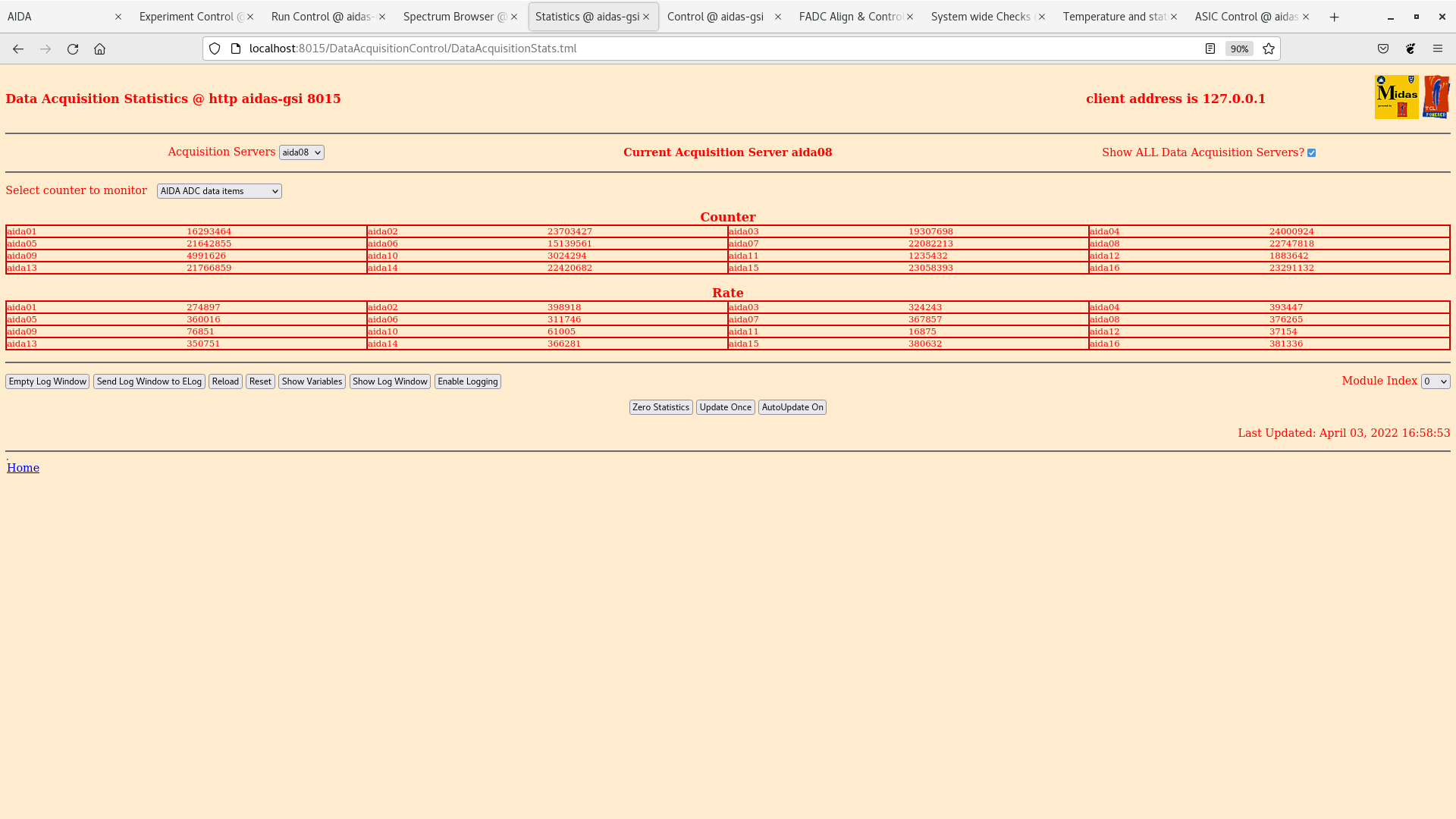

Attachment 1 ADC data item stats

Attachment 2 FEE64 temps OK

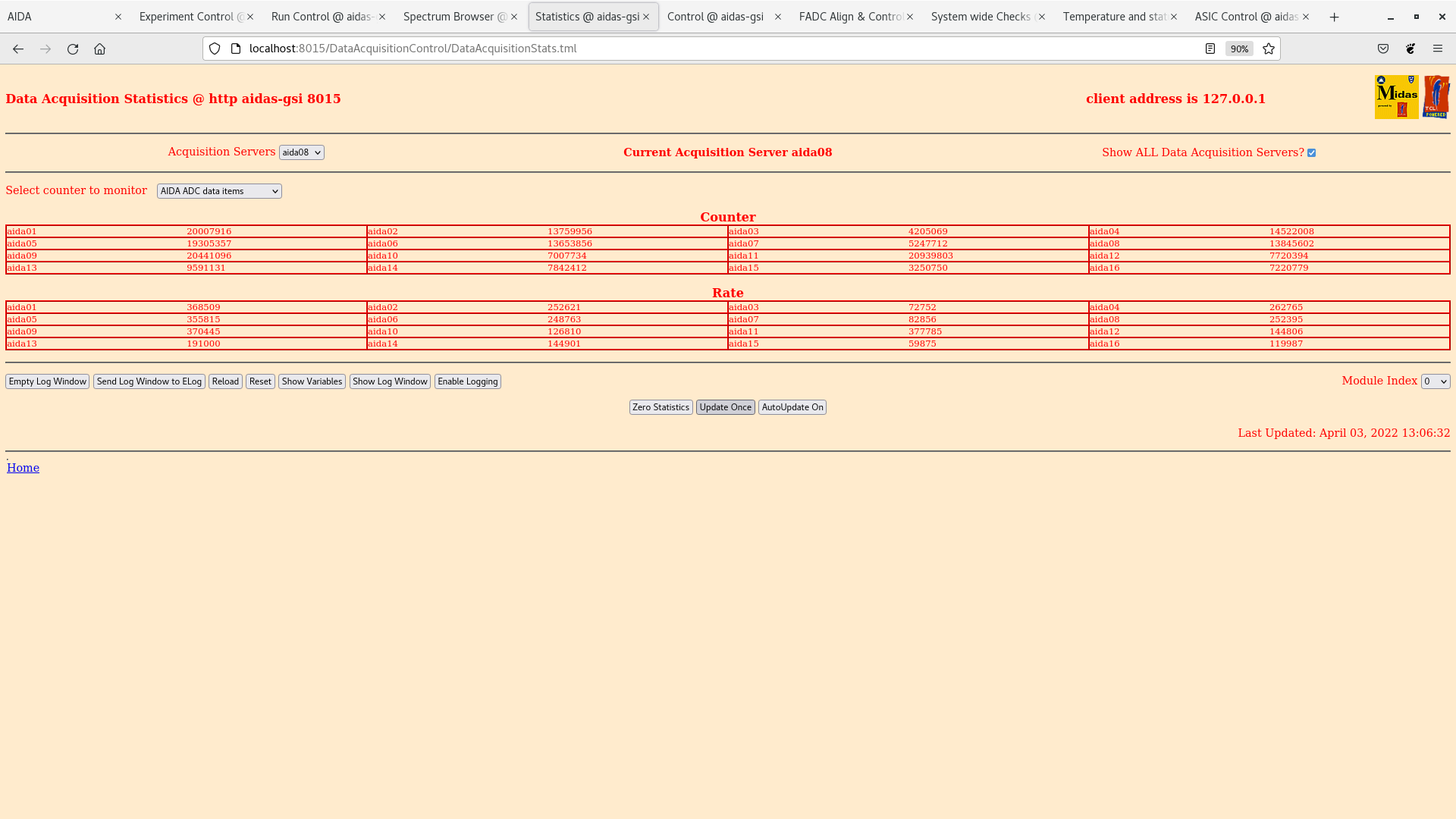

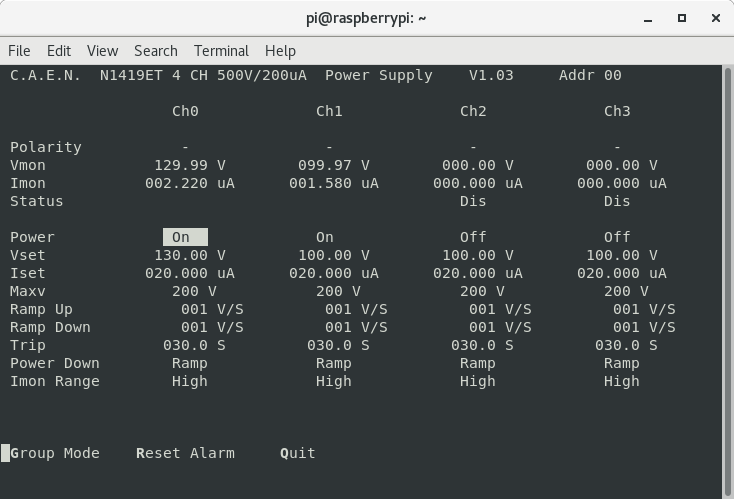

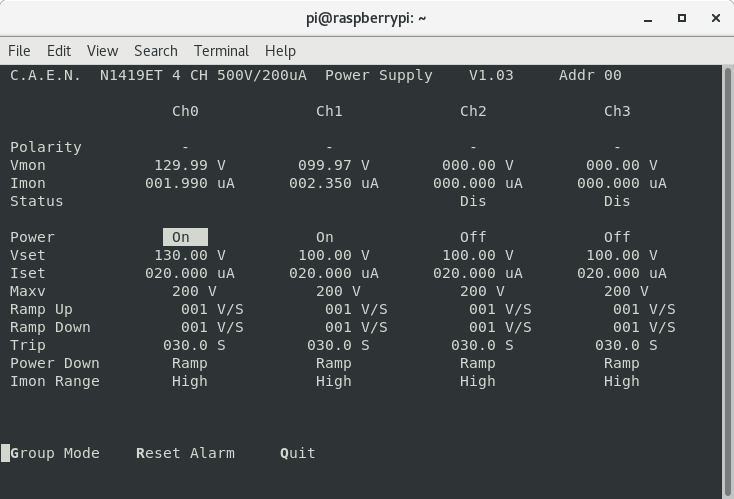

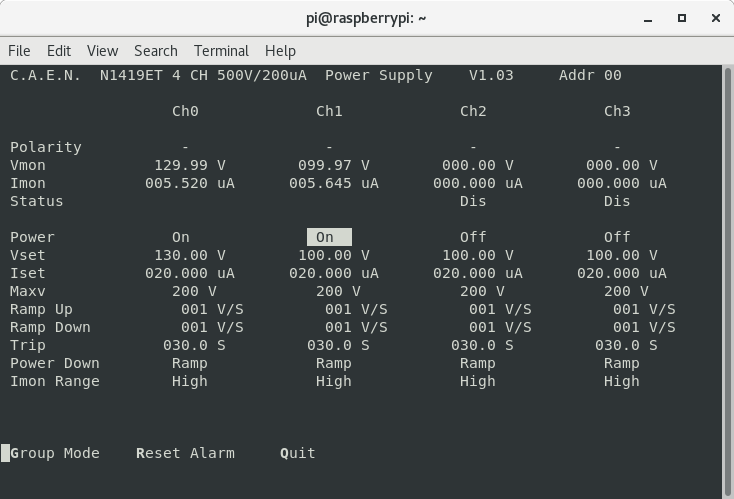

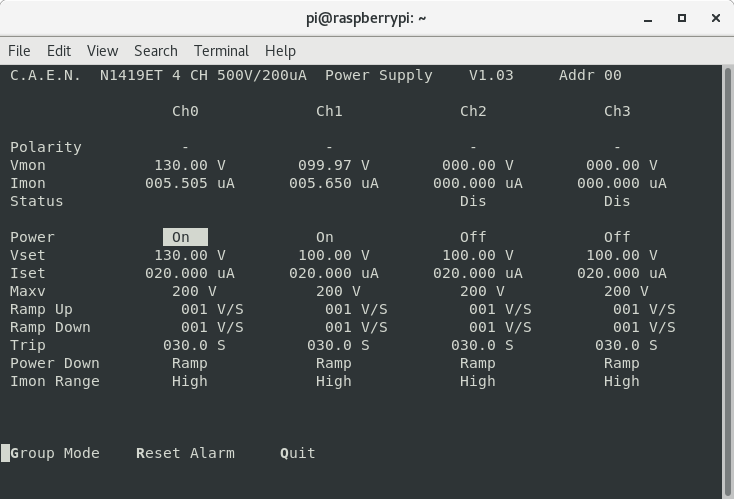

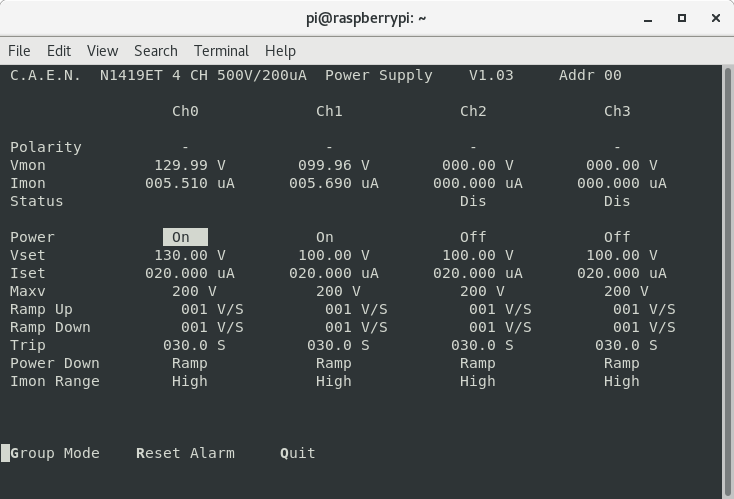

Attachment 3 DSSSD bias & leakage currents OK

DSSSD bias to left (looking upstream) wafer *only*

FEE64s 10 & 12, 14 & 16

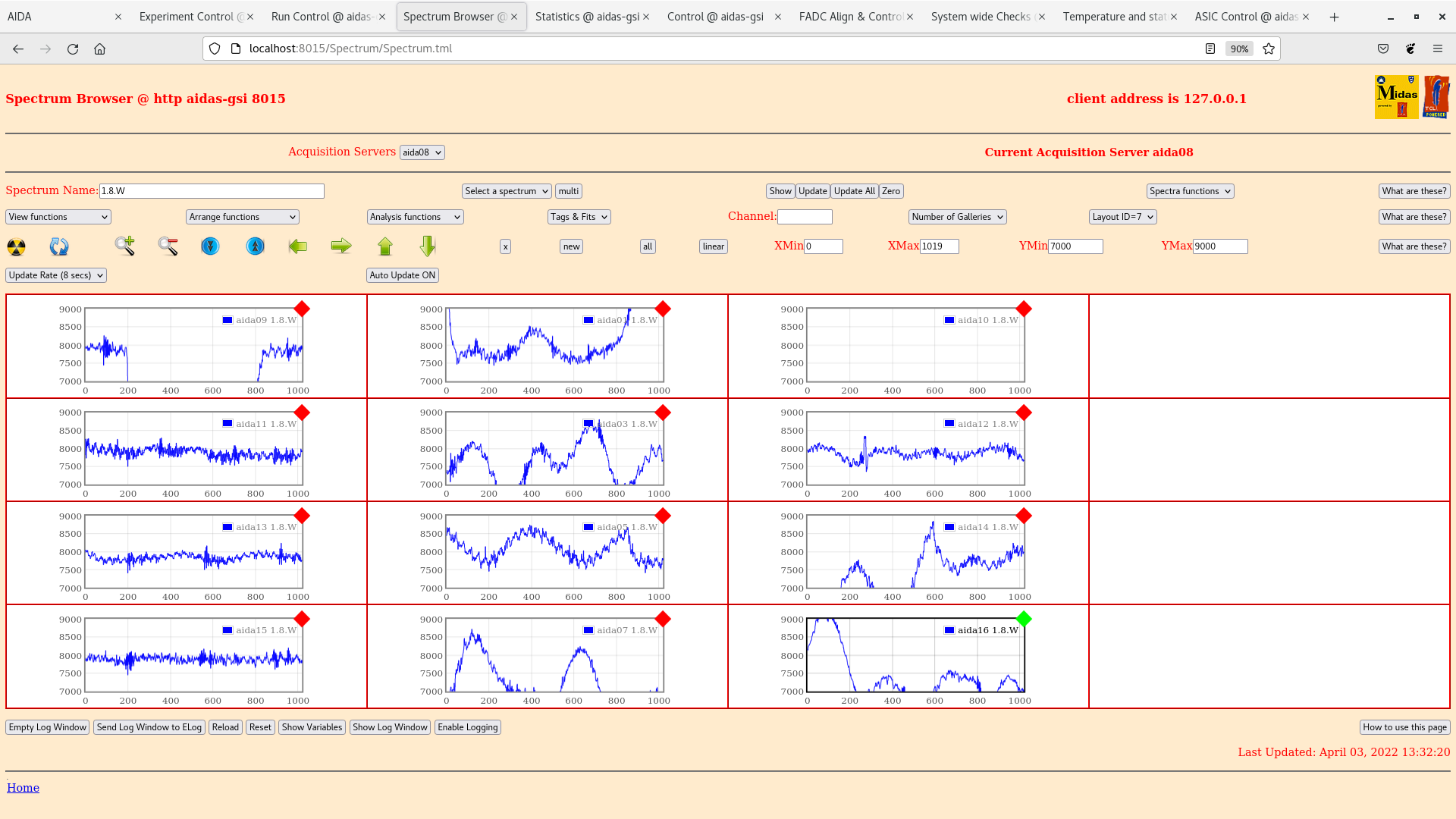

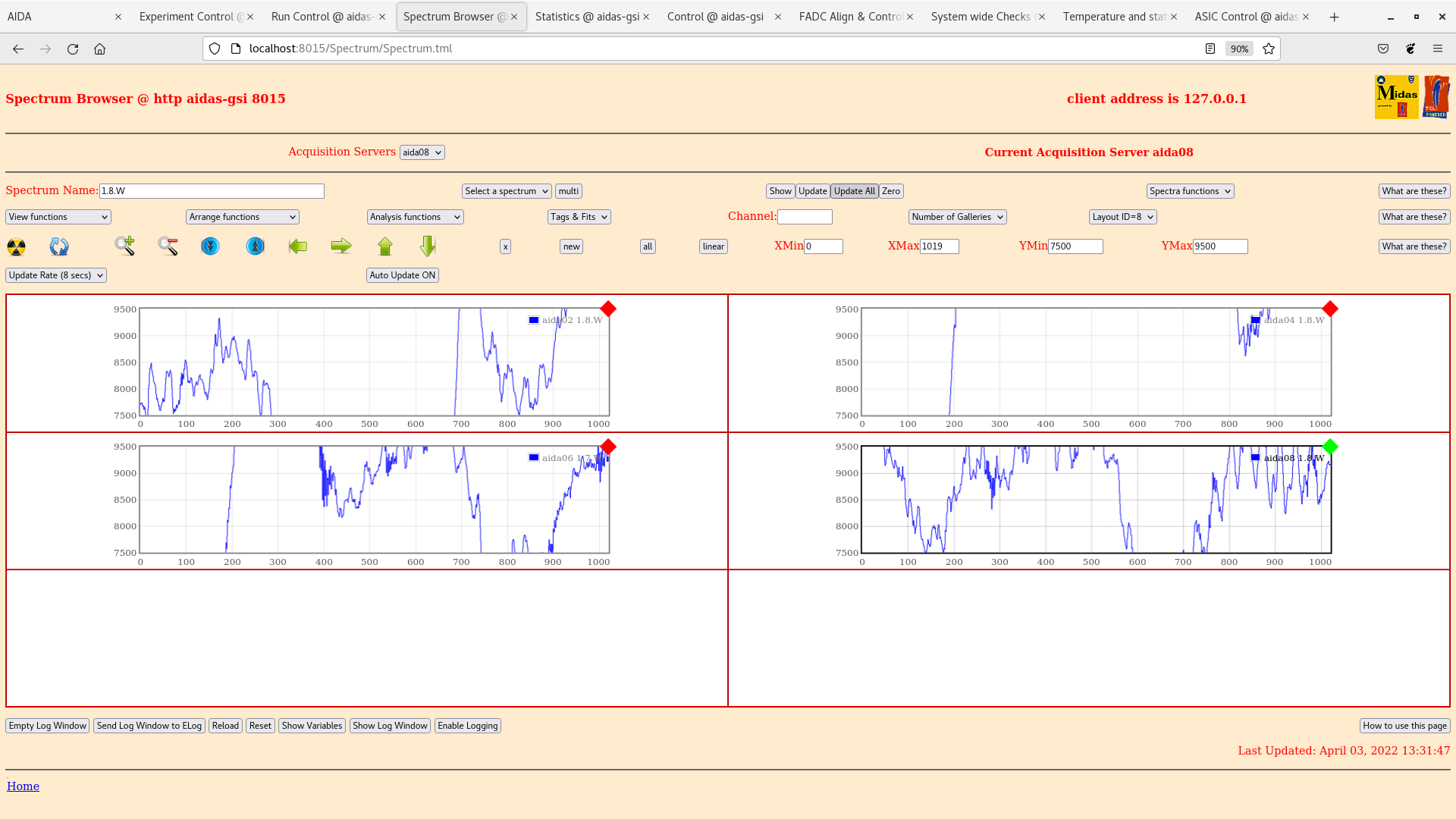

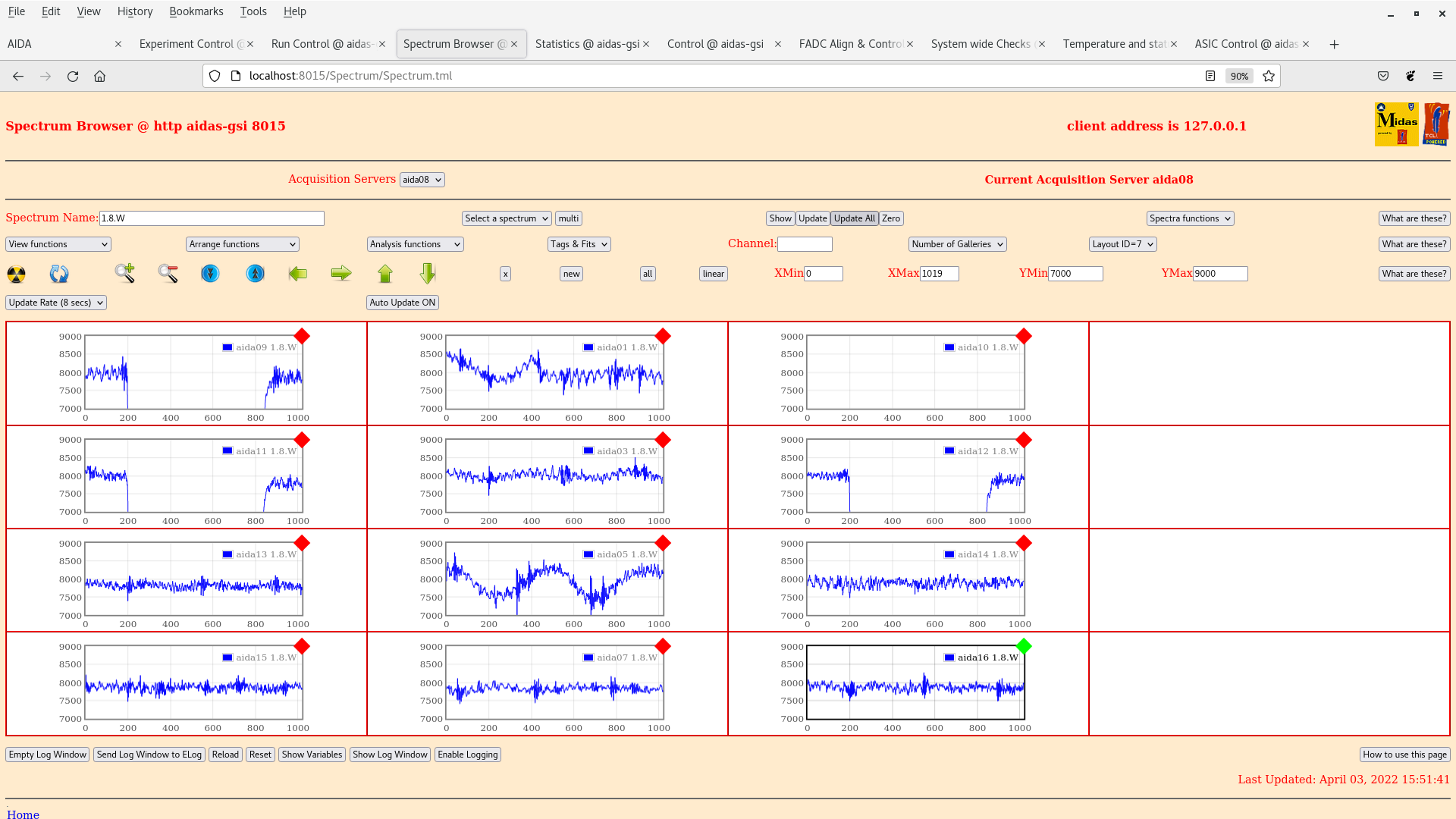

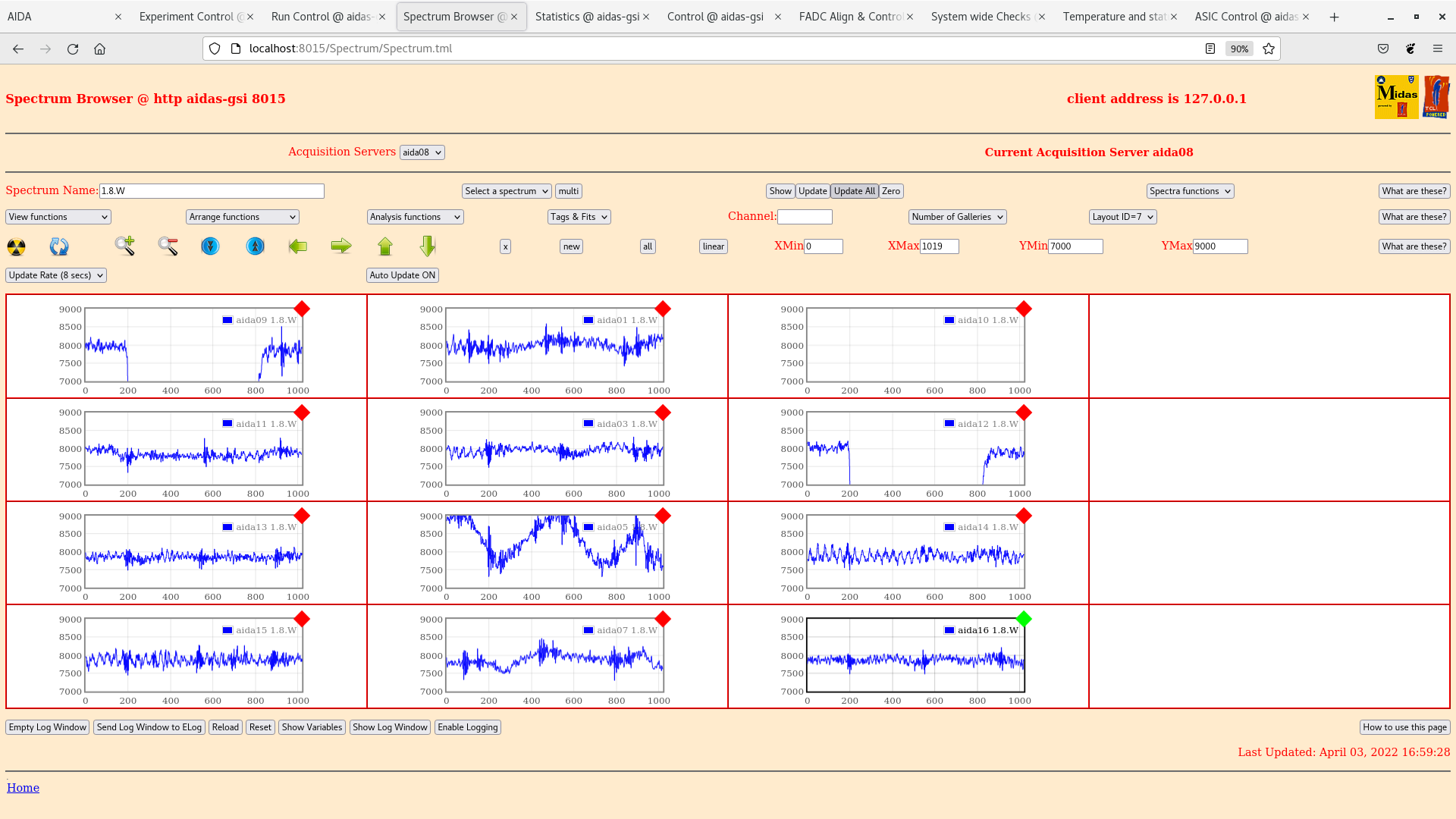

Attachments 4 & 5 1.8.W spectra 20us FSR

Attachment 6 ADC data item stats

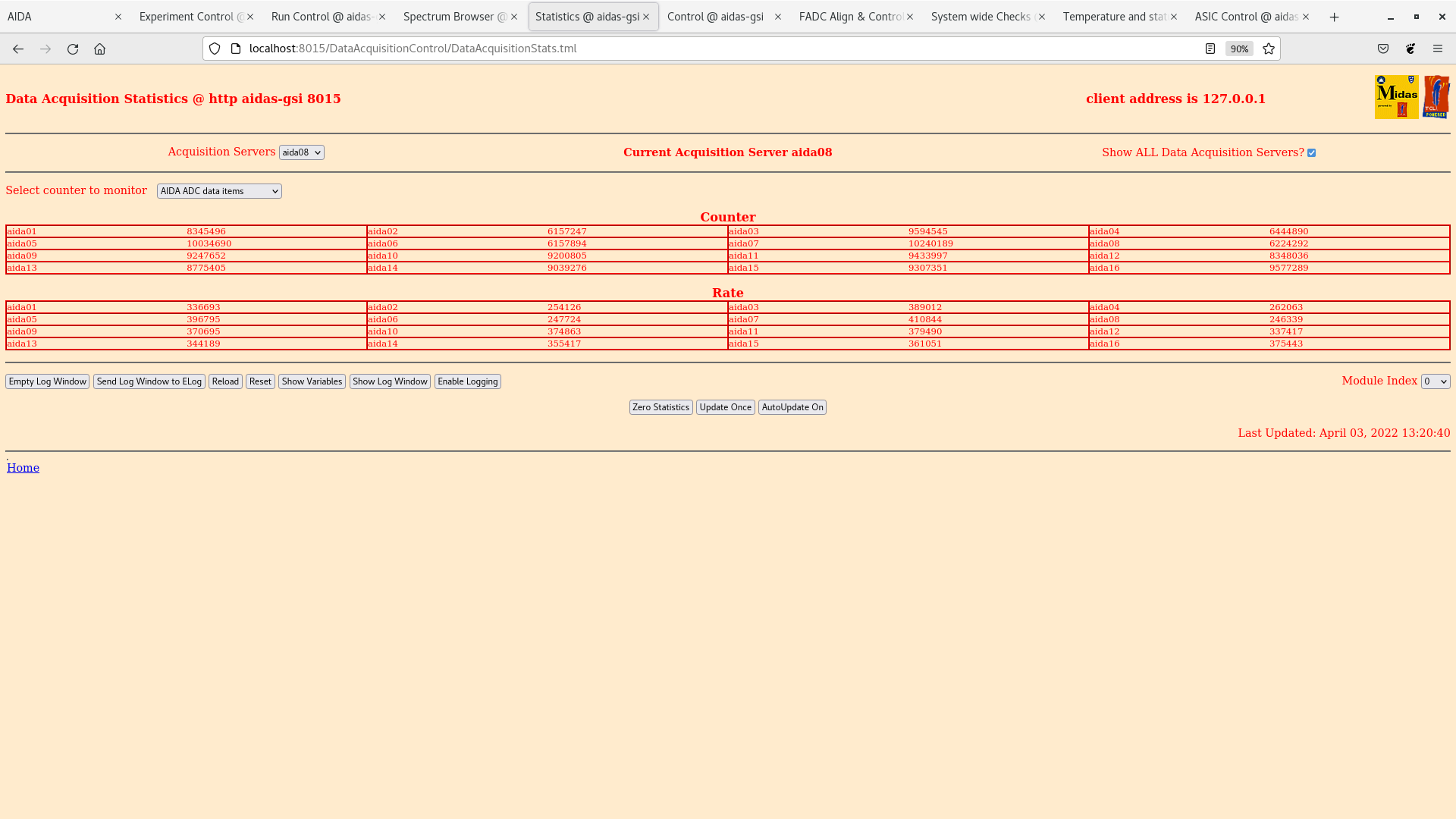

Attachment 7 DSSSD bias & leakage current

ASIC check all FEE64s

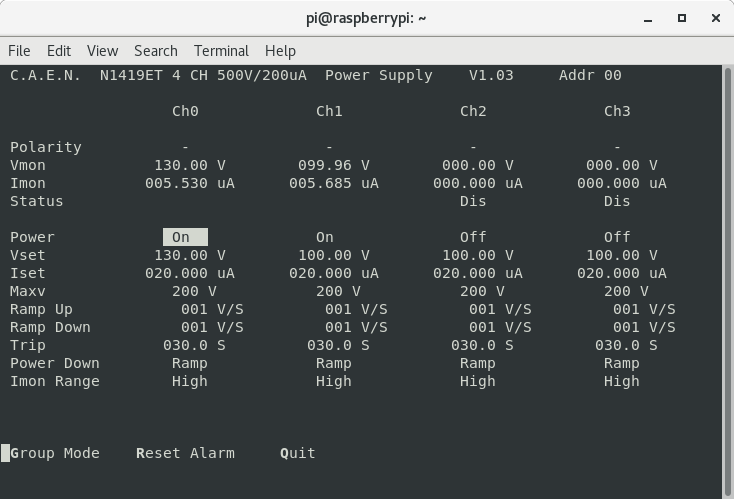

DSSSD bias to middle (looking upstream) wafer *only*

FEE64s 1 & 3, 5 & 7

Attachments 8 & 9 1.8.W spectra 20us FSR

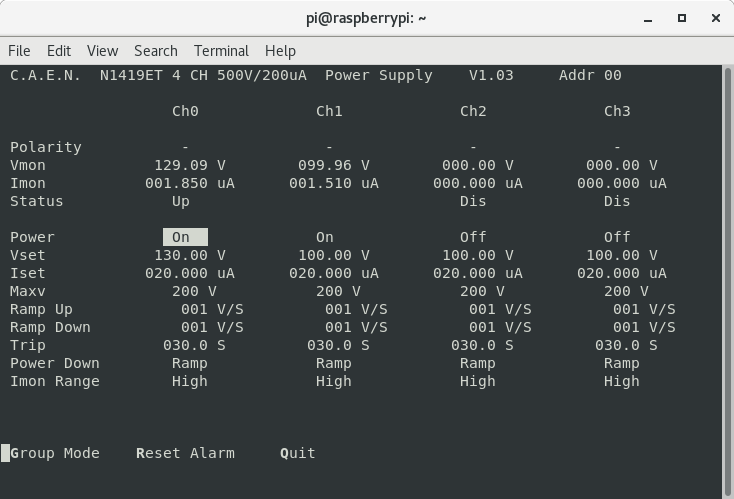

Attachment 10 ADC data item stats

Attachment 11 DSSSD bias & leakage current

ASIC check all FEE64s

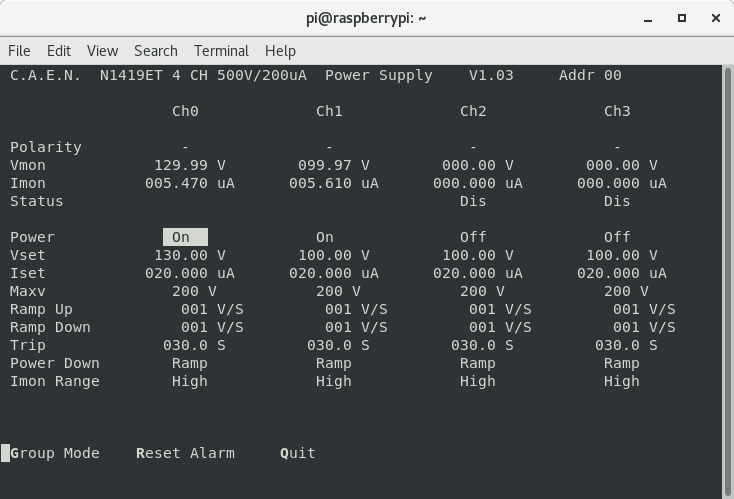

DSSSD bias to right (looking upstream) wafer *only*

FEE64s 9 & 11, 13 & 15

Attachments 12 & 13 1.8.W spectra 20us FSR

Attachment 14 ADC data item stats

Attachment 15 DSSSD bias & leakage current

Conclusions

ADC data item stats -> 300-400k

n+n 1.8.W spectra show large signal excursions

p+n 1.8.W spectra for biased Si wafers OK - unbiased Si wafers show large signal excursions

DSSSD#1 leakage currents 1.850+2.220+1.990=6.06uA cf. 5.095uA with all 3 wafers biased

DSSSD#2 leakage currents 1.510+1.580+2.350=5.44uA cf. 5.235uA

Right wafer (looking upstream)

Bias(V) -20 -40 -60 -80 -100

DSSSD#1 I_L(uA) -1.135 -1.475 -1.645 -1.750 -1.805

DSSSD#2 I_l(uA) -1.625 -2.020 -2.205 -2.320 -2.360

Middle wafer (looking upstream)

Bias(V) -20 -40 -60 -80 -100

DSSSD#1 I_L(uA) -1.540 -1.870 -2.035 -2.150 -2.210

DSSSD#2 I_l(uA) -0.985 -1.285 -1.465 -1.575 -1.615

Left wafer (looking upstream)

Bias(V) -20 -40 -60 -80 -100

DSSSD#1 I_L(uA) -0.735 -0.915 -1.005 -1.080 -1.110

DSSSD#2 I_l(uA) -0.865 -1.205 -1.400 -1.510 -1.560

Bias versus leakage cuurent characteristic of each wafer of each DSSSD indicates diode behaviour.

Note LK1 not fitted - presumably LK3 of mid/top p+n FEE64 adaptor PCBs (aida01 and aida05) connecting n+n bias to gnd is sufficient to establish circuit.

15.50 Re-connect bias to all 3x Si wafers p+n junction side bias rings

ASIC check all FEE64s

Attachments 16 & 17 1.8.W spectra 20us FSR

Attachment 18 ADC data item stats

Attachment 19 DSSSD bias & leakage current

Conclusion - status quo ante restored

16.40 Remove aida01 & aida05 LK3, add aida04 & aida08 LK1

ASIC check all FEE64s

Attachments 20 & 21 1.8.W spectra 20us FSR

Attachment 22 ADC data item stats

Attachment 23 DSSSD bias & leakage current

Conclusion - no change

17.00 Add Thorn-Lab HV filters DSSSD#1 & #2

ASIC check all FEE64s

Attachments 24 & 25 1.8.W spectra 20us FSR

Attachment 26 ADC data item stats

Attachment 27 DSSSD bias & leakage current

Conclusion - aida09-aida12 no change, aida13-aida16 -> 300-400k

I do not know why there's a difference between DSSSD#1 & #2 but more important point (probably) no improvement aida09-aida12

Thorn Lab HV filters removed - status quo ante restored

18.02 Remove LK2 & LK4 all top p+n adaptor PCBs (aida13, 5, 14, 9, 1, & 10)

ASIC check all FEE64s

Attachments 28 & 29 1.8.W spectra 20us FSR

Attachment 30 ADC data item stats

Attachment 31 DSSSD bias & leakage current

Conclusion - no change cf. 16.40 test

19.10 Re-order power cabling at AIDA FEE64 PSUs from ...

Top 1-3 2-4 9-10 11-12

Bottom 5-7 6-8 13-14 15-16

to ...

Top 1-2 3-4 9-10 11-12

Bottom 5-6 7-8 13-14 15-16

ASIC check all FEE64s

Attachments 32 & 33 1.8.W spectra 20us FSR

Attachment 34 ADC data item stats

Attachment 35 DSSSD bias & leakage current

Conclusion - all p+n FEE64 rates c. 100k, or less, n+n FEE64 rates c. 400k

FEE64 adaptor PCB config

LK2-LK3-LK4 fitted for all bottom p+n FEE64s (aida11, 3, 12, 15, 7, 16)

LK1 fitted n+n FEE64s aida06 & aida02 *only* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|