|

|

|

AIDA

GELINA

BRIKEN

nToF

CRIB

ISOLDE

CIRCE

nTOFCapture

DESPEC

DTAS

EDI_PSA

179Ta

CARME

StellarModelling

DCF

K40

|

| DESPEC |

|

|

|

|

Message ID: 706

Entry time: Sun Jun 15 10:53:08 2025

|

| Author: |

TD |

| Subject: |

Sunday 15 June 2025 |

|

|

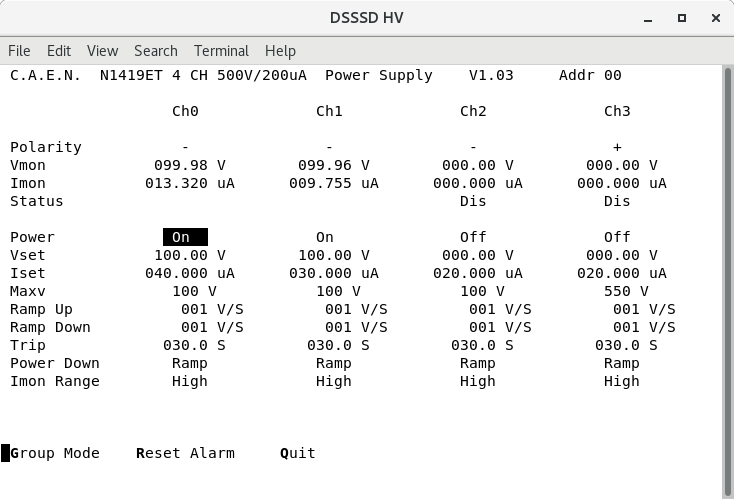

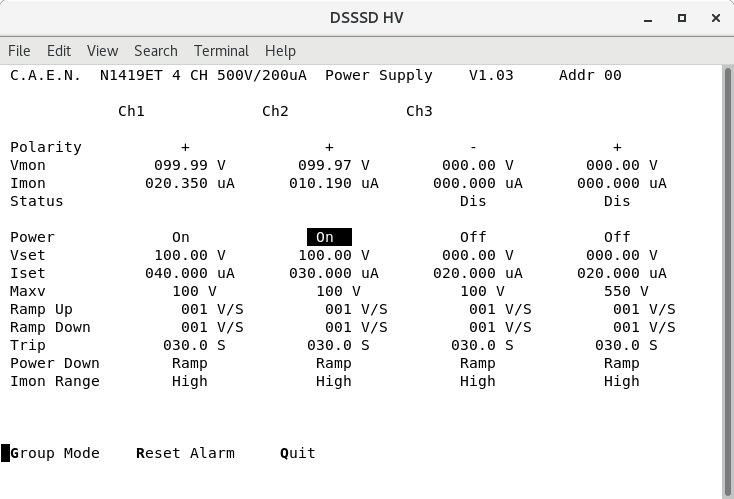

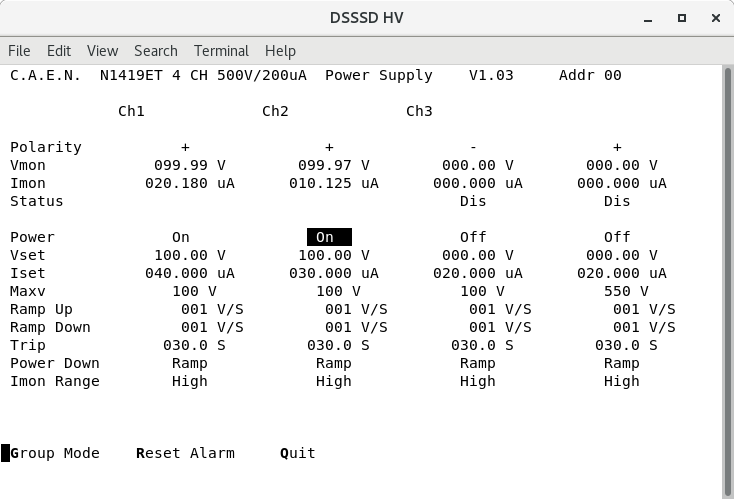

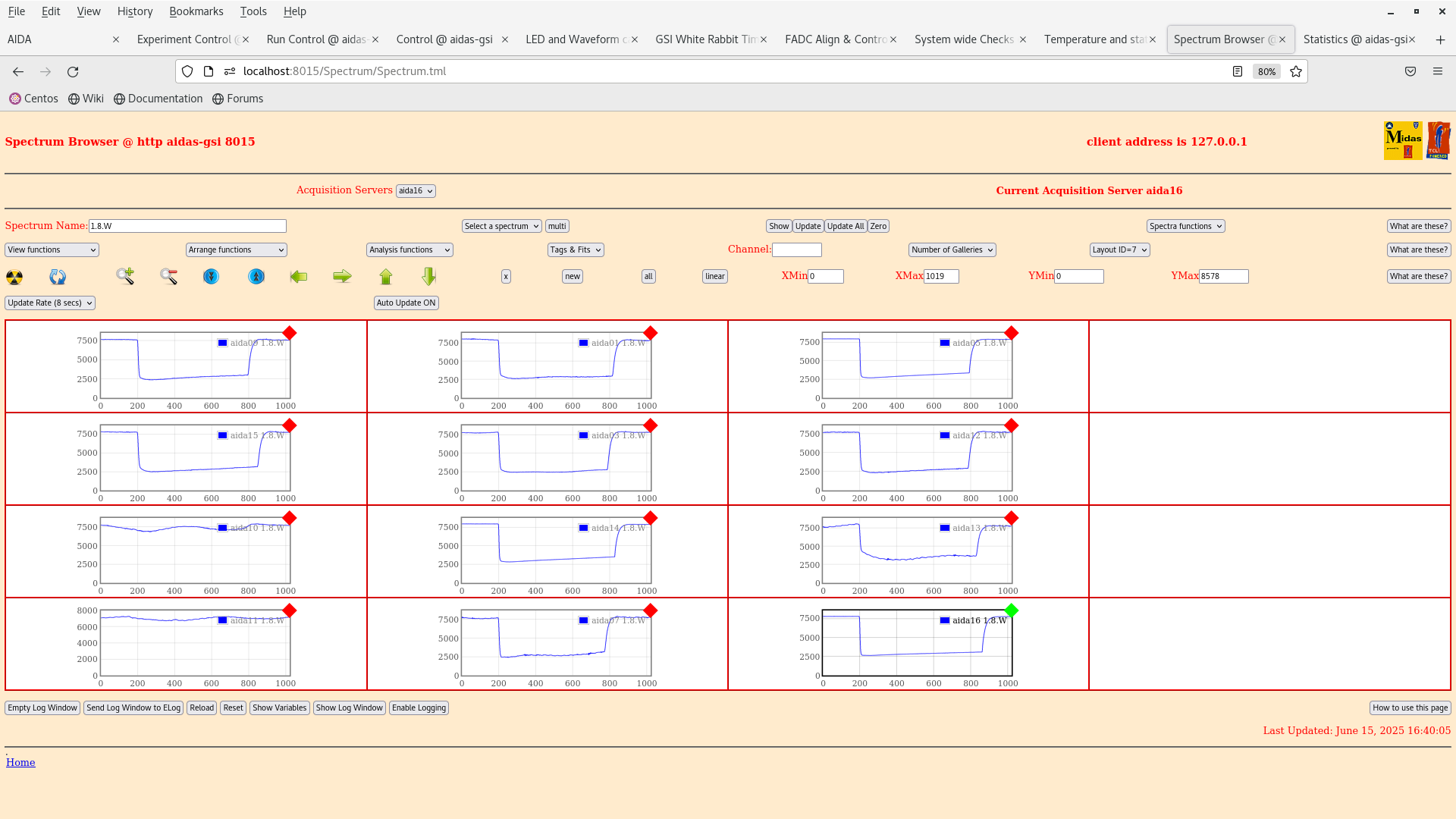

11.45 DSSSD bias & leakage current - attachment 1

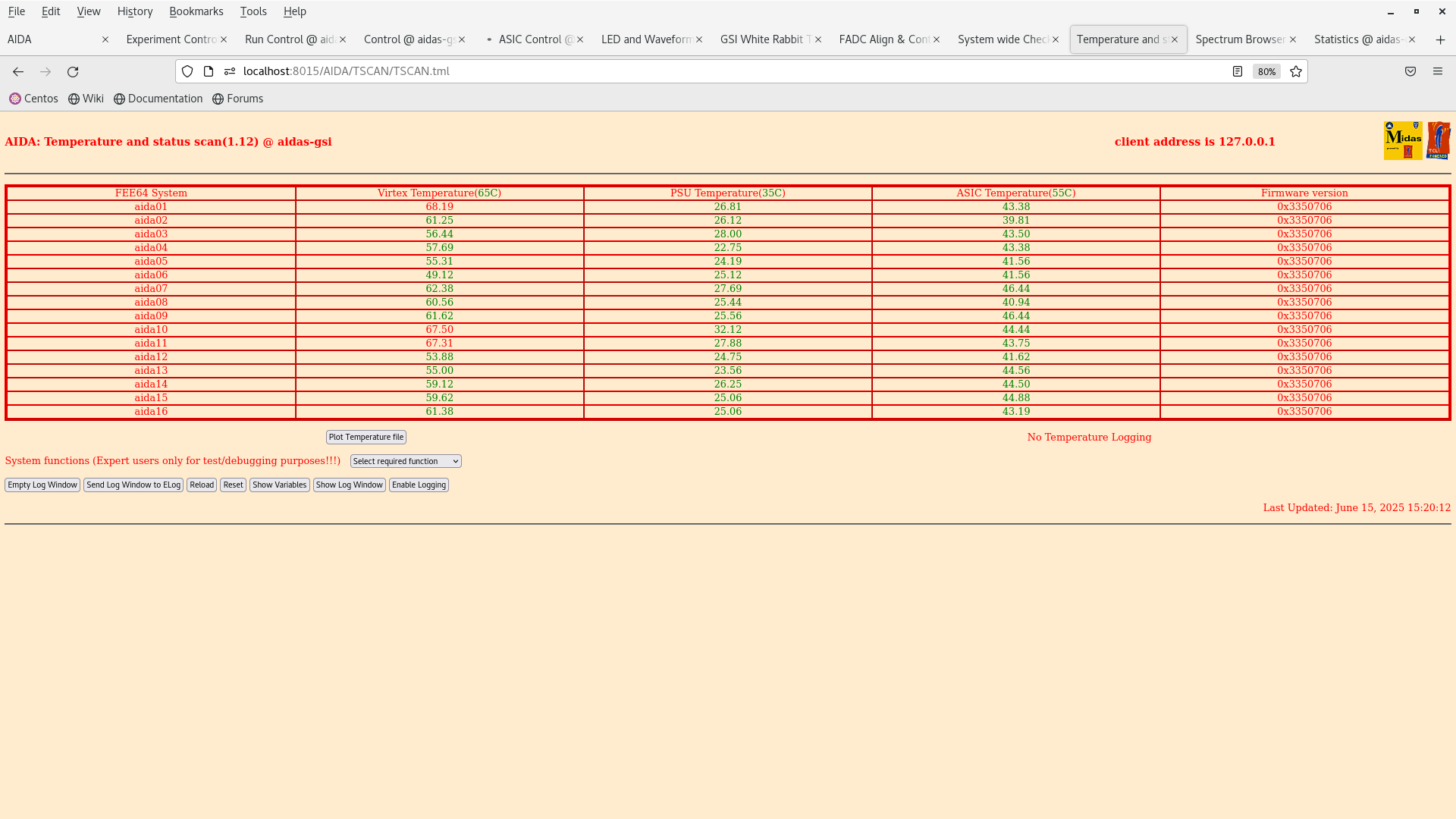

FEE64 temps OK - attachment 2

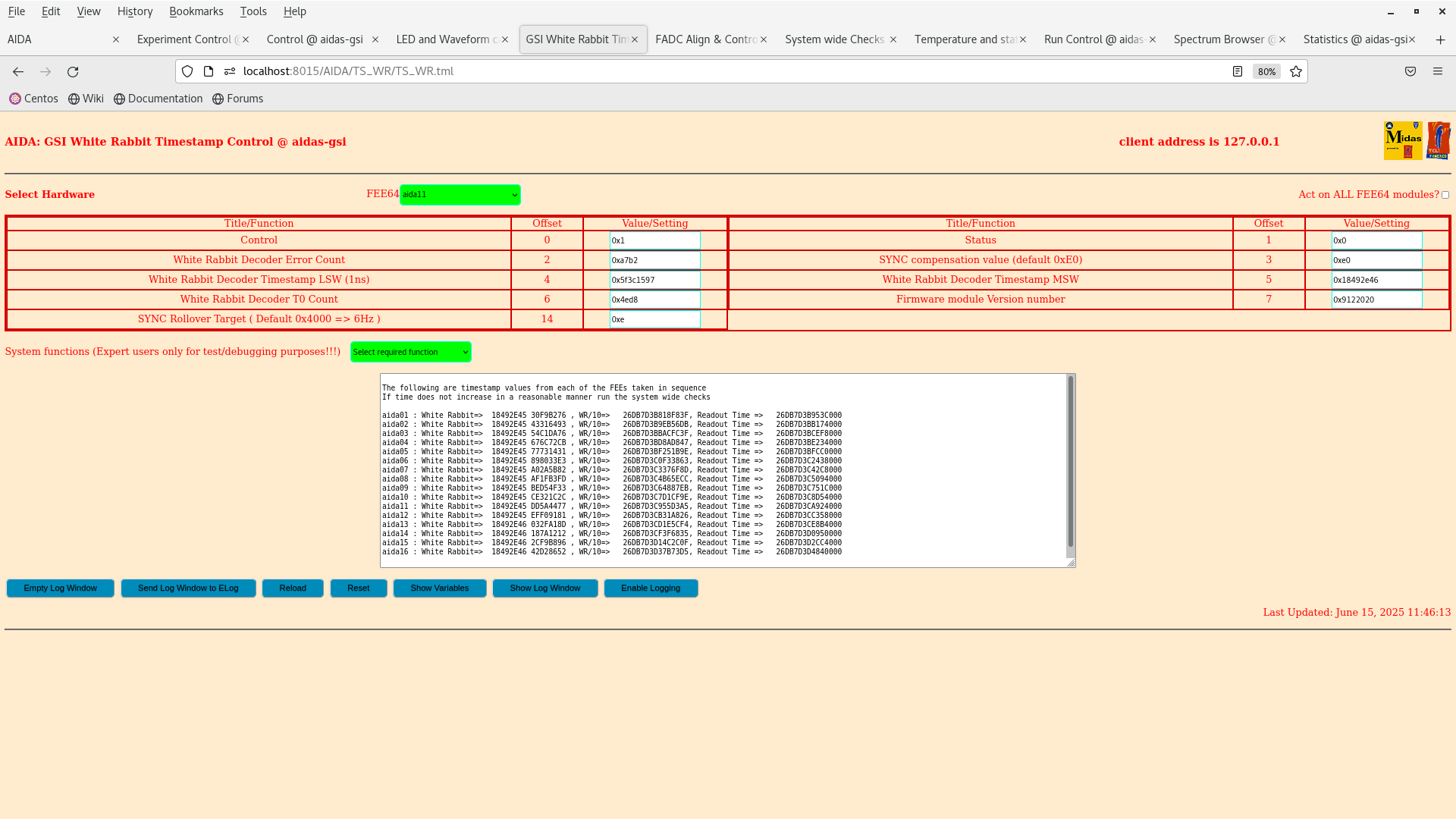

All system wide checks OK *except* WR decoder status aida02 - attachment 3

WR timestamps OK - attachment 4

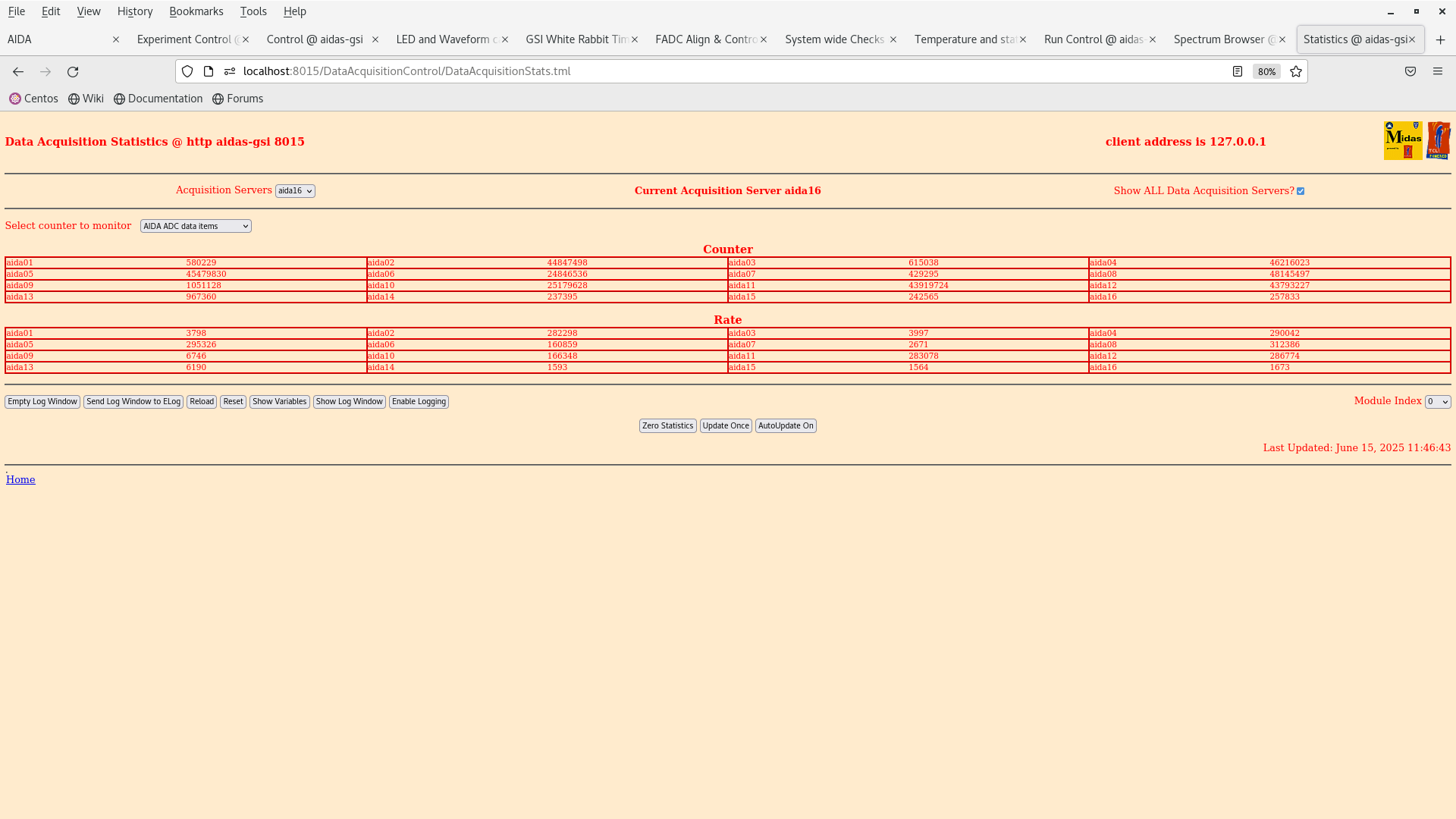

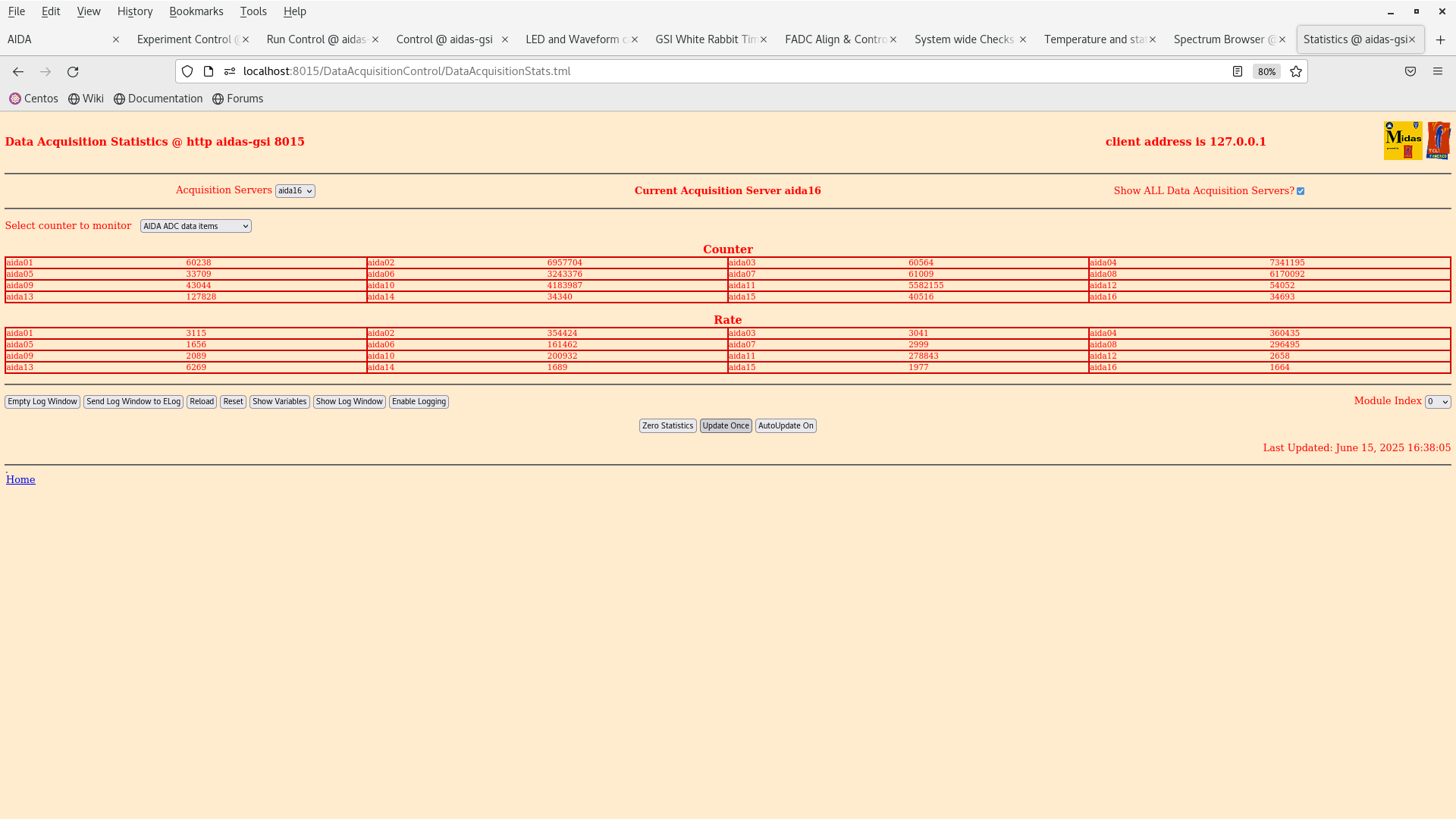

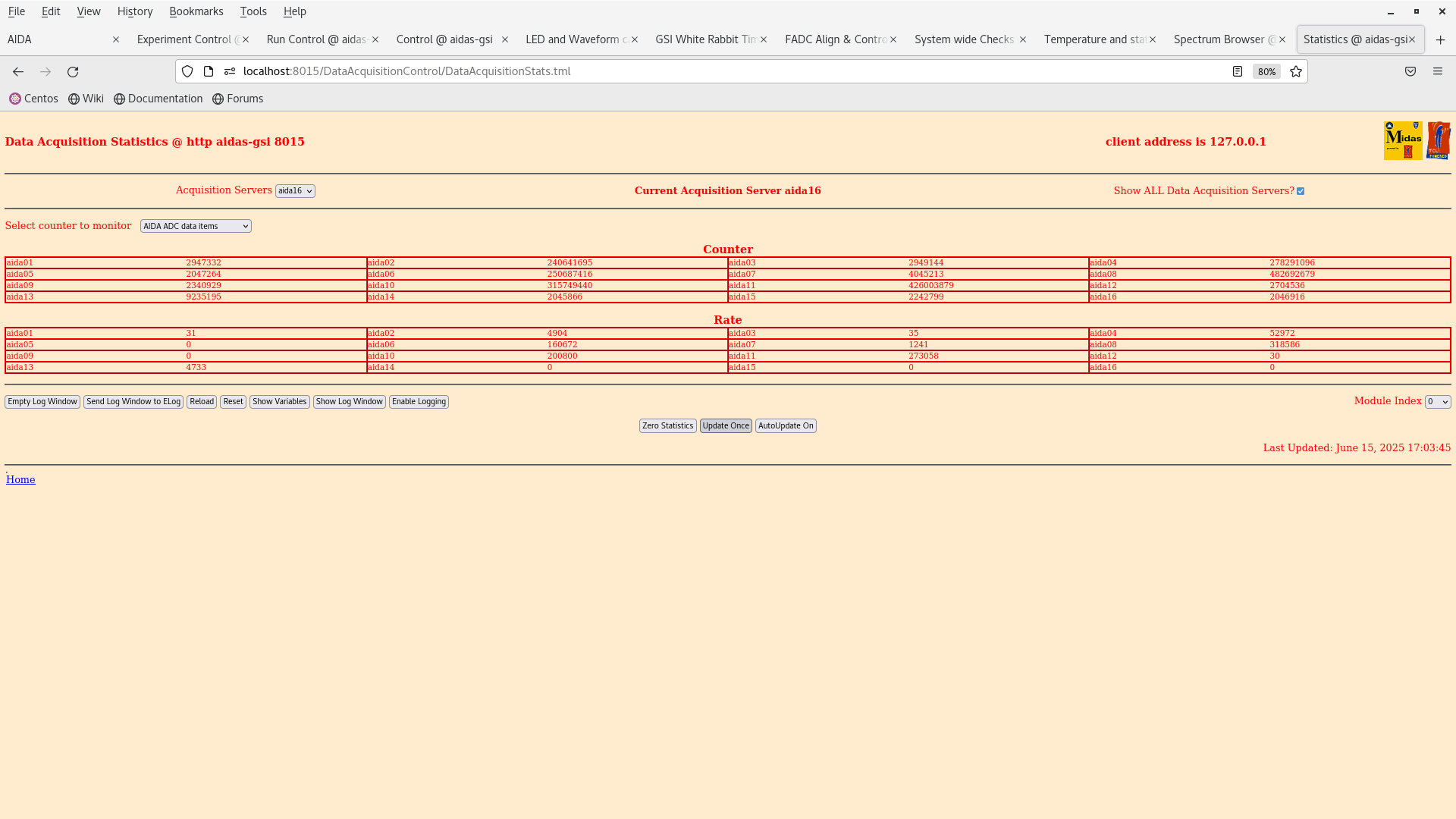

ADC data item stats - attachment 5

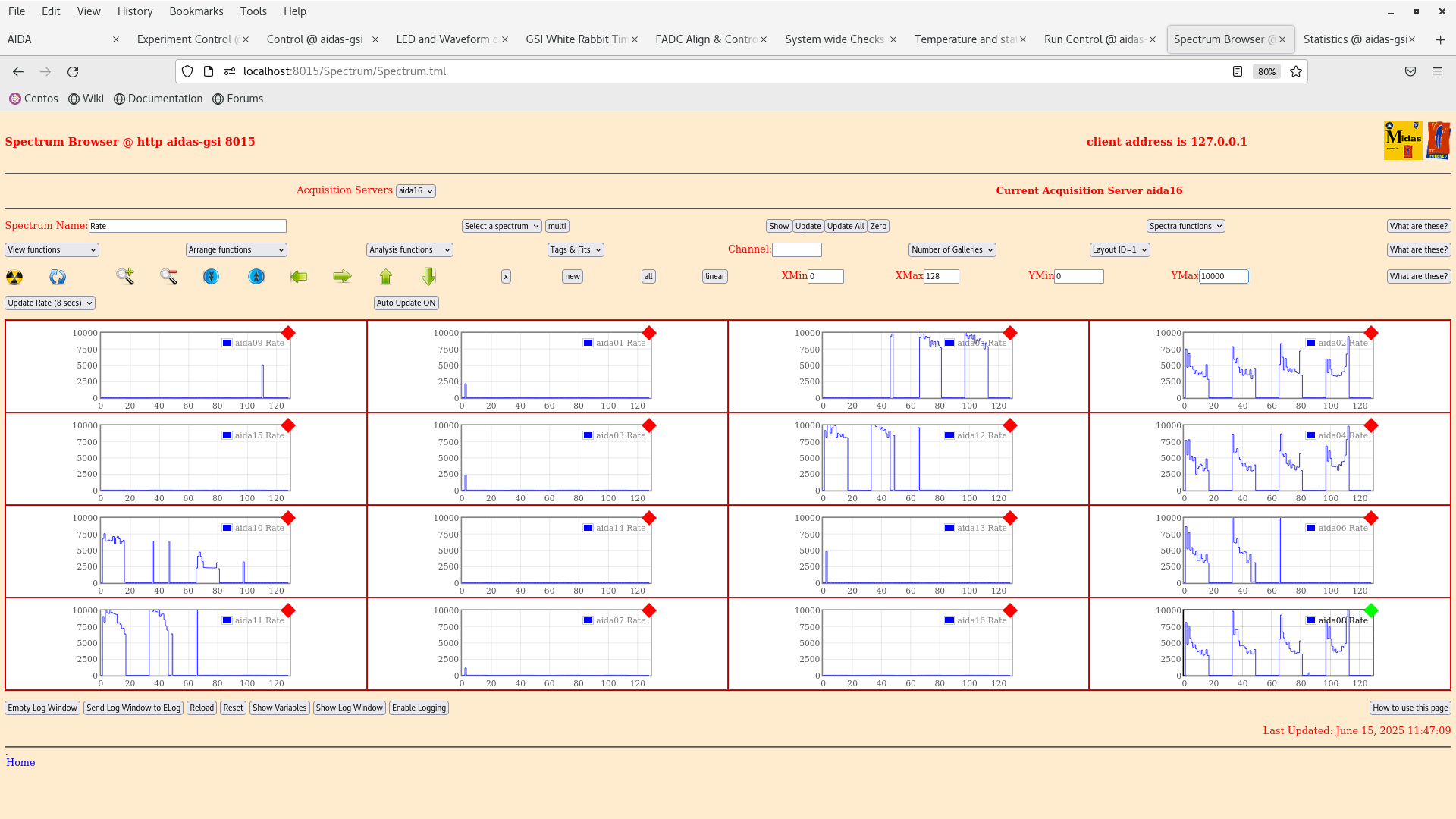

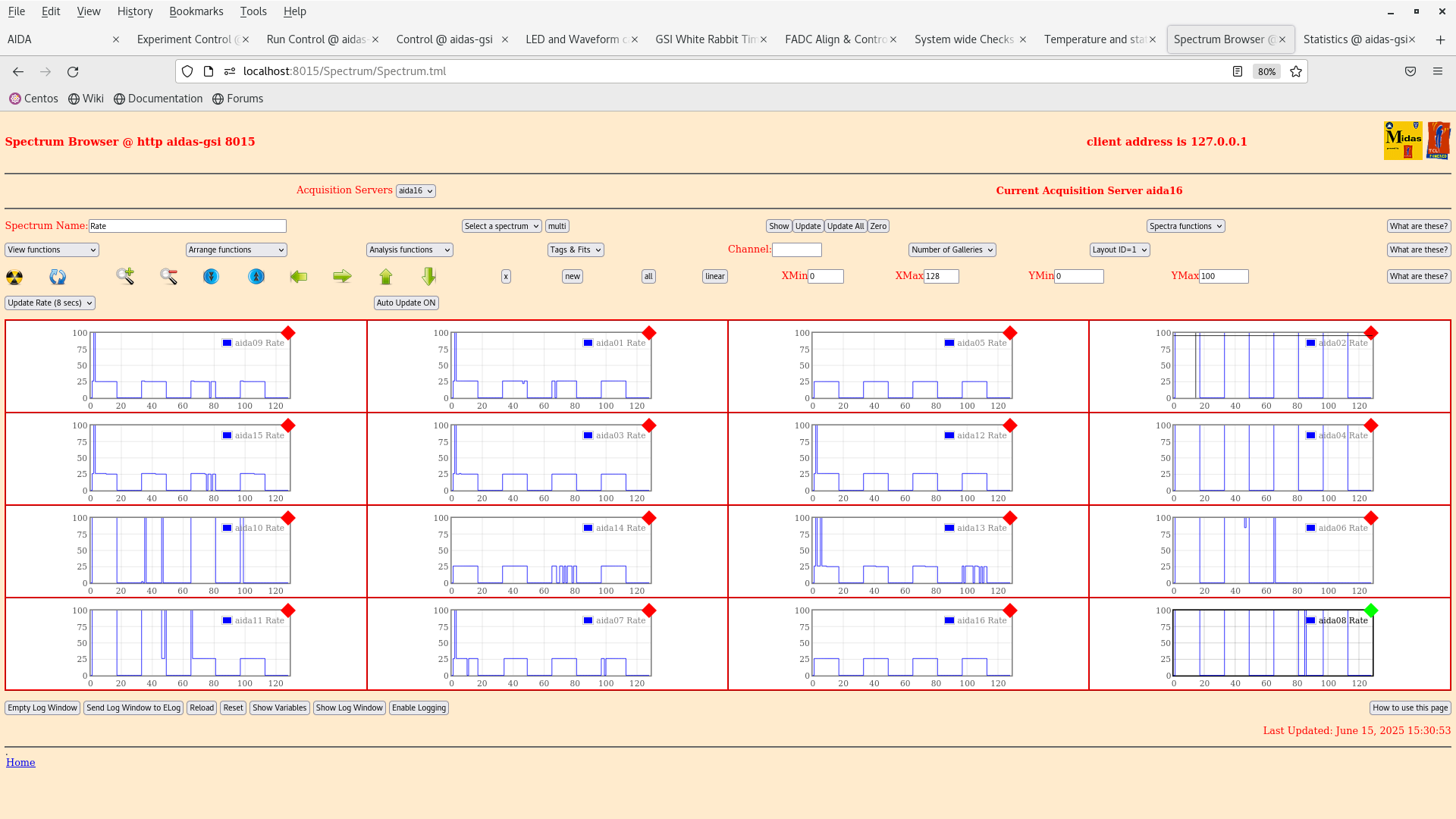

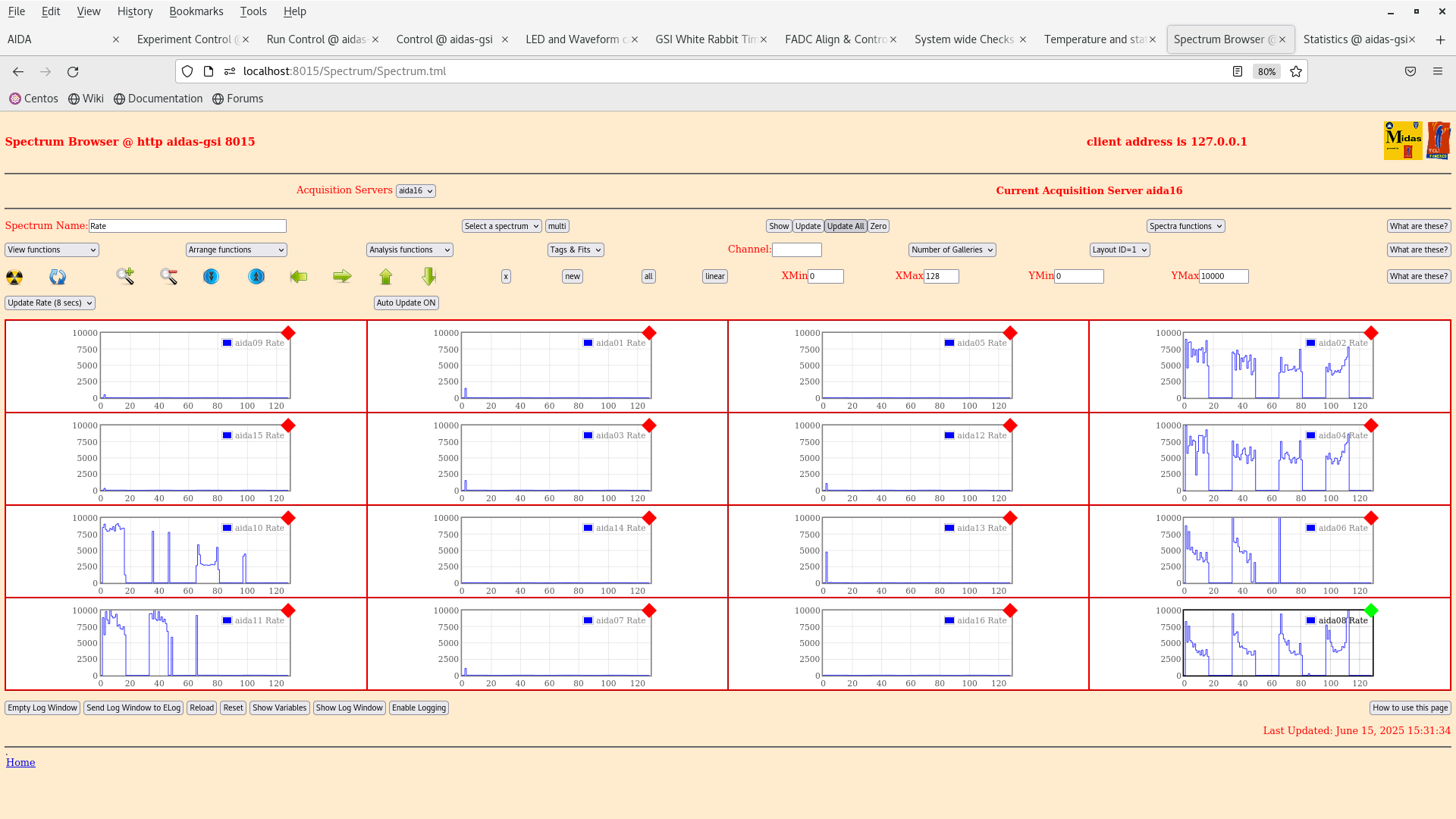

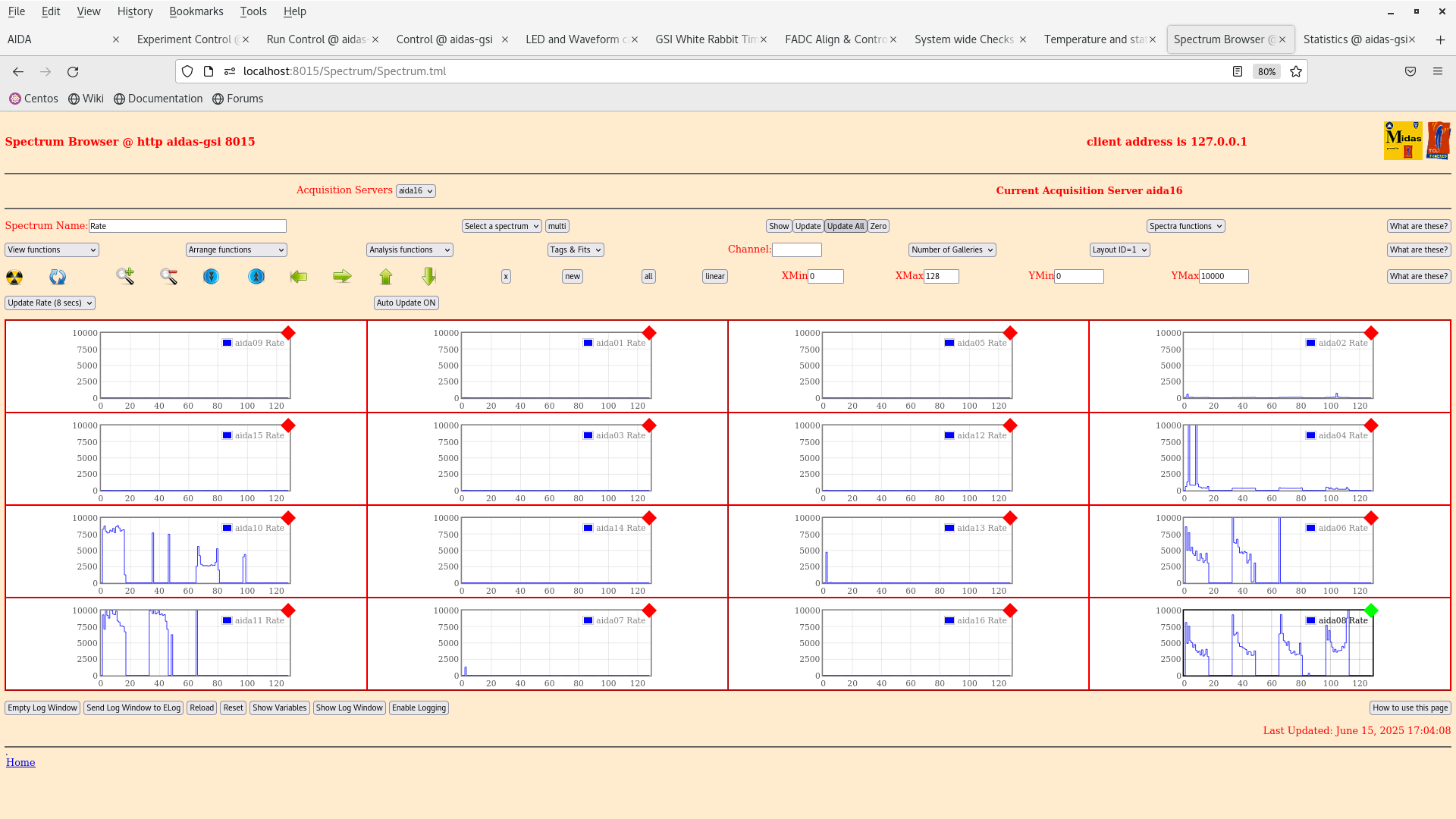

per FEE64 Rate spectra - attachments 6-7

note ASICs with per channel rates of 22Hz (pulser)

note *all* FEE64 slow comparator 0x64

note ignore aida10 - connected to MSL type BB7 - not biased yet

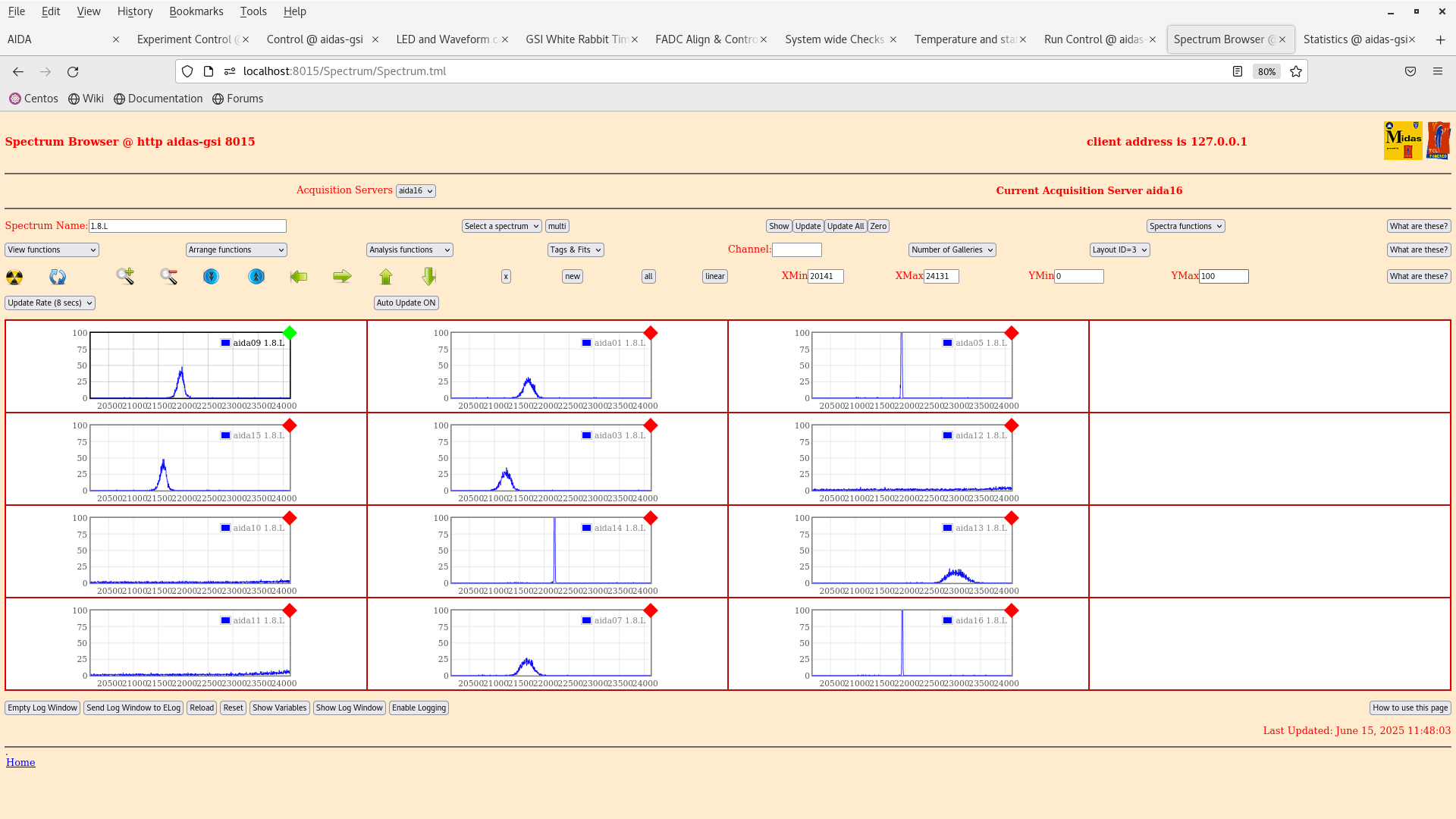

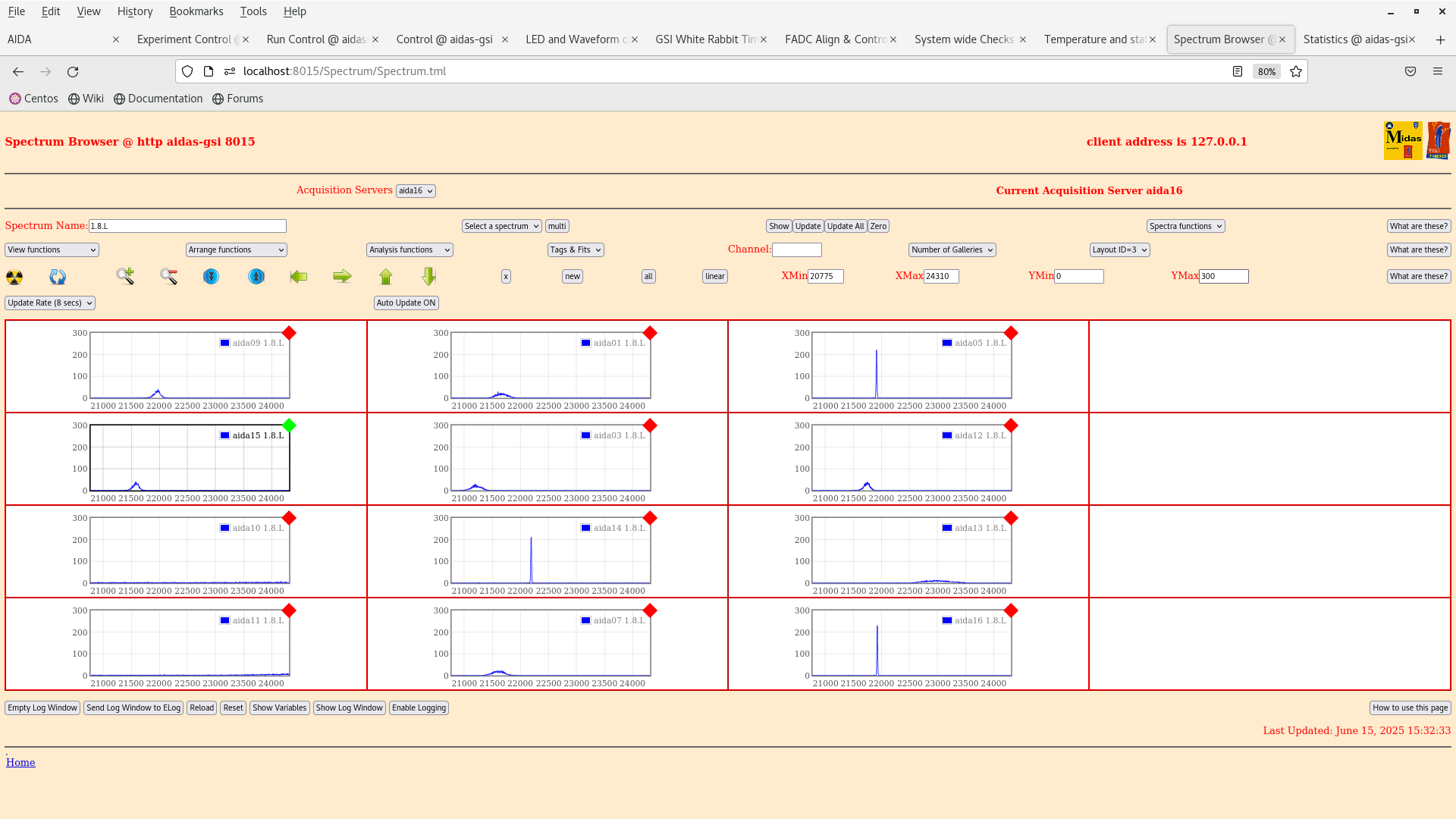

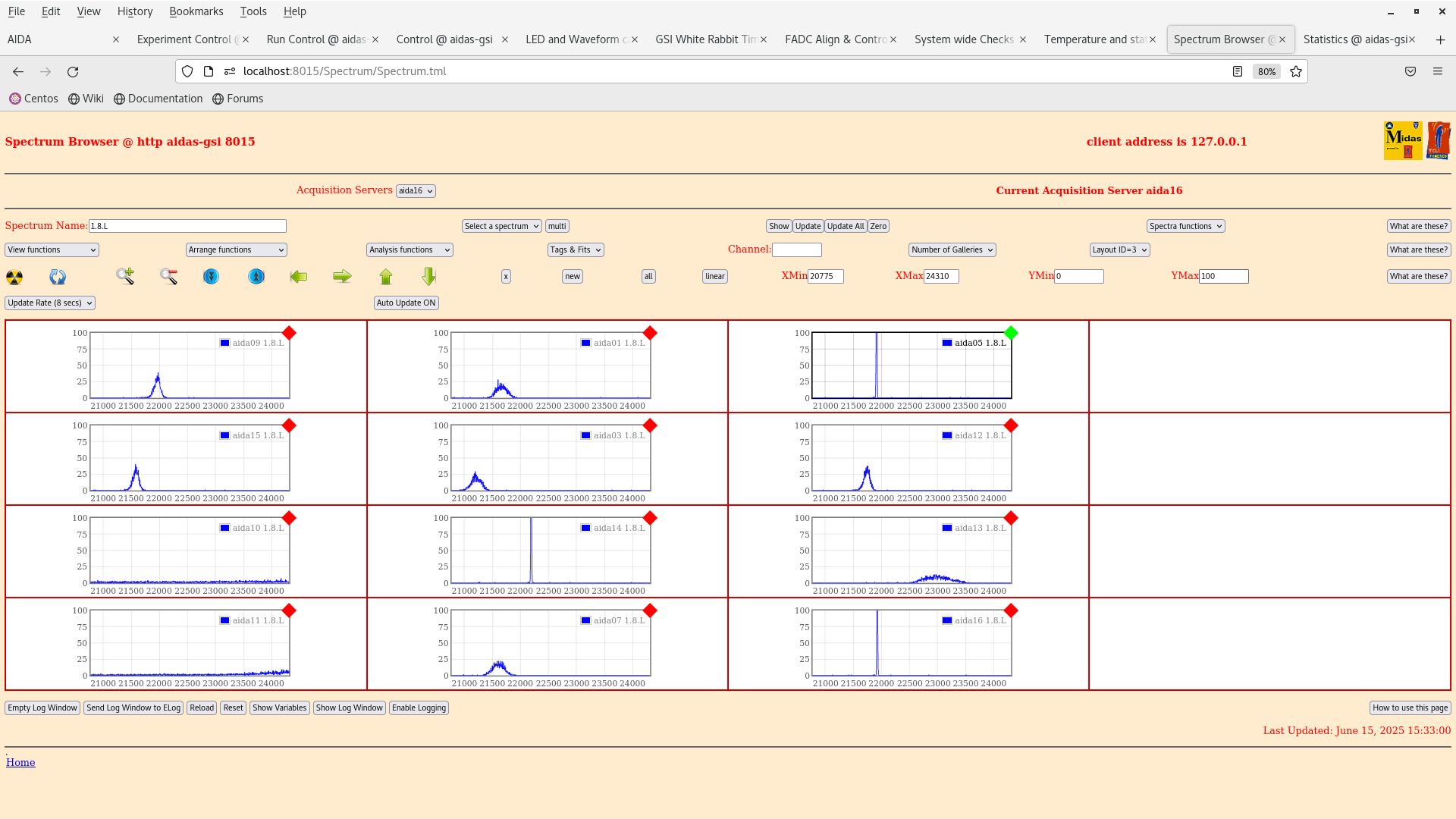

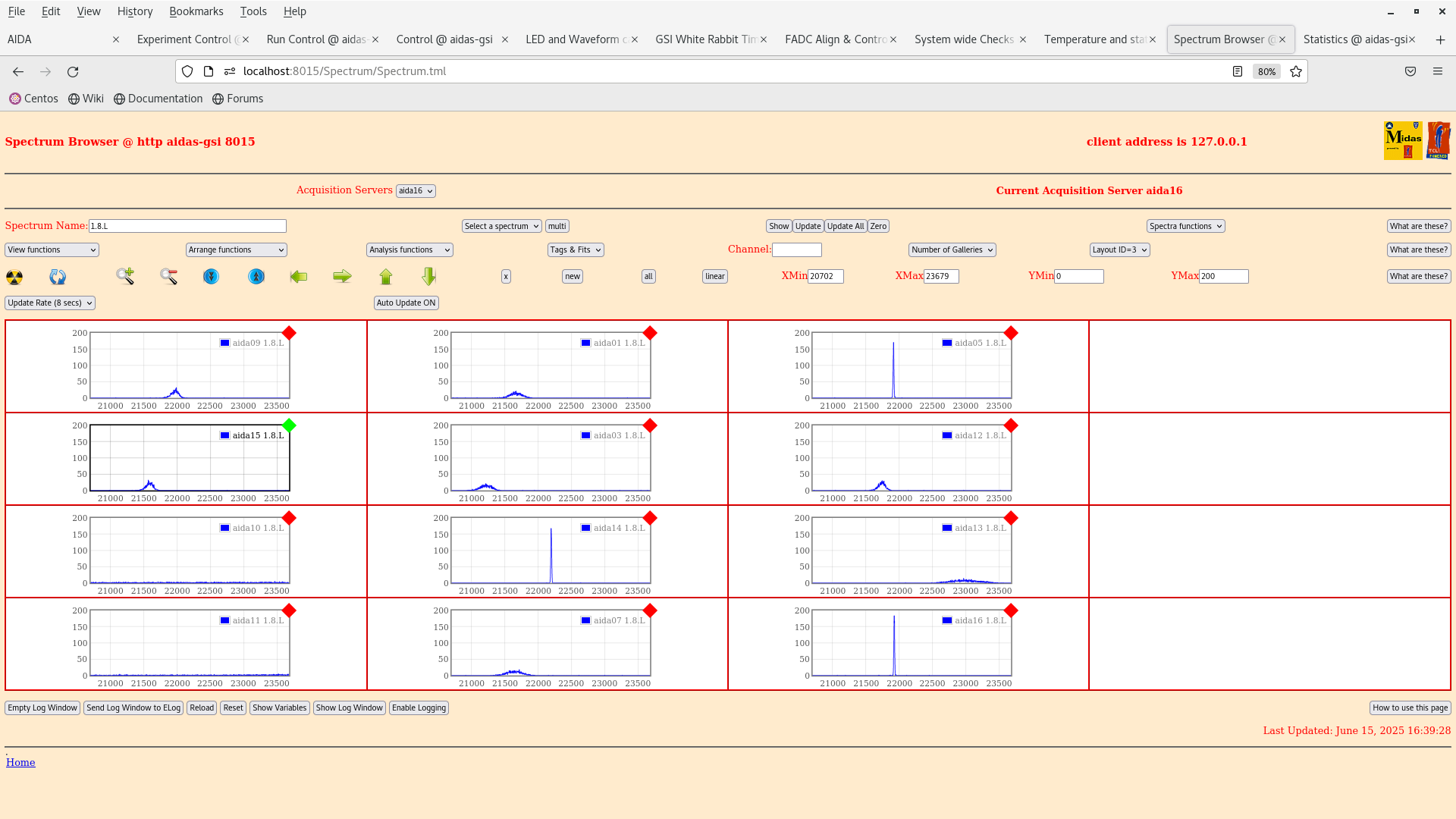

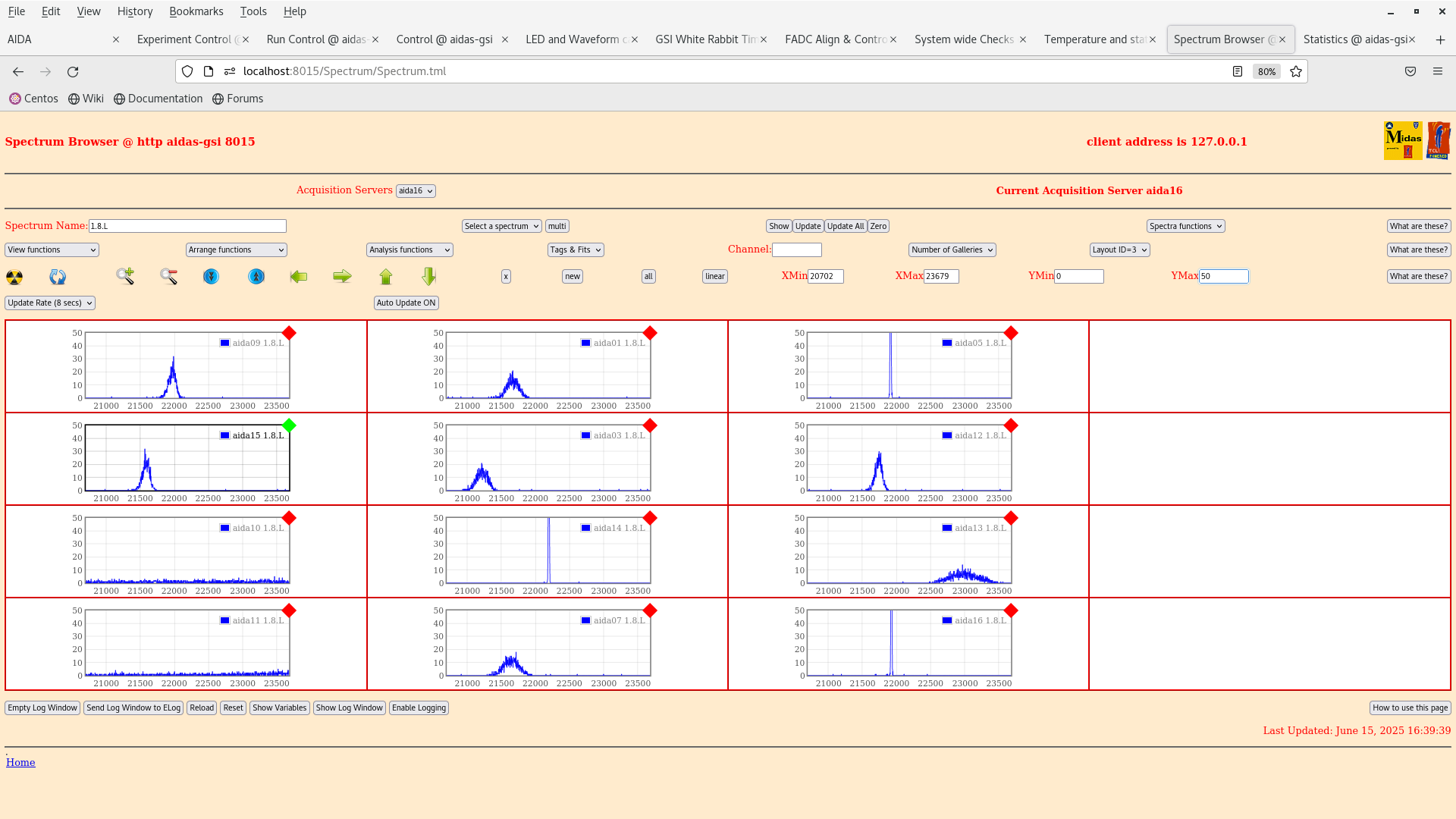

per p+n FEE64 1.8.L spectra - attachment 8-9

pulser peak widths

aida05, aida14, aida16 c. 15-20 ch FWHM ( c. 10-15keV FWHM ) - cable from DSSSD not connected to adaptor PCB

aida15 c. 137 ch FWHM - electronic noise c. 2x worse than configuration used for 2023/4 tests

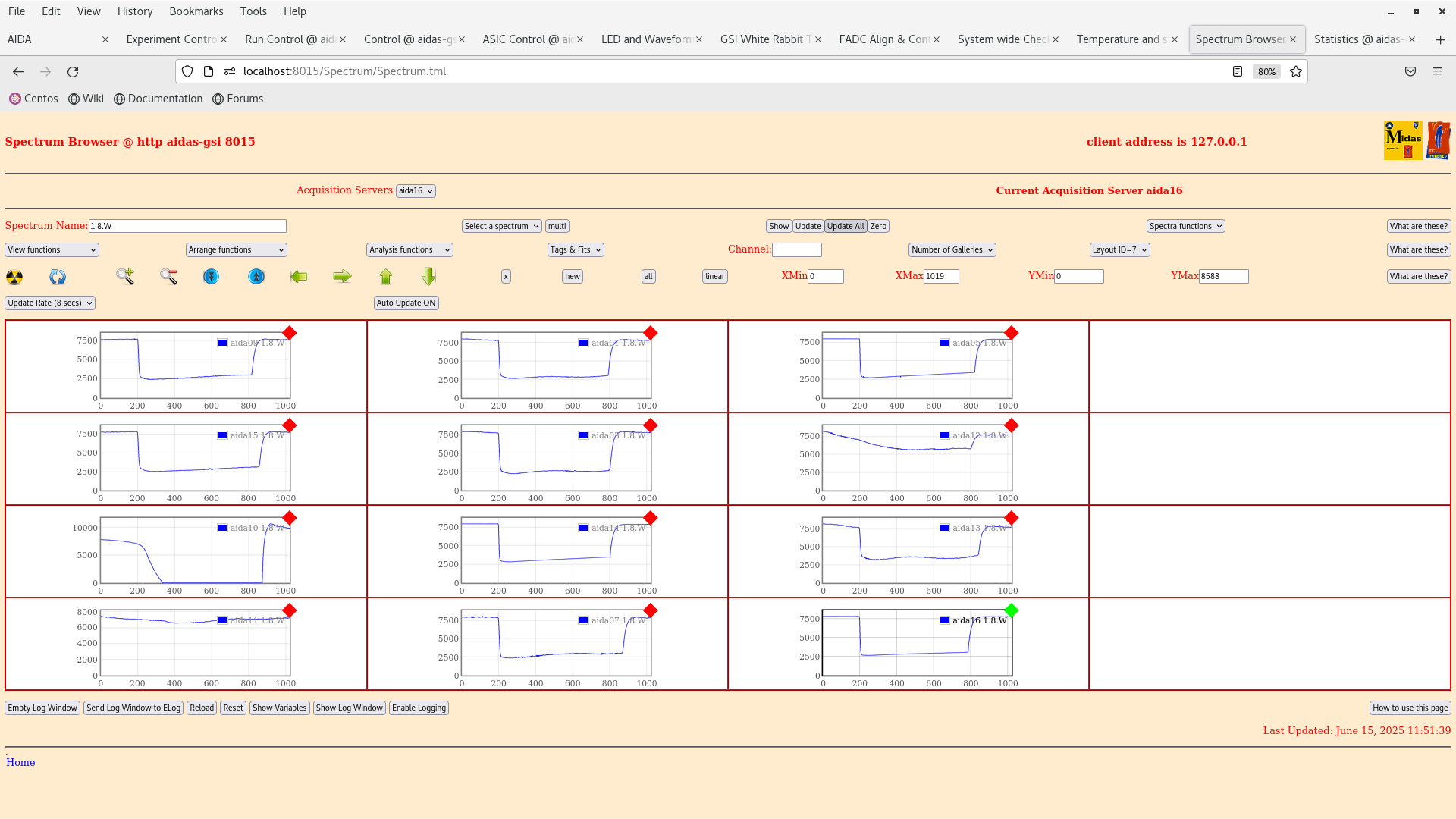

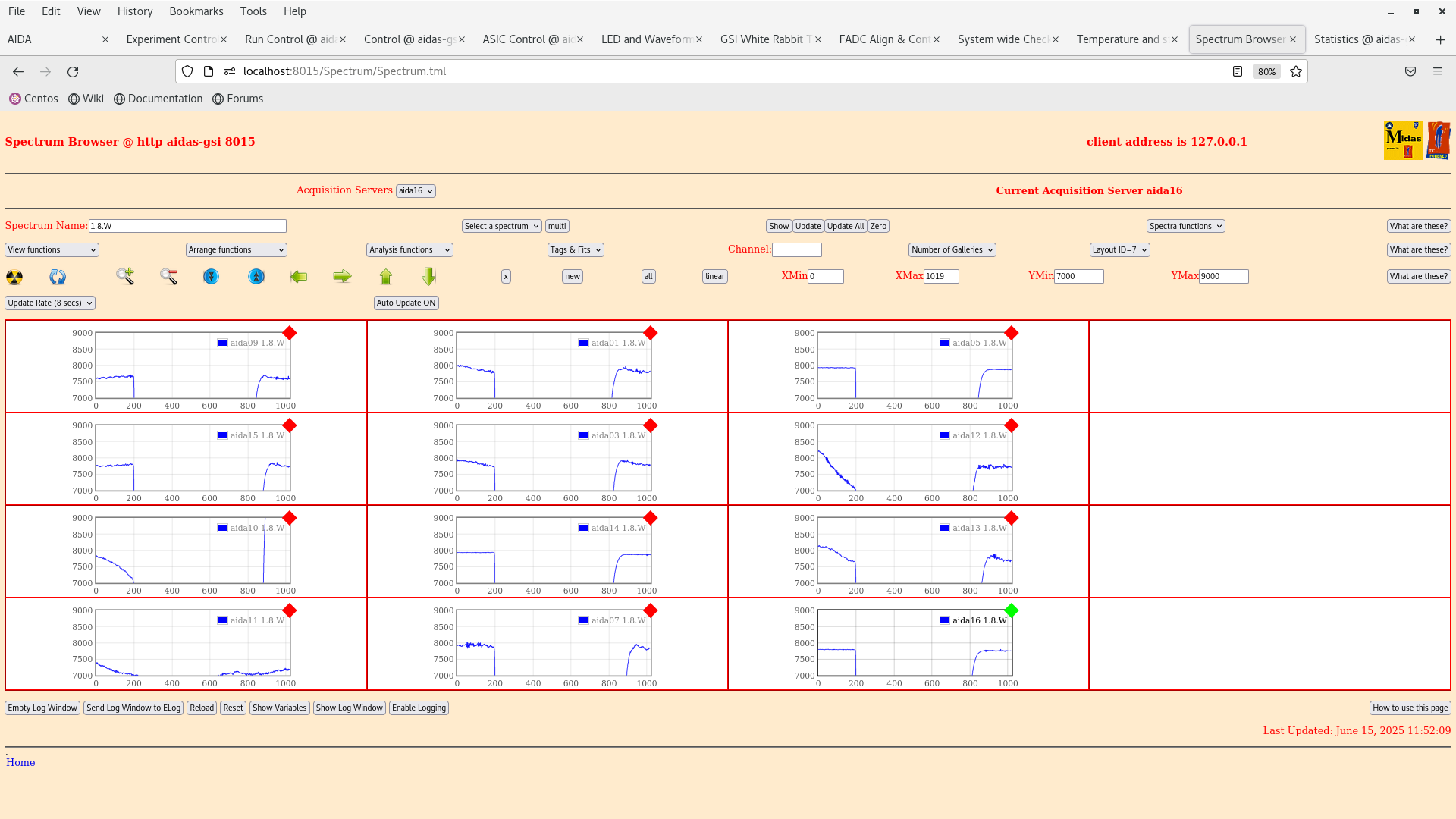

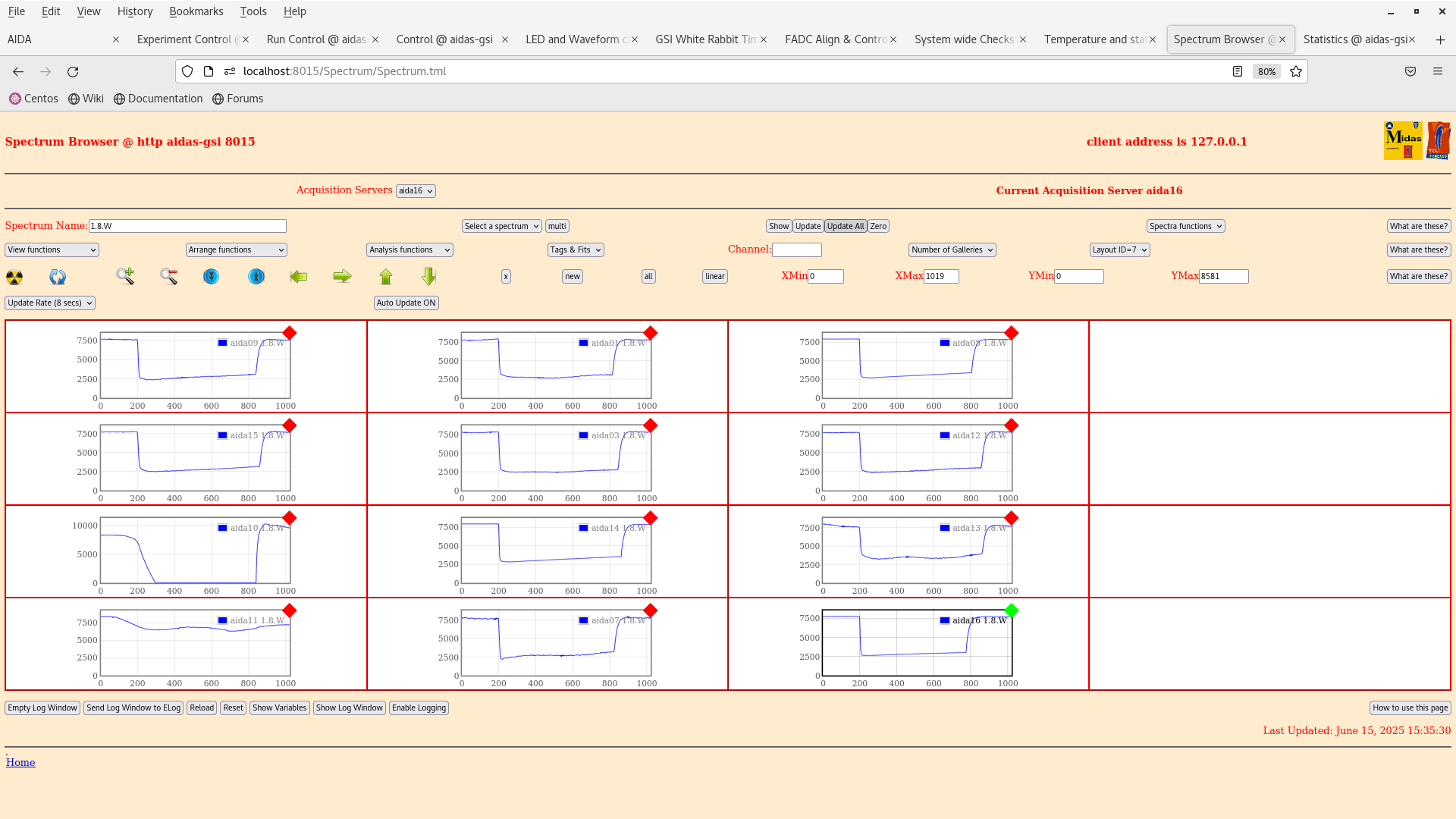

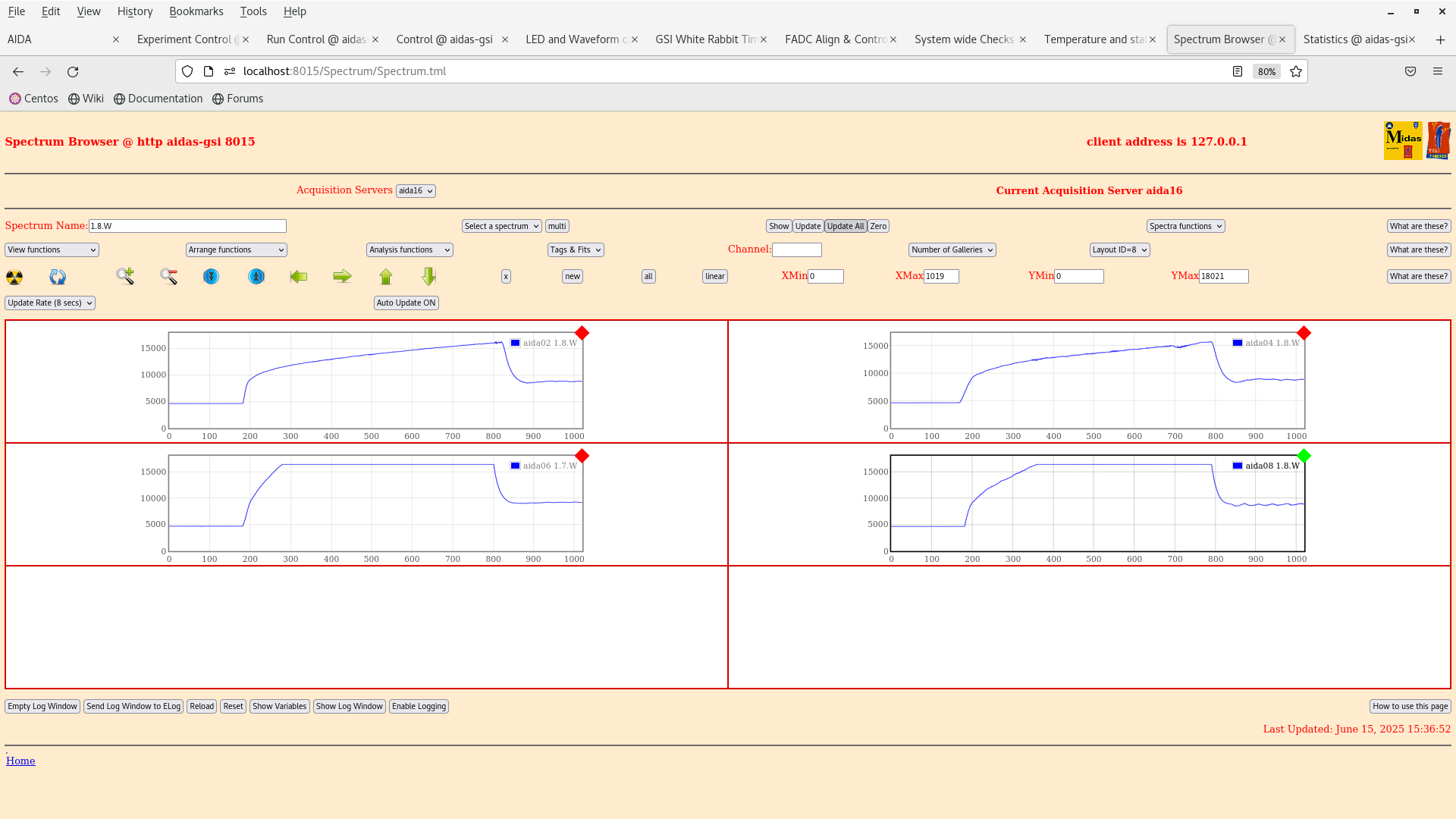

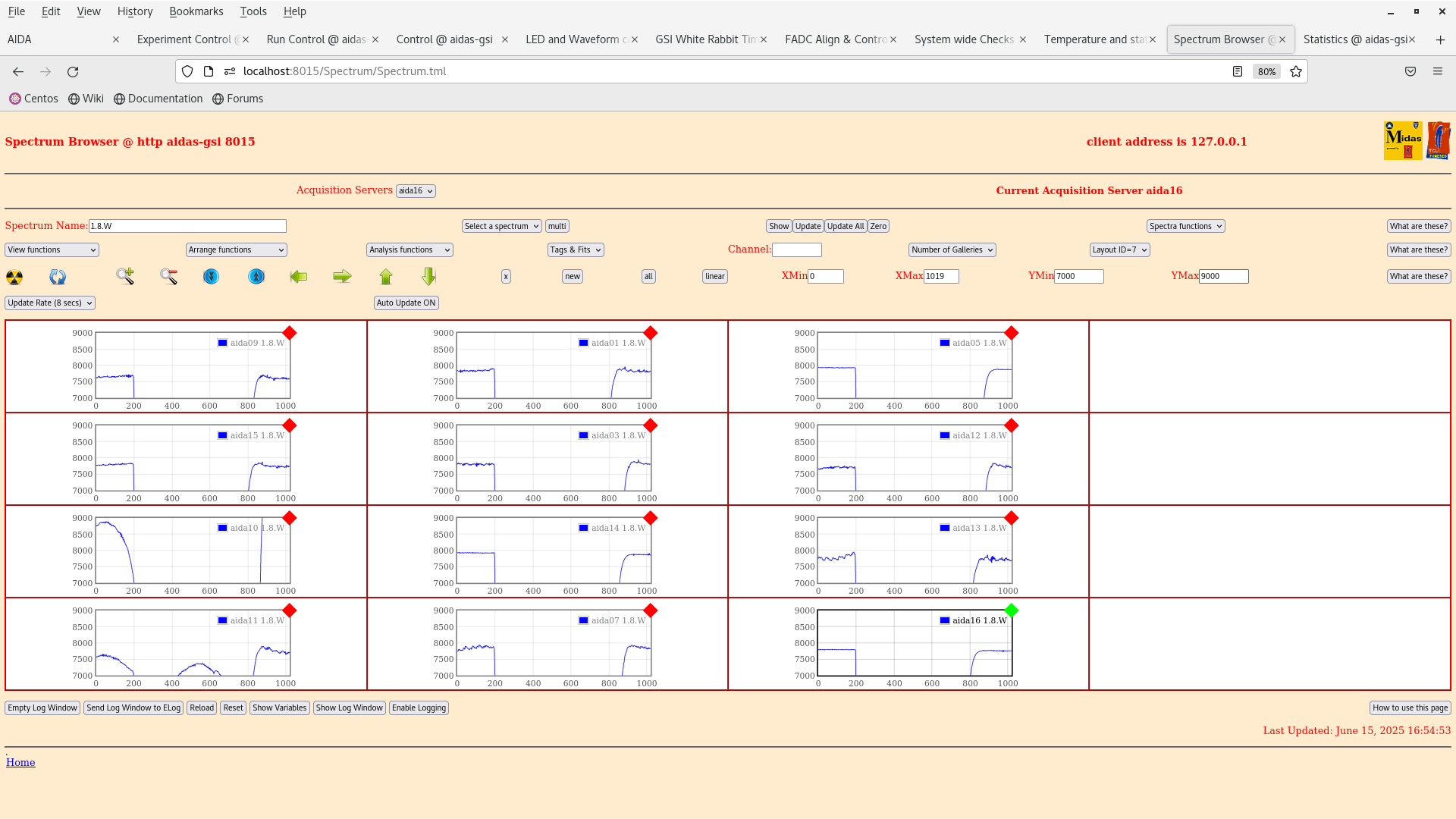

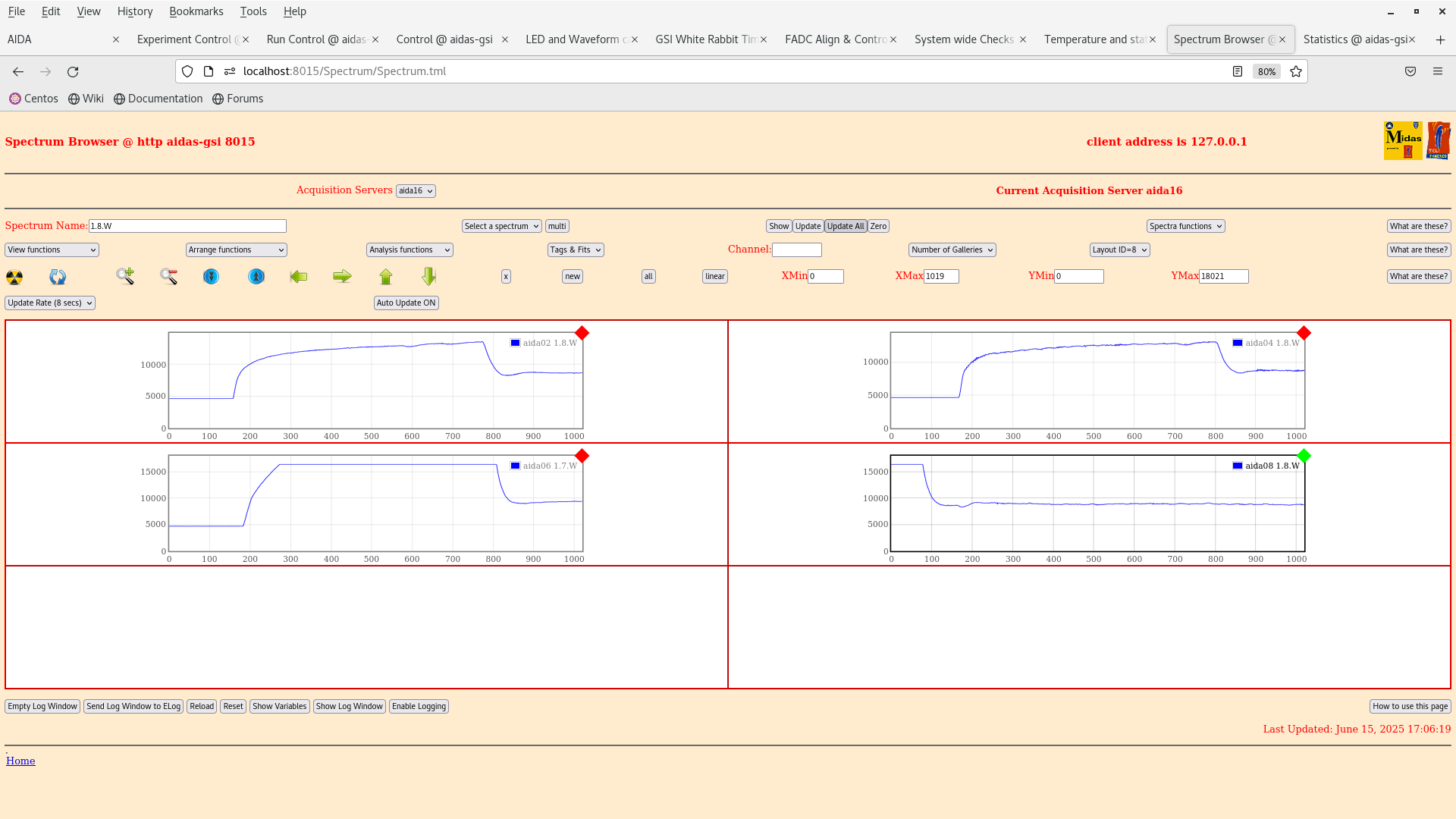

per p+n FEE64 1.8.W spectra - 20us FSR - attachments 10

per p+n FEE64 1.8.W spectra - 20us FSR - expanded y-scale = 2000 x 122uV/LSB = 0.244V FSR - attachment 11

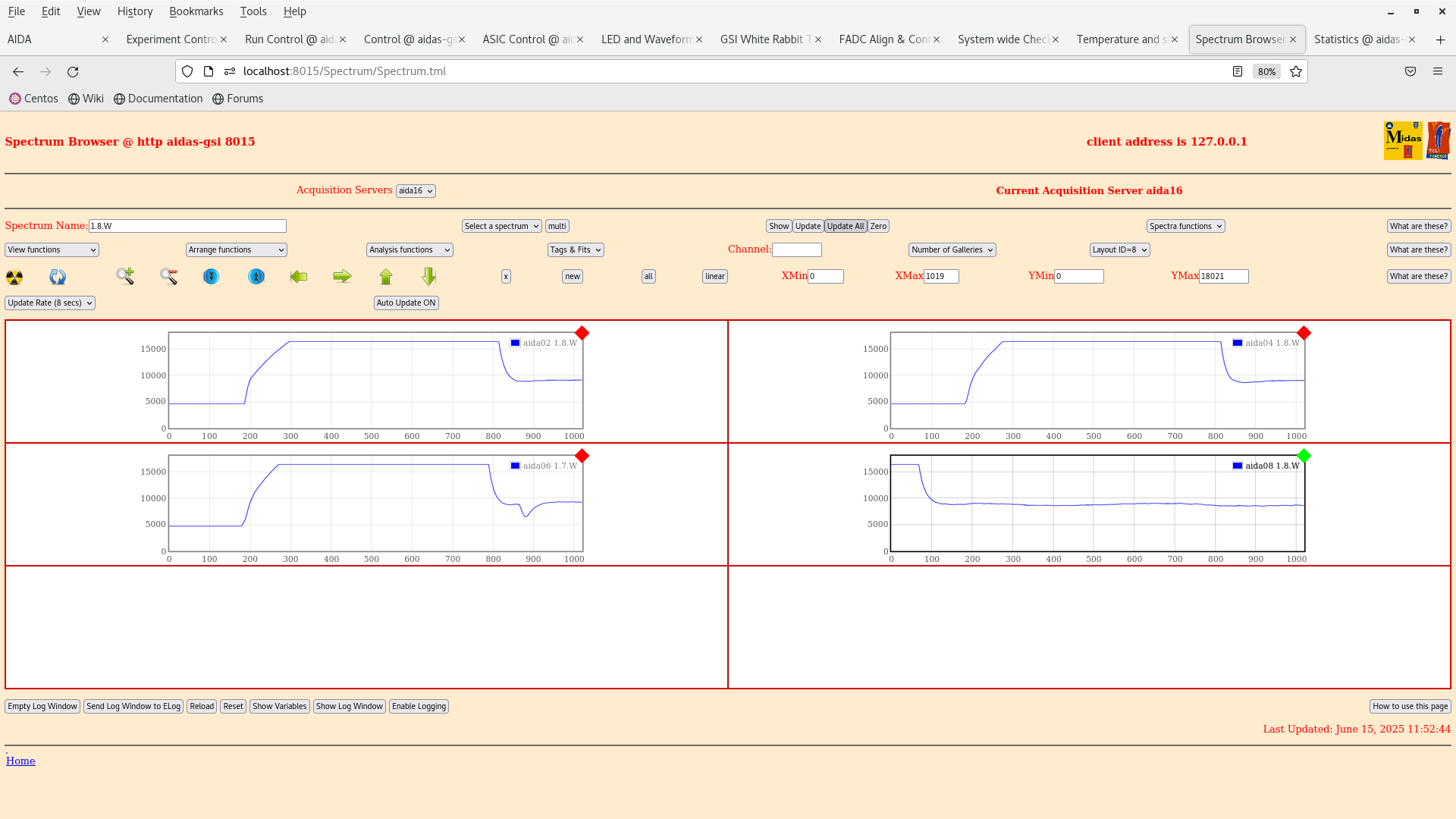

per n+n FEE64 1.8.W spectra - 20us FSR - attachments 12

15.20 Data suggests 2x (of 6x) Si wafers are not biased - aida11 & aida05-aida12 - J2 cable disconnected

Switch from negative to positive bias polarity

CAEN N1419ET channels 1 and 2 switched from negative to positive polarity

Note internal LK fitted - HV outputs *not* floating

Channel 1 -> DSSSD#0 from aida12 to aida04 (HV daisy chain aida12-aida03-aida15 *not* removed)

Channel 2 -> DSSSD#1 from aida16 to aida08 (HV daisy chain aida16-aida07-aida11 *not* removed)

LK1 removed from adaptor PCBs for aida02. aida04, aida06, aaida08

LK1 fitted aida05, aida13, aida10, aida09, aida15, aida11

LK3 *no* change

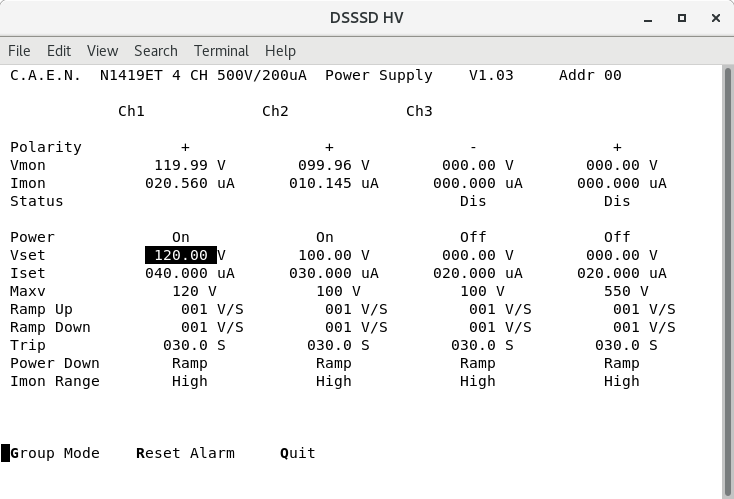

DSSSD bias & leakage current - attachment 13

note increase in leakage current for DSSSD#0 but not DSSSD#1

- indicating DSSSD#0 has all Si wafers biased

- all wafers of DSSSD#1 not biased => damaged adaptor PCB and/or cabling, misaligned ribbon cable/Kapton PCB connection within snout

FEE64 temps OK - attachment 14

ADC data item stats - attachment 15

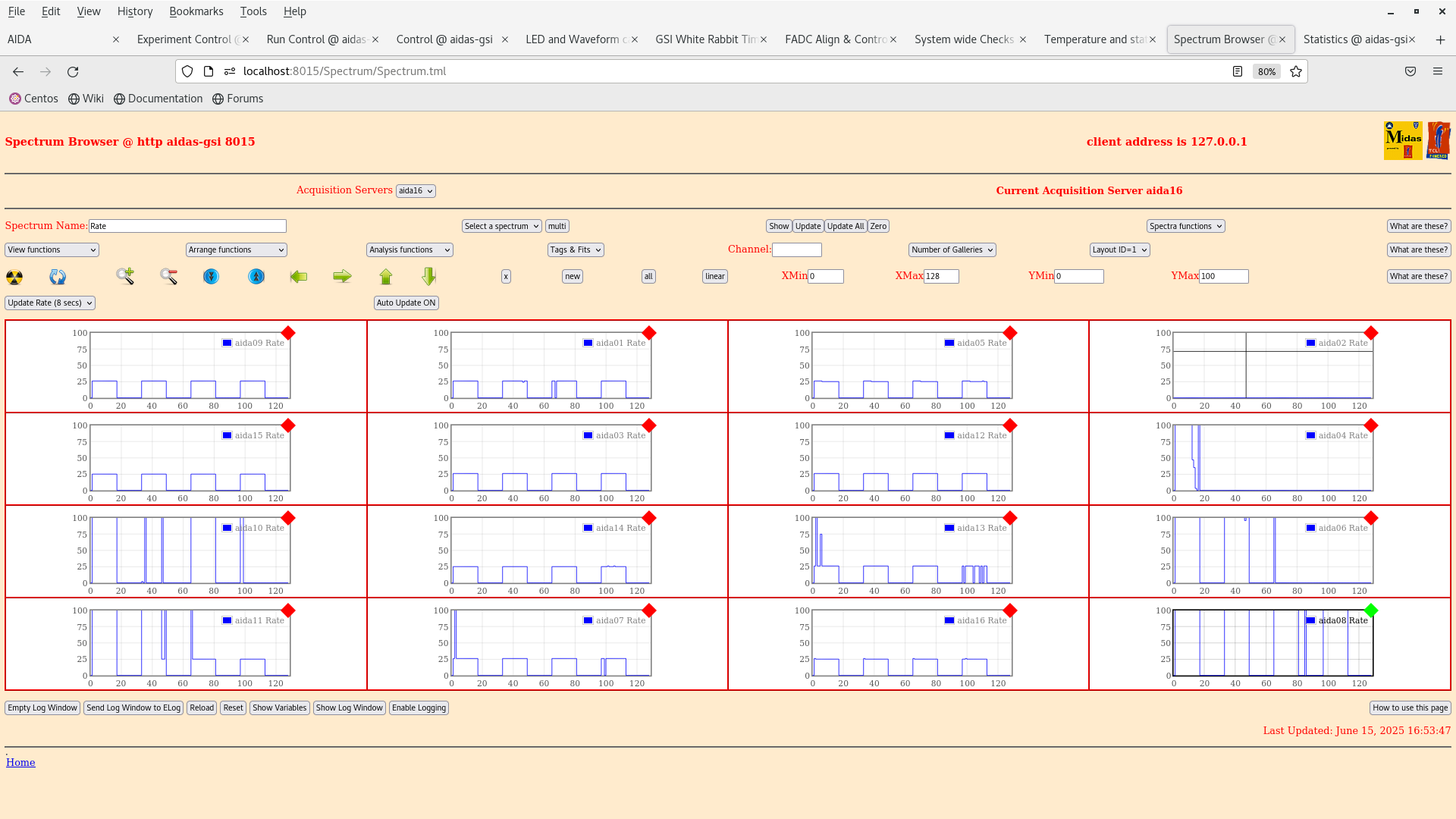

per FEE64 Rate spectra - attachments 16-17

note ASICs with per channel rates of 22Hz (pulser)

note *all* FEE64 slow comparator 0x64

note ignore aida10 - connected to MSL type BB7 - not biased yet

per p+n FEE64 1.8.L spectra - attachment 18-19

pulser peak widths

aida05, aida14, aida16 c. 15-20 ch FWHM ( c. 10-15keV FWHM ) - cable from DSSSD not connected to adaptor PCB

aida15 c. 108 ch FWHM - electronic noise c. 2x worse than configuration used for 2023/4 tests

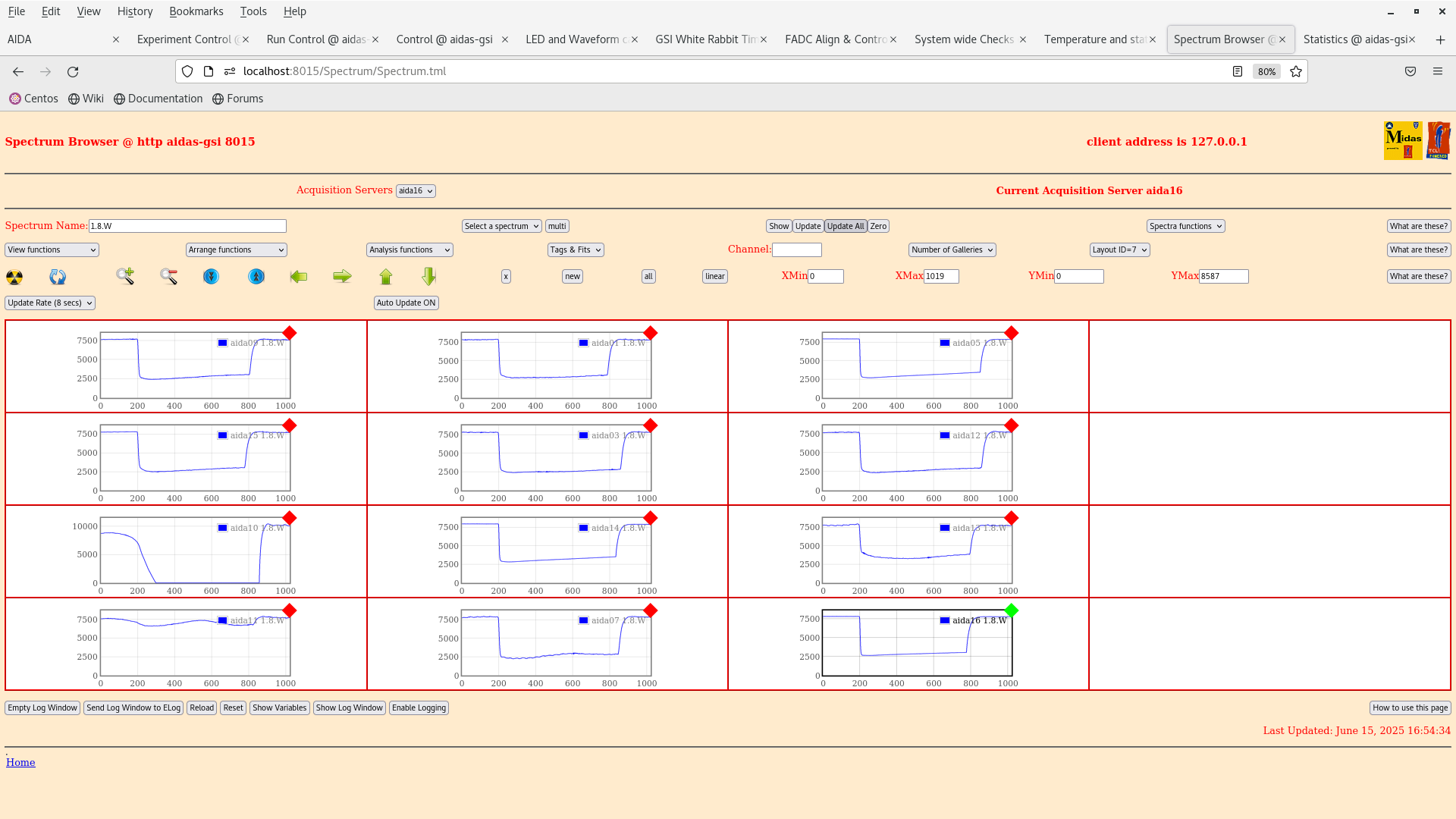

per p+n FEE64 1.8.W spectra - 20us FSR - attachments 20

per p+n FEE64 1.8.W spectra - 20us FSR - expanded y-scale = 2000 x 122uV/LSB = 0.244V FSR - attachment 21

per n+n FEE64 1.8.W spectra - 20us FSR - attachments 22

16.40 Add LK1 to aida03, aida07

DSSSD bias & leakage current - attachment 23

no change

ADC data item stats - attachment 24

per p+n FEE64 1.8.L spectra - attachment 25-26

pulser peak widths

aida05, aida14, aida16 c. 15-20 ch FWHM ( c. 10-15keV FWHM ) - cable from DSSSD not connected to adaptor PCB

aida15 c. 117 ch FWHM - electronic noise c. 2x worse than configuration used for 2023/4 tests

per p+n FEE64 1.8.W spectra - 20us FSR - attachments 27

no change

16.50 Increase DSSSD#0 bias from +100V to +120V

DSSSD bias & leakage current - attachment 28

per p+n FEE64 1.8.L spectra - attachment 29-30

pulser peak widths

aida05, aida14, aida16 c. 15-20 ch FWHM ( c. 10-15keV FWHM ) - cable from DSSSD not connected to adaptor PCB

aida15 c. 70 ch FWHM - electronic noise c. 1.2-2x worse than configuration used for 2023/4 tests

per FEE64 Rate spectra - attachments 31-32

per FEE64 1.8.W spectra - 20us FSR - attachments 33-36

aida02 & aida04 stabilised but still very noisy

Switch BNC PB-5 Pulser polarity + to - and connect test- test daisy chain

ADC data item stats - attachment 37

per FEE64 Rate spectra - attachments 38-39

aida02 & aida04 rates significantly lower but not 25Hz expected

per n+n FEE64 1.8.L spectra - attachment 40

pulser peak width aida02 c. 700 ch FWHM - very noisy!

per n+n FEE64 1.8.W spectra 20us FSR - attachment 41

*** Summary

DSSSD#0

3x Si wafers biased OK

p+n junction side electronic noise c. 1.2-2x 2023/4 configuration

n+n Ohmic side very noisy - increased detector HV to stabilise => increased capacitative load cf. 2023/4 configuration?

DSSSD#1

2x Si wafers biased OK, 1x probably not biased

p+n junction side electronic noise > 4x 2023/4 configuration

n+n Ohmic side very noisy/unstable - increased detector HV not attempted due to issues with biasing all 3x Si wafers

MSL type BB7

not biased yet

To Do

Complete connection and grounding of Bplas detectors |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|