|

|

|

AIDA

GELINA

BRIKEN

nToF

CRIB

ISOLDE

CIRCE

nTOFCapture

DESPEC

DTAS

EDI_PSA

179Ta

CARME

StellarModelling

DCF

K40

MONNET

|

| AIDA |

|

|

|

|

Message ID: 423

Entry time: Sat Nov 5 01:55:15 2016

|

| Author: |

CG, TD, OH |

| Subject: |

Saturday 5th November |

|

|

10.55 DAQ found to have stopped at 06:47 during LN fill cycle.

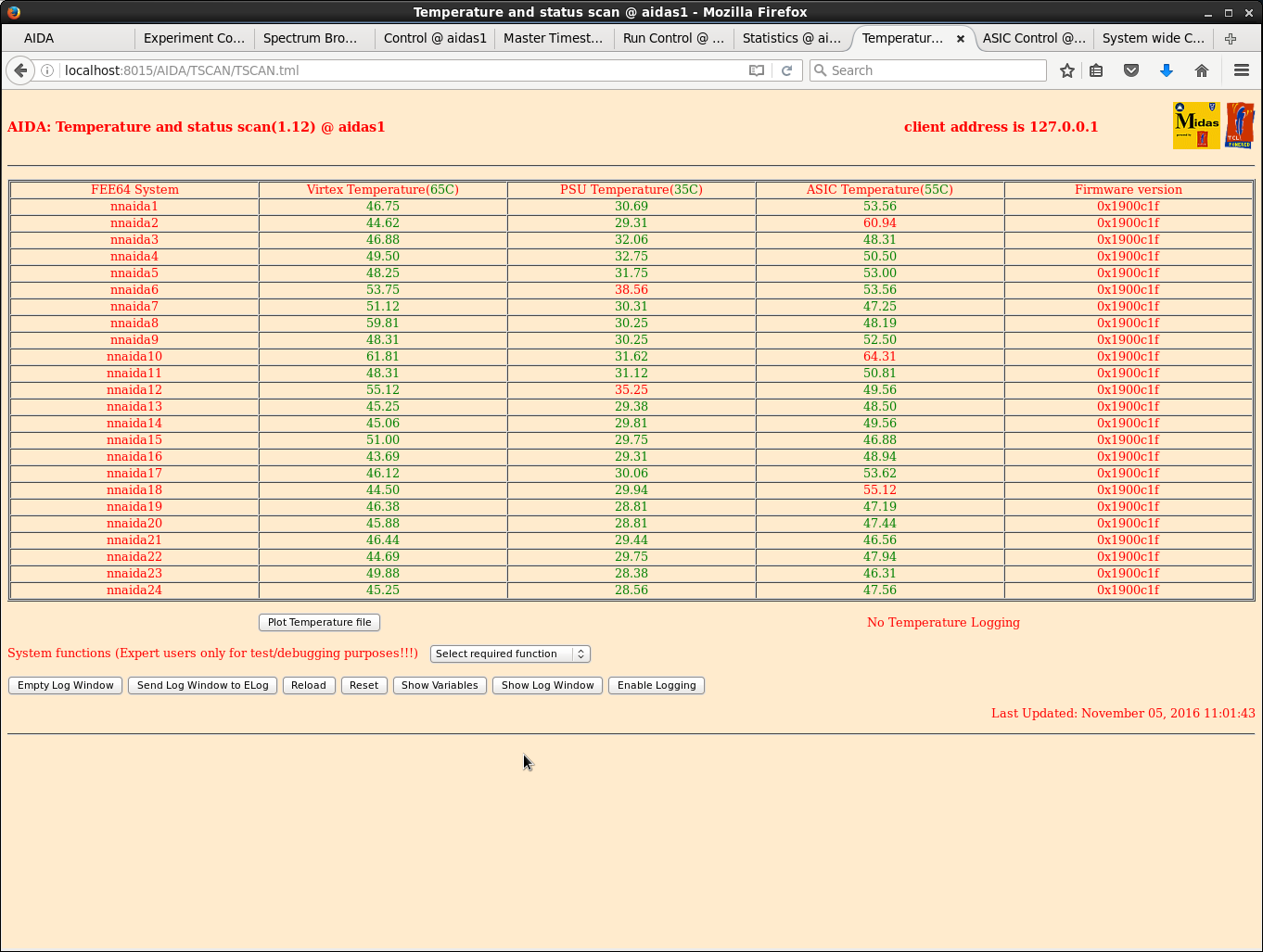

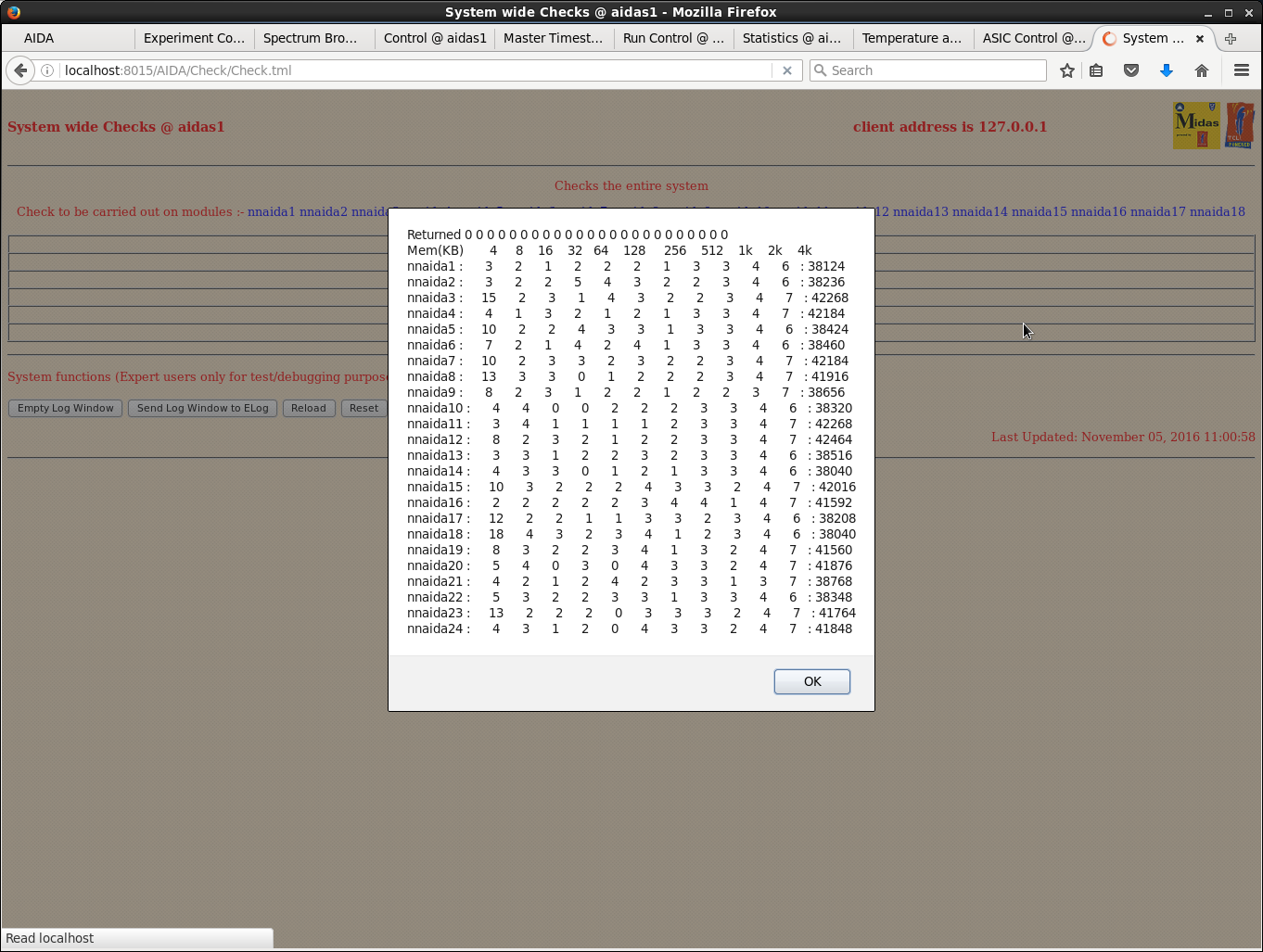

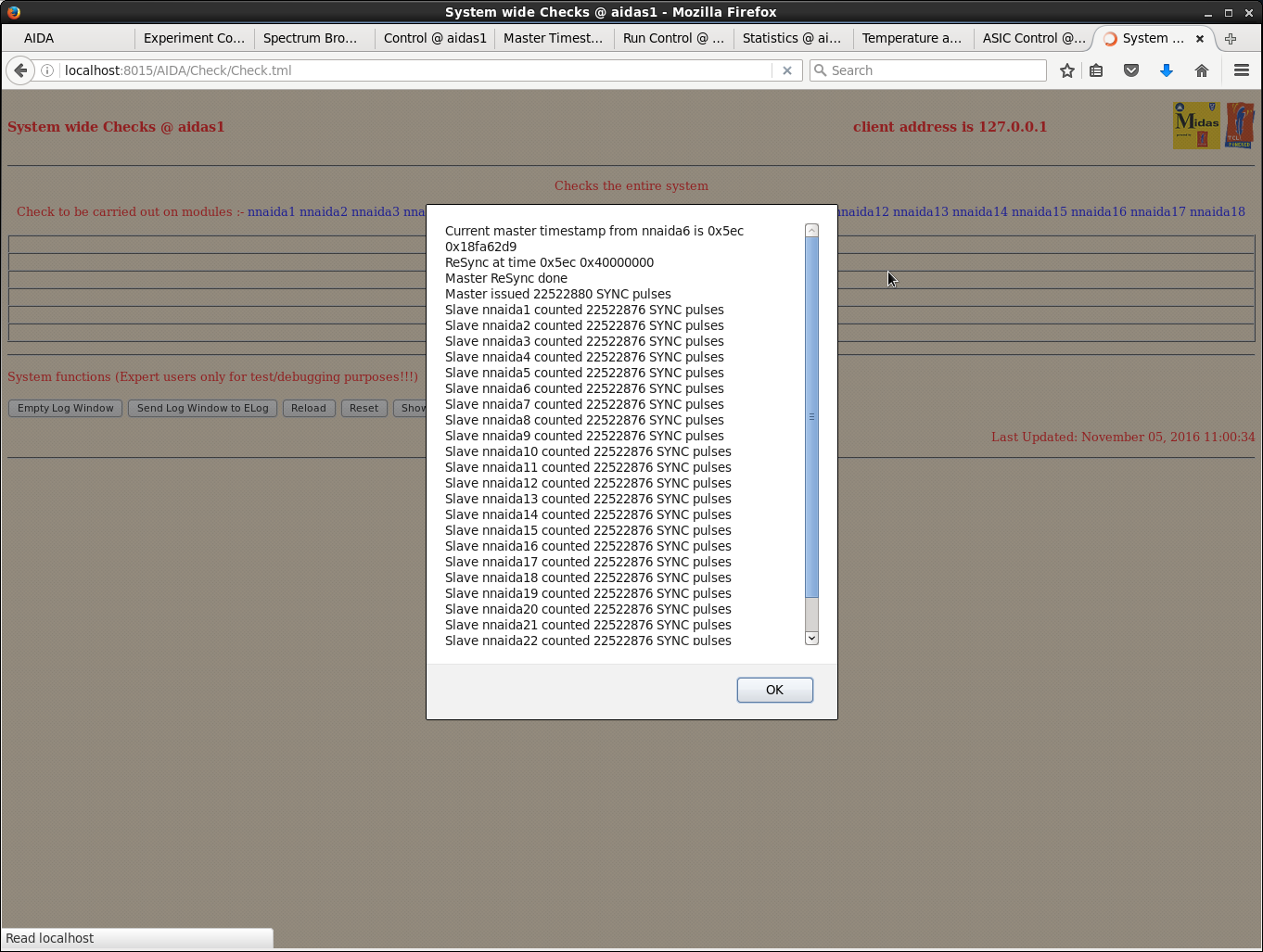

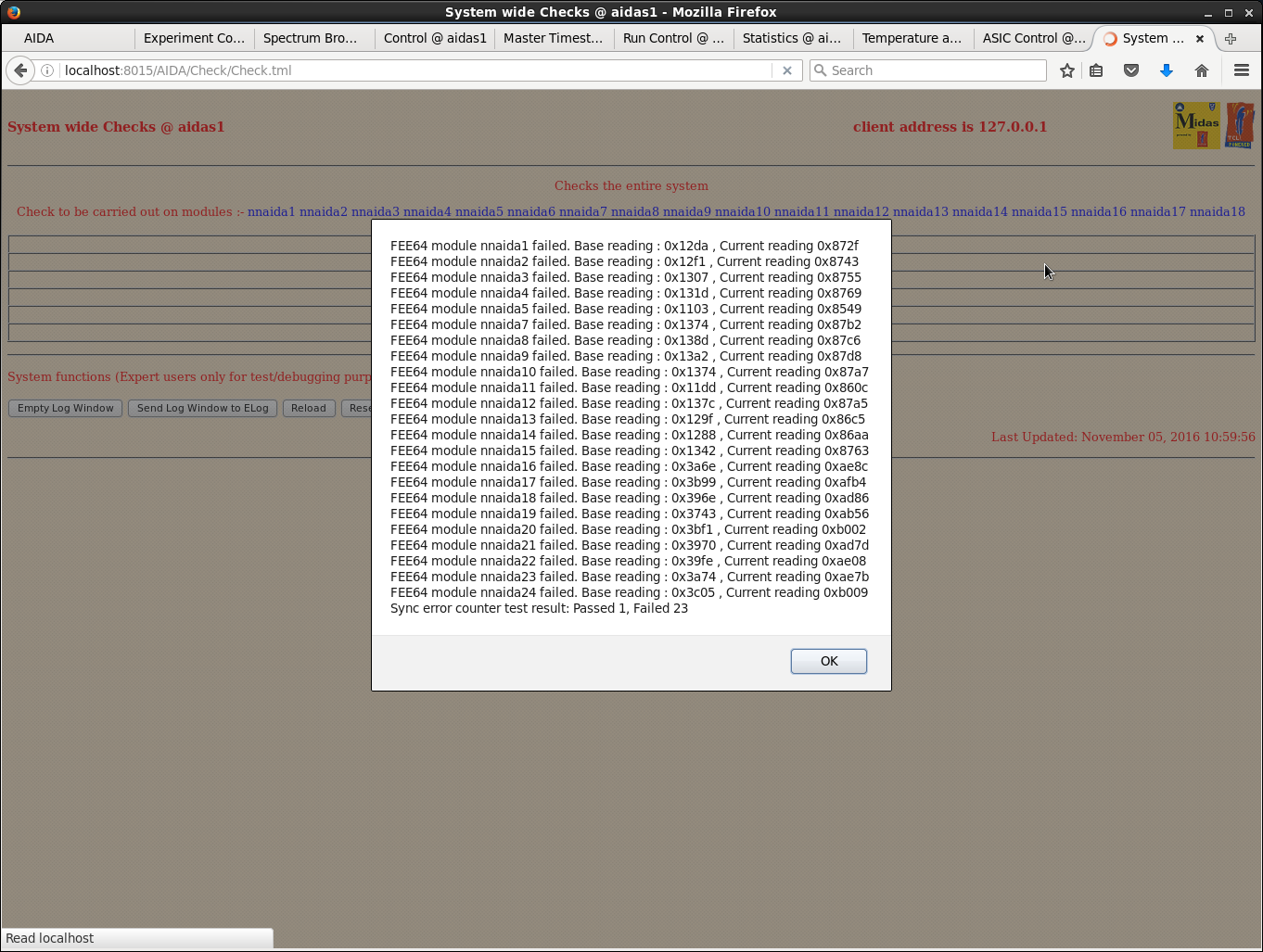

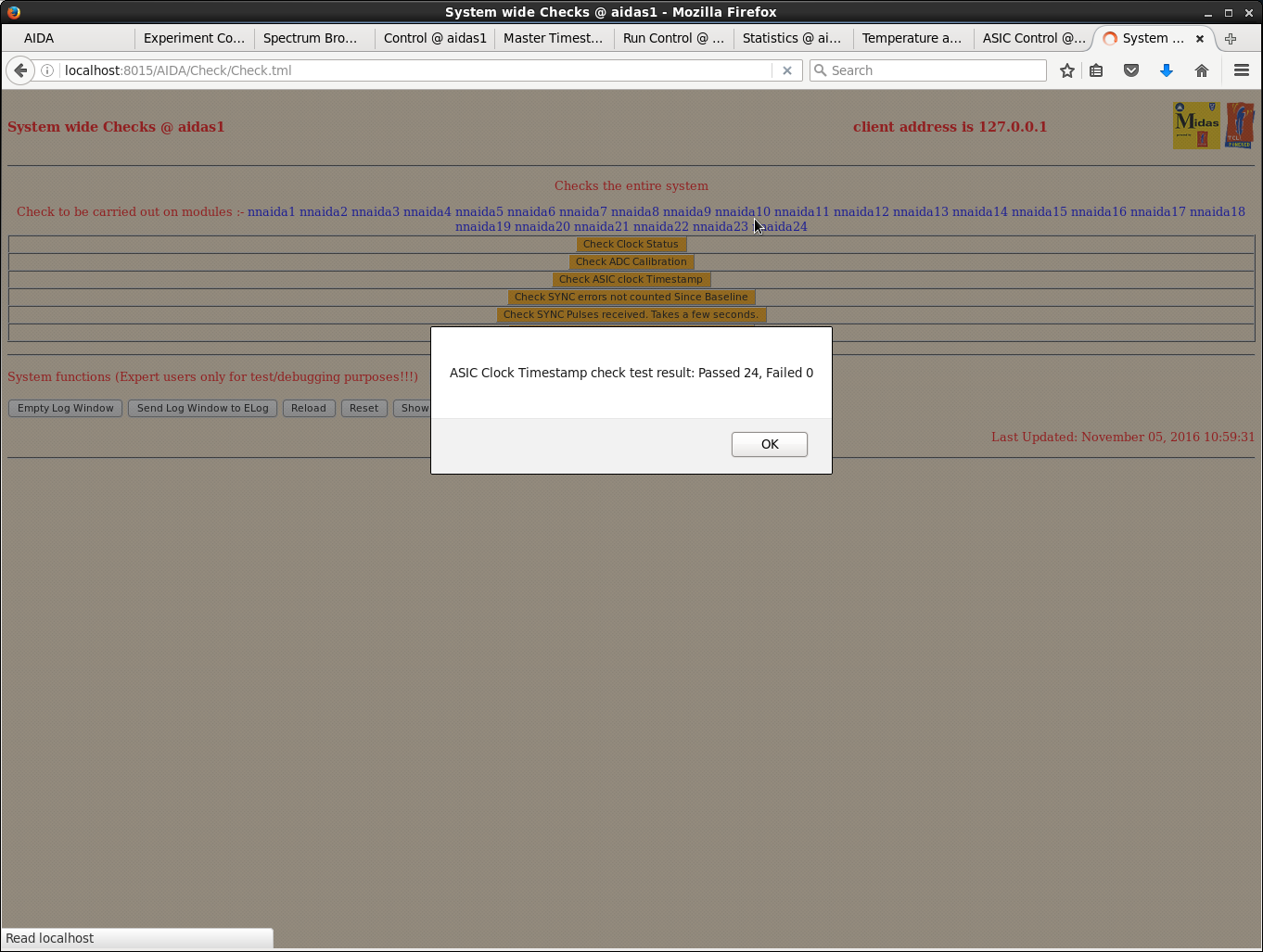

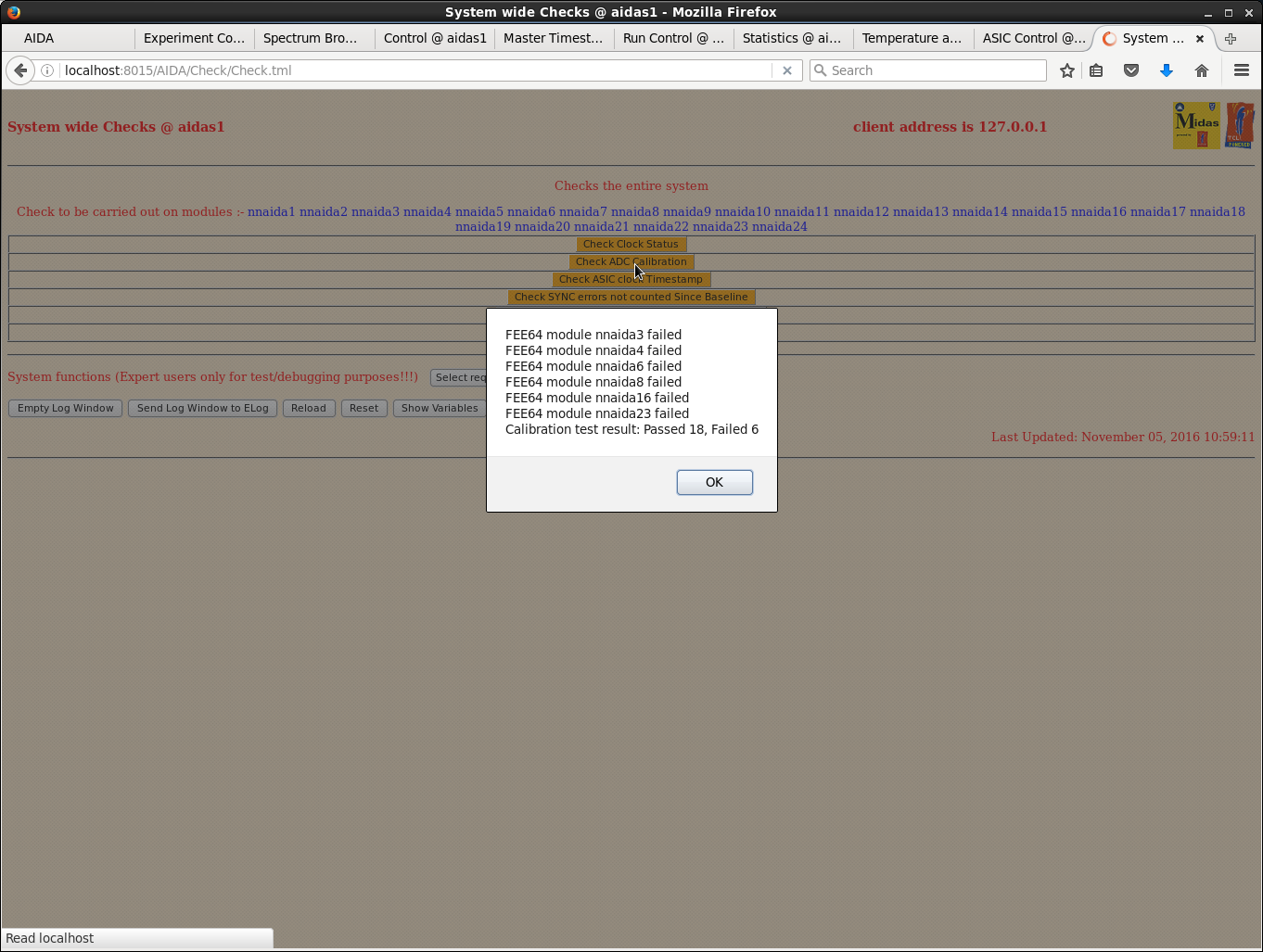

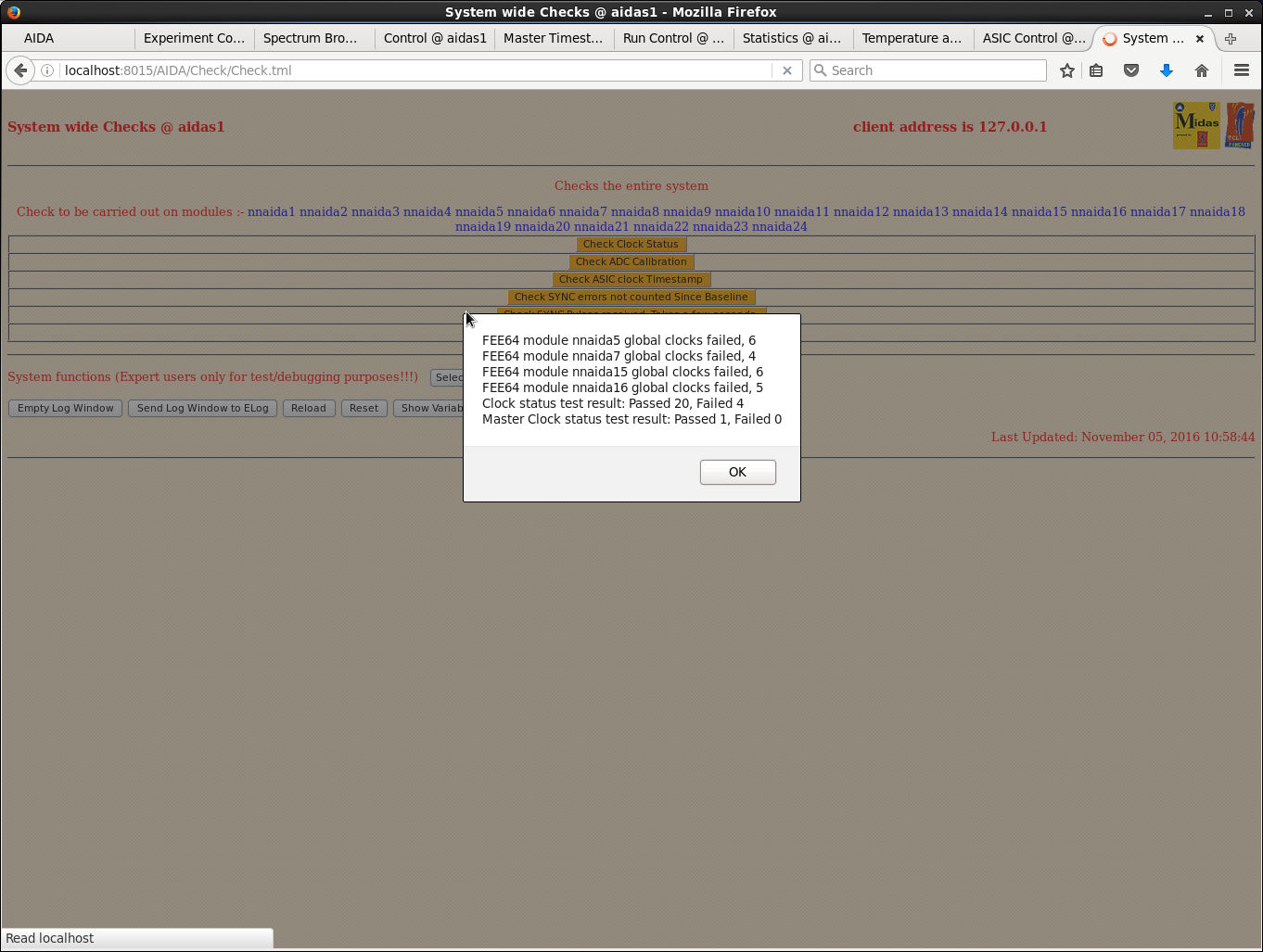

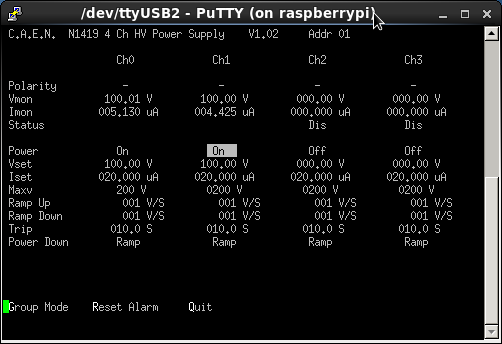

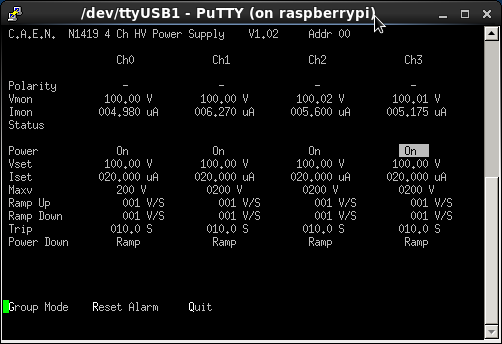

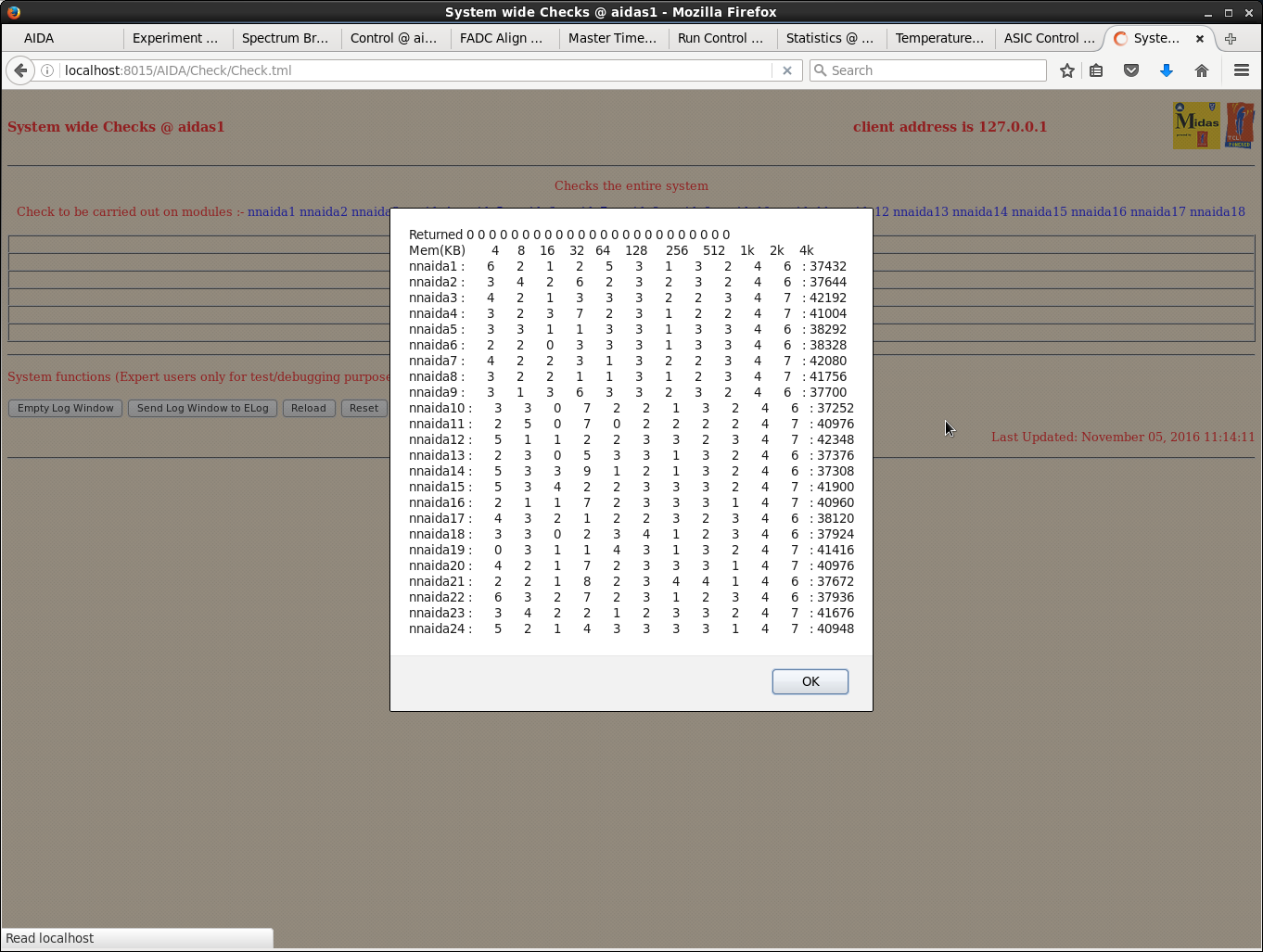

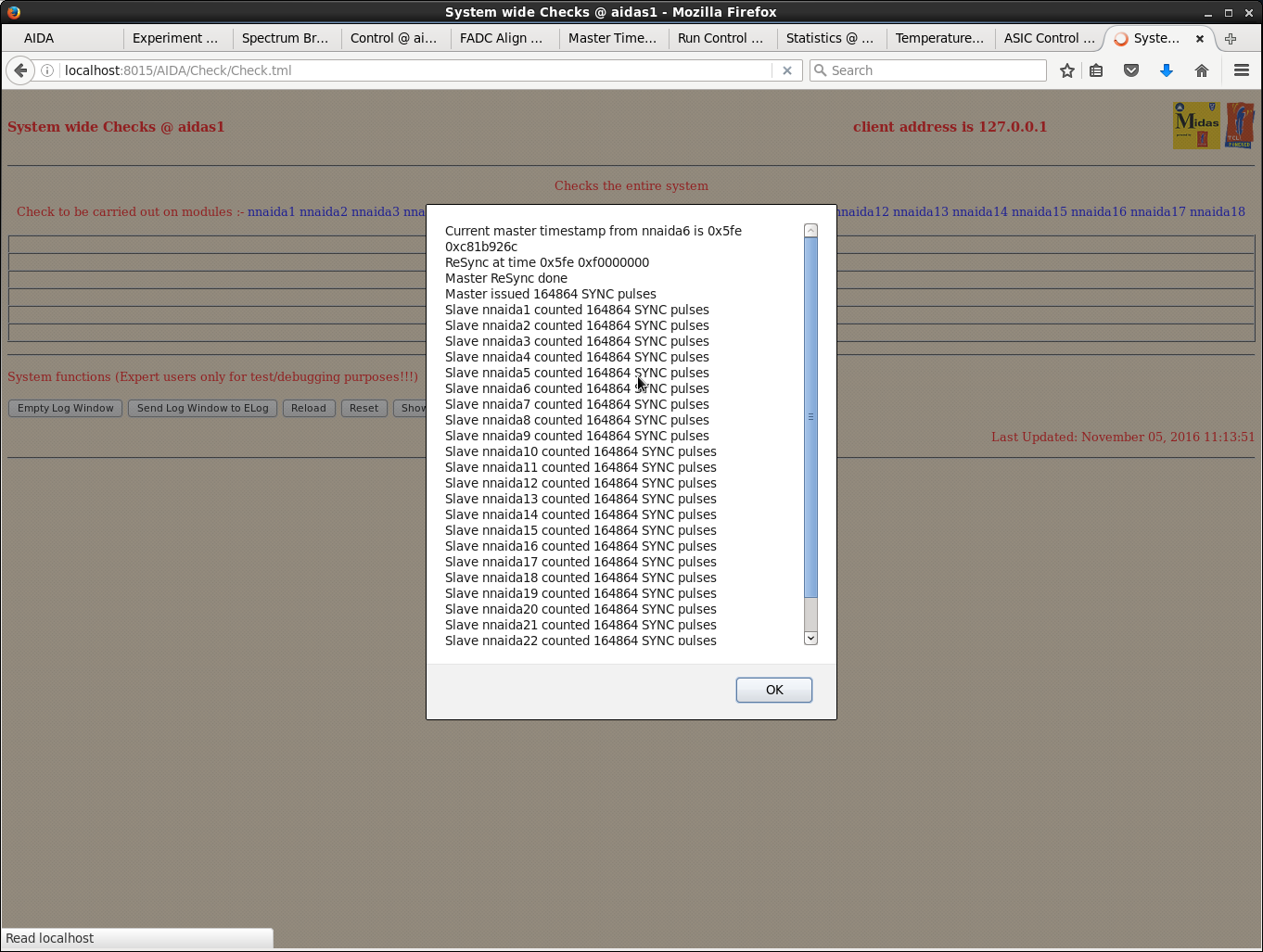

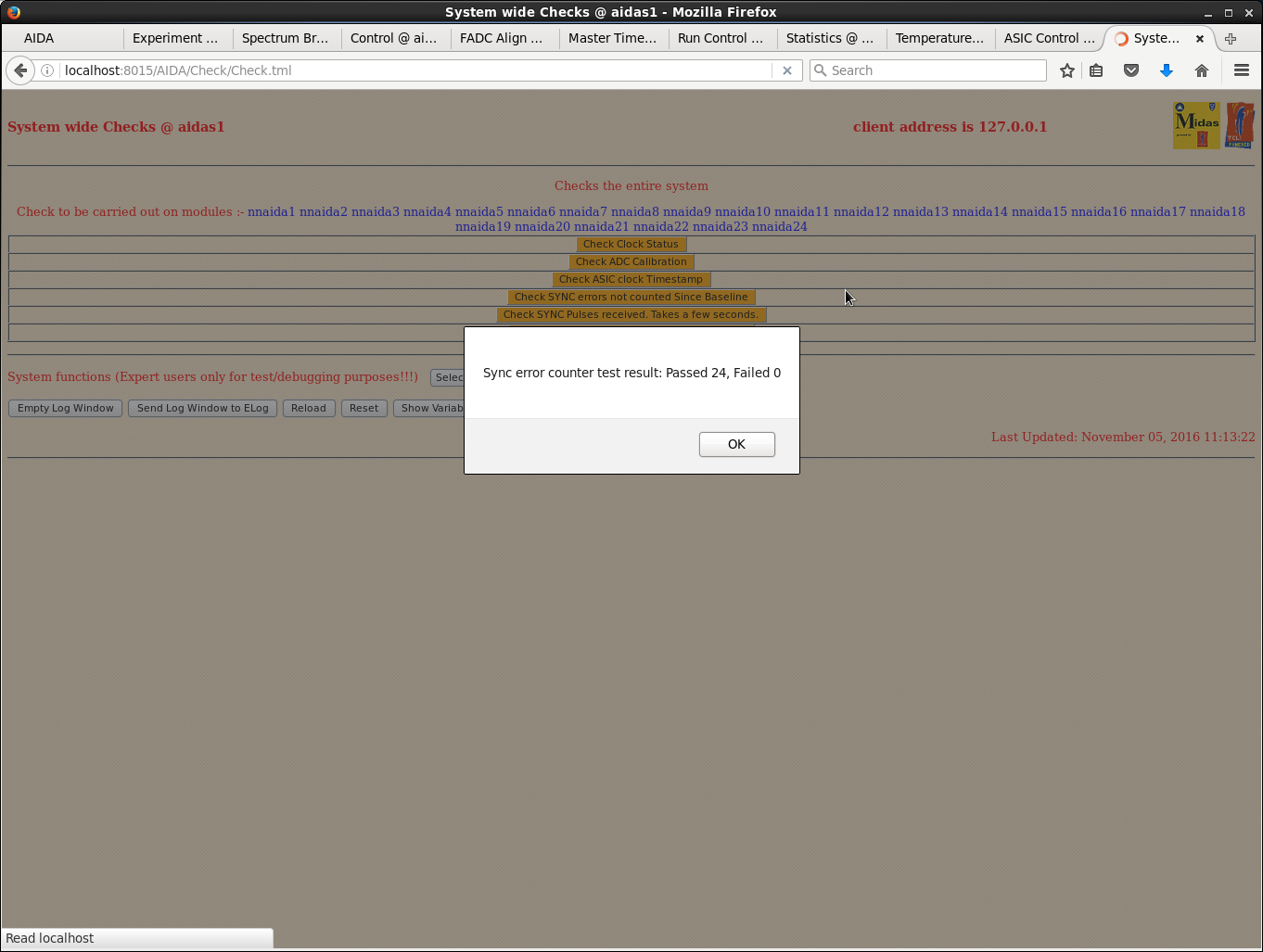

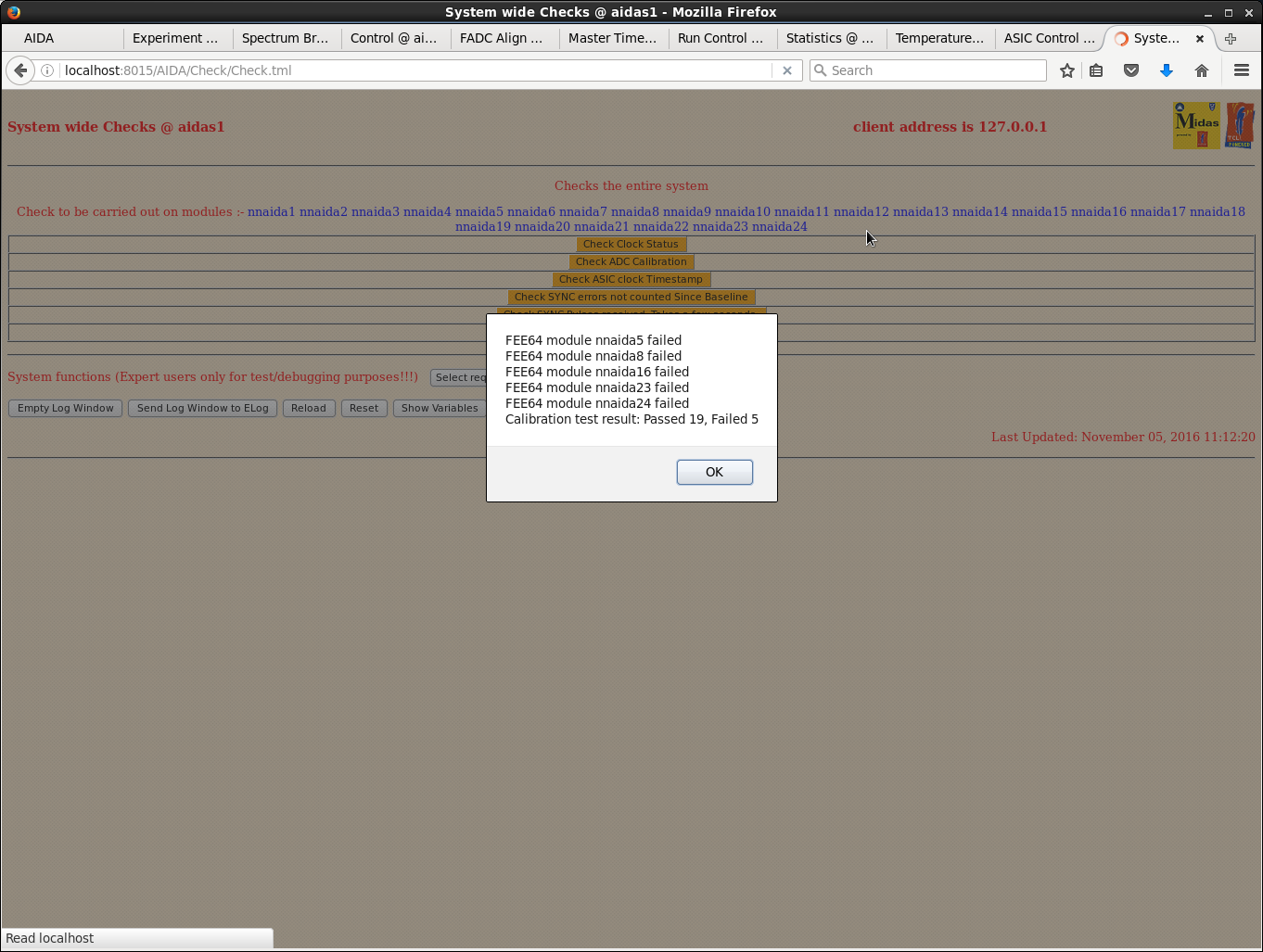

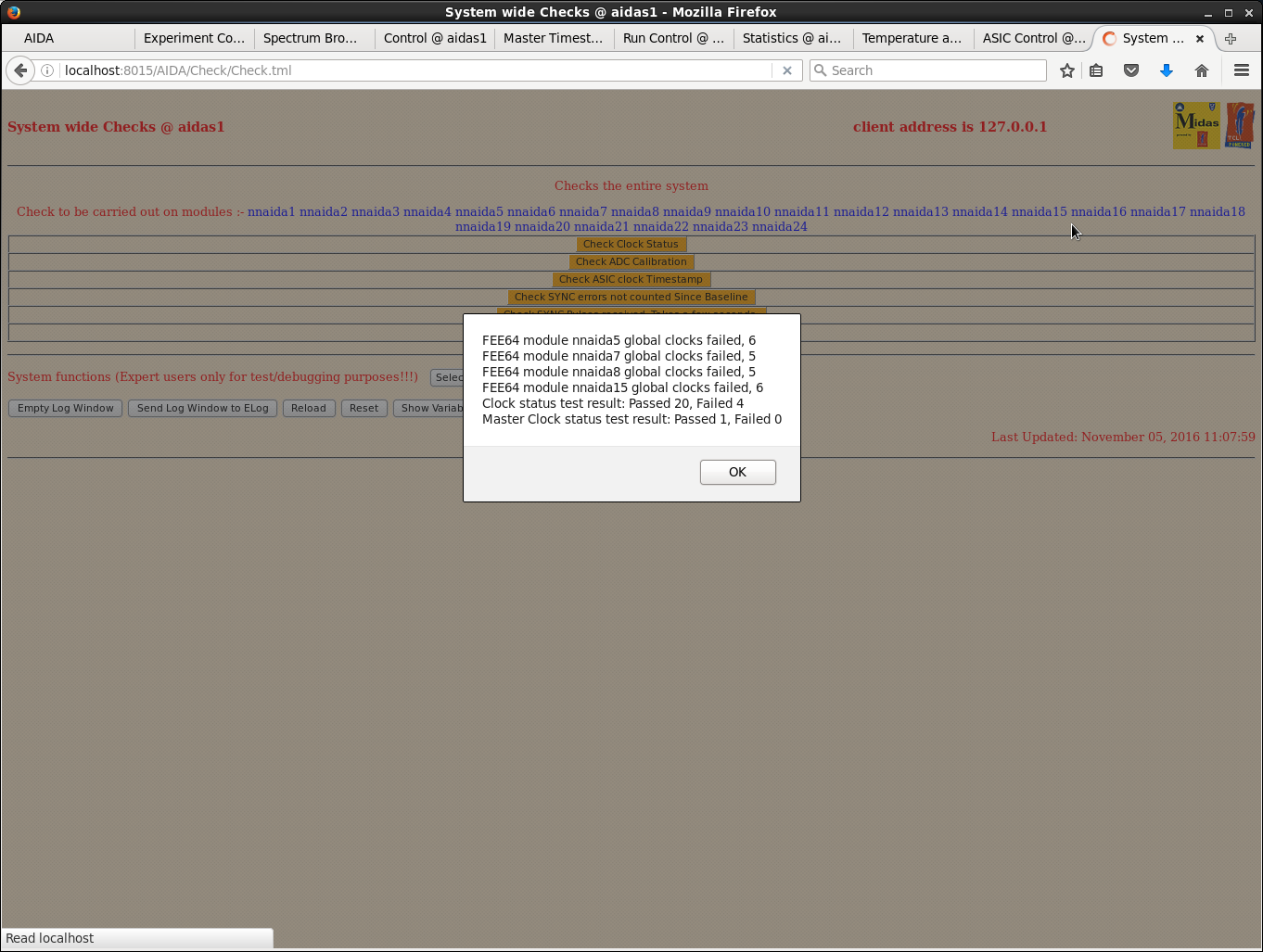

10:57 Screen shots of system after stop

11.20 R122 started.

System check screen shots attached at 11:08

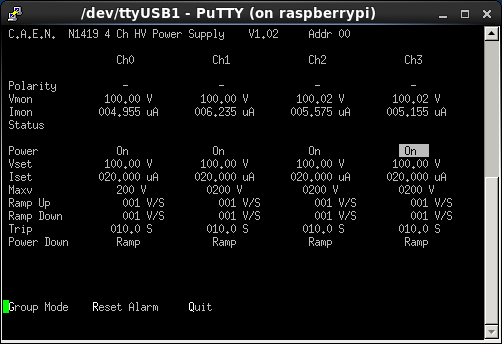

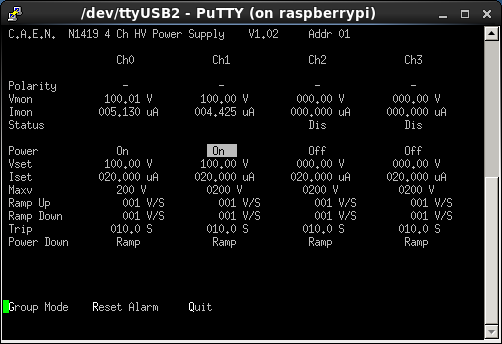

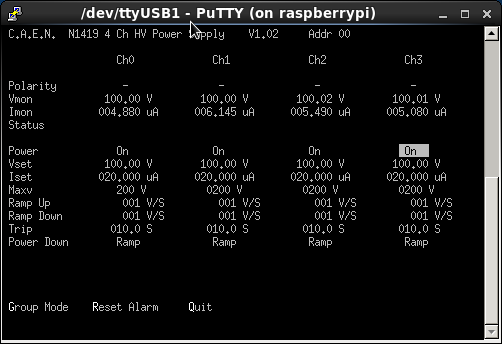

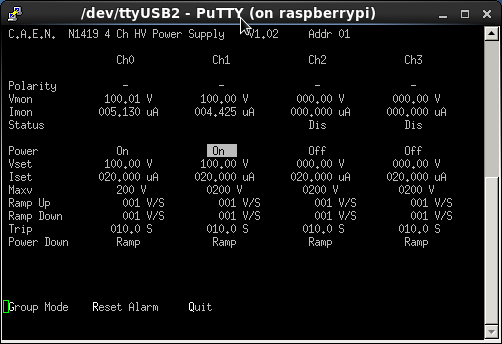

18.20 System been running stably all day. Leakage currents attachments 14+15.

LN2 fill cycle shortly, anticipate DAQ stop.

19.16 DAQ stopped.

Closed file R122.

19.37 Temp 25.3 DP 6.1 Hum 31.1

Added 2 extra stacks of lead bricks to protect AIDA. Now ~15cm of lead (Attachment 17)

23.30 DSSSD bias & leakage currents OK - see attachments 18-19

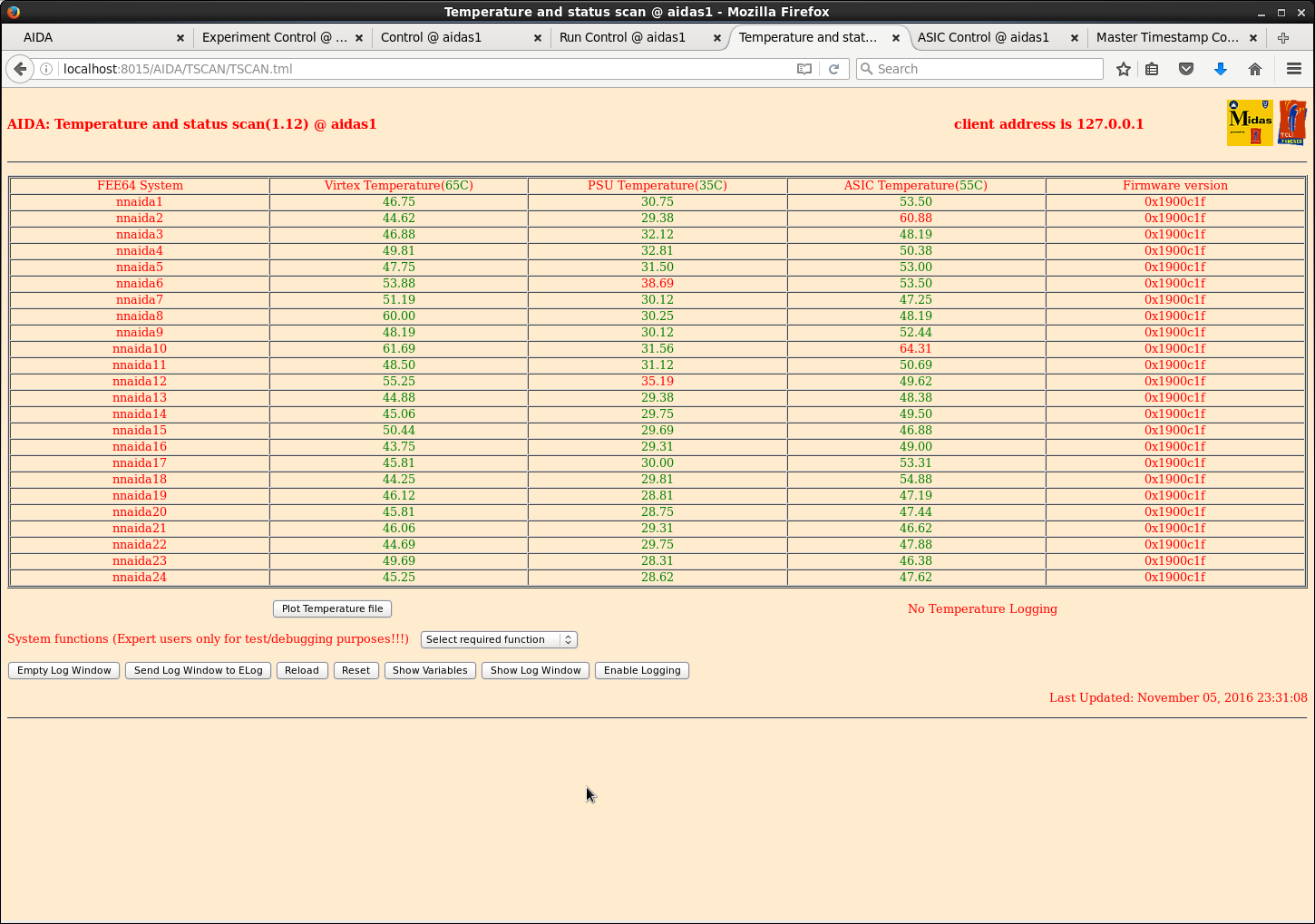

FEE74 temperatures OK - see attachment 20

23.54 DAQ starts (R124)

Merge rate 1.8M items/s, c. 13Mb/s to disk c. x2 earlier rates

Dominated by significantly higher rates from DSSSD#1

FEE64 #17 ASIC 2*L pulser peak widths ~300 ch FWHM

Needs to be investigated at next entry opportunity |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|