|

|

|

AIDA

GELINA

BRIKEN

nToF

CRIB

ISOLDE

CIRCE

nTOFCapture

DESPEC

DTAS

EDI_PSA

179Ta

CARME

StellarModelling

DCF

K40

MONNET

|

| AIDA |

|

|

|

|

Message ID: 947

Entry time: Tue Apr 1 15:34:16 2025

|

| Author: |

TD, MR, CU |

| Subject: |

Tests of new AIDA ASIC mezzanines - 2024 production batch |

|

|

Tests of new AIDA ASIC mezzanines - 2024 production batch

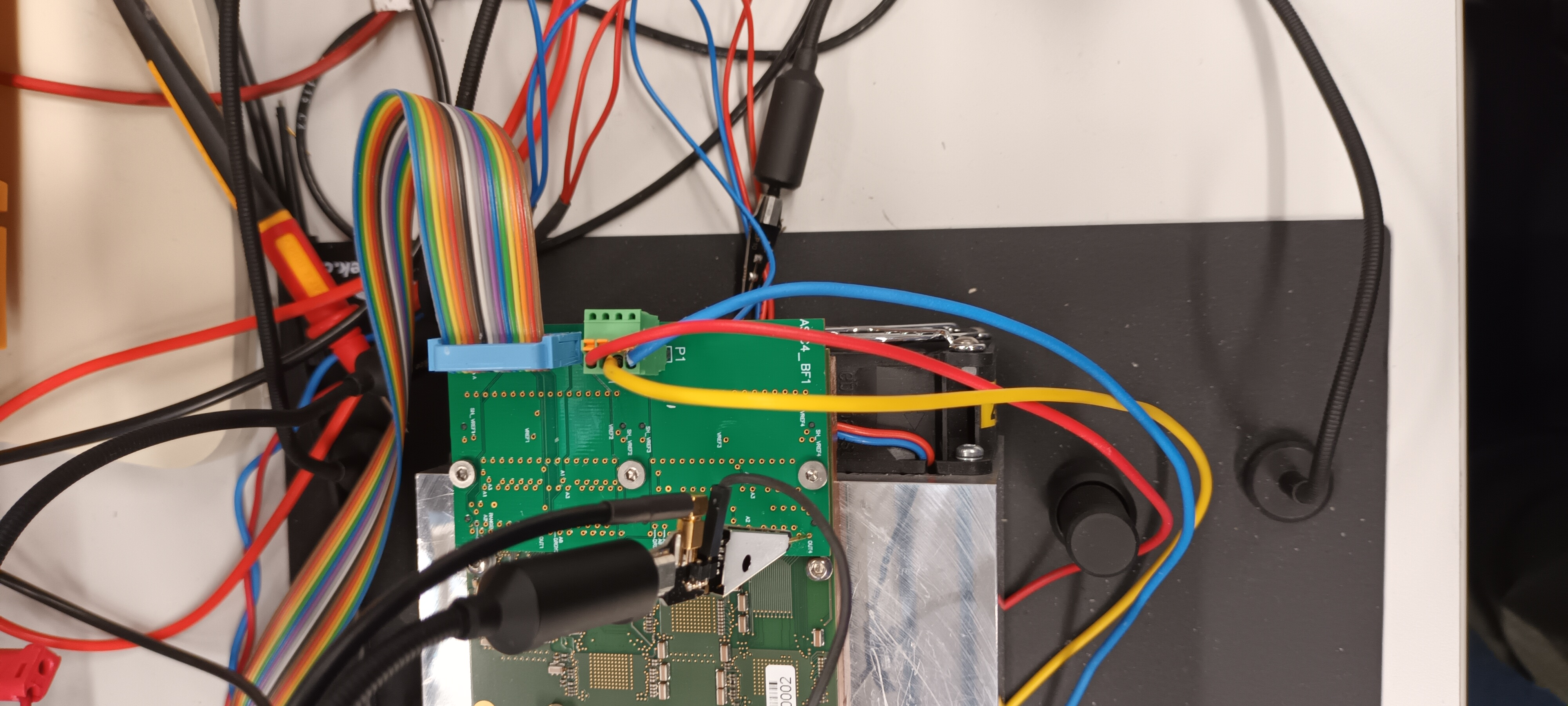

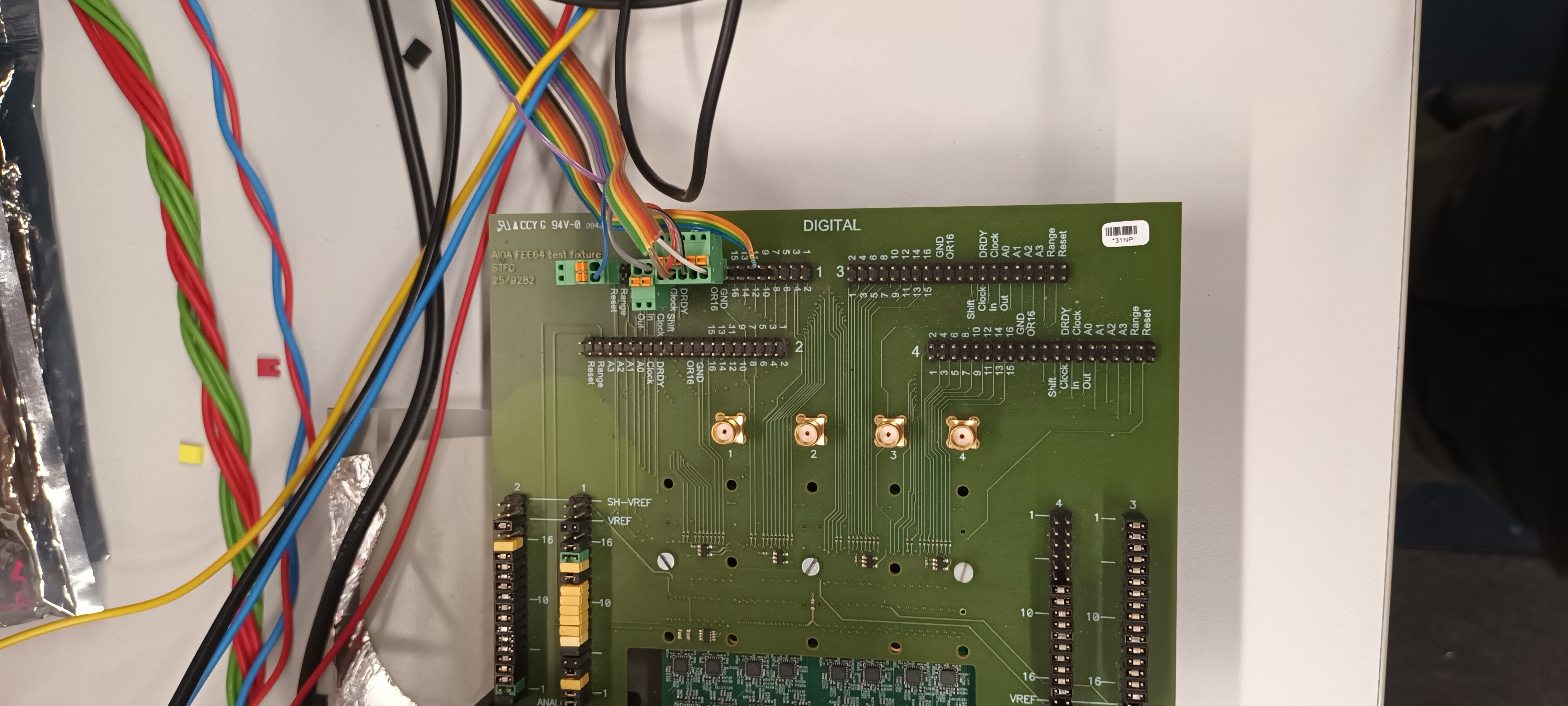

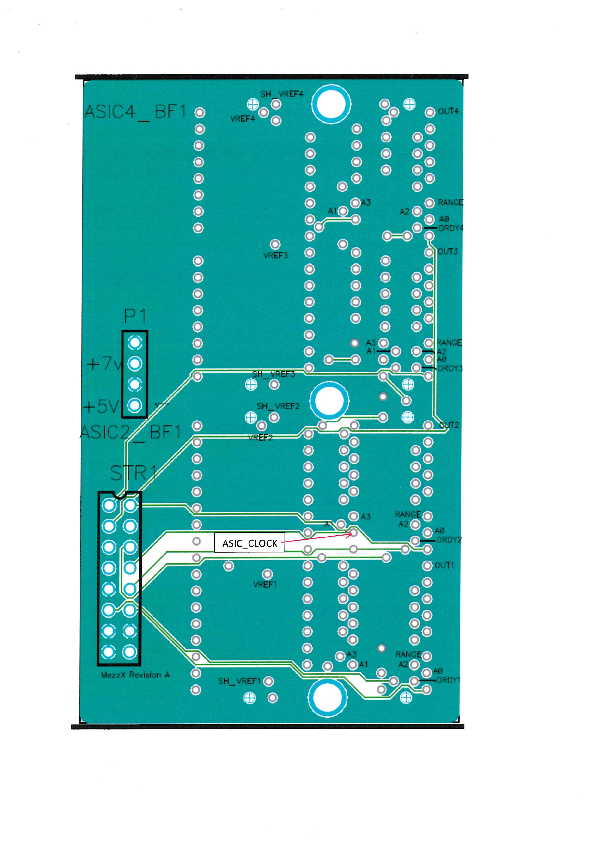

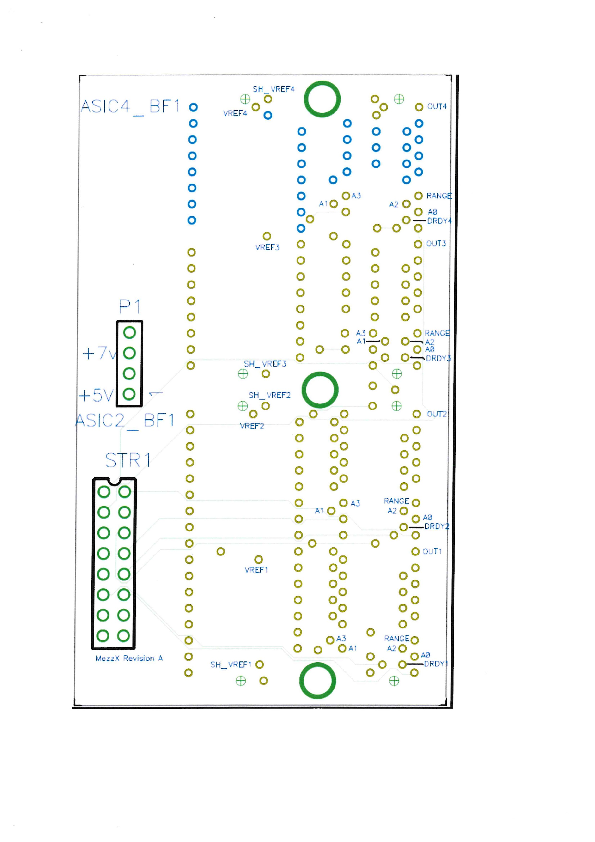

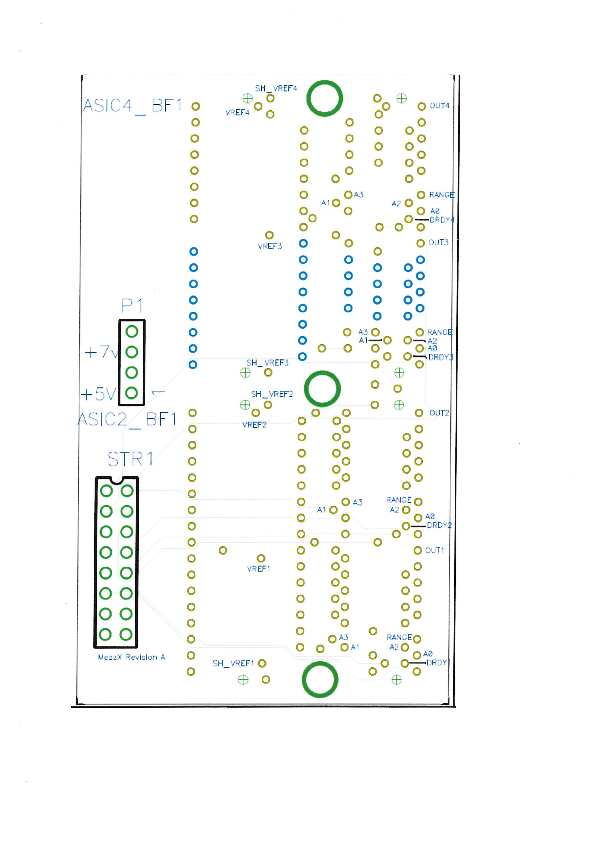

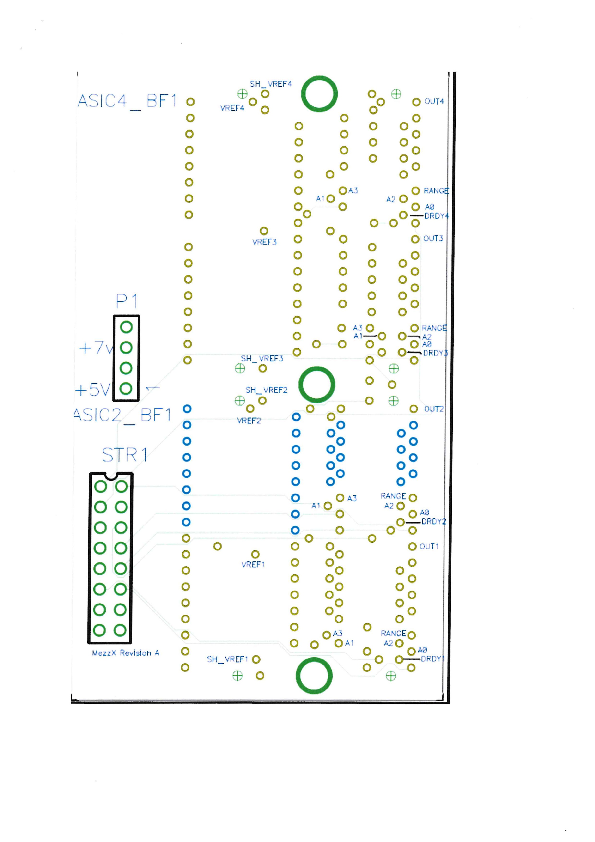

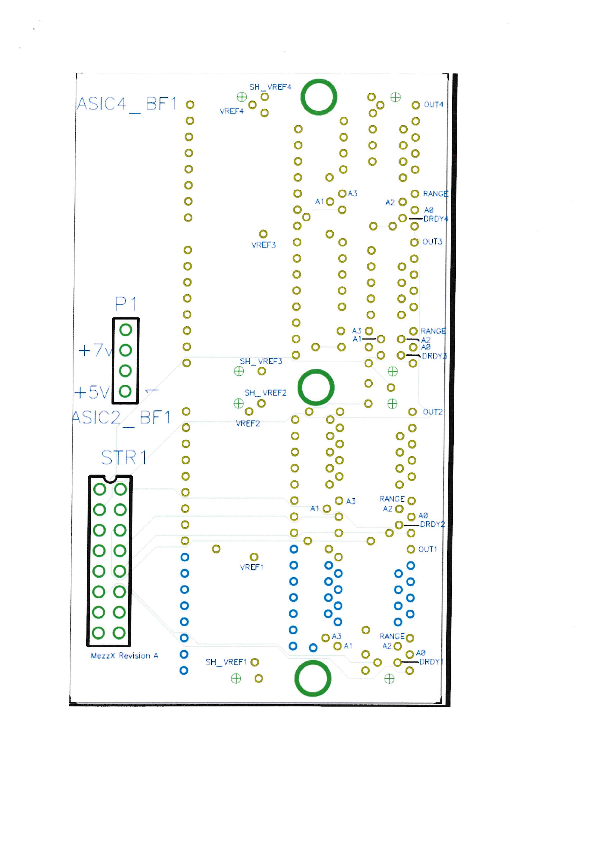

Using nnlycca4/MezzX PCB test bench T9, STFC DL - attachments 1 & 2

nnlycca4 193.62.115.228

BNC PB-4 Pulser

Amplitude ?9000

Attenuator x5 IN

Frequency 25Hz

Polarity +

t_r 50ns

tau_d 200us

Delay MIN

Ref INT

Output amplitude (DSO hi Z input) c. 500mV

MACB

Program switch = 1

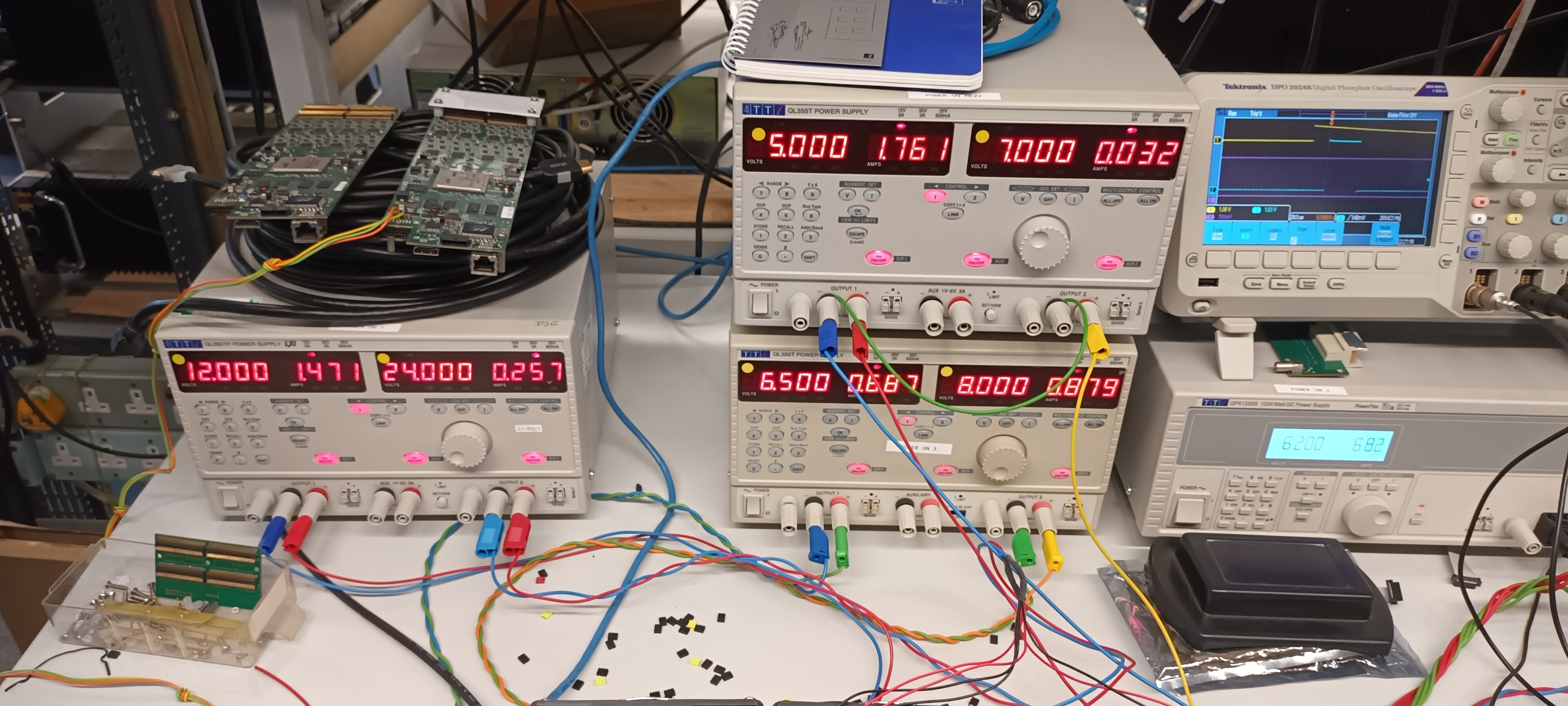

Power on sequence - 1 2 3 Mezzanine - attachment 3

1 - FEE64 and ASIC mezzanine cooling fans

2 - FEE64 +6.2V/+6.8A

3 - FEE64 -6.5V/-0.69A, +8V/+0.88A

4 - Mezzanine +5V/+1.7A +7V/+0.03A

At power up ASIC mezzanine +5V/+2.1A which decreases to +5V/+1.7A following DAQ SETUP

Pulser to *all* inputs via test adaptor PCB (PJCS design)

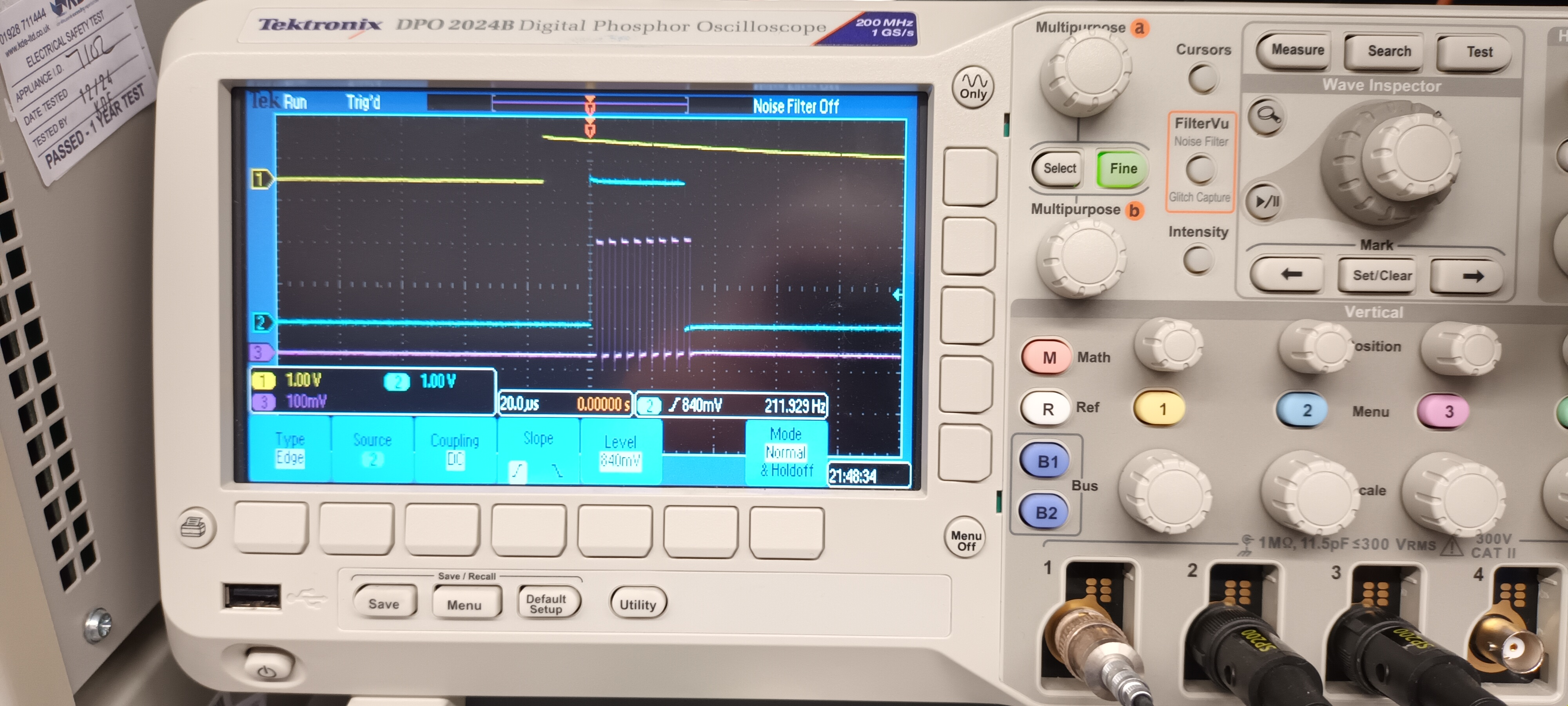

Examples of test signals as follows:

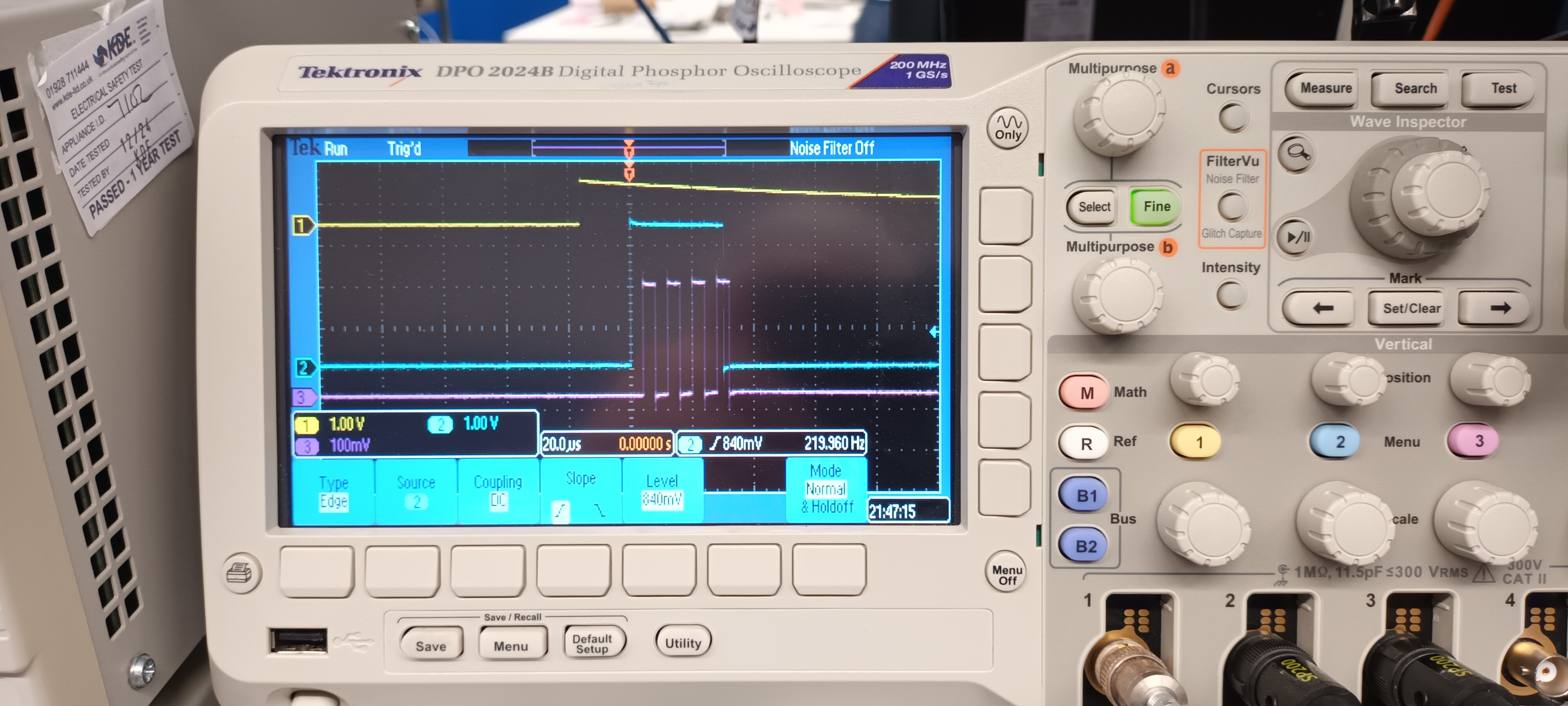

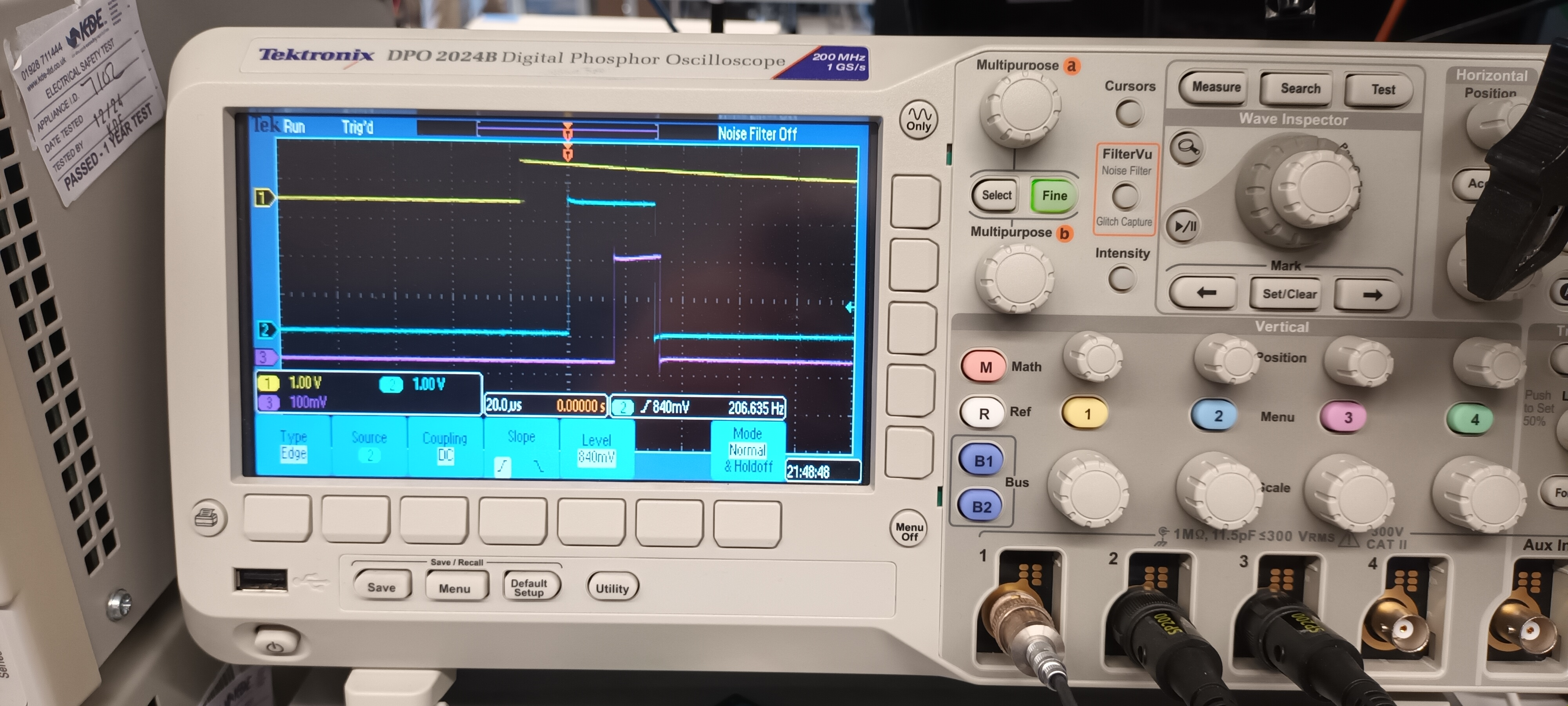

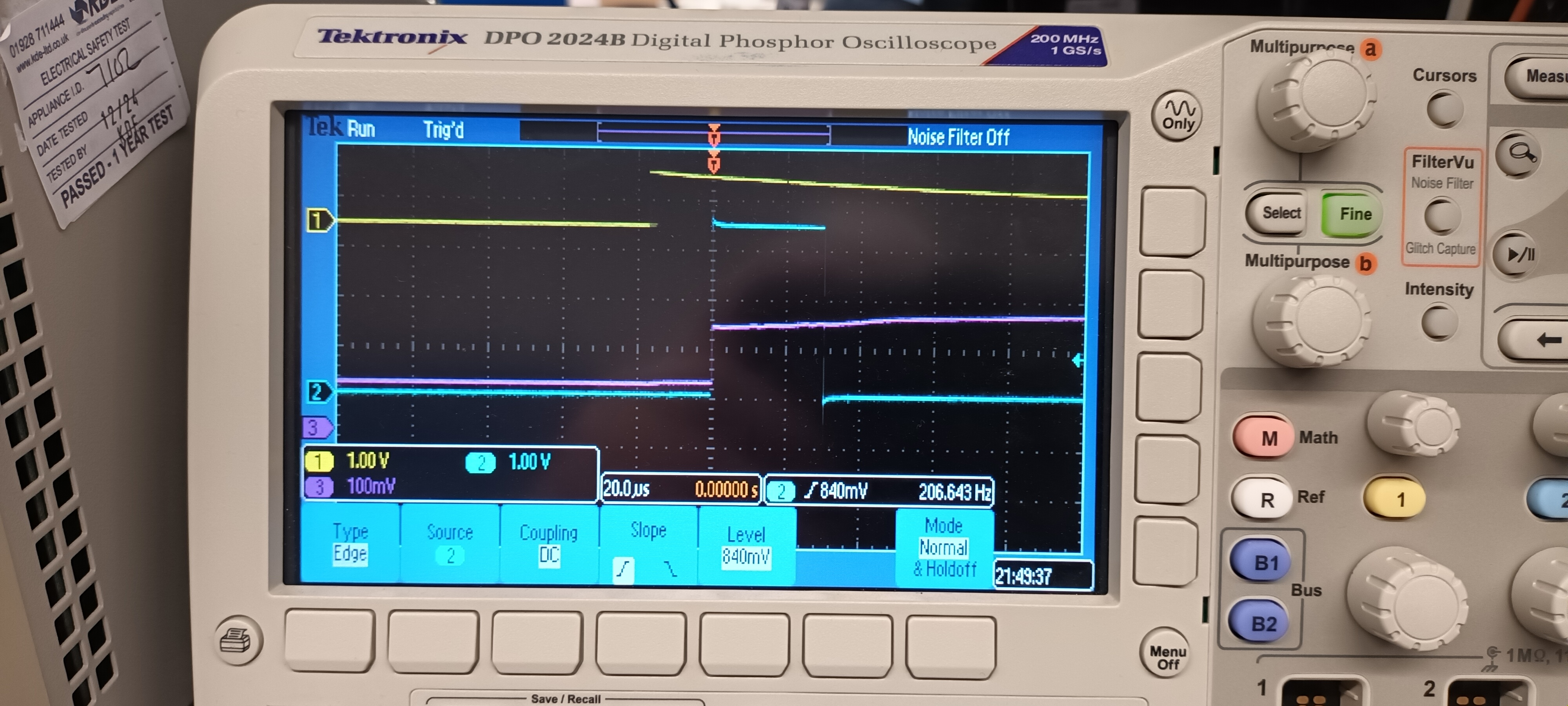

Data Ready DRDY (blue), Address bits A0-A3 (magenta), pulser (yellow) - attachments 4-7

MUX Out (magenta) - attachment 8

LEC fast comparator (magenta) - attachment 9

Preamp output (magenta) - attachment 10

Following power up and the boot of the embedded PowerPC processor

DAQ RESET

DAQ SETUP

DAQ GO

Start ASIC Readout

*multiple* Check ASIC Load for ASIC #2 (note this check loads all ASICs)

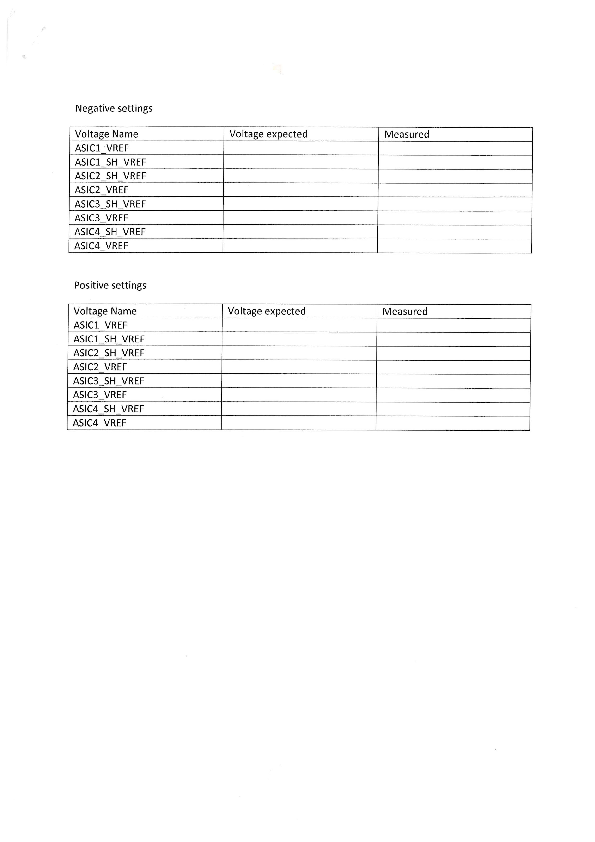

Use DSO scope probe at MezzX PCB test points - attachment 11

All ASICs of the following ASIC mezzanines tested OK

Batch 0216240101

-0009

Batch 0213110101

-0002

Batch 0324390101 (*new* batch 2024/Q4)

-0010

-0011

-0019 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|