|

|

|

AIDA

GELINA

BRIKEN

nToF

CRIB

ISOLDE

CIRCE

nTOFCapture

DESPEC

DTAS

EDI_PSA

179Ta

CARME

StellarModelling

DCF

K40

MONNET

|

| DESPEC |

|

|

|

|

Message ID: 298

Entry time: Thu May 6 16:59:20 2021

|

| Author: |

TD, OH |

| Subject: |

Wednesday 6 May |

|

|

18.09 NH has installed jumpers LK2-4 for *all* adaptor PCBs

per FEE64 rate spectra - attachments 1-4

attachment 4 with BNC PB-5 pulser 10Hz

ADC data items stats - attachment 5

1.8.W spectra - attachments 6 & 7

Observe significant reduction in DSSSD/ribbon cable boundary channel rates

- status quo ante Tuesday 4 May https://elog.ph.ed.ac.uk/DESPEC/291 ?

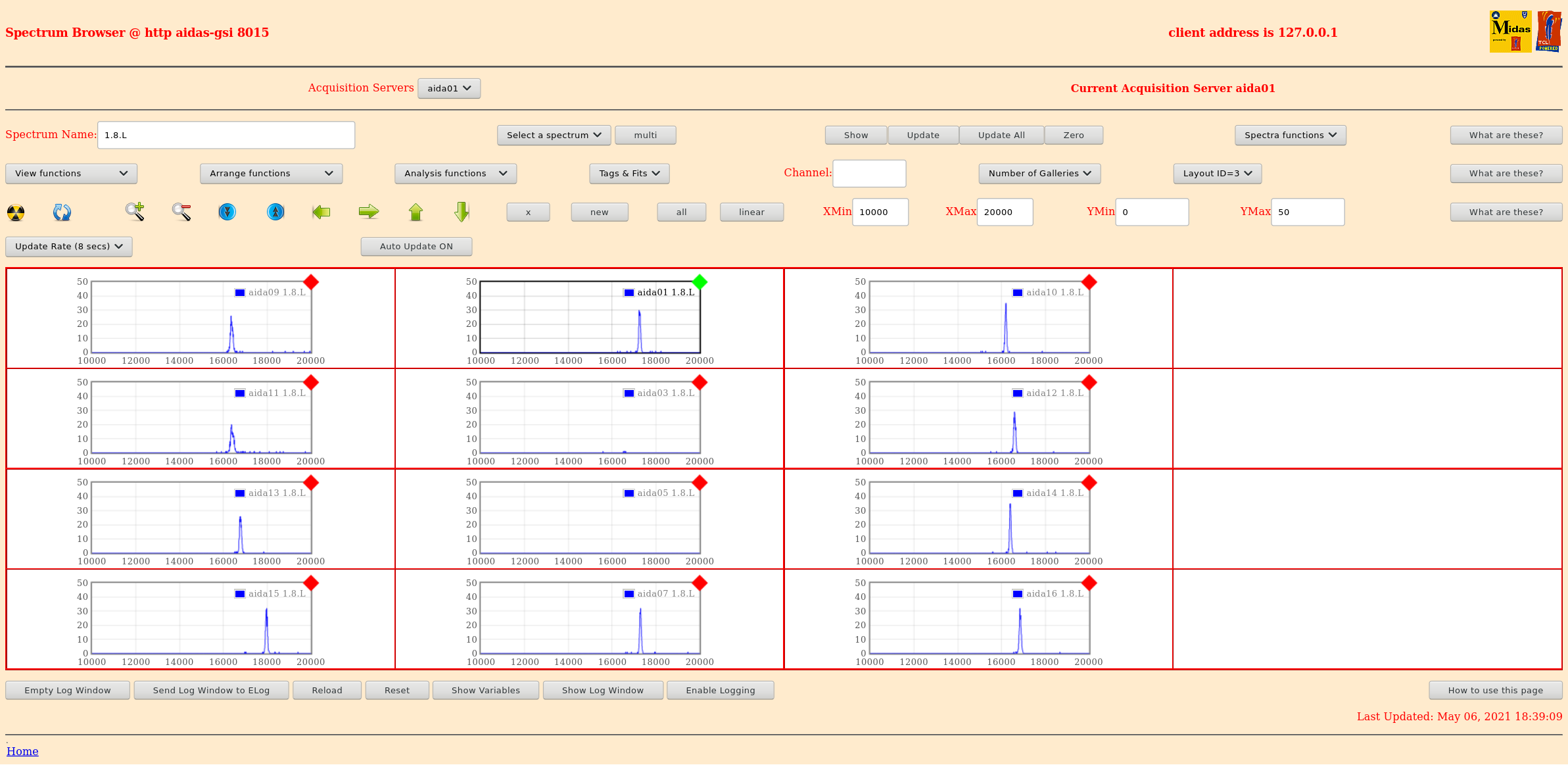

1.8.L spectra - attachments 8 & 9

pulser peak width aida01 85 ch FWHM, aida2 295 ch FWHM

19:21 Alpha run started May21/R6

Statistics dominated by aida04 with a rate of 6k

System wide checks all ok except:

Base Current Difference

aida13 fault 0x0 : 0x17 : 23

FPGA Timestamp error counter test result: Passed 15, Failed 1

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

Writing to file at ~300kB/s

Rate spectra for aida04 shows dominated by first asic - attachment 10

1*L spectra for aida04 asic 1 - attachment 11

20.25 per FEE64 rate spectra - attachment 12

handful of hot channels aida06, 09 & 10

ADC data item stats - attachment 13 |

|

.png.png)

|

|

.png.png)

|

|

.png.png)

|

|

.png.png)

|

|

.png.png)

|

|

.png.png)

|

|

.png.png)

|

|

|

|

.png.png)

|

|

|

|

|

|

.png.png)

|

|

|