|

|

|

AIDA

GELINA

BRIKEN

nToF

CRIB

ISOLDE

CIRCE

nTOFCapture

DESPEC

DTAS

EDI_PSA

179Ta

CARME

StellarModelling

DCF

K40

MONNET

|

| DESPEC |

|

|

|

|

Message ID: 316

Entry time: Fri May 14 07:05:08 2021

|

| Author: |

CA |

| Subject: |

Friday 14th May 08:00 - 16:00 shift |

|

|

08:00 CA takes over

08:28 Problem at UNILAC - no beam

09:30 all system wide checks ok *except*

all FEE64 fail ADC calibration (no waveforms)

WR decoder status:

Base Current Difference

aida01 fault 0xf932 : 0xf933 : 1

aida02 fault 0x62ec : 0x62ed : 1

aida03 fault 0x8679 : 0x867a : 1

aida04 fault 0xf0e4 : 0xf0e5 : 1

aida05 fault 0x9db8 : 0x9dc2 : 10

aida06 fault 0x7f18 : 0x7f19 : 1

aida07 fault 0xdd2c : 0xdd2d : 1

aida08 fault 0x1557 : 0x1558 : 1

White Rabbit error counter test result: Passed 8, Failed 8

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

FPGA timestamp errors:

Base Current Difference

aida05 fault 0x0 : 0x2 : 2

FPGA Timestamp error counter test result: Passed 15, Failed 1

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

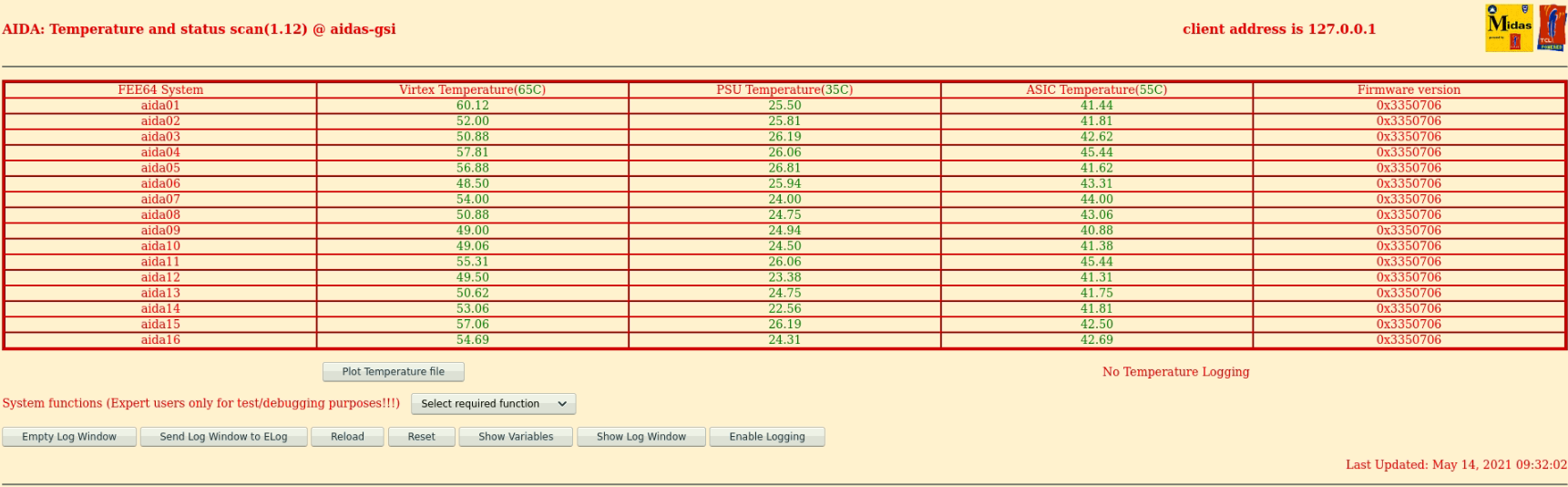

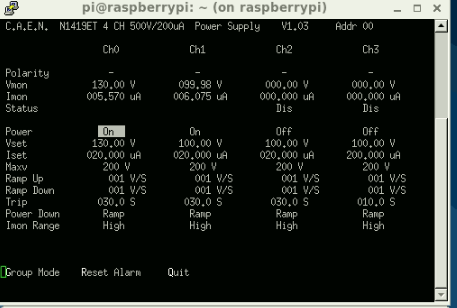

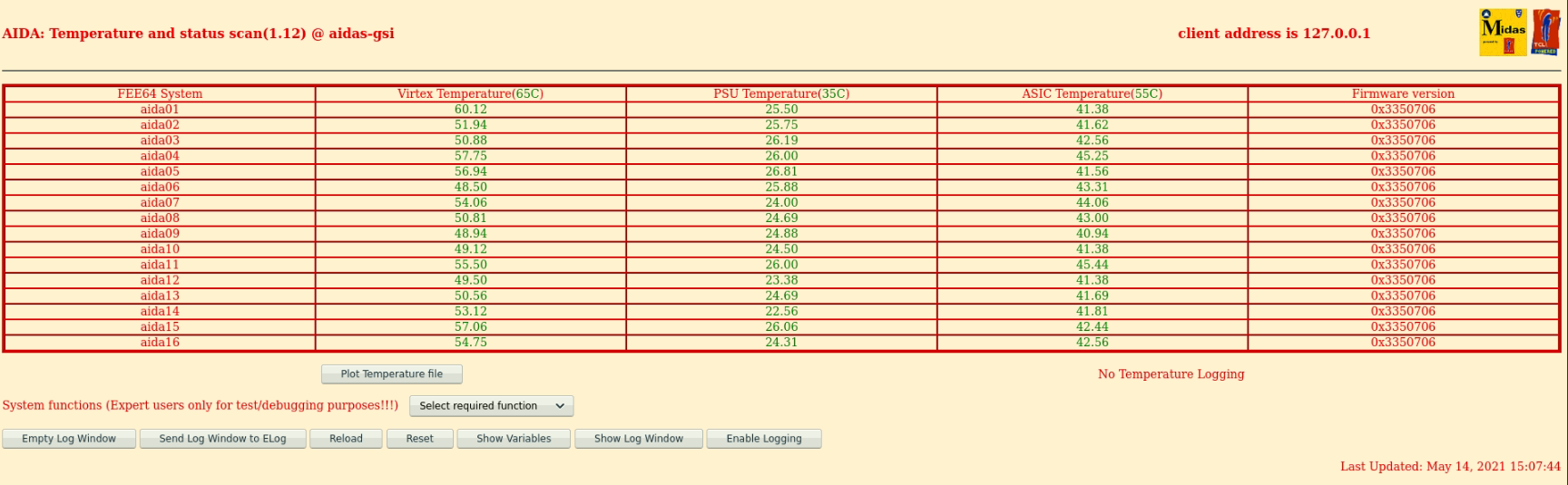

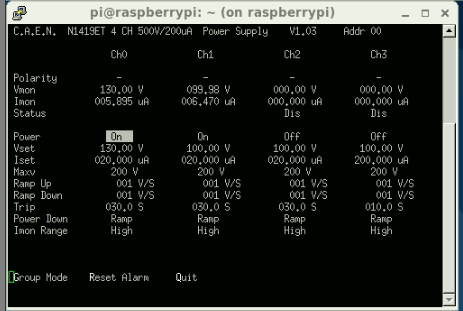

09:36 FEE64 Temperatures ok - attachment 1

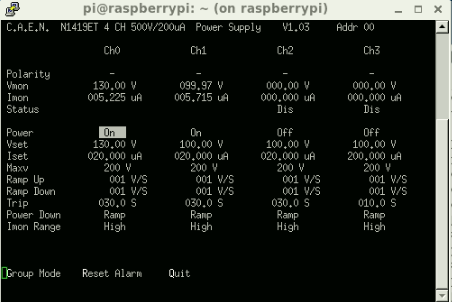

Detector bias / leakage currents ok - attachment 2

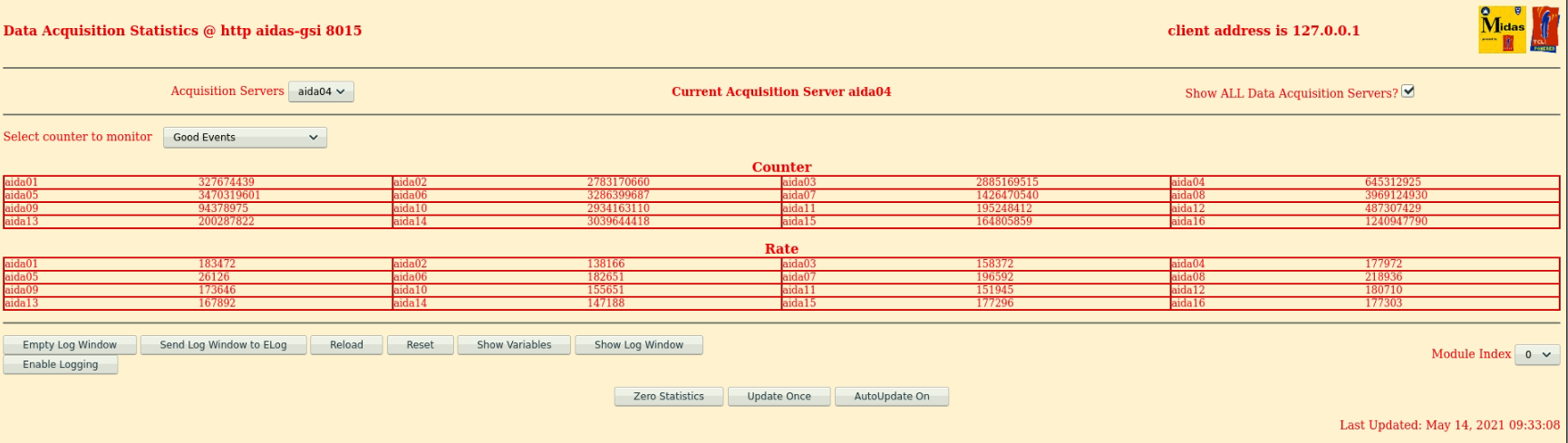

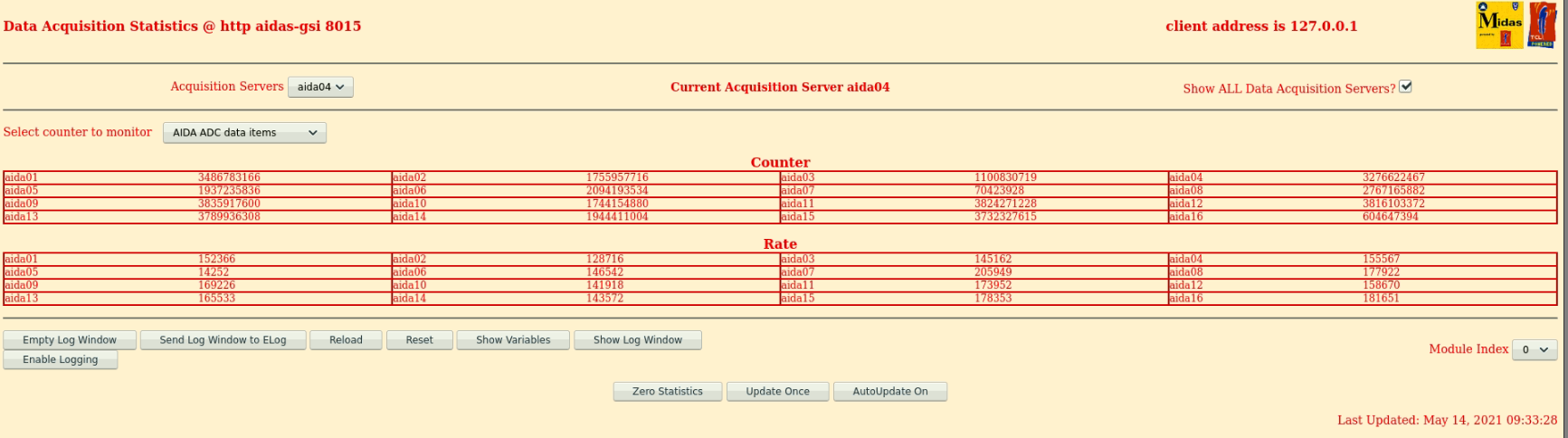

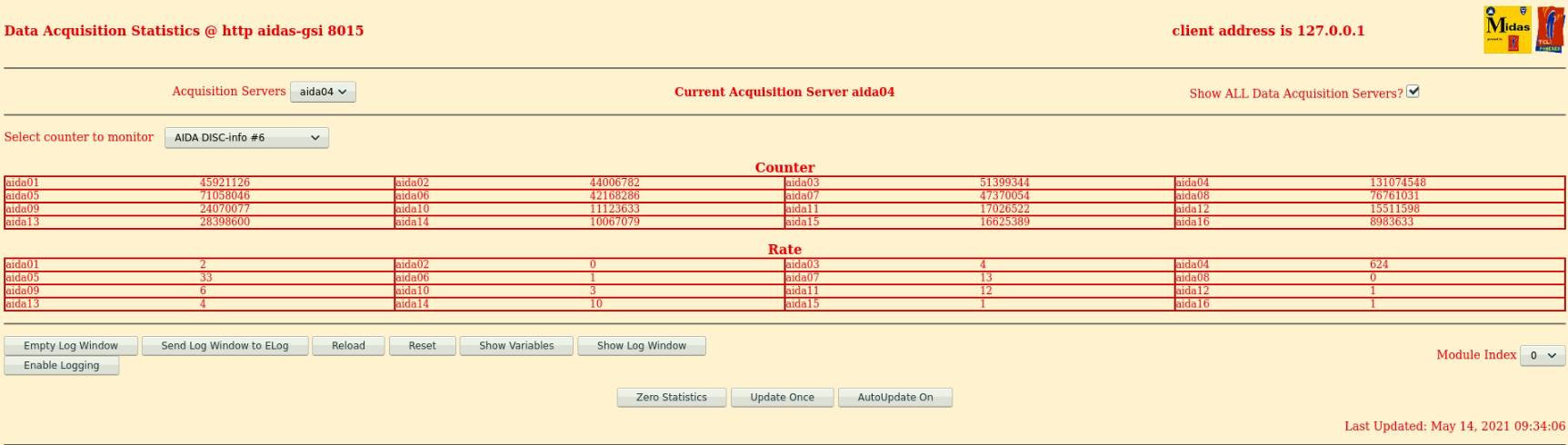

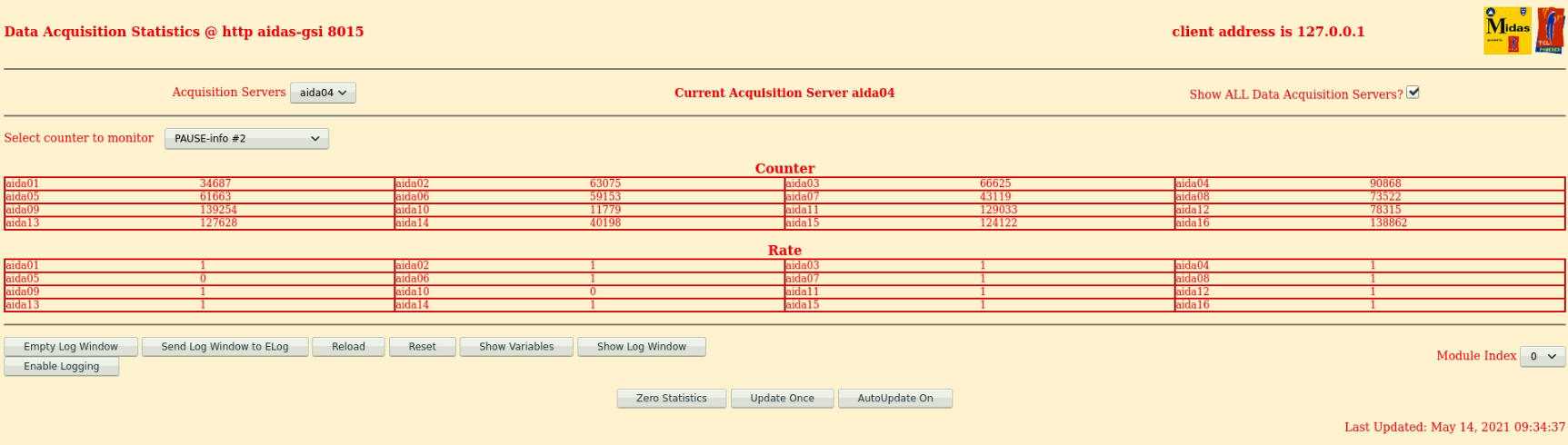

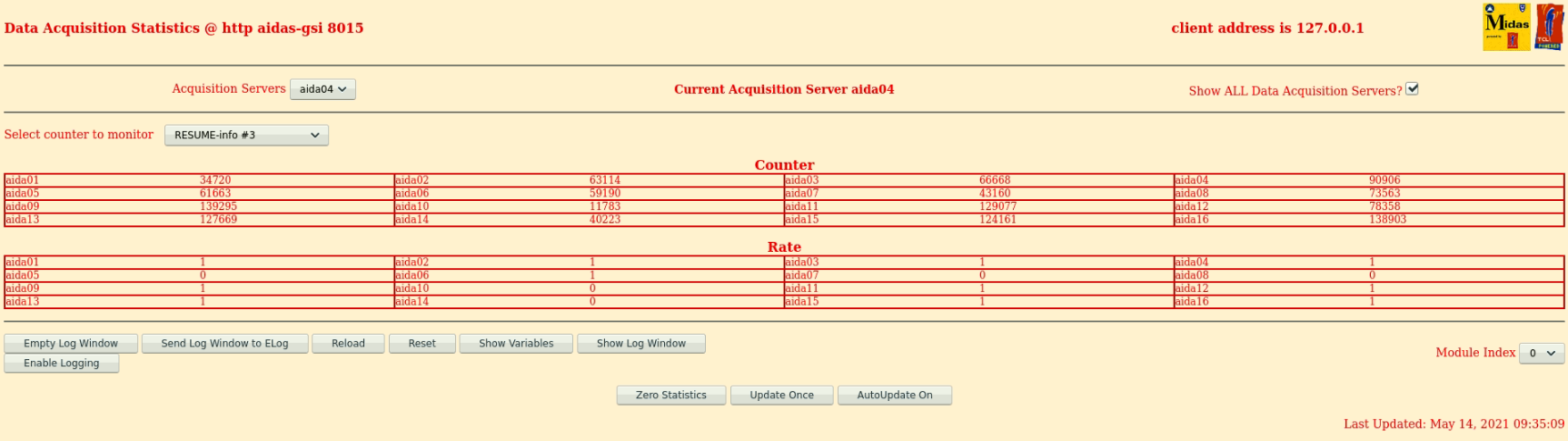

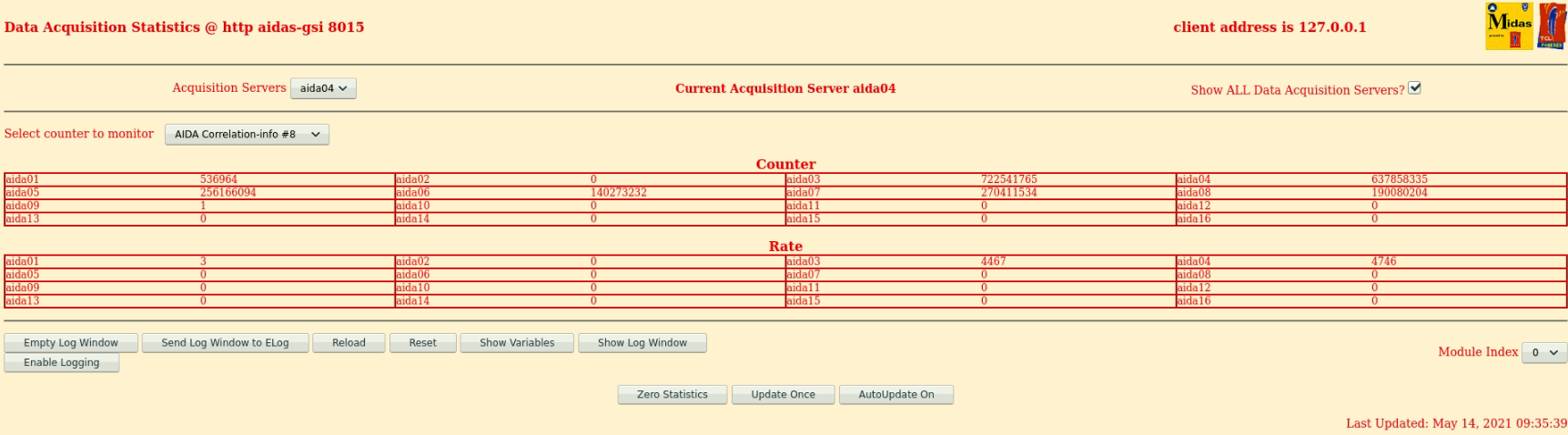

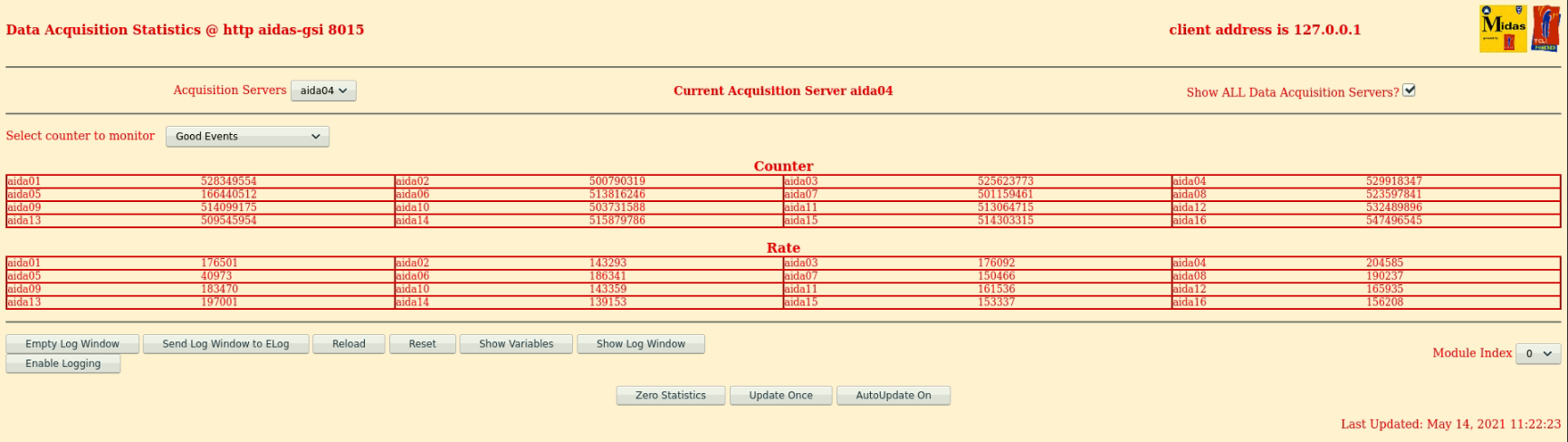

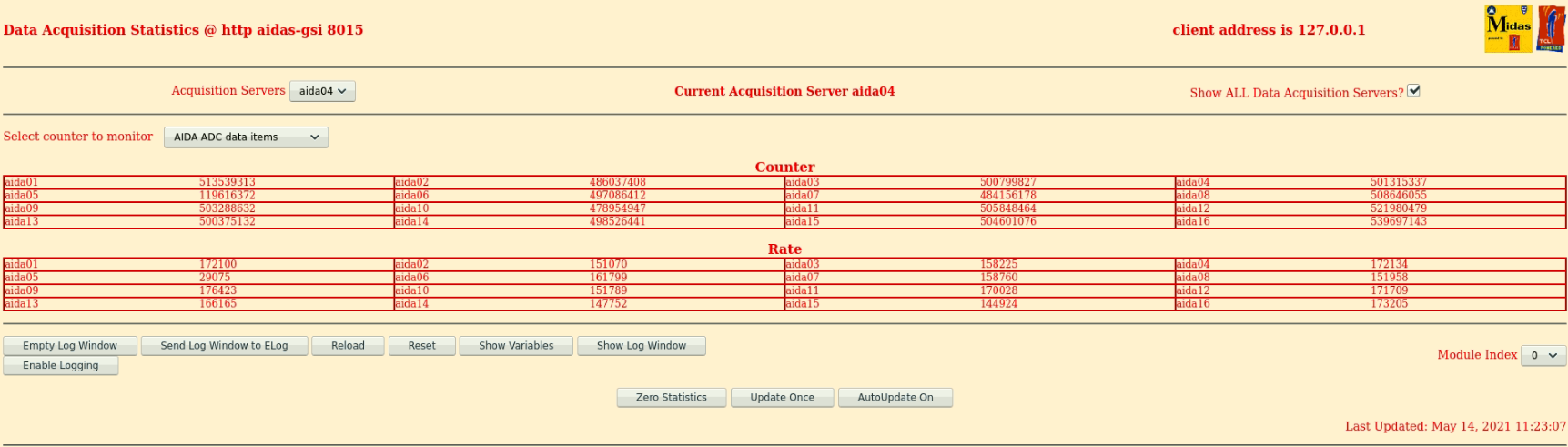

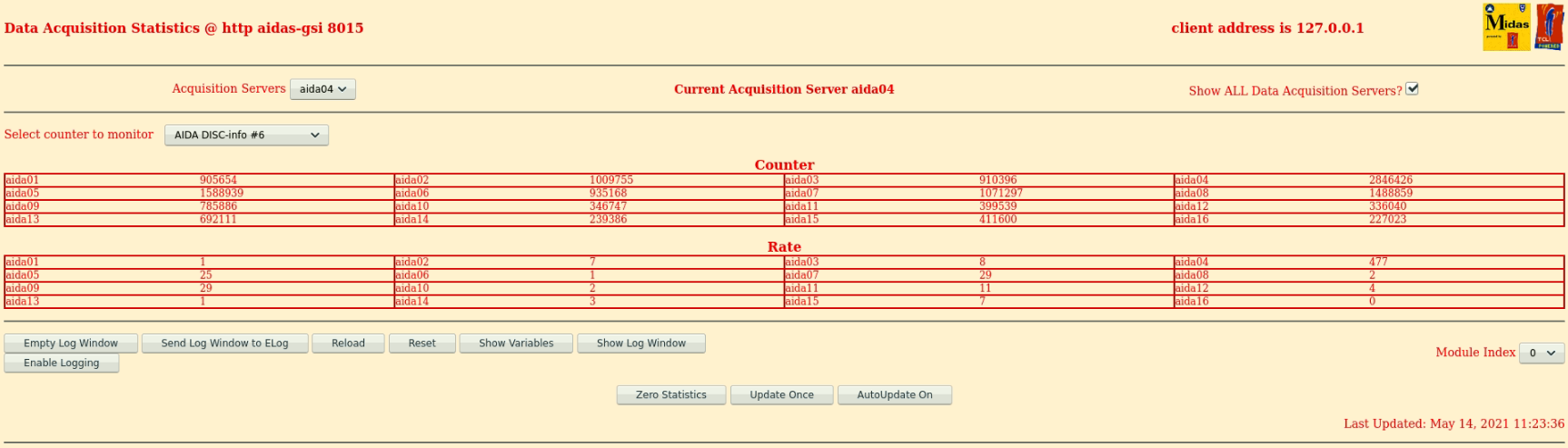

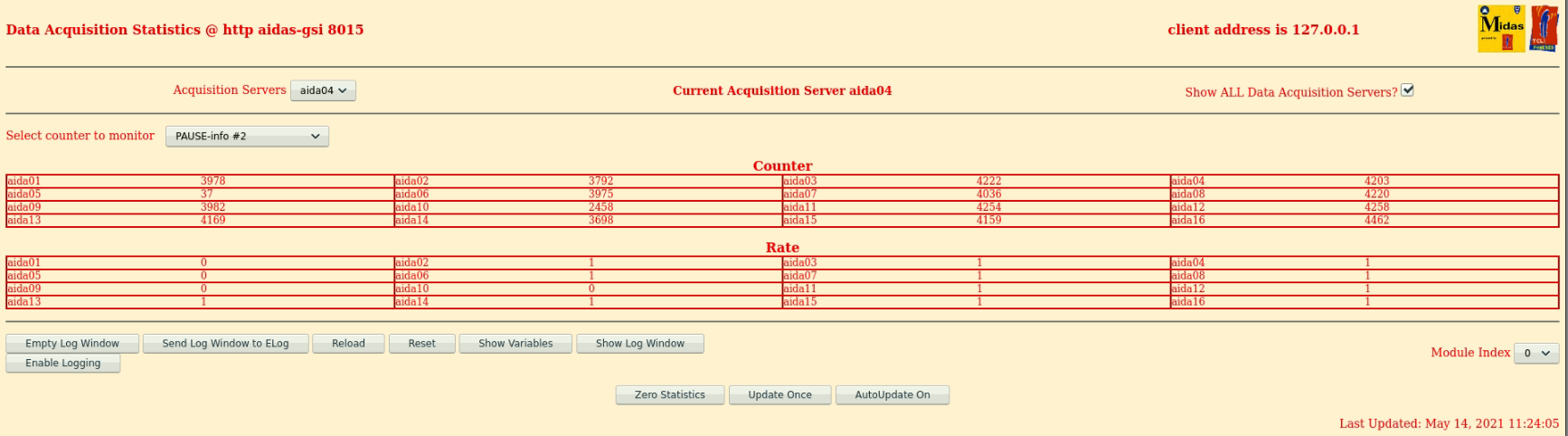

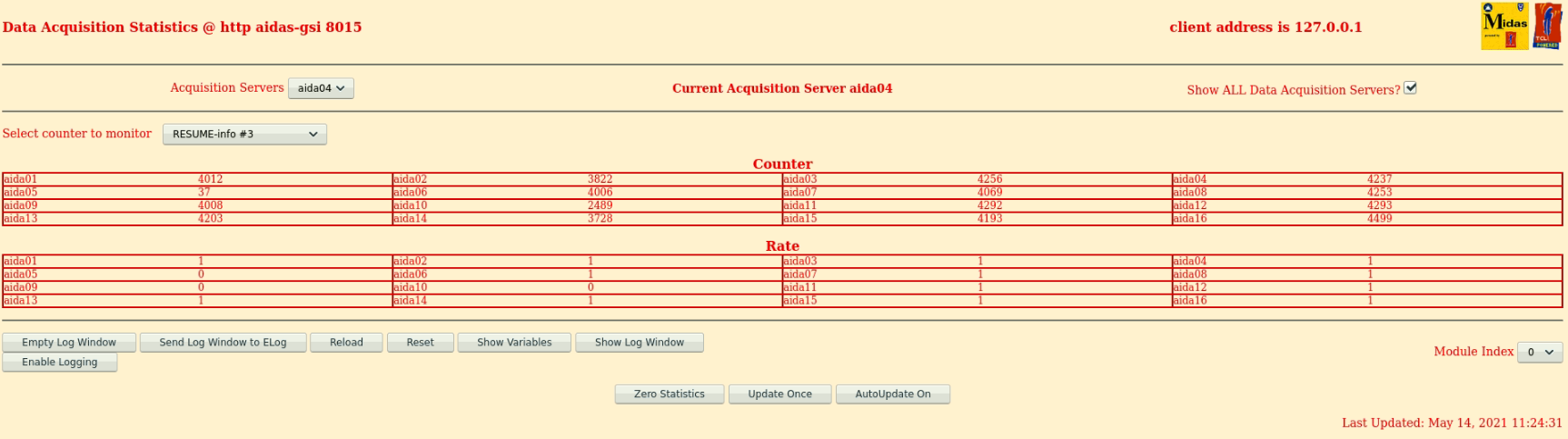

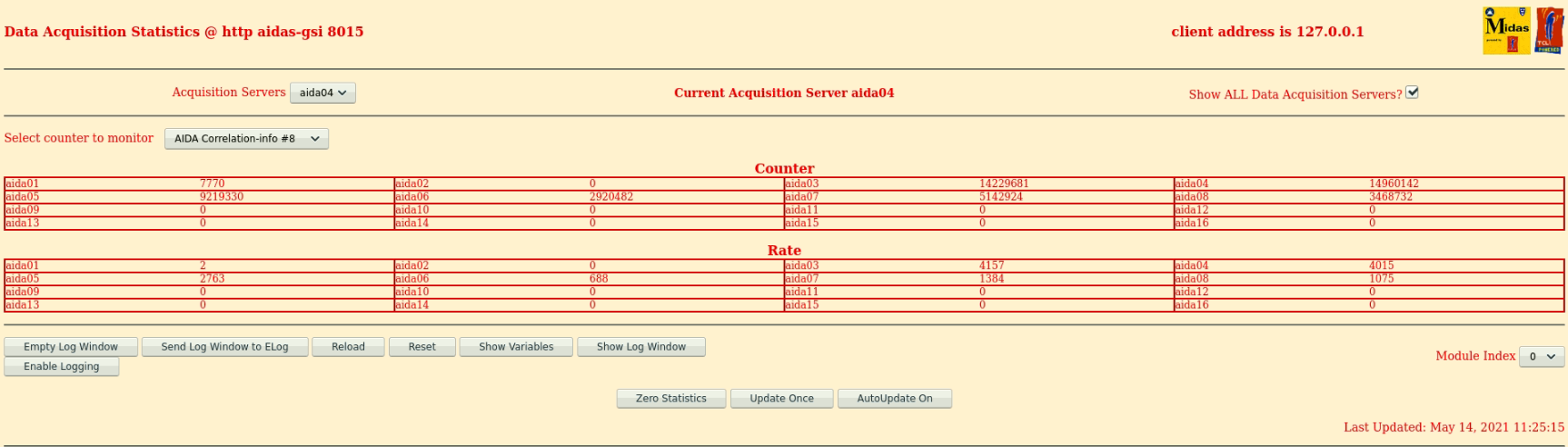

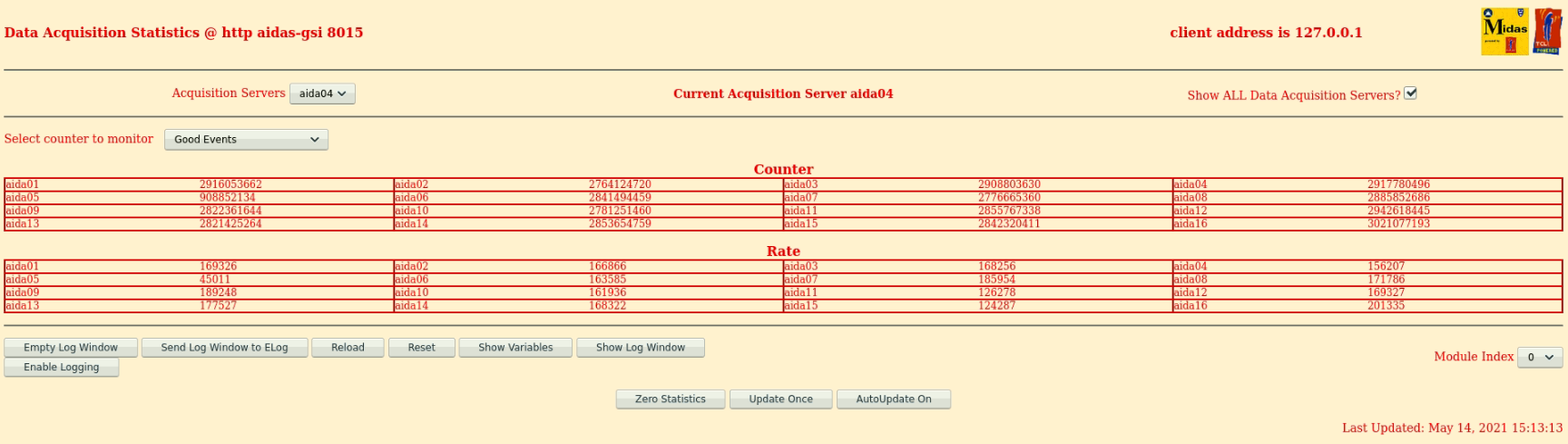

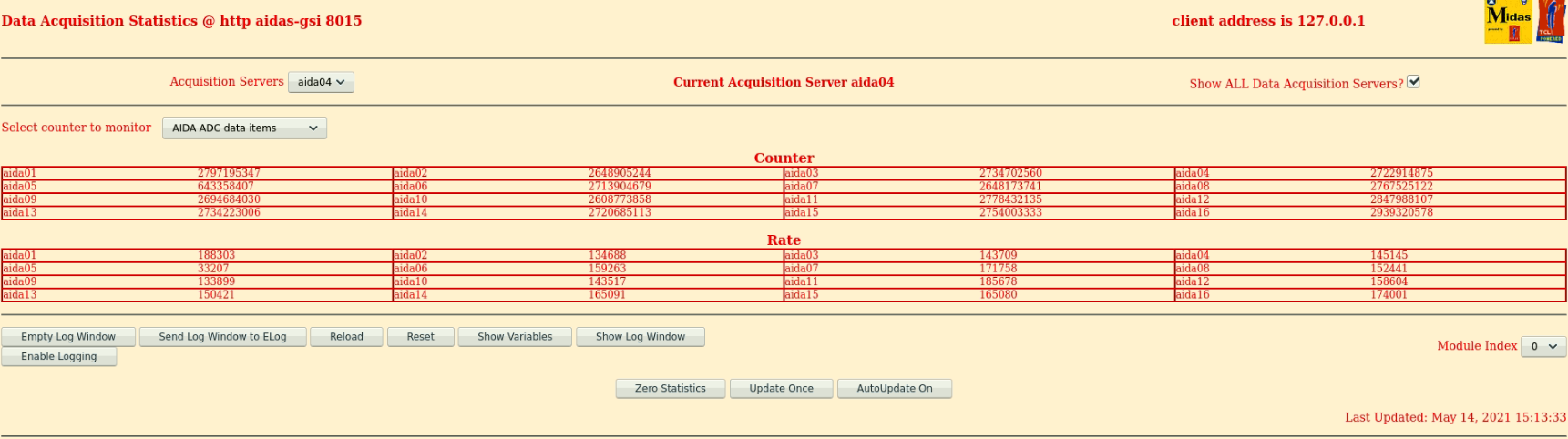

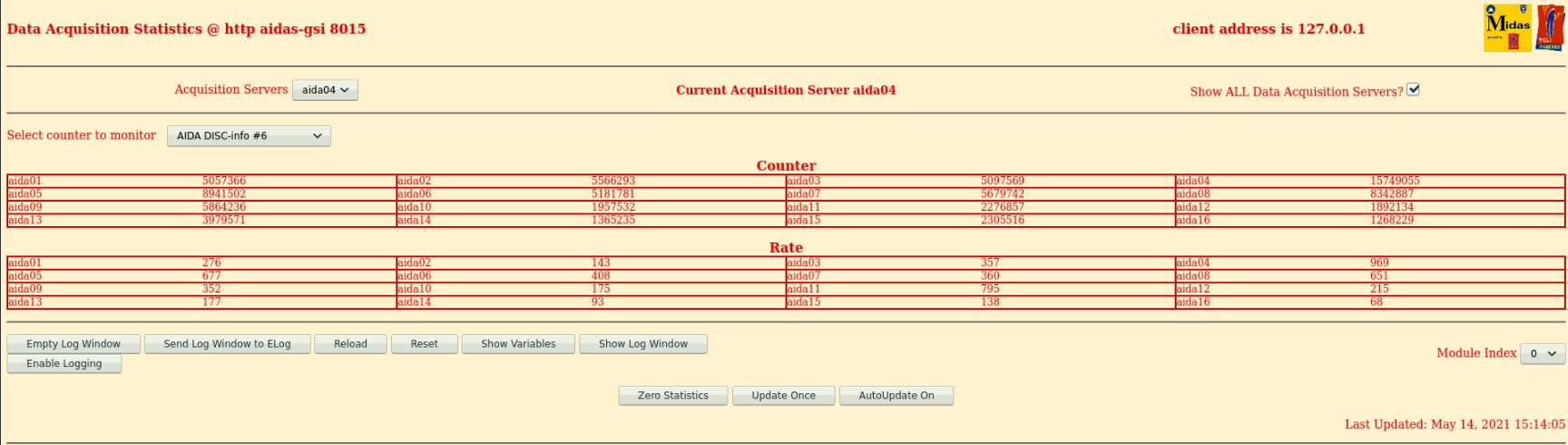

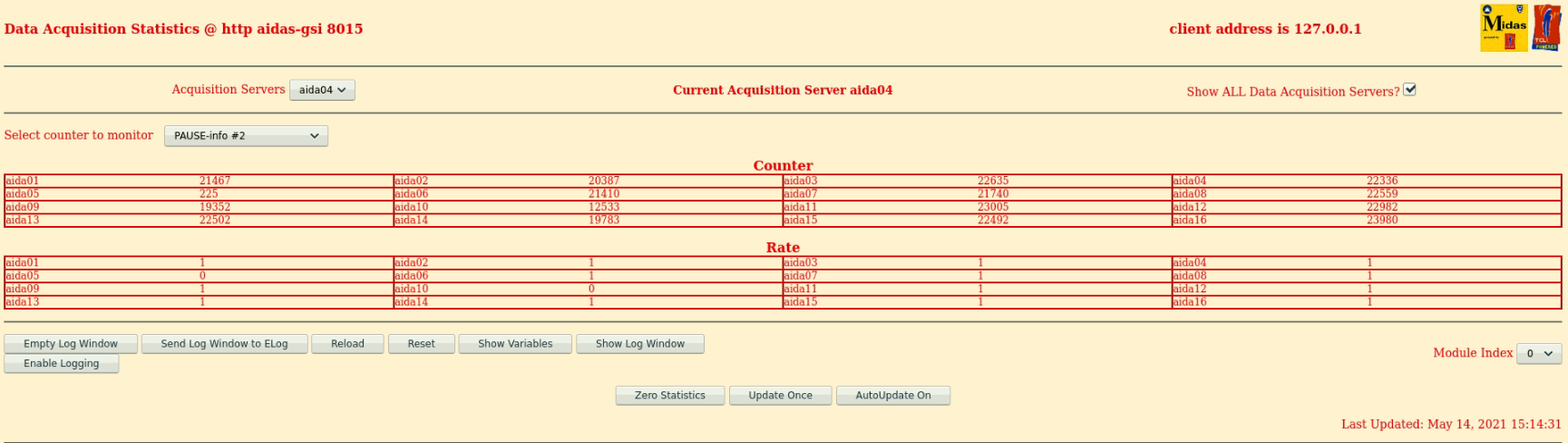

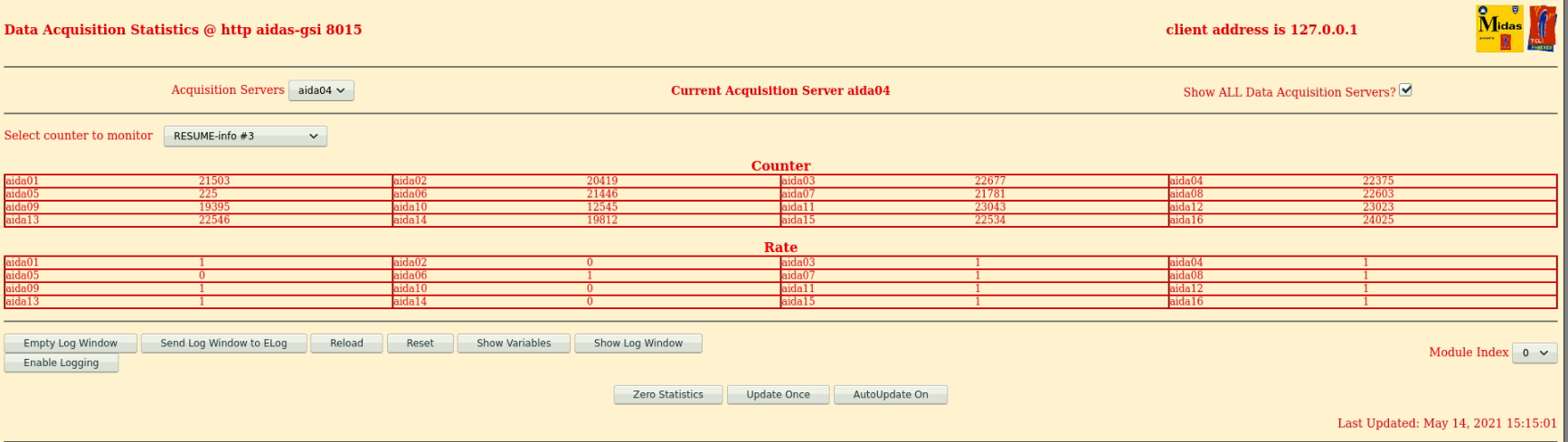

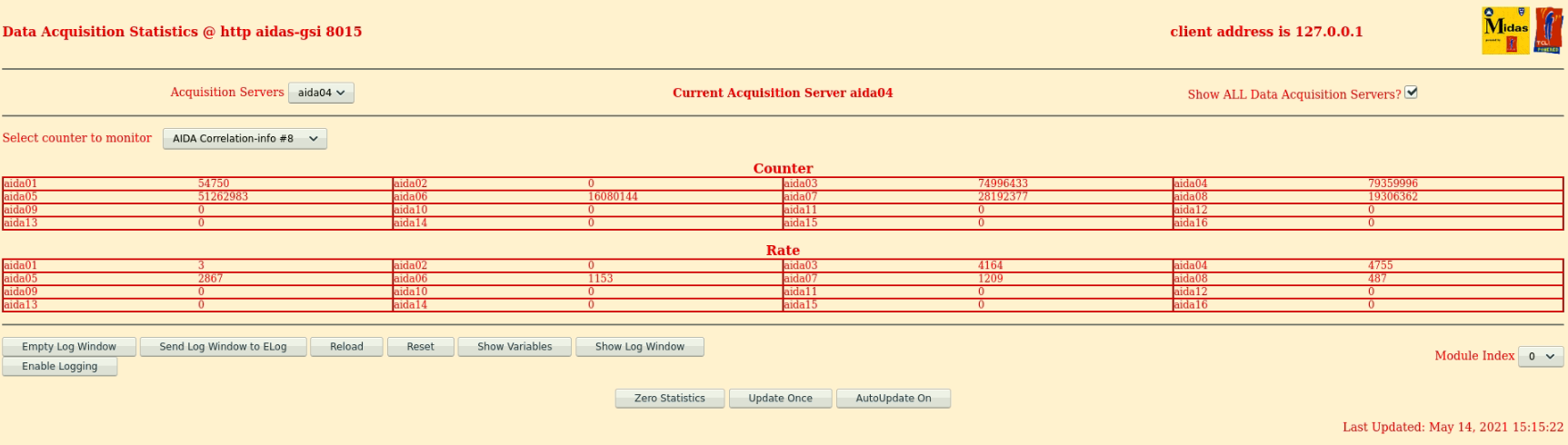

Statistics - attachments 3-8

09:50 beam is back - writing to file R4_265

09:56 FRS adjusting degrader settings (S4) - temporarily remove to check counts in scintillator vs AIDA

10:10 FRS increase degrader thickness

10.28 all histograms, stats and merger stats zero'd

10.50 all system wide checks ok *except*

Base Current Difference

aida01 fault 0xf932 : 0xf933 : 1

aida02 fault 0x62ec : 0x62ed : 1

aida03 fault 0x8679 : 0x867a : 1

aida04 fault 0xf0e4 : 0xf0e5 : 1

aida05 fault 0x9db8 : 0x9dc2 : 10

aida06 fault 0x7f18 : 0x7f19 : 1

aida07 fault 0xdd2c : 0xdd2d : 1

aida08 fault 0x1557 : 0x1558 : 1

White Rabbit error counter test result: Passed 8, Failed 8

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

Base Current Difference

aida05 fault 0x0 : 0x3 : 3

FPGA Timestamp error counter test result: Passed 15, Failed 1

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

Returned 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 3 2 2 2 2 2 2 4 3 3 6 : 36860

aida02 : 7 3 5 1 2 5 2 4 3 3 6 : 37284

aida03 : 7 5 3 1 4 4 2 3 3 3 6 : 36756

aida04 : 3 1 20 4 2 3 3 5 1 3 6 : 36052

aida05 : 19 25 26 6 2 2 3 2 2 3 6 : 35828

aida06 : 1 3 16 1 3 4 1 5 1 3 6 : 35580

aida07 : 6 4 1 2 3 3 2 3 3 3 6 : 36552

aida08 : 8 5 2 3 2 3 2 2 2 4 6 : 37064

aida09 : 9 7 1 2 2 4 2 3 3 3 6 : 36652

aida10 : 2 5 3 1 1 4 2 3 3 3 6 : 36544

aida11 : 16 4 4 2 1 2 2 3 3 3 6 : 36384

aida12 : 2 1 1 3 1 2 2 3 3 3 6 : 36288

aida13 : 0 1 1 2 0 4 3 2 3 3 6 : 36184

aida14 : 6 3 2 0 2 3 2 3 3 3 6 : 36432

aida15 : 25 8 2 1 2 3 1 2 2 4 6 : 36836

aida16 : 3 5 1 2 2 2 3 2 3 3 6 : 36100

Collecting the file size of each FEE64 Options CONTENTS file to check they are all the same

FEE : aida01 => Options file size is 1026 Last changed Thu May 13 05:49:42 CEST 2021

FEE : aida02 => Options file size is 1014 Last changed Thu Apr 29 14:43:46 CEST 2021

FEE : aida03 => Options file size is 1014 Last changed Thu Apr 29 14:43:50 CEST 2021

FEE : aida04 => Options file size is 1014 Last changed Thu Apr 29 14:43:53 CEST 2021

FEE : aida05 => Options file size is 1014 Last changed Thu Apr 29 14:43:55 CEST 2021

FEE : aida06 => Options file size is 1014 Last changed Thu Apr 29 14:43:59 CEST 2021

FEE : aida07 => Options file size is 1014 Last changed Thu Apr 29 14:44:02 CEST 2021

FEE : aida08 => Options file size is 1025 Last changed Wed May 05 12:15:54 CEST 2021

FEE : aida09 => Options file size is 1014 Last changed Thu Apr 29 14:44:08 CEST 2021

FEE : aida10 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida11 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida12 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida13 => Options file size is 1025 Last changed Fri May 07 19:40:34 CEST 2021

FEE : aida14 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida15 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida16 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

10.50 DAQ continues S496/R4_304

11:18 FEE64 Temperatures ok - attachment 9

Detector bias & leakage currents ok - attachment 10

statistics - attachments 11-16

15:00 FEE64 avg. CPU usage (%)

1 52

2 55

3 55

4 60

5 93

6 50

7 53

8 55

9 55

10 51

11 50

12 67

13 56

14 55

15 55

16 58

15:08 all system wide checks ok *except*

all FEE64 fail ADC calibration (no waveform)

WR decoder status:

Base Current Difference

aida01 fault 0xf932 : 0xf933 : 1

aida02 fault 0x62ec : 0x62ed : 1

aida03 fault 0x8679 : 0x867a : 1

aida04 fault 0xf0e4 : 0xf0e5 : 1

aida05 fault 0x9db8 : 0x9dc3 : 11

aida06 fault 0x7f18 : 0x7f19 : 1

aida07 fault 0xdd2c : 0xdd2d : 1

aida08 fault 0x1557 : 0x1558 : 1

White Rabbit error counter test result: Passed 8, Failed 8

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

FPGA errors:

Base Current Difference

aida05 fault 0x0 : 0x3 : 3

FPGA Timestamp error counter test result: Passed 15, Failed 1

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

15:10 Temperatures ok - attachment 17

Detector bias / leakage current ok - attachment 18

Statistics - attachments 18 -24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|