| ID |

Date |

Author |

Subject |

|

552

|

Wed Mar 27 14:22:35 2024 |

JB, NH | Installing FEE64s of DSSSD2 |

Mounted on frame:

DSSD 1 (Upstream) : 3208-2/3208-5/3208-8

DSSD 2 (Downstream): 3208-3/3208-21/3208-22

Current mapping has been redone for better management.

| AIDA - FEE Mapping |

| DSSSD 1 |

DSSSD2 |

| FEE |

MAC |

FEE |

MAC |

| aida01 |

41:ba:8a |

aida06 |

41:05:15 |

| aida02 |

41:f6:b7 |

aida07 |

41:f6:5a |

| aida03 |

41:d8:21 |

aida08 |

41:d7:cd |

| aida04 |

41:a0:71 |

aida10 |

41:d0:0E |

| aida05 |

41:cf:ac |

aida13 |

41:d8:2b |

| aida09 |

41:ee:10 |

aida14 |

42:0d:15 |

| aida15 |

41:b4:0c |

aida11 |

41:EE:0f |

| aida12 |

41:ba:89 |

aida16 |

41:f6:ed |

Going to try optimising noise now.

DHCP updated

new ASIC settings: 2024Mar27-11.25.32 - 16 FEEs (2,4,6,8 n+n, rest p+n)

New layouts: /home/npg/LayOut/GSI_Triple_S100

New layout.txt

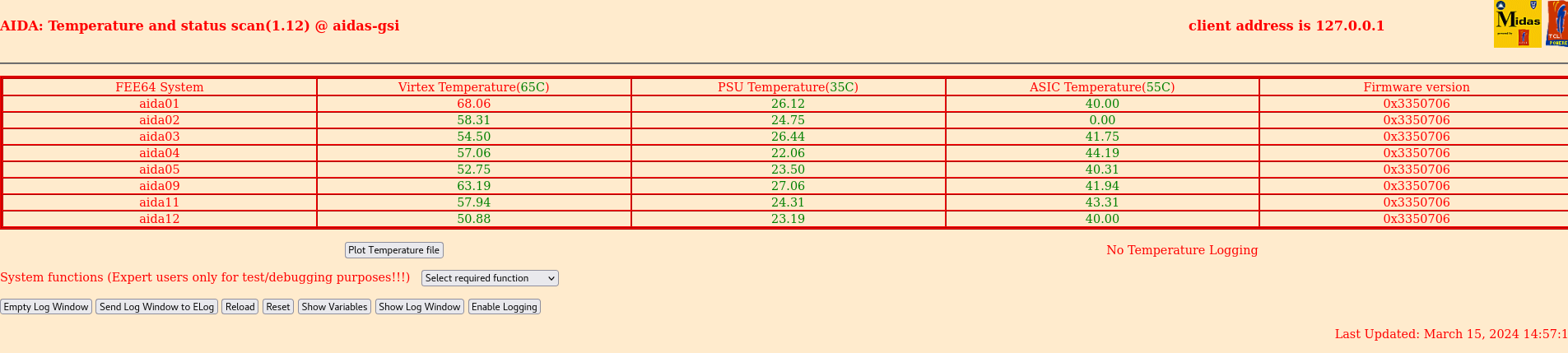

Firmware of aida11 updated from 0xea40704 to 0x3350706

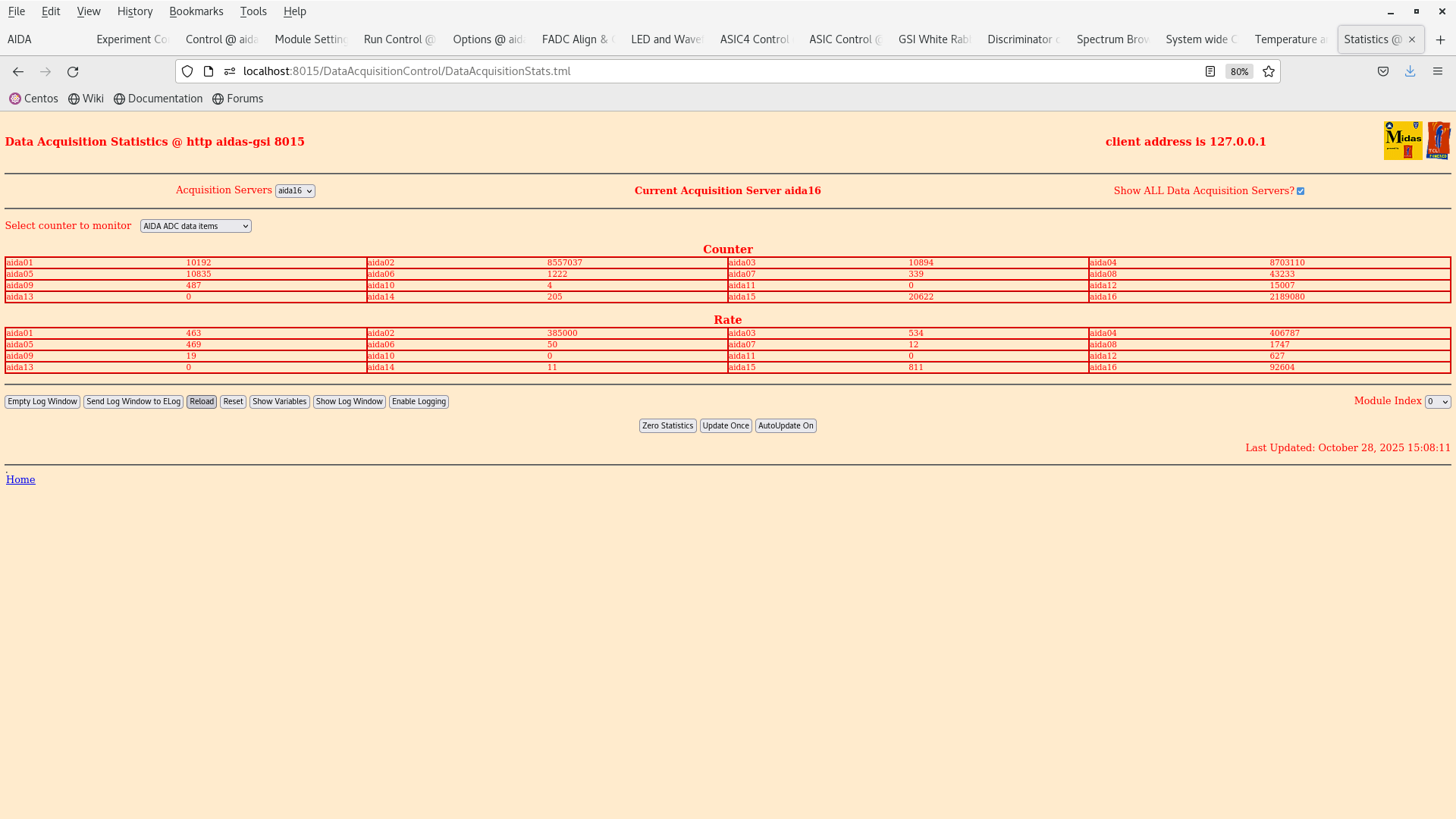

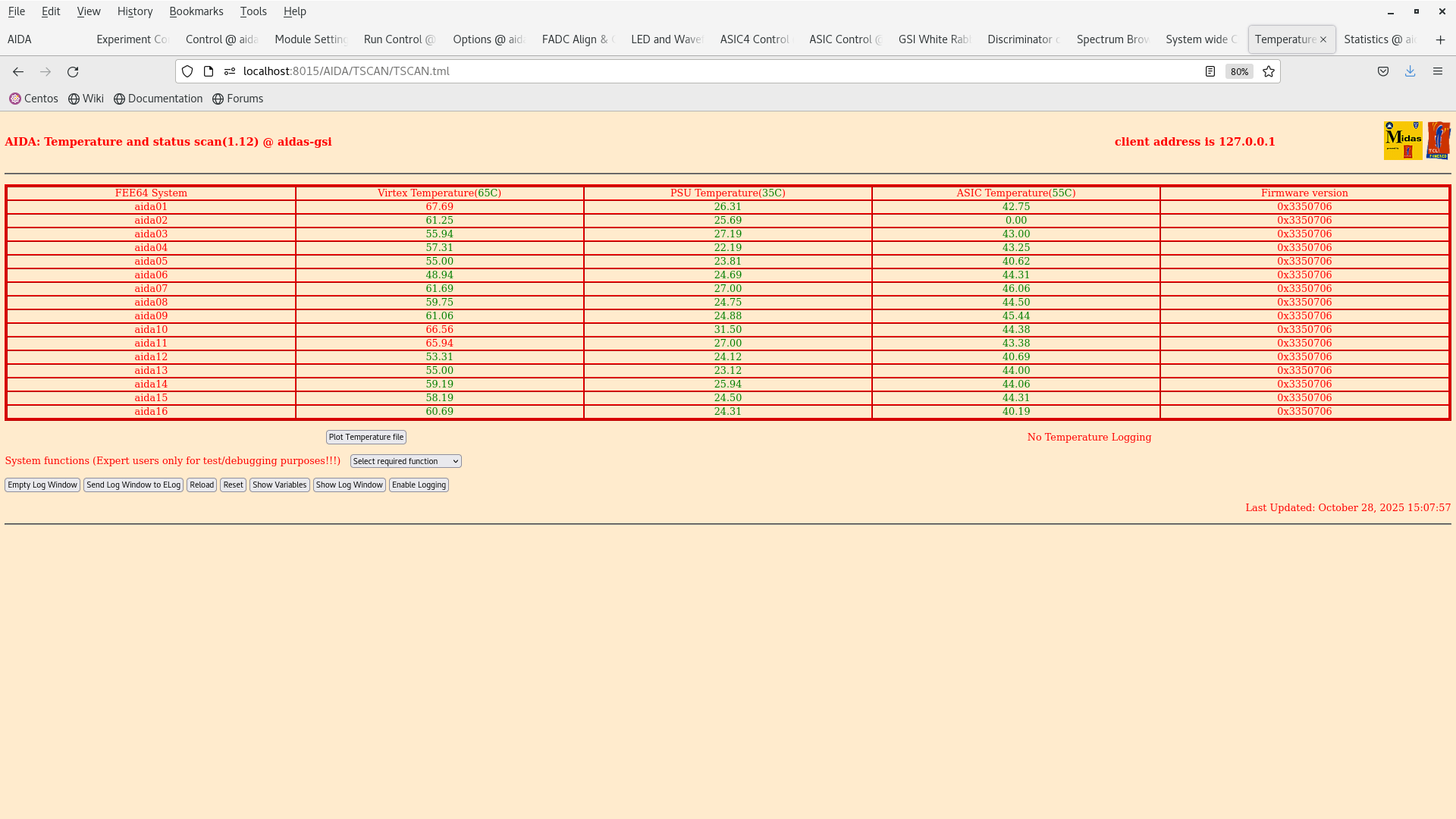

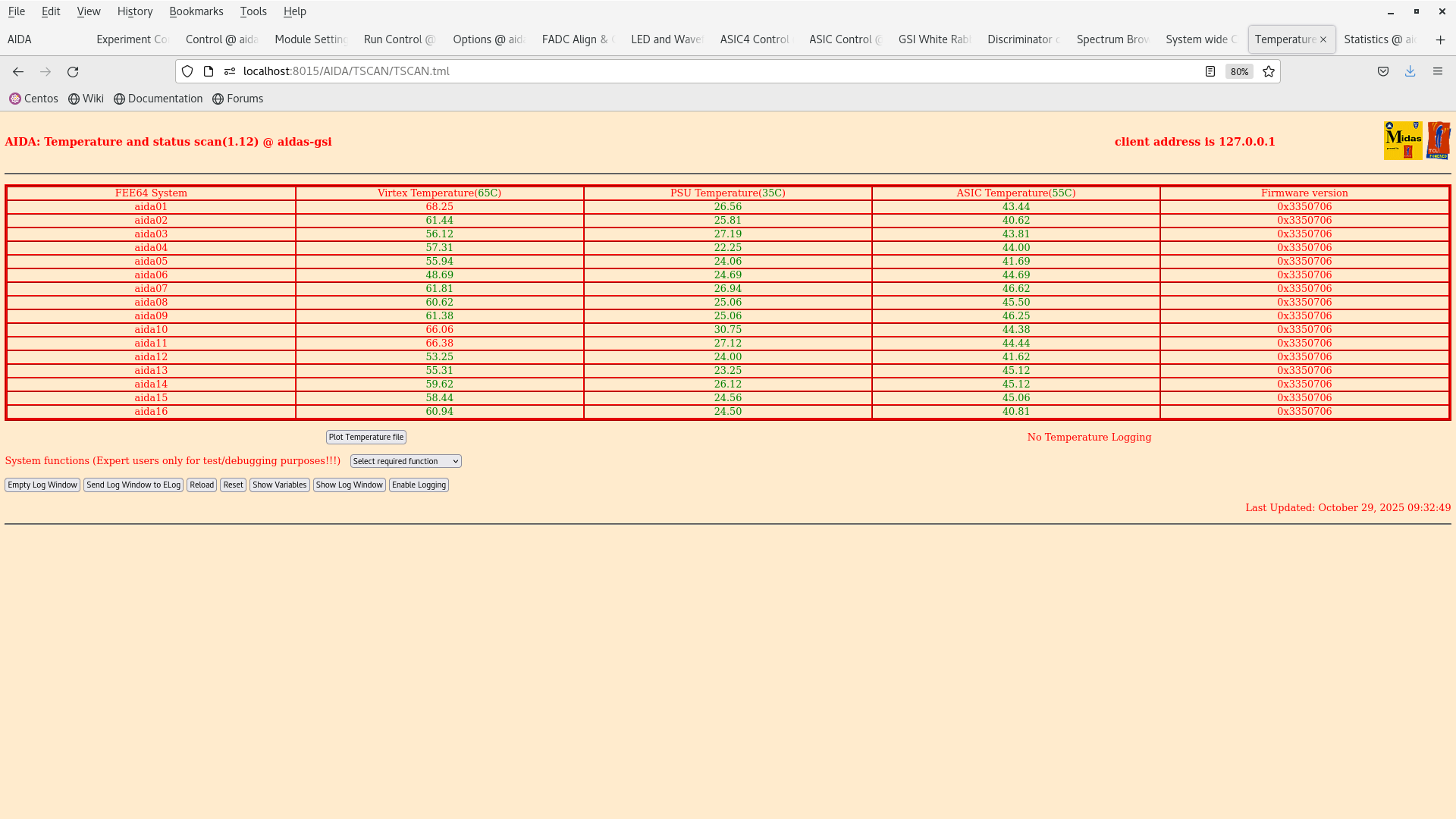

Temps GOOD fig 5

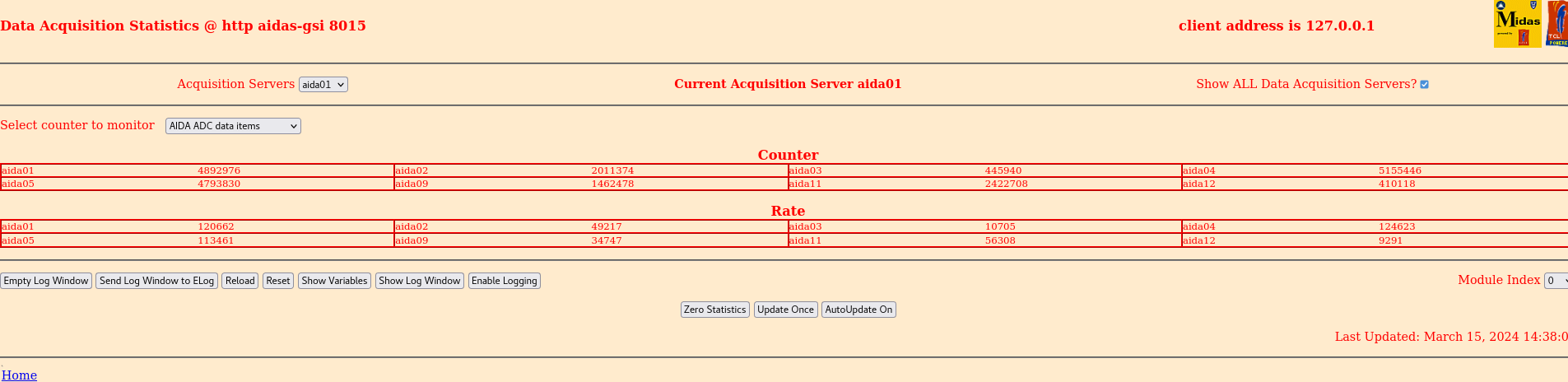

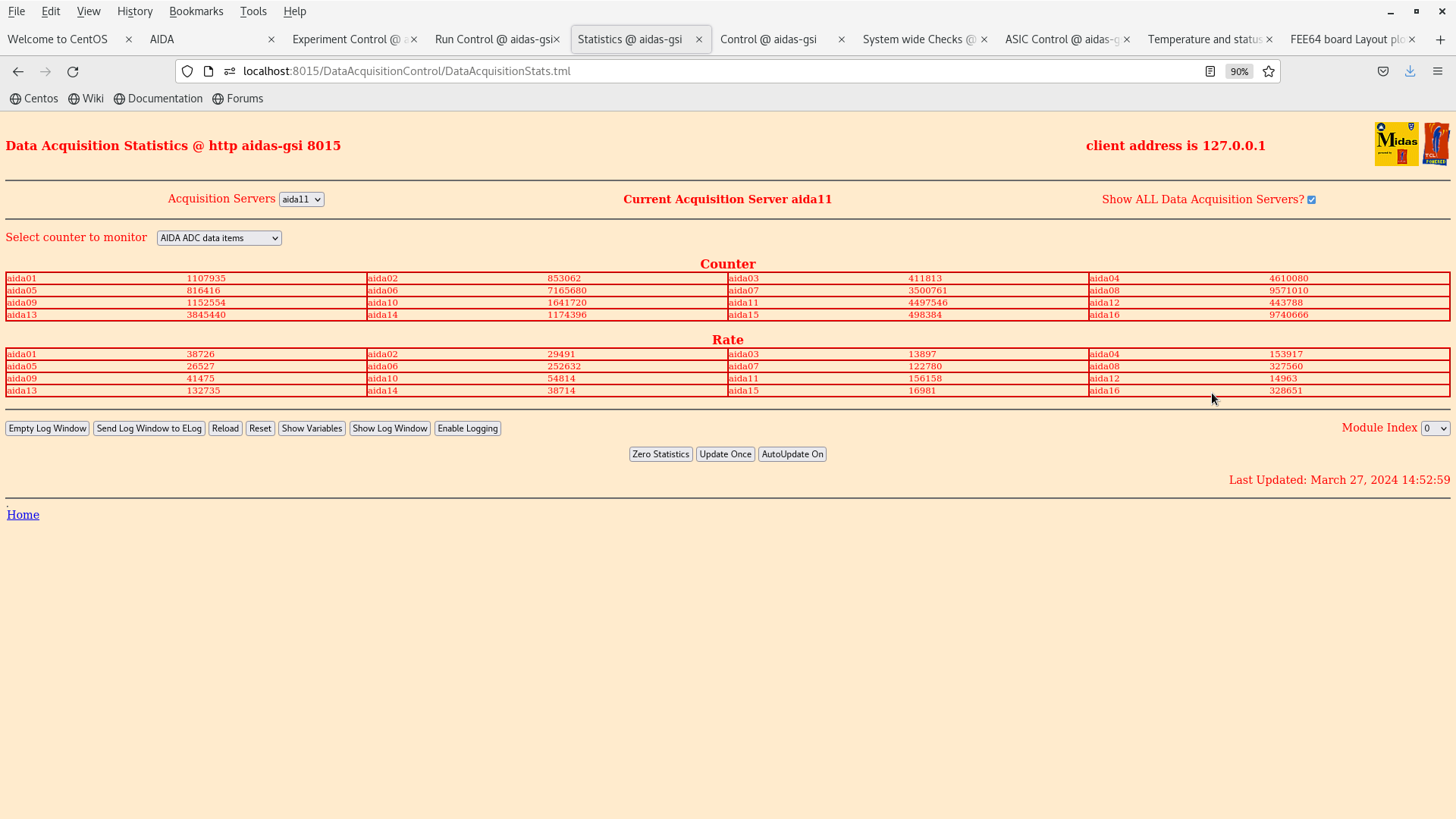

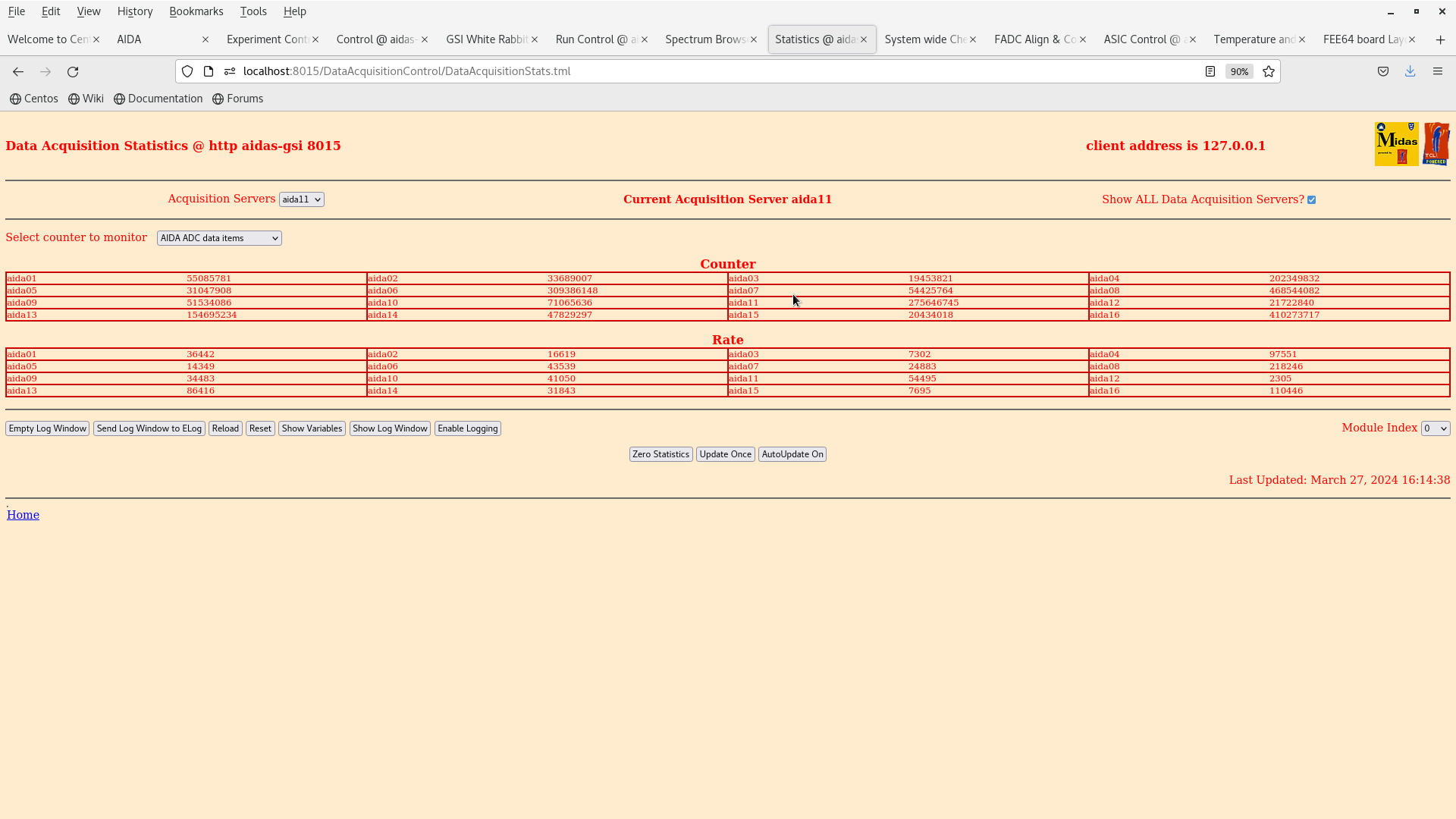

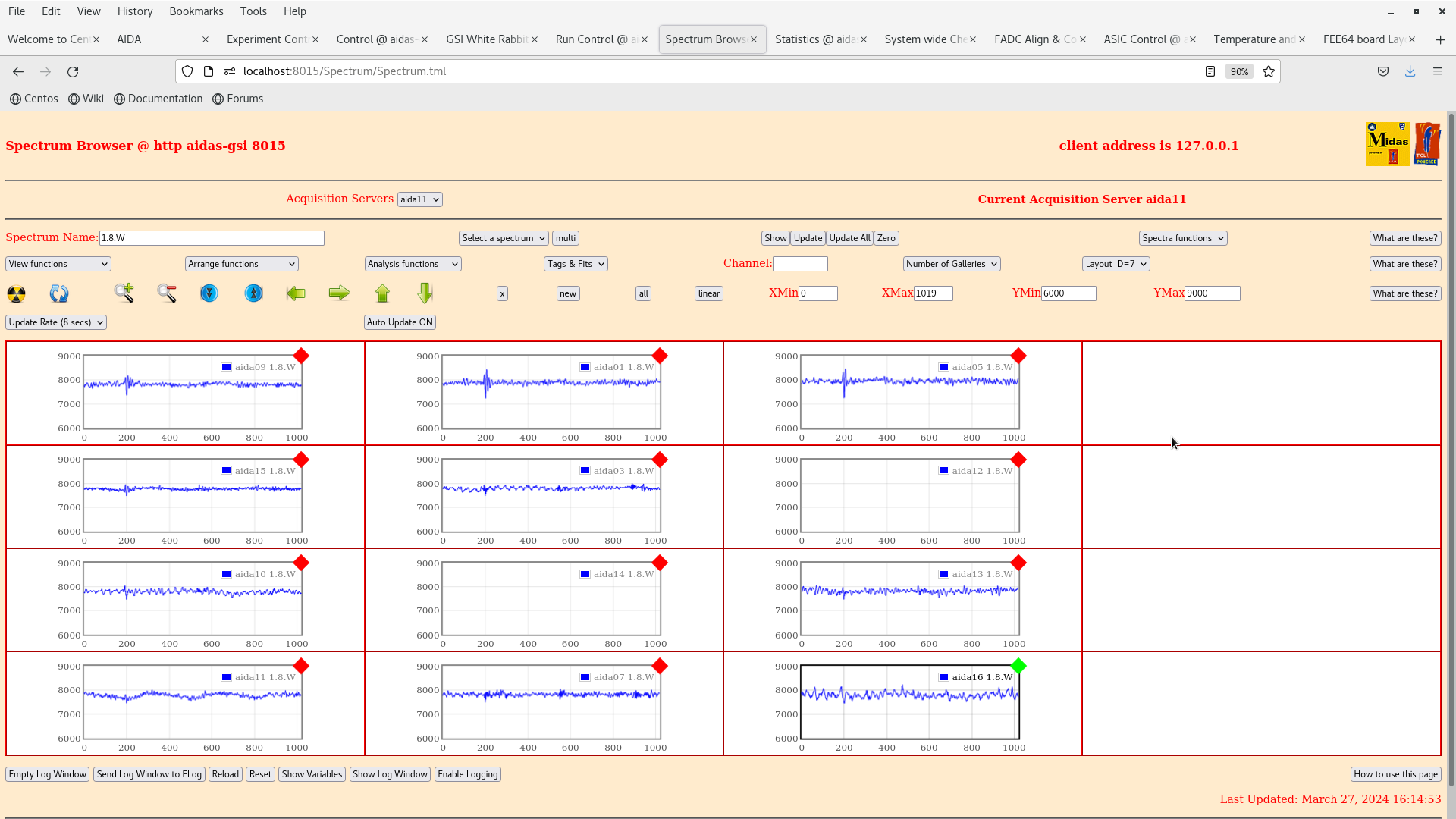

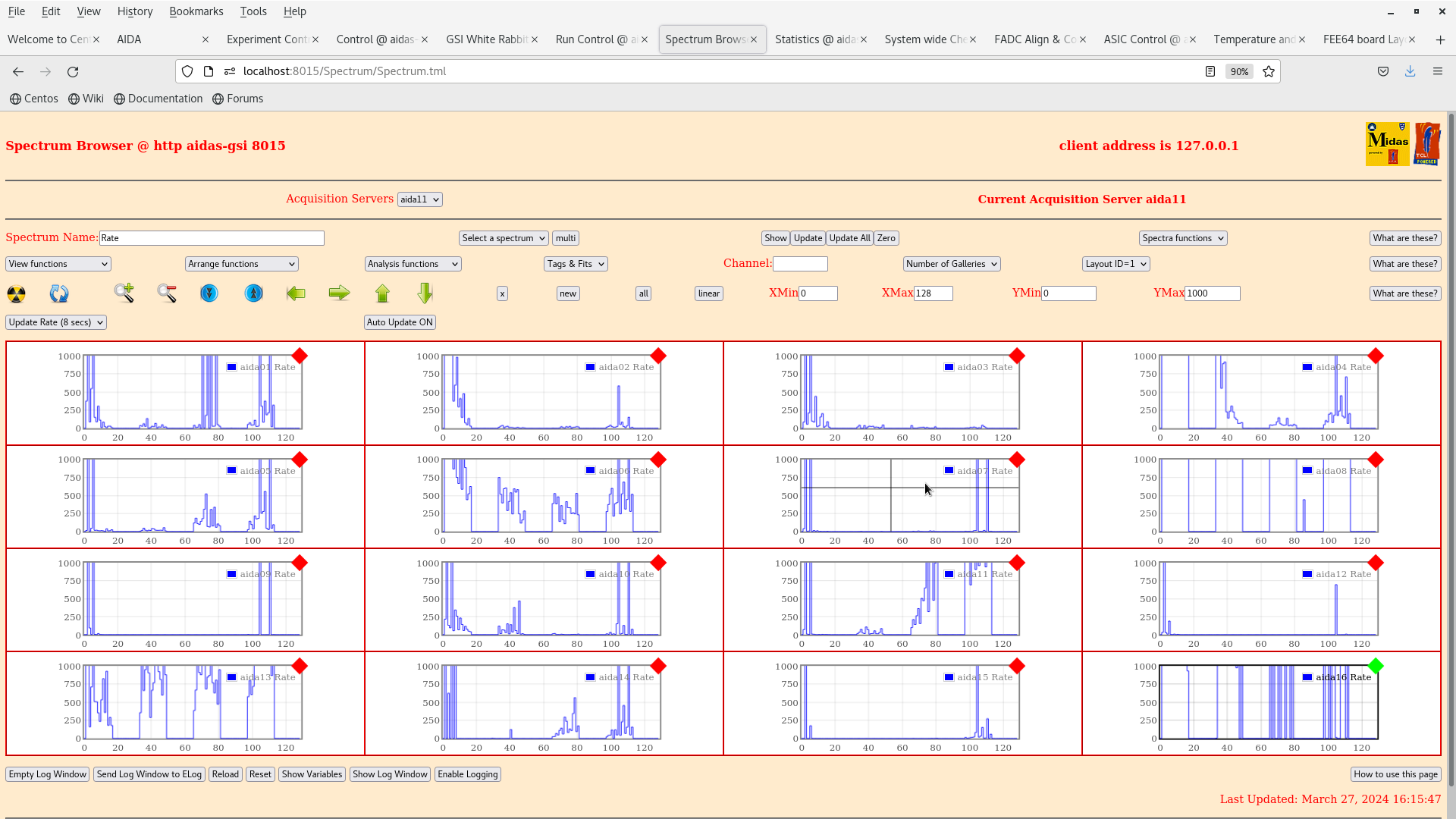

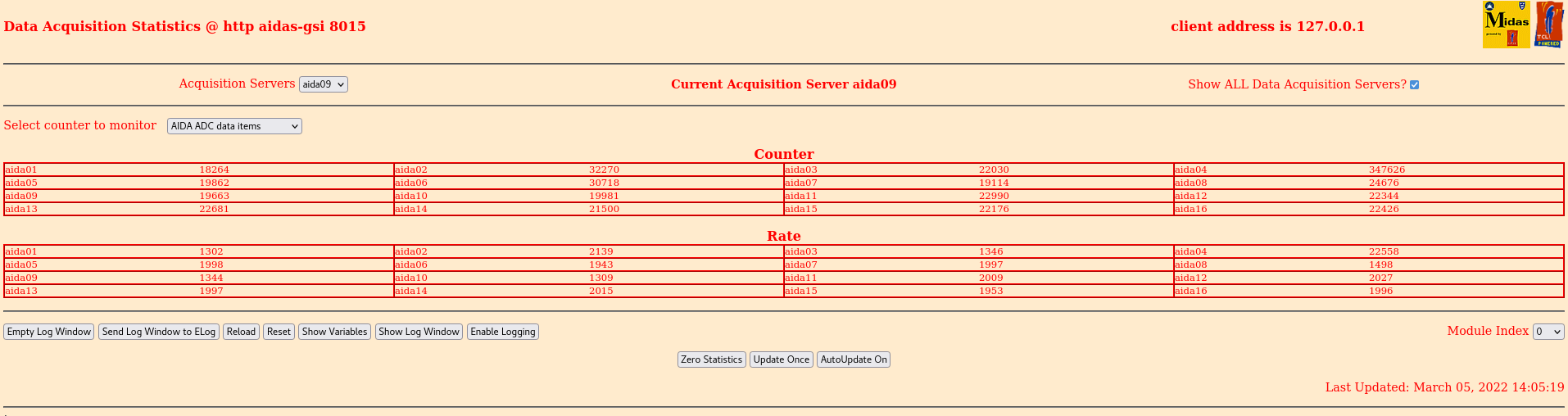

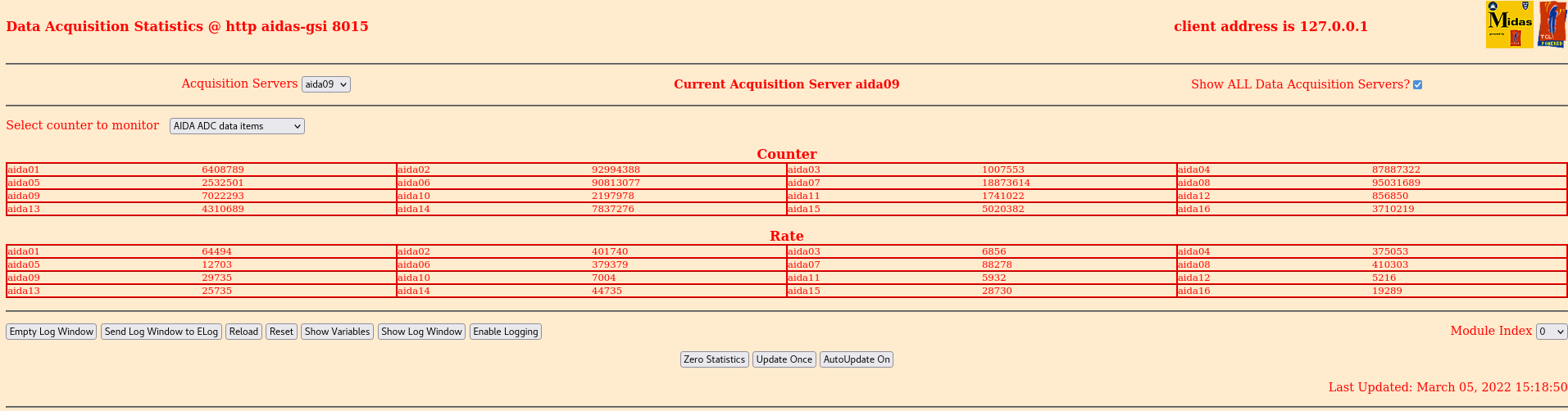

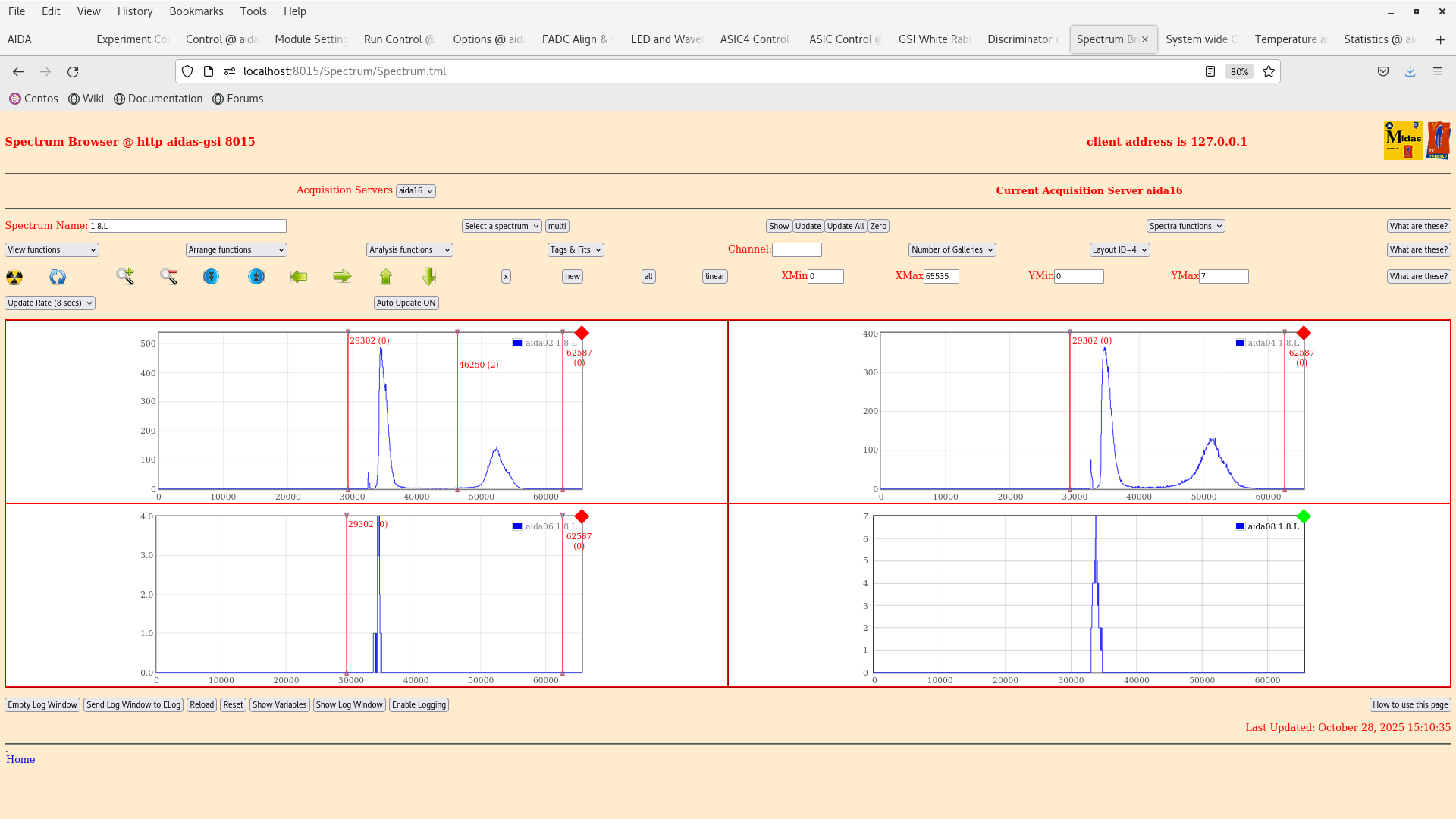

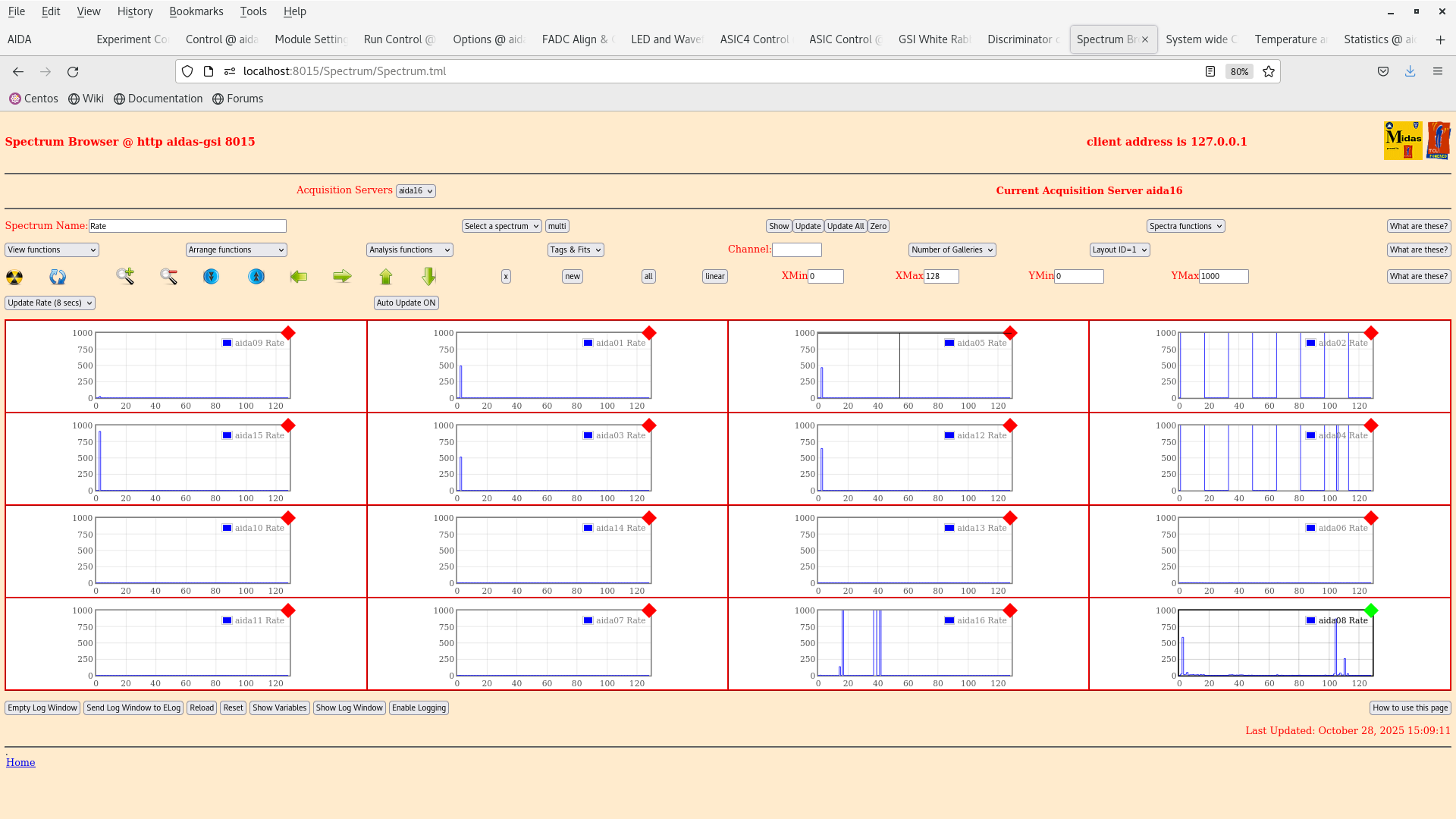

Rates fig 6, 7

Check adapter alignment aida14 and aida16

bPlas left/right cables are not insulated and shorting to the snout

Logs on nnpi1 archived and deleted, start again

All 16 FEEs are showing USB logging connectivity and can be monitored with Pi_Monitor

From waveforms aida08 and aida16 are quite unhappy. The rest don't seem too bad. DSSSD 1 is much quieter than it was before!

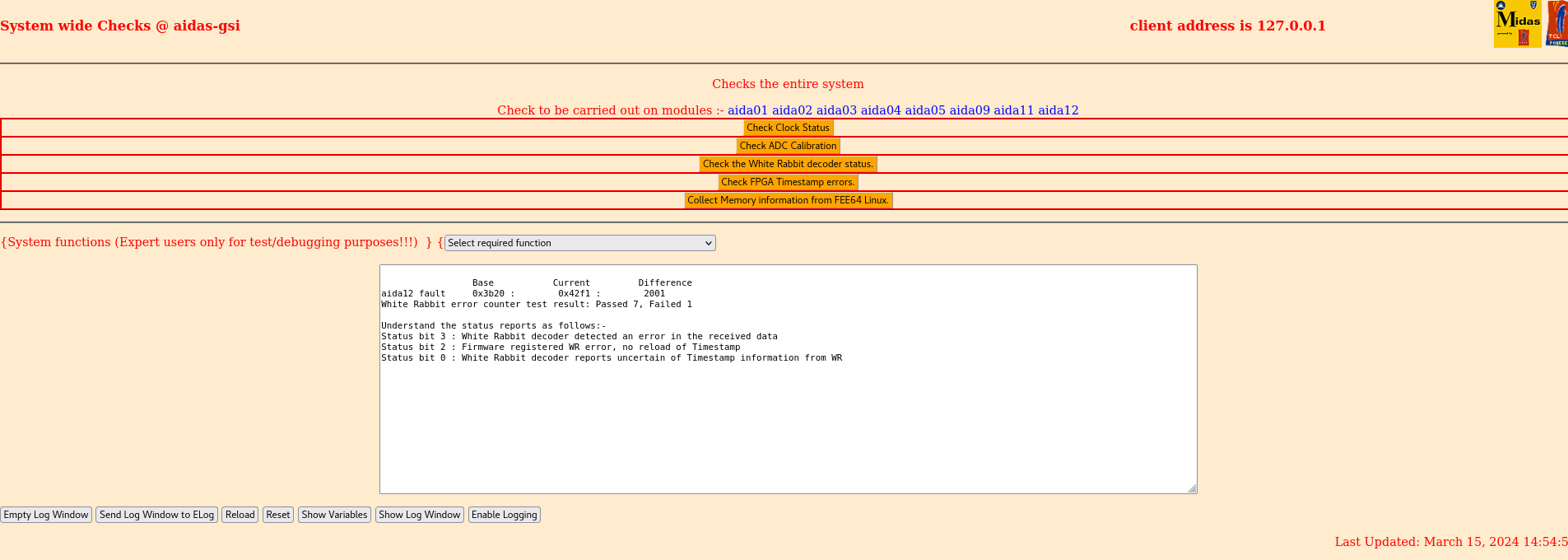

White Rabbit Analysis: aida02 has lots of WR error counter, HDMI reseat needed

aida09-12 have no WR timestamp, the cable to the MACB is bad or the MACB is bad.

Not needed to fix right now (for noise testing)

Turn off bPlas

We see the noise drop a lot |

| Attachment 1: Screenshot_2024-03-15_at_14-41-48_Spectrum_Browser_aidas-gsi.png

|

|

| Attachment 2: Screenshot_2024-03-15_at_14-44-59_Statistics_aidas-gsi.png

|

|

| Attachment 3: Screenshot_2024-03-15_at_14-55-07_System_wide_Checks_aidas-gsi.png

|

|

| Attachment 4: Screenshot_2024-03-15_at_14-57-19_Temperature_and_status_scan_aidas-gsi.png

|

|

| Attachment 5: Screenshot_from_2024-03-27_14-51-12.png

|

|

| Attachment 6: Screenshot_from_2024-03-27_14-53-05.png

|

|

| Attachment 7: Screenshot_from_2024-03-27_14-53-56.png

|

|

| Attachment 8: Screenshot_from_2024-03-27_15-31-10.png

|

|

| Attachment 9: Screenshot_from_2024-03-27_15-35-38.png

|

|

| Attachment 10: Screenshot_from_2024-03-27_15-36-13.png

|

|

| Attachment 11: Screenshot_from_2024-03-27_16-14-44.png

|

|

| Attachment 12: Screenshot_from_2024-03-27_16-15-00.png

|

|

| Attachment 13: Screenshot_from_2024-03-27_16-15-27.png

|

|

| Attachment 14: Screenshot_from_2024-03-27_16-15-56.png

|

|

|

553

|

Thu Mar 28 09:18:53 2024 |

TD | Installing FEE64s of DSSSD2 |

Some additional checks

- check 'top hat' electrical isolators are correctly installed at each of the 4x mounting points of the AIDA snout assembly

- check snout is electrically isolated with respect to AIDA support assembly/stand, bPlas PCBs/cabling/ground/drain wires and BB7

- check LK1 installed aida02 or aida04 *and* aida06 or aida08 ( I assume these are the n+n Ohmic FEE64s? )

- check LK3 installed bottom, middle p+n junction FEE64s ( i.e. LK3 installed on 2 of 16 FEE64 adaptor PCBs )

- check FEE64 power cables are paired correctly, e.g. aida02 & aida04, aida01 & aida03 etc. Remember that the numbering of the power cables at the FEE64 PSUs may no longer correspond to which FEE64 is actually connected to that cable

- check test and test - cable daisy chains are removed

- check ground cabling attachment to Lemo 00.250 connectors is tight - they have tendency to loosen with handling

| Quote: |

|

Mounted on frame:

DSSD 1 (Upstream) : 3208-2/3208-5/3208-8

DSSD 2 (Downstream): 3208-3/3208-21/3208-22

Current mapping has been redone for better management.

| AIDA - FEE Mapping |

| DSSSD 1 |

DSSSD2 |

| FEE |

MAC |

FEE |

MAC |

| aida01 |

41:ba:8a |

aida06 |

41:05:15 |

| aida02 |

41:f6:b7 |

aida07 |

41:f6:5a |

| aida03 |

41:d8:21 |

aida08 |

41:d7:cd |

| aida04 |

41:a0:71 |

aida10 |

41:d0:0E |

| aida05 |

41:cf:ac |

aida13 |

41:d8:2b |

| aida09 |

41:ee:10 |

aida14 |

42:0d:15 |

| aida15 |

41:b4:0c |

aida11 |

41:EE:0f |

| aida12 |

41:ba:89 |

aida16 |

41:f6:ed |

Going to try optimising noise now.

DHCP updated

new ASIC settings: 2024Mar27-11.25.32 - 16 FEEs (2,4,6,8 n+n, rest p+n)

New layouts: /home/npg/LayOut/GSI_Triple_S100

New layout.txt

Firmware of aida11 updated from 0xea40704 to 0x3350706

Temps GOOD fig 5

Rates fig 6, 7

Check adapter alignment aida14 and aida16

bPlas left/right cables are not insulated and shorting to the snout

Logs on nnpi1 archived and deleted, start again

All 16 FEEs are showing USB logging connectivity and can be monitored with Pi_Monitor

From waveforms aida08 and aida16 are quite unhappy. The rest don't seem too bad. DSSSD 1 is much quieter than it was before!

White Rabbit Analysis: aida02 has lots of WR error counter, HDMI reseat needed

aida09-12 have no WR timestamp, the cable to the MACB is bad or the MACB is bad.

Not needed to fix right now (for noise testing)

Turn off bPlas

We see the noise drop a lot

|

|

|

106

|

Wed Dec 11 10:58:52 2019 |

NH | Initital Dec. Analysis |

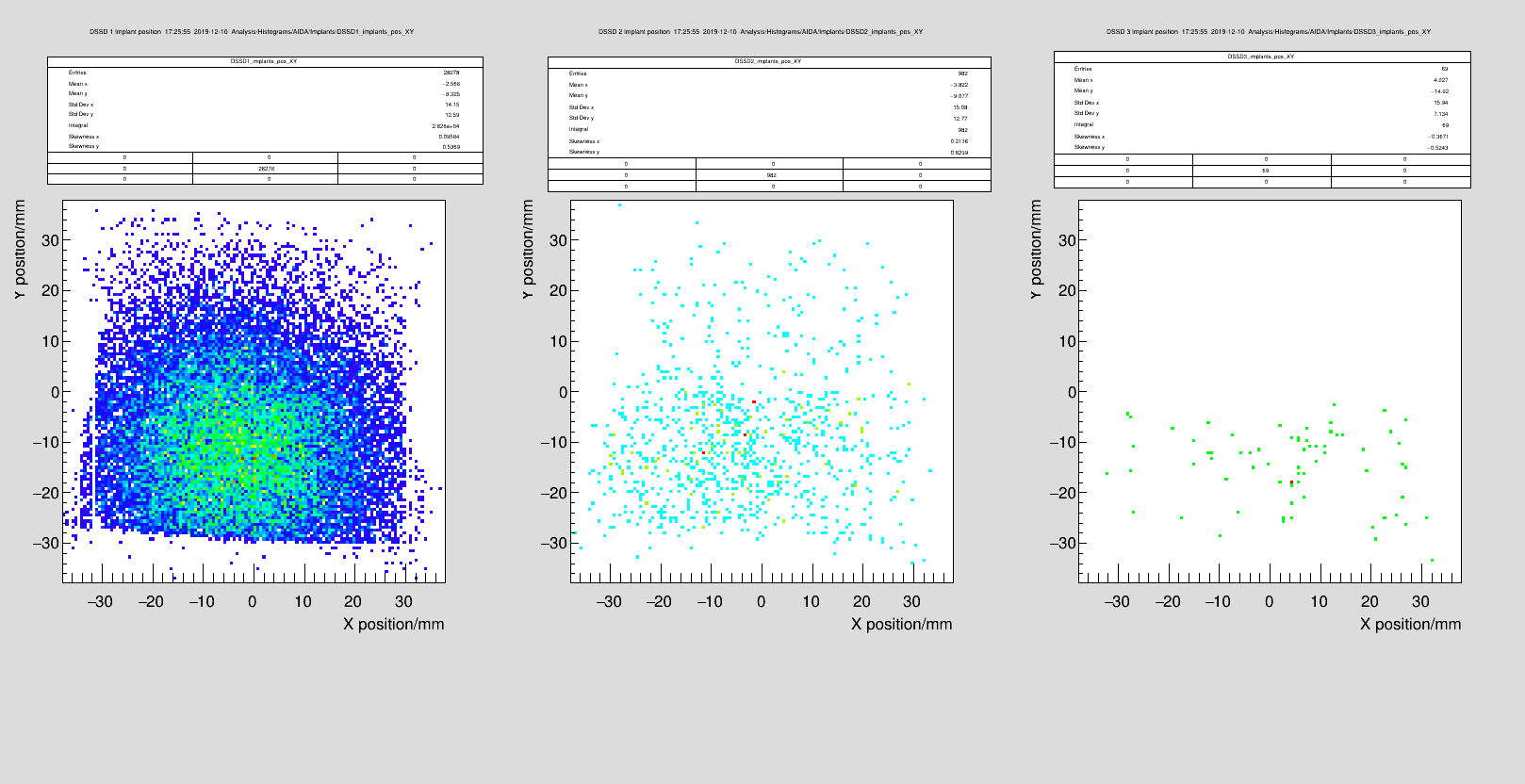

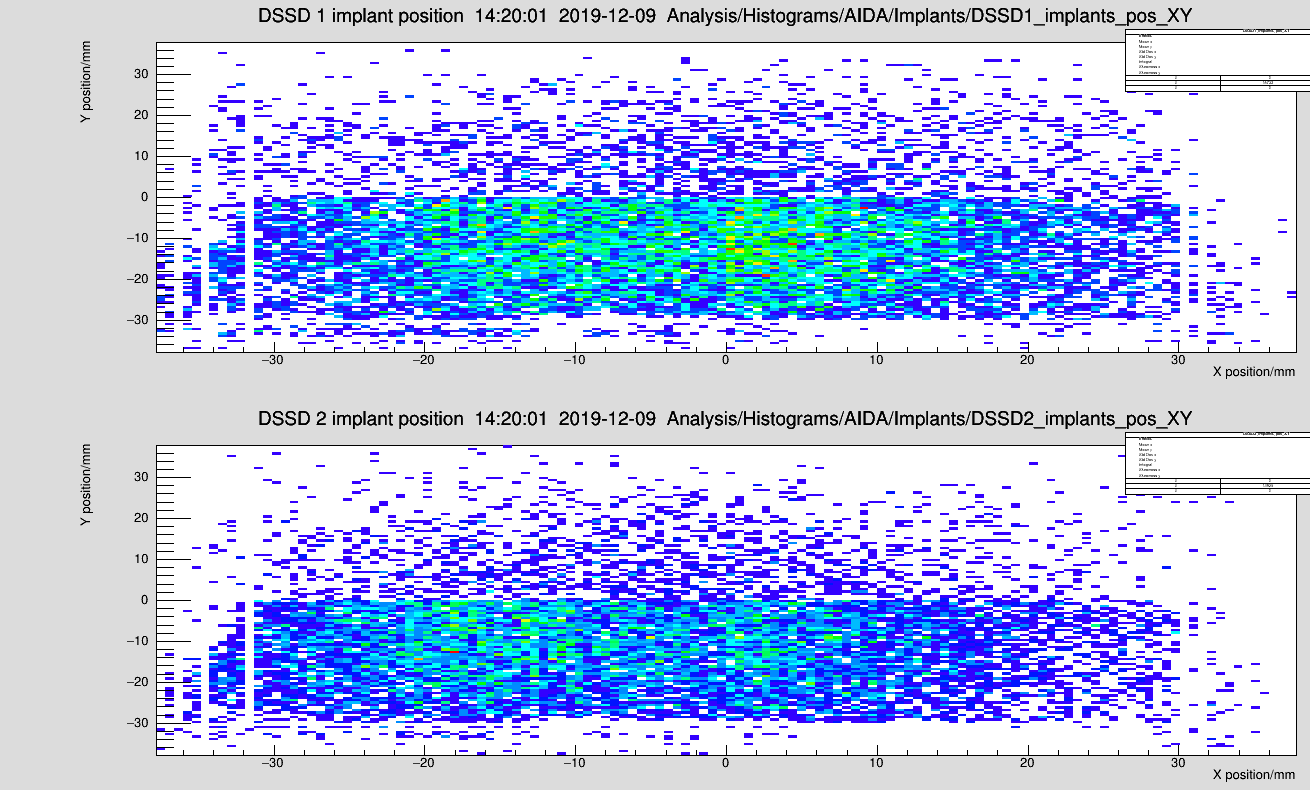

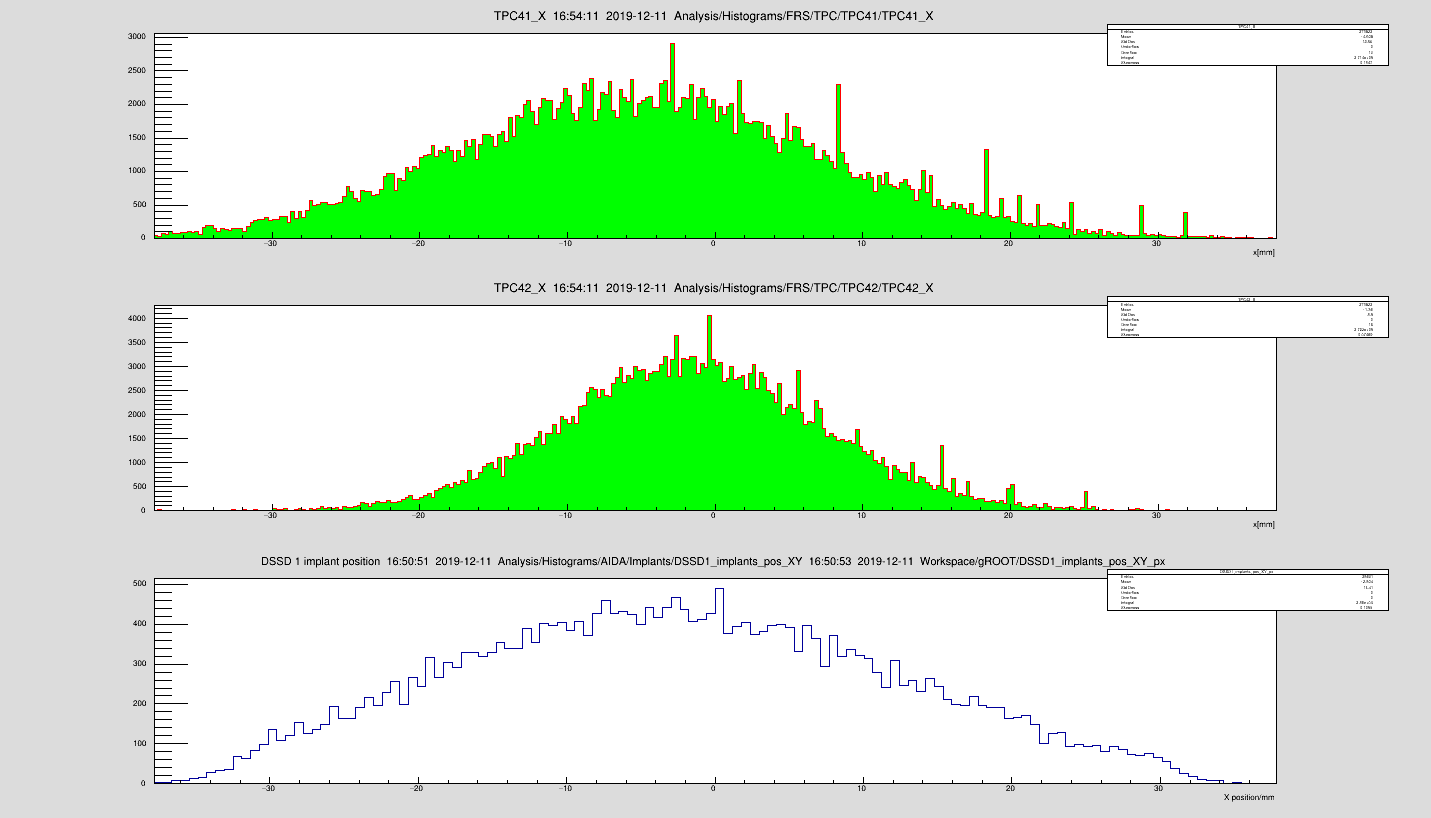

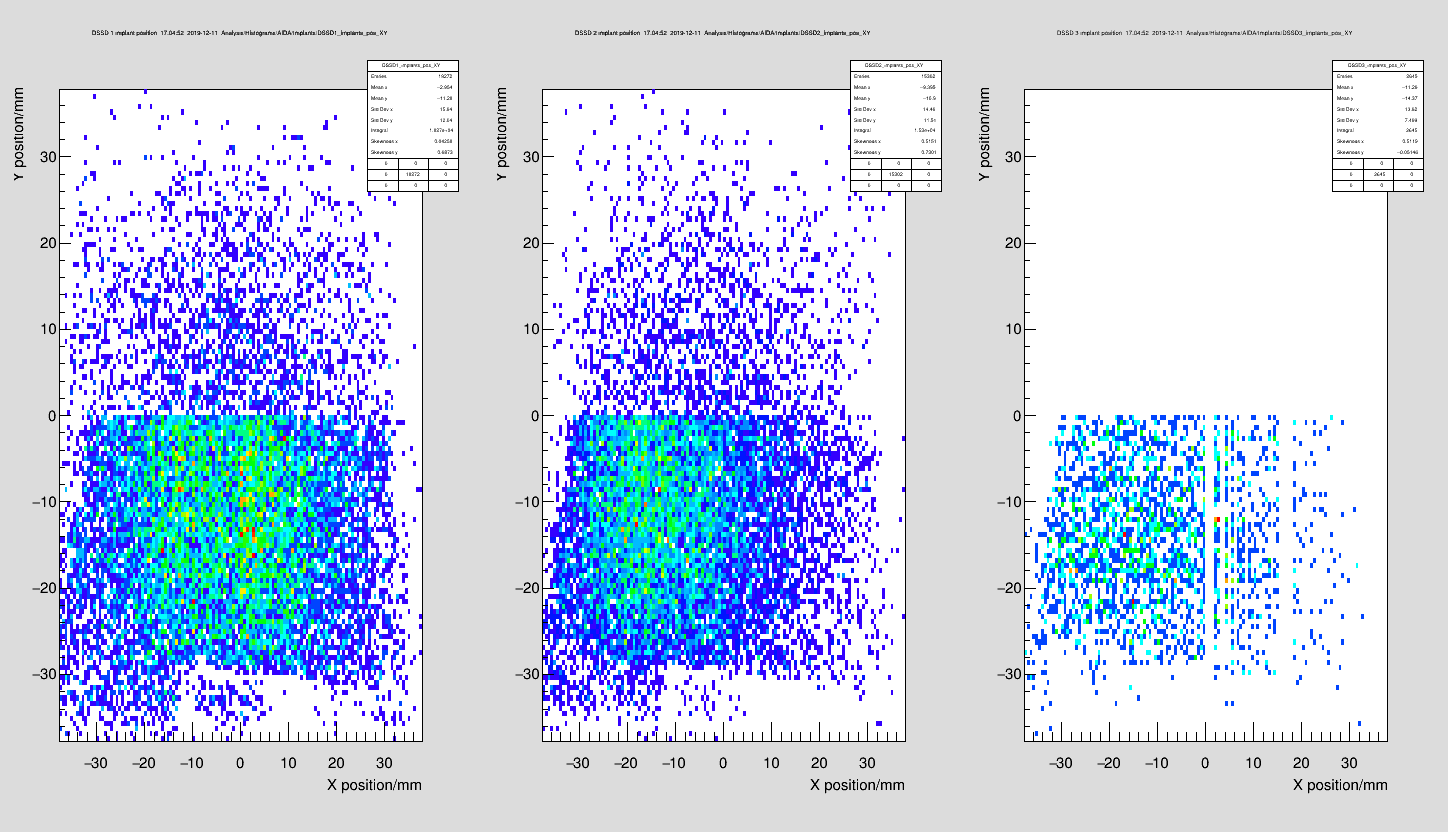

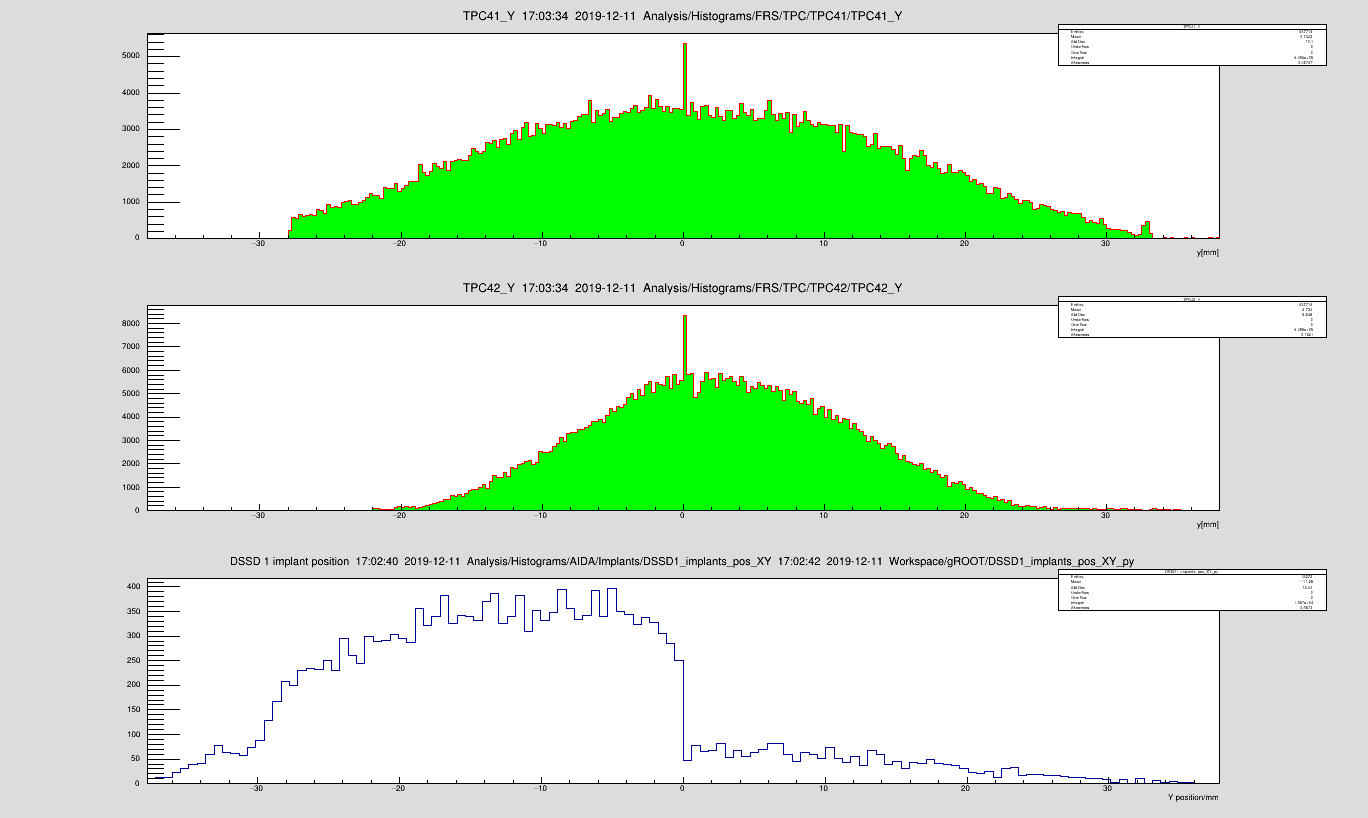

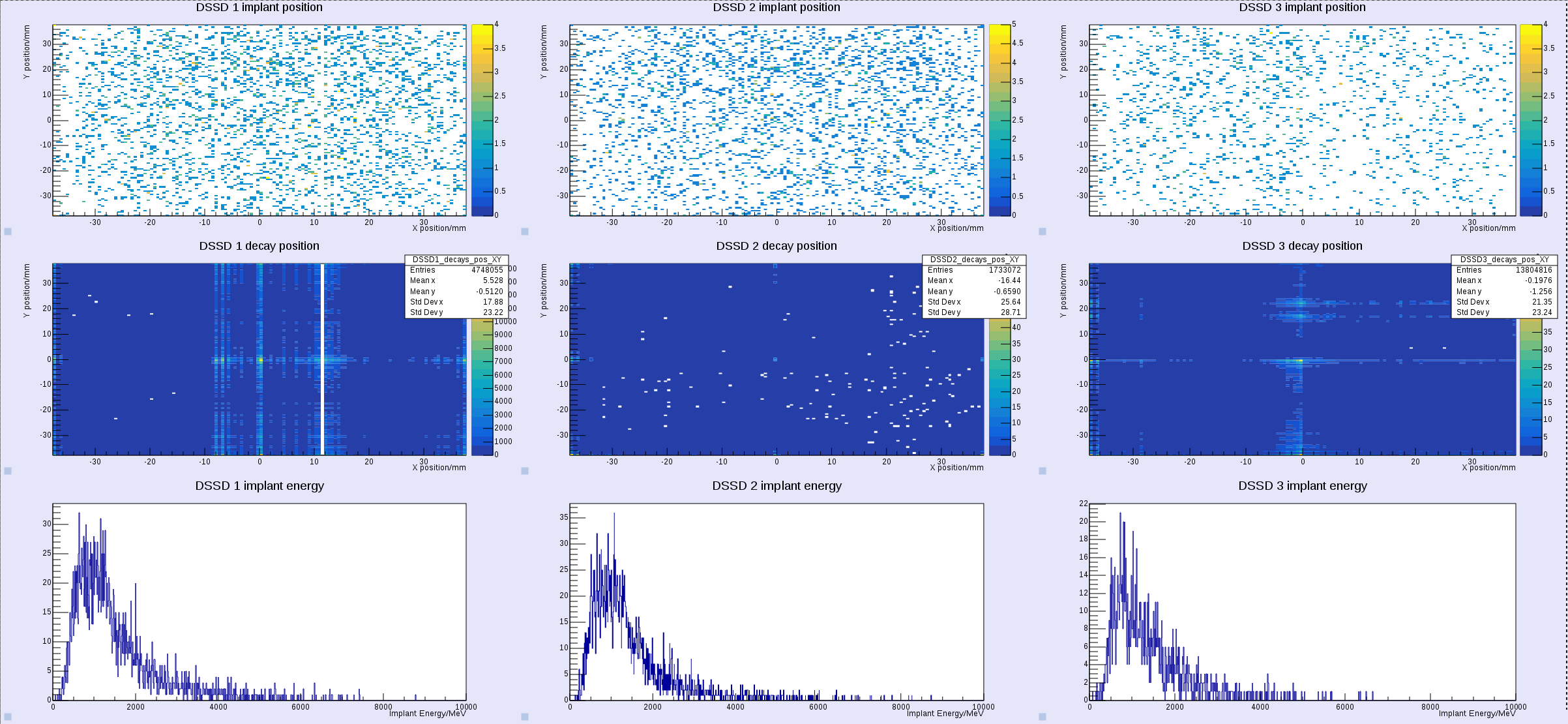

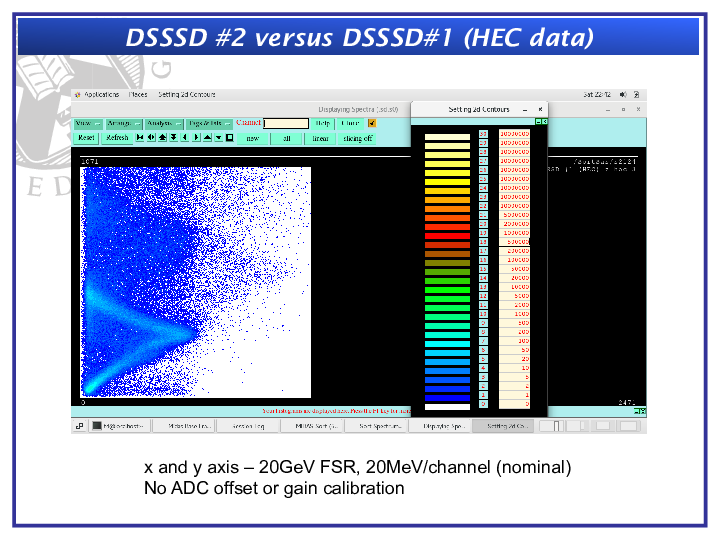

Fig 1: 2D hit pattern of each AIDA DSSD for MBS run 24 (40Ar primary beam, centred)

Low statistics in DSSD2 partly due to low energy deposition

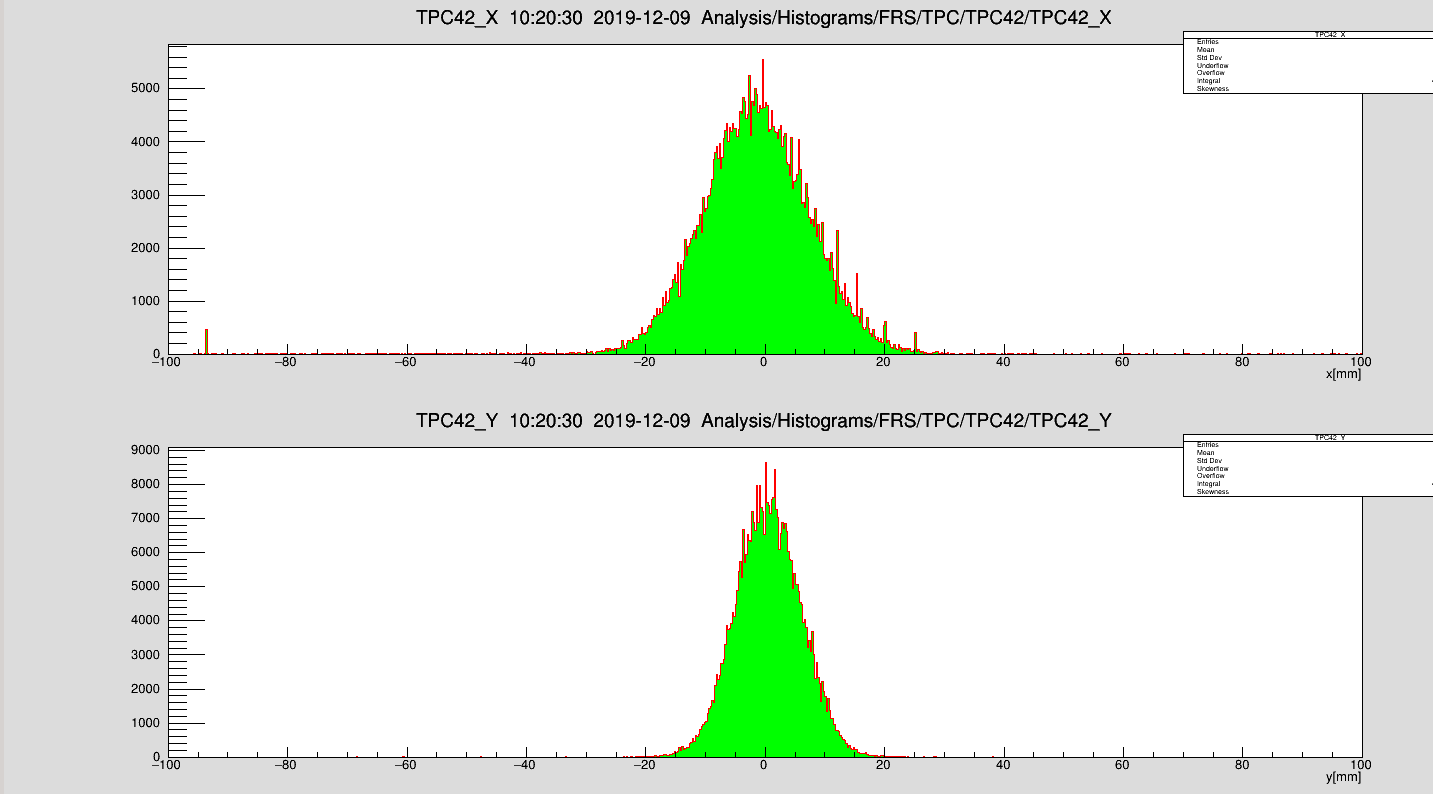

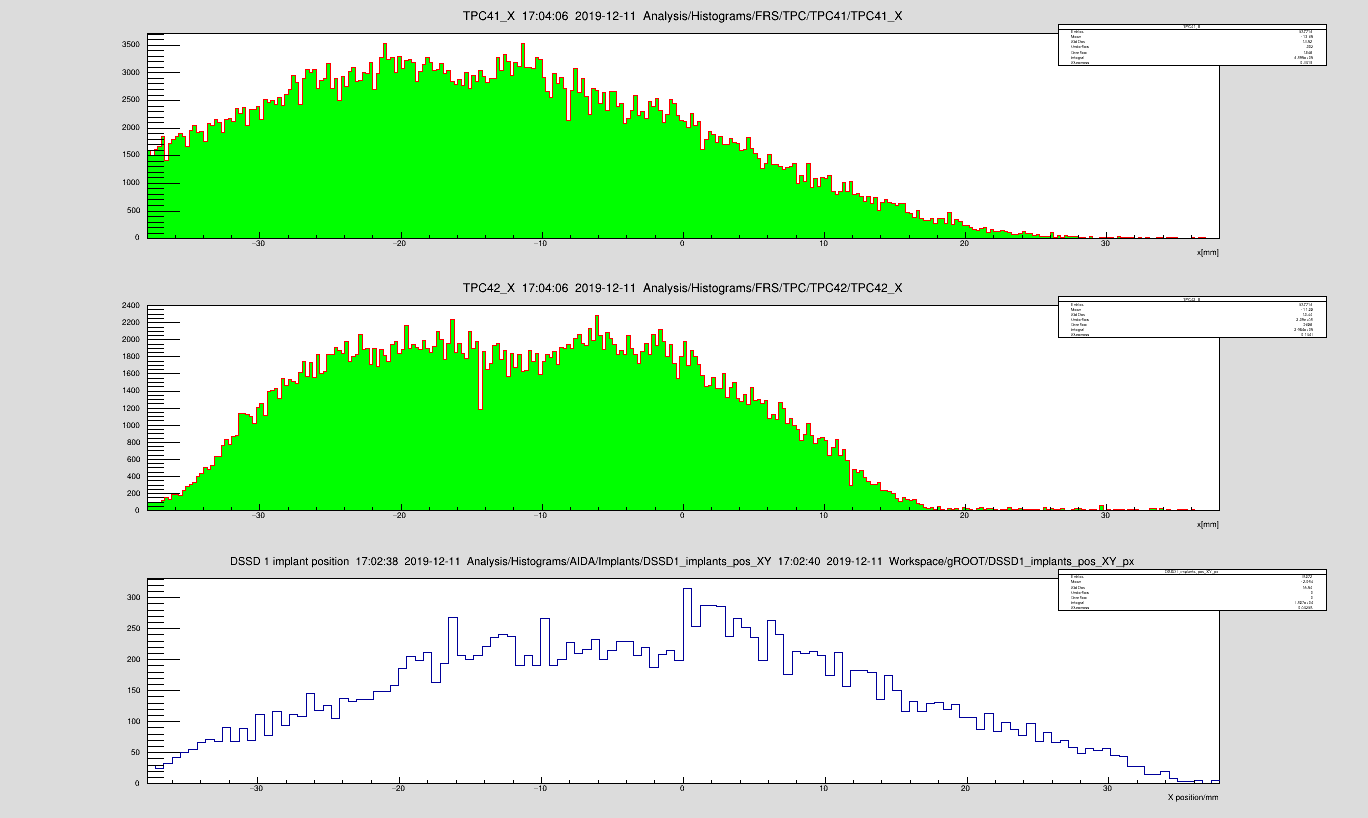

Fig 2: Position according to TPC42 (ca. 2 metres before AIDA)

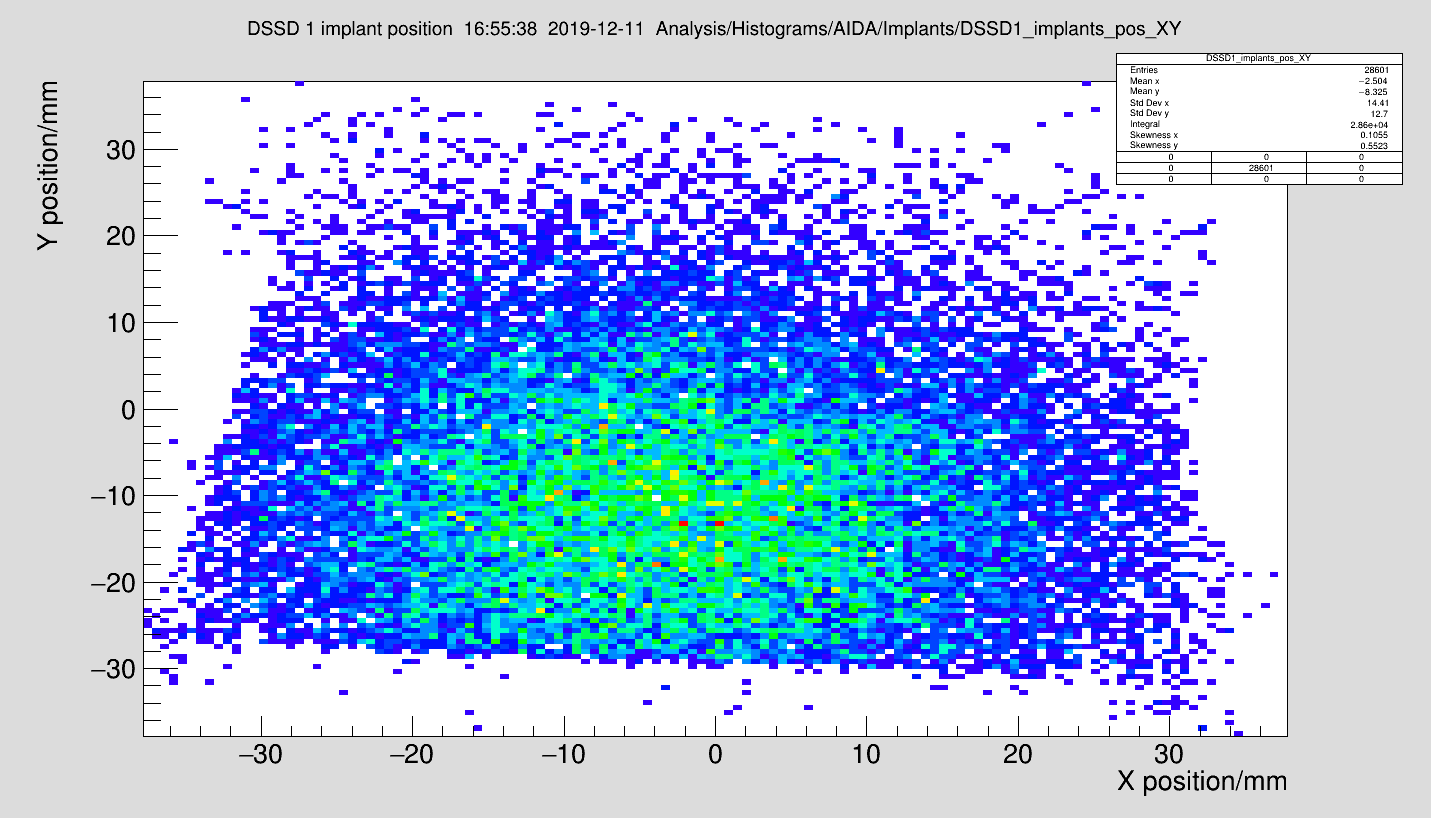

Fig 3: 2D hit pattern of DSSD 1 for MBS run 37 (34Si fragments, no PID gate)

-

Bottom part of AIDA noticably cut off - rotation in DSSD also noticed (not an issue)

Snout was investigated and platform was discovered to not be fully level by Bogdan using a laser level - he has adjusted it so that the AIDA snout is now level to within 1 mm.

(The beam right side was previous 4-6mm below the beam left side)

Y cut in fragment run is currently of unknown origin. Optics are being investigated

-

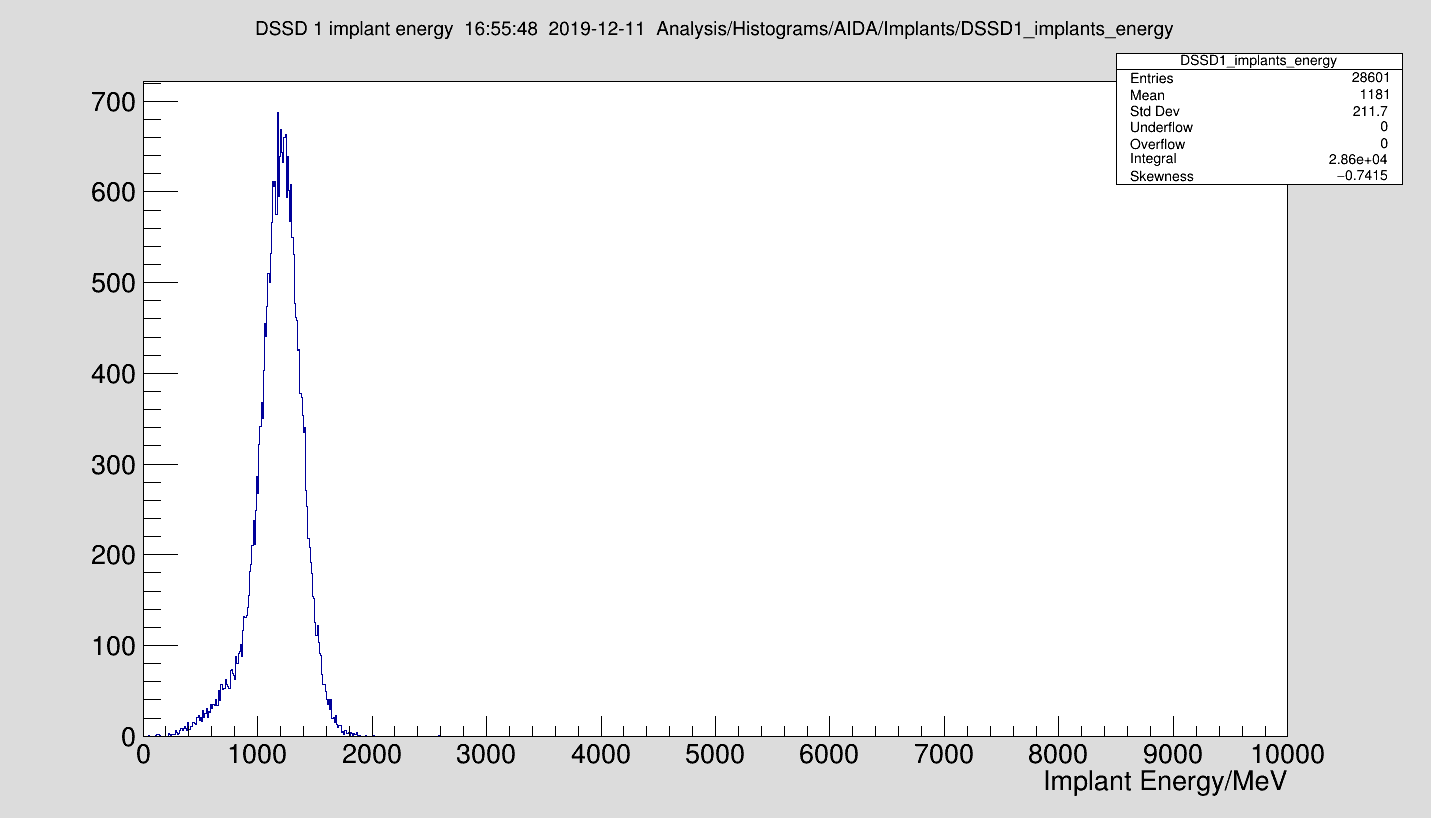

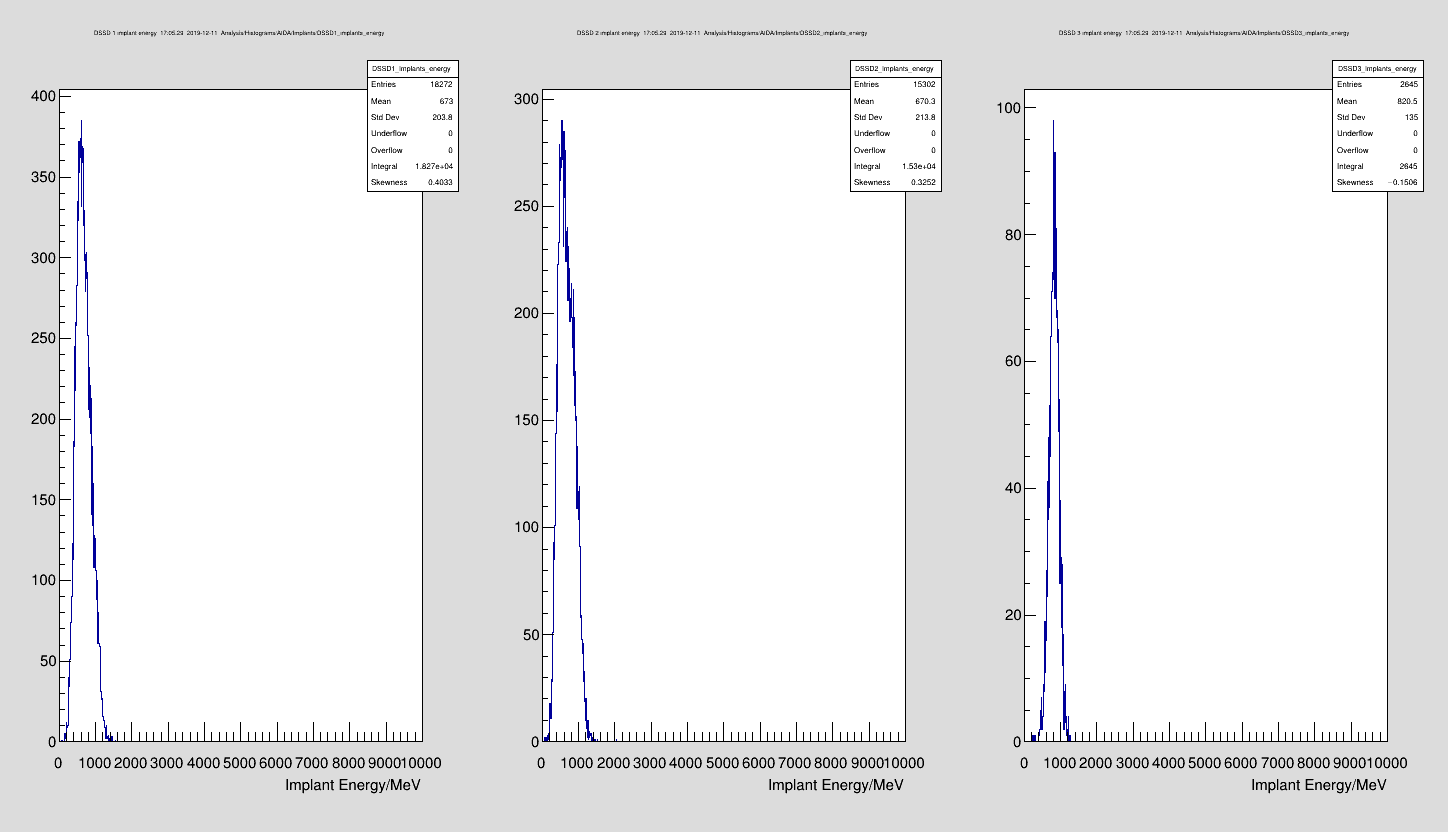

Fig 4: Hit pattern of 40Ar with strip offsets fixed (no missing strips)

Fig 5: Energy loss in DSSD1 of 40Ar primary beam

Fig 6: TPC 41, TPC 42, AIDA X comparison

Fig 7: " Y comparison

Fig 8-11: As above for 34Si run

Y cut unknown still.

Statistics of 40Ar file

======================================

AIDA Unpacker Analysis

--------------------------------------

First event: Fri Dec 6 05:21:42 2019

Last event : Fri Dec 6 05:26:17 2019

Duration : 274.604 seconds

--------------------------------------

MBS Events (M): 131808426 (481 kHz)

AIDA Words (W): 110608065 (403 kHz)

ADC Words (A): 36869349 (134 kHz)

ADC Decays (D): 36782621 (134 kHz)

ADC Implants (I): 86728 (316 Hz)

Info Words (F): 73738716 (269 kHz)

SYNC48 Words (S): 36869354 (134 kHz)

SYNC63 Words (s): 36869354 (134 kHz)

PAUSE Words (P): 4 (0 Hz)

RESUME Words (R): 4 (0 Hz)

Discrim Words(D): 0 (0 Hz)

Unknown Words(U): 0 (0 Hz)

Timewarps (T): 0 (0 Hz)

Dead Time (X): 0.113631 s (0.0413799%)

======================================

======================================

Individual FEE Overview

======================================

FEE | W A D I F S s P R D U T X

1 | 4383018 1461006 1439401 21605 2922012 1461006 1461006 0 0 0 0 0 0

2 | 11468351 3822783 3814577 8206 7645568 3822783 3822783 1 1 0 0 0 0.00733666

3 | 4353624 1451208 1428500 22708 2902416 1451208 1451208 0 0 0 0 0 0

4 | 8355002 2785000 2755870 29130 5570002 2785001 2785001 0 0 0 0 0 0

5 | 1133544 377848 376489 1359 755696 377848 377848 0 0 0 0 0 0

6 | 9617940 3205980 3205767 213 6411960 3205980 3205980 0 0 0 0 0 0

7 | 4385477 1461825 1460962 863 2923652 1461826 1461826 0 0 0 0 0 0

8 | 15105135 5035043 5032985 2058 10070092 5035045 5035045 1 1 0 0 0 0.0126429

9 | 37487211 12495735 12495422 313 24991476 12495736 12495736 2 2 0 0 0 0.0936512

10 | 110316 36772 36772 0 73544 36772 36772 0 0 0 0 0 0

11 | 12329904 4109968 4109763 205 8219936 4109968 4109968 0 0 0 0 0 0

12 | 1878543 626181 626113 68 1252362 626181 626181 0 0 0 0 0 0

Statistics of 34Si file

======================================

AIDA Unpacker Analysis

--------------------------------------

First event: Sat Dec 7 05:20:22 2019

Last event : Sat Dec 7 05:23:51 2019

Duration : 208.635 seconds

--------------------------------------

MBS Events (M): 148639738 (714 kHz)

AIDA Words (W): 132033086 (634 kHz)

ADC Words (A): 44011024 (211 kHz)

ADC Decays (D): 43874168 (210 kHz)

ADC Implants (I): 136856 (657 Hz)

Info Words (F): 88022062 (423 kHz)

SYNC48 Words (S): 44011028 (211 kHz)

SYNC63 Words (s): 44011028 (211 kHz)

PAUSE Words (P): 3 (0 Hz)

RESUME Words (R): 3 (0 Hz)

Discrim Words(D): 0 (0 Hz)

Unknown Words(U): 0 (0 Hz)

Timewarps (T): 0 (0 Hz)

Dead Time (X): 0.0806864 s (0.0386734%)

======================================

======================================

Individual FEE Overview

======================================

FEE | W A D I F S s P R D U T X

1 | 6814953 2271651 2255653 15998 4543302 2271651 2271651 0 0 0 0 0 0

2 | 14012582 4670860 4668280 2580 9341722 4670860 4670860 1 1 0 0 0 0.0088226

3 | 7618290 2539430 2523614 15816 5078860 2539430 2539430 0 0 0 0 0 0

4 | 8928934 2976310 2950380 25930 5952624 2976312 2976312 0 0 0 0 0 0

5 | 1631415 543805 531957 11848 1087610 543805 543805 0 0 0 0 0 0

6 | 10908021 3636007 3633830 2177 7272014 3636007 3636007 0 0 0 0 0 0

7 | 5644296 1881432 1864053 17379 3762864 1881432 1881432 0 0 0 0 0 0

8 | 14863755 4954585 4931620 22965 9909170 4954585 4954585 0 0 0 0 0 0

9 | 36745143 12248379 12244135 4244 24496764 12248380 12248380 2 2 0 0 0 0.0718638

10 | 198573 66191 66191 0 132382 66191 66191 0 0 0 0 0 0

11 | 15101900 5033966 5018830 15136 10067934 5033967 5033967 0 0 0 0 0 0

12 | 9565224 3188408 3185625 2783 6376816 3188408 3188408 0 0 0 0 0 0

All good (no deadtime issues) |

| Attachment 1: AIDA_HitDec19.png

|

|

| Attachment 2: TPCs.png

|

|

| Attachment 3: AIDA-fragments.png

|

|

| Attachment 4: AIDA_XY.png

|

|

| Attachment 5: AIDA_E.png

|

|

| Attachment 6: TPC_41_42_AIDA_X.png

|

|

| Attachment 7: TPC_41_42_AIDA_Y.png

|

|

| Attachment 8: AIDA_XY_34Si.png

|

|

| Attachment 9: AIDA_E_34Si.png

|

|

| Attachment 10: TPC_41_42_AIDA_X_34Si.png

|

|

| Attachment 11: TPC_41_42_AIDA_Y_34Si.png

|

|

|

227

|

Fri Apr 16 02:15:12 2021 |

NH | Implants/Punchthrough |

Rate with beam < 1000 Hz still

Not Uranium but some fragments possibly produced in the thick 9g degrader

S4 slits are +/- 20mm but these punchthrough and cover the +/- 40mm of AIDA |

| Attachment 1: 53_AM.png

|

|

|

7

|

Thu Sep 20 09:16:31 2018 |

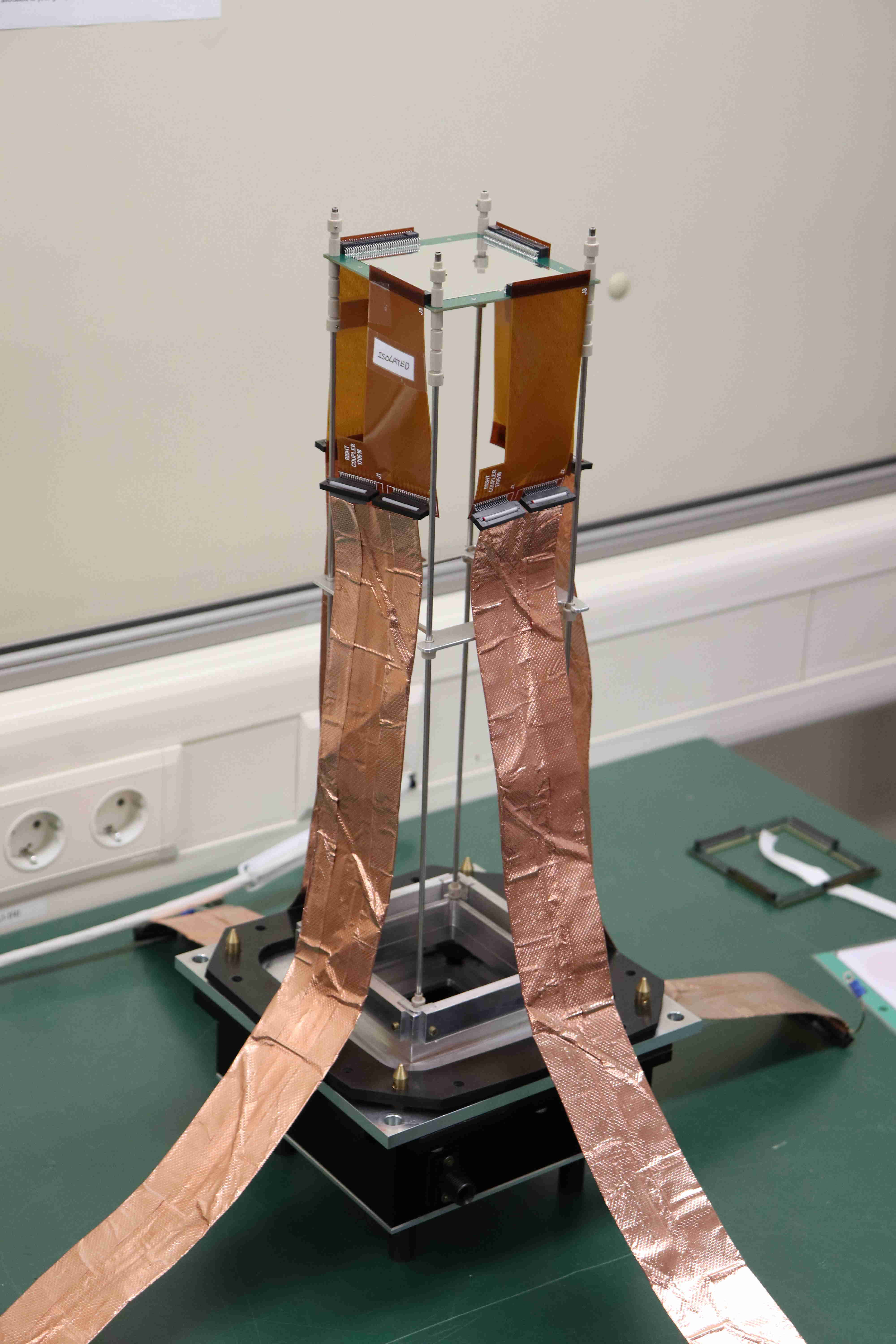

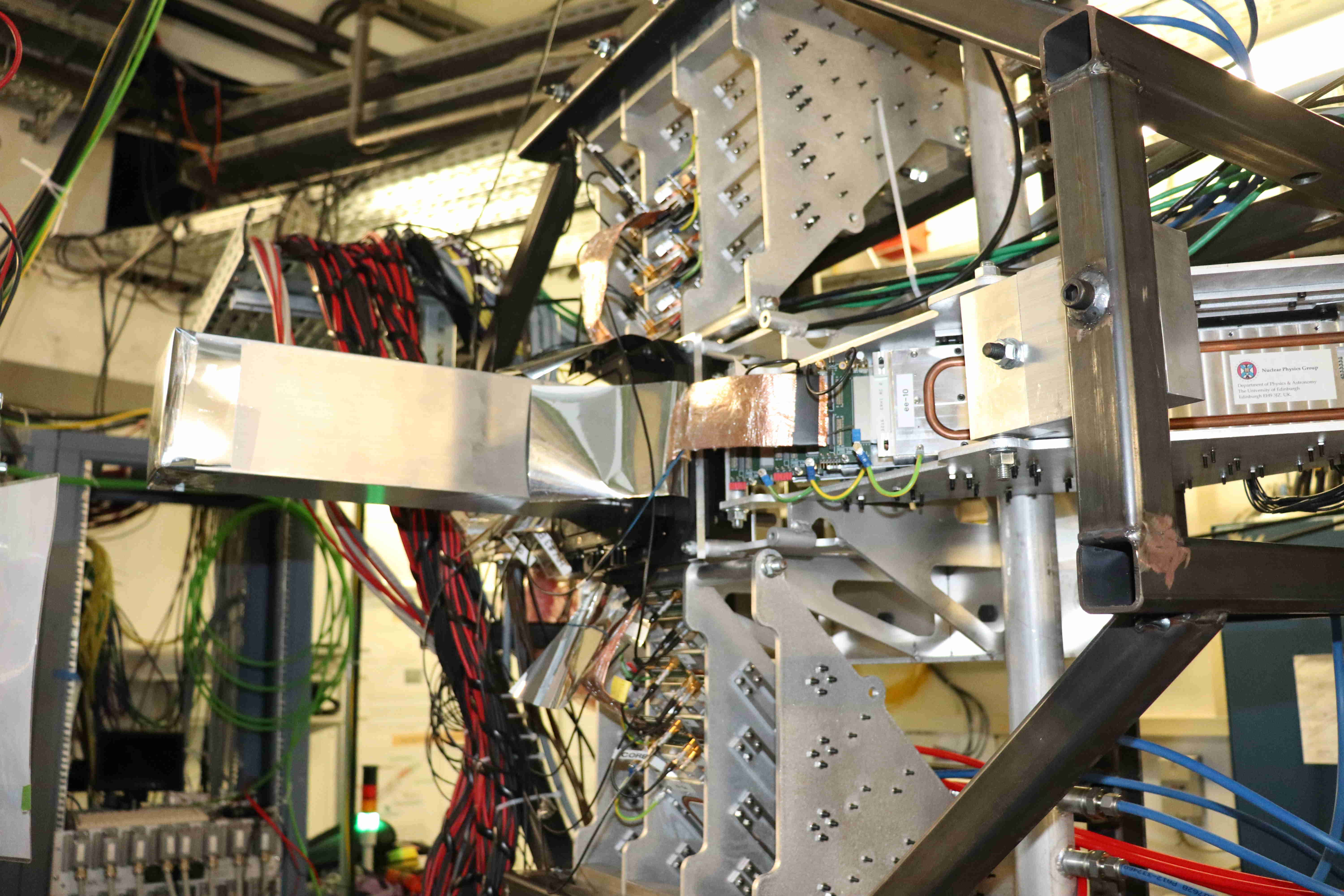

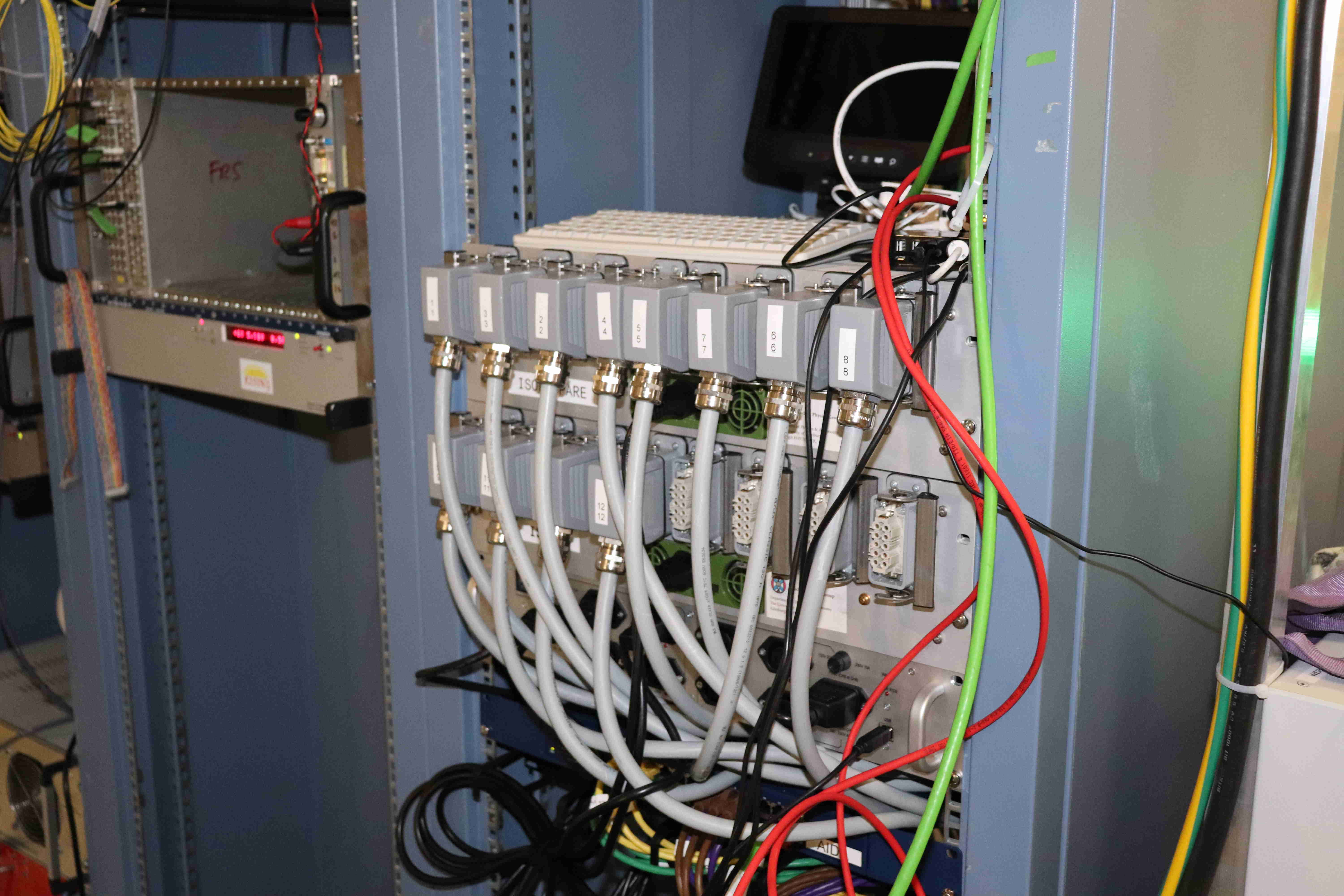

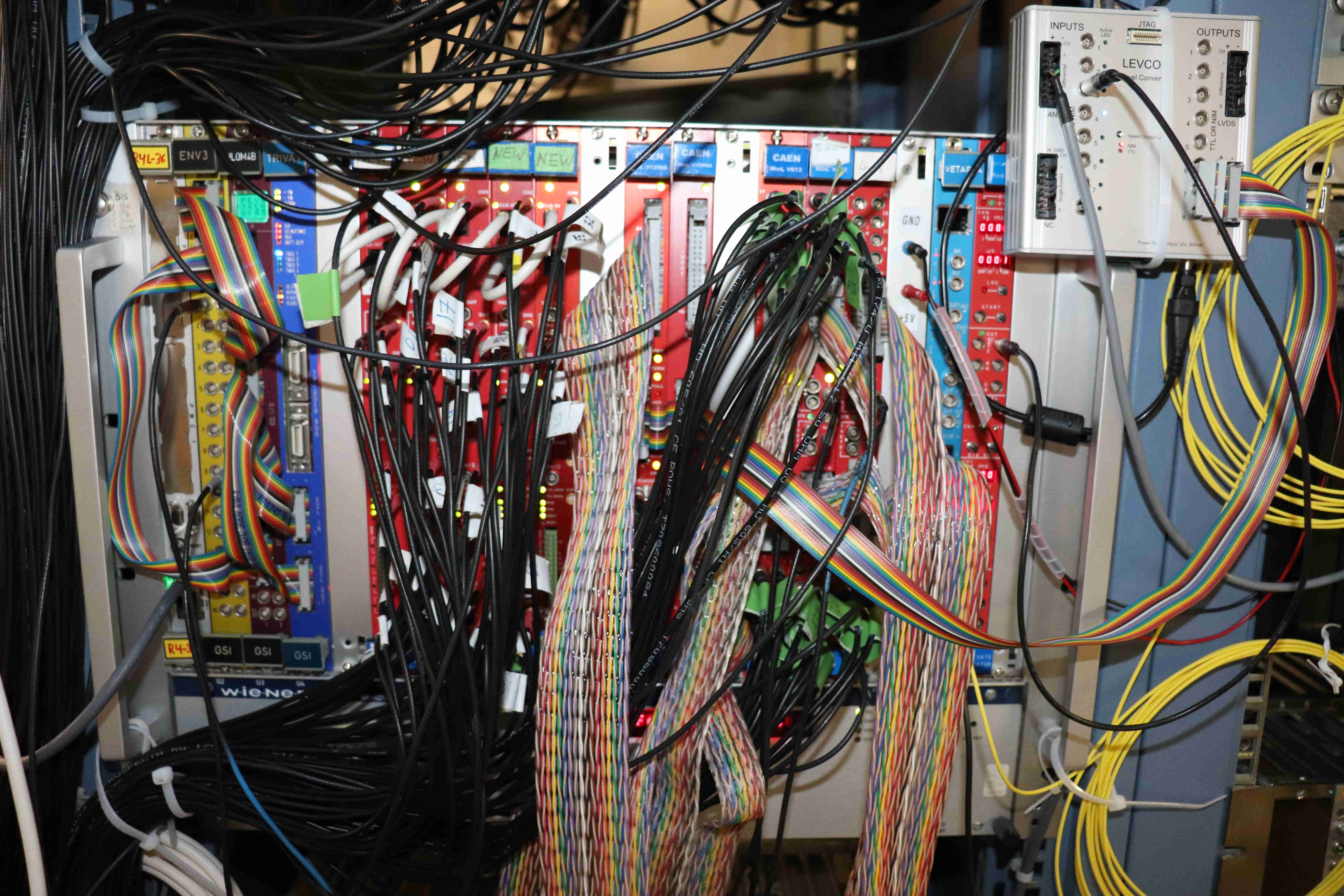

TD | Images of AIDA setup for DESPEC |

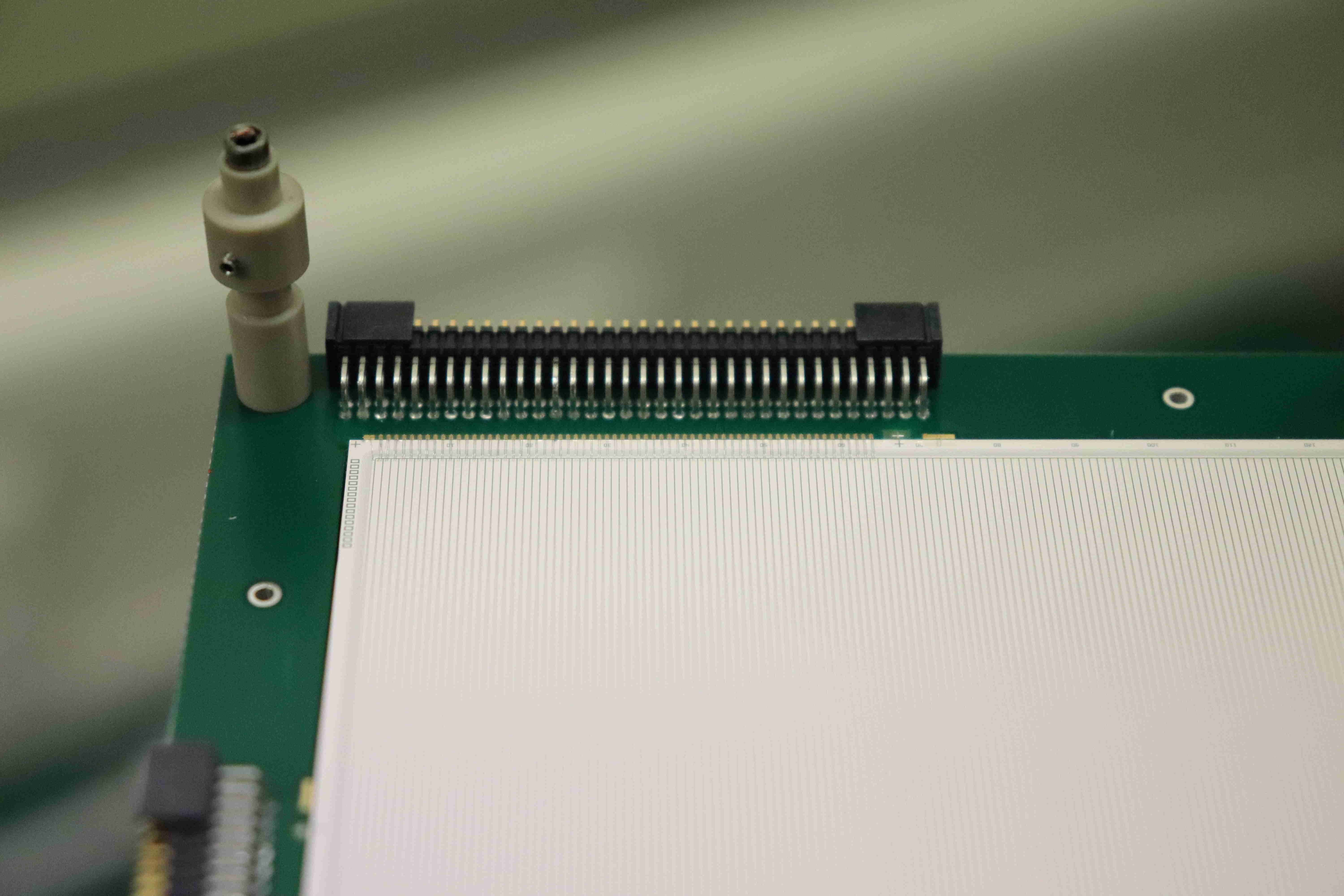

Attachment 1 - detail of MSL type BB18(DS)-1000 p+n junction side strips, bias ring, multiple guard rings, filed

plates and bond wires

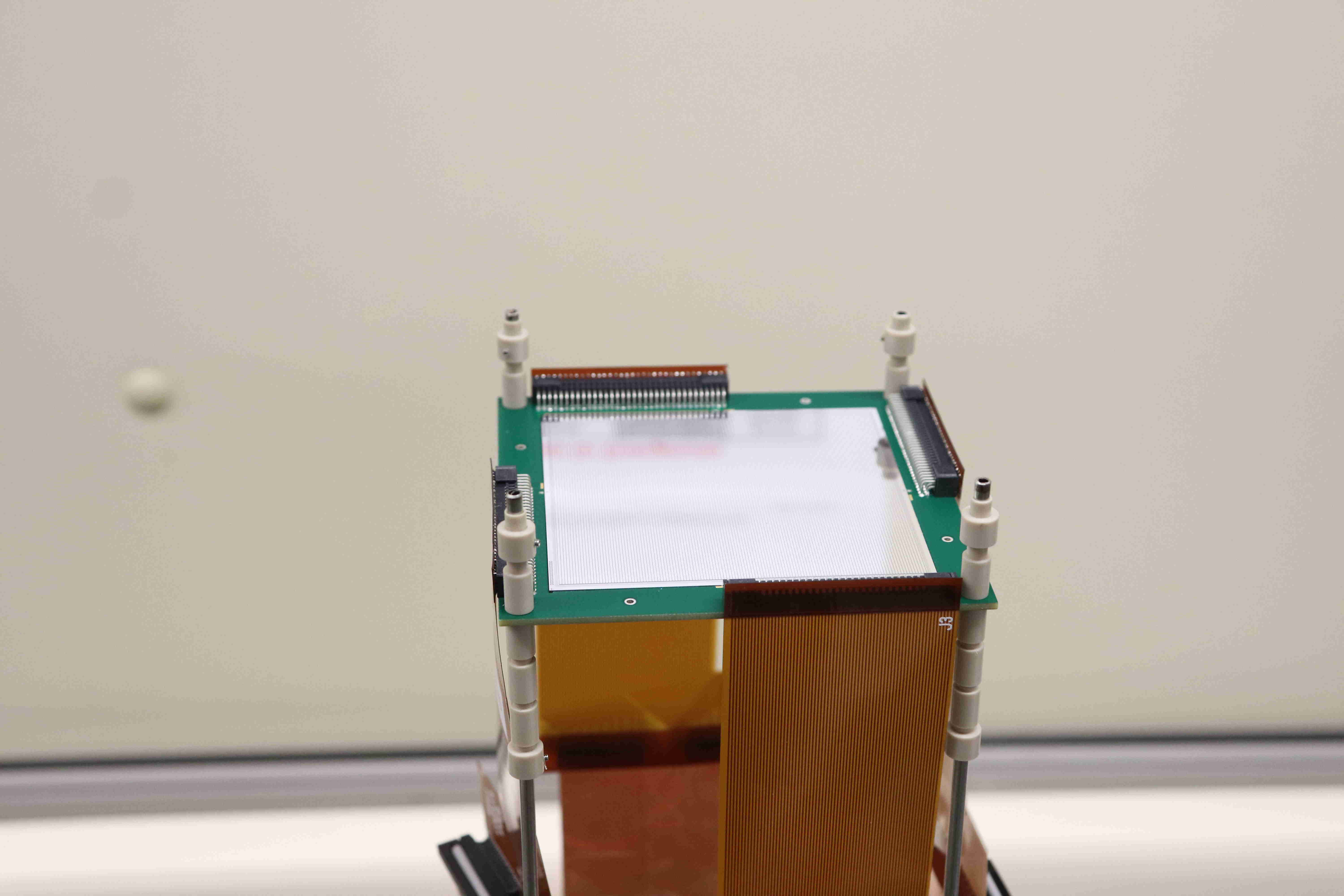

Attachment 2 - MSL type BB18(DS)-1000 with Kapton PCBs attached

Attachment 3 - MSL type BB18(DS)-1000 with Kapton PCBs + 3M 1245 copper foil-screened Samtec FTSH ribbon cables

attached

Attachment 4 - AIDA snout installed (with 1x DSSSD) with cabling to 4x FEE64s in AIDA support assembly

Attachment 5 - AIDA + FATIMA array

Attachment 6 - AIDA FEE64 PSUs, network switch, USB-controlled ac mains relay

Attachment 7 - AIDA MACBs, pulser, detector bias

Attachment 8 - FATIMA DAQ

Attachment 9 - DESPEC 19" racks on detector platform |

| Attachment 1: xIMG_1652.JPG

|

|

| Attachment 2: xIMG_1653.JPG

|

|

| Attachment 3: xIMG_1659.JPG

|

|

| Attachment 4: xIMG_1660.JPG

|

|

| Attachment 5: xIMG_1663.JPG

|

|

| Attachment 6: xIMG_1664.JPG

|

|

| Attachment 7: xIMG_1665.JPG

|

|

| Attachment 8: xIMG_1666.JPG

|

|

| Attachment 9: xIMG_1667.JPG

|

|

|

490

|

Wed Jun 22 10:09:12 2022 |

PJCS | INFO: FEE64 supply Voltages |

Study of the FEE64 power supply distribution has yielded the following :-

The most sensitive regulator, as regards the device voltage input, is the TPS51100 that supplies the DDR memory reference voltages. This requires +4.75 to +5.25 volts. This is supplied from the Power input connector +5v input.

The common LT3080 regulator used over much of the board is a Low Voltage Dropout regulator. This requires 0.5v difference between input and output voltage as minimum. This is not a problem with the +4.75v minimum for the TPS51100 requirement setting the voltage for the board.

The supply to the mezzanine is direct from the power connector +5v input. On the mezzanine there is an LT3080 for each ASIC supplying the required 3.3v. These regulators would possibly benefit from a 1uF capacitor at the Control voltage input.

The simplest approach would be to add a capacitor to the bottom layer where the Control voltage enters the mezzanine.

The power cable has a nominal resistance of 13.3ohms/km. The 3 conductors of the cable are supplying 10A when all is in operation. So the expected voltage drop would thus be ( 10 x 13.3 x 0.007 ) /3 => 0.3v each core.

The conclusion would be that the voltage at the power supply should drop to 5.25 v thus ensuring the TPS51100 is supplied as required regardless of the operation of the FEE.

This will be tested at Daresbury. |

|

514

|

Wed Sep 14 19:07:07 2022 |

PJCS | INFO : Three Merger Statistics explained |

There are three Merger statistics that can be used to better understand how the data flow through the Merger system is proceeding.

Two are from the Link task and one is from the Merger.They are all "No data buffers avaliable" with #1, #2, #3 at the end.

#1: This is incremented when the Link task has a data item to put in the queue for the Merge process but there is no room.

#2: This is incremented when the Link task has found no room in the queue for the Merge process ( #1 ) , waited , tried again and failed.

#3: This the other end of the queue. When the Merge task requests a data item from a Link task queue and there is nothing available.

|

|

300

|

Fri May 7 19:47:54 2021 |

PJCS | HowTo mitigate excessive temperature in an FEE64 |

After tests in the Daresbury T9 system.

Disabling the waveform ADCs in an FEE64 which is running with the FPGA over temperature will drop the FPGA temperature by 10 degrees.

To disable the ADCs open the Local Control browser window and set the ADC Control register , @2, to 0xFF

The easiest way to restart the waveform ADCs correctly is to rerun SETUP from the control window selecting just the FEE that is affected.

Alternatively STOP acquisition, set the ADC Control register back to 0 and rerun the calibrate ADCs in the FADC Align and Control browser window.

|

|

52

|

Mon May 20 13:51:45 2019 |

NH | HowTo Verify WR Times |

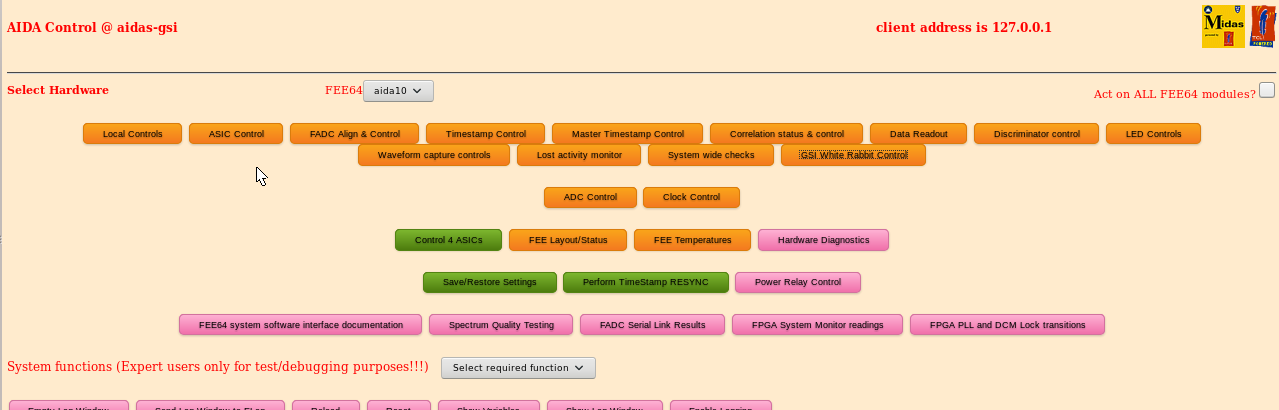

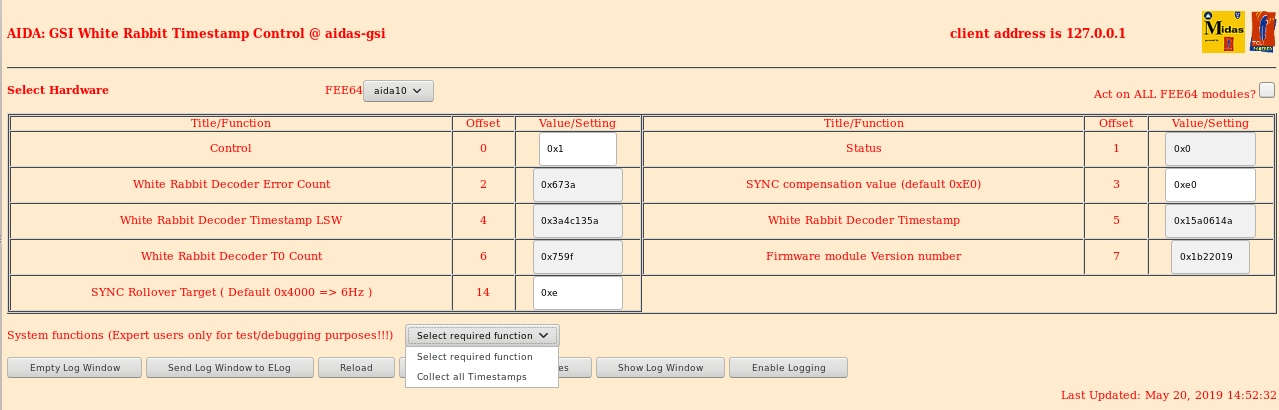

The latest version of MIDAS has a new page to check the WR timestamp of each FEE.

In AIDA Hardware control click: GSI White Rabbit Control

In expert options click: Collect all Timestamps

Verify every FEE has a good timestamp. |

| Attachment 1: HowTo-WR1.png

|

|

| Attachment 2: HowTo-WR2.png

|

|

| Attachment 3: HowTo-WR3.png

|

|

|

211

|

Wed Mar 31 15:46:09 2021 |

PJCS | HowTo : Synchronize the ASIC clocks. |

To Synchronize the FEE64 ASIC clocks to rise at the same timestamp time use the System function Synchronise the ASIC clocks in the System Wide Checks browser page.

The Server will read the current timestamp value and calculate, based on the number of FEEs and the access delay, a timestamp value sometime in the future. F_stamp

F_stamp is written to each FEE and the synchronization is enabled.

In a state machine in the FEE ASIC clock control, logic is enabled to synchronize its ASIC clock. It compares the current timestamp with F_stamp and if the current timestamp is >= F_stamp then it will start the ASIC clock.

The report in the browser log window gives the 3 LSBs of the timestamp at the instant the ASIC clock is started. They should all be the same. They are from the 10ns timestamp.

|

|

209

|

Wed Mar 31 12:46:10 2021 |

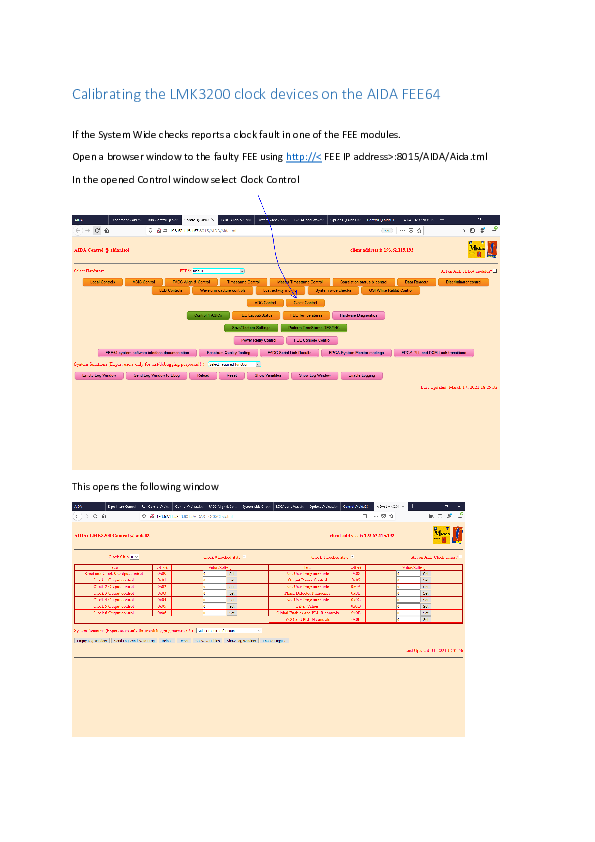

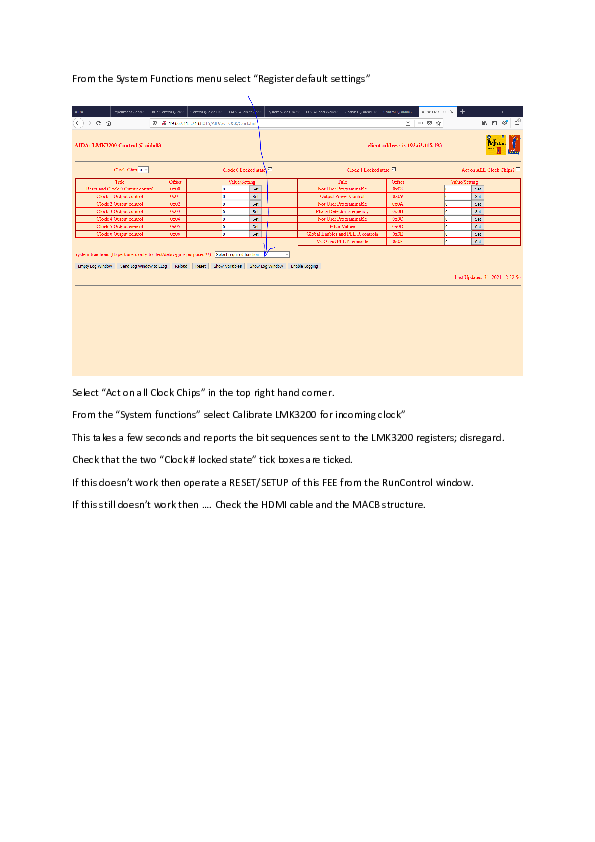

PJCS | HowTo : Calibrate the LMK3200 clock devices |

Here is a document showing how and where to calibrate the LMK3200 devices that lock to the system clock and generate the clocks for the ADCs and the FPGA internal logic. |

| Attachment 1: Calibrating_the_LMK3200_clock_devices_on_the_AIDA_FEE64.pdf

|

|

|

36

|

Tue Mar 26 14:58:09 2019 |

NH, VP | How to reset merger |

If the merger doesn't show "xfer Links => Merger" at the top, it is probably the merger setting has been corrupted somehow. This is how to reset it

If you go to the web page from which you started the Merge and TapeServer

(probably localhost:8115)

Then select the item NetVar Service which is at the left hand end.

Click on Inquire Registers

then enter NetVar.MERGE.RunOptions into the "Register Name" entry and when finished move the mouse out of the entry box.

NetVar.MERGE.RunOptions will appear in the center of the top row. (it is an item in the menu but not so easy to find)

Click on Read and I expect you will get 0

Type 1 into the data entry box and click on Write

Now return to the Merger and click on Reload

The Merger State will now end as xfer Links => Merger

The button Output: will now toggle between this and xfer links => Merger => Storage. |

|

63

|

Wed Aug 14 14:40:18 2019 |

NH | High Frequency Noise in AIDA |

Figures of intense high frequency noise pickup in AIDA.

Will investigate source in S4.

Edit: Period is approx 40 cycles / approx 2.5 MHz (?) |

| Attachment 1: HF.png

|

|

| Attachment 2: HFZ.png

|

|

|

133

|

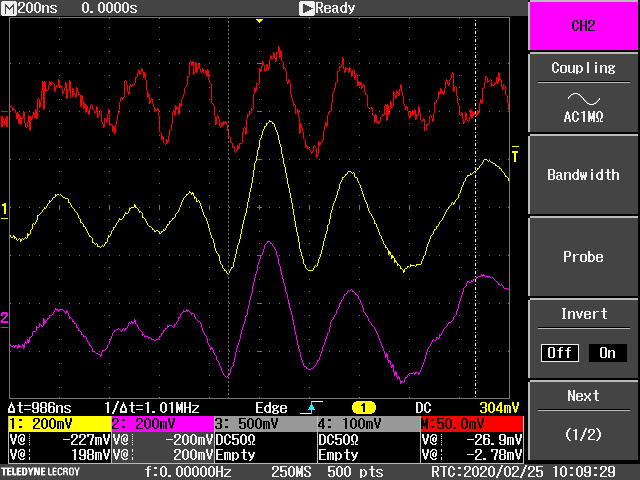

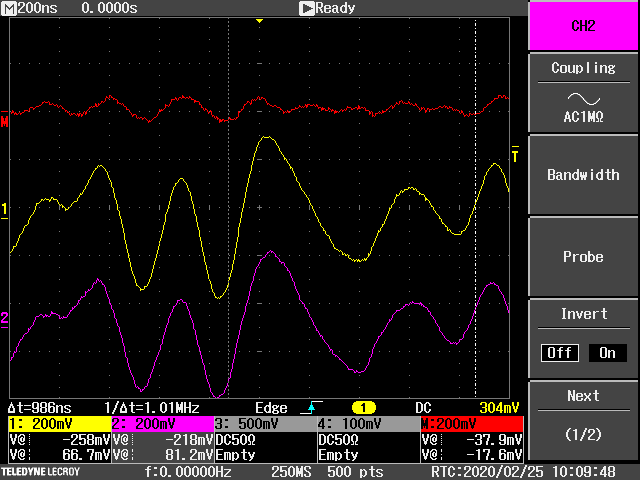

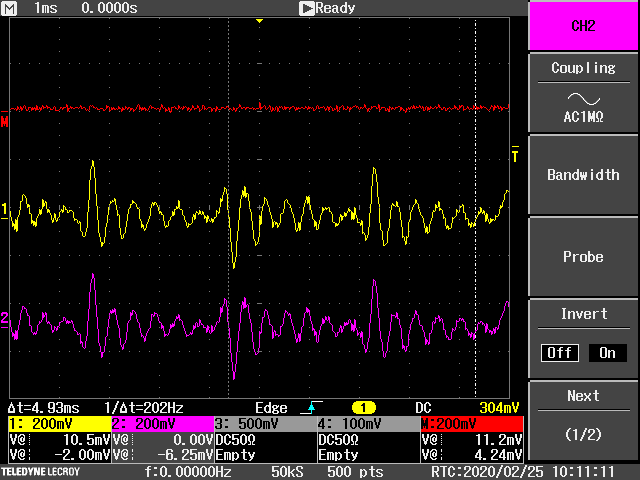

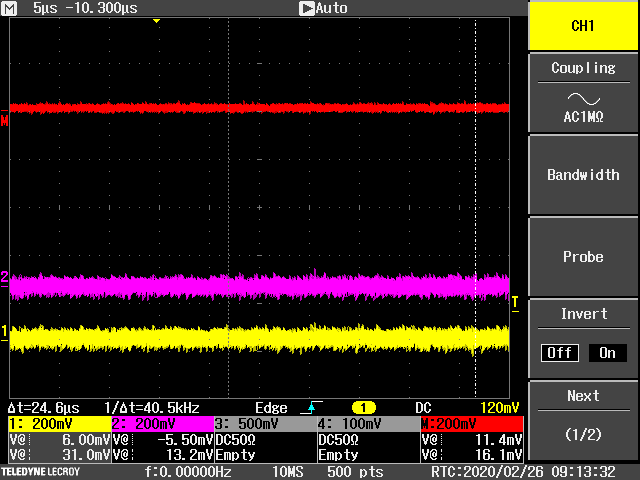

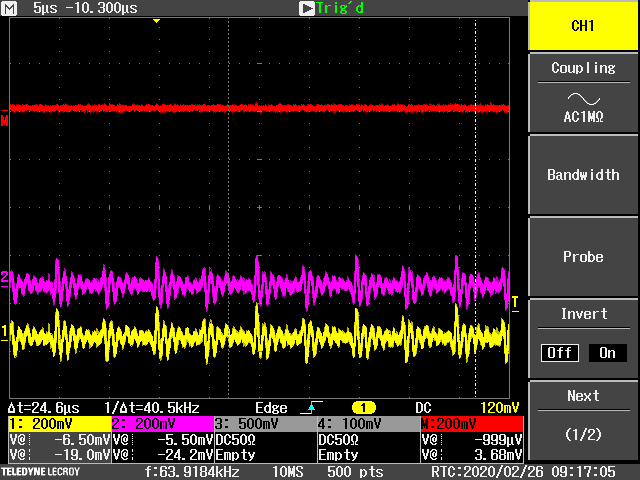

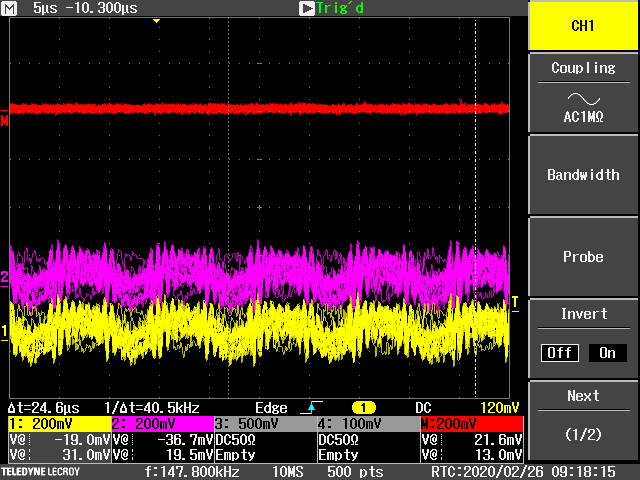

Tue Feb 25 09:55:59 2020 |

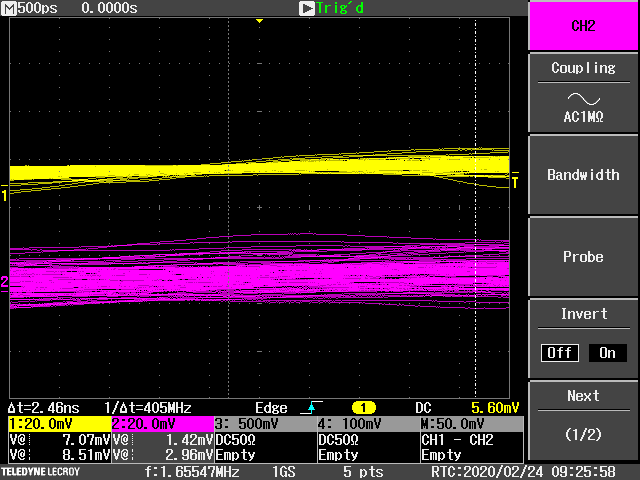

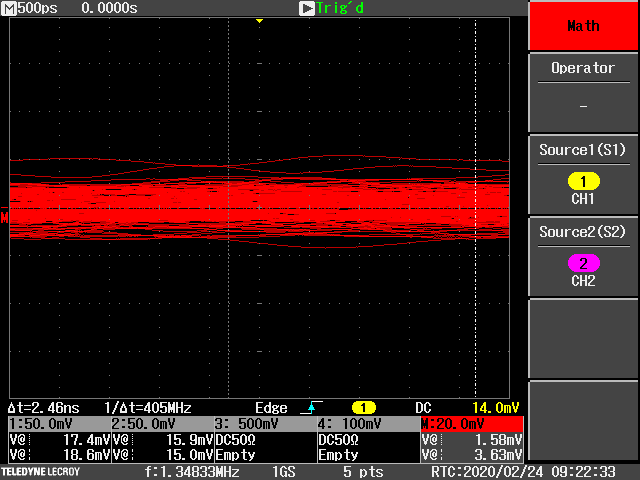

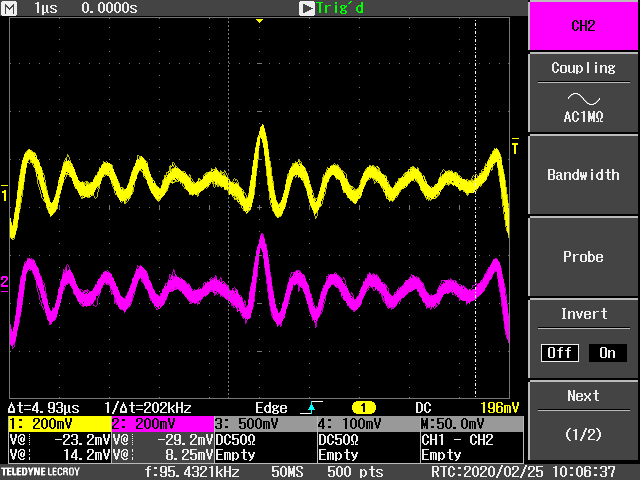

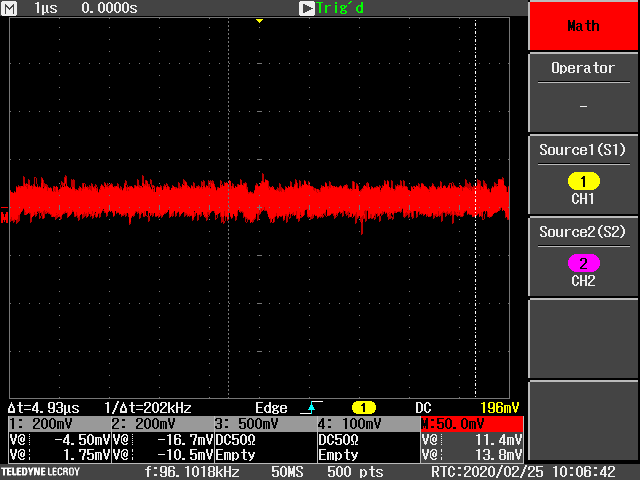

NH | HV Scope Traces |

Looking at the HV bias in a scope to see if it is the source of noise especially on the p+n side

Channel 1: HV Core channel 4

Channel 2: HV Braid Channel 4

Math: Ch1 - Ch2

100V bias (100 uA leakage current for 1 MOhm)

No obvious frequency components or large frequency components?

I do not know how this compares to RIKEN or STFC-DL

Updated to put the right frequency range (misread before)

Fig 3-4: Normalish looking data

Fig 5-6: Examples of noise appearing randomly on math line

Fig 7: 1ms long trace, noise stopped appearing

Update 26.02.2020

Fig 8: Trace with all 4 HV channels off

Fig 9: Trace with only oscilloscope biased

Fig 10: Trace with braids unplugged from all 3 FEE64s (only channel 4 connected)

Things to try:

Joining clean earth & chassis ground?

Checking HV jumper?

Finding 'scope probes and testing NIM socket? |

| Attachment 1: SCRN0057.PNG

|

|

| Attachment 2: SCRN0054.PNG

|

|

| Attachment 3: SCRN0059.PNG

|

|

| Attachment 4: SCRN0060.PNG

|

|

| Attachment 5: SCRN0071.PNG

|

|

| Attachment 6: SCRN0073.PNG

|

|

| Attachment 7: SCRN0075.PNG

|

|

| Attachment 8: SCRN0078.PNG

|

|

| Attachment 9: SCRN0079.PNG

|

|

| Attachment 10: SCRN0080.PNG

|

|

|

672

|

Wed Dec 4 09:57:24 2024 |

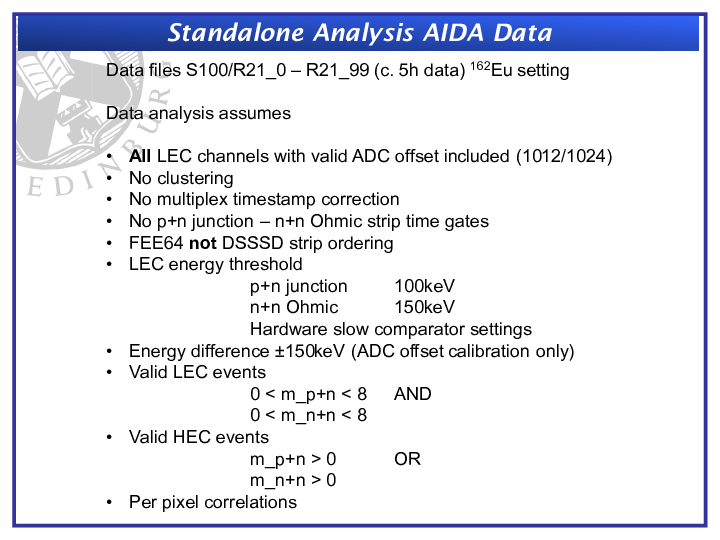

TD | HISPEC DESPEC meeting presentation - November 2024 -0 Summary of AIDA performance 2024 |

|

| Attachment 1: Summary_of_AIDA_2024_distro.pdf

|

|

|

403

|

Sat Mar 5 10:43:45 2022 |

OH, NH | Grounding and noise tests 4th-5th March Summary |

Tests performed

- After leaving overnight noticed the pulser was not fully inserted into aida09

- Little change in rates observed in 9 but otherwise nothing else

- Connected bias of aida02 (n+n ground) to aida06 (n+n ground) and likewise 4-8

- No change observed in rates

- Also tested covering the snout in light tight material

- Unplugged the system monitor from 6 and 8, no change

- Connected the snout to ground with copper tape

- Rates became very unpredictable in the FEEs unsure if this was snout grounding related though

- Removed the ground and powercycled and rates restored to where previously

- Changed the bias supply jumper inside to have the bias line connected to the rack ground

- At the same time noticed that the ground cable connecting the adaptor board of aida06 to the FEE had become disconnected from the ring terminal

- Recrimped and inserted again

- Saw an improvment in the rates of the p+n strips and also the n+n strips - attachment 1

- Pulser widths however larger than yesterday

p+n width

| FEE |

Width |

| 9 |

118 |

| 1 |

88 |

| 10 |

75 |

| 11 |

77 |

| 3 |

67 |

| 12 |

66 |

| 13 |

96 |

| 5 |

89 |

| 14 |

107 |

| 15 |

93 |

| 7 |

118 |

| 16 |

87 |

n+n width

- Connected up entire pulser circuit to n+n FEEs

| FEE |

Width |

| 2 |

428 |

| 4 |

N/A |

| 6 |

428 |

| 8 |

343 |

Switching bias supply back

- because changes were made to the n+n ground, and the pulser circuit it was decided to go back and check the previous bias configuration with the module set in a floating configuration

- DAQ was then left overnight as had to leave to catch the bus

- Rates are observed to be back at their higher values - attachment 2

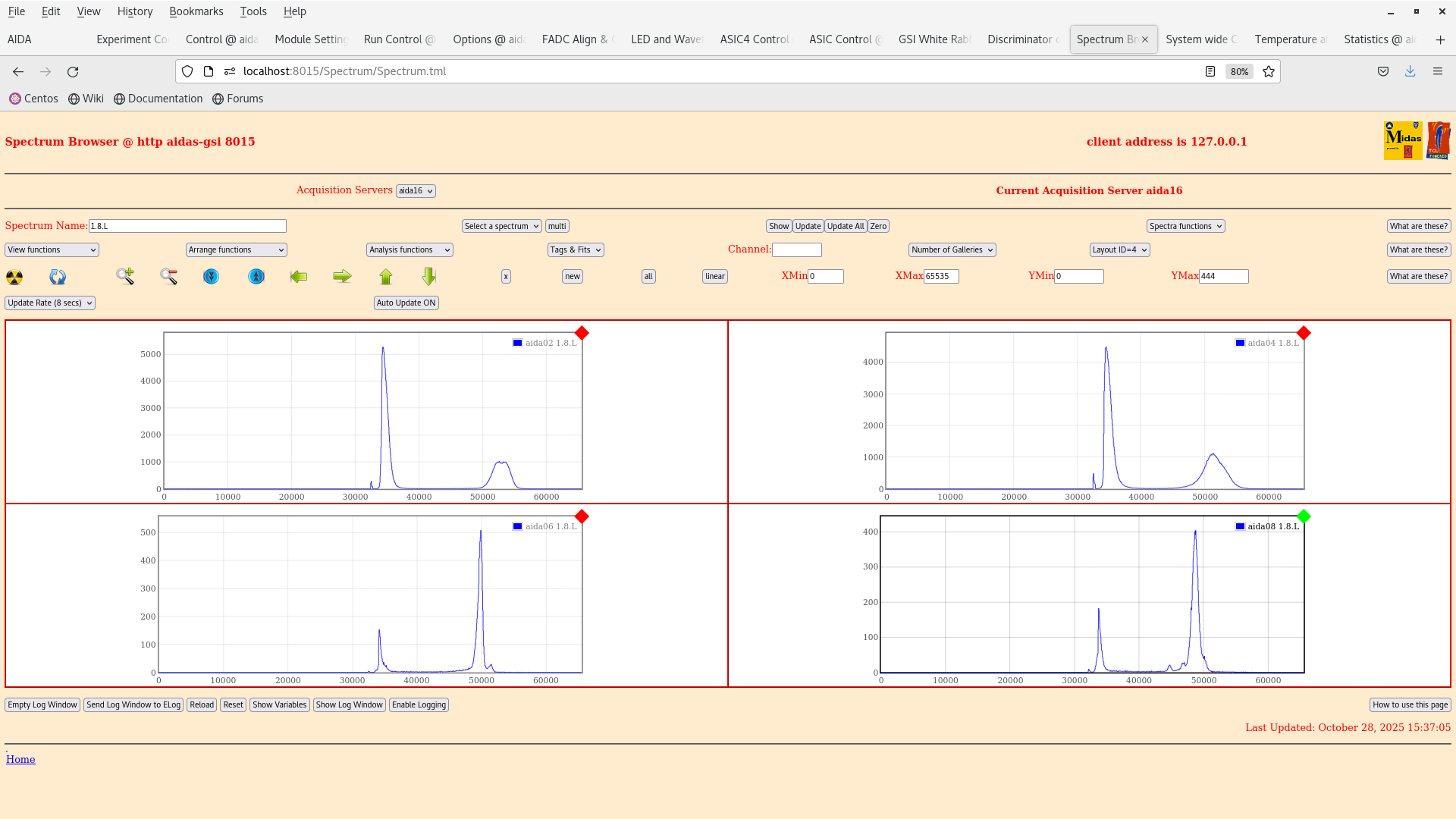

- n+n 1.8.L spectra - attachment 3

- p+n 1.8.L spectra - attachment 4

p+n widths

| FEE |

Wdith |

| 9 |

130 |

| 1 |

128 |

| 10 |

75 |

| 11 |

78 |

| 3 |

71 |

| 12 |

71 |

| 13 |

96 |

| 5 |

85 |

| 14 |

110 |

| 15 |

99 |

| 7 |

123 Dbl |

| 16 |

92 |

n+n widths

| FEE |

width |

| 2 |

56 |

| 4 |

983 |

| 6 |

523 |

| 8 |

358 |

- The results show no improvment to slightly worse performance so will go back to having the bias module grounded internally and check the previous conclusions hold before making further changes

Return to grounded bias module

Widths

p+n

| FEE |

Width |

| 9 |

106 |

| 1 |

79 |

| 10 |

72 |

| 11 |

78 |

| 3 |

70 |

| 12 |

73 |

| 13 |

102 |

| 5 |

112 |

| 14 |

105 |

| 15 |

110 |

| 7 |

131 |

| 16 |

104 |

n+n

| FEE |

Width |

| 2 |

- |

| 4 |

298 |

| 6- |

- |

| 8 |

278 |

- Don't see a pulser peak in 4 or 2

- Will replace cable between 4 and 2 and 2 and 6

- Statistics at 0x64 with pulser on - atachment 5

- Now see peaks - attachment 6

- Statistics at 0xa - attachment 7

| FEE |

Width |

| 2 |

284 |

| 4 |

1089 (Triple) |

| 6 |

371 |

| 8 |

318 |

With the grounded bias in place in the module move the braid cable to the frame rather than being connected to bias line

- Still observe a triple peak in 4 and have worse perfromance in 2 and no improvement in p+n

- 0x64 stats - attachment 7

- 0xa statistics - attachment 8

- p+n 1.8.L - attachment 9

- p+n waveform - attachment 10

- n+n waveform - attachment 11

- Same high frequency component in both

- 35 channel spacing corresponds to a frequency of ~1.4MHz

| FEE p+n |

Width |

| 9 |

109 |

| 1 |

118 |

| 10 |

78 |

| 11 |

80 |

| 3 |

70 |

| 12 |

73 |

| 13 |

92 |

| 5 |

85 |

| 14 |

99 |

| 15 |

100 |

| 7 |

123 |

| 16 |

92 |

| FEE n+n |

Width |

| 2 |

531 |

| 4 |

1185 (Triple) |

| 6 |

536 |

| 8 |

376 |

Next tests

- Returned braid to FEE 4 and 8

- Recovered earlier rates and performance

- Re-added the ground cable to the snout

- Much worse noise performance across all FEEs

- p+n rates in 200k

- Removed the ground from the snout

- Got really good rates originally - attachment 12

- Noticed 1 and 5 failed ADC calibration

- Calibrated them and there rates increased massively - attachment 13

- Notice that the pulser peak in FEE2 and 6 keeps dropping out

- As the cables have been changed multiple times thought it could be that an adaptor board was broken

- 4 seemed the most likely suspect with its high rates and triple peaks

- Replaced the adaptor board with one missing an outer ERNI pin (PIN doesn't interface with the FEE so didn't see any issues)

- Pulser peaks were still muissing

- Issue could be then with adaptor board 2 possibly

Conclusions

- Rates on the FEEs are in a better place now than they were at the start of the week

- p+n in particular have shown a large amount of improvement

- There are still however issues with the n+n FEEs

- I think there is likely an issue with one of the adaptor boards

- Possible aida02 at the pulser connection point

- Could explain the triple peaking in aida04 and the pulser issues with aida02 and aida06 dropping out.

- Would recomend swapping out aida02 as a test next week

- Other possible issues coiuld be the clingfilm around the cables has torn and we are grounding the cables to the inside of the snout

- Nic would like to use something other than clingfilm in future

- One suggestion would be mylar which could be held in place with strips of double sided tape

- This would make the cables less likely to stick to each other which is an issue with the tightness of the snout

- Could also try removing LK3 from FEE3 and 7 leaving the PCB ground floating

- I am at a slight loss of what else to try

- I have left the daq running at 0x64 overnight to check for alphas

- Histograms and statistics zeroed

|

| Attachment 1: 220304_1704_groundedbias_stats.png

|

|

| Attachment 2: 220305_1154_Stats.png

|

|

| Attachment 3: 220305_1157_nn_18L.png

|

|

| Attachment 4: 220305_1200_pn_18L.png

|

|

| Attachment 5: 220305_1336_0x64Stats.png

|

|

| Attachment 6: 220305_1341_nn_18L.png

|

|

| Attachment 7: 220305_1342_Stats.png

|

|

| Attachment 8: 220305_1405_0x64_stats.png

|

|

| Attachment 9: 220305_1421_pn_18L.png

|

|

| Attachment 10: 220305_1424_pn_waveform.png

|

|

| Attachment 11: 220305_1429_nn_waveform.png

|

|

| Attachment 12: 220305_1518_stats.png

|

|

| Attachment 13: 220305_1519_waveform_enabled.png

|

|

|

392

|

Fri Oct 29 23:00:04 2021 |

NH | Ground cable information |

For future refinement of the AIDA ground cables using copper bus bar or similar:

Thin cable (from AIDA FEEs to common connection point)

- AWG14 grn/ylw ground cable

- M6 screw crimp?

Thick cable (from common point to mechanical ground)

- AWG4 (25mm2) grn/ylw ground cable

- M12 bolt to mechanical frame |

|

729

|

Tue Oct 28 12:43:38 2025 |

JB, GB, MP, AM | Further setup of tests for 207Bi test |

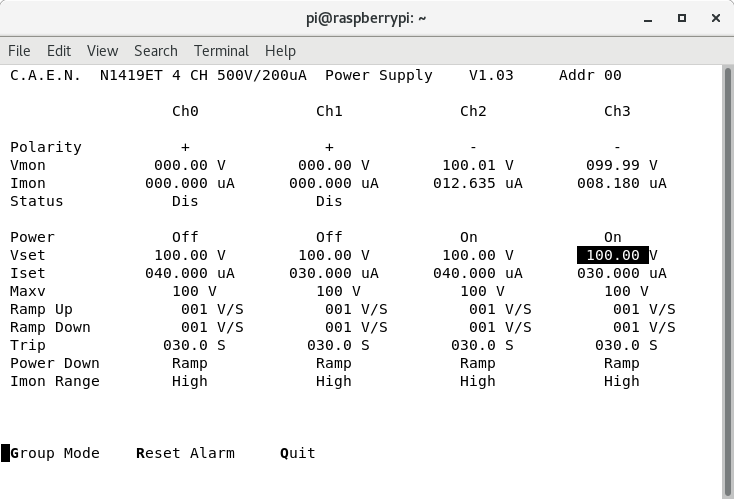

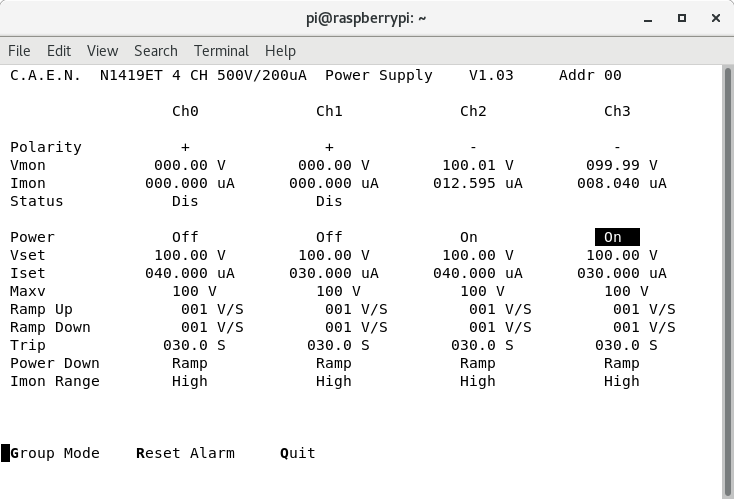

- Ch 2 and 3 of CAEN HV module changed to negative polarity, Ch 0,1 still with positive polarity

- Bias changed from the n+n to the p+n side (now Ch 2,3) - att. 1

- EXPERIMENTS/AIDA/2025Oct28-14.55.15 -> Slow comparitor -> 0x64 (1MeV) p+n Pos. bias & n+n Neg. bias

- Attachment 7: aida01 had its threshold lowered to 500 keV -> Rate increased from 500 to 6500 Hz

- Pulser inputs plugged in.

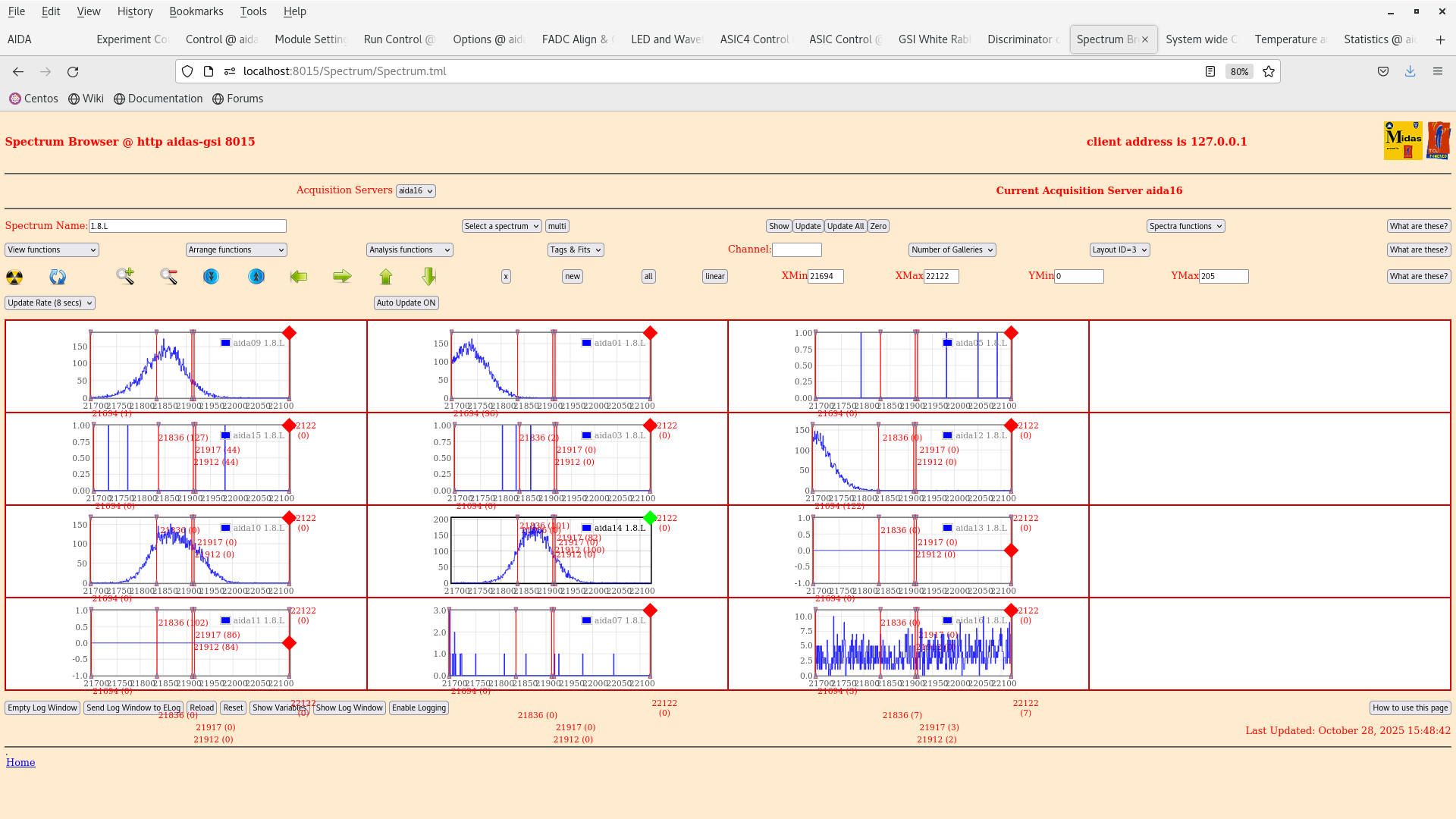

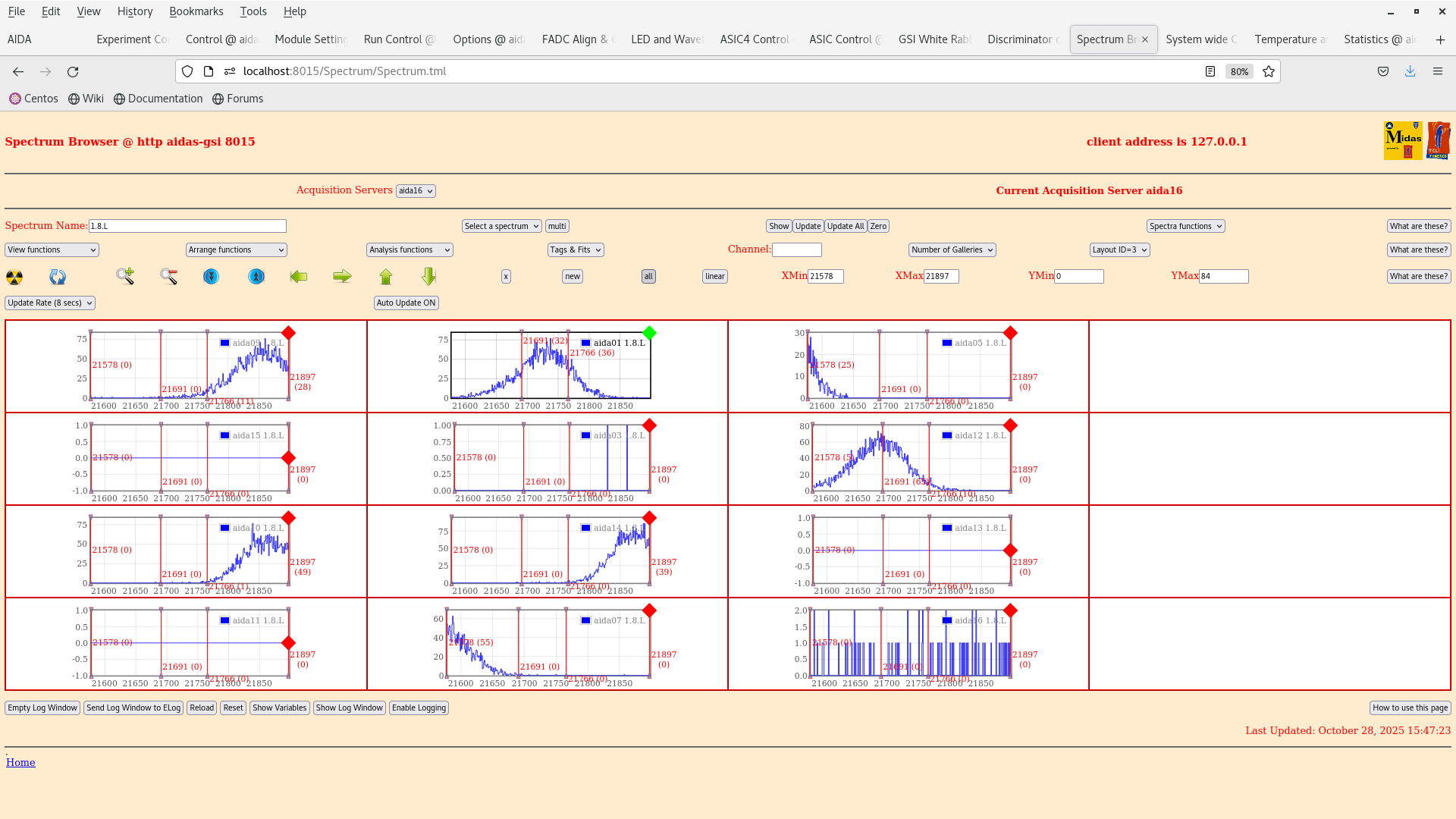

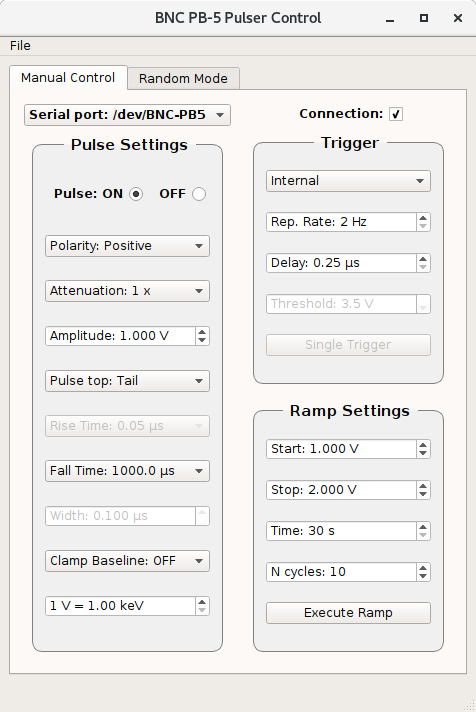

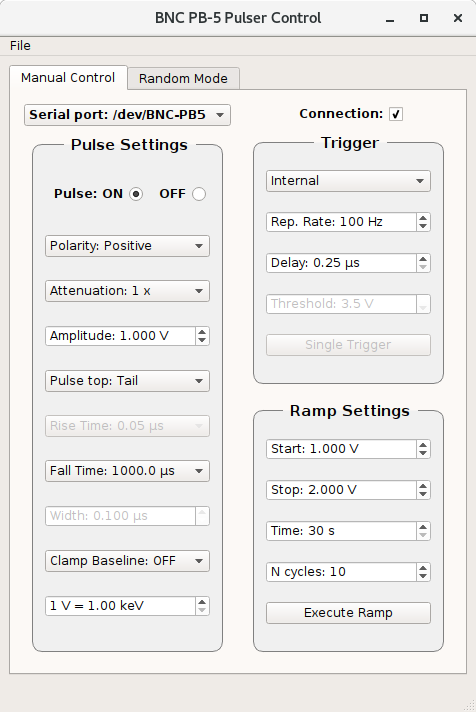

We have input a 1V pulser input into the data and have measured a peak in aida01 with a FWHM = 75 channel see attachment 9 and a FWHM in aida 14 (DSSD2) of also 76 channels which is similar to the results obtained in June from Nabil.

We cannot see anything from the n+n side as the signals are too noisy. Probably best to go with a higher trigger rate on the pulser and check with log scale tomorrow. It might also be worth checking the grounding on the y-strips as the problem with biasing with positive polarity is still seen in aida02 and aida04 (high noise repetition0 signal, attachment 2).

Conclusion is that we have reproduced in part the result from Nabil.

Tomorrow we will continue with the tests by lowering the thresholds and hopefully collect some data :-) |

| Attachment 1: Screenshot_from_2025-10-28_14-28-30.png

|

|

| Attachment 2: Screenshot_from_2025-10-28_15-12-27.png

|

|

| Attachment 3: Screenshot_from_2025-10-28_15-10-42.png

|

|

| Attachment 4: Screenshot_from_2025-10-28_15-09-59.png

|

|

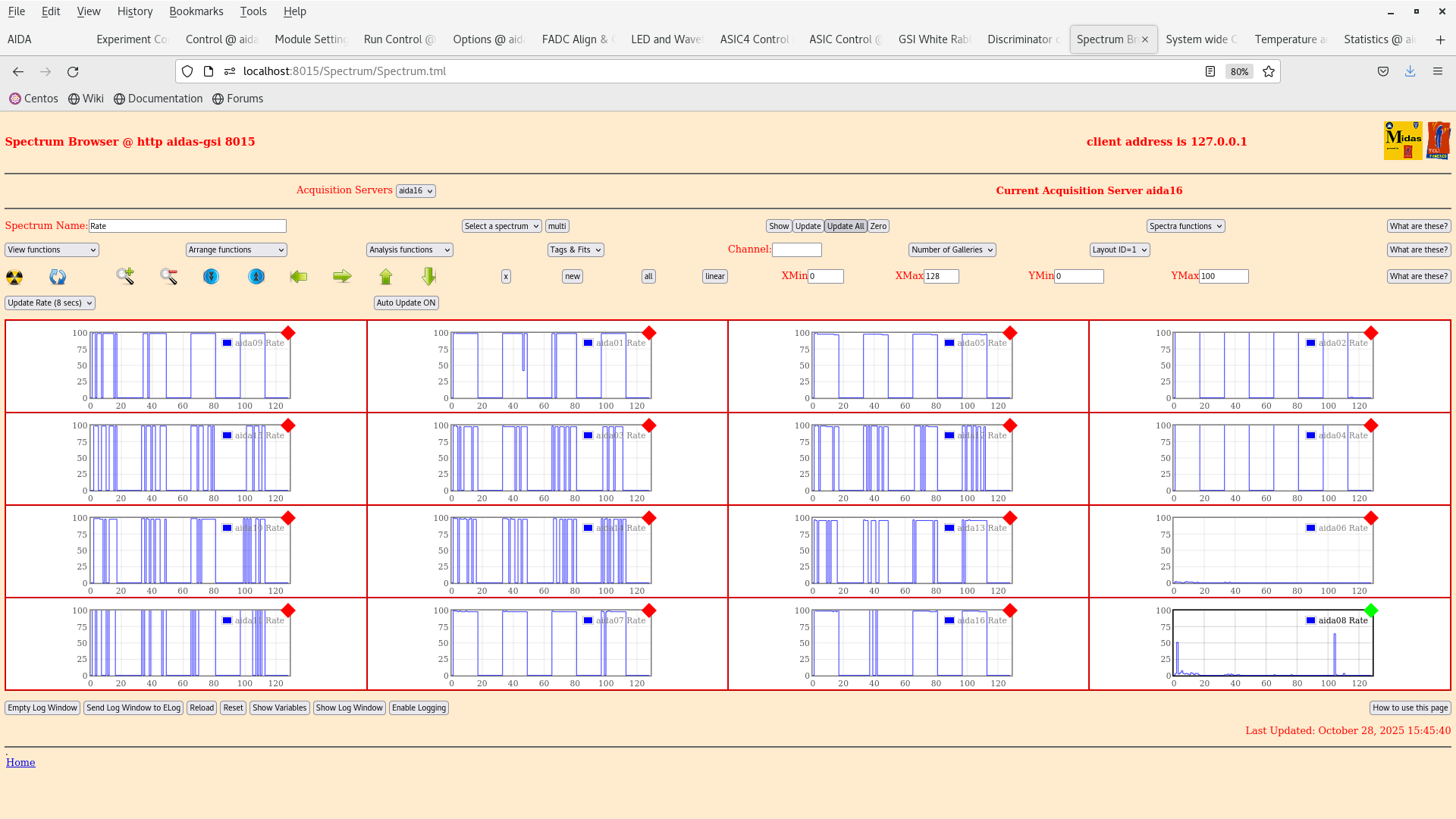

| Attachment 5: Screenshot_from_2025-10-28_15-08-24.png

|

|

| Attachment 6: Screenshot_from_2025-10-28_15-08-02.png

|

|

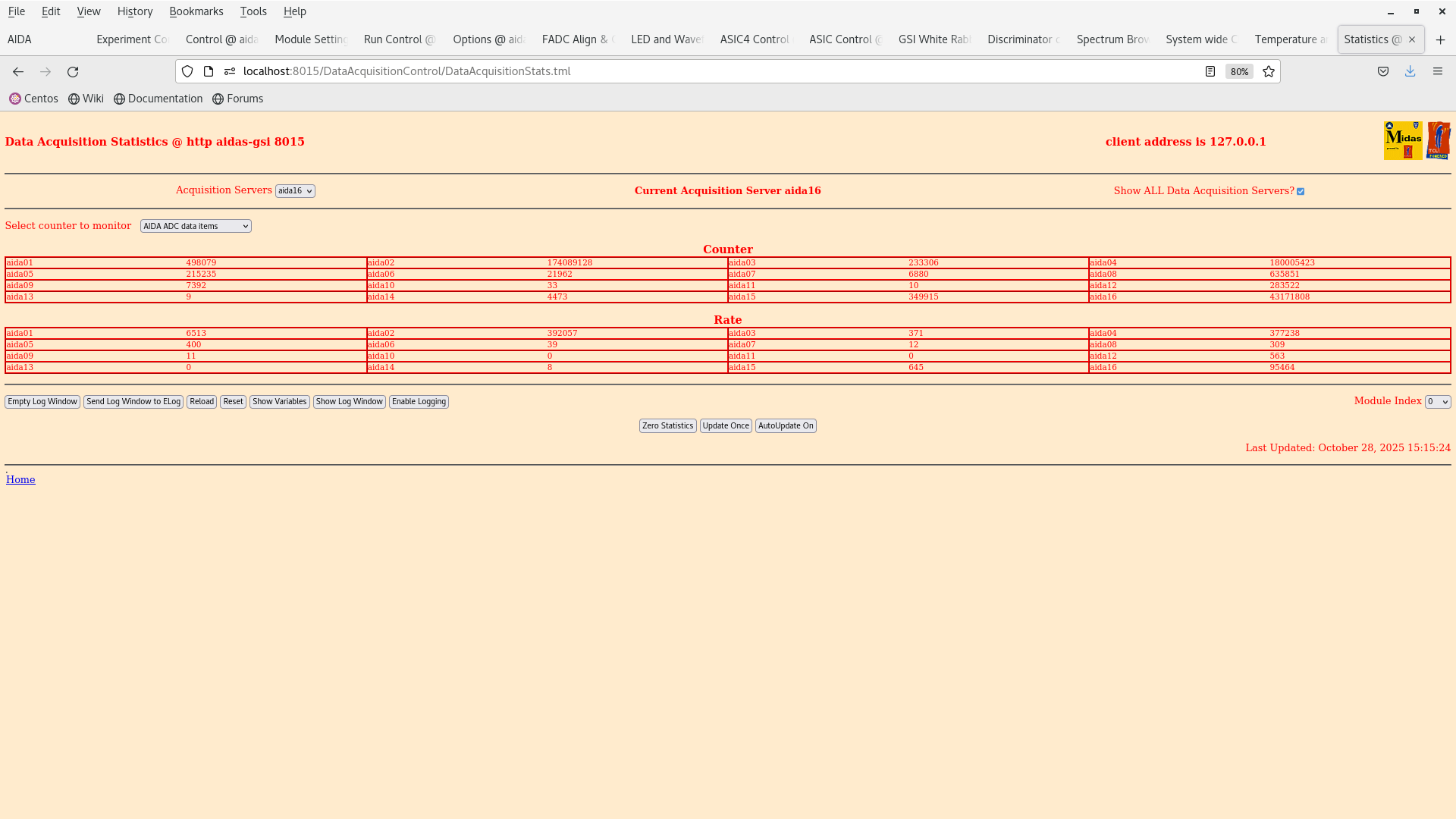

| Attachment 7: Screenshot_from_2025-10-28_15-15-31.png

|

|

| Attachment 8: Screenshot_from_2025-10-28_15-49-20.png

|

|

| Attachment 9: Screenshot_from_2025-10-28_15-47-44.png

|

|

| Attachment 10: Screenshot_from_2025-10-28_15-45-44.png

|

|

| Attachment 11: Screenshot_from_2025-10-28_15-37-13.png

|

|

| Attachment 12: Screenshot_from_2025-10-28_15-31-20.png

|

|

| Attachment 13: Screenshot_from_2025-10-28_15-50-19.png

|

|

| Attachment 14: AIDA_scheme_241020525(1).png

|

.png.png)

|

|

730

|

Wed Oct 29 08:12:35 2025 |

MP | Further setup for 207Bi test |

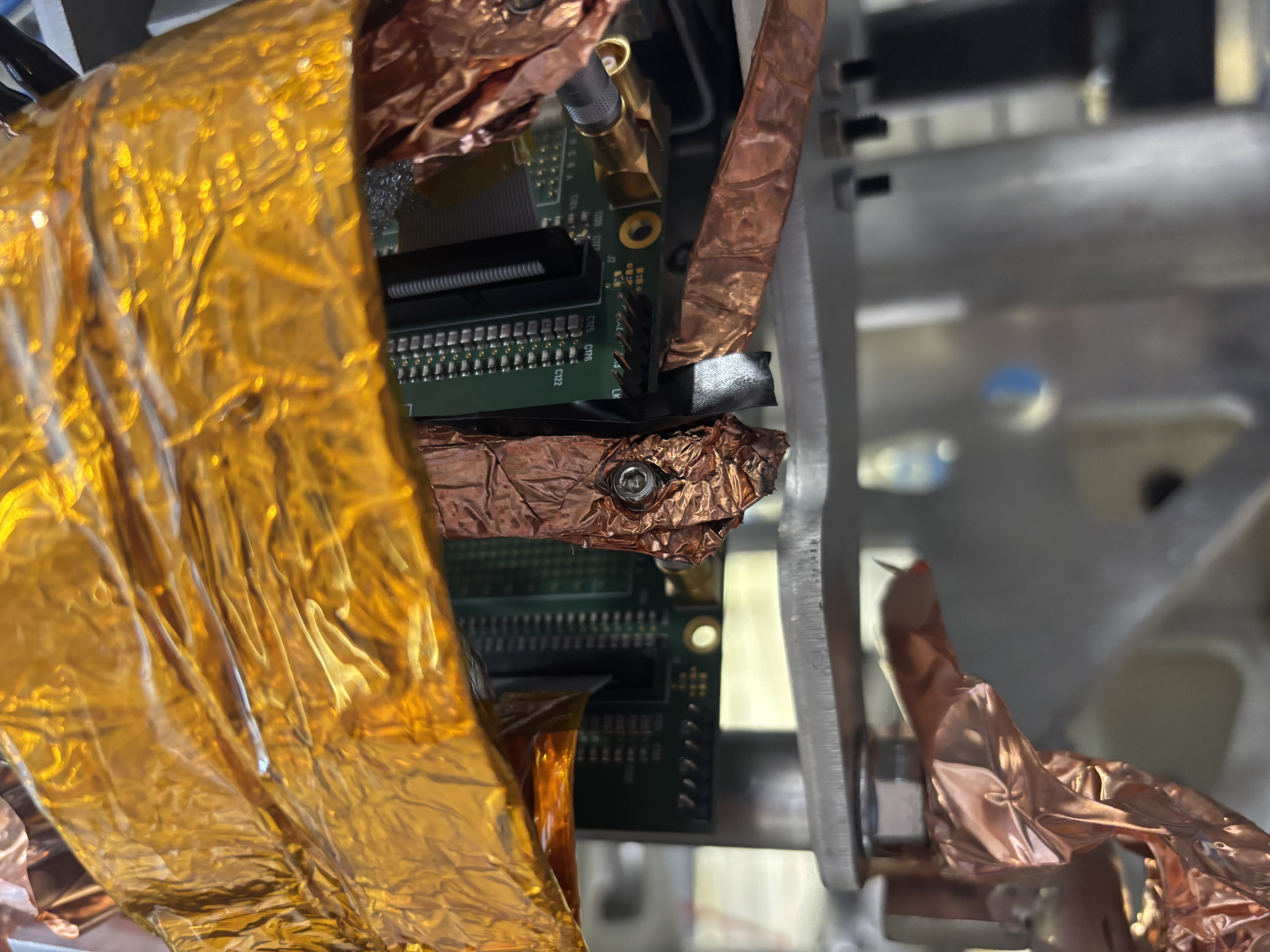

Inspection of side FEEs (2,6,4,8) and possible grounding improvements:

- all screws and nuts for copper connections were tightenedFee

- FEE 6 was isolated from the copper connection grounding FEE2 with insulating tape (attachment 1)

- A piece of tape was found below FEE6 (attachments 2,3) --> shall this be removed?

Bias and power on of FEES, preparation of two settings with lower thresholds:

- note: cannot calibrate ADC of aida15 even after trying multiple times (?)

- 500-keV thresholds settings saved as EXPERIMENTS/AIDA/2025Oct29-09.49.01

- 200-keV thresholds settings saved as EXPERIMENTS/AIDA/2025Oct29-09.55.31

|

| Attachment 1: IMG_5959.jpeg

|

|

| Attachment 2: IMG_5958.jpeg

|

|

| Attachment 3: IMG_5957.jpeg

|

|

| Attachment 4: Screenshot_from_2025-10-29_09-23-32.png

|

|

| Attachment 5: Screenshot_from_2025-10-29_09-32-52.png

|

|

|

731

|

Wed Oct 29 12:56:29 2025 |

TD | Further setup for 207Bi test |

Remember that 'ADC calibration' refers to the setup of the fast serial output of the AD9222 Octal, 50MSPS, 14 bit ADC which generates the waveforms - if the FEE64 is unable to calibrate all that happens is that you will not be able to see preamp output waveforms. Energy spectra will work regardless as they use a different ADC.

| Quote: |

|

Inspection of side FEEs (2,6,4,8) and possible grounding improvements:

- all screws and nuts for copper connections were tightenedFee

- FEE 6 was isolated from the copper connection grounding FEE2 with insulating tape (attachment 1)

- A piece of tape was found below FEE6 (attachments 2,3) --> shall this be removed?

Bias and power on of FEES, preparation of two settings with lower thresholds:

- note: cannot calibrate ADC of aida15 even after trying multiple times (?)

- 500-keV thresholds settings saved as EXPERIMENTS/AIDA/2025Oct29-09.49.01

- 200-keV thresholds settings saved as EXPERIMENTS/AIDA/2025Oct29-09.55.31

|

|