|

|

|

AIDA

GELINA

BRIKEN

nToF

CRIB

ISOLDE

CIRCE

nTOFCapture

DESPEC

DTAS

EDI_PSA

179Ta

CARME

StellarModelling

DCF

K40

|

| AIDA |

|

|

|

|

Message ID: 419

Entry time: Thu Nov 3 17:42:37 2016

|

| Author: |

TD, CG, DK |

| Subject: |

Friday 4 November |

|

|

00.40-02.30 Discussion with PJCS

Confirm both NIM bin voltages OK

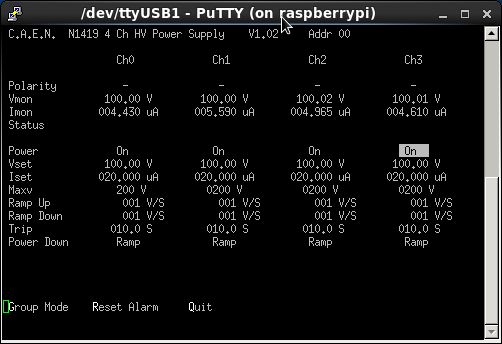

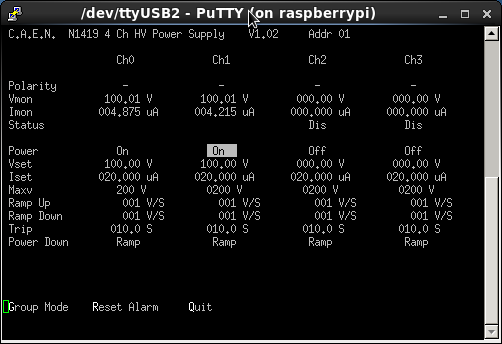

Move master MACB to lower NIM bin (with BNC PB_4, Ortec 433, 2x CAEN N1419B, 1x CAEN N1419)

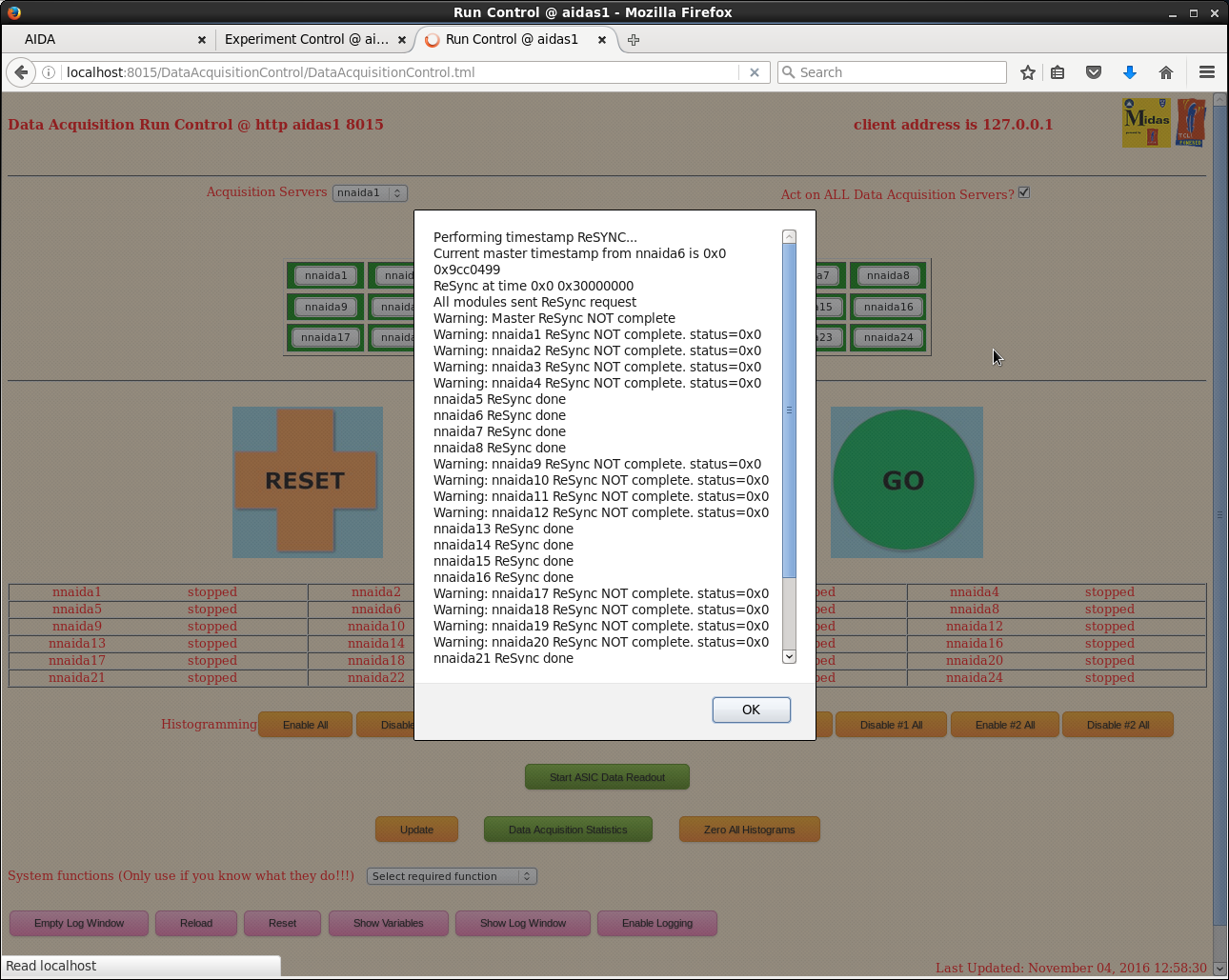

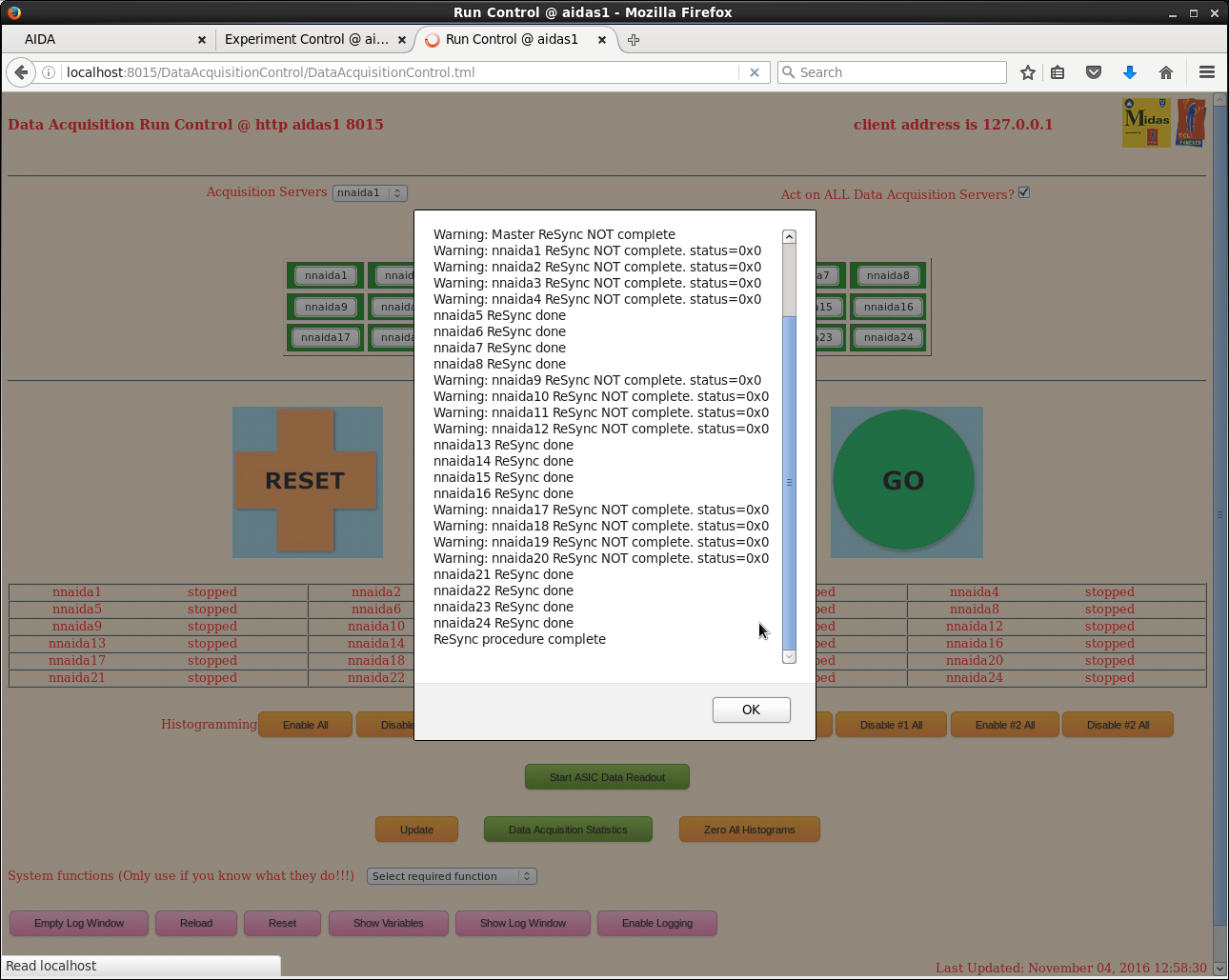

successful ReSYNC

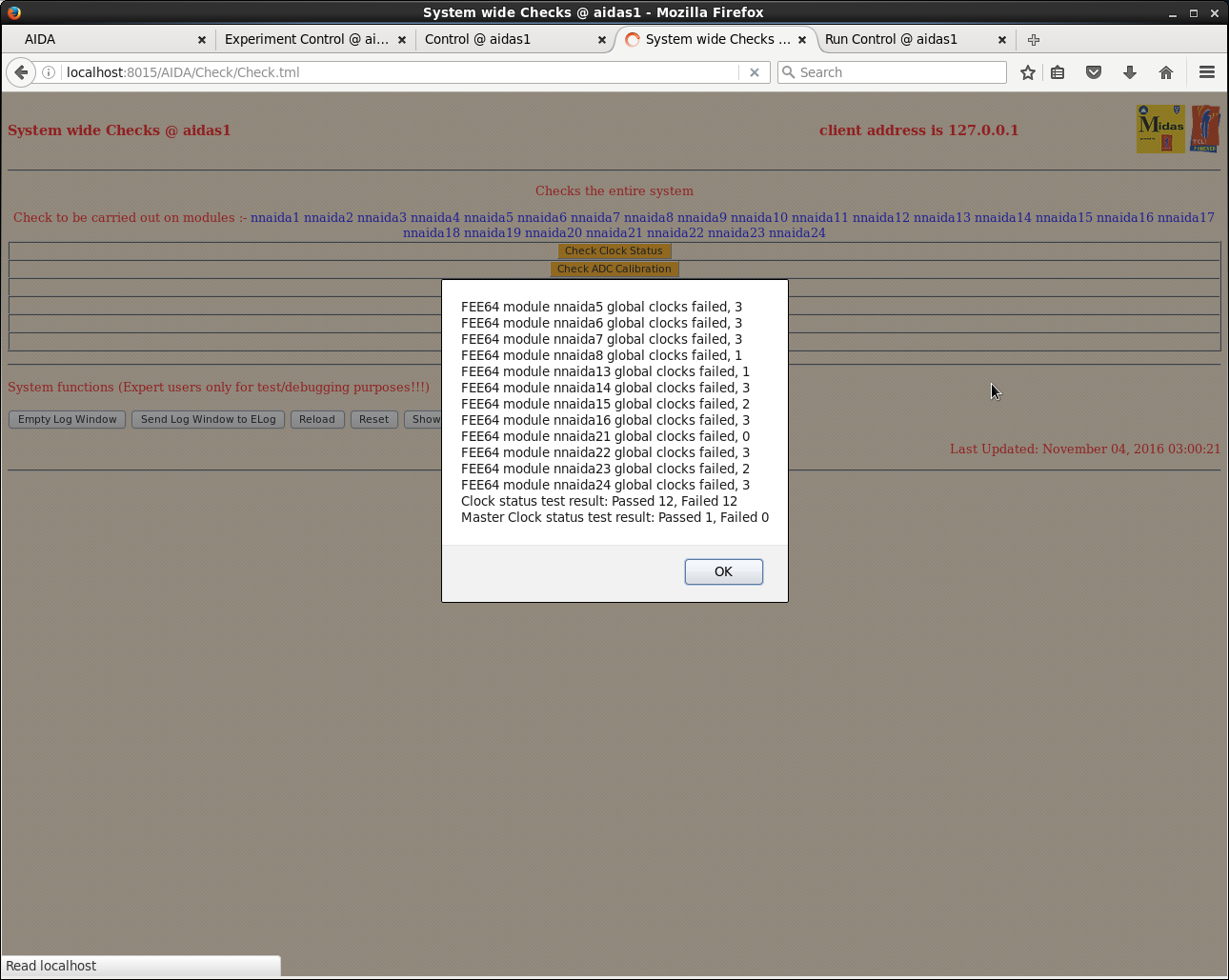

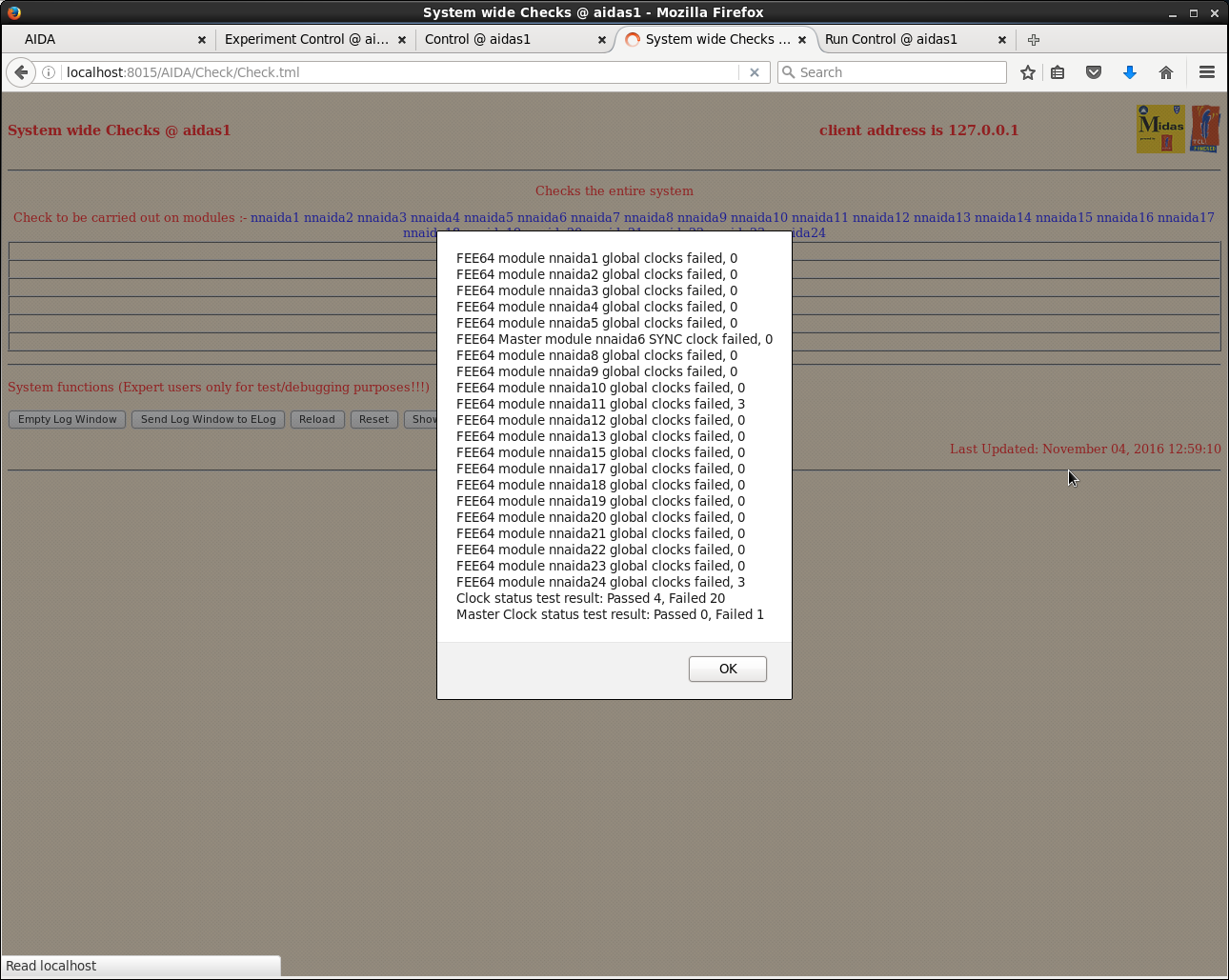

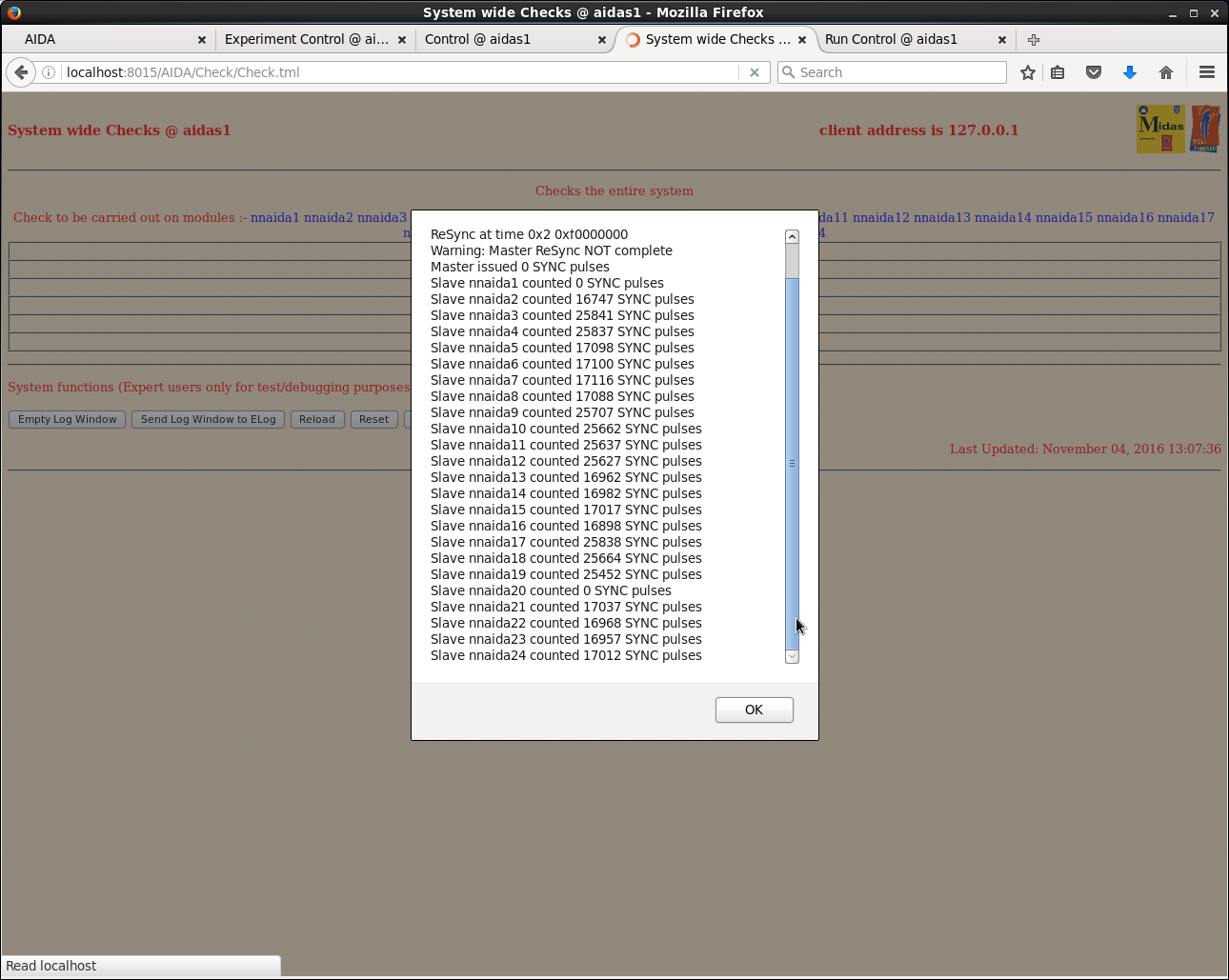

system-wide checks clock test fails from zero to all of the following FEE64s - nnaida7, 8, 15 & 16

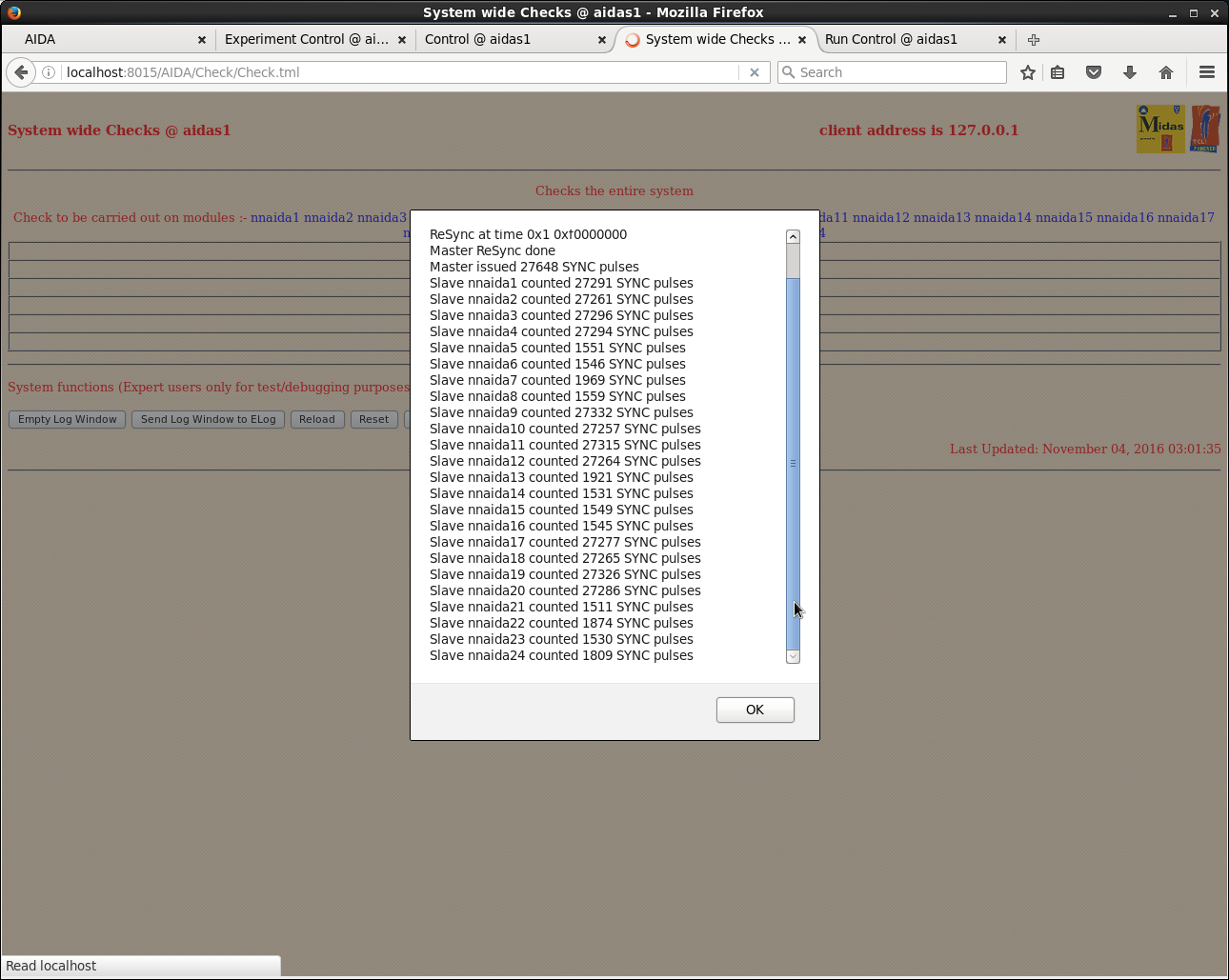

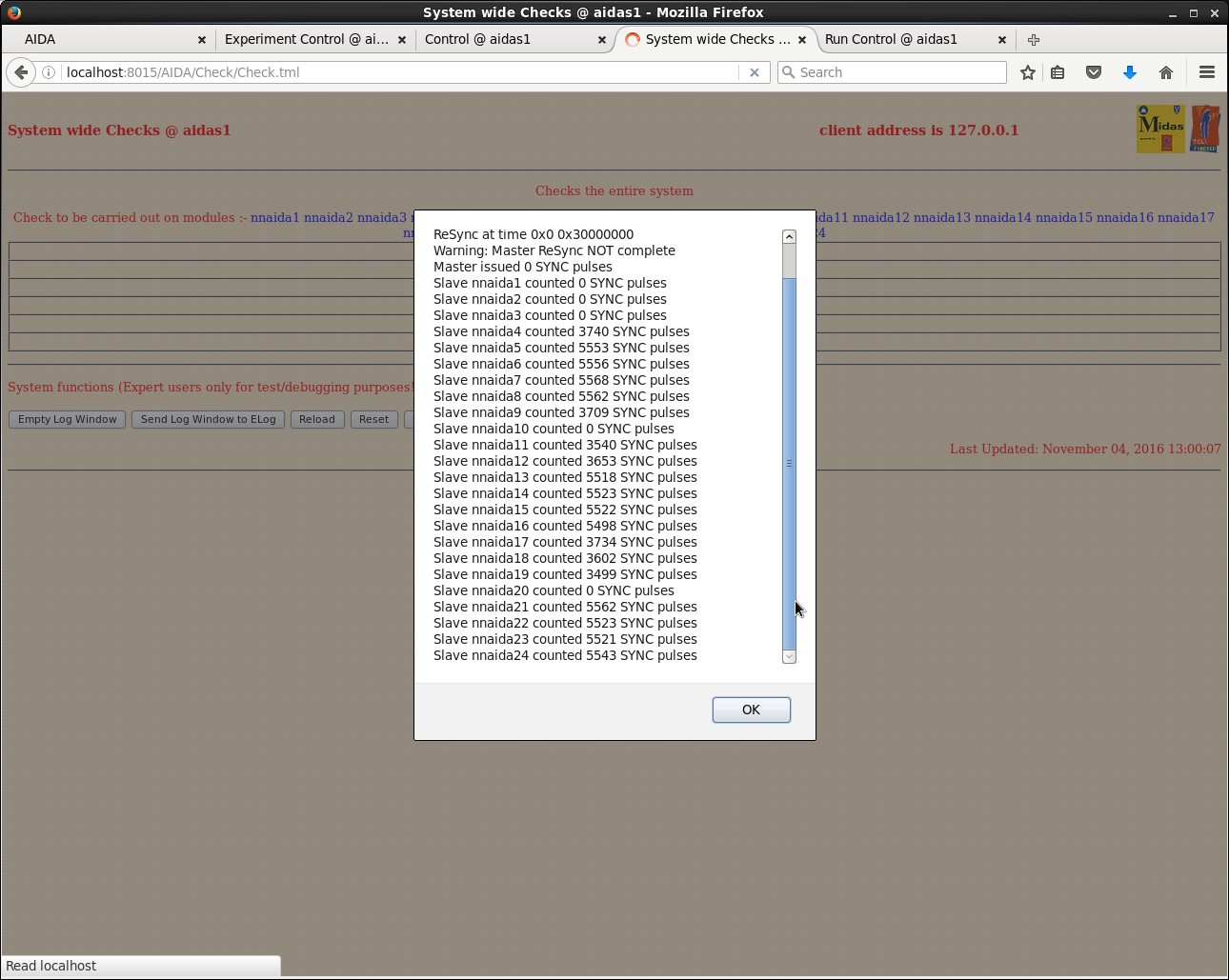

SYNC count test OK *except* nnaida19 which has greater number of SYNC pulses

online analysis indicates nnaida19 ADC data not synchronised with other FEE64s by ~200ms

Replace master MACB rev B mode 0 with MACB module #13 mode 5 (external clock 50MHz TTL)

Move MACB module 2 from upper NIM bin to lower NIM bin

Swap nnaida19/port1 <-> nnaida20/port2

Power cycle FEE64s and restart

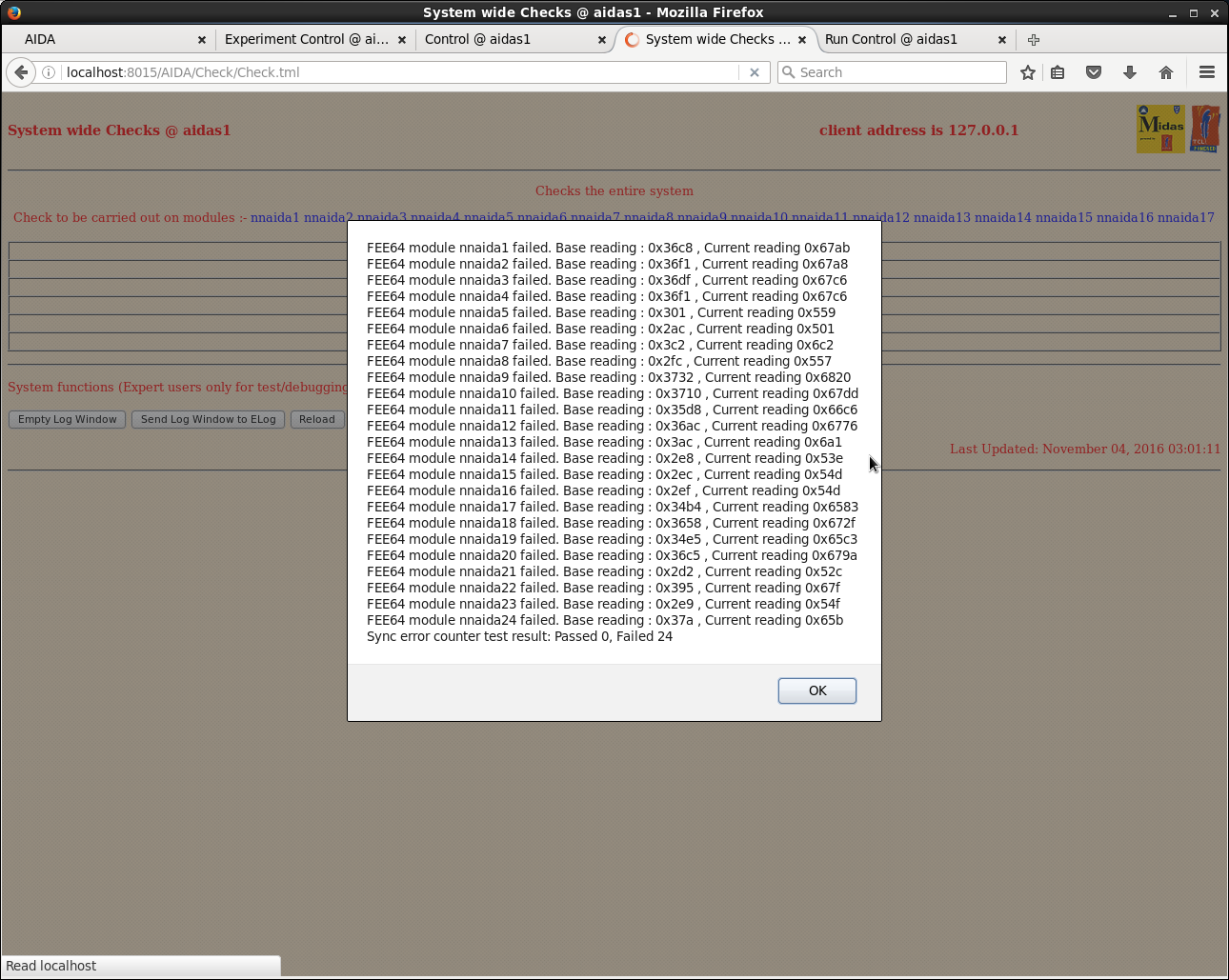

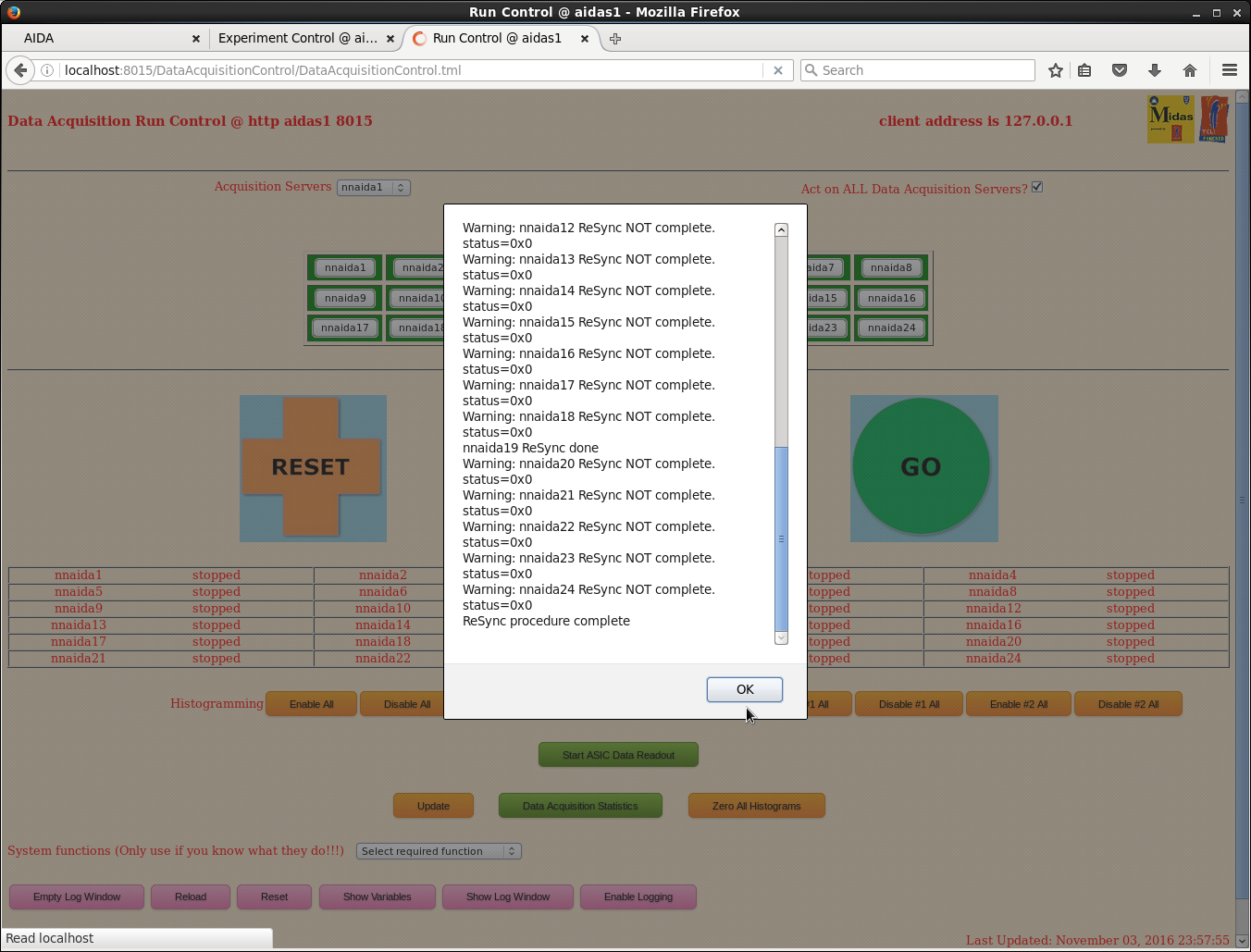

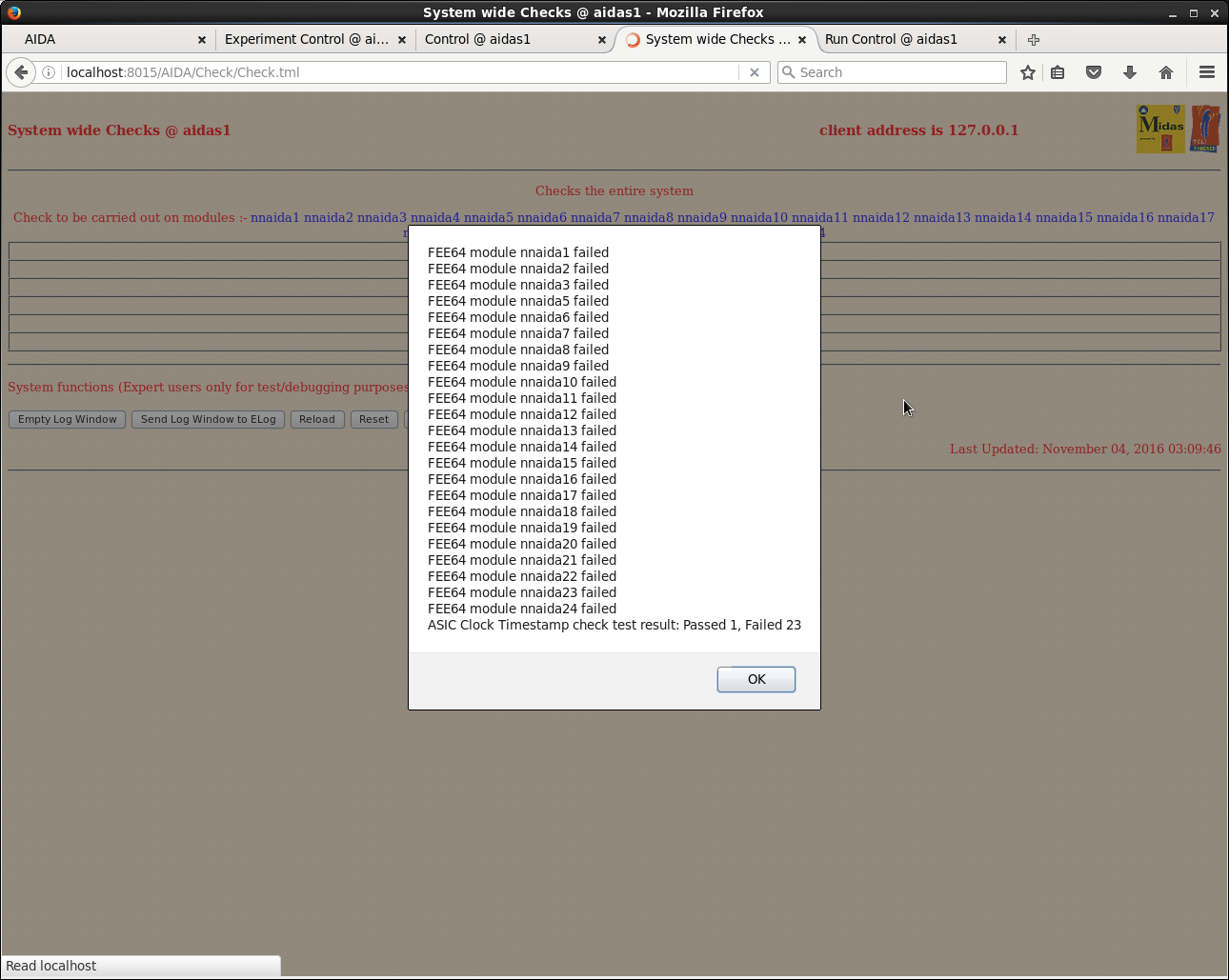

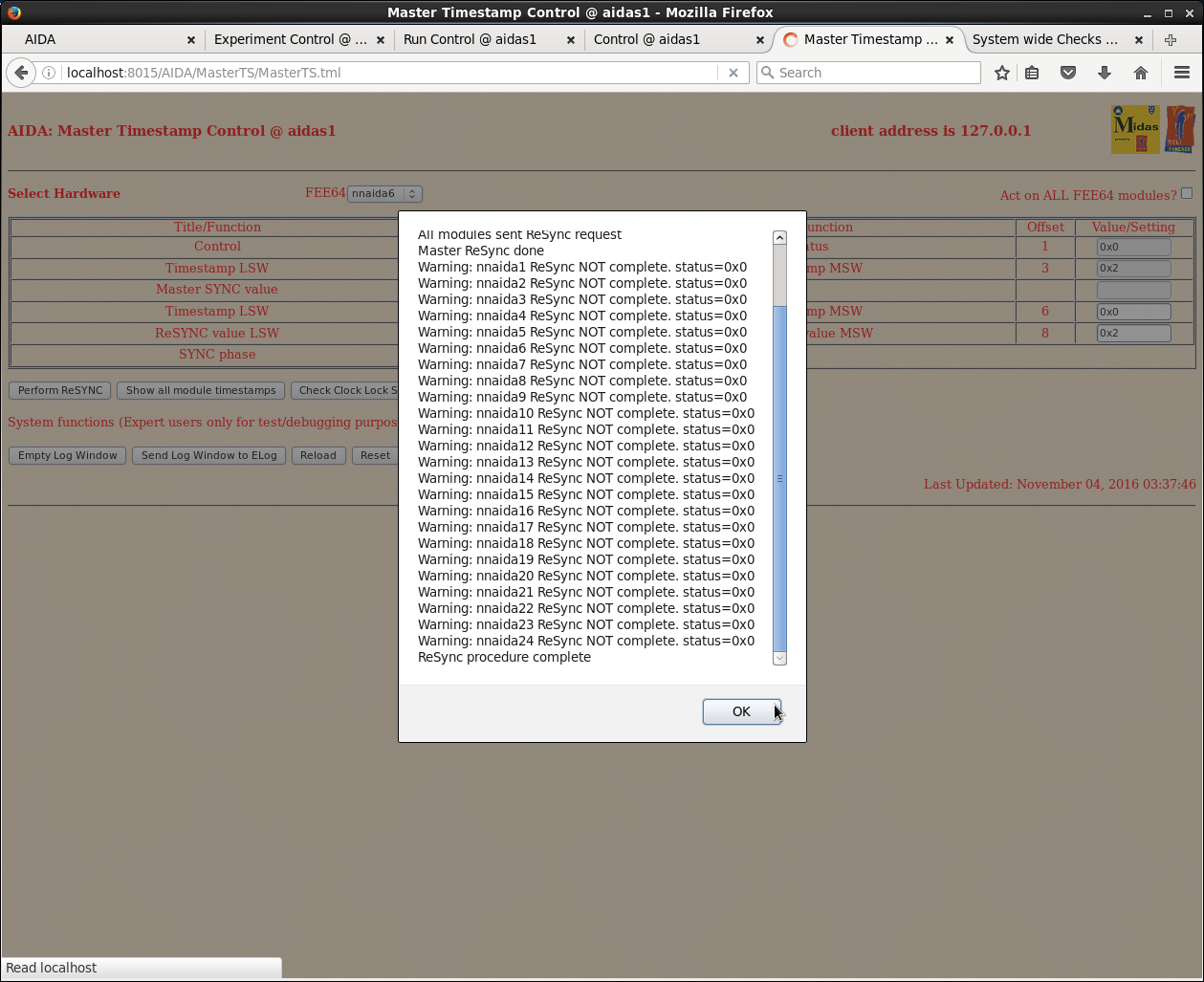

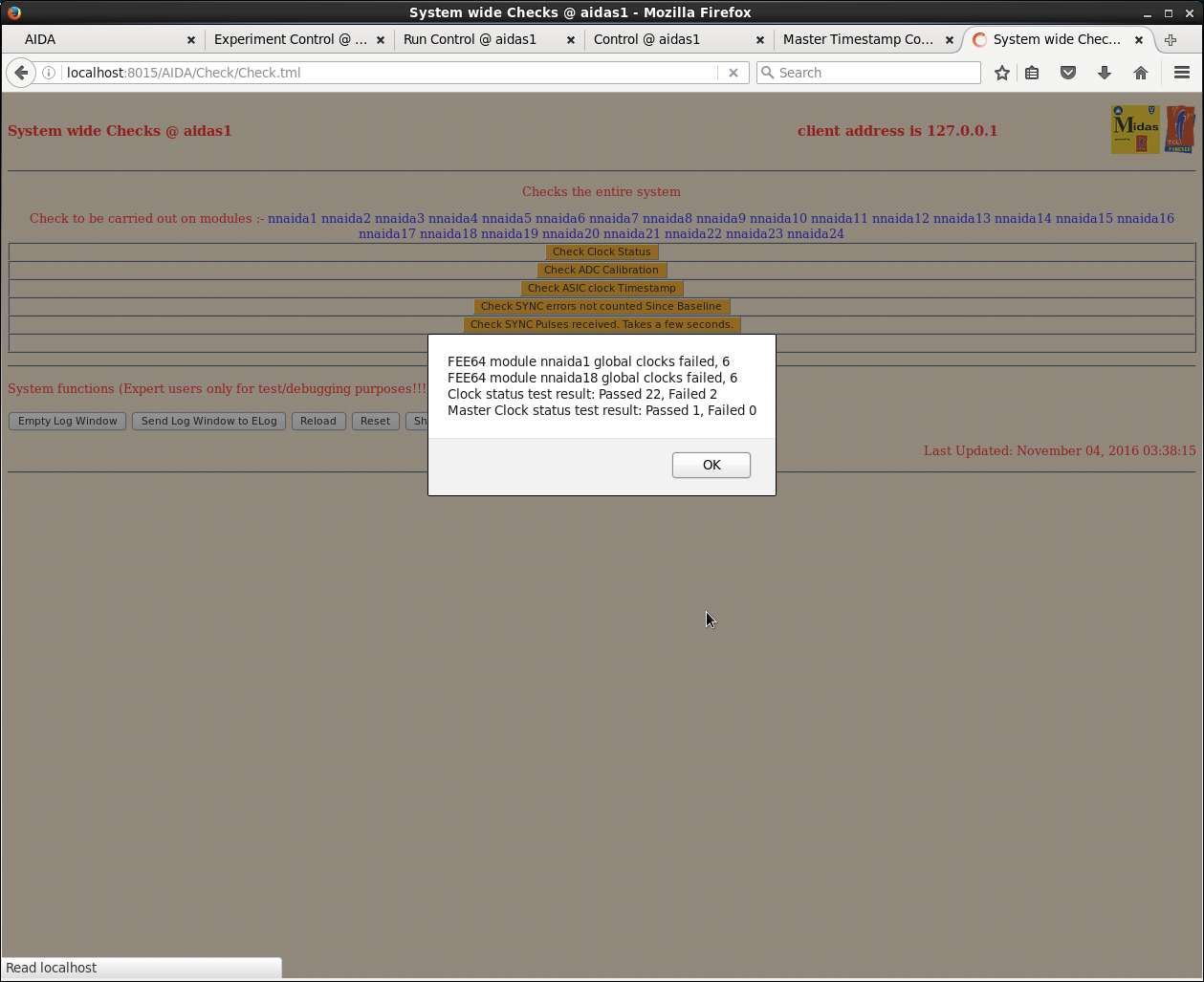

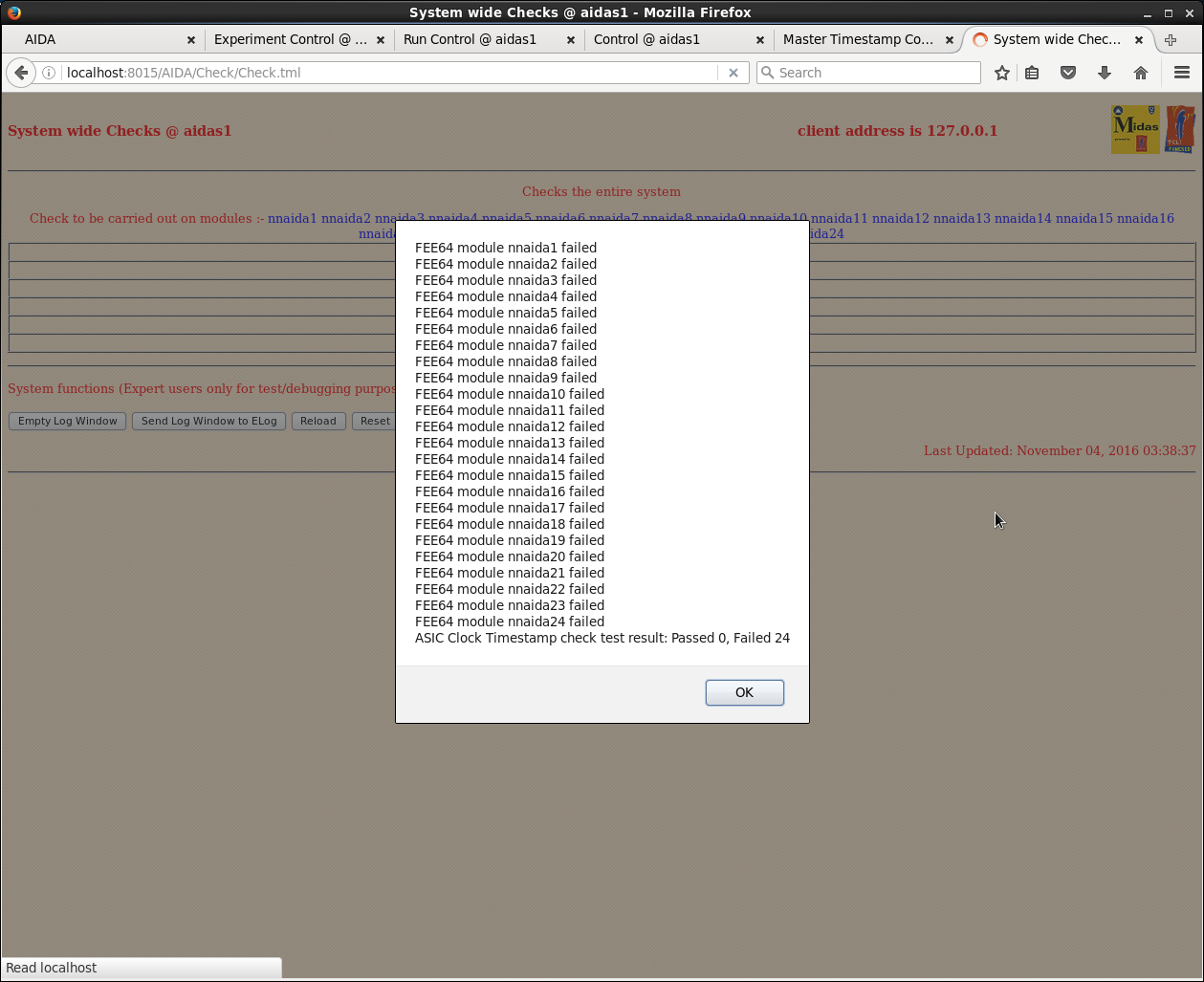

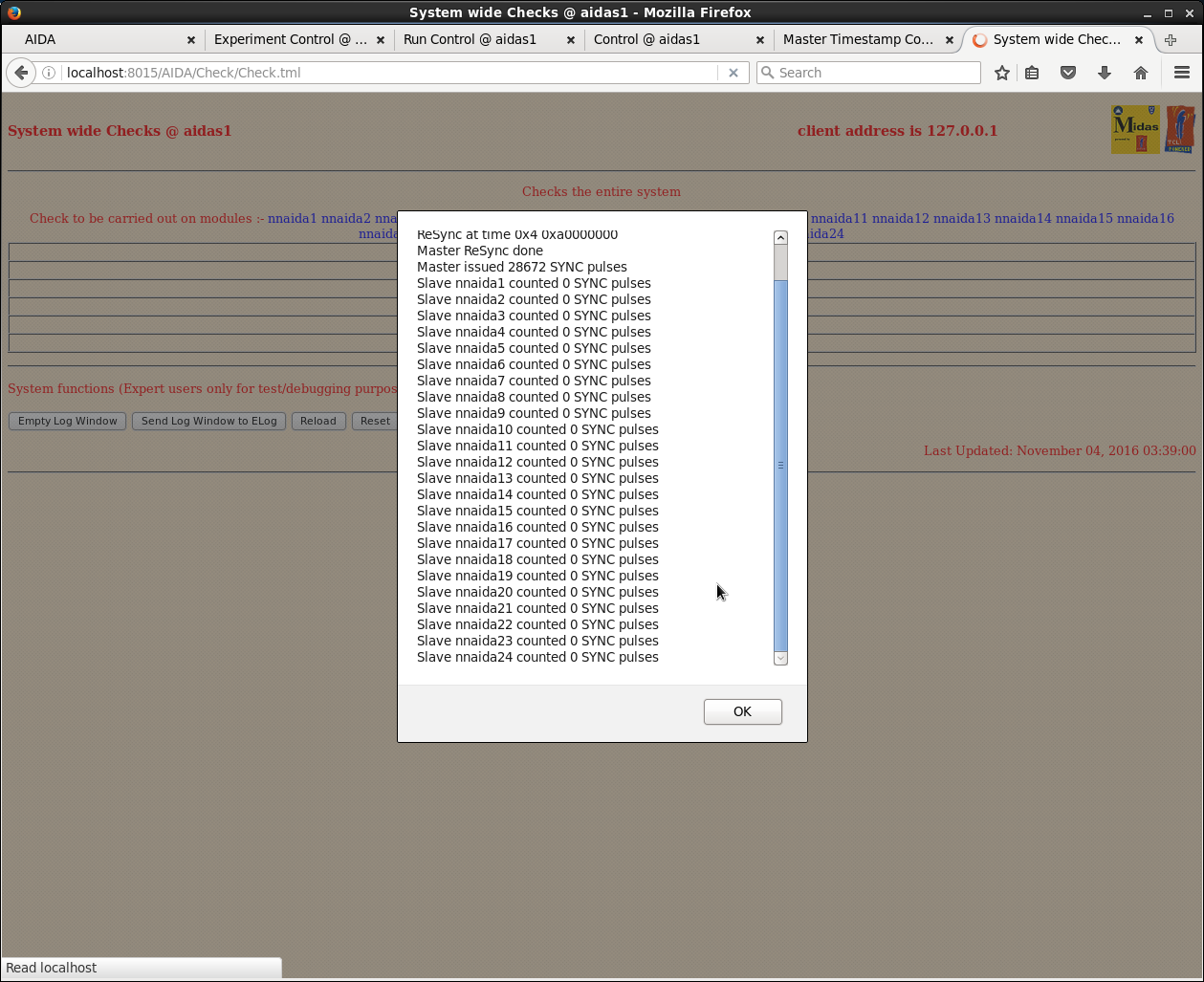

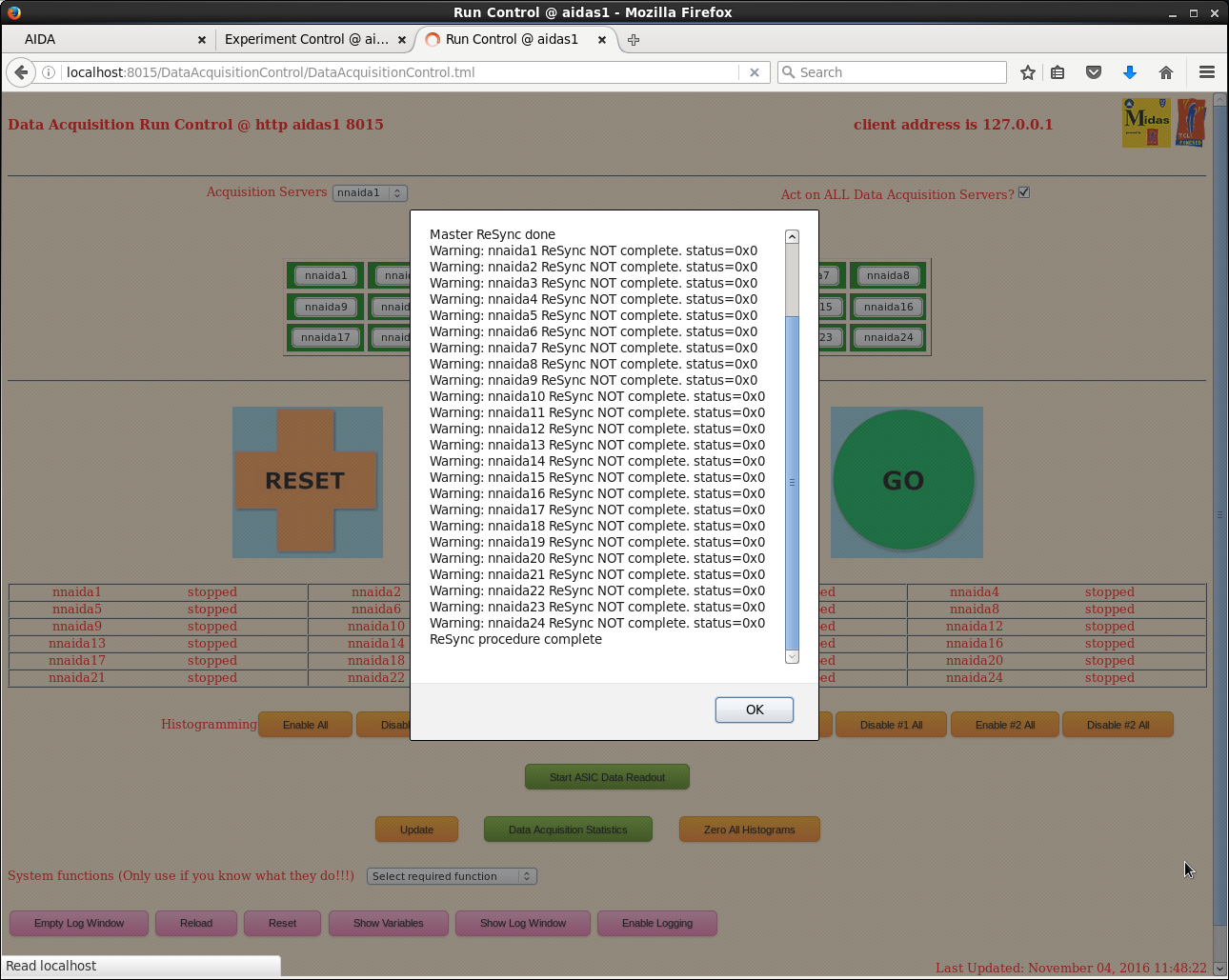

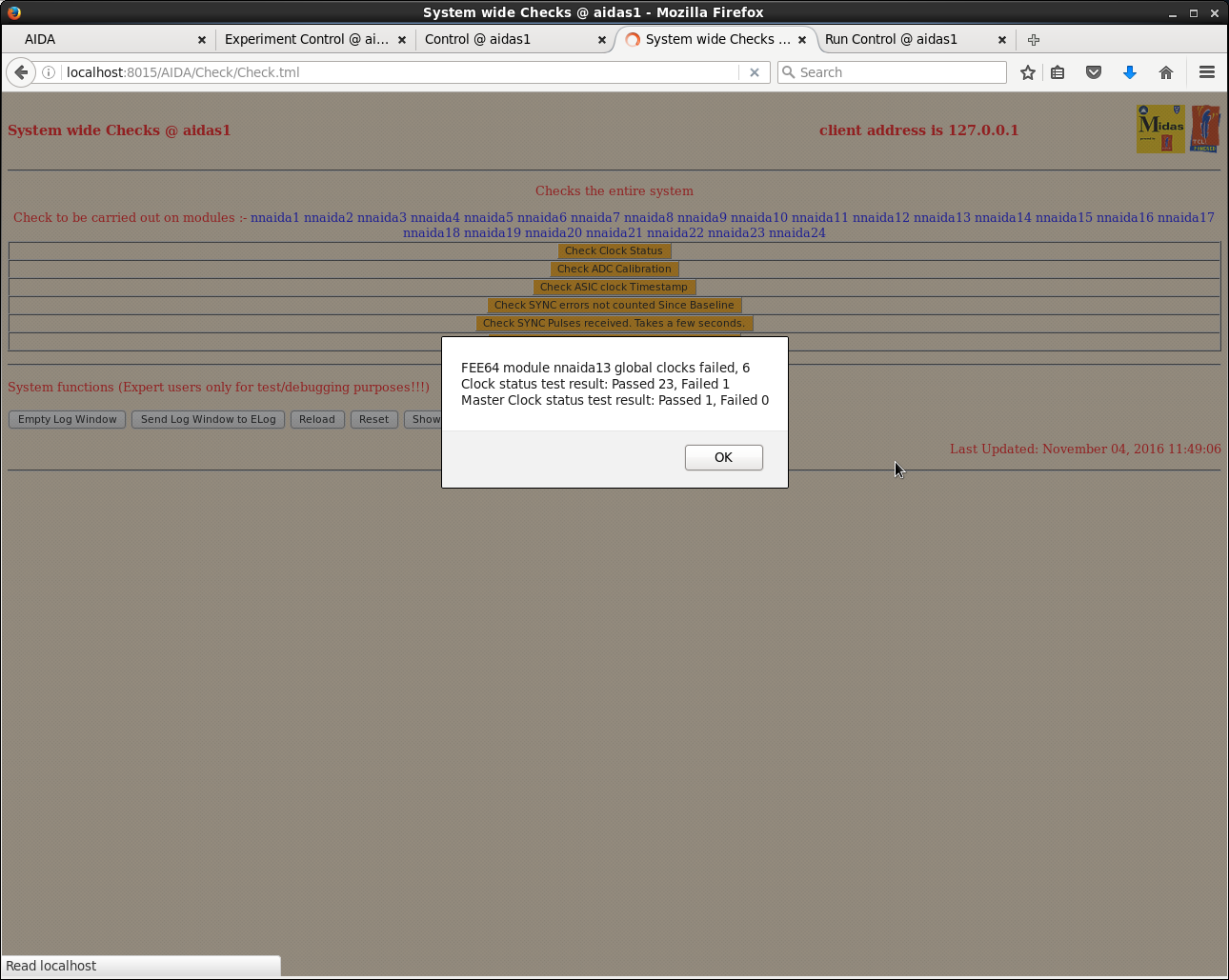

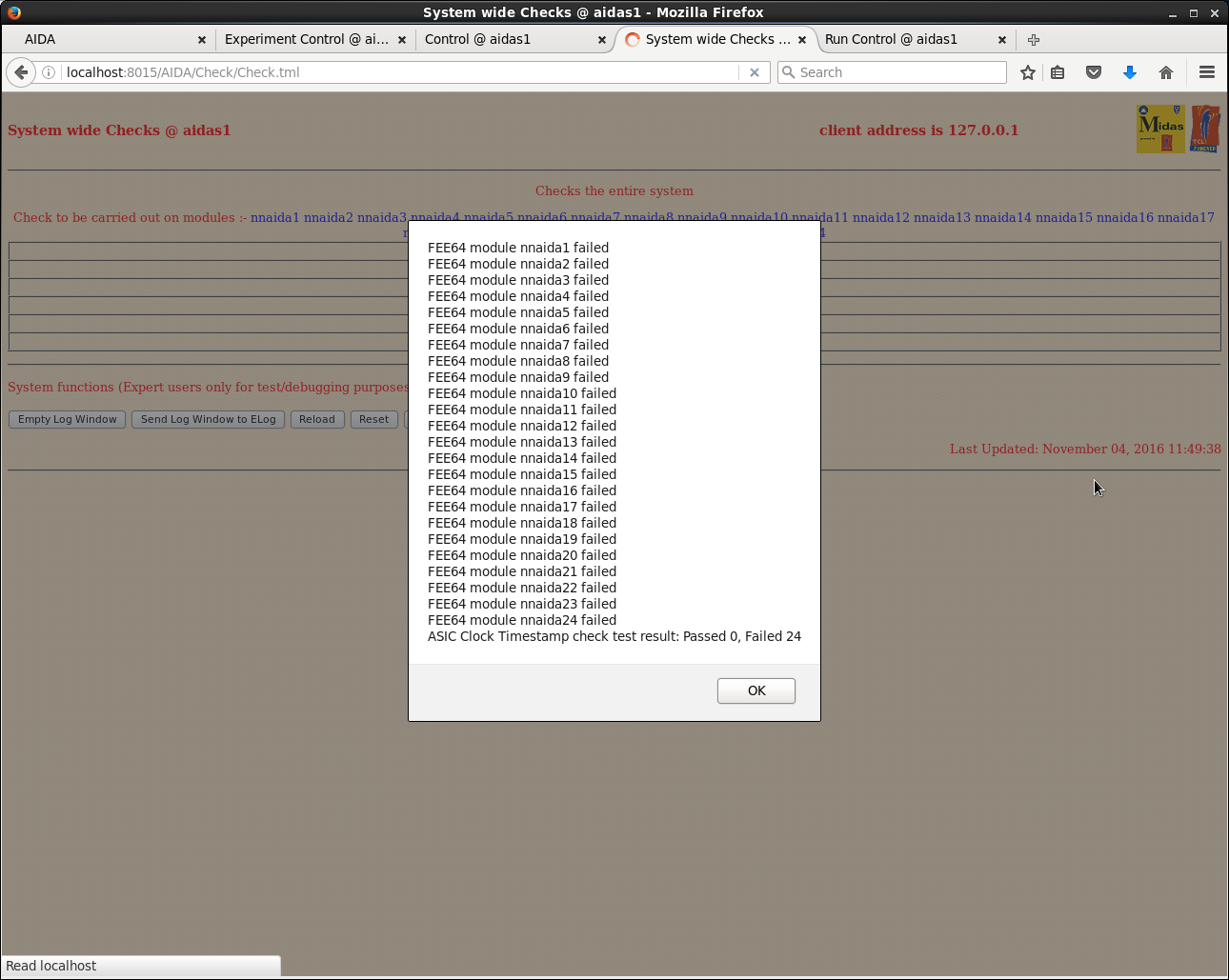

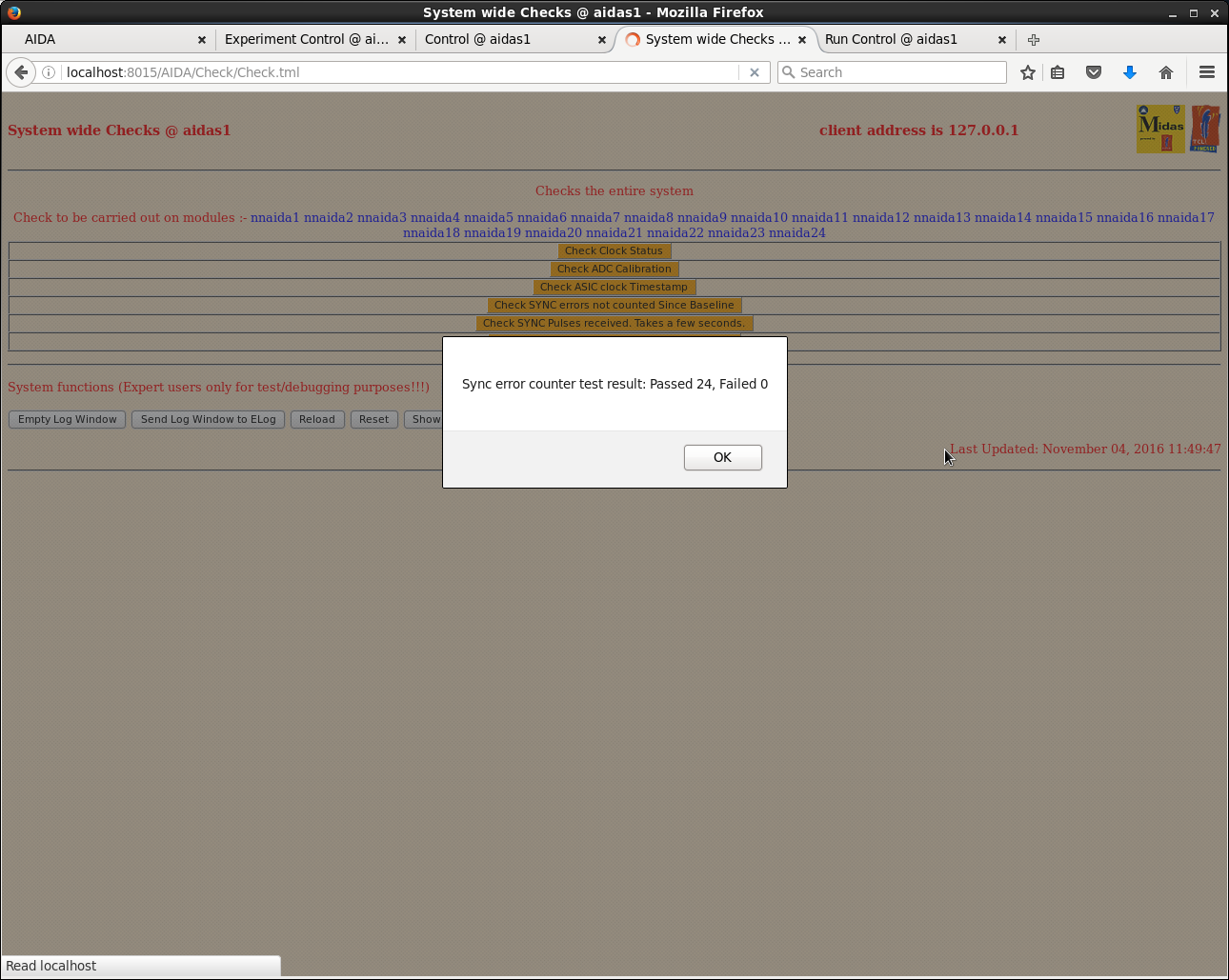

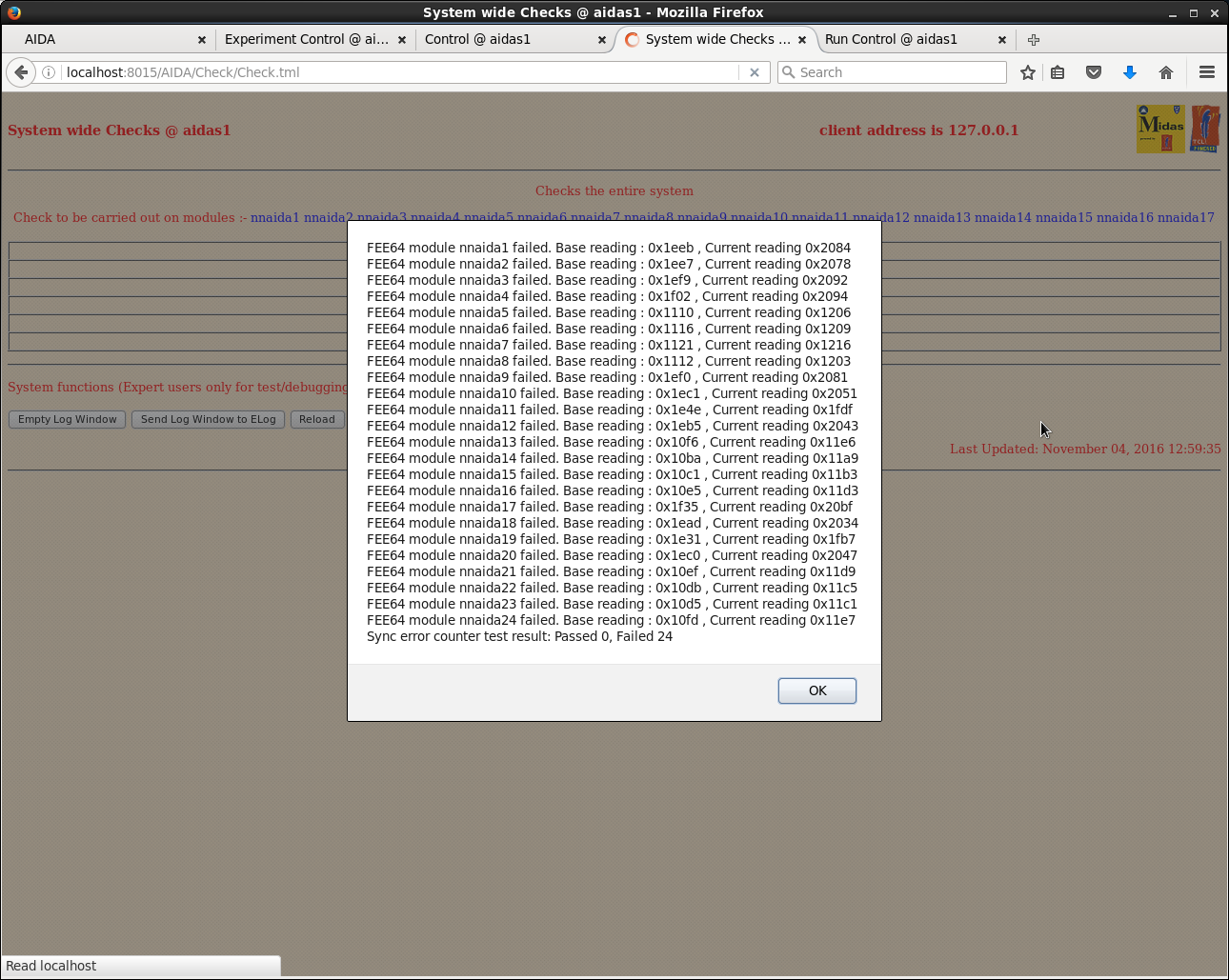

System wide checks fail - see attachments 1-4

Re-seat HDMI cabling master MACB -> MACB modules 3-6

System wide checks fail - see attachments 7-10

Swap ports of 2x HDMI cables from master MACB

Power cycle FEE64s

Re_SYNC & system wide checks fail - see attachments 11-15

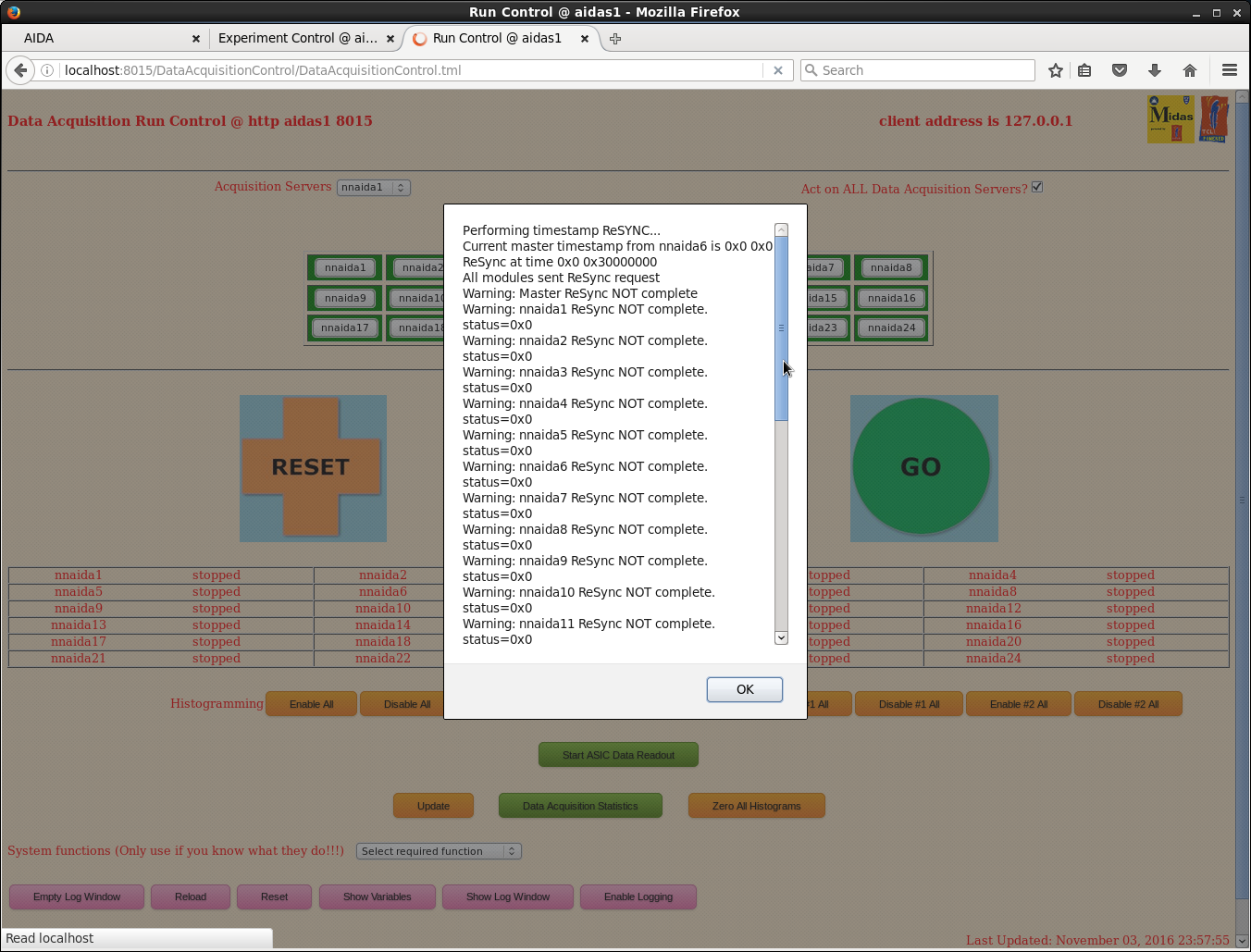

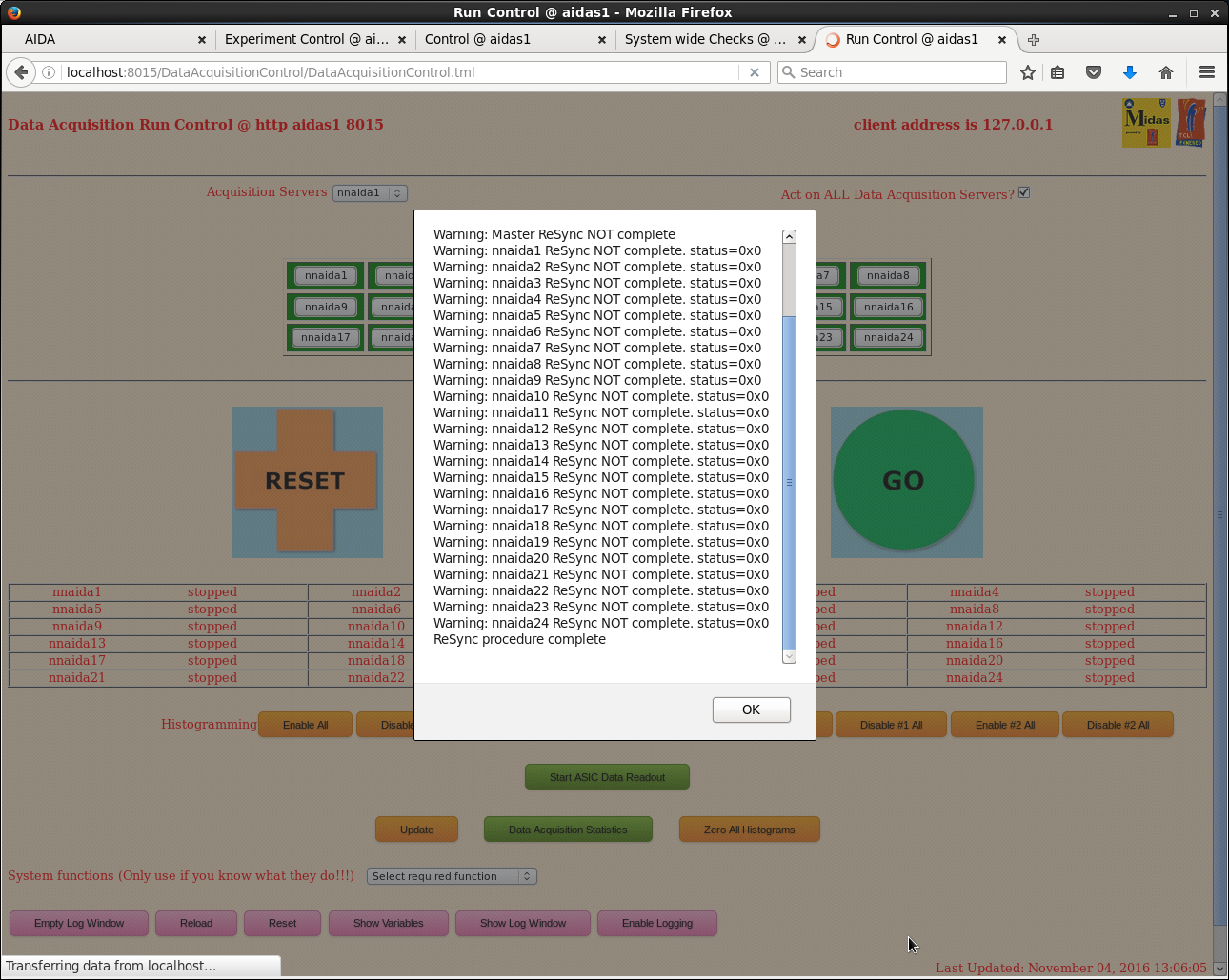

10.20 ReSYNC fails for all TS_SYNC_PHASE settings 0-3

DK checks MACB mode settings

master -> 5

module #2 2

module #3 2

modules #4-11 3

Check HDMI cable seating nnaida6 to master MACB

No change - ReSYNC fails, system wide checks fail as before

Per PJCS e-mail check MACB settings per https://elog.ph.ed.ac.uk/AIDA/258

and change MACB module # 7 from mode 3 to mode 2. MACB settings are now

MACB # 1 2 3 4 5 6 7 8 9 10 11 spare 1 spare 2

Mode 5 2 3 3 3 3 2 3 3 3 3

Rev B y y 50MHz? y

*BUT* remember the system has been in the previous state since Elog 258

abd has been working OK

No change - ReSYNC fails, system wide checks fail as before

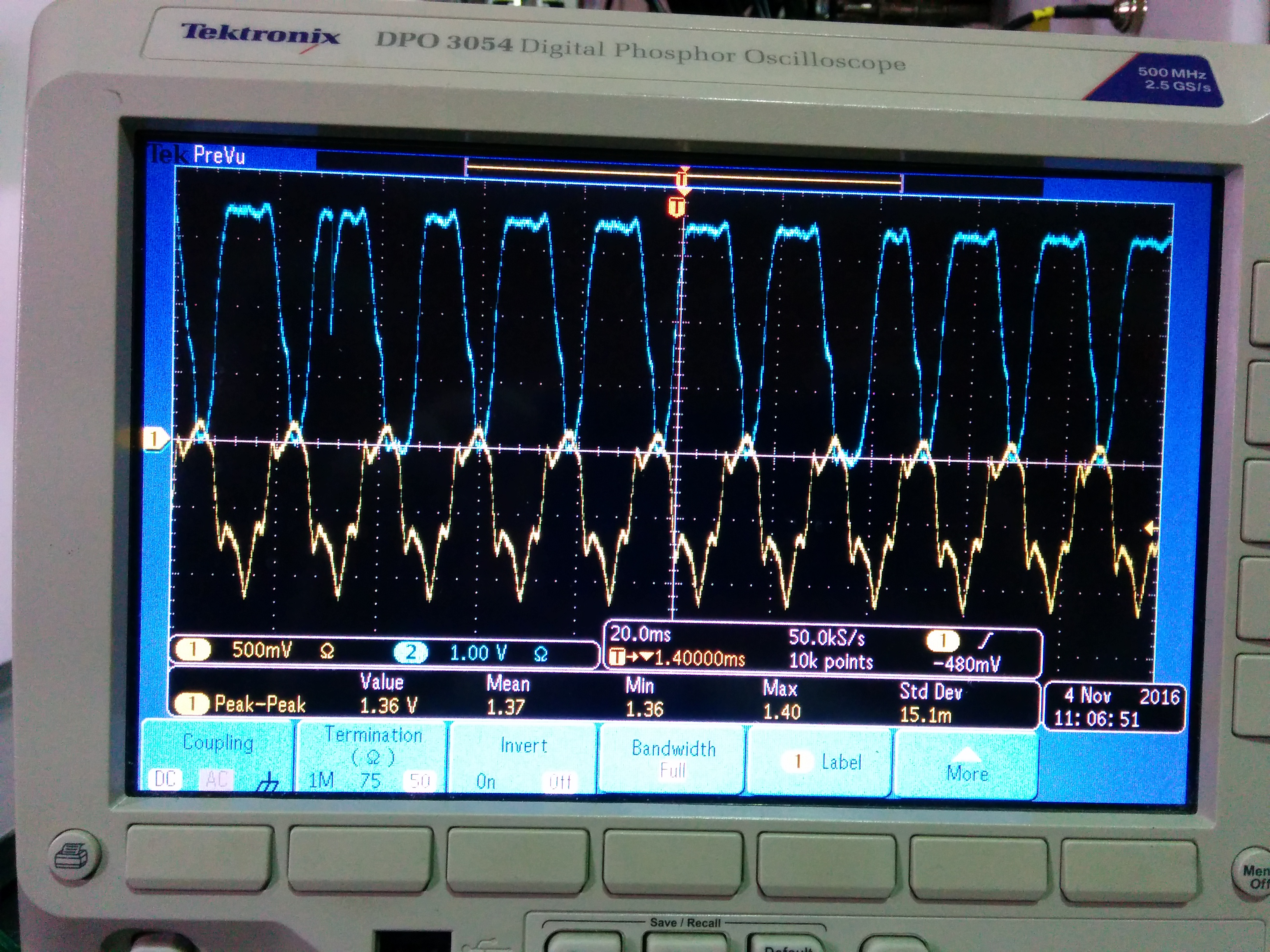

Check 50MHz TTL external clock signal and observe transients and width changes

in clock signal - see attachment 16

This may not be *the* explanation of current problems but I doubt the the hardware

will be 'happy' with it either

JAR cycles NIM signal through NIM-TTL signal converter several times to produce

better (no transients or width changes) clock signal with c. 3.2V amplitude

Power cycle and restart FEE64s

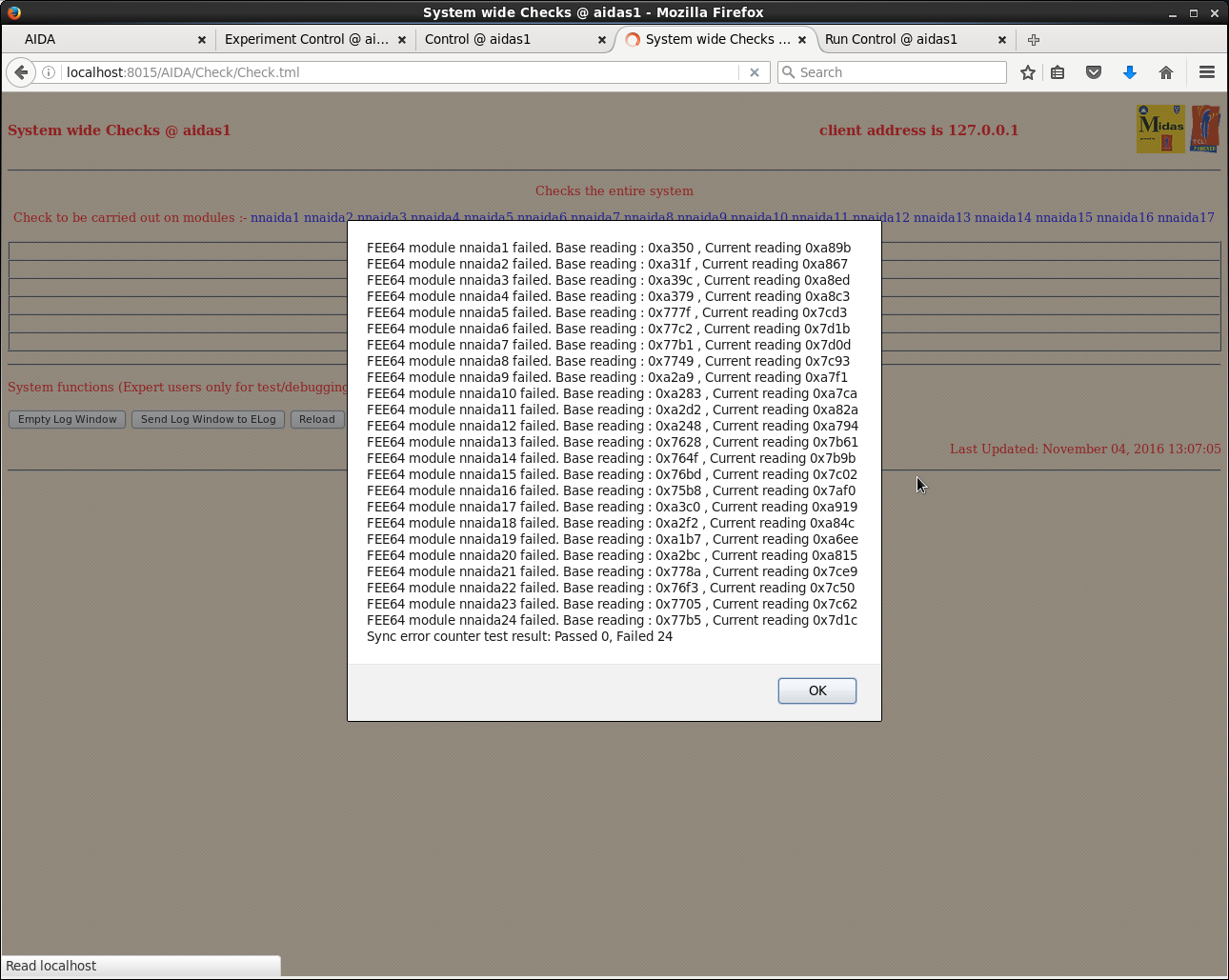

No change - ReSYNC and system wide checks fail - see attachments 17-21

12.40 Re-checked HDMI cabling

found master MACB port 1 -> MACB #7 next, port 2 -> MACB #3 next

change to master MACB port 1 -> MACB #3 next, port 2 -> MACB #7 next

Power cycle FEE64s

ReSYNC partial failure (left side OK, right side of tree fails), system wide checks fail - see attachments

22-26

13.05 Swap HDMI cables from master MACB to parents, i.e. HDMI cable master port 1 to MACB #3 next

changes to master port 2 to MACB #7 next

ReSYNC and system wide checks fail - see attachments 30-34

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|