| ID |

Date |

Author |

Subject |

|

146

|

Tue Nov 9 15:03:29 2021 |

RSS + OG | Burnt cables issues |

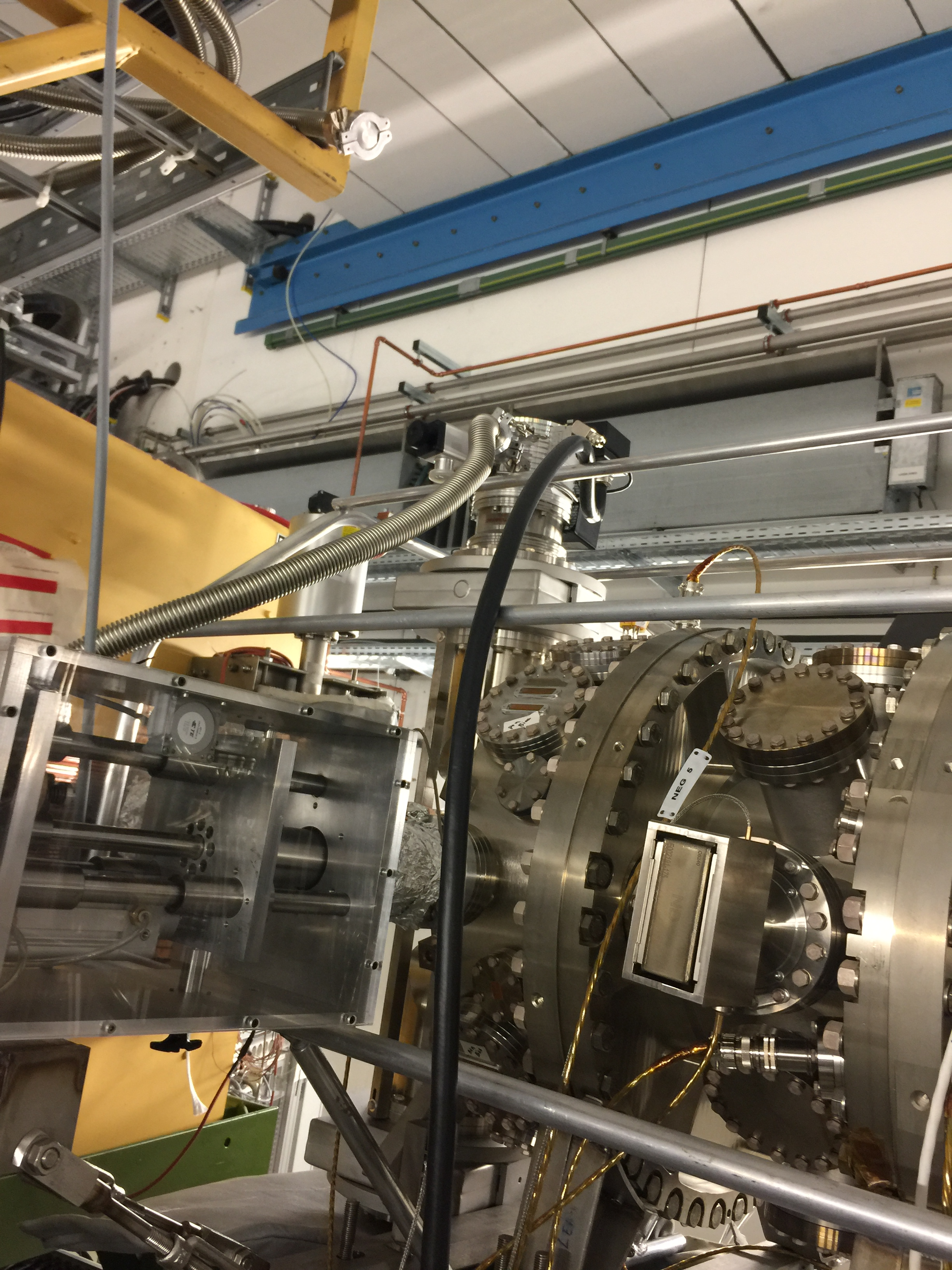

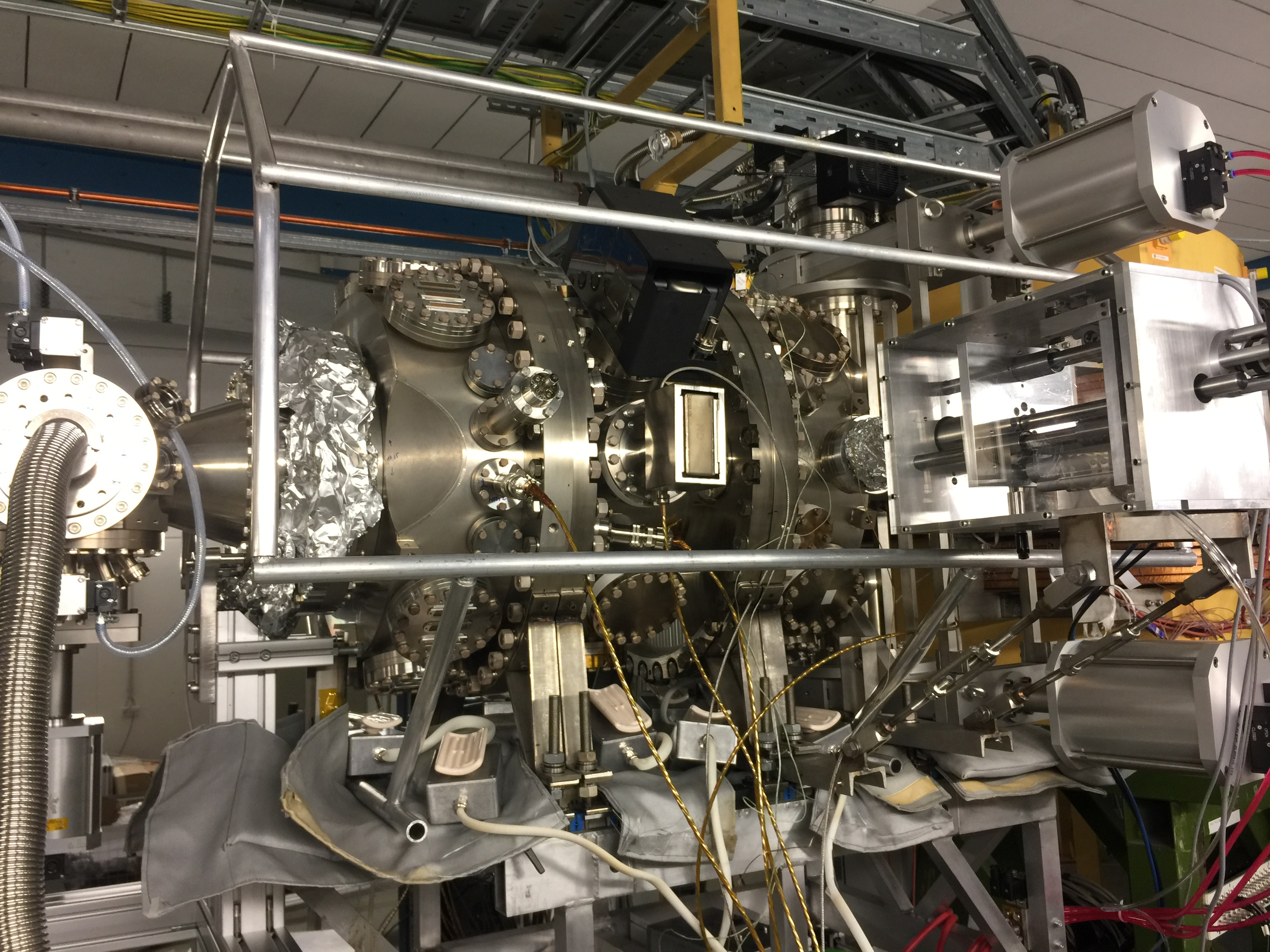

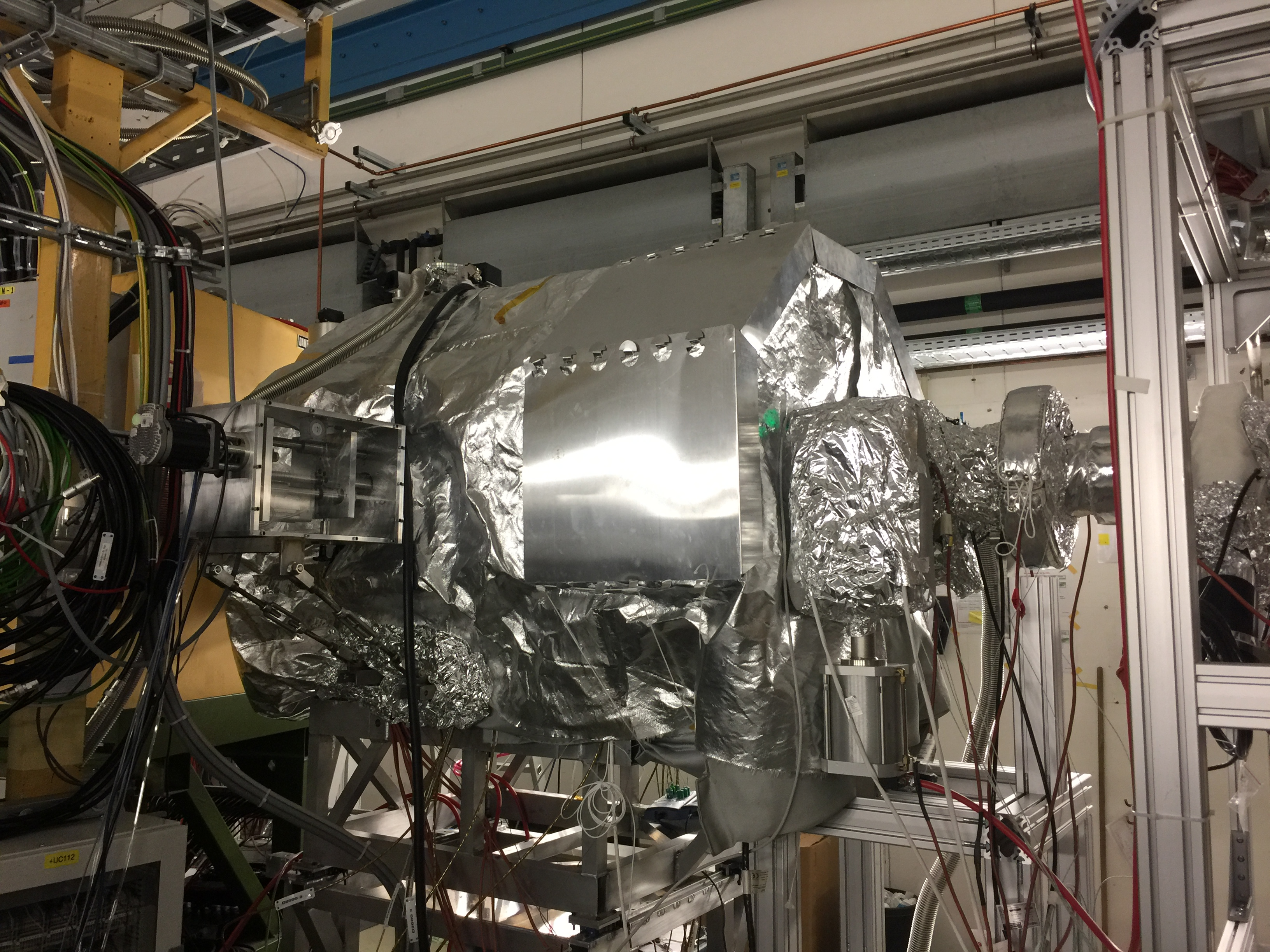

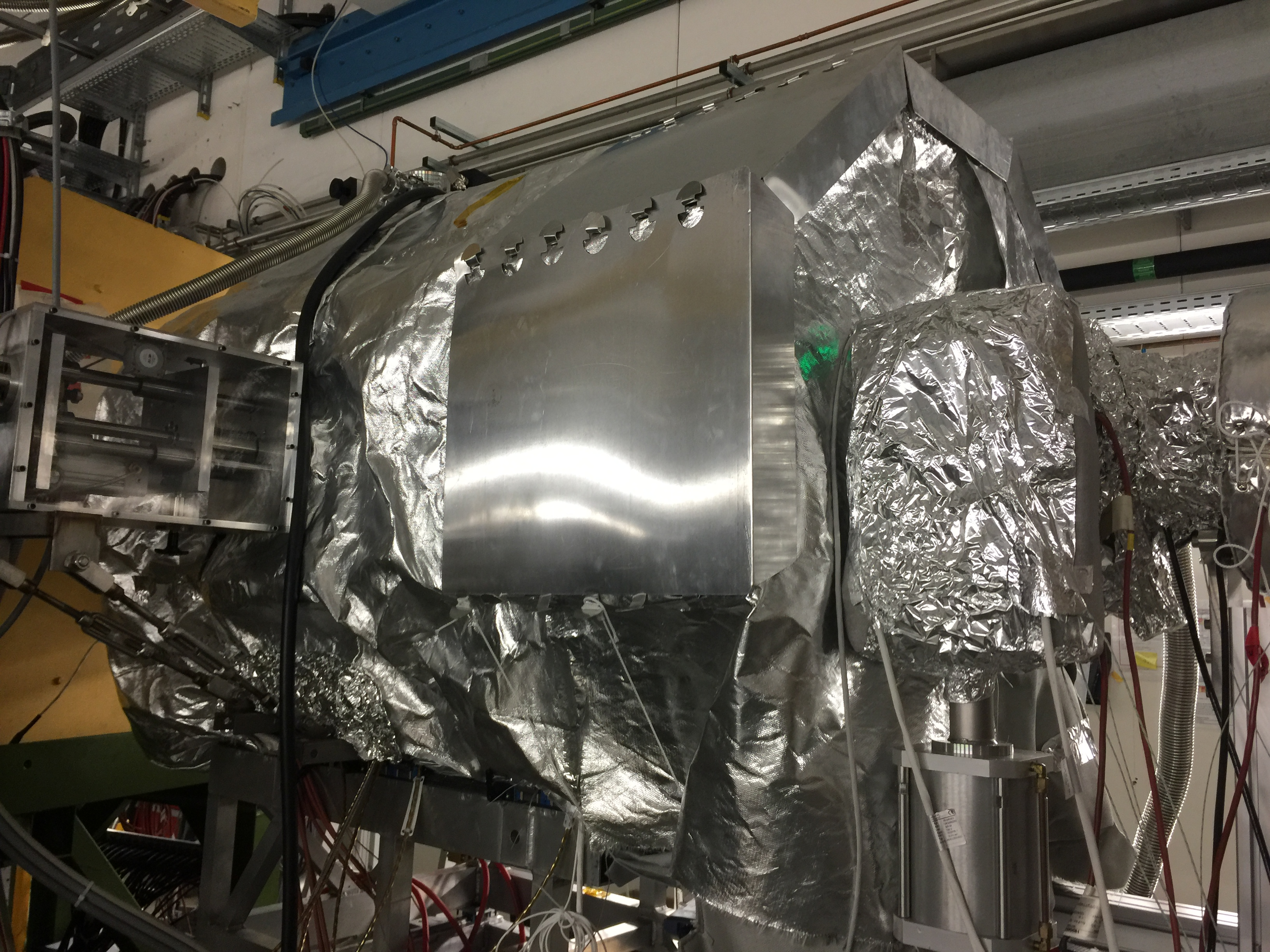

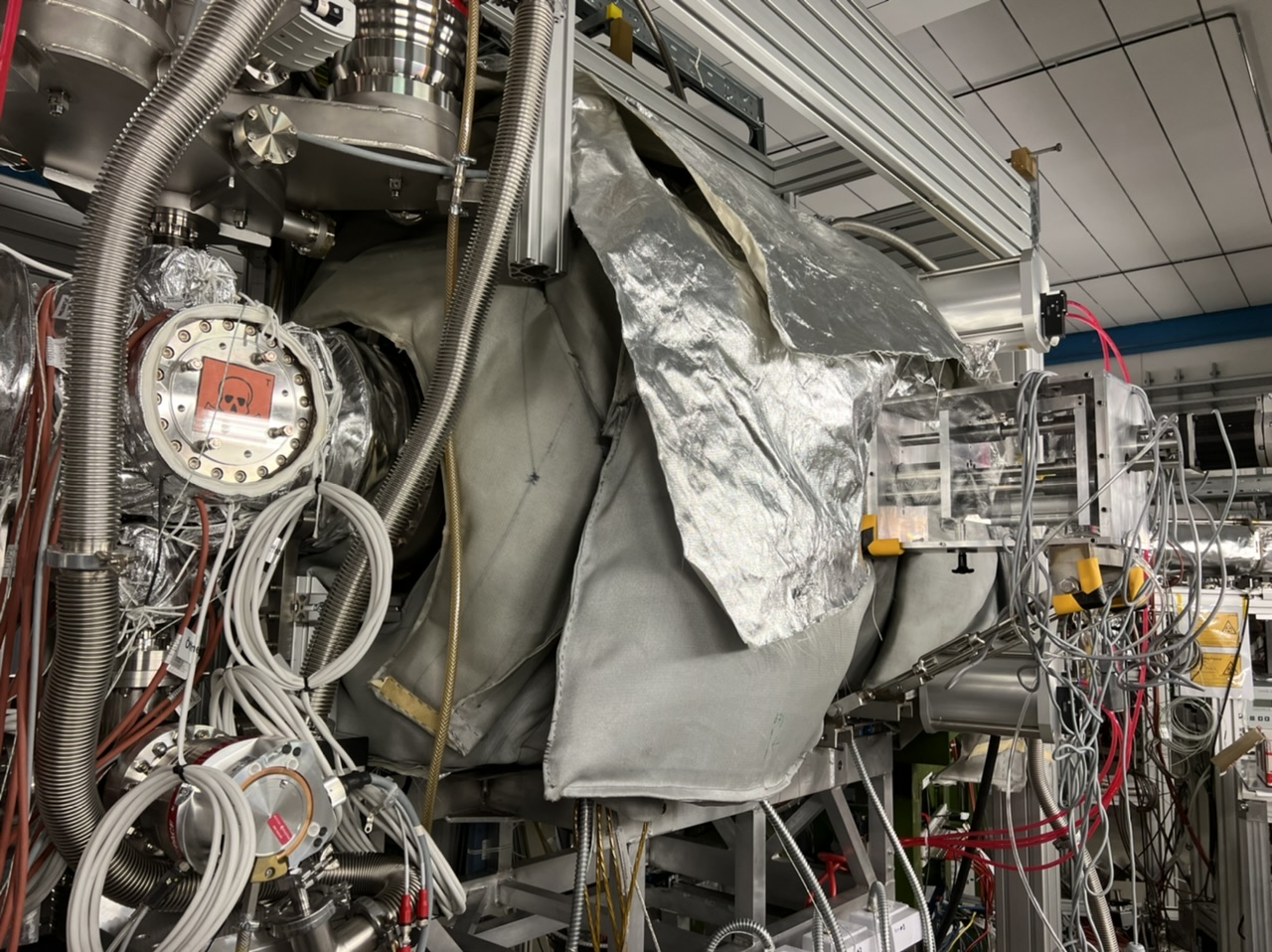

Upper part of the frame was mounted. In order to do so, the valve was closed, turbo wire and hose were disconnected and then connected. Valve was opened again. See pictures 1-2.

Bottom part of the tent was constructed with 3 heaters (from one of the controllers) at the front, 4 in the middle, and 4 at the back (4+4 from the other controller). See pictures 3.

Thermocouples were tested and connected to TC08 modules.

Wire connecting to four heaters was damaged which caused a spark and sound when the upper tent was being constructed. This caused a power failure two times, turning off all three pumps. The upper valve was immediately closed. Power supplies of heaters were disconnected and pumps were turned on again. Valve was opened again as well.

Construction of tent is paused. Waiting for the wire to be repaired by tomorrow and start again. |

| Attachment 1: IMG_5493.JPG

|

|

| Attachment 2: IMG_5496.JPG

|

|

| Attachment 3: IMG_5497.JPG

|

|

| Attachment 4: IMG_5500.JPG

|

|

| Attachment 5: IMG_5502.JPG

|

|

| Attachment 6: IMG_5503.JPG

|

|

| Attachment 7: IMG_5507.JPG

|

|

|

151

|

Thu Nov 11 11:44:58 2021 |

RSS + ML OG + CB (remotely) | CARME baking started |

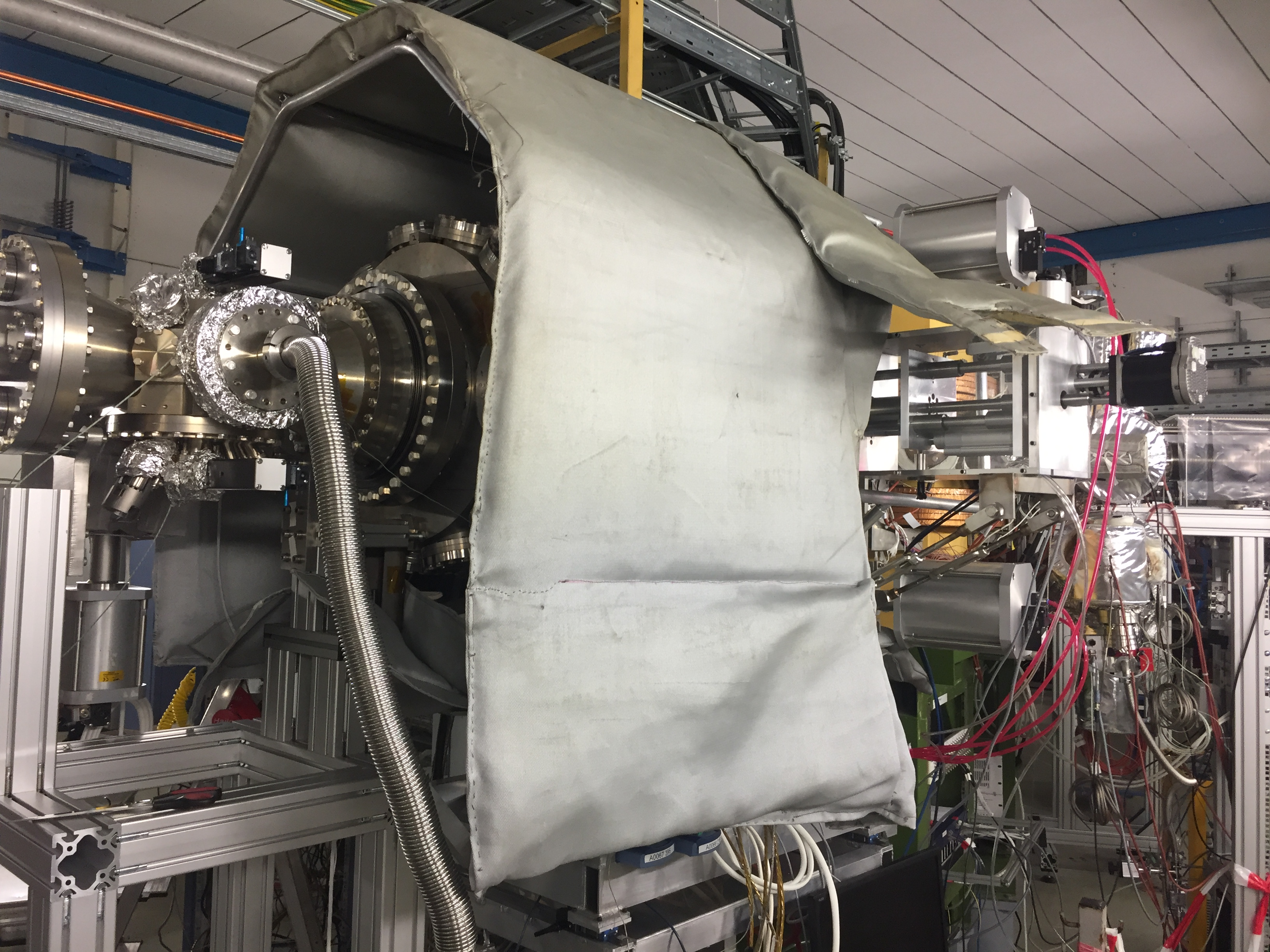

With the help of OG, the baking tent was built. MG started baking around 11:30 am with a rate of 0.2 K/minute.

Heating update can be found on: https://web-docs.gsi.de/~lestinsk/baking.php (CARME temperature plot now visible as well - thanks Michael!)

where, device - 192.168.207.192 is for CARME.

Ch1: CARME chamber long tape (2 kW)

Ch2: CF100 flanges exit side

Ch3: CF100 bellows exit side

Ch5: 200 W (x3) CF 100 flanges

Ch6: 40 W CF 100 flange

Ch8: VAT 100 gate valve to ring

example: in 39:50, 39 is the temperature and 50 is the set temperature. |

| Attachment 1: IMG_5535.JPG

|

|

| Attachment 2: IMG_5537.JPG

|

|

| Attachment 3: IMG_5531.JPG

|

|

| Attachment 4: IMG_5534.JPG

|

|

| Attachment 5: IMG_5539.JPG

|

|

|

149

|

Wed Nov 10 18:24:12 2021 |

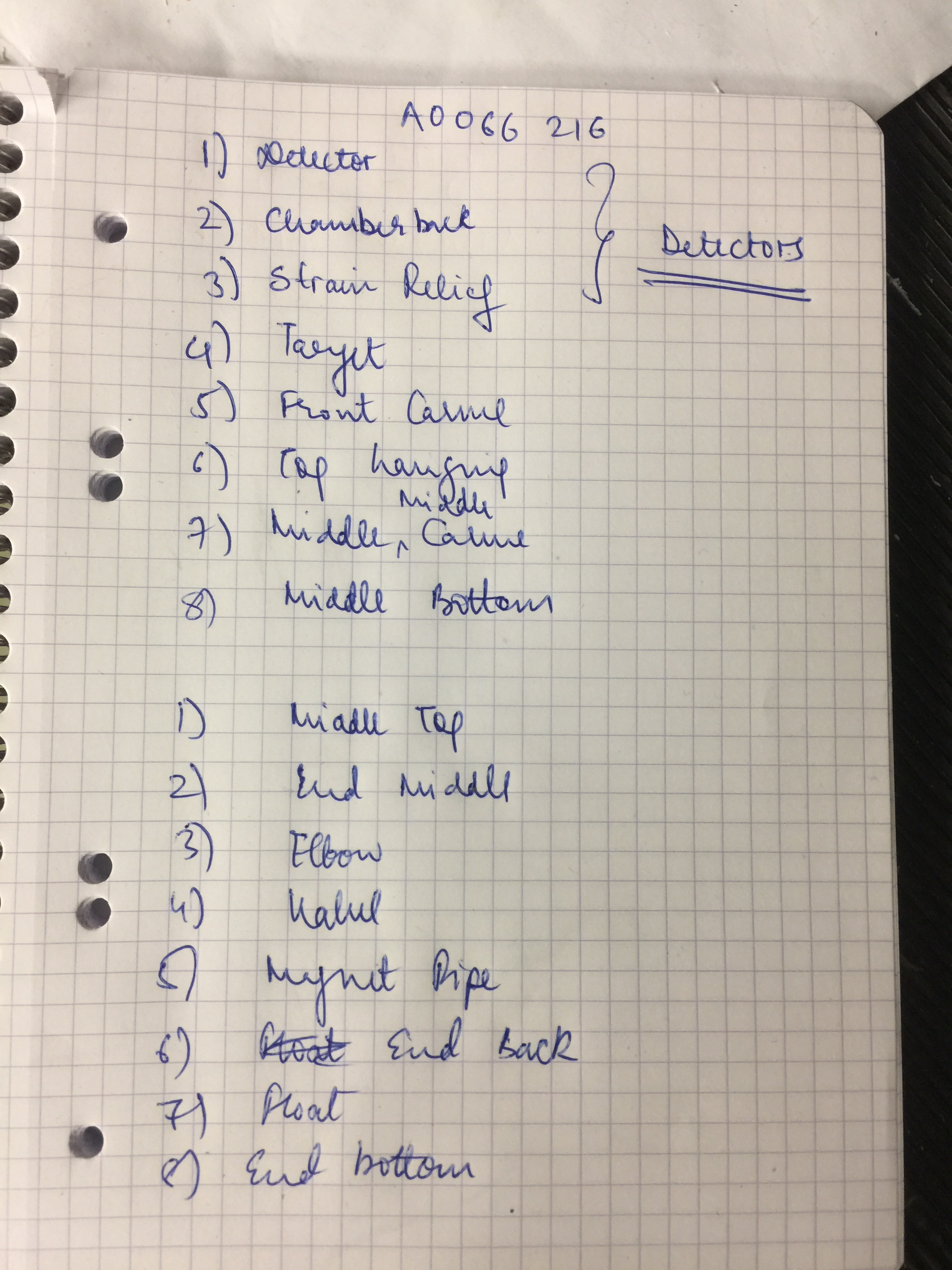

RSS | Thermocouple labelling |

1. Detector

2. Chamber back

3. Strain relief

4. Target

5. Front CARME

6. Top hanging

7. Middle middle CARME

8. Middle bottom

1. Middle top

2. End middle

3. Elbow

4. Valve

5. Magnet pipe

6. End back

7. Float

8. End bottom |

| Attachment 1: labeling.JPG.svg

|

|

| Attachment 2: Labelling.svg

|

|

| Attachment 3: IMG_5512.JPG

|

|

|

428

|

Tue Jul 25 09:12:15 2023 |

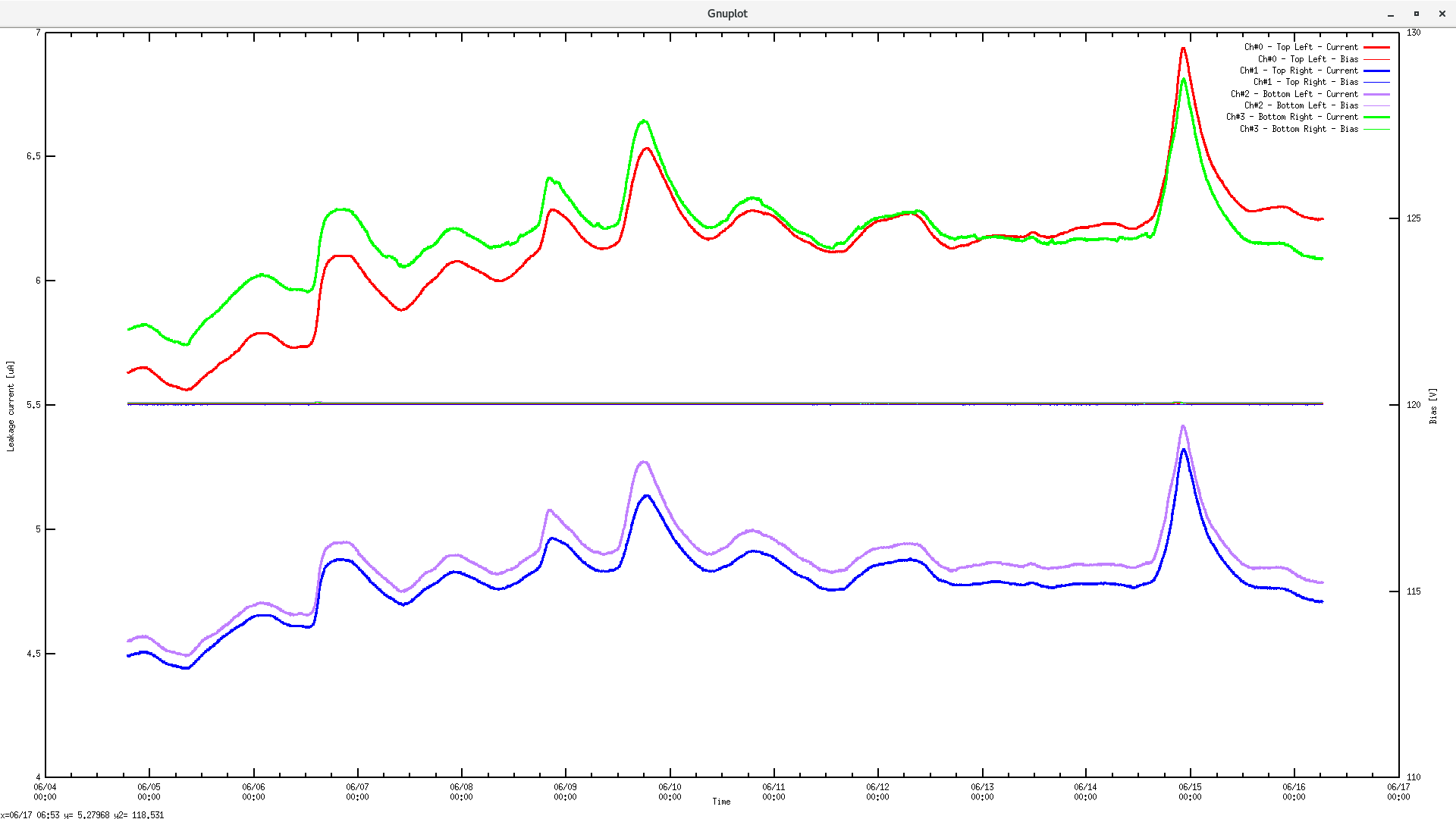

RSS | Building tent |

10:10 IE514 2.0e-08mbar

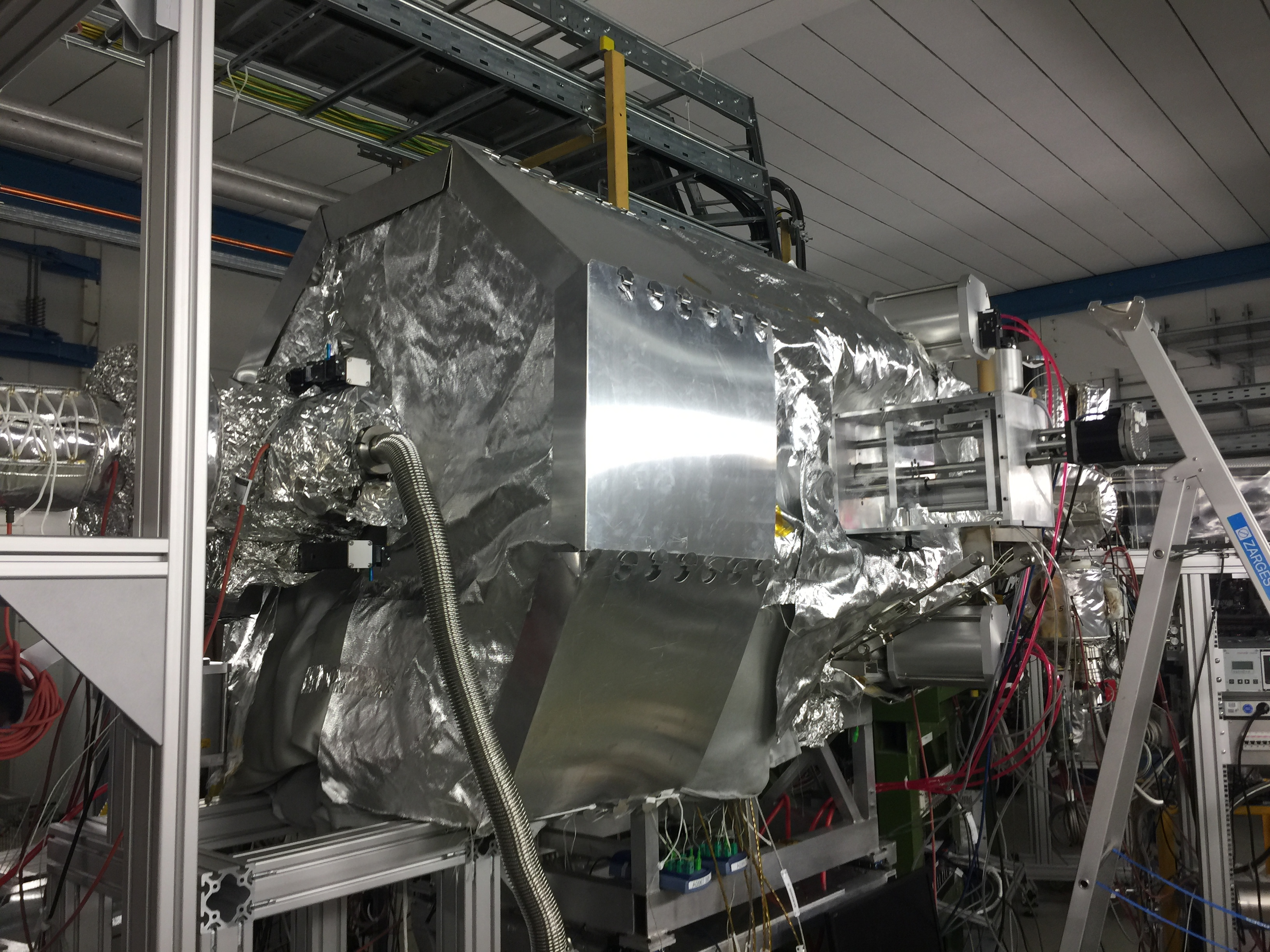

Upstream part of the CARME is covered. |

| Attachment 1: BD01C0C8-5181-49B8-8751-AD4C99A459CC.jpeg

|

|

| Attachment 2: 7B3836F1-8A7E-491B-AFDC-46033BF84760.jpeg

|

|

|

429

|

Wed Jul 26 08:28:09 2023 |

RSS | Building tent |

09:26 IE514 1.96e-08mbar |

| Attachment 1: IMG_9897.jpg

|

|

| Attachment 2: IMG_9899.jpg

|

|

| Attachment 3: IMG_9901.jpg

|

|

| Attachment 4: IMG_9902.jpg

|

|

|

430

|

Thu Jul 27 09:43:56 2023 |

RSS | Thermocouples connected -2 |

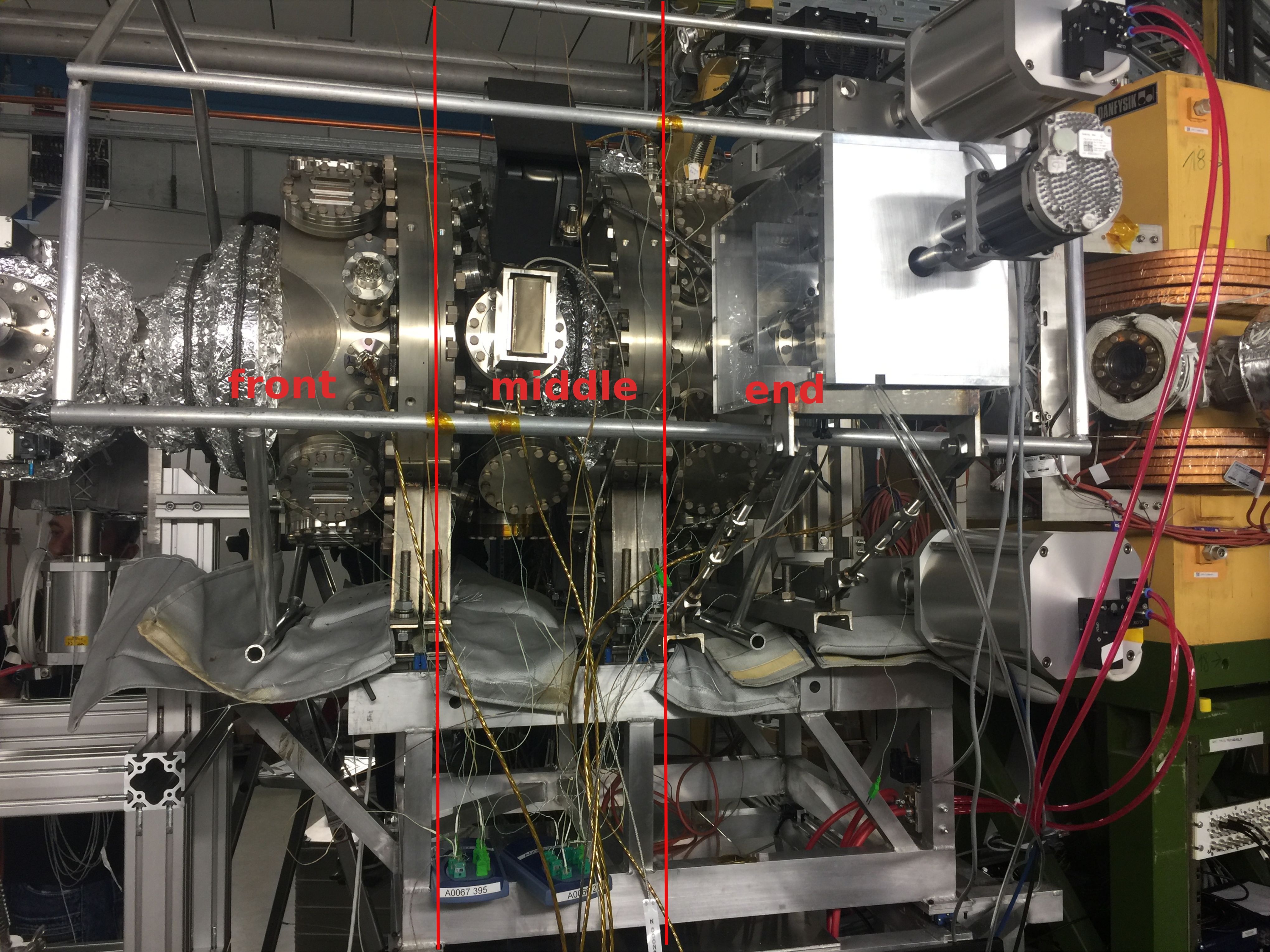

10:30 IE514 1.80e-08mbar

Most of the CARME is covered by the baking tent. The tent needs to be closed and a bit covered from the front (upstream), end (downstream), and bottom side. TCs are labeled with a marker in the sequence 1-1 to 2-8.

1-1 Internal TC 1

1-2 Internal TC 2

1-3 Internal TC 3

1-4 CARME front top

1-5 CARME front bottom

1-6 Top hanging middle

1-7 CARME middle middle

1-8 CARME middle bottom

2-1 CARME middle top

2-2 CARME back middle

2-3 Elbow

2-4 Valve

2-5 Magnet pipe

2-6 CARME back top

2-7 CARME back float

2-8 CARME back bottom

Also, TC extensions would be needed to connect to TC-8 modules. |

| Attachment 1: IMG_9920.jpg

|

|

| Attachment 2: IMG_9919.jpg

|

|

|

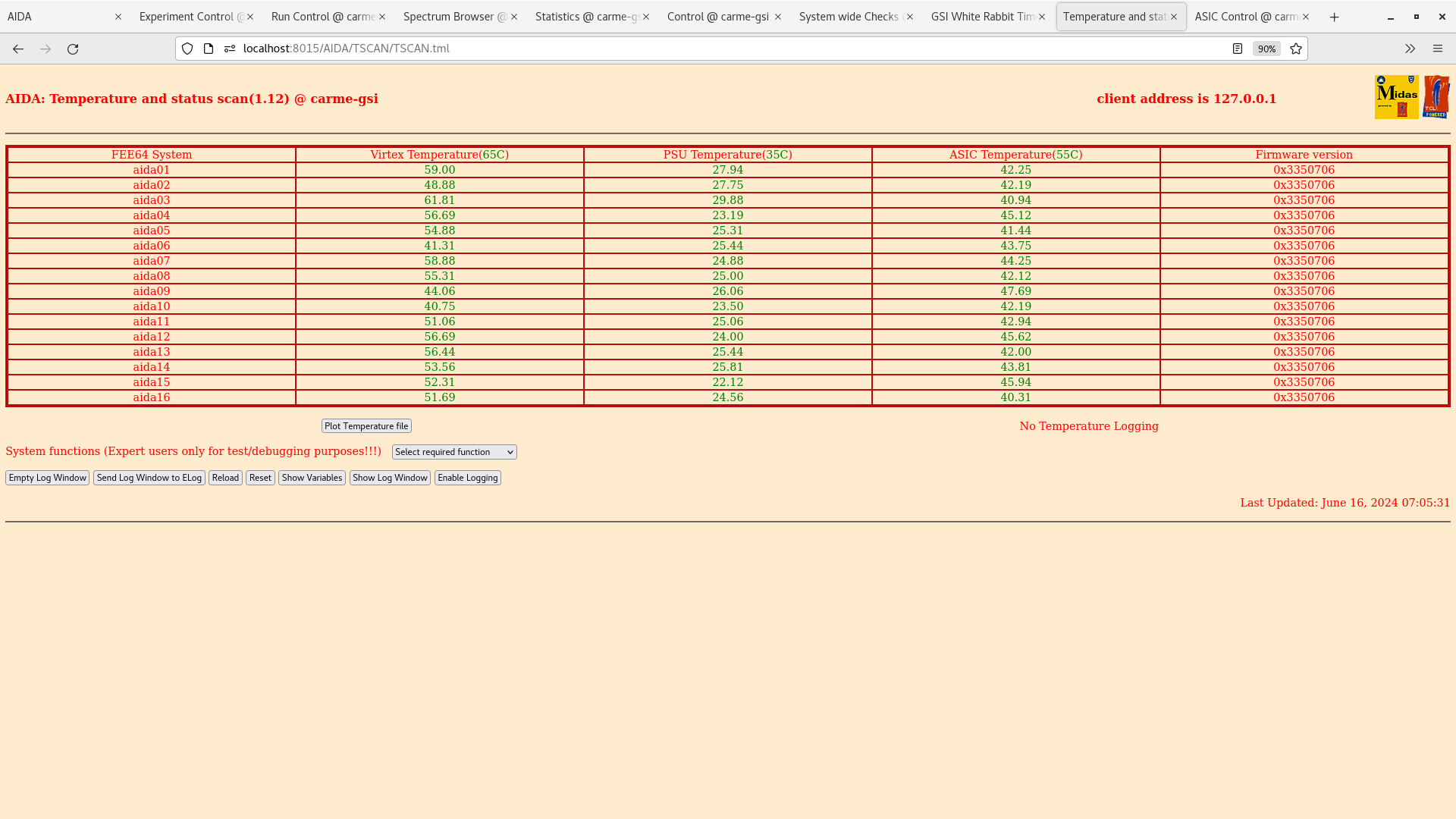

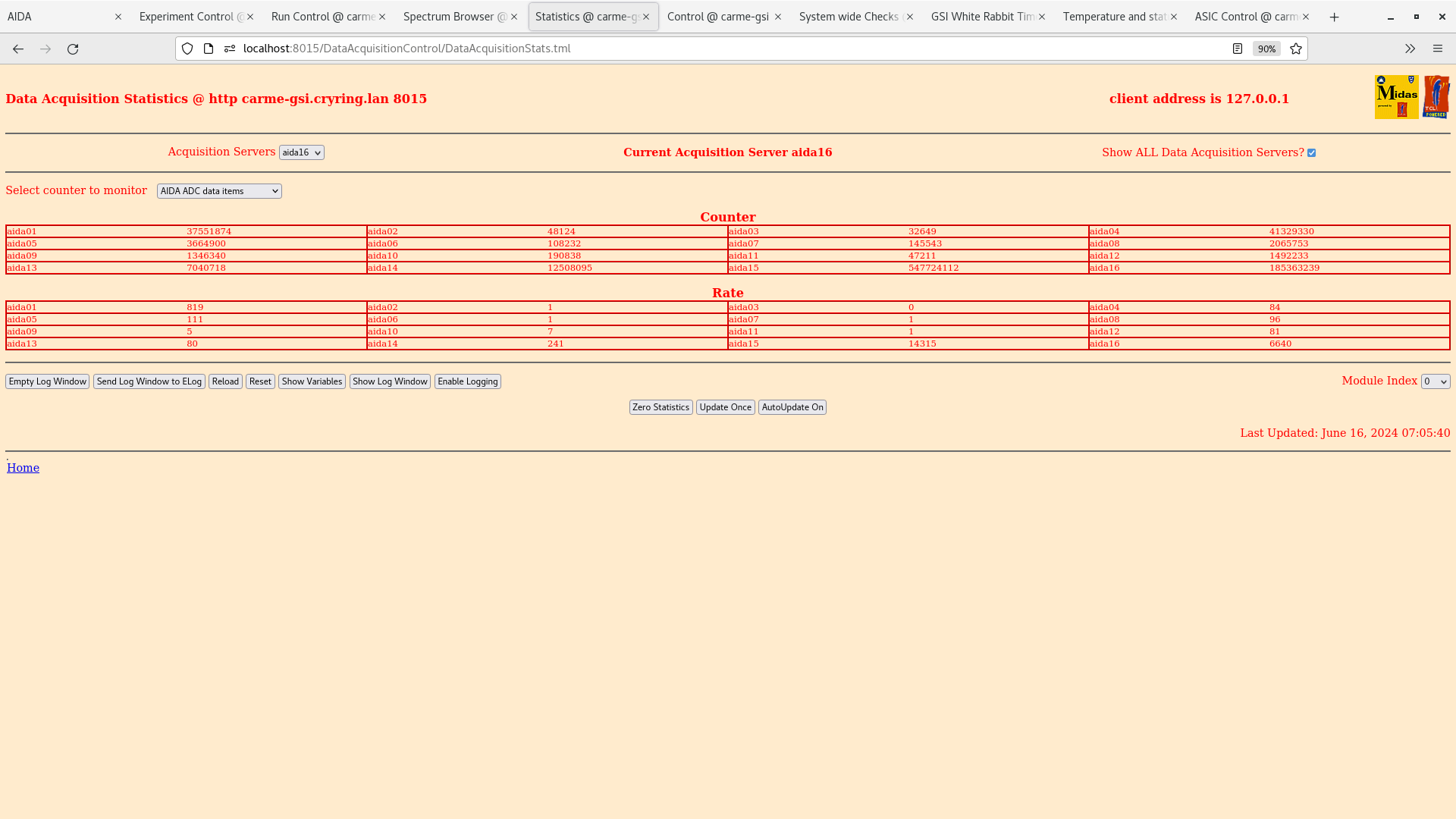

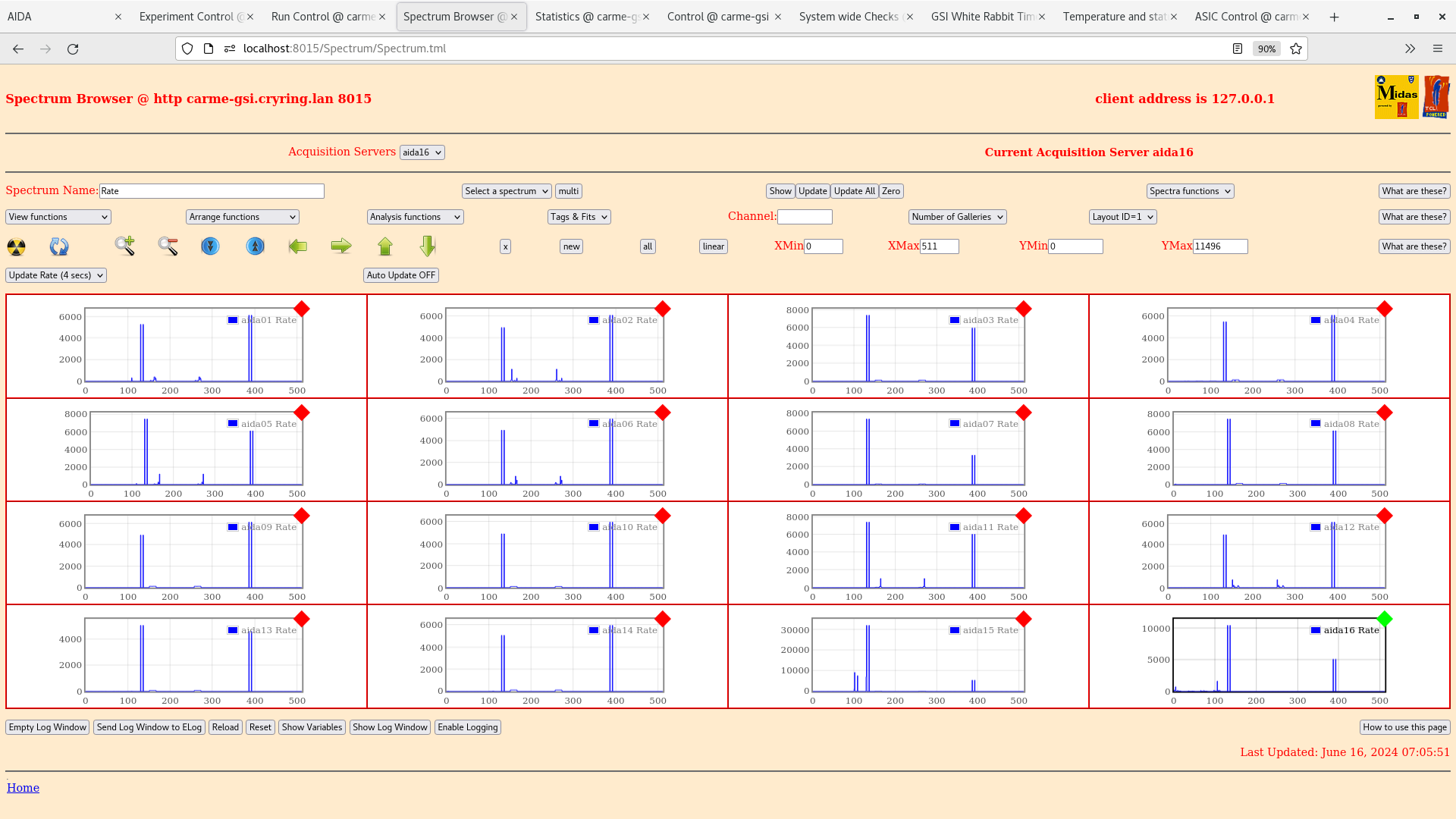

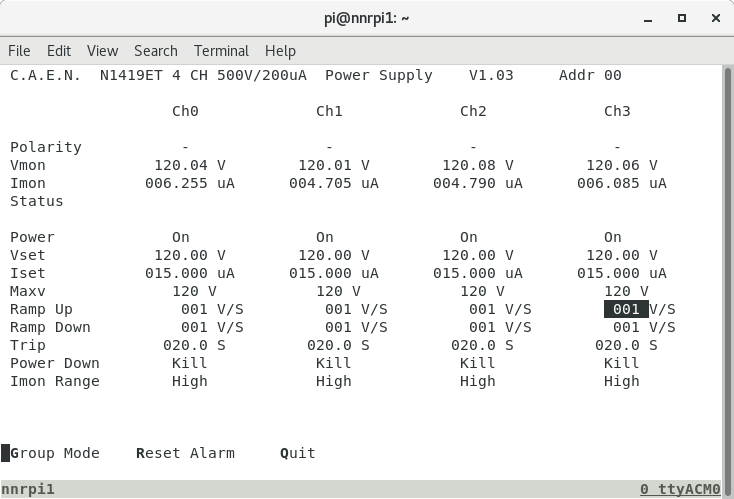

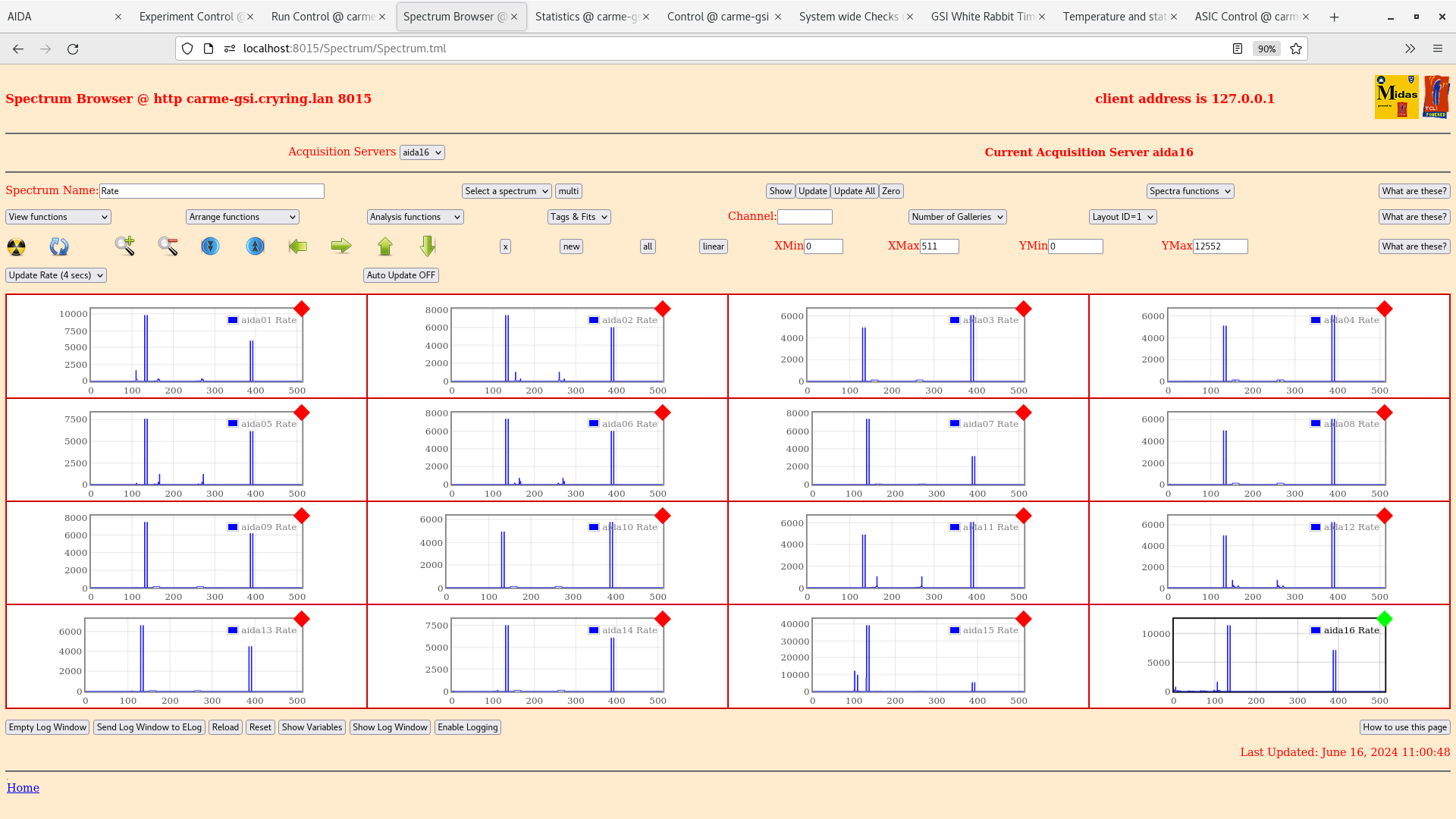

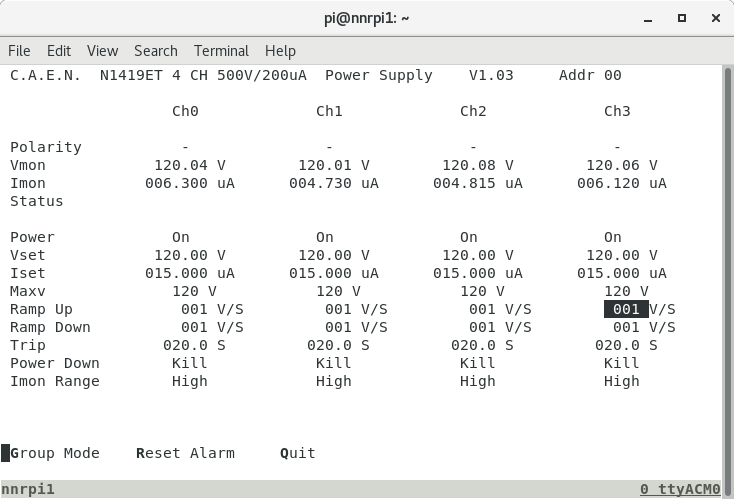

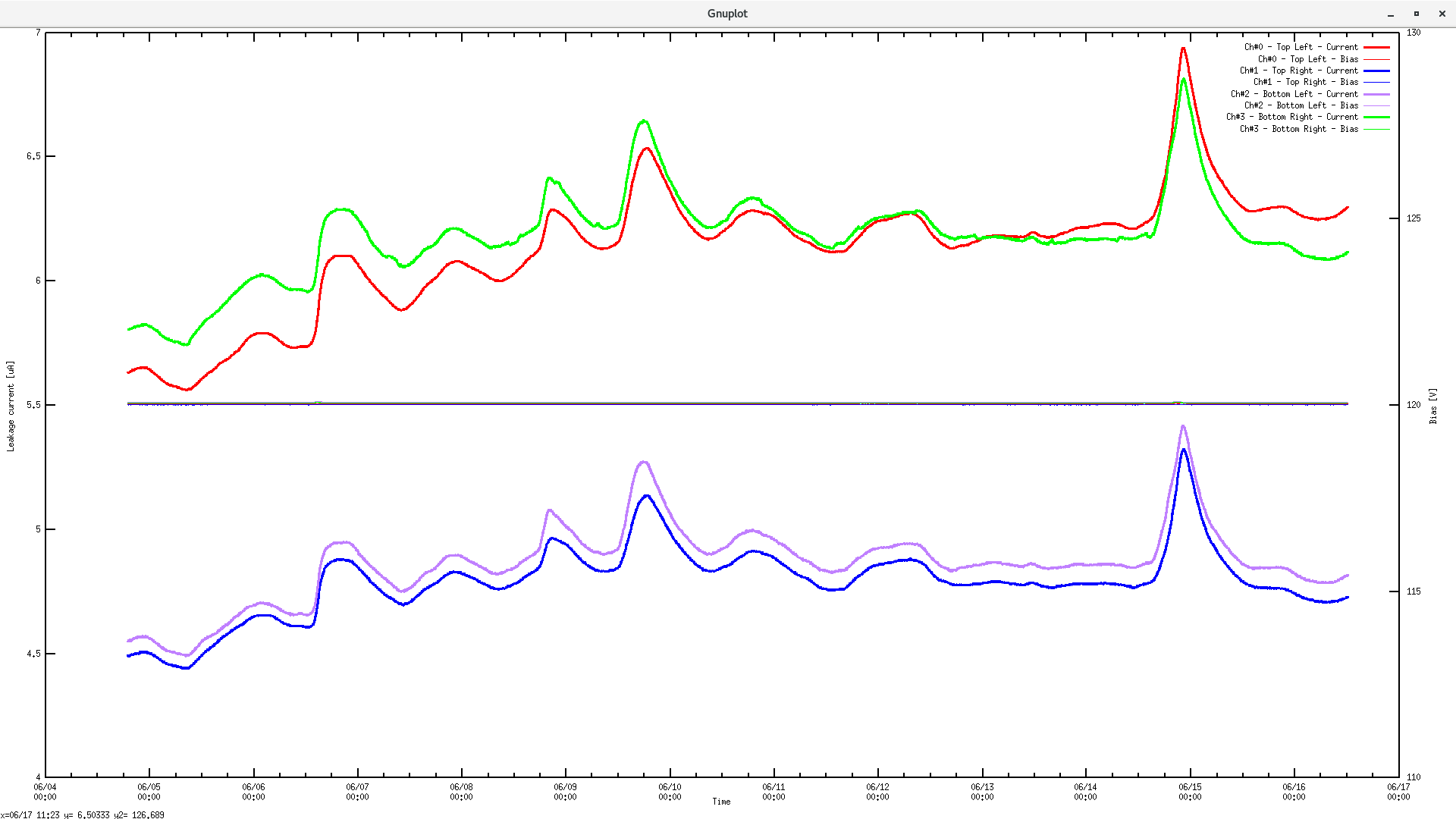

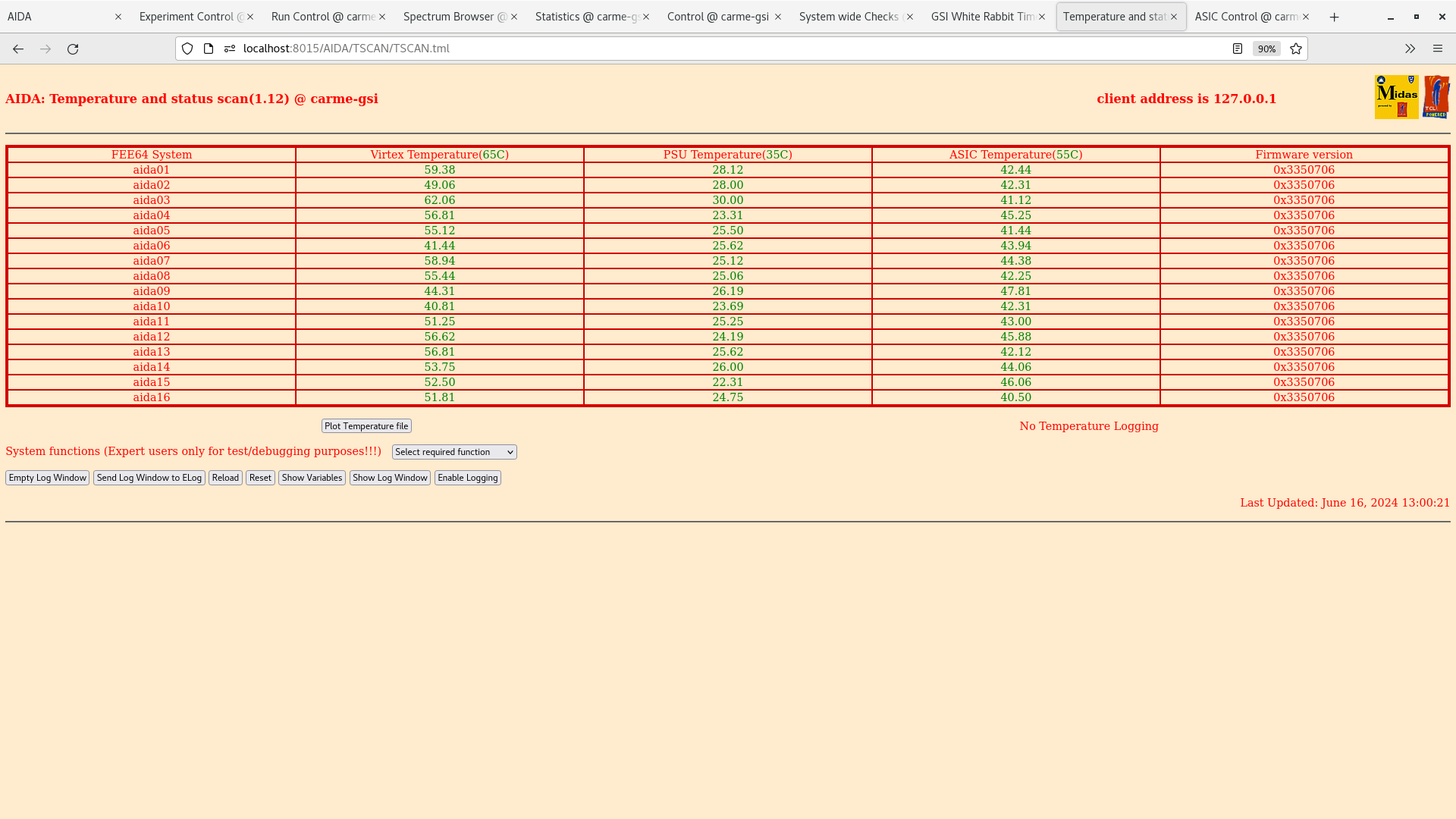

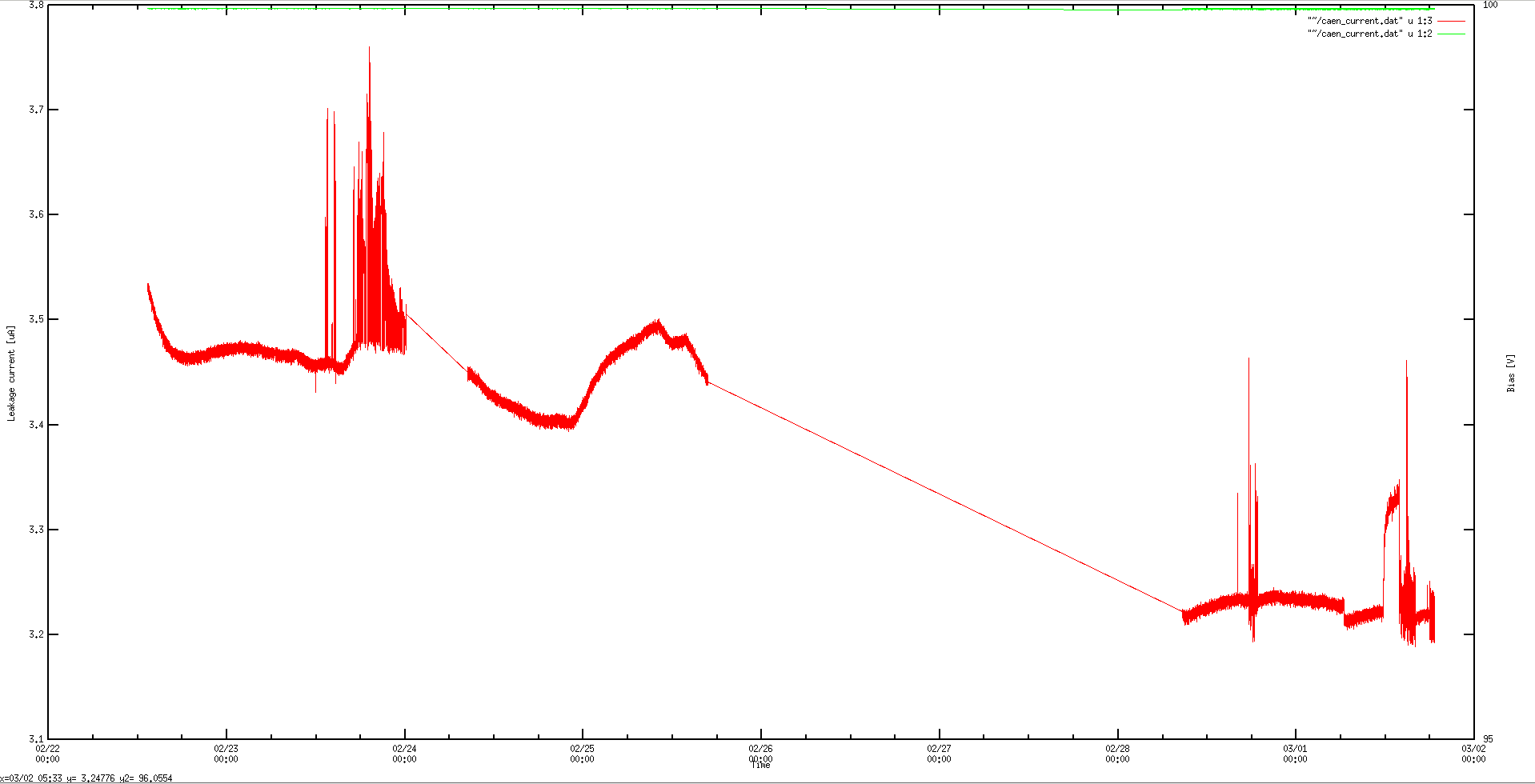

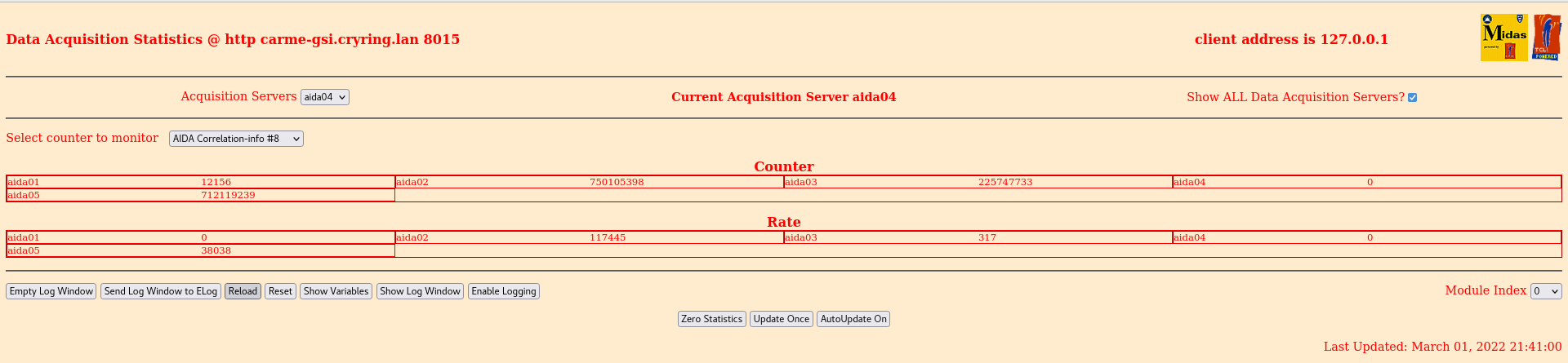

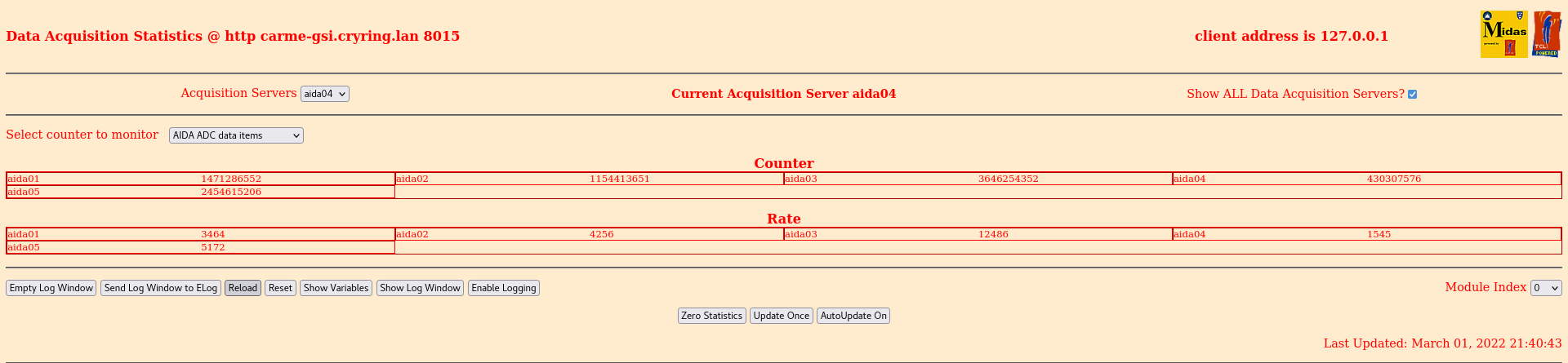

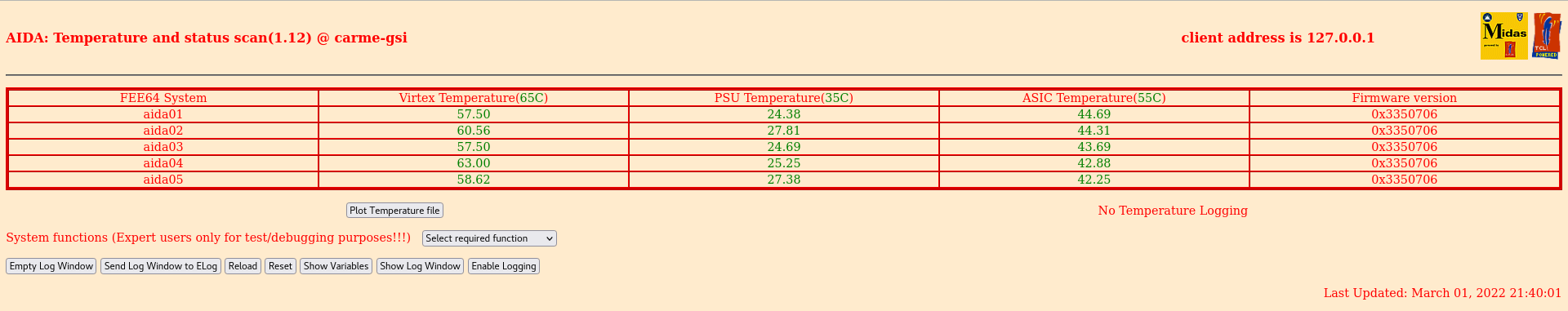

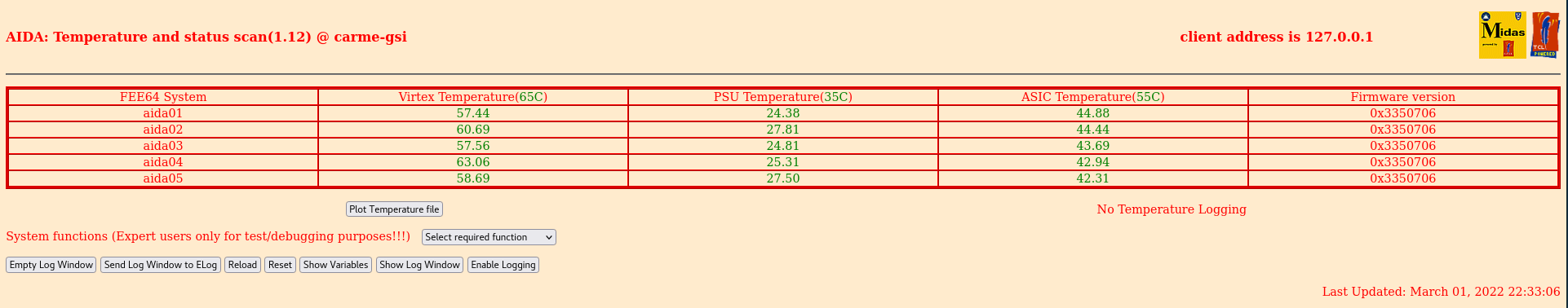

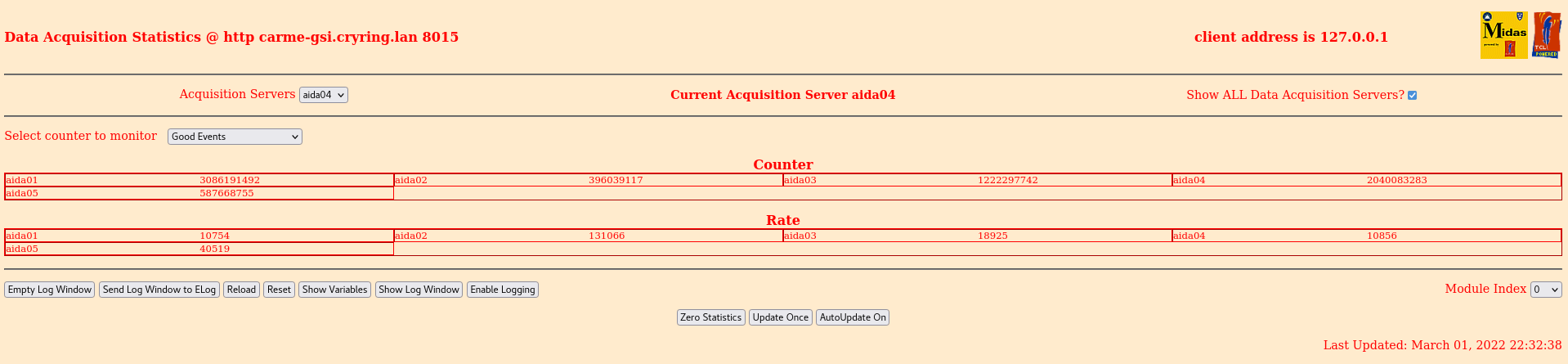

639

|

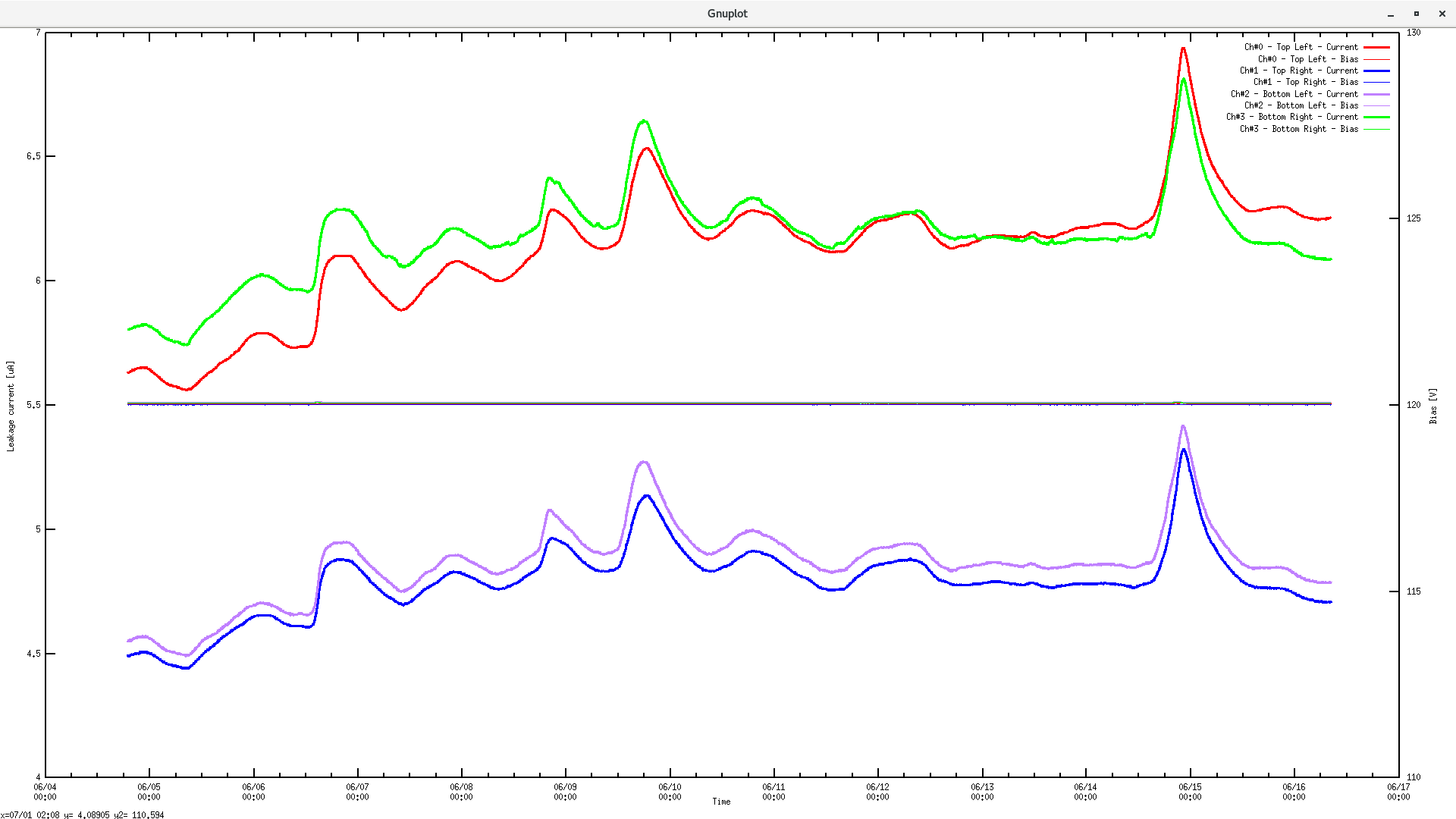

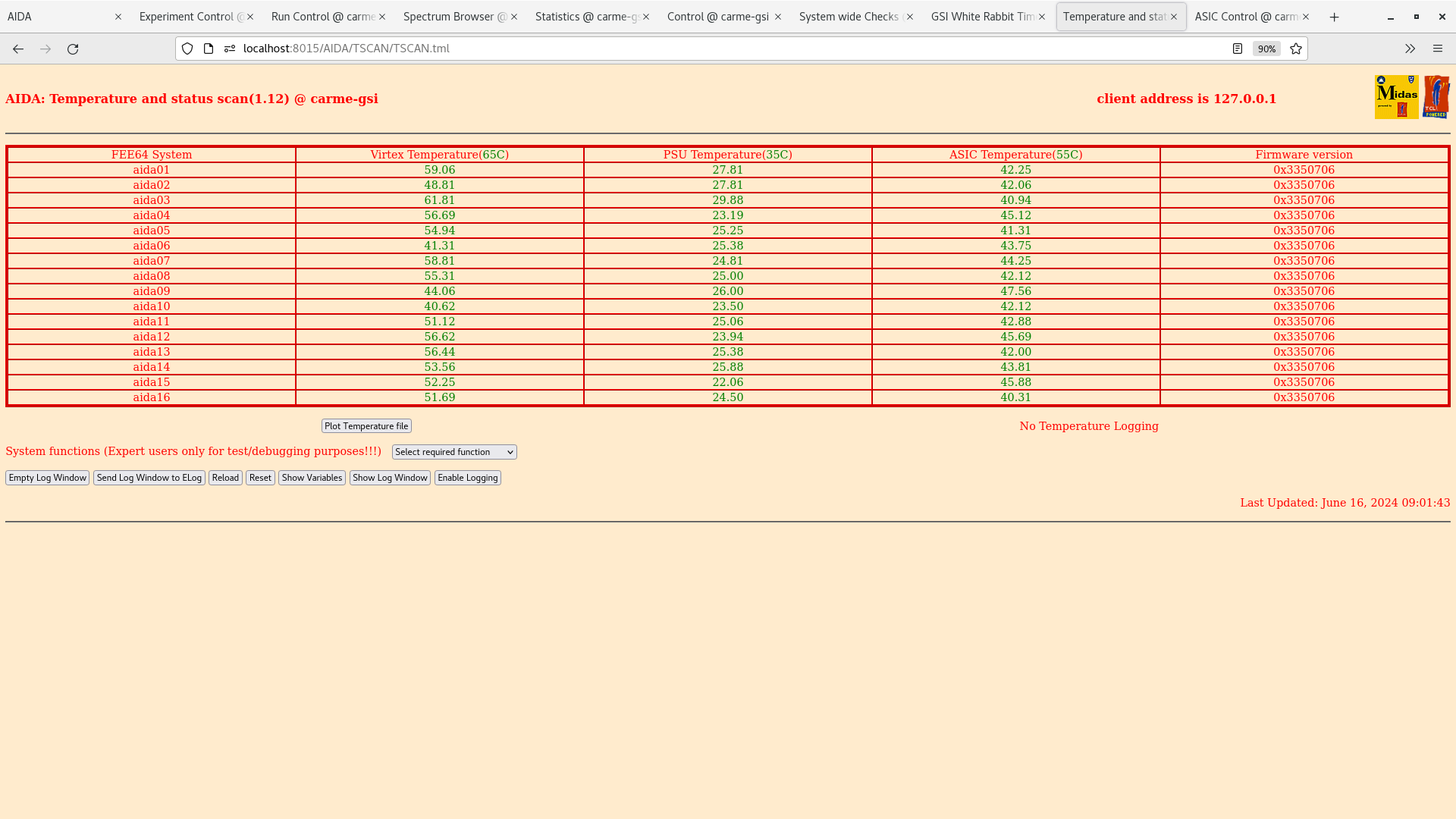

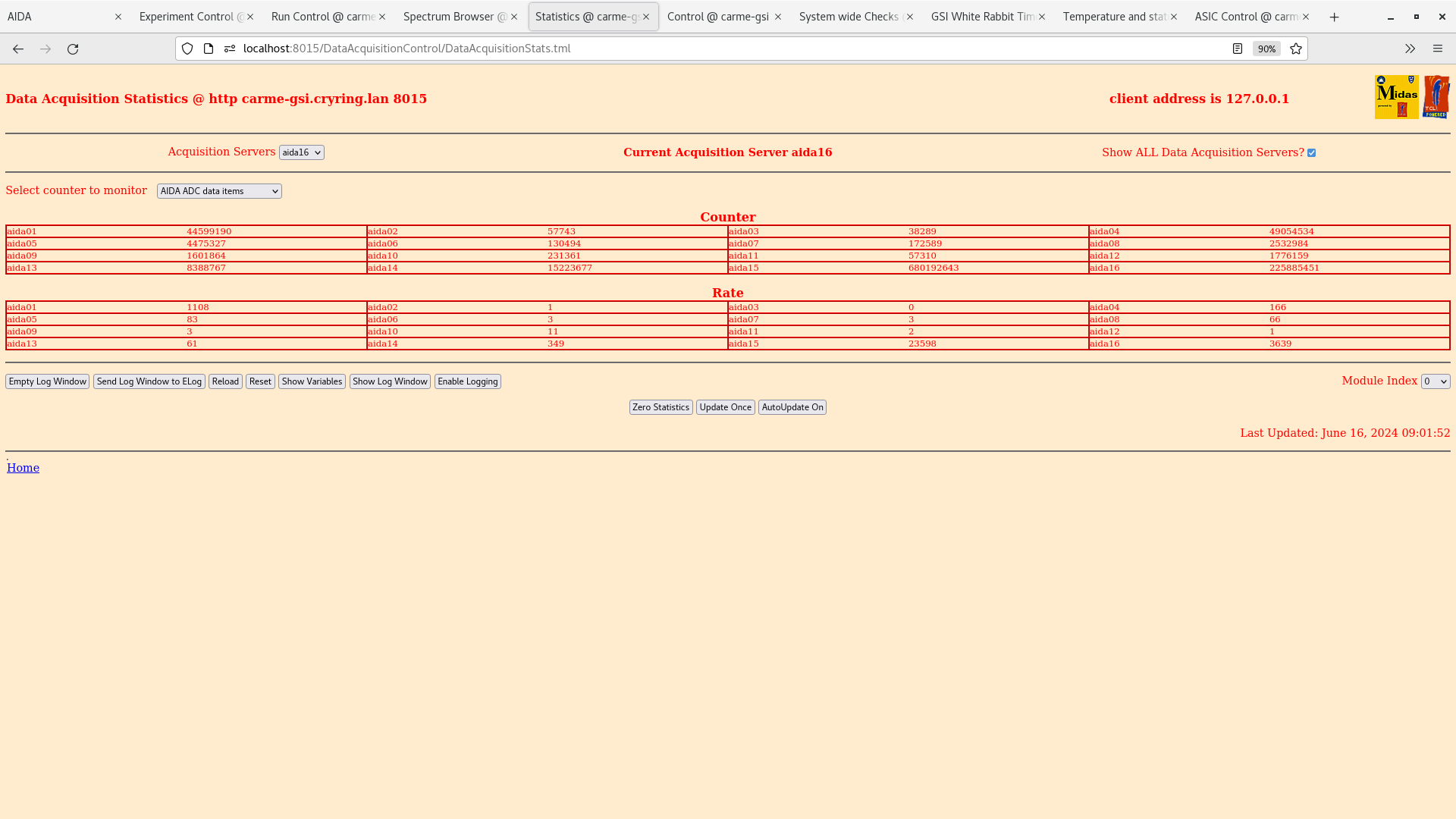

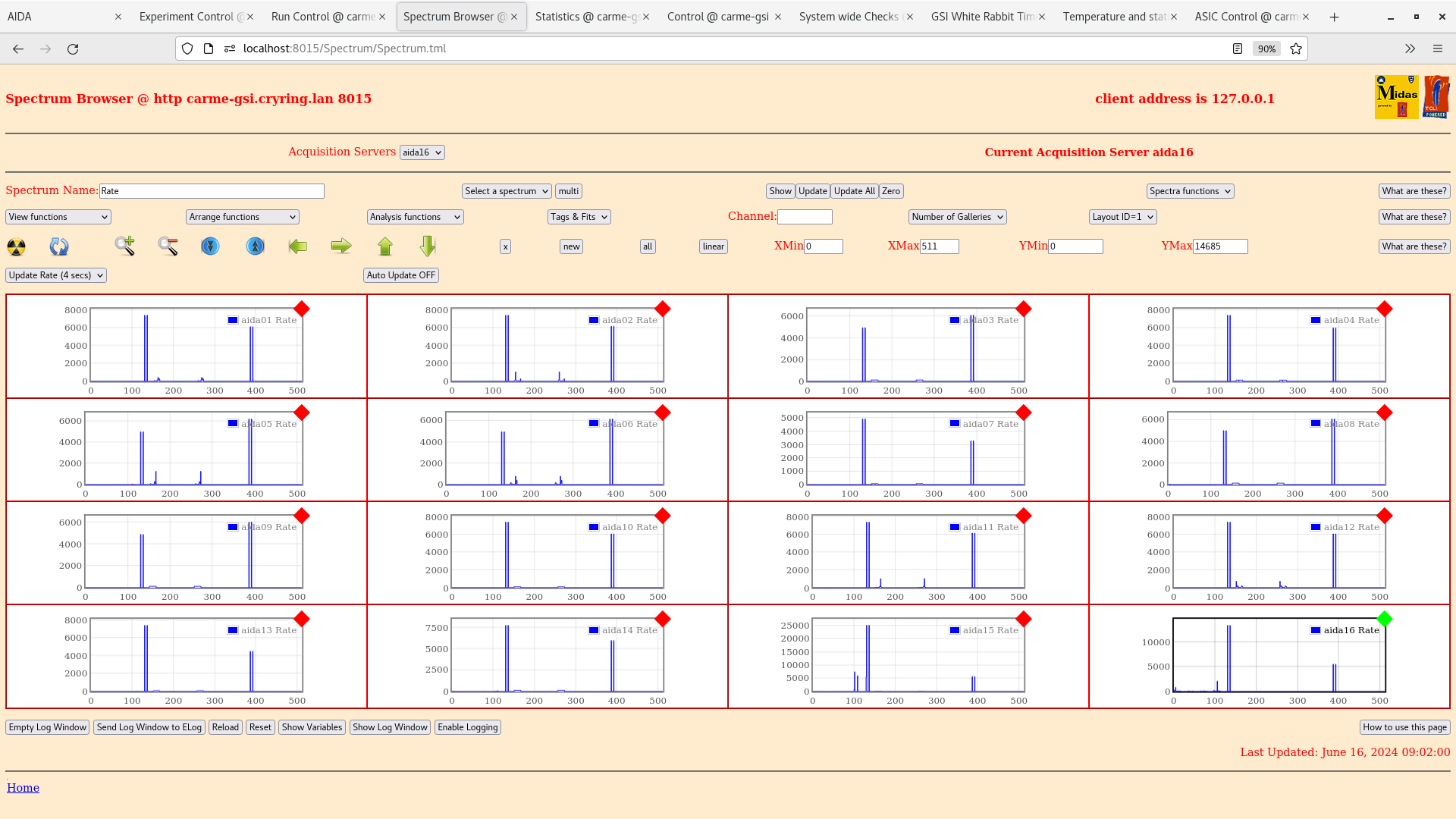

Sun Jun 16 06:02:31 2024 |

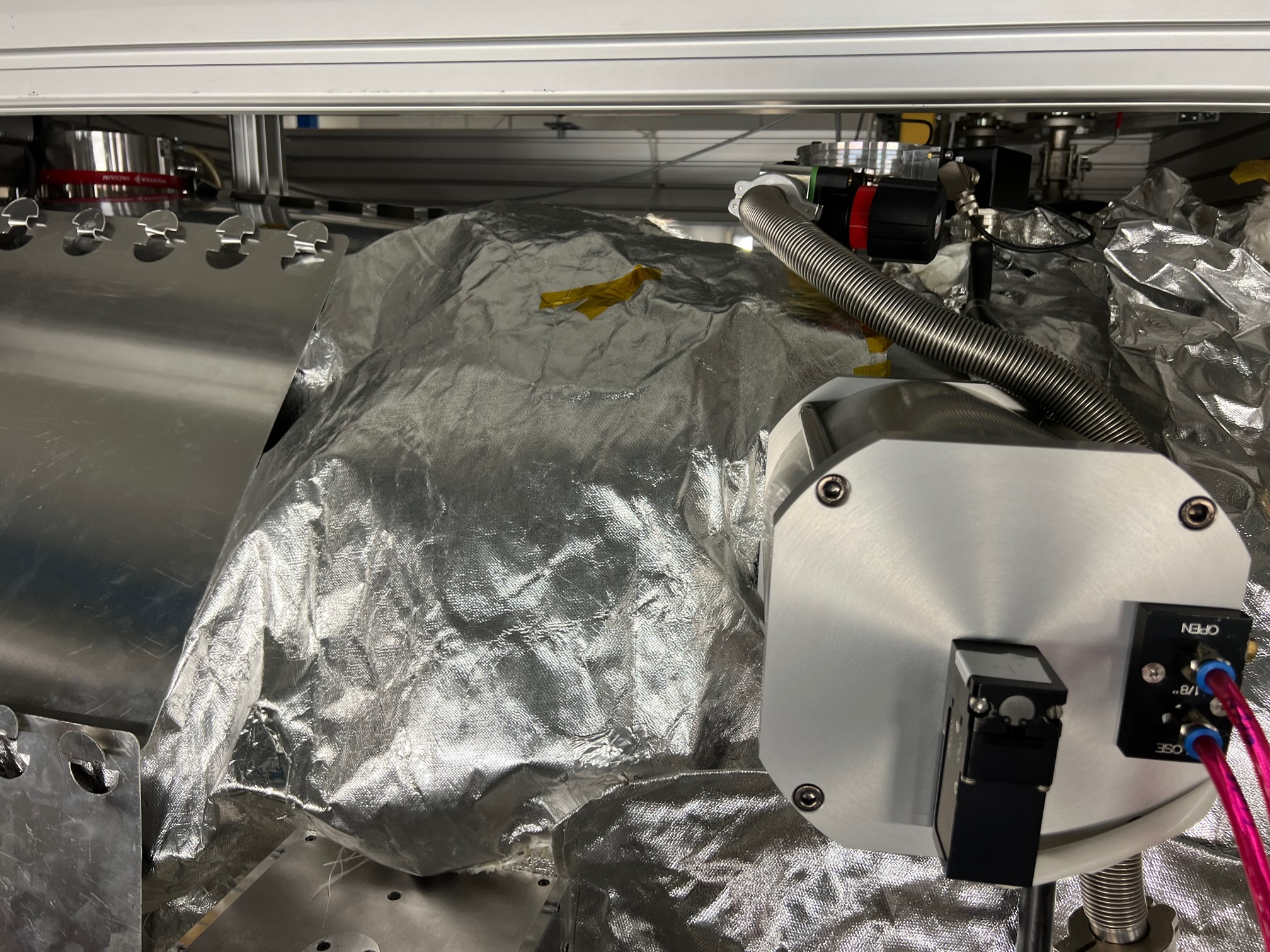

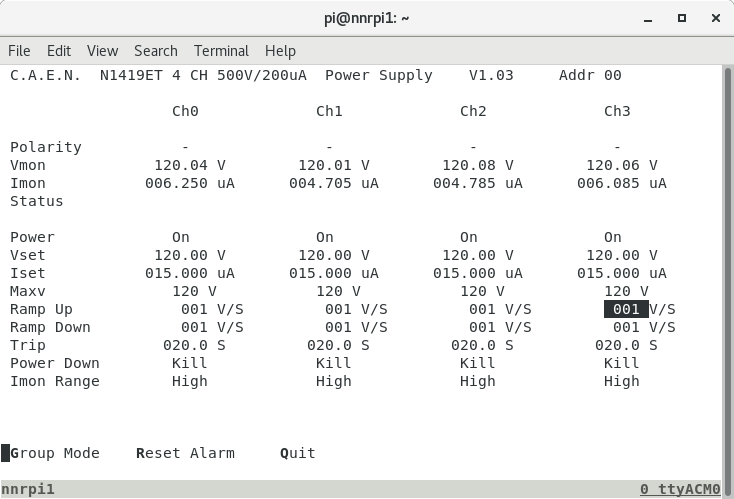

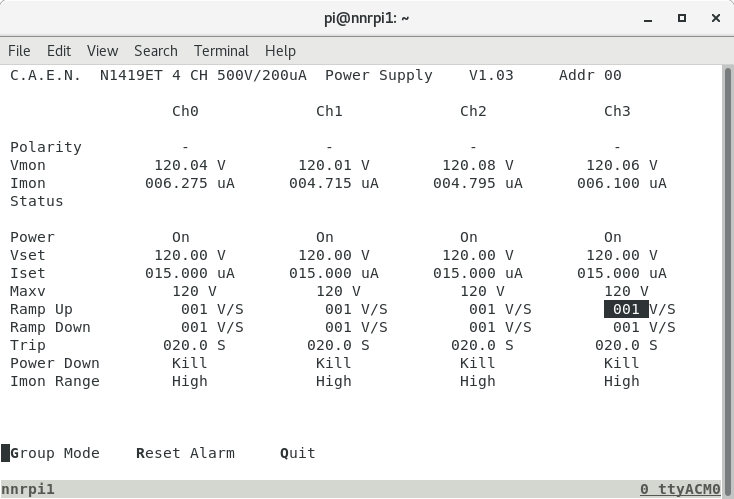

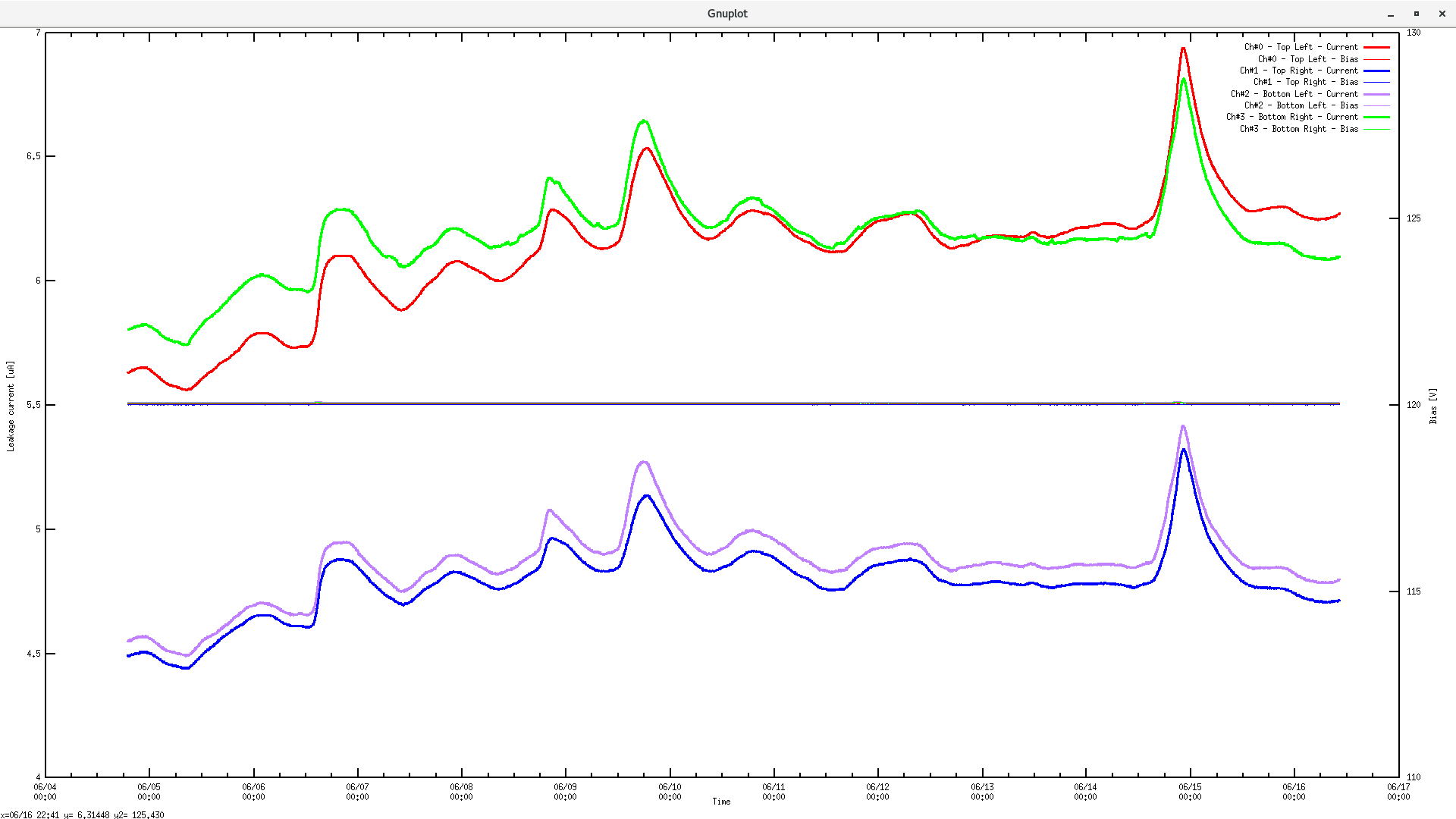

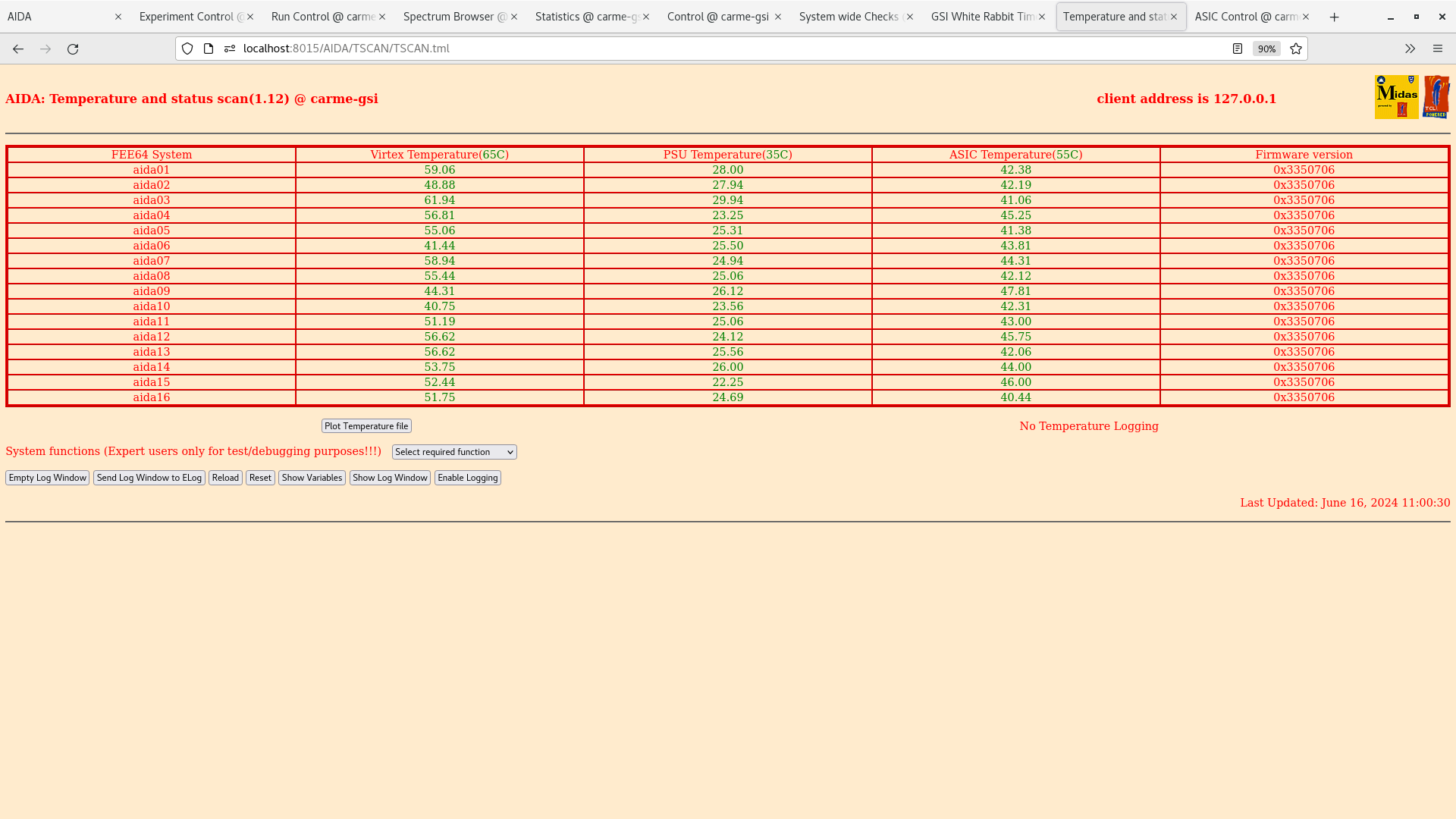

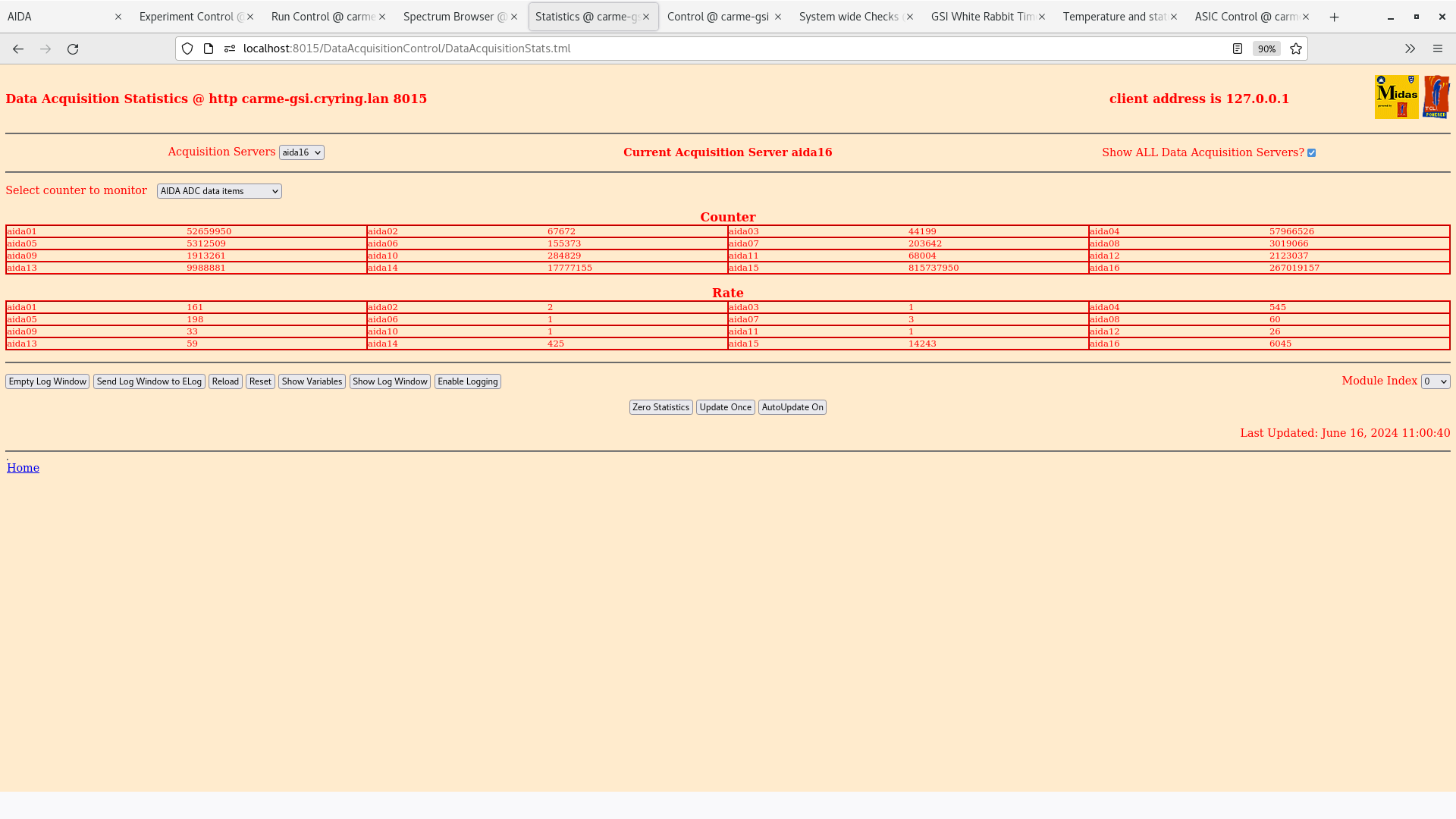

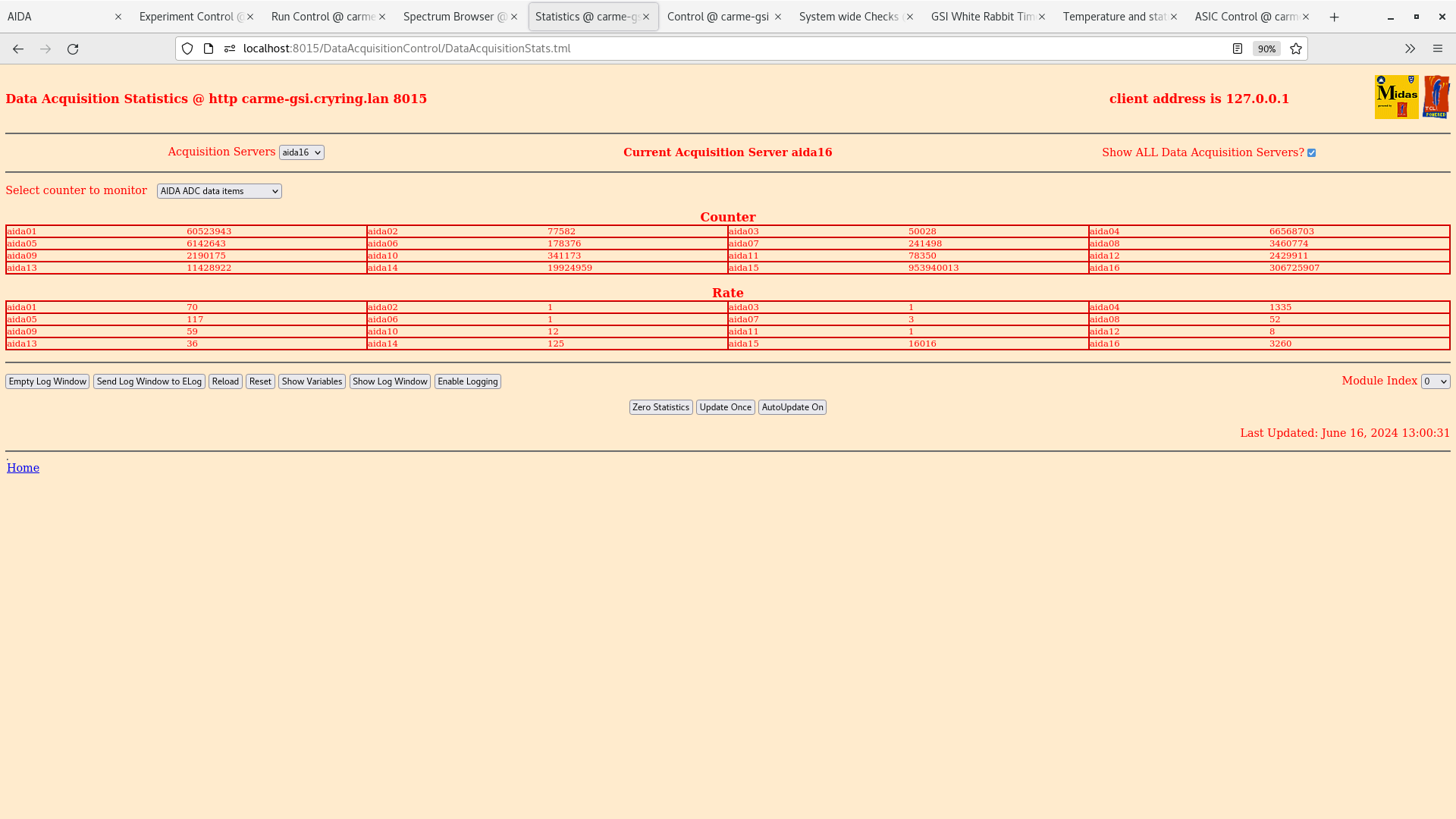

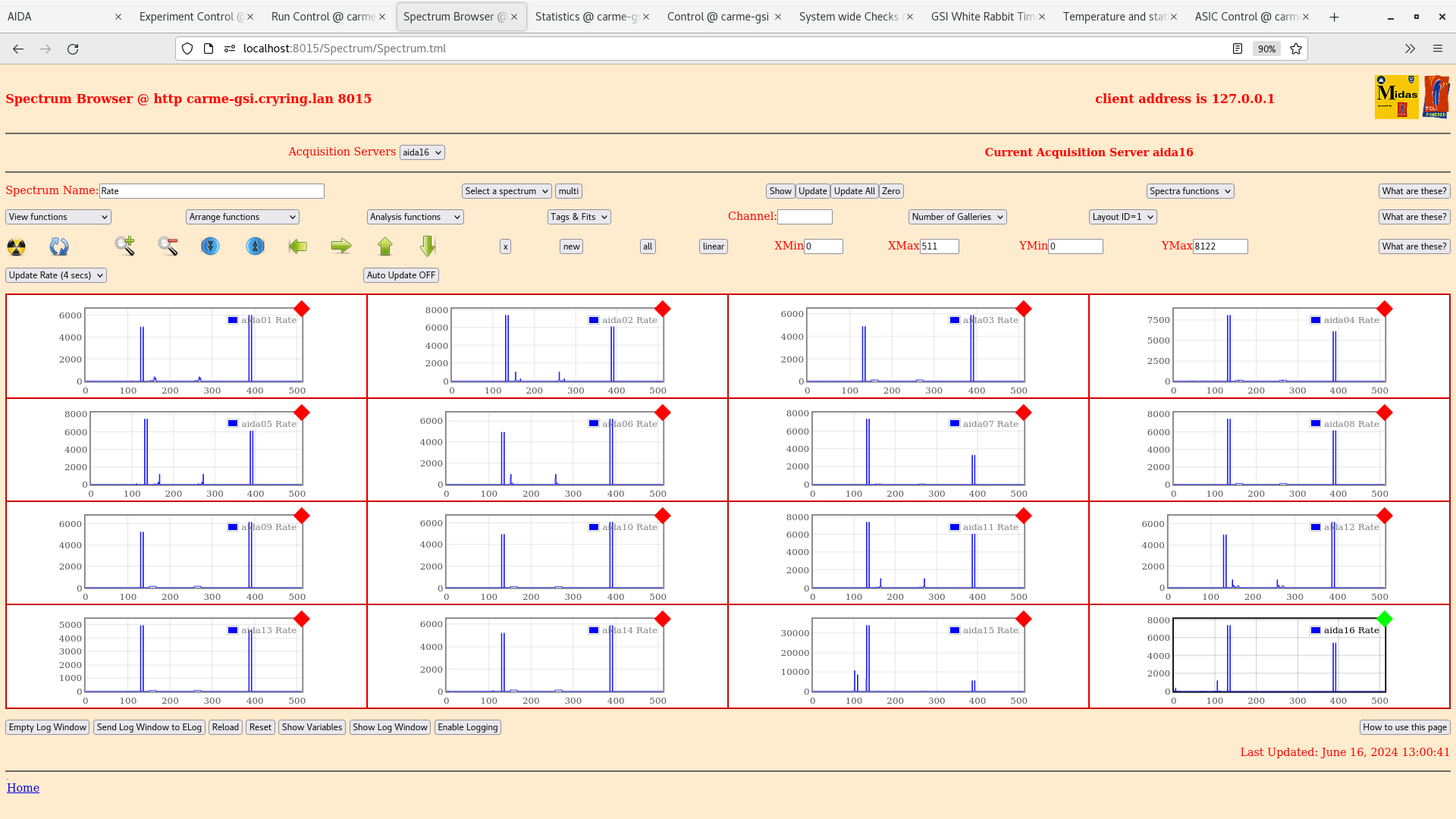

RSS | Run 77 |

Run 77 started at 06:48

Cooler voltage setpoint 247.0 V.

07:05

DSSSD bias & leakage current OK - attachments 1 & 2

FEE64 temperatures OK - attachment 3

ADC data item stats OK - attachment 4

per FEE64 Rate spectra OK - attachment 5

Beam intensity 8.45e+7 particles

Target density ~5.34E11 atoms/cm2

09:02

DSSSD bias & leakage current OK - attachments 6 & 7

FEE64 temperatures OK - attachment 8

ADC data item stats OK - attachment 9

per FEE64 Rate spectra OK - attachment 10

Beam intensity 7.85e+7 particles

Target density ~5.29E11 atoms/cm2

11:00

DSSSD bias & leakage current OK - attachments 11 & 12

FEE64 temperatures OK - attachment 13

ADC data item stats OK - attachment 14

per FEE64 Rate spectra OK - attachment 15

Beam intensity 8.5e+7 particles

Target density ~6.1E11 atoms/cm2

13:00

DSSSD bias & leakage current OK - attachments 16 & 17

FEE64 temperatures OK - attachment 18

ADC data item stats OK - attachment 19

per FEE64 Rate spectra OK - attachment 20

Beam intensity 8.2e+7 particles

Target density ~6.1E11 atoms/cm2 |

| Attachment 1: Screenshot_from_2024-06-16_07-05-18.png

|

|

| Attachment 2: Screenshot_from_2024-06-16_07-06-01.png

|

|

| Attachment 3: Screenshot_from_2024-06-16_07-05-33.png

|

|

| Attachment 4: Screenshot_from_2024-06-16_07-05-44.png

|

|

| Attachment 5: Screenshot_from_2024-06-16_07-05-53.png

|

|

| Attachment 6: Screenshot_from_2024-06-16_09-01-29.png

|

|

| Attachment 7: Screenshot_from_2024-06-16_09-02-12.png

|

|

| Attachment 8: Screenshot_from_2024-06-16_09-01-46.png

|

|

| Attachment 9: Screenshot_from_2024-06-16_09-01-55.png

|

|

| Attachment 10: Screenshot_from_2024-06-16_09-02-03.png

|

|

| Attachment 11: Screenshot_from_2024-06-16_11-00-13.png

|

|

| Attachment 12: Screenshot_from_2024-06-16_11-00-18.png

|

|

| Attachment 13: Screenshot_from_2024-06-16_11-00-33.png

|

|

| Attachment 14: Screenshot_from_2024-06-16_11-00-43.png

|

|

| Attachment 15: Screenshot_from_2024-06-16_11-00-52.png

|

|

| Attachment 16: Screenshot_from_2024-06-16_12-59-53.png

|

|

| Attachment 17: Screenshot_from_2024-06-16_13-00-04.png

|

|

| Attachment 18: Screenshot_from_2024-06-16_13-00-24.png

|

|

| Attachment 19: Screenshot_from_2024-06-16_13-00-34.png

|

|

| Attachment 20: Screenshot_from_2024-06-16_13-00-45.png

|

|

|

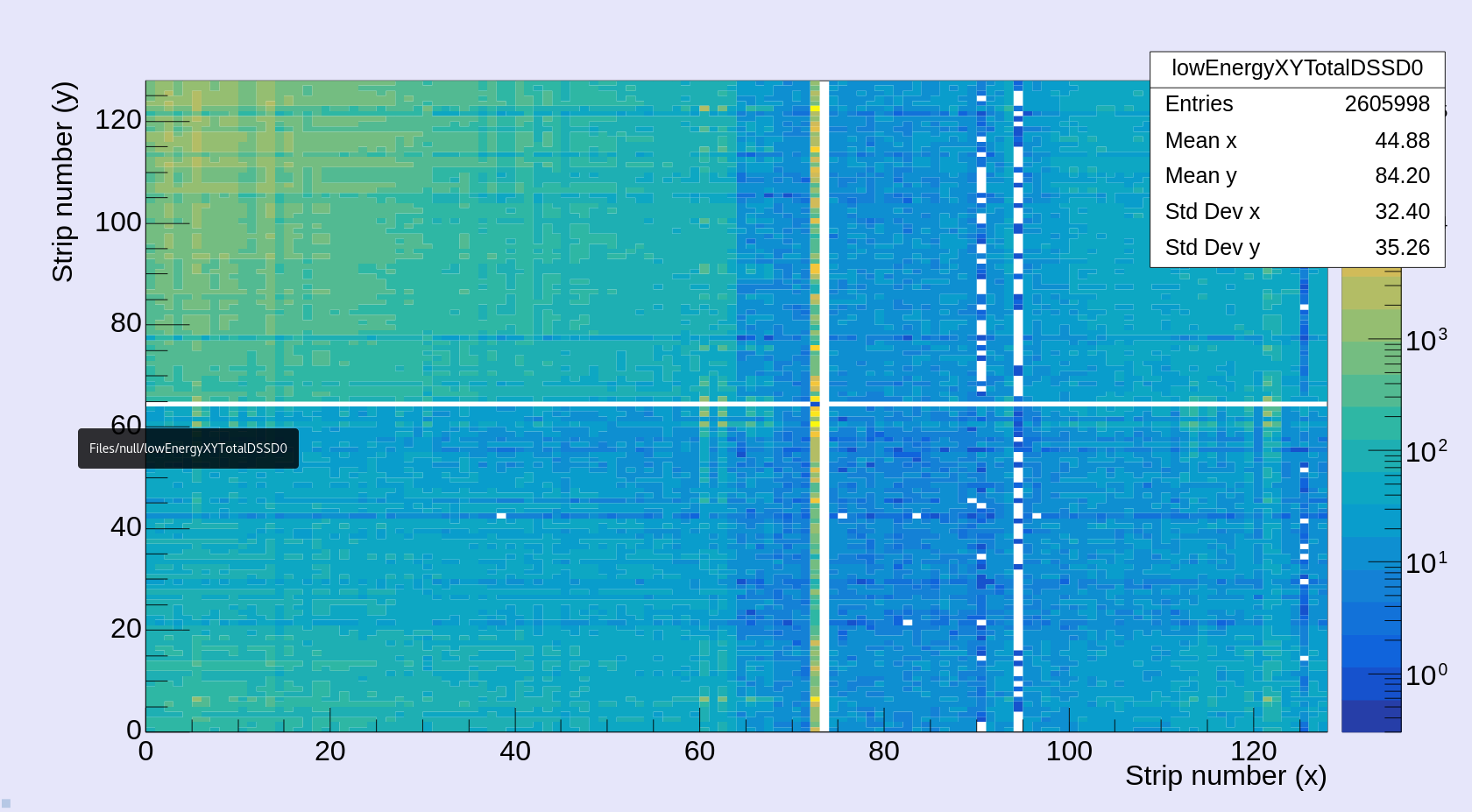

717

|

Tue Jun 3 14:54:29 2025 |

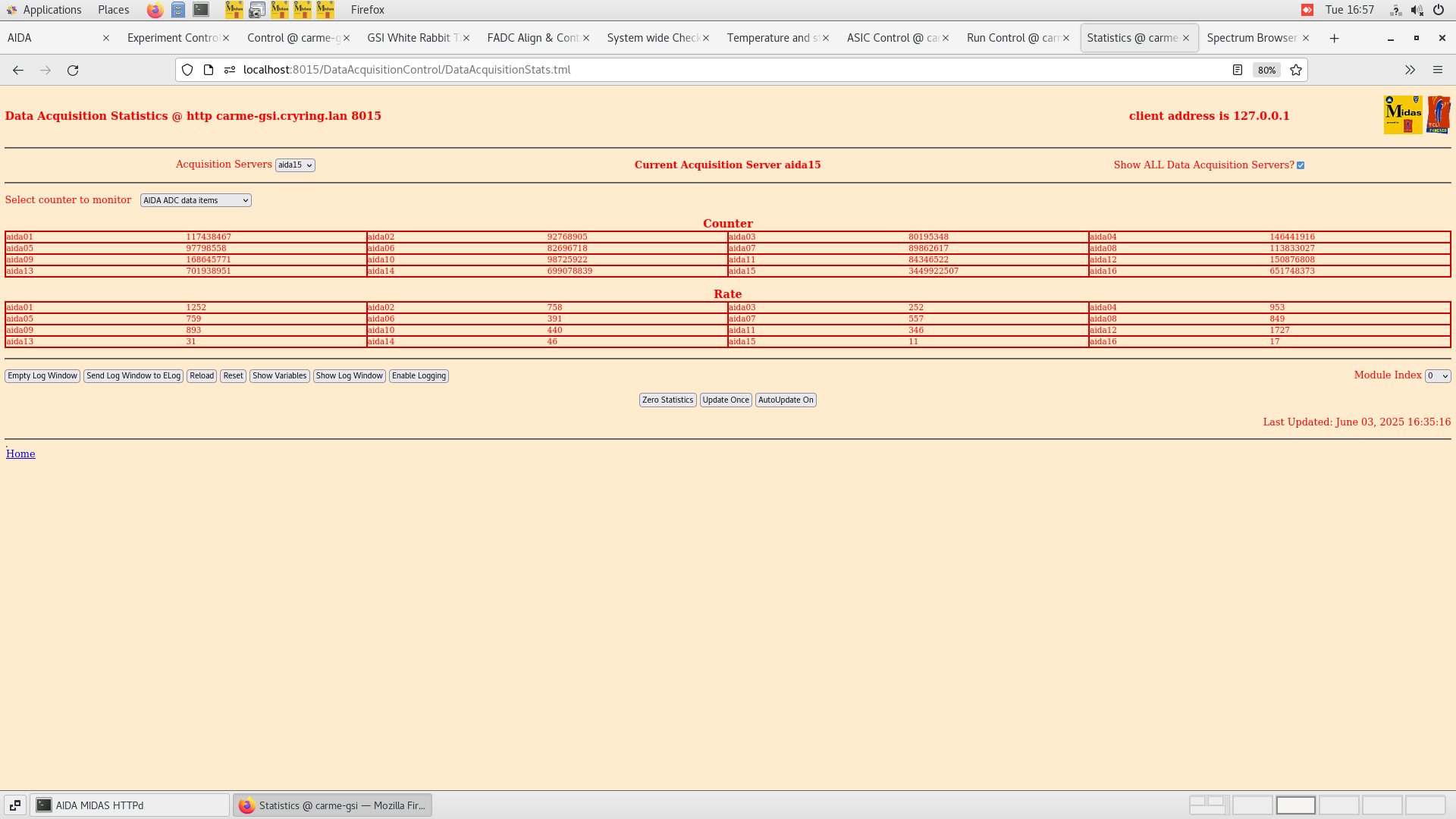

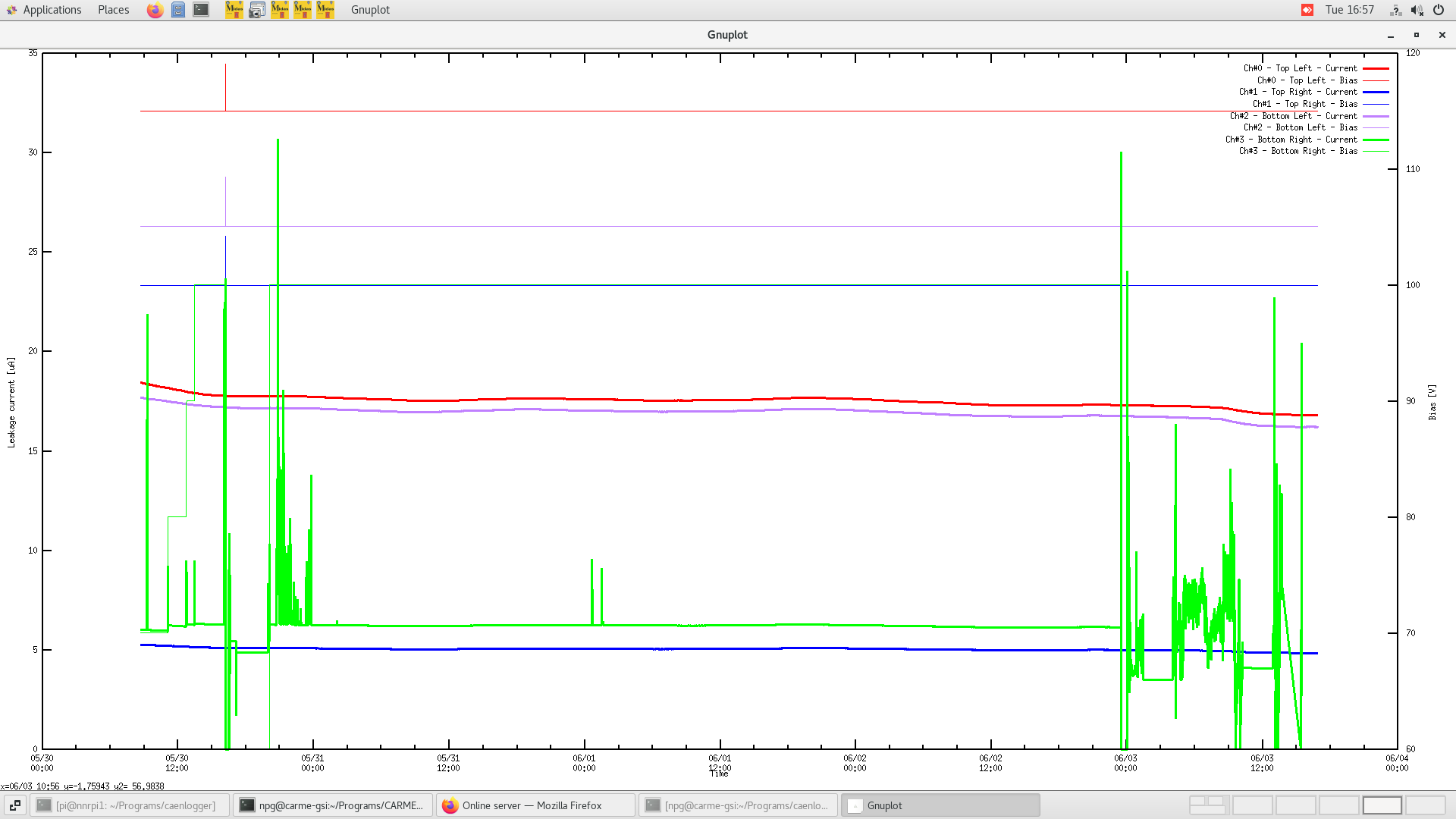

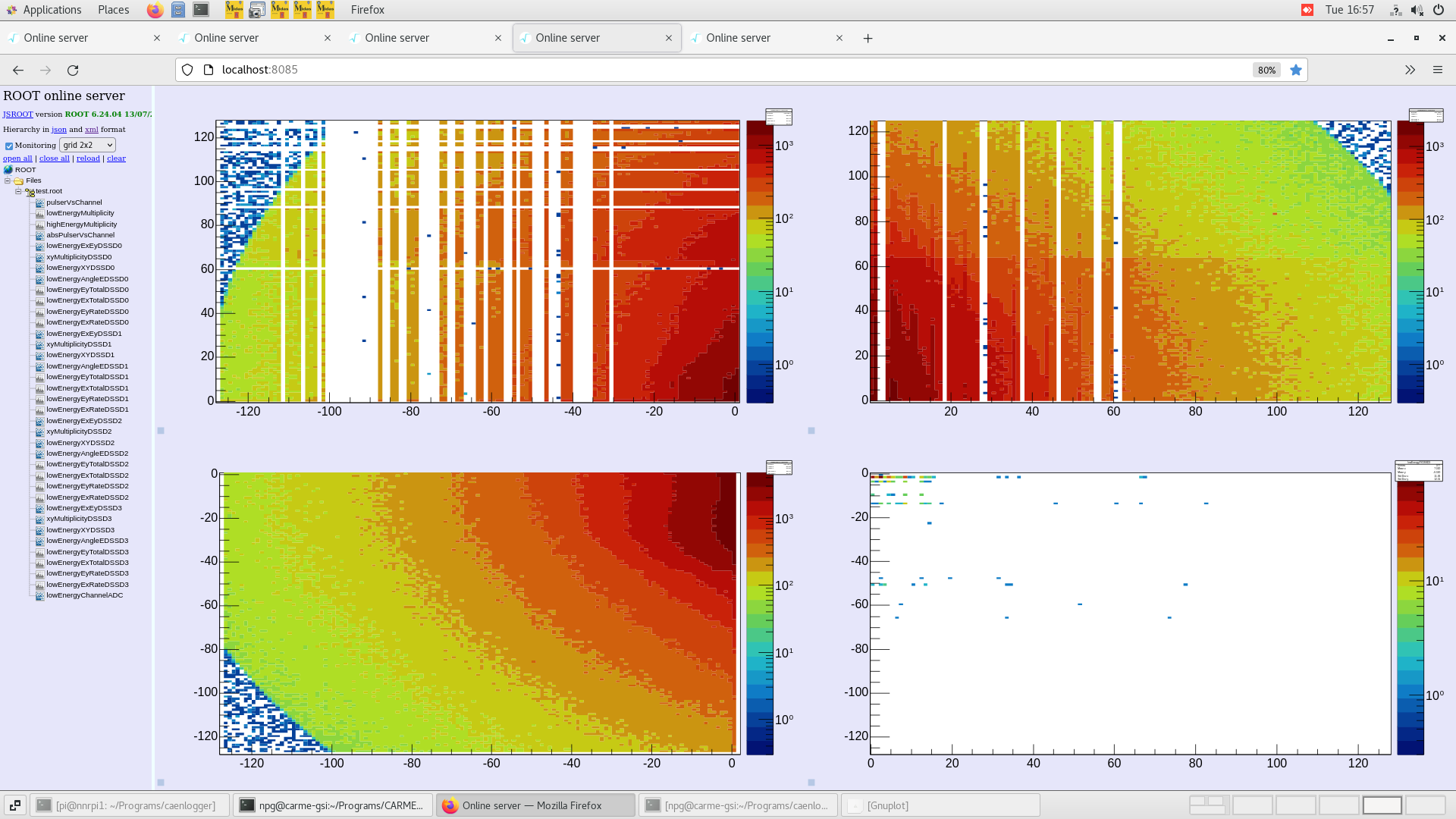

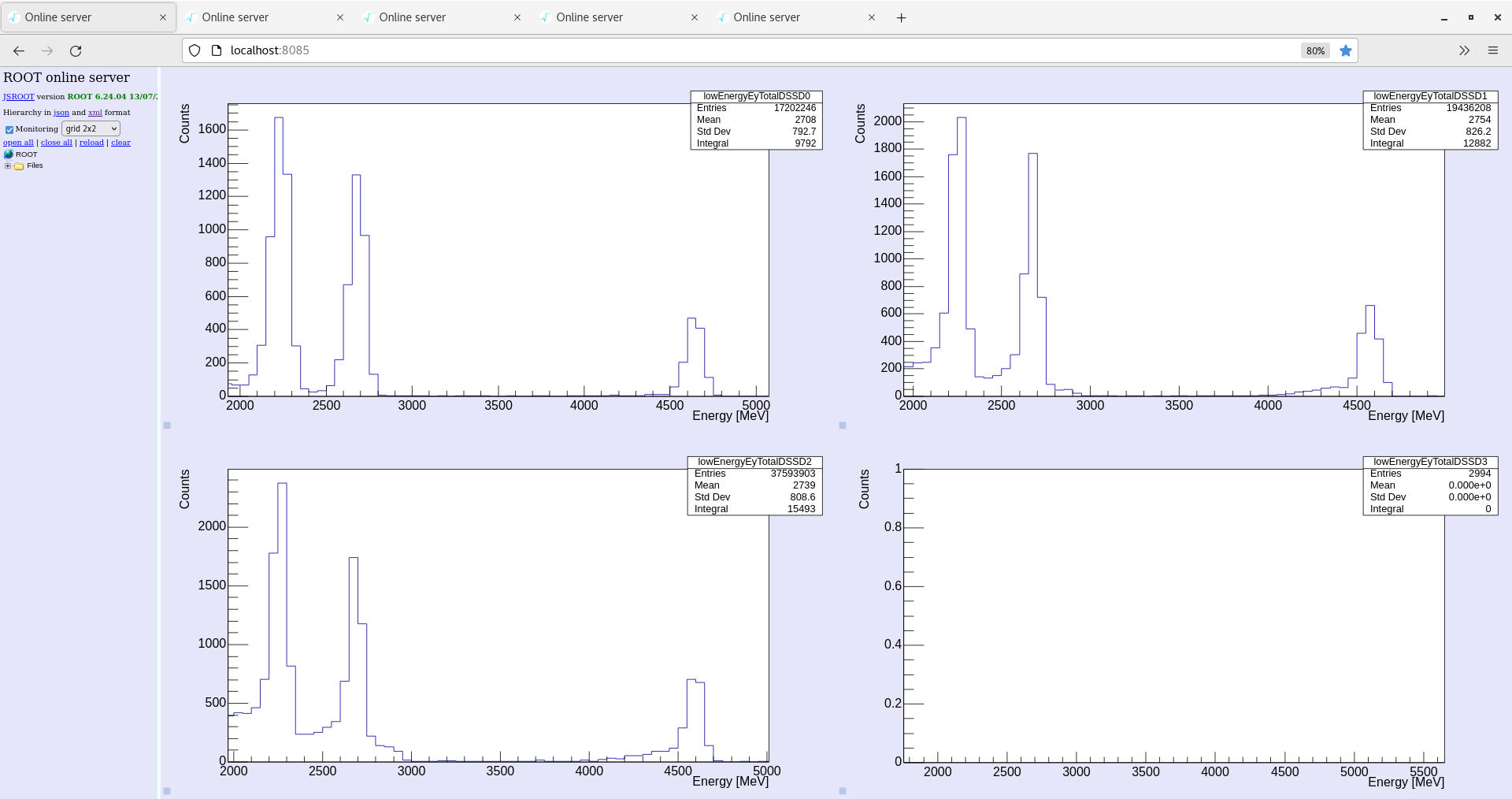

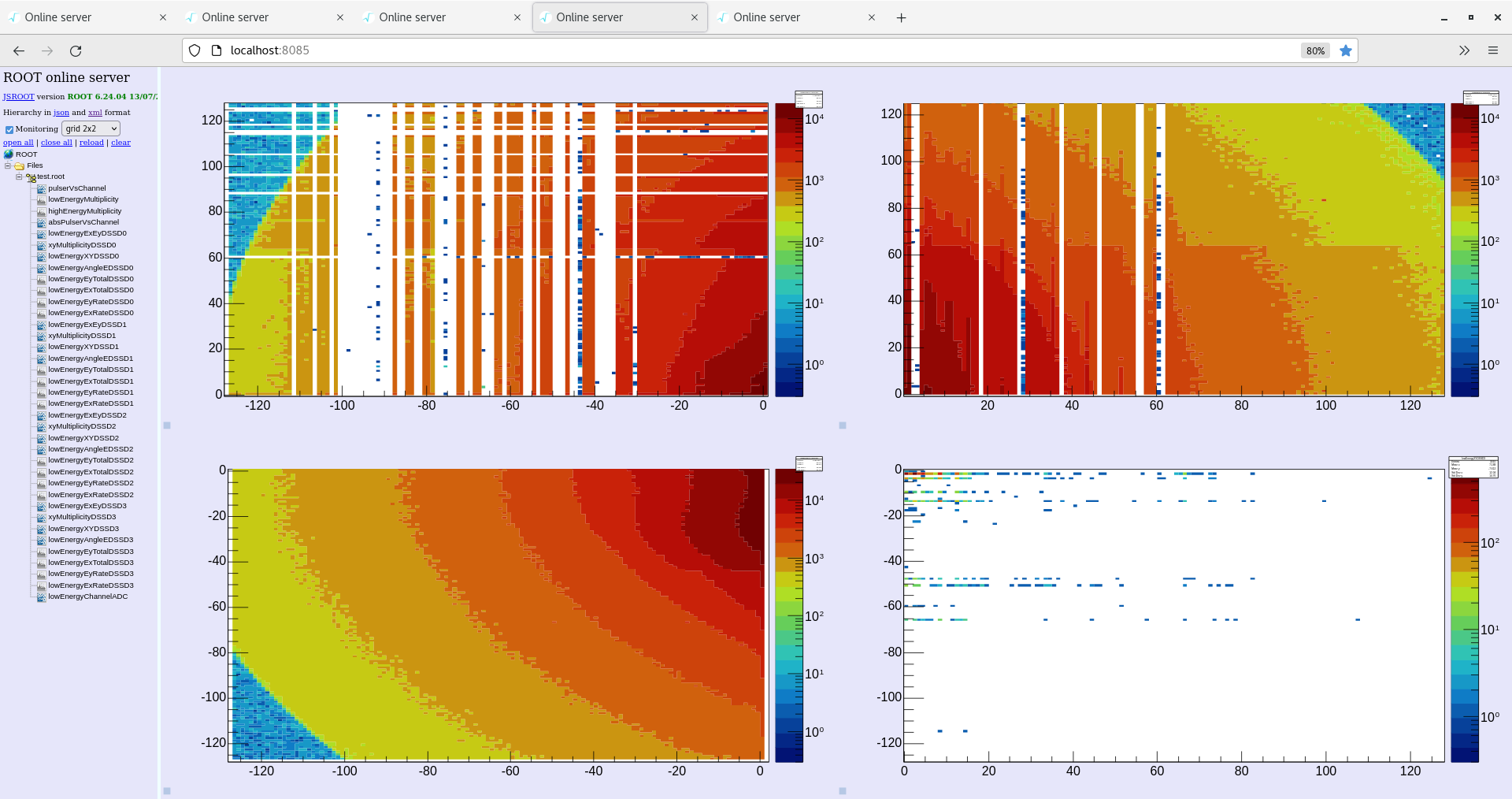

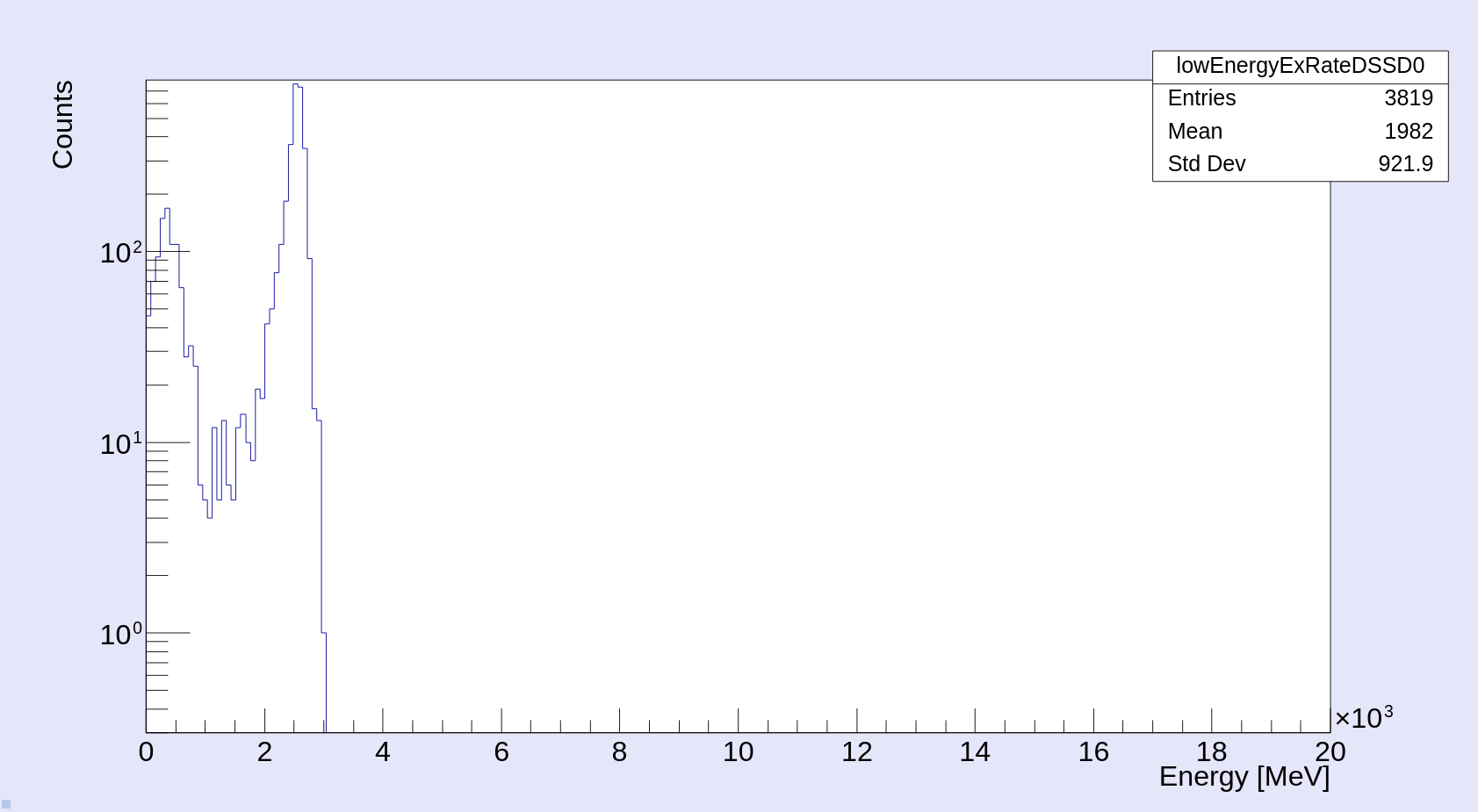

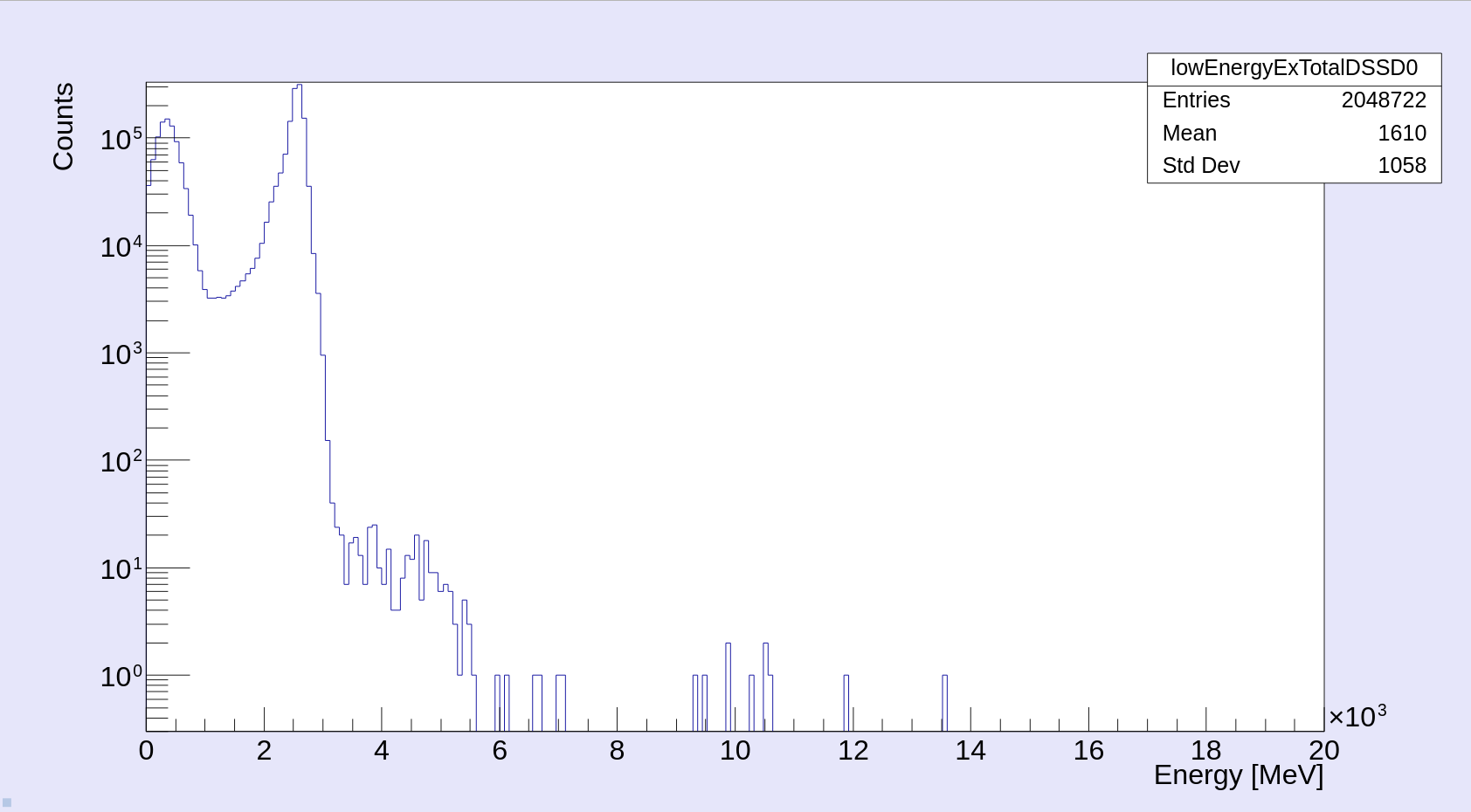

PMH, ST | Run 48 |

Run 48 started. Everything is running again. We started at 3E13 at/cm2

D+ beam deuterium target. D+ beam energy is still 0.5 MeV/u. (beam calc calculation is 0.5143 MeV/u). See previous entry for beamcalc.

All four detectors positioned fully out and stationary, however we switched off detector #4.

Left potentiometer = -3.03mm (corresponds to x = 0, which is the more trustworthy value)

Right potentiometer = 1.74 mm (corresponds to y = -500, which is the more trustworthy value)

Ring cycle time is 10 seconds.

Cooler set value = 297.2 V, 8 mA. Read value = 296.7 V, 7 mA

All leakage currents look good (except dssd4, currently turned off)

Beam position. Vertical =0.0mm , Horizontal=0.0 mm

Data rate ~ 108kB/s

16:40 Change Gasjet target Y=-500 to Y=0

17:37 Change Gasjet target Y= 0 to Y= 500

20:30 We now take some time to optimize the areal density

20:30 Change Gasjet target Y= 500 to Y= 1000 (resulting in 2E12)

20:32 Change Gasjet target Y= 1000 to Y= 500 (resulting in 4E12)

20:33 Change Gasjet target Y= 500 to Y= 0 (resulting in 7E12)

20:35 Change Gasjet target Y= 0 to Y= -500 (resulting in 1.1E13)

20:37 Change Gasjet target Y= -500 to Y= -1000 (resulting in 1.8E13, still increasing and amazing for almost 1h)

21:48: Since approximately 20min its just going down systematically from a stable 2E13 to 6E12...) Lets try another round of optimization...

21:48 Change Gasjet target Y= -1000 to Y= -1500 (starting at 7E12 and resulting in 2E12)

21:49 Change Gasjet target Y= -1500 to Y= -1000 (starting at 2E12 and resulting in 6E12)

21:50 Change Gasjet target Y= -1000 to Y= -500 (starting at 6E12 and resulting in 9E12)

21:51 Change Gasjet target Y= -500 to Y= 0 (starting at 9E12 and resulting in 1.3E13 but dropping back to 7E12 within 3min)

21:54 Change Gasjet target. Leaving Y at 0, but moving X from 0 to -500 (starting at 6E12 and resulting in 3E12)

21:55 Change Gasjet target. Leaving Y at 0, but moving X from -500 to 0 (starting at 3E12 and resulting in 4E12)

21:56 Change Gasjet target. Leaving Y at 0, but moving X from 0 to +500 (starting at 4E12 and resulting in 6E12)

21:59 Change Gasjet target. Leaving X at 500, but moving Y from 0 to +500 (starting at 5E12 and resulting in 7E11...)

22:00 Change Gasjet target. Leaving X at 500, but moving Y from +500 to 0 (starting at 7E11 and resulting in 2E12)

Side comment: It seems no matter what we do, that there is a general decrease within the last 30min...

22:00 Change Gasjet target. Leaving X at 500, but moving Y from +500 to 0 (starting at 7E11 and resulting in 2E12)

Okay... No matter what we do... Its still decreasing...

22:03 Change Gasjet target. Leaving Y at 0, but moving X from 500 to 0 (starting at 1E12 and resulting in 2E12)

22:06 Change Gasjet target. Leaving X at 0, but moving Y = 0 from to -500 (starting at 2E12 and resulting in 5E12

22:09 Change Gasjet target. Leaving X at 0, but moving Y = -500 from to -1000 (starting at 5E12 and just randomly fluctuating within the next 15min... and more decreasing than increasing...)

22:25 Change Gasjet target. Leaving X at 0, but moving Y = -1000 from to -1500 (starting at 1E12 and resulting in 2E12... )

22:31 Change Gasjet target. Leaving X at 0, but moving Y = -1500 from to -2000 (starting at 1E12 and resulting in 8E11... ) Whaaaat????

22:32 Change Gasjet target. Leaving X at 0, but moving Y = -2000 from to -1000 (starting at 9E11 and resulting in 4E12... ) Okaaaay lets wait and see...

01:00

Run stopped.

Final statistics very high. Over 10,000 counts for 3He and 3H, Over 5000 counts for proton.

Final energy histogram and xy plot on final attachments |

| Attachment 1: Screenshot_from_2025-06-03_16-57-29.png

|

|

| Attachment 2: Screenshot_from_2025-06-03_16-57-46.png

|

|

| Attachment 3: Screenshot_from_2025-06-03_16-57-55.png

|

|

| Attachment 4: Screenshot_from_2025-06-03_16-58-15.png

|

|

| Attachment 5: Screenshot_from_2025-06-04_00-54-02.png

|

|

| Attachment 6: Screenshot_from_2025-06-04_00-57-33.png

|

|

|

351

|

Tue Mar 1 17:36:04 2022 |

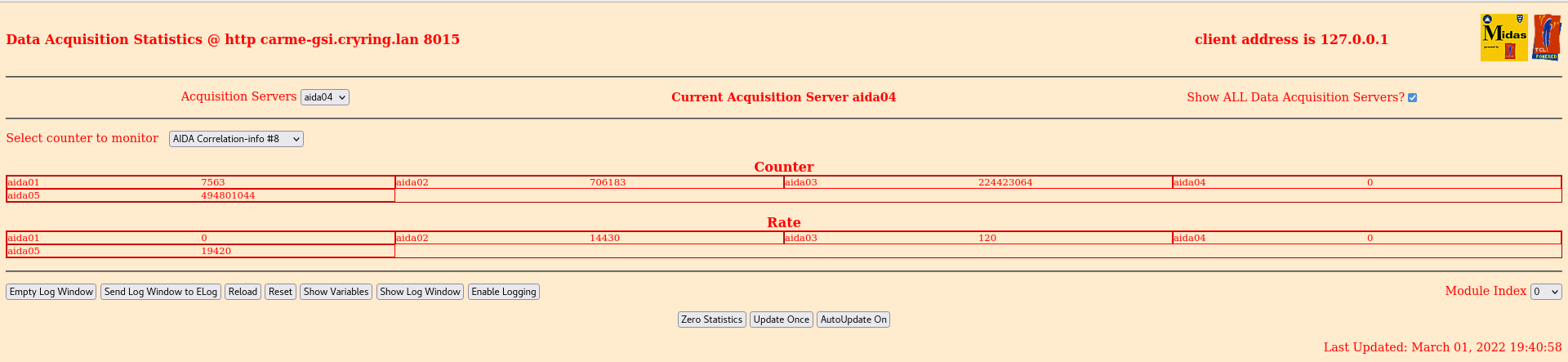

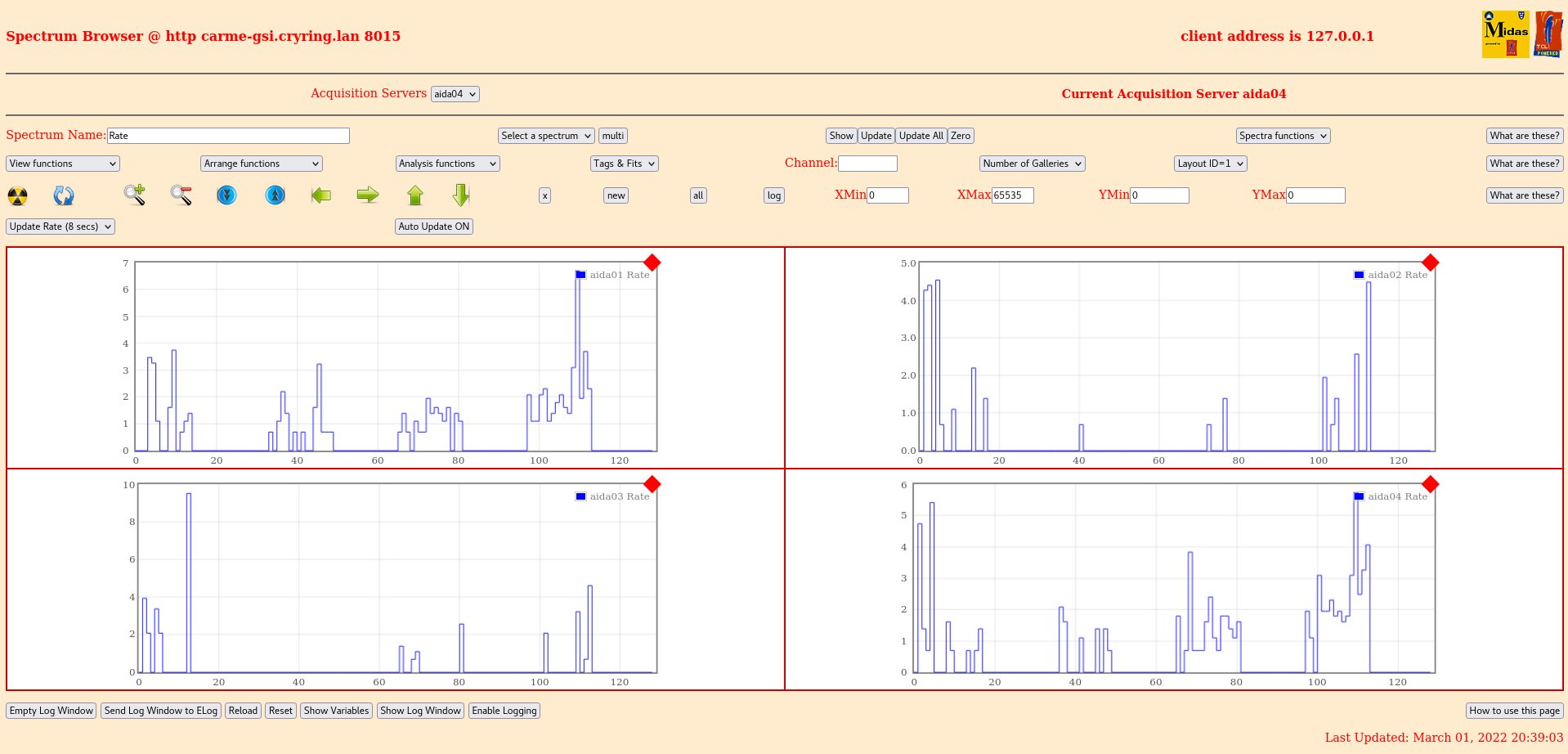

PM, LV | check |

no change:

Check Clock Status': Passed 5, Failed 0

Check ADC Calibration: Passed 5, Failed 0

'Check the White rabbit decoder status: Passed 0, Failed 5

target density at S1: 2.1-2.4e-8

temp: 116K |

| Attachment 1: Screenshot_from_2022-03-01_18-43-15.png

|

|

| Attachment 2: Screenshot_from_2022-03-01_18-42-59.png

|

|

| Attachment 3: Screenshot_from_2022-03-01_18-42-21.png

|

|

| Attachment 4: Screenshot_from_2022-03-01_18-41-49.png

|

|

| Attachment 5: Screenshot_from_2022-03-01_18-41-30.png

|

|

| Attachment 6: Screenshot_from_2022-03-01_18-41-04.png

|

|

| Attachment 7: Screenshot_from_2022-03-01_18-40-39.png

|

|

| Attachment 8: Screenshot_from_2022-03-01_18-40-07.png

|

|

| Attachment 9: Screenshot_from_2022-03-01_18-39-34.png

|

|

| Attachment 10: Screenshot_from_2022-03-01_18-39-13.png

|

|

| Attachment 11: Screenshot_from_2022-03-01_18-38-57.png

|

|

| Attachment 12: Screenshot_from_2022-03-01_18-38-41.png

|

|

| Attachment 13: Screenshot_from_2022-03-01_18-35-09.png

|

|

| Attachment 14: Screenshot_from_2022-03-01_18-34-35.png

|

|

|

352

|

Tue Mar 1 18:43:41 2022 |

PM, LV | check |

no change:

Check Clock Status': Passed 5, Failed 0

Check ADC Calibration: Passed 5, Failed 0

'Check the White rabbit decoder status: Passed 0, Failed 5

target density at S1: 2.1-2.4e-8

temp: 116K |

| Attachment 1: Screenshot_from_2022-03-01_19-42-59.png

|

|

| Attachment 2: Screenshot_from_2022-03-01_19-42-45.png

|

|

| Attachment 3: Screenshot_from_2022-03-01_19-41-54.png

|

|

| Attachment 4: Screenshot_from_2022-03-01_19-41-39.png

|

|

| Attachment 5: Screenshot_from_2022-03-01_19-41-25.png

|

|

| Attachment 6: Screenshot_from_2022-03-01_19-41-12.png

|

|

| Attachment 7: Screenshot_from_2022-03-01_19-41-00.png

|

|

| Attachment 8: Screenshot_from_2022-03-01_19-40-29.png

|

|

| Attachment 9: Screenshot_from_2022-03-01_19-40-19.png

|

|

| Attachment 10: Screenshot_from_2022-03-01_19-40-00.png

|

|

| Attachment 11: Screenshot_from_2022-03-01_19-39-40.png

|

|

| Attachment 12: Screenshot_from_2022-03-01_19-39-26.png

|

|

| Attachment 13: Screenshot_from_2022-03-01_19-39-08.png

|

|

| Attachment 14: Screenshot_from_2022-03-01_19-38-49.png

|

|

|

353

|

Tue Mar 1 19:40:28 2022 |

PM, LV | check |

no change:

Check Clock Status': Passed 5, Failed 0

Check ADC Calibration: Passed 5, Failed 0

'Check the White rabbit decoder status: Passed 0, Failed 5

target density at S1: 2.1-2.3e-8

temp: 116K

beam at injection: 7e7 |

| Attachment 1: Screenshot_from_2022-03-01_20-39-20.png

|

|

| Attachment 2: Screenshot_from_2022-03-01_20-39-06.png

|

|

| Attachment 3: Screenshot_from_2022-03-01_20-38-50.png

|

|

| Attachment 4: Screenshot_from_2022-03-01_20-38-35.png

|

|

| Attachment 5: Screenshot_from_2022-03-01_20-38-22.png

|

|

| Attachment 6: Screenshot_from_2022-03-01_20-37-52.png

|

|

| Attachment 7: Screenshot_from_2022-03-01_20-37-42.png

|

|

| Attachment 8: Screenshot_from_2022-03-01_20-37-30.png

|

|

| Attachment 9: Screenshot_from_2022-03-01_20-37-16.png

|

|

| Attachment 10: Screenshot_from_2022-03-01_20-37-00.png

|

|

| Attachment 11: Screenshot_from_2022-03-01_20-36-41.png

|

|

| Attachment 12: Screenshot_from_2022-03-01_20-36-28.png

|

|

|

354

|

Tue Mar 1 19:41:24 2022 |

PM, LV | target temperature walkthrough |

A target temperature walkthrough has been initiated at 20:41 since the target density at S1 had slightly decreased (with ~0.1-0.2)

Current temprature 116K

set to 126K at 20:41

set to 95K at 20:47:30

set to 108.5K at 21:01:30, at this temperature was a sweetspot observerd for target density.

set to 109.7 at 21:08:30

set to 110K at 21:13:30 - we keep at this value for a while. the values at S1 are changing between 2.2-2.9e-8 |

|

355

|

Tue Mar 1 20:41:28 2022 |

PM, LV | check |

no change:

Check Clock Status': Passed 5, Failed 0

Check ADC Calibration: Passed 5, Failed 0

'Check the White rabbit decoder status: Passed 0, Failed 5

target density at S1: 2.3-2.7e-8

temp: 110K

beam at injection: 7e7 |

| Attachment 1: Screenshot_from_2022-03-01_21-41-02.png

|

|

| Attachment 2: Screenshot_from_2022-03-01_21-40-45.png

|

|

| Attachment 3: Screenshot_from_2022-03-01_21-40-33.png

|

|

| Attachment 4: Screenshot_from_2022-03-01_21-40-19.png

|

|

| Attachment 5: Screenshot_from_2022-03-01_21-40-03.png

|

|

| Attachment 6: Screenshot_from_2022-03-01_21-39-35.png

|

|

| Attachment 7: Screenshot_from_2022-03-01_21-39-20.png

|

|

| Attachment 8: Screenshot_from_2022-03-01_21-39-00.png

|

|

| Attachment 9: Screenshot_from_2022-03-01_21-38-50.png

|

|

| Attachment 10: Screenshot_from_2022-03-01_21-38-31.png

|

|

| Attachment 11: Screenshot_from_2022-03-01_21-38-06.png

|

|

| Attachment 12: Screenshot_from_2022-03-01_21-37-50.png

|

|

| Attachment 13: Screenshot_from_2022-03-01_21-37-40.png

|

|

| Attachment 14: Screenshot_from_2022-03-01_21-37-27.png

|

|

|

356

|

Tue Mar 1 21:34:06 2022 |

PM, LV | check |

no change:

Check Clock Status': Passed 5, Failed 0

Check ADC Calibration: Passed 5, Failed 0

'Check the White rabbit decoder status: Passed 0, Failed 5

target density at S1: 2.2-2.7e-8

temp: 110K

beam at injection: 7e7 |

| Attachment 1: Screenshot_from_2022-03-01_22-33-08.png

|

|

| Attachment 2: Screenshot_from_2022-03-01_22-32-53.png

|

|

| Attachment 3: Screenshot_from_2022-03-01_22-32-40.png

|

|

| Attachment 4: Screenshot_from_2022-03-01_22-32-30.png

|

|

| Attachment 5: Screenshot_from_2022-03-01_22-32-18.png

|

|

| Attachment 6: Screenshot_from_2022-03-01_22-32-04.png

|

|

| Attachment 7: Screenshot_from_2022-03-01_22-31-54.png

|

|

| Attachment 8: Screenshot_from_2022-03-01_22-31-34.png

|

|

| Attachment 9: Screenshot_from_2022-03-01_22-31-20.png

|

|

| Attachment 10: Screenshot_from_2022-03-01_22-31-10.png

|

|

| Attachment 11: Screenshot_from_2022-03-01_22-30-58.png

|

|

| Attachment 12: Screenshot_from_2022-03-01_22-30-46.png

|

|

| Attachment 13: Screenshot_from_2022-03-01_22-30-31.png

|

|

| Attachment 14: Screenshot_from_2022-03-01_22-30-09.png

|

|

|

384

|

Thu Dec 8 14:41:19 2022 |

PJCS | Results of tests on AIDA PSU in DL T9 |

We opened one up and soldered a co-ax cable to one of the +6v power contacts at the output of the filter board.

Connecting this to a 'scope we observed a level of +/- 5mv noise with no FEE connected.

Connecting one FEE made little difference.

Re-connected the FEE to the power supply in the cabinet and wired a co-ax to a spare FEE power plug.

Ran the system with two FEEs on the bench top and two in the cabinet. The benchtop FEEs were connected to the NIM bin in the cabinet with copper braid.

Using a PB4 in the NIM bin and my test input cards on the FEE mezzanine connector, the following readings were taken using the 'integrate' function in the spectrum browser.

Shaping 8us, negative pulse.

aida02, ASIC1, ch0 Peak width => 16.58 channels ( full 16 bit spectra )

aida03, ASIC1, ch0 Peak width => 18.48 channels ( full 16 bit spectra )

aida04, ASIC1, ch0 Peak width => 18.05 channels ( full 16 bit spectra )

These could be better but the output of the PB4 was not perfect. I think ASIC 1 Ch0 is normally the worst on the mezzanine.

Attachments 1 to 6 are the waveforms and some zoomed in.

The co-ax from the power supply was connected to a 'scope and showed a noise level of +/-50mv.

Fourier analysis of this noise showed two peaks 109kHz and 218kHz. ( Attachments 7 & 8 ) |

| Attachment 1: IMG_5492.jpeg

|

|

| Attachment 2: IMG_5493.jpeg

|

|

| Attachment 3: IMG_5495_small.jpg

|

|

| Attachment 4: IMG_5496_small.jpg

|

|

| Attachment 5: IMG_5497_small.jpg

|

|

| Attachment 6: IMG_5498_small.jpg

|

|

| Attachment 7: IMG_5499_small.jpg

|

|

| Attachment 8: IMG_5500_small.jpg

|

|

|

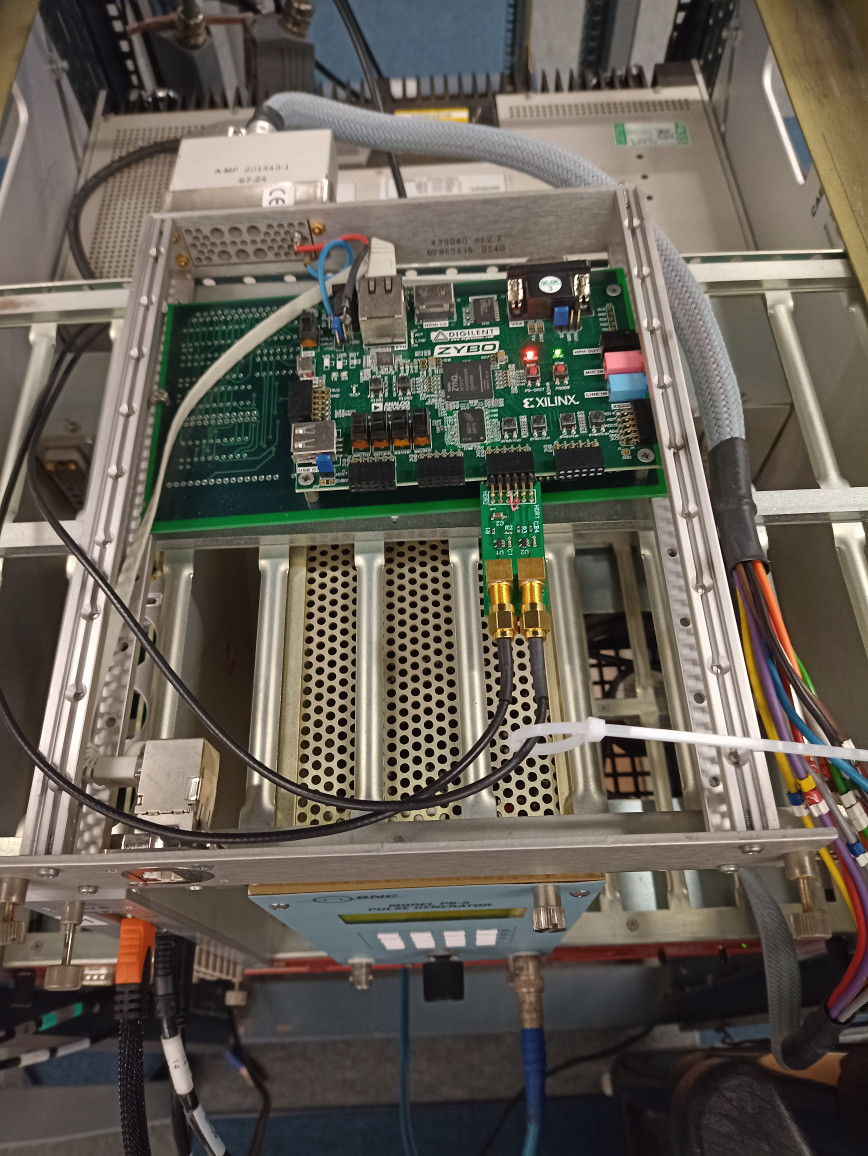

385

|

Wed Jan 18 13:32:36 2023 |

PJCS | MACB settings with either Emulator or VETAR |

When using the VITAR connected to the HDMI port of the root MACB the settings for all the MACB in the system 0x3.

This setting takes the Clock and Data line from the input HDMI and outputs it via teh HDMI output ports.

When using the Emulator connected via the SMA connectors on the back of the root MACB then the setting for the root MACB should be 0xD and all others should be 0x3.

Attached is the .jed file for programming the MACB and the .vhd source file to help with understanding of the settings. |

| Attachment 1: macb_apr20.jed

|

| Attachment 2: macb_apr20.vhd

|

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 17:03:27 03/16/2011

-- Design Name:

-- Module Name: macb_top - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

library UNISIM;

use UNISIM.VComponents.all;

-- NOTE all in/out notations are relative to this unit

entity macb_apr20 is

Port (

port1_sp : inout STD_LOGIC_VECTOR (3 downto 0);

port2_sp : inout STD_LOGIC_VECTOR (3 downto 0);

port3_sp : inout STD_LOGIC_VECTOR (3 downto 0);

port4_sp : inout STD_LOGIC_VECTOR (3 downto 0);

layer_sp : inout STD_LOGIC_VECTOR (3 downto 0);

layer_trigger : out std_logic ;

sync_return : in STD_LOGIC_VECTOR (3 downto 1);

selector : in STD_LOGIC_VECTOR (3 downto 0);

sync_select : out STD_LOGIC_vector(1 downto 0 );

clock200_select : out STD_LOGIC_vector( 1 downto 0 ) ;

butis_divide_reset : out std_logic ;

butis_divide_s : out std_logic_vector( 2 downto 0 ) ;

clock_5 : in std_logic ;

sync_5 : in std_logic ;

trigger : in std_logic_vector( 3 downto 0 ) ;

MBS_in : in STD_LOGIC_VECTOR (3 downto 0);

MBS_out : out STD_LOGIC_VECTOR (3 downto 0));

end macb_apr20;

architecture Behavioral of macb_apr20 is

signal port1_spi : STD_LOGIC_VECTOR (3 downto 0) := ( others => '0' );

signal port1_spo : STD_LOGIC_VECTOR (3 downto 0) := ( others => '0' );

signal port1_t : STD_LOGIC_VECTOR (3 downto 0) := ( others => '1' );

signal port2_spi : STD_LOGIC_VECTOR (3 downto 0) := ( others => '0' );

signal port2_spo : STD_LOGIC_VECTOR (3 downto 0) := ( others => '0' );

signal port2_t : STD_LOGIC_VECTOR (3 downto 0) := ( others => '1' );

signal port3_spi : STD_LOGIC_VECTOR (3 downto 0) := ( others => '0' );

signal port3_spo : STD_LOGIC_VECTOR (3 downto 0) := ( others => '0' );

signal port3_t : STD_LOGIC_VECTOR (3 downto 0) := ( others => '1' );

signal port4_spi : STD_LOGIC_VECTOR (3 downto 0) := ( others => '0' );

signal port4_spo : STD_LOGIC_VECTOR (3 downto 0) := ( others => '0' );

signal port4_t : STD_LOGIC_VECTOR (3 downto 0) := ( others => '1' );

signal layer_spi : STD_LOGIC_VECTOR (3 downto 0) := ( others => '0' );

signal layer_spo : STD_LOGIC_VECTOR (3 downto 0) := ( others => '0' );

signal layer_t : STD_LOGIC_VECTOR (3 downto 0) := ( others => '1' );

signal seli : integer range 0 to 15 := 0 ;

-- well really

signal MBS_in_n : std_logic_vector( 3 downto 0 ) := "0000" ;

begin

MBS_in_n <= ( not MBS_in);

seli <= conv_integer(not selector) ;

-- MBS signal allocations to sp lines and HDMI pin. This maps to NIM connections

-- 0 : MBS_clock10 SP0 13

-- 1 : MBS_reset SP1 14

-- 2 : MBS_reset_rq SP2 15

-- 3 : MBS_Trigger SP3 16

layer_trigger <= trigger(0) or trigger(1) or trigger(2) or trigger(3) ;

-- divider controls set for pass-through

butis_divide_reset <= '1' ; -- for now don't reset ;

process ( seli , MBS_in_n, port1_spi, port2_spi, port3_spi, port4_spi, layer_spi, sync_return ,sync_5 )

-- note : & => concatenate

begin

case seli is

when 0 => --- Master/ Root / MBS / Internal clock

port1_spo <= MBS_in_n(3) & MBS_in_n(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= ( others => '0' ) ;

layer_t <= ( others => '1' ) ; -- disable the drive to the "next" port

sync_select <= "00" ; -- select sync from port 1

clock200_select <= "00" ; -- select internal 200 MHz oscillator

MBS_out <= MBS_in_n(3) & MBS_in_n(2) & port1_spi(1) & port1_spi(0) ;

butis_divide_s <= "000" ; -- s2 is 0 for pass,

when 1 => --- Master/ Root / MBS / BuTiS clock and SYNC

port1_spo <= MBS_in_n(3) & MBS_in_n(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= ( others => '0' ) ;

layer_t <= ( others => '1' ) ; -- disable the drive to the "next" port

sync_select <= "01" ; -- select sync from external using SMA input

clock200_select <= "01" ; -- select external 200 MHz oscillator using SMA input

MBS_out <= MBS_in_n(3) & MBS_in_n(2) & port1_spi(1) & port1_spi(0) ;

butis_divide_s <= "000" ; -- s2 is 0 for pass,

when 2 => --- Master/ Branch / MBS / Next layer clock next layer SYNC

port1_spo <= layer_spi(3) & layer_spi(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= layer_spi(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= layer_spi(3) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= layer_spi(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= '0' & '0' & port1_spi(1) & port1_spi(0) ; -- drive the clock and reset down a layer

layer_t <= "1100" ; -- just drive the bottom two bits to the "next" port

sync_select <= "10" ; -- select sync from next_layer

clock200_select <= "10" ; -- select clock from next layer

MBS_out <= layer_spi(3) & layer_spi(2) & port1_spi(1) & port1_spi(0) ;

butis_divide_s <= "000" ; -- s2 is 0 for pass,

when 3 => --- Slave / Branch / MBS / Next layer clock and sync

port1_spo <= layer_spi(3) & '0' & layer_spi(1) & layer_spi(0);

port1_t <= "0100" ; -- drive clock, reset, trigger only

port2_spo <= layer_spi(3) & '0' & layer_spi(1) & layer_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= layer_spi(3) & '0' & layer_spi(1) & layer_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= layer_spi(3) & '0' & layer_spi(1) & layer_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= '0' & '0' & '0' & '0' ; -- drive nothing

layer_t <= "1111" ; -- just drive nothing down

sync_select <= "10" ; -- select sync from next layer

clock200_select <= "10" ; -- select clock from next layer

MBS_out <= layer_spi ; -- map all the signals for monitoring ?

butis_divide_s <= "000" ; -- s2 is 0 for pass,

when 4 => --- Master/ Root / MBS / BuTiS clock / Internal SYNC / External timestamp reset

port1_spo <= MBS_in_n(3) & '0' & MBS_in_n(1) & '0' ;

port1_t <= "0100" ; -- drive clock, reset, trigger only

port2_spo <= MBS_in_n(3) & '0' & MBS_in_n(1) & '0' ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & MBS_in_n(1) & '0' ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & MBS_in_n(1) & '0' ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= ( others => '0' ) ;

layer_t <= ( others => '1' ) ; -- disable the drive to the "next" port

sync_select <= "00" ; -- select sync from port 1

clock200_select <= "01" ; -- select external 50 MHz oscillator using SMA input

MBS_out <= MBS_in_n(3) & MBS_in_n(2) & MBS_in_n(1) & sync_5 ;

butis_divide_s <= "000" ; -- s2 is 0 for pass,

when 5 => --- Master/ Root / MBS / External 50Mhz clock / Internal Sync

port1_spo <= MBS_in_n(3) & MBS_in_n(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= ( others => '0' ) ;

layer_t <= ( others => '1' ) ; -- disable the drive to the "next" port

sync_select <= "00" ; -- select sync from port 1

clock200_select <= "01" ; -- select external SMA input

MBS_out <= MBS_in_n(3) & MBS_in_n(2) & port1_spi(1) & port1_spi(0) ;

butis_divide_s <= "000" ; -- s2 is 0 for pass through.

when 6 => --- Master/ Root / MBS / External 100Mhz clock / Internal Sync

port1_spo <= MBS_in_n(3) & MBS_in_n(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= ( others => '0' ) ;

layer_t <= ( others => '1' ) ; -- disable the drive to the "next" port

sync_select <= "00" ; -- select sync from port 1

clock200_select <= "01" ; -- select external SMA input

MBS_out <= MBS_in_n(3) & MBS_in_n(2) & port1_spi(1) & port1_spi(0) ;

butis_divide_s <= "100" ; -- s2 is 1 for external, 00 for /2.

when 7 => --- Fast NIM input for each FEE / Next layer clock next layer SYNC

port1_spo <= MBS_in_n(0) & layer_spi(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(1) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(2) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= '0' & '0' & port1_spi(1) & port1_spi(0) ; -- drive the clock and reset down a layer

layer_t <= "1100" ; -- just drive the bottom two bits to the "next" port

sync_select <= "10" ; -- select sync from next_layer

clock200_select <= "10" ; -- select clock from next layer

MBS_out <= layer_spi(3) & layer_spi(2) & port1_spi(1) & port1_spi(0) ;

butis_divide_s <= "000" ; -- s2 is 0 for pass,

when 8 => --- Fast NIM input from Input 3 for each FEE / Next layer clock next layer SYNC

port1_spo <= MBS_in_n(3) & layer_spi(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= '0' & '0' & port1_spi(1) & port1_spi(0) ; -- drive the clock and reset down a layer

layer_t <= "1100" ; -- just drive the bottom two bits to the "next" port

sync_select <= "10" ; -- select sync from next_layer

clock200_select <= "10" ; -- select clock from next layer

MBS_out <= layer_spi(3) & layer_spi(2) & port1_spi(1) & port1_spi(0) ;

butis_divide_s <= "000" ; -- s2 is 0 for pass,

when 9 => --- Master/ Root / Internal clock / sync_returns to NIM

port1_spo <= MBS_in_n(3) & MBS_in_n(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= ( others => '0' ) ;

layer_t <= ( others => '1' ) ; -- disable the drive to the "next" port

sync_select <= "00" ; -- select sync from port 1

clock200_select <= "00" ; -- select internal 200 MHz oscillator

MBS_out <= sync_return(3) & sync_return(2) & sync_return(1) & '0' ;

butis_divide_s <= "000" ; -- s2 is 0 for pass,

when 10 => --- Master/ Root / MBS / BuTiS clock /2 and SYNC

port1_spo <= MBS_in_n(3) & MBS_in_n(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= "0000" ;

layer_t <= ( others => '1' ) ; -- disable the drive to the "next" port

sync_select <= "01" ; -- select sync from external using SMA input

clock200_select <= "01" ; -- select external 200 MHz oscillator using SMA input

MBS_out <= MBS_in_n ; -- for testing NIM I/O

butis_divide_s <= "100" ; -- s2 = 1 and s1,s0 decode to 00=>/2 , 01=>/4, /8 , /16

when 12 => --- Master/ Root / MBS / BuTiS clock /2 and SYNC

port1_spo <= MBS_in_n(3) & MBS_in_n(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= ( others => '0' ) ;

layer_t <= ( others => '1' ) ; -- disable the drive to the "next" port

sync_select <= "01" ; -- select sync from external using SMA input

clock200_select <= "01" ; -- select external 200 MHz oscillator using SMA input

MBS_out <= MBS_in_n(3) & MBS_in_n(2) & port1_spi(1) & port1_spi(0) ;

butis_divide_s <= "100" ; -- s2 = 1 and s1,s0 decode to 00=>/2 , 01=>/4, /8 , /16

when 13 => --- Master/ Root / MBS / BuTiS clock /4 and SYNC

port1_spo <= MBS_in_n(3) & MBS_in_n(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port3_t <= "0100" ; -- drive clock, reset, trigger only

port4_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port4_t <= "0100" ; -- drive clock, reset, trigger only

layer_spo <= ( others => '0' ) ;

layer_t <= ( others => '1' ) ; -- disable the drive to the "next" port

sync_select <= "01" ; -- select sync from external using SMA input

clock200_select <= "01" ; -- select external 200 MHz oscillator using SMA input

MBS_out <= MBS_in_n(3) & MBS_in_n(2) & port1_spi(1) & port1_spi(0) ;

butis_divide_s <= "101" ; -- s2 = 1 and s1,s0 decode to 01=>/4

when 14 => --- Master/ Root / MBS / BuTiS clock /8 and SYNC

port1_spo <= MBS_in_n(3) & MBS_in_n(2) & '0' & '0' ;

port1_t <= "0011" ; -- drive trigger and reset request only

port2_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

port2_t <= "0100" ; -- drive clock, reset, trigger only

port3_spo <= MBS_in_n(3) & '0' & port1_spi(1) & port1_spi(0) ;

... 161 more lines ...

|

| Attachment 3: zybo.jpg

|

|

| Attachment 4: MACB.jpg

|

|

|

478

|

Sat Jan 27 20:38:15 2024 |

PJCS | [INFO] Steps to diagnose White Rabbit problems |

This is a suggested sequence of actions to help with the current problem with the White Rabbit timestamp distribution. Test the system between each intervention. If a test provides an answer to the problem then proceed accordingly rather than continue with the suggestions.

- Please sketch the current MACB wiring.

- Unplug and replug the connectors of the VETAR HDMI connecting cable. If possible clean the pcb and cable HDMI connectors with contact cleaner.

- Disconnect the VETAR and connect the Emulator. If the clocks are not correct then at the Local and Waveform control page change the entry for LMK03200 control register at offset 5 to 0xB. If clocks are now ok then repeat for all the FEEs. Be aware that this value will be set back to 0x1B during SETUP. If the Emulator fails then continue with VETAR and setting 0x1B.

- Connect one or more FEE64 to the base MACB.

- Change the base MACB and repeat the test above.

- Connect a FEE to the VETAR direct.

I am at present unable to advise further. However should there be more then I will update this entry. |

|

263

|

Wed Feb 23 22:29:50 2022 |

PE, EM, CB (remotely) | check - 23:30 |

Motor position ok

Data rate: 1030kbytes/s

T ok

System wide check ok

plots uploaded

DAQ crashed soon afterwards |

|

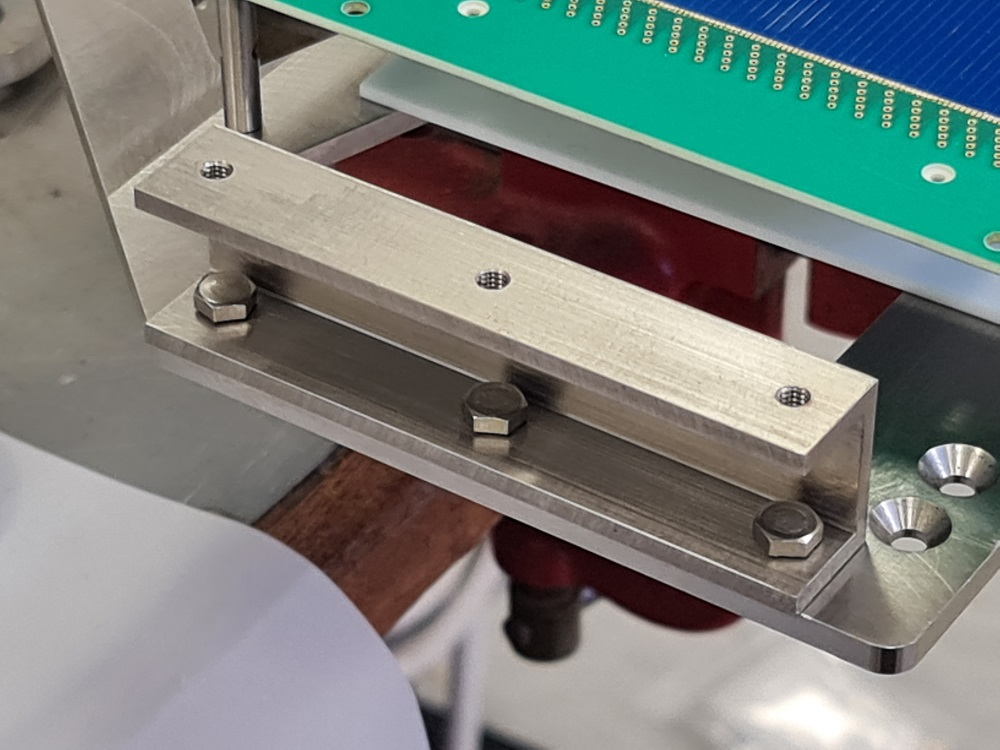

109

|

Wed Oct 6 09:39:59 2021 |

PB CB | Original dirty assembly of CARME internals |

PB found pictures of the original dirty assembly, before screws and components were shipped to DL.

See attached. |

| Attachment 1: 20210202_121656.jpg

|

|

| Attachment 2: 20210202_122403.jpg

|

|

| Attachment 3: 20210202_122522.jpg

|

|

| Attachment 4: 20210202_123119.jpg

|

|

| Attachment 5: 20210202_123124.jpg

|

|

| Attachment 6: 20210202_123500.jpg

|

|

| Attachment 7: 20210202_124224.jpg

|

|

|

182

|

Mon Jan 31 08:58:38 2022 |

OH, TD, JM | centos server configuration |

Steps taken:

- MIDAS_Releases, Embedded and Exports files brought across from the previously working SL6 aida-gsi install. Brought as tar balls to preserve ownership

- dhcpd.conf set up with same IP addresses as used on the SL6 install from aida-gsi

- nfs-utils package installed on centos7

- Paths to directories listed in /etc/exports checked that they point to the correct locations on the centos system

- Firewall disabled to confirm that it is not interfering

- setenforce 0 to confirm selinux is not interfering.

- Attachment 1 Screenshot of FEE console for aida04 as it stops booting.

- Attachment 2 text dump of /var/log/messages during the FEE boot sequence

- Attachment 3 text dump from tcpdump filtered to aida04

- Attachment 4 /var/lib/dhcp/dhcp.leases file as mentioned in the /var/log/messages dump

- Attachment 5 A copy of dhcpd.conf

- Attachment 6 A copy of /etc/hosts

- Attachment 7 A copy of /etc/exports

- Attachment 8 Text dump of ifconfig -a (Note the FEEs are conencted to p4p1)

From the messages dump it seems there is an issue being encountered with dhcp leases for the static IP addresses of the FEEs. They are then getting assigned new IP addresses which are getting put in the leases file. |

| Attachment 1: 220131_0950_FEE_CONSOLE.png

|

|

| Attachment 2: 220131_0951_logmessages.txt

|

an 31 09:48:40 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:d0:05 via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:d0:05 via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPOFFER on 192.168.11.3 to d8:80:39:41:d0:05 via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.3 (192.168.11.99) from d8:80:39:41:d0:05 via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.3 (192.168.11.99) from d8:80:39:41:d0:05 via p4p1: unknown lease 192.168.11.3.

Jan 31 09:48:40 carme-gsi dhcpd: DHCPACK on 192.168.11.3 to d8:80:39:41:d0:05 via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:b4:0b via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPOFFER on 192.168.11.5 to d8:80:39:41:b4:0b via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:b4:0b via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:d7:cd via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:d7:cd via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPOFFER on 192.168.11.8 to d8:80:39:41:d7:cd via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.5 (192.168.11.99) from d8:80:39:41:b4:0b via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPACK on 192.168.11.5 to d8:80:39:41:b4:0b via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.5 (192.168.11.99) from d8:80:39:41:b4:0b via p4p1: unknown lease 192.168.11.5.

Jan 31 09:48:40 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.8 (192.168.11.99) from d8:80:39:41:d7:cd via p4p1: unknown lease 192.168.11.8.

Jan 31 09:48:40 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.8 (192.168.11.99) from d8:80:39:41:d7:cd via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPACK on 192.168.11.8 to d8:80:39:41:d7:cd via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:d8:20 via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPOFFER on 192.168.11.6 to d8:80:39:41:d8:20 via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:d8:20 via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.6 (192.168.11.99) from d8:80:39:41:d8:20 via p4p1

Jan 31 09:48:40 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.6 (192.168.11.99) from d8:80:39:41:d8:20 via p4p1: unknown lease 192.168.11.6.

Jan 31 09:48:40 carme-gsi dhcpd: DHCPACK on 192.168.11.6 to d8:80:39:41:d8:20 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:d7:c2 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPOFFER on 192.168.11.4 to d8:80:39:41:d7:c2 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:d7:c2 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.4 (192.168.11.99) from d8:80:39:41:d7:c2 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.4 (192.168.11.99) from d8:80:39:41:d7:c2 via p4p1: unknown lease 192.168.11.4.

Jan 31 09:48:41 carme-gsi dhcpd: DHCPACK on 192.168.11.4 to d8:80:39:41:d7:c2 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:42:0d:0c via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:42:0d:0c via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:b4:16 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:b4:16 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPOFFER on 192.168.11.7 to d8:80:39:41:b4:16 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.7 (192.168.11.99) from d8:80:39:41:b4:16 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.7 (192.168.11.99) from d8:80:39:41:b4:16 via p4p1: unknown lease 192.168.11.7.

Jan 31 09:48:41 carme-gsi dhcpd: DHCPACK on 192.168.11.7 to d8:80:39:41:b4:16 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:d8:2b via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPDISCOVER from d8:80:39:41:d8:2b via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPOFFER on 192.168.11.2 to d8:80:39:41:d8:2b via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.2 (192.168.11.99) from d8:80:39:41:d8:2b via p4p1: unknown lease 192.168.11.2.

Jan 31 09:48:41 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.2 (192.168.11.99) from d8:80:39:41:d8:2b via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPACK on 192.168.11.2 to d8:80:39:41:d8:2b via p4p1

Jan 31 09:48:41 carme-gsi rpc.mountd[79344]: authenticated mount request from 192.168.11.3:956 for /home/Embedded/XilinxLinux/ppc_4xx/rfs/aida03 (/home/Embedded/XilinxLinux/ppc_4xx/rfs)

Jan 31 09:48:41 carme-gsi rpc.mountd[79344]: authenticated mount request from 192.168.11.8:675 for /home/Embedded/XilinxLinux/ppc_4xx/rfs/aida08 (/home/Embedded/XilinxLinux/ppc_4xx/rfs)

Jan 31 09:48:41 carme-gsi rpc.mountd[79344]: authenticated mount request from 192.168.11.5:907 for /home/Embedded/XilinxLinux/ppc_4xx/rfs/aida05 (/home/Embedded/XilinxLinux/ppc_4xx/rfs)

Jan 31 09:48:41 carme-gsi rpc.mountd[79344]: authenticated mount request from 192.168.11.6:883 for /home/Embedded/XilinxLinux/ppc_4xx/rfs/aida06 (/home/Embedded/XilinxLinux/ppc_4xx/rfs)

Jan 31 09:48:41 carme-gsi rpc.mountd[79344]: authenticated mount request from 192.168.11.4:985 for /home/Embedded/XilinxLinux/ppc_4xx/rfs/aida04 (/home/Embedded/XilinxLinux/ppc_4xx/rfs)

Jan 31 09:48:41 carme-gsi rpc.mountd[79344]: authenticated mount request from 192.168.11.7:682 for /home/Embedded/XilinxLinux/ppc_4xx/rfs/aida07 (/home/Embedded/XilinxLinux/ppc_4xx/rfs)

Jan 31 09:48:41 carme-gsi rpc.mountd[79344]: authenticated mount request from 192.168.11.2:707 for /home/Embedded/XilinxLinux/ppc_4xx/rfs/aida02 (/home/Embedded/XilinxLinux/ppc_4xx/rfs)

Jan 31 09:48:41 carme-gsi dhcpd: DHCPOFFER on 192.168.11.121 to d8:80:39:41:d0:05 via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPOFFER on 192.168.11.122 to d8:80:39:41:b4:0b via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPOFFER on 192.168.11.120 to d8:80:39:41:d7:cd via p4p1

Jan 31 09:48:41 carme-gsi dhcpd: DHCPOFFER on 192.168.11.118 to d8:80:39:41:d8:20 via p4p1

Jan 31 09:48:42 carme-gsi dhcpd: DHCPOFFER on 192.168.11.119 to d8:80:39:41:d7:c2 via p4p1

Jan 31 09:48:42 carme-gsi dhcpd: DHCPOFFER on 192.168.11.123 to d8:80:39:42:0d:0c via p4p1

Jan 31 09:48:42 carme-gsi dhcpd: DHCPOFFER on 192.168.11.123 to d8:80:39:42:0d:0c via p4p1

Jan 31 09:48:42 carme-gsi dhcpd: Can't create new lease file: Permission denied

Jan 31 09:48:42 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.123 (192.168.11.99) from d8:80:39:42:0d:0c via p4p1

Jan 31 09:48:42 carme-gsi dhcpd: DHCPACK on 192.168.11.123 to d8:80:39:42:0d:0c via p4p1

Jan 31 09:48:42 carme-gsi dhcpd: Wrote 0 deleted host decls to leases file.

Jan 31 09:48:42 carme-gsi dhcpd: Wrote 0 new dynamic host decls to leases file.

Jan 31 09:48:42 carme-gsi dhcpd: Wrote 8 leases to leases file.

Jan 31 09:48:42 carme-gsi dhcpd: DHCPREQUEST for 192.168.11.123 (192.168.11.99) from d8:80:39:42:0d:0c via p4p1

Jan 31 09:48:42 carme-gsi dhcpd: DHCPACK on 192.168.11.123 to d8:80:39:42:0d:0c via p4p1

Jan 31 09:48:42 carme-gsi dhcpd: DHCPOFFER on 192.168.11.124 to d8:80:39:41:b4:16 via p4p1

Jan 31 09:48:42 carme-gsi dhcpd: DHCPOFFER on 192.168.11.125 to d8:80:39:41:d8:2b via p4p1

|

| Attachment 3: 220131_0952_tcpdump.txt

|

[root@carme-gsi MIDAS]# tcpdump host aida04 -vvv -s 192 -i p4p1

tcpdump: listening on p4p1, link-type EN10MB (Ethernet), capture size 192 bytes

09:48:41.015348 IP (tos 0x10, ttl 128, id 0, offset 0, flags [none], proto UDP (17), length 382)

carme-gsi.bootps > aida04.bootpc: BOOTP/DHCP, Reply, length 354, xid 0x37935d60, Flags [none] (0x0000)

Your-IP aida04

Server-IP carme-gsi

Client-Ethernet-Address d8:80:39:41:d7:c2 (oui Unknown)

sname "192.168.11.99"[|bootp]

09:48:41.020188 IP (tos 0x10, ttl 128, id 0, offset 0, flags [none], proto UDP (17), length 382)

carme-gsi.bootps > aida04.bootpc: BOOTP/DHCP, Reply, length 354, xid 0x37935d60, Flags [none] (0x0000)

Your-IP aida04

Server-IP carme-gsi

Client-Ethernet-Address d8:80:39:41:d7:c2 (oui Unknown)

sname "192.168.11.99"[|bootp]

09:48:41.447747 ARP, Ethernet (len 6), IPv4 (len 4), Request who-has carme-gsi tell aida04, length 46

09:48:41.447758 ARP, Ethernet (len 6), IPv4 (len 4), Reply carme-gsi is-at 00:e0:4c:a1:16:af (oui Unknown), length 28

09:48:41.450602 IP (tos 0x0, ttl 64, id 0, offset 0, flags [DF], proto UDP (17), length 112)

aida04.38162 > carme-gsi.sunrpc: [udp sum ok] UDP, length 84

09:48:41.450809 IP (tos 0x0, ttl 64, id 1841, offset 0, flags [DF], proto UDP (17), length 56)

carme-gsi.sunrpc > aida04.38162: [udp sum ok] UDP, length 28

09:48:41.505482 IP (tos 0x0, ttl 64, id 0, offset 0, flags [DF], proto UDP (17), length 112)

aida04.59139 > carme-gsi.sunrpc: [udp sum ok] UDP, length 84

09:48:41.505648 IP (tos 0x0, ttl 64, id 1895, offset 0, flags [DF], proto UDP (17), length 56)

carme-gsi.sunrpc > aida04.59139: [udp sum ok] UDP, length 28

09:48:41.508775 IP (tos 0x0, ttl 64, id 0, offset 0, flags [DF], proto UDP (17), length 68)

aida04.985 > carme-gsi.mountd: [udp sum ok] UDP, length 40

09:48:41.508921 IP (tos 0x0, ttl 64, id 1896, offset 0, flags [DF], proto UDP (17), length 52)

carme-gsi.mountd > aida04.985: [udp sum ok] UDP, length 24

09:48:41.511947 IP (tos 0x0, ttl 64, id 0, offset 0, flags [DF], proto UDP (17), length 148)

aida04.985 > carme-gsi.mountd: [udp sum ok] UDP, length 120

09:48:41.512632 IP (tos 0x0, ttl 64, id 1898, offset 0, flags [DF], proto UDP (17), length 88)

carme-gsi.mountd > aida04.985: [udp sum ok] UDP, length 60

09:48:41.516436 IP (tos 0x0, ttl 64, id 0, offset 0, flags [DF], proto UDP (17), length 68)

aida04.1004 > carme-gsi.nfs: NFS request xid 1193702076 40 null

09:48:41.516487 IP (tos 0x0, ttl 64, id 1902, offset 0, flags [DF], proto UDP (17), length 60)

carme-gsi.nfs > aida04.1004: NFS reply xid 1193702076 reply ok 32 null

09:48:46.461884 ARP, Ethernet (len 6), IPv4 (len 4), Request who-has aida04 tell carme-gsi, length 28

09:48:46.464693 ARP, Ethernet (len 6), IPv4 (len 4), Reply aida04 is-at d8:80:39:41:d7:c2 (oui Unknown), length 46

|

| Attachment 4: 220131_0953_dhcpdleases.txt

|

# The format of this file is documented in the dhcpd.leases(5) manual page.

# This lease file was written by isc-dhcp-4.2.5

lease 192.168.11.118 {

starts 1 2022/01/31 08:48:40;

ends 1 2022/01/31 08:50:40;

cltt 1 2022/01/31 08:48:40;

binding state free;

hardware ethernet d8:80:39:41:d8:20;

}

lease 192.168.11.120 {

starts 1 2022/01/31 08:48:40;

ends 1 2022/01/31 08:50:40;

cltt 1 2022/01/31 08:48:40;

binding state free;

hardware ethernet d8:80:39:41:d7:cd;

}

lease 192.168.11.122 {

starts 1 2022/01/31 08:48:40;

ends 1 2022/01/31 08:50:40;

cltt 1 2022/01/31 08:48:40;

binding state free;

hardware ethernet d8:80:39:41:b4:0b;

}

lease 192.168.11.121 {

starts 1 2022/01/31 08:48:40;

ends 1 2022/01/31 08:50:40;

cltt 1 2022/01/31 08:48:40;

binding state free;

hardware ethernet d8:80:39:41:d0:05;

}

lease 192.168.11.125 {

starts 1 2022/01/31 08:48:41;

ends 1 2022/01/31 08:50:41;

cltt 1 2022/01/31 08:48:41;

binding state free;

hardware ethernet d8:80:39:41:d8:2b;

}

lease 192.168.11.124 {

starts 1 2022/01/31 08:48:41;

ends 1 2022/01/31 08:50:41;

cltt 1 2022/01/31 08:48:41;

binding state free;

hardware ethernet d8:80:39:41:b4:16;

}

lease 192.168.11.119 {

starts 1 2022/01/31 08:48:41;

ends 1 2022/01/31 08:50:41;

cltt 1 2022/01/31 08:48:41;

binding state free;

hardware ethernet d8:80:39:41:d7:c2;

}

lease 192.168.11.123 {

starts 1 2022/01/31 08:48:42;

ends 1 2022/01/31 20:48:42;

cltt 1 2022/01/31 08:48:42;

binding state active;

next binding state free;

rewind binding state free;

hardware ethernet d8:80:39:42:0d:0c;

}

server-duid "\000\001\000\001)\211c\037\000\340L\241\026\257";

|

| Attachment 5: dhcpd.conf

|

#

# DHCP Server Configuration file.

# see /usr/share/doc/dhcp*/dhcpd.conf.example

# see dhcpd.conf(5) man page

#

# 2 days

#default-lease-time 172800;

# 4 days

default-lease-time 345600;

# 8 days

max-lease-time 691200;

option domain-search code 119 = string;

option domain-name "dl.ac.uk";

option domain-name-servers 193.62.115.16, 148.79.80.78;

option netbios-name-servers 148.79.160.89;

option netbios-node-type 8;

option nis-domain "nuclear.physics";

option nis-servers 193.62.115.77;

subnet 192.168.11.0 netmask 255.255.255.0 {

option subnet-mask 255.255.255.0;

option broadcast-address 192.168.11.255;

pool {

range 192.168.11.118 192.168.11.199;

}

}

group {

use-host-decl-names true;

default-lease-time 3600;

max-lease-time 14400;

server-name "192.168.11.99";

next-server 192.168.11.99;

host nnrpi1 {

hardware ethernet dc:a6:32:1d:21:db;

fixed-address 192.168.11.251;

}

host nnrpi2 {

hardware ethernet b8:27:eb:40:53:e8;

fixed-address 192.168.11.117;

}

host aida01 {

hardware ethernet d8:80:39:42:02:0c;

fixed-address 192.168.11.1;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida01";

}

host aida02 {

hardware ethernet d8:80:39:41:d8:2b;

fixed-address 192.168.11.2;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida02";

}

host aida03 {

hardware ethernet d8:80:39:41:d0:05;

fixed-address 192.168.11.3;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida03";

}

host aida04 {

hardware ethernet d8:80:39:41:d7:c2;

fixed-address 192.168.11.4;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida04";

}

host aida05 {

hardware ethernet d8:80:39:41:b4:0b;

fixed-address 192.168.11.5;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida05";

}

host aida06 {

hardware ethernet d8:80:39:41:d8:20;

fixed-address 192.168.11.6;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida06";

}

host aida07 {

hardware ethernet d8:80:39:41:b4:16;

fixed-address 192.168.11.7;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida07";

}

host aida08 {

hardware ethernet d8:80:39:41:d7:cd;

fixed-address 192.168.11.8;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida08";

}

host aida09 {

hardware ethernet d8:80:39:41:f6:ee;

fixed-address 192.168.11.9;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida09";

}

host aida10 {

hardware ethernet d8:80:39:41:ba:89;

fixed-address 192.168.11.10;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida10";

}

host aida11 {

hardware ethernet d8:80:39:41:f6:5a;

fixed-address 192.168.11.11;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida11";

}

host aida12 {

hardware ethernet d8:80:39:41:cf:ac;

fixed-address 192.168.11.12;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida12";

}

host aida13 {

hardware ethernet d8:80:39:42:d:15;

fixed-address 192.168.11.13;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida13";

}

host aida14 {

hardware ethernet d8:80:39:42:d:b;

fixed-address 192.168.11.14;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida14";

}

host aida15 {

hardware ethernet d8:80:39:41:ee:10;

fixed-address 192.168.11.15;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida15";

}

host aida16 {

hardware ethernet d8:80:39:41:f6:ed;

fixed-address 192.168.11.16;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida16";

}

}

subnet 192.168.12.0 netmask 255.255.255.0 {

option subnet-mask 255.255.255.0;

option broadcast-address 192.168.12.255;

pool {

range 192.168.12.100 192.168.12.199;

}

}

group {

use-host-decl-names true;

default-lease-time 3600;

max-lease-time 14400;

server-name "192.168.12.99";

next-server 192.168.12.99;

host aida21 {

hardware ethernet d8:80:39:41:d8:2a;

fixed-address 192.168.12.1;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida21";

}

host aida22 {

hardware ethernet 00:04:a3:2a:d0:26;

fixed-address 192.168.12.2;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida22";

}

host aida23 {

hardware ethernet 00:04:a3:2b:09:ce;

fixed-address 192.168.12.3;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida23";

}

host aida24 {

hardware ethernet 00:04:a3:2b:09:e8;

fixed-address 192.168.12.4;

option root-path "/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida24";

}

}

|

| Attachment 6: hosts.txt

|

127.0.0.1 localhost localhost.localdomain localhost4 localhost4.localdomain4

::1 localhost localhost.localdomain localhost6 localhost6.localdomain6

192.168.11.251 nnrpi1

192.168.11.1 aida01

192.168.11.2 aida02

192.168.11.3 aida03

192.168.11.4 aida04

192.168.11.5 aida05

192.168.11.6 aida06

192.168.11.7 aida07

192.168.11.8 aida08

|

| Attachment 7: exports.txt

|

/home/Embedded/XilinxLinux/ppc_4xx/rfs 192.168.0.0/255.255.0.0(rw,sync,nohide,no_root_squash)

/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 192.168.0.0/255.255.0.0(rw,sync,nohide)

/MIDAS_130718 192.168.0.0/255.255.0.0(rw,sync,nohide)

|

| Attachment 8: ifconfig.txt

|

enp0s31f6: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500

ether a4:bb:6d:d1:81:9a txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

device interrupt 16 memory 0x90300000-90320000

enp2s0: flags=4163<UP,BROADCAST,RUNNING,MULTICAST> mtu 1500

inet 192.168.207.142 netmask 255.255.255.0 broadcast 192.168.207.255

inet6 fd43:525a:5249:4e47:d923:1a54:9ea8:e9b1 prefixlen 64 scopeid 0x0<global>

inet6 fe80::4194:b06d:5173:1c42 prefixlen 64 scopeid 0x20<link>

ether a4:bb:6d:d1:7f:ca txqueuelen 1000 (Ethernet)

RX packets 15104702 bytes 22030764707 (20.5 GiB)

RX errors 0 dropped 29 overruns 0 frame 0

TX packets 2199234 bytes 424845717 (405.1 MiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

device memory 0x90100000-9017ffff

lo: flags=73<UP,LOOPBACK,RUNNING> mtu 65536

inet 127.0.0.1 netmask 255.0.0.0

inet6 ::1 prefixlen 128 scopeid 0x10<host>

loop txqueuelen 1000 (Local Loopback)

RX packets 1157441 bytes 870407343 (830.0 MiB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 1157441 bytes 870407343 (830.0 MiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

p4p1: flags=4163<UP,BROADCAST,RUNNING,MULTICAST> mtu 1500

inet 192.168.11.99 netmask 255.255.255.0 broadcast 192.168.11.255

inet6 fe80::74a5:671:a523:2bc5 prefixlen 64 scopeid 0x20<link>

ether 00:e0:4c:a1:16:af txqueuelen 1000 (Ethernet)

RX packets 2283907 bytes 3266470097 (3.0 GiB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 256271 bytes 19134505 (18.2 MiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

p4p2: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500

ether 00:e0:4c:a1:16:b0 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

p4p3: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500

ether 00:e0:4c:a1:16:b1 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

p4p4: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500

ether 00:e0:4c:a1:16:b2 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

virbr0: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500

inet 192.168.122.1 netmask 255.255.255.0 broadcast 192.168.122.255

ether 52:54:00:9c:18:b1 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

virbr0-nic: flags=4098<BROADCAST,MULTICAST> mtu 1500

ether 52:54:00:9c:18:b1 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

|