| |

ID |

Date |

Author |

Subject |

|

|

476

|

Sat Nov 26 15:32:38 2016 |

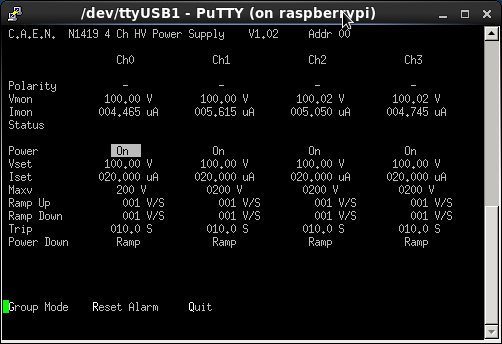

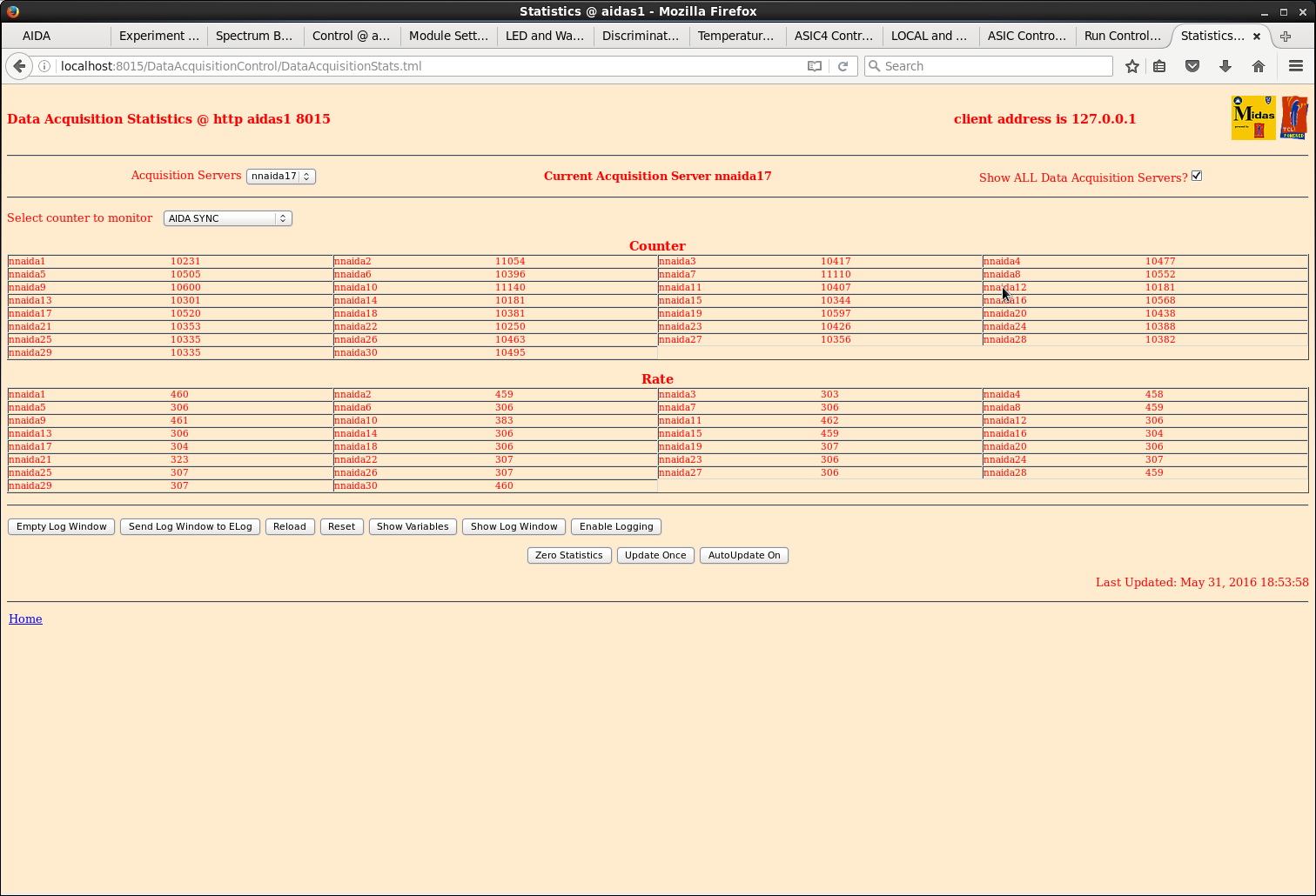

TD, AE, CG, DK | Sunday 27 November | 00.33 DSSSD bias & leakage currents OK - see attachments 1 & 2

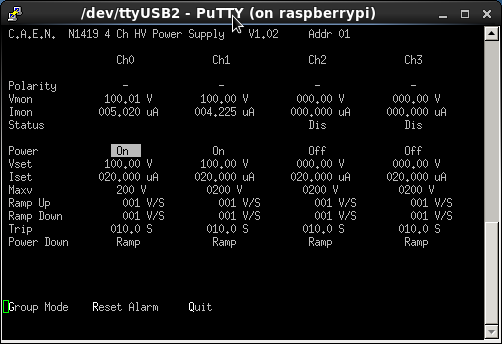

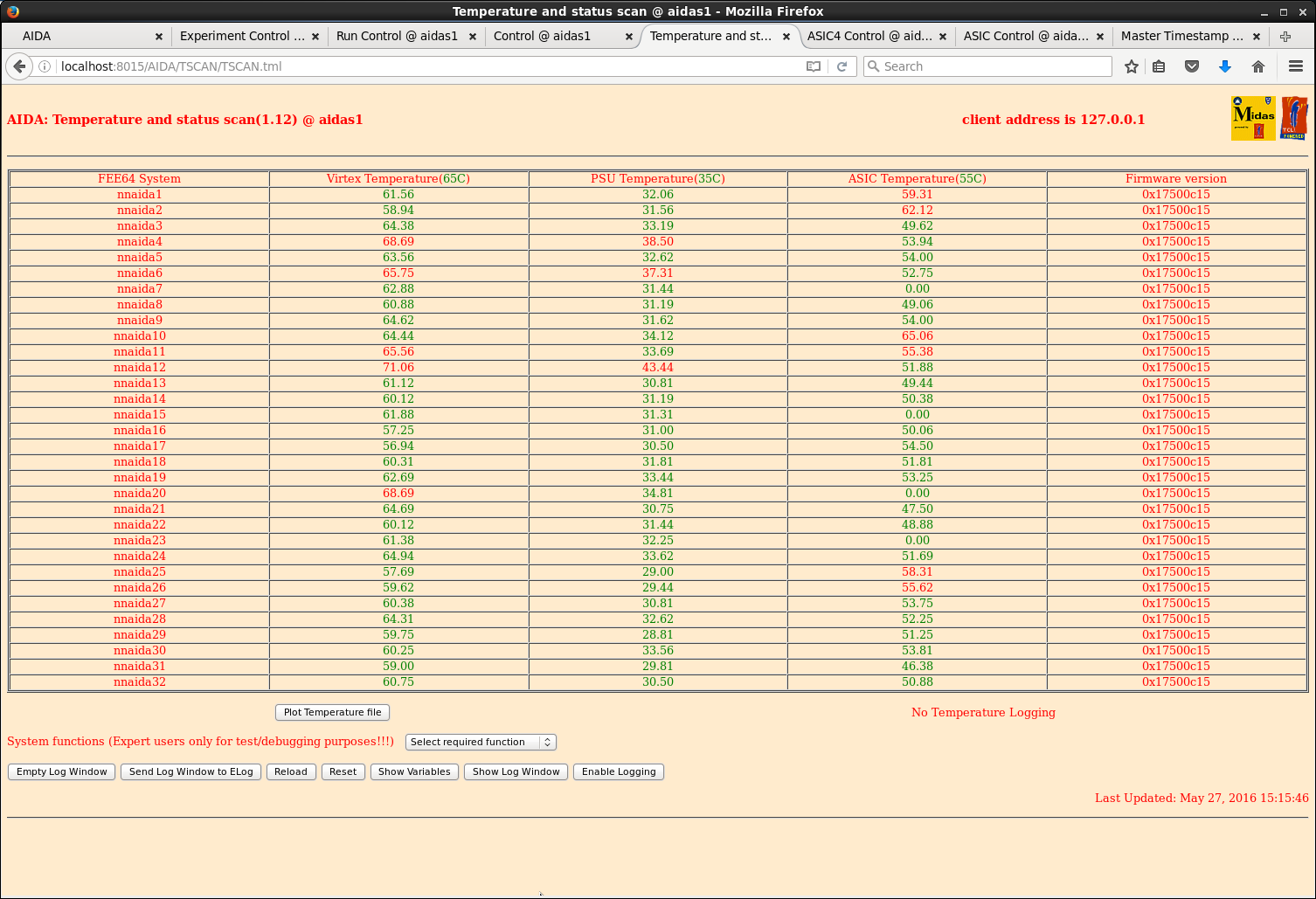

FEE64 temperatures OK - see attachment 3

00.34 DAQ continues (RIBF03R1/R10)

ASIC settings 2016Nov17-10.50.10

BNC PB-4 pulser

Amplitude 90,000

x5 attenuator IN

frequency 25Hz range

t_r 50ns, tau_d 50us

polarity -, tail pulse, delay MIN, INT ref

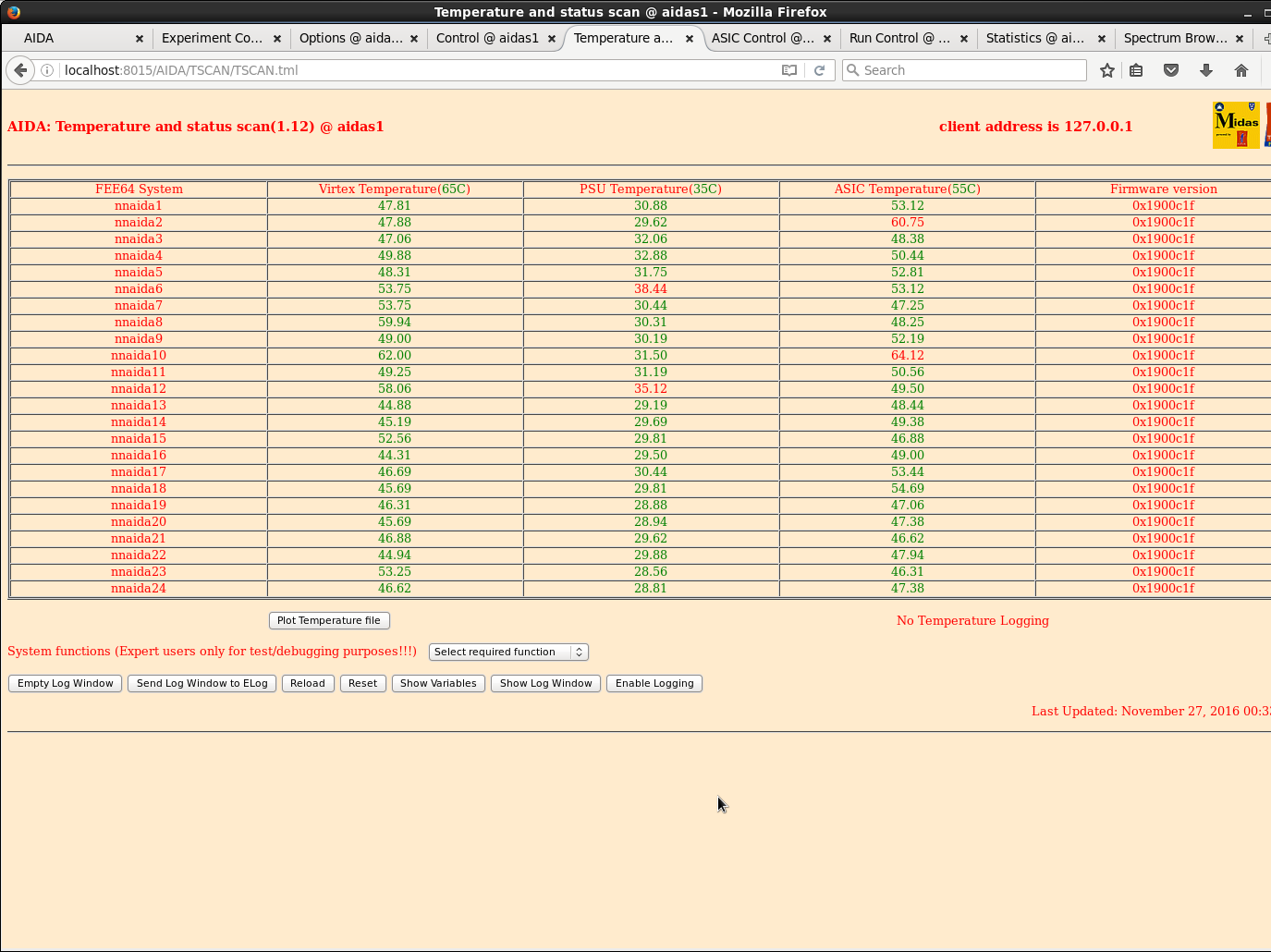

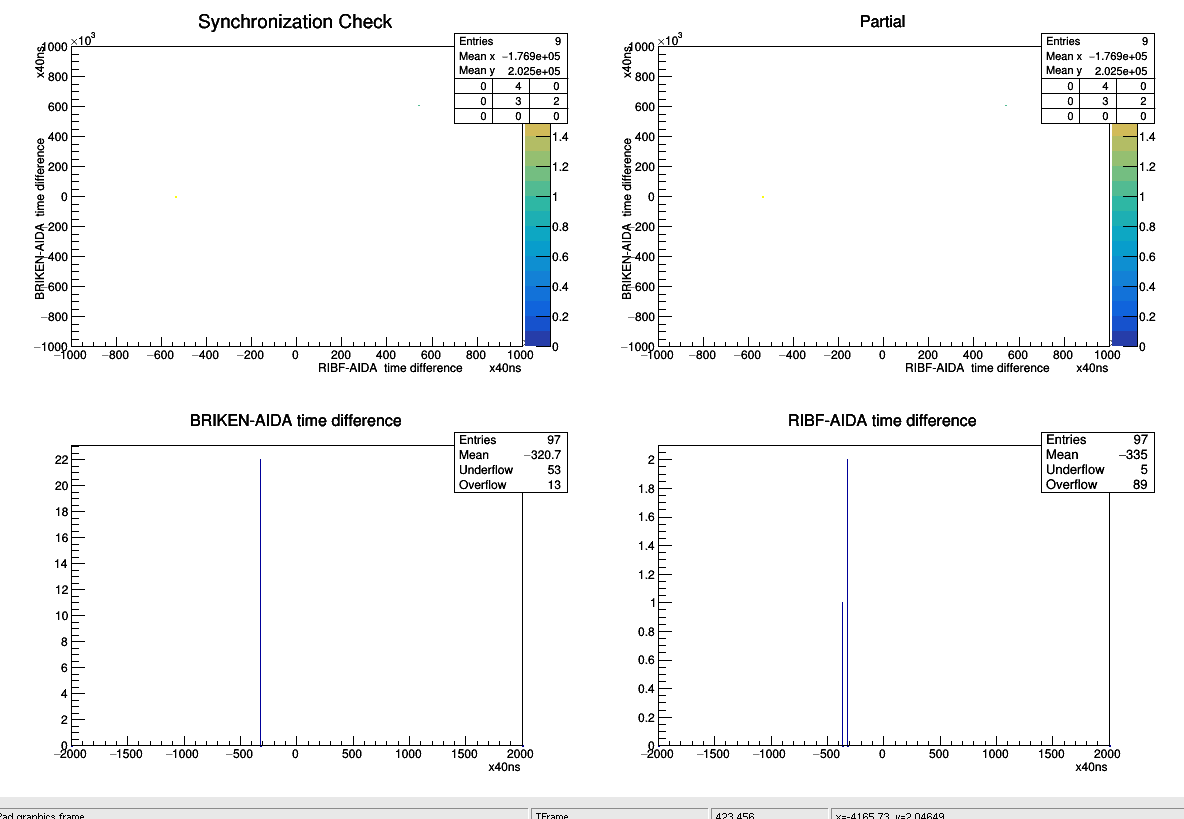

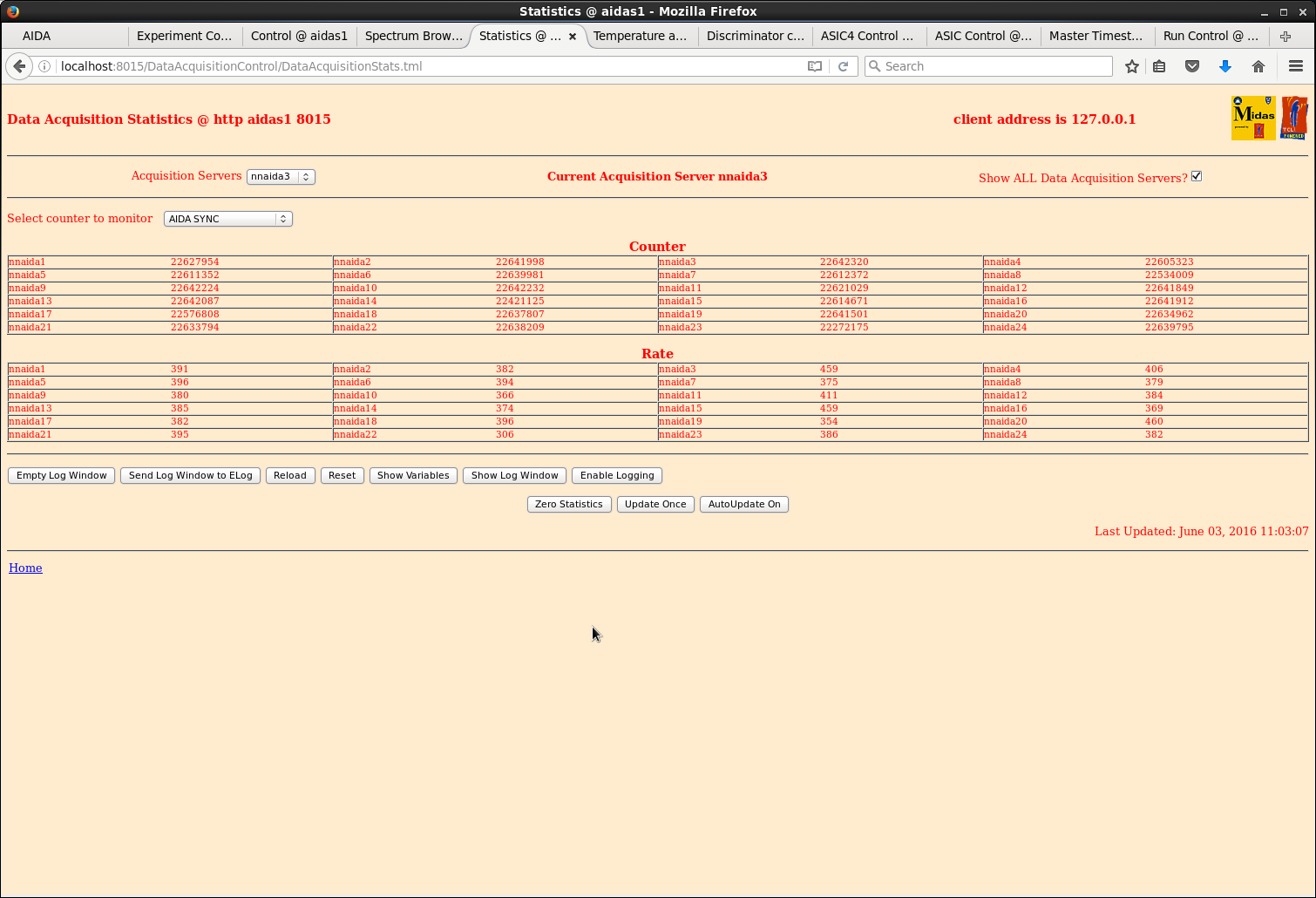

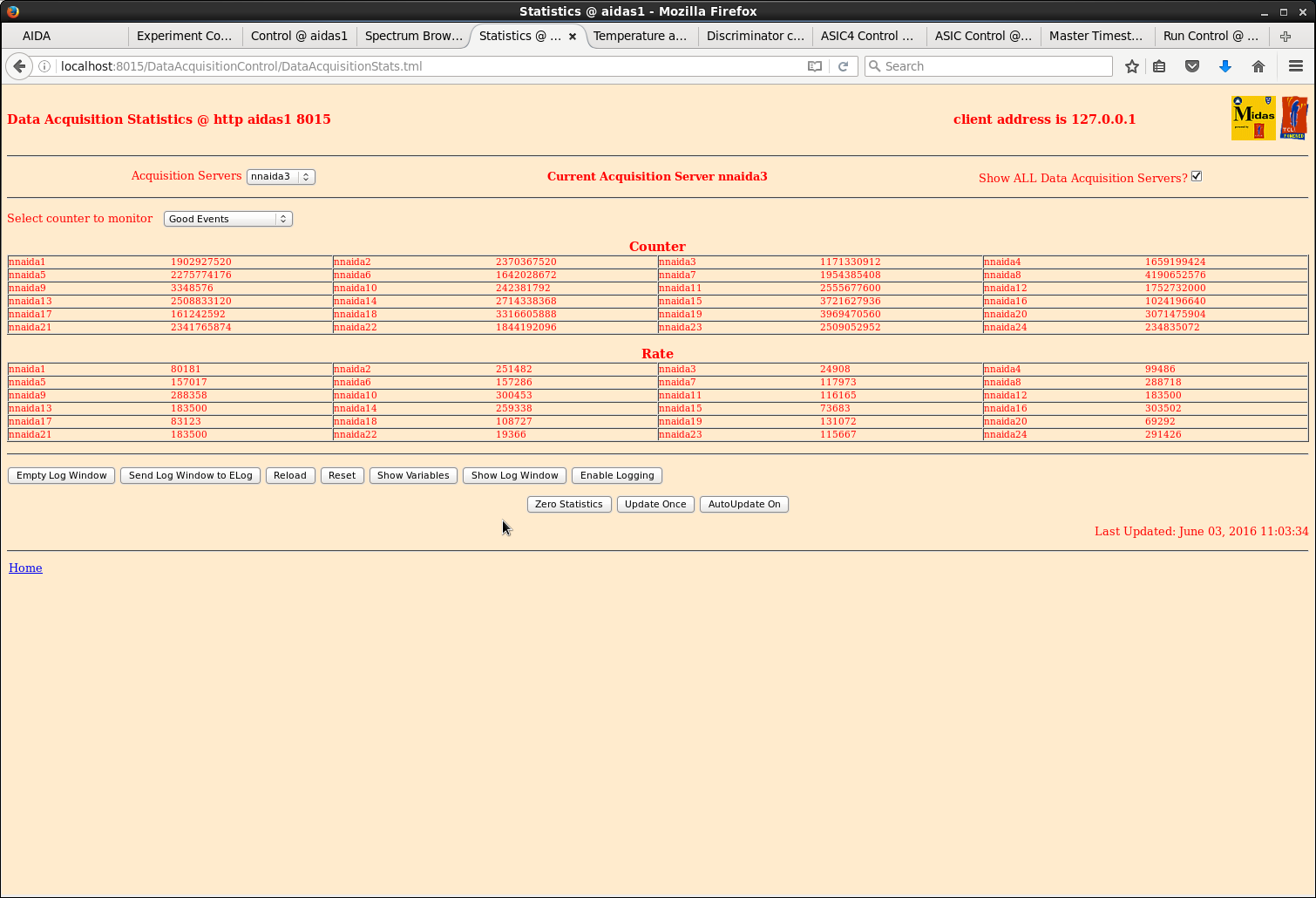

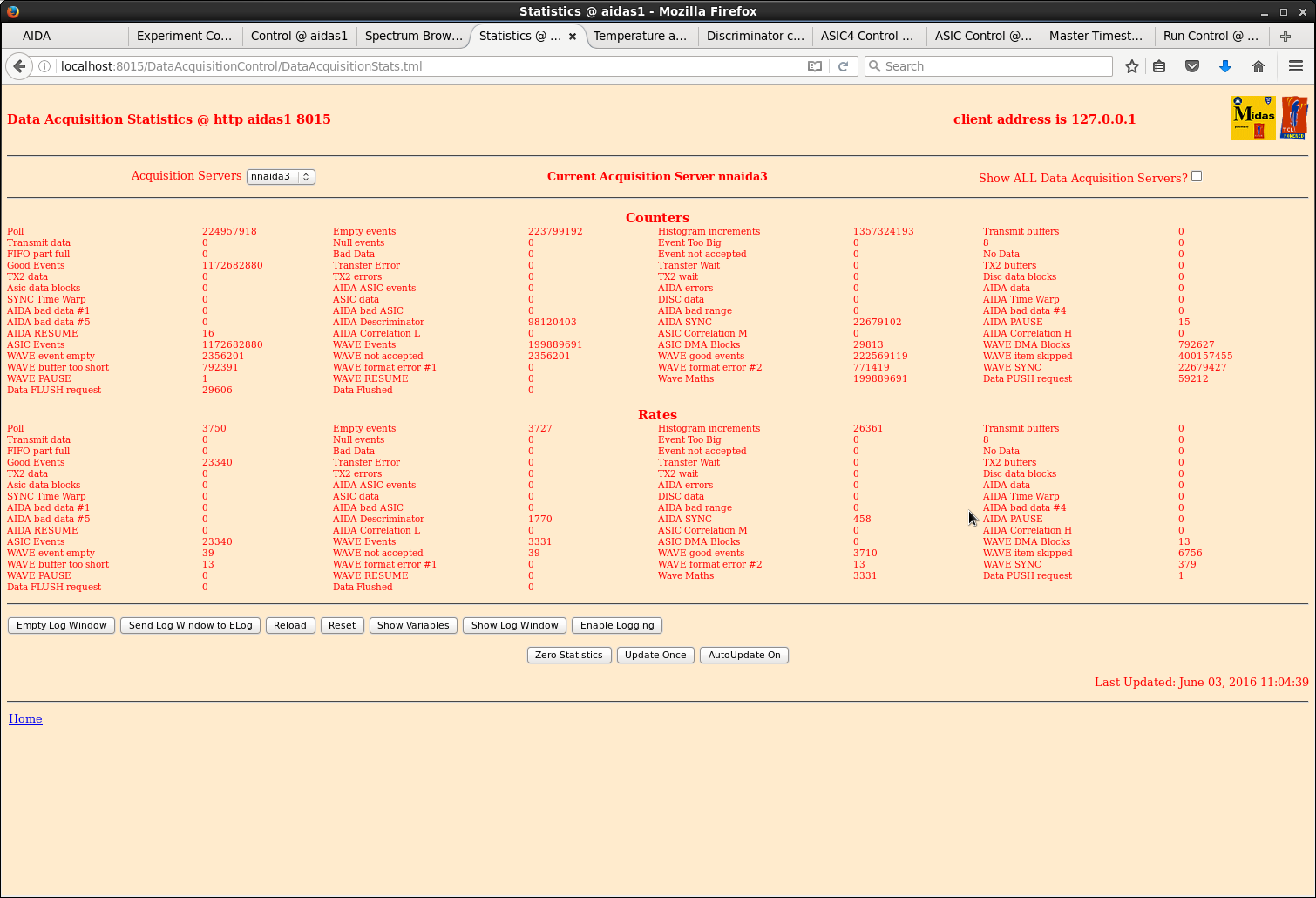

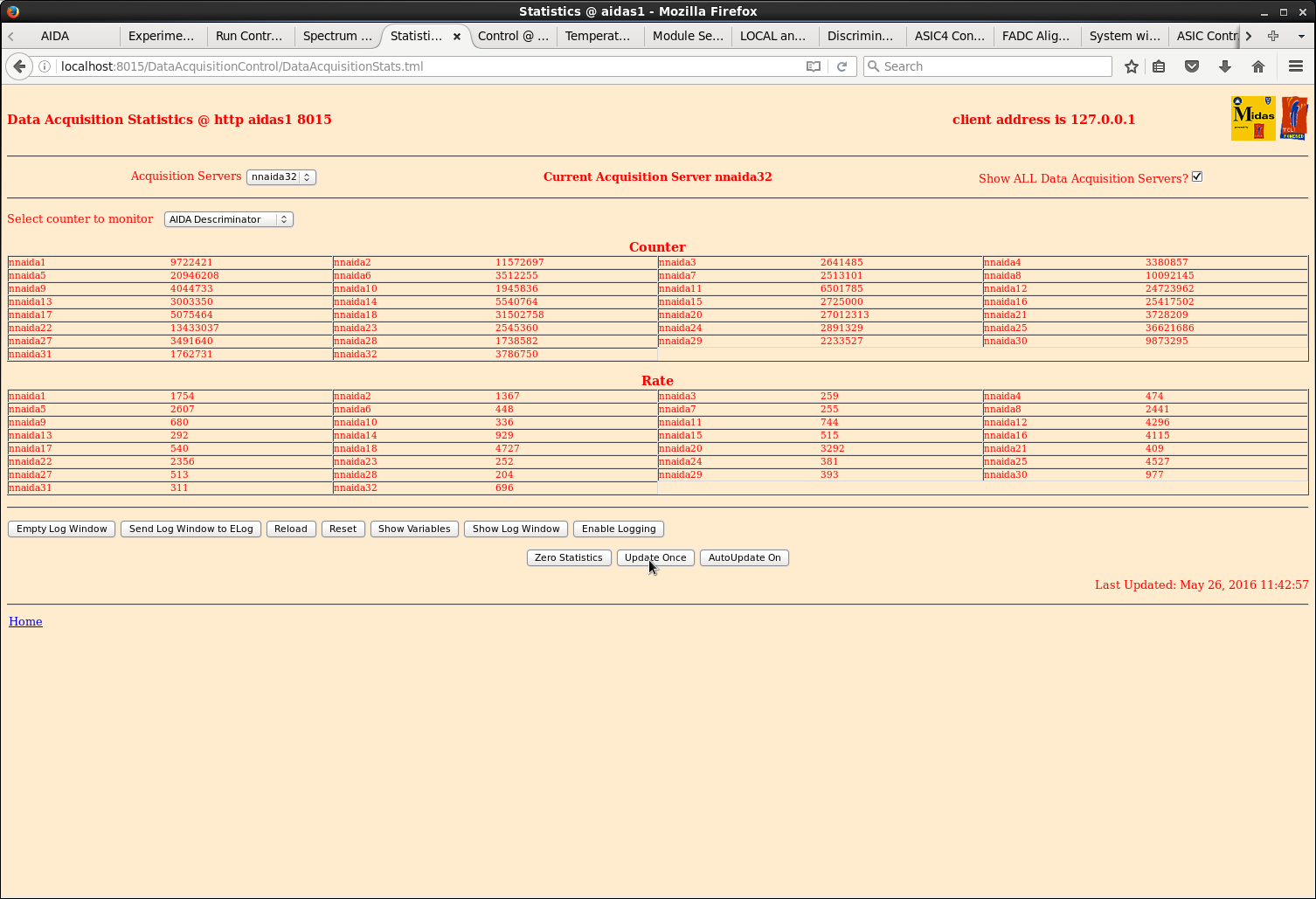

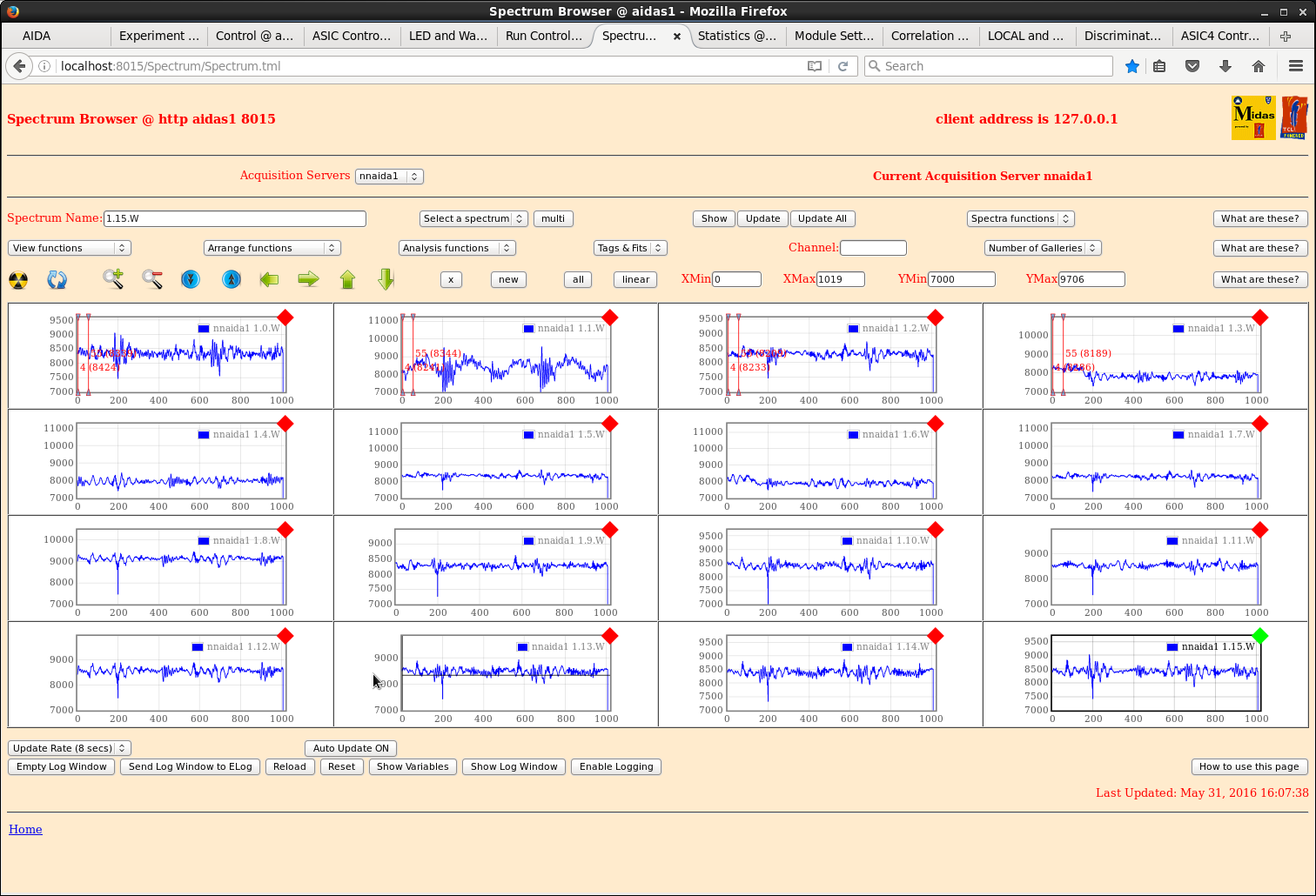

good events - see attachment 4

N.B. 5x FEE64s > 100k data items/s - intrinsic/extrinsic noise has changed cf. 0x FEE64s previously

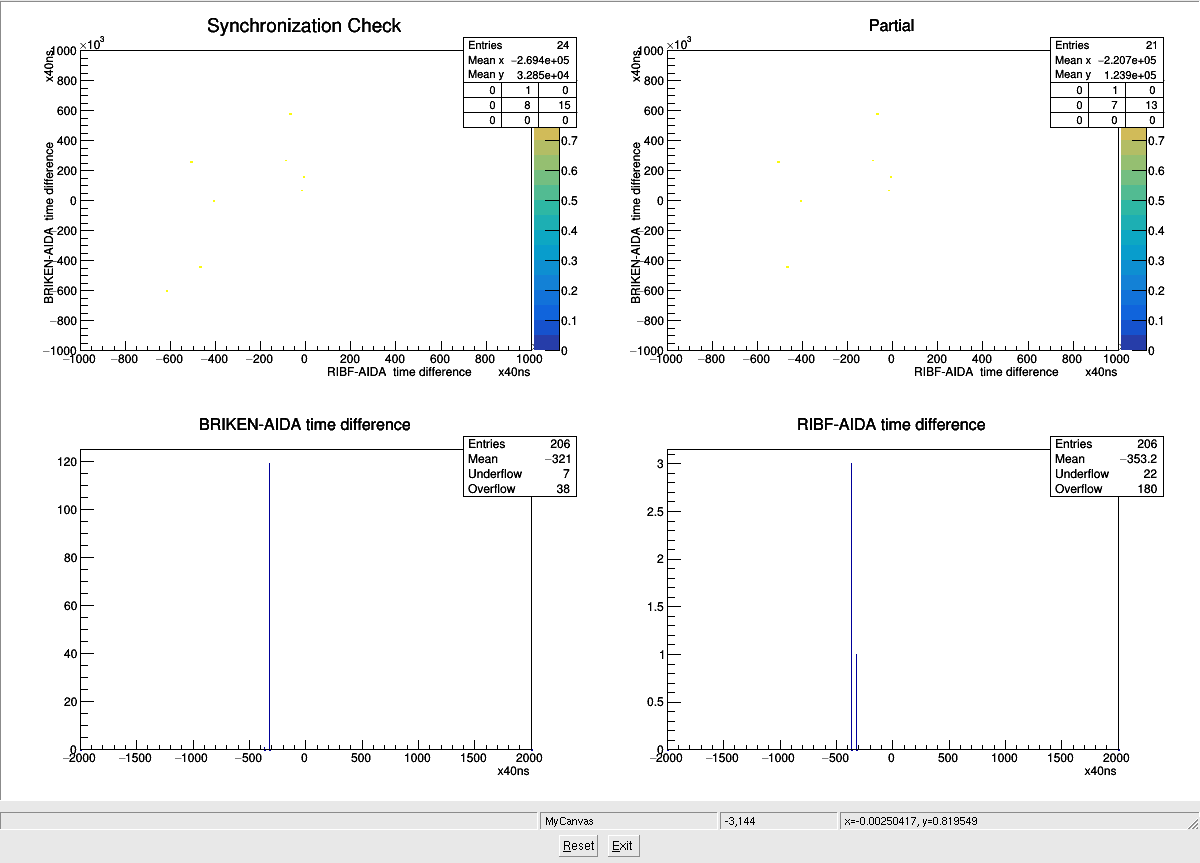

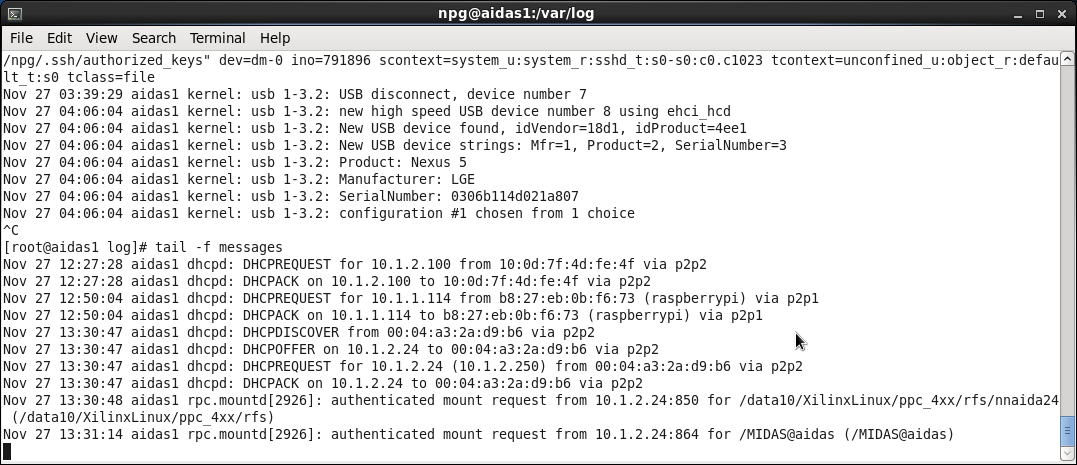

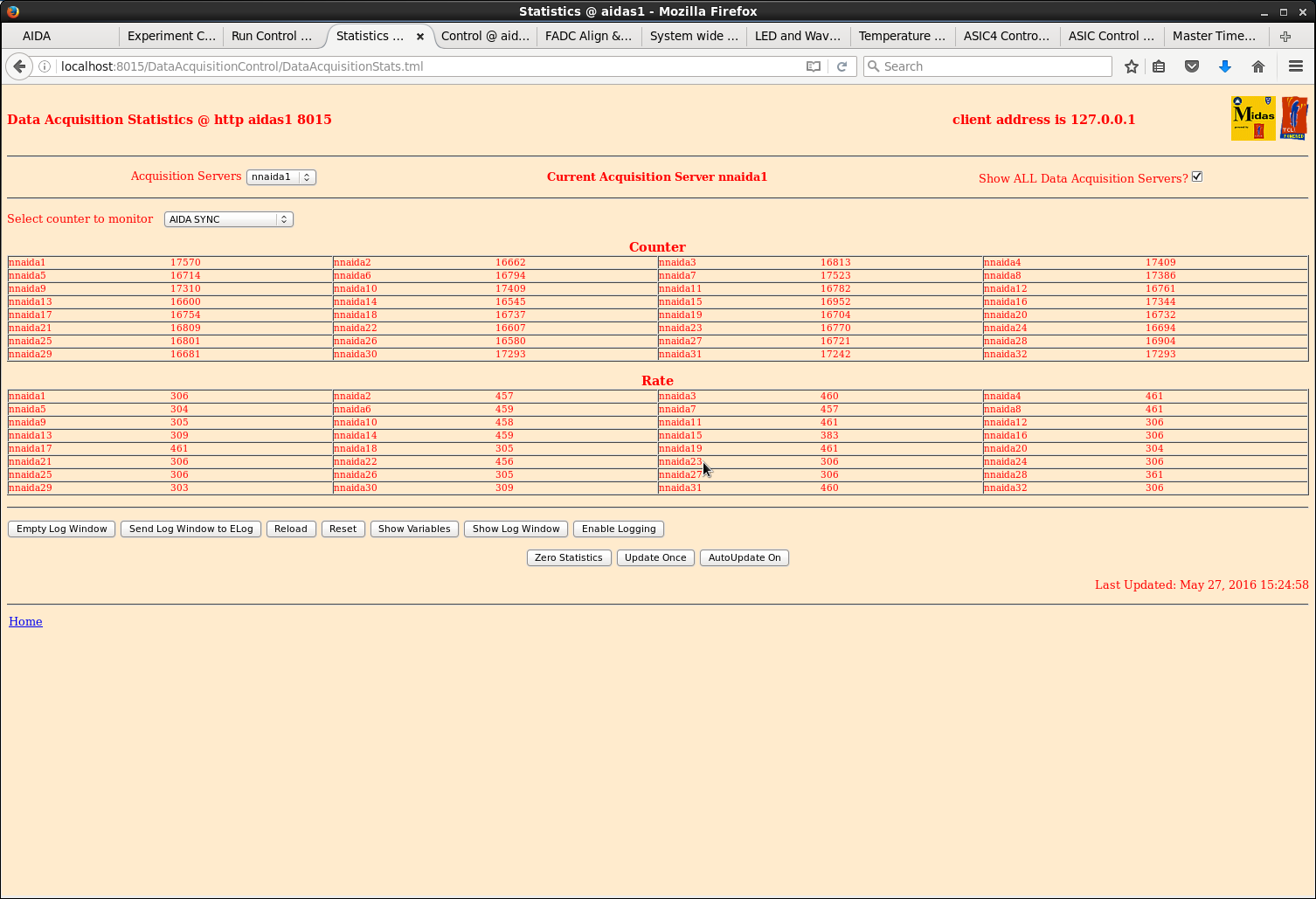

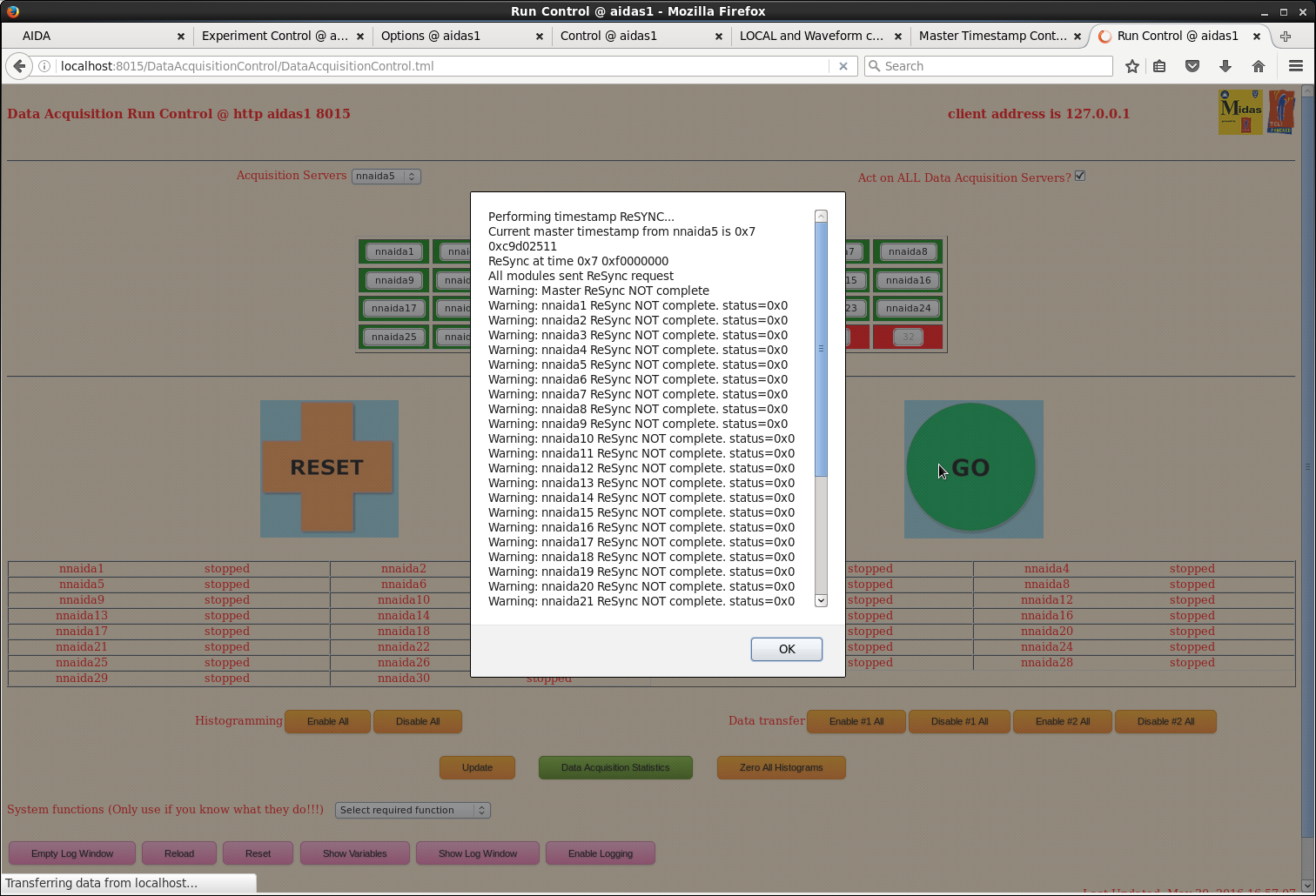

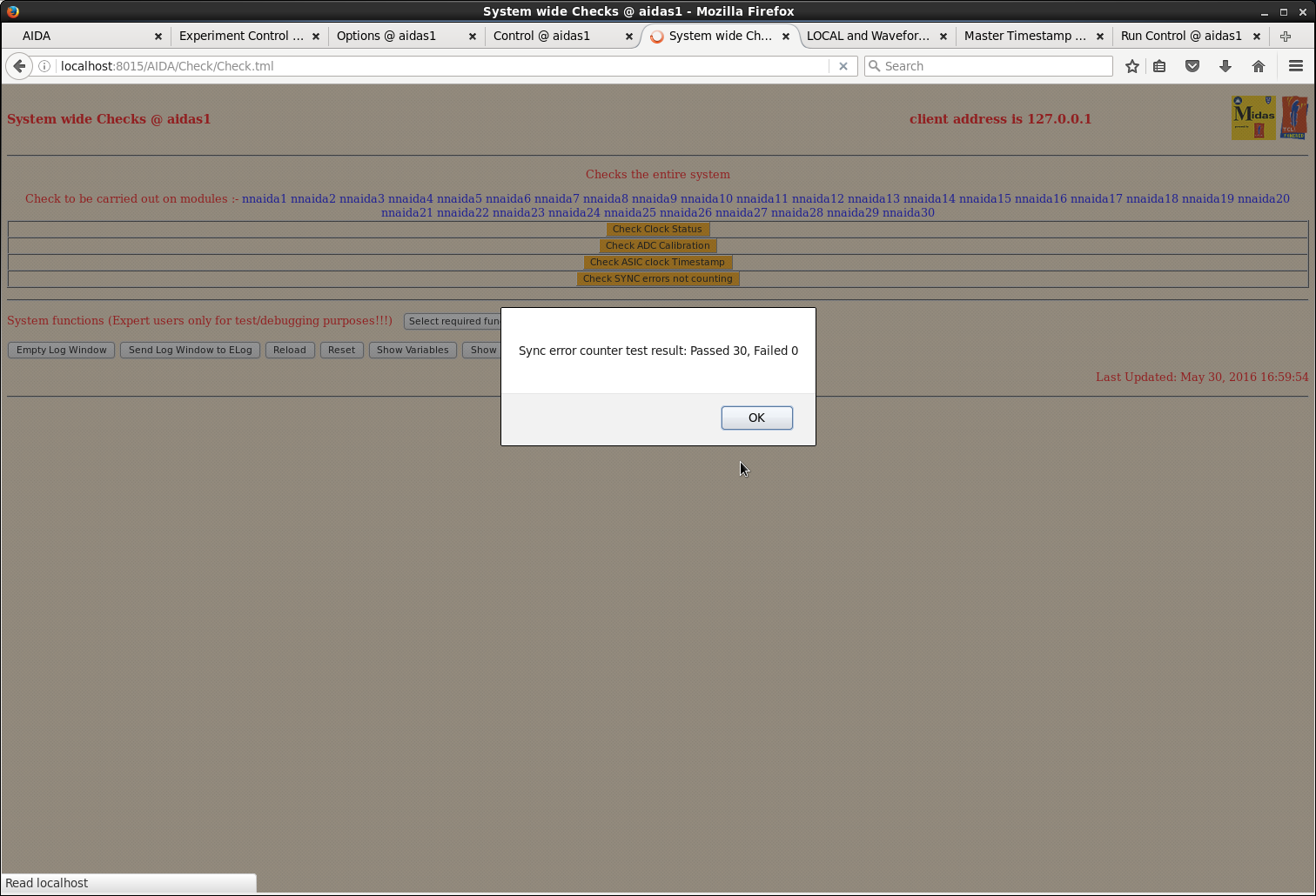

00.50 SyncCheck - see attachment 5

Two peaks for RIBF-AIDA, one peak for BRIKEN-AIDA => RIBF issue?

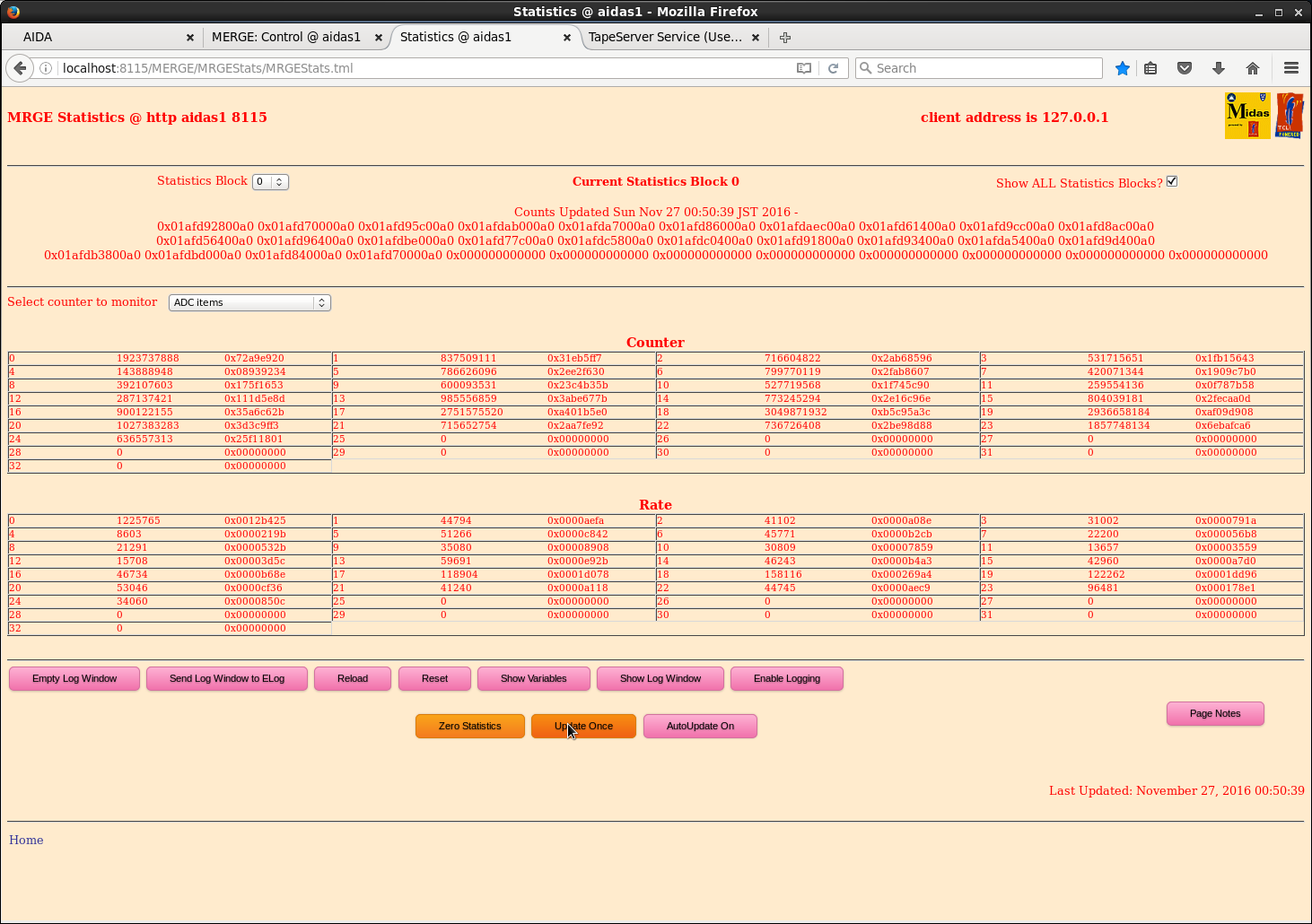

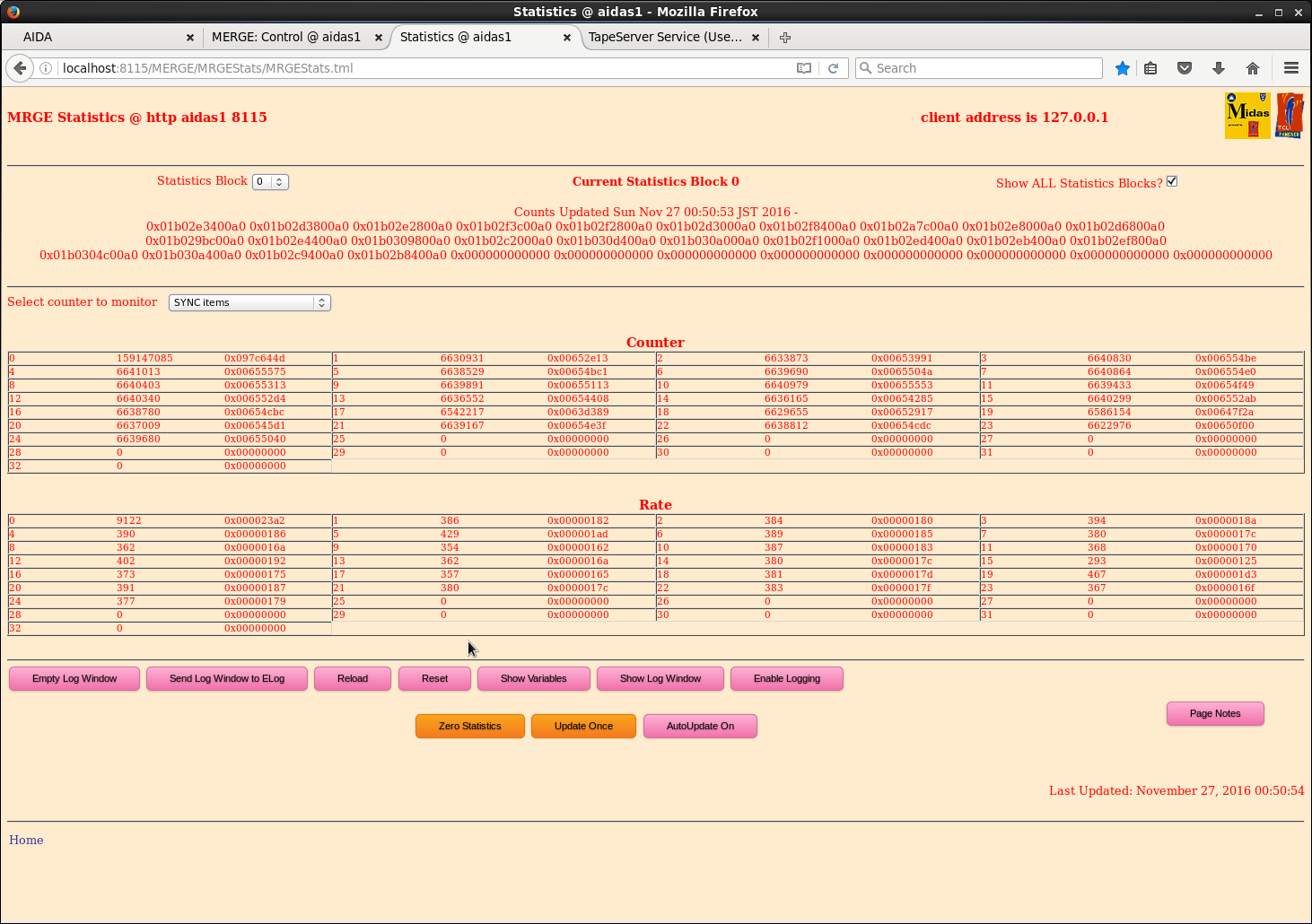

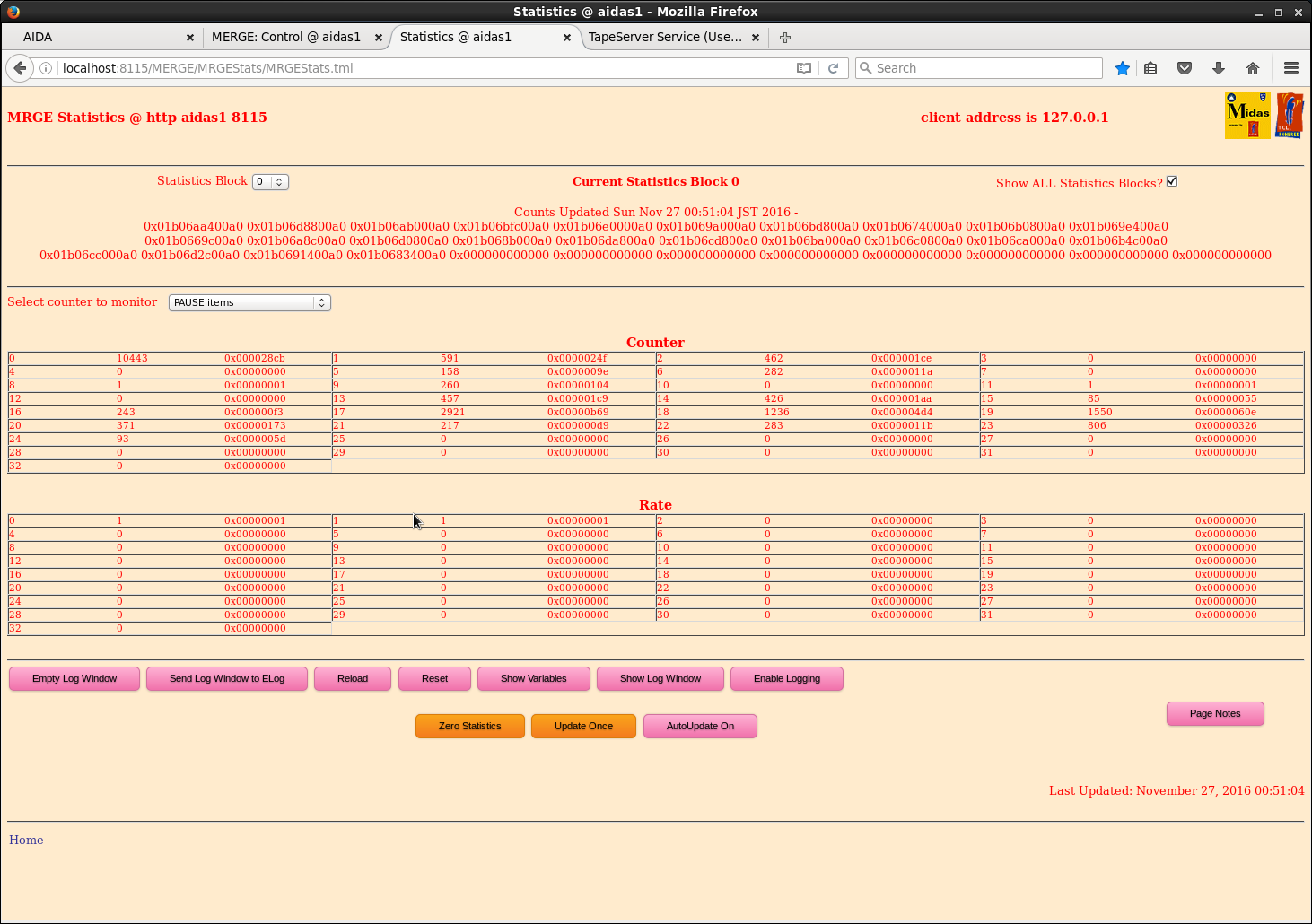

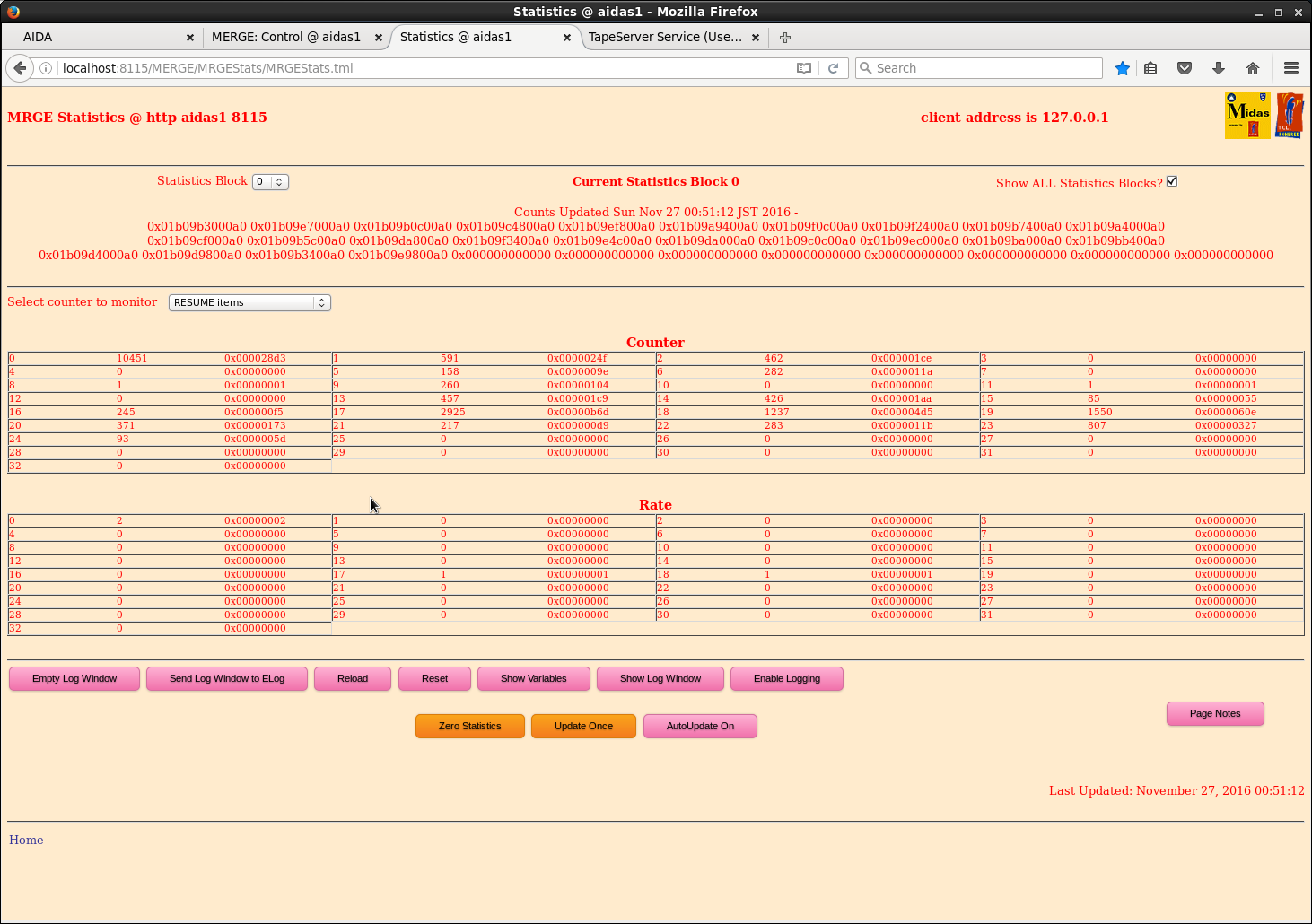

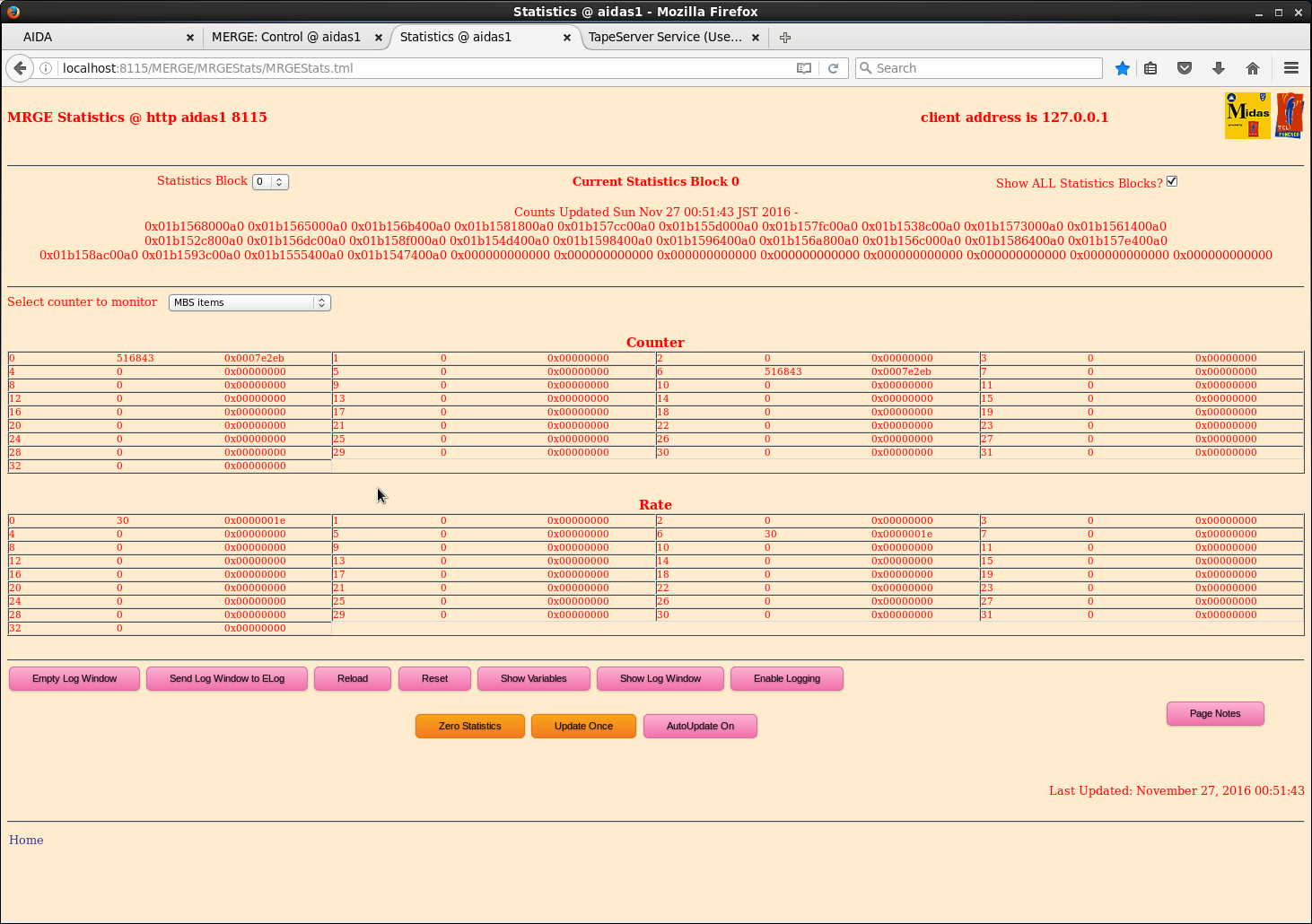

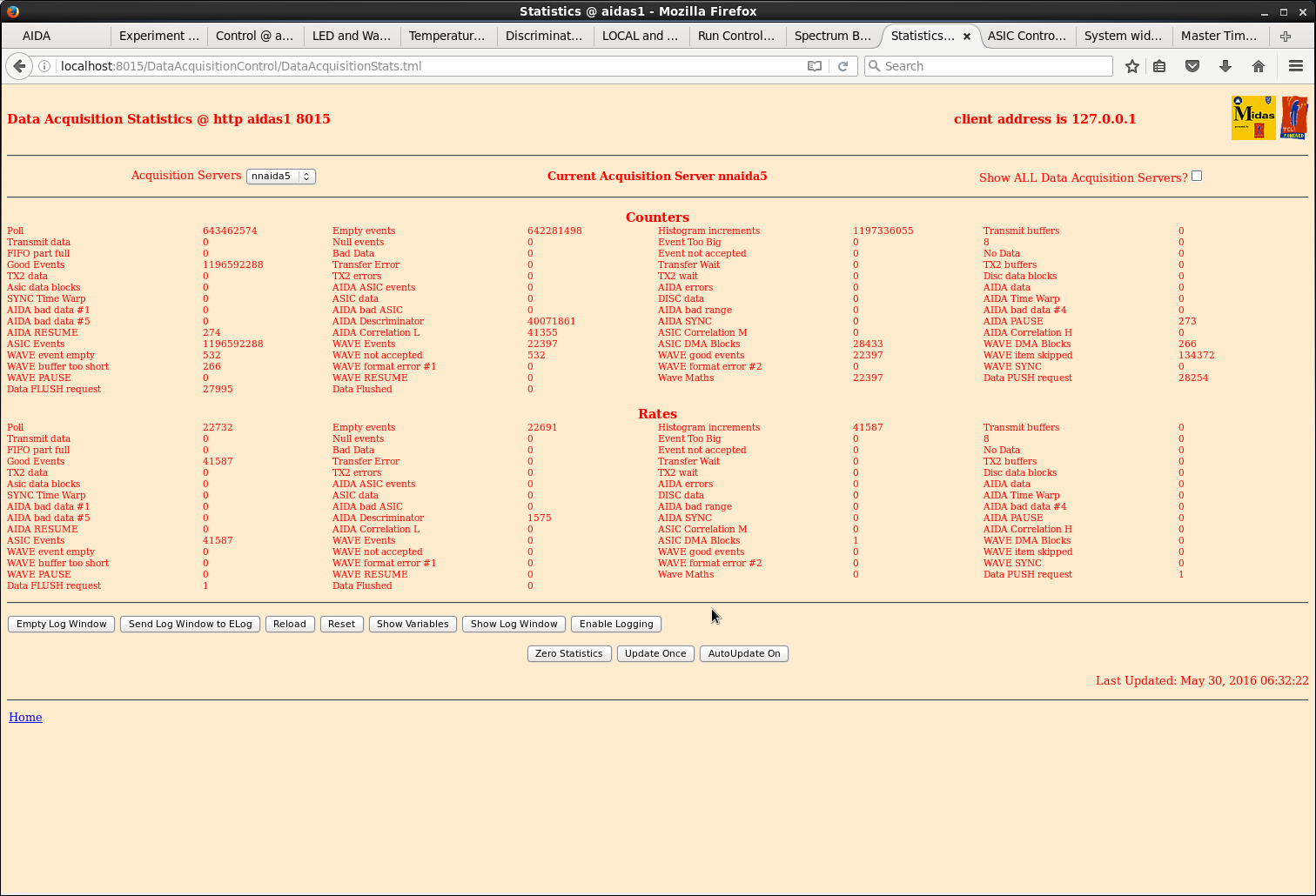

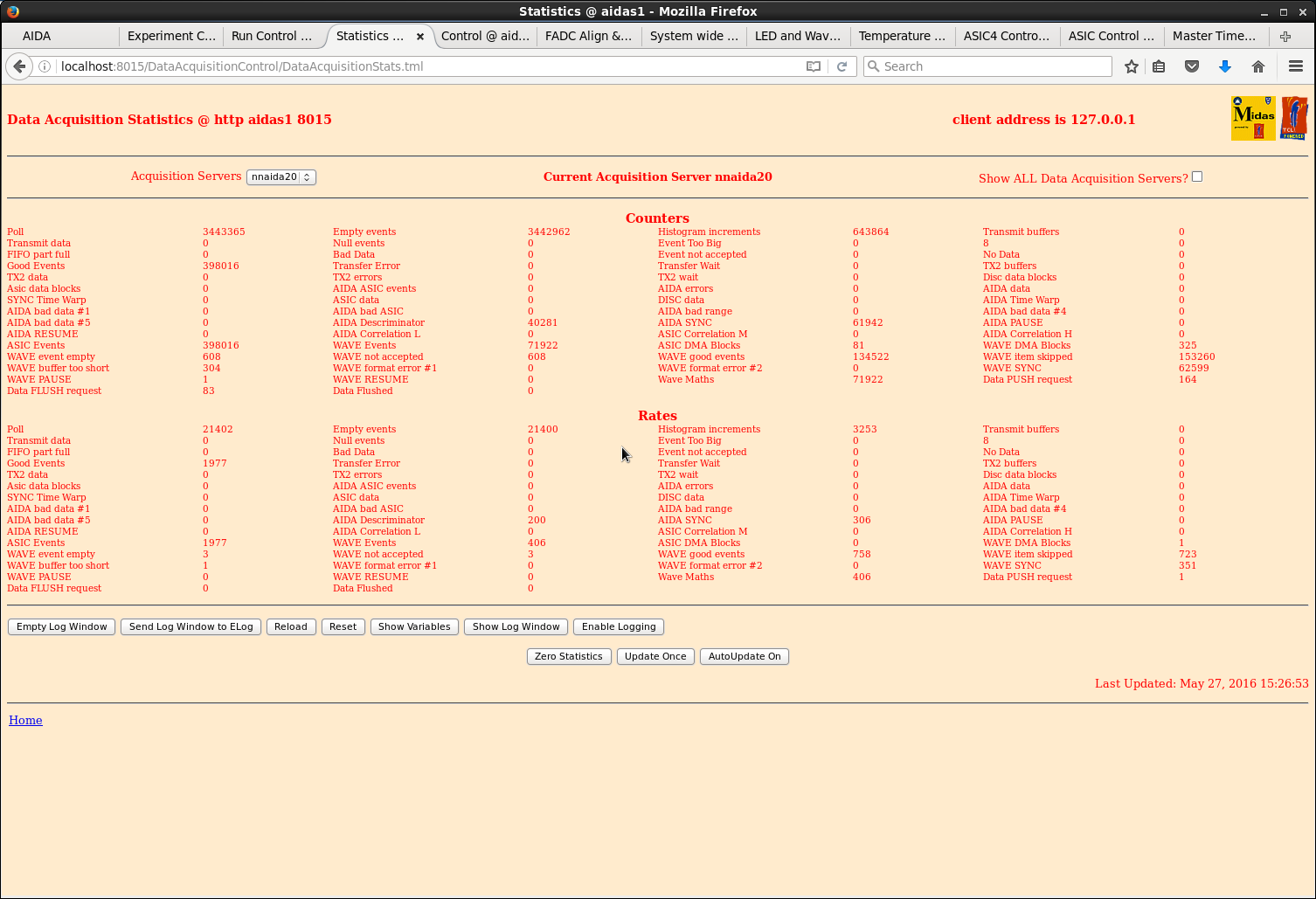

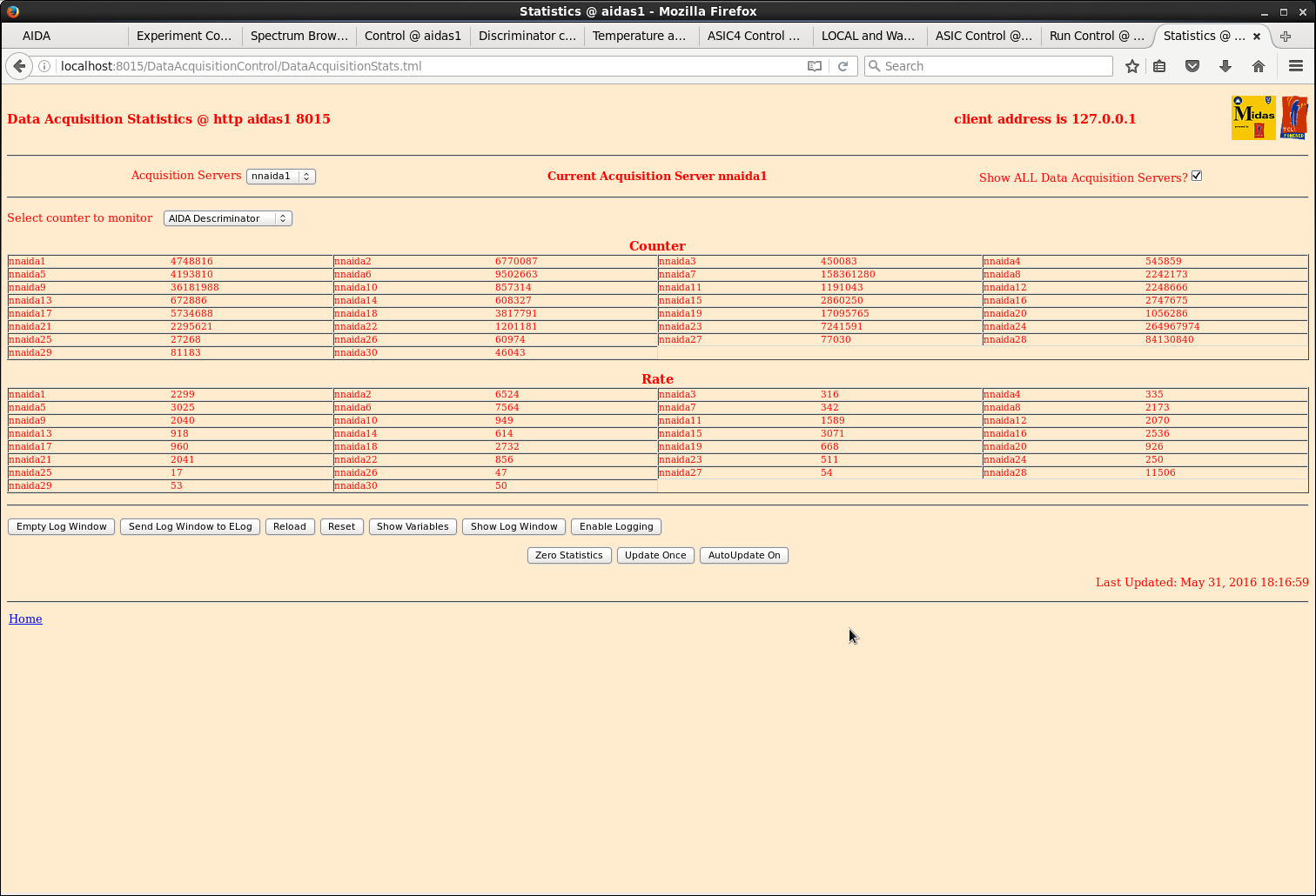

Merge statistics - see attachments 6-11

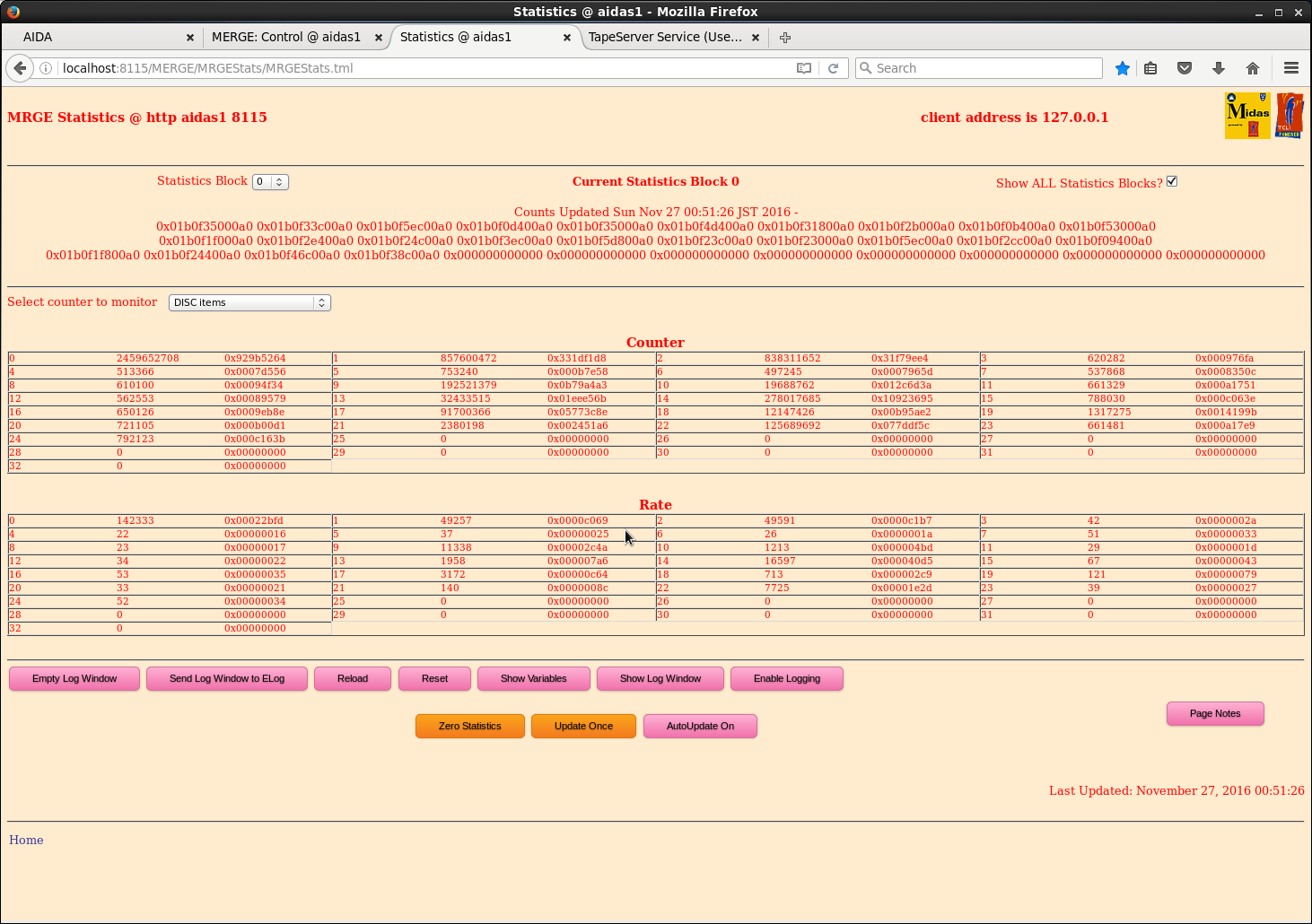

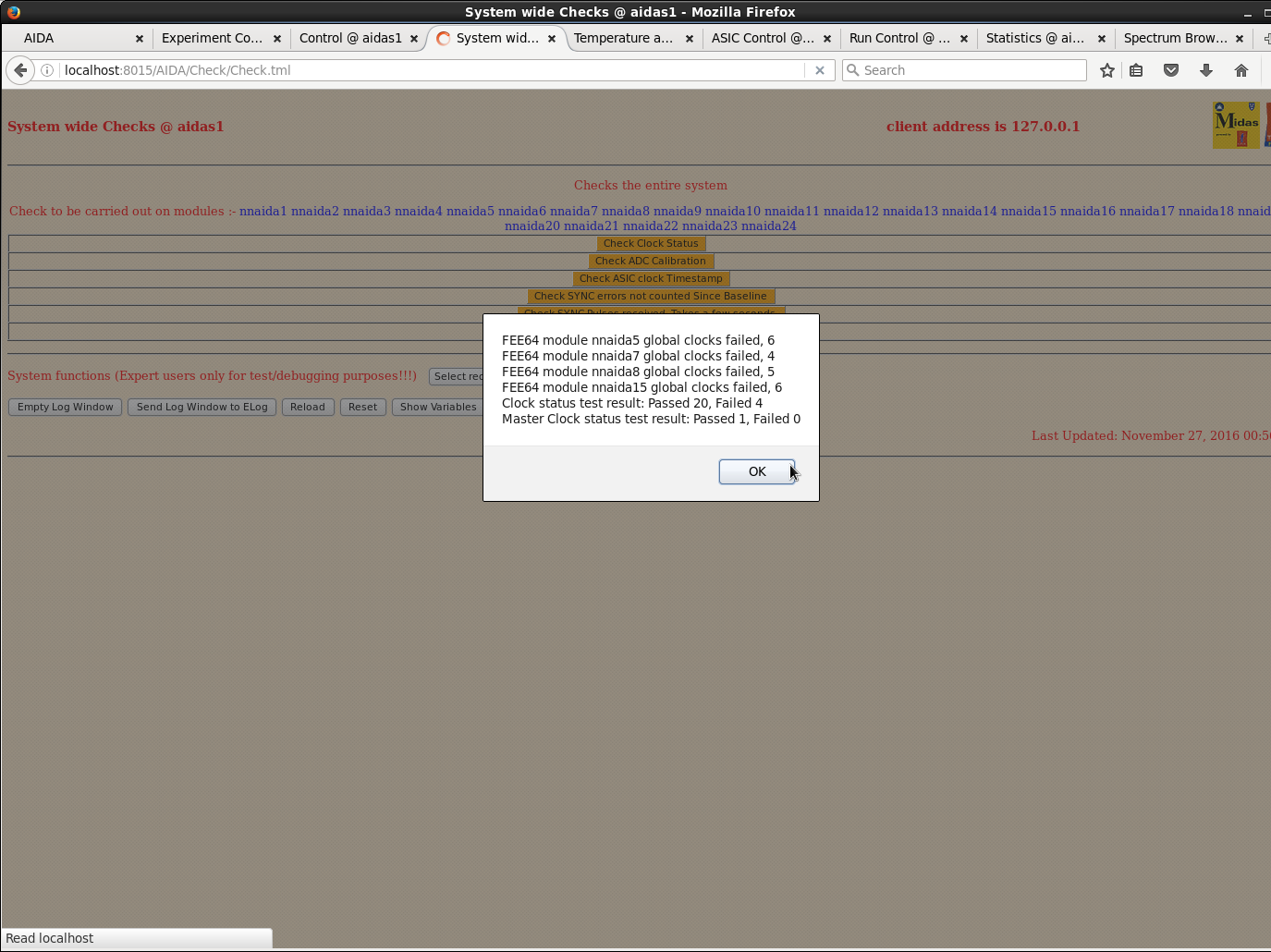

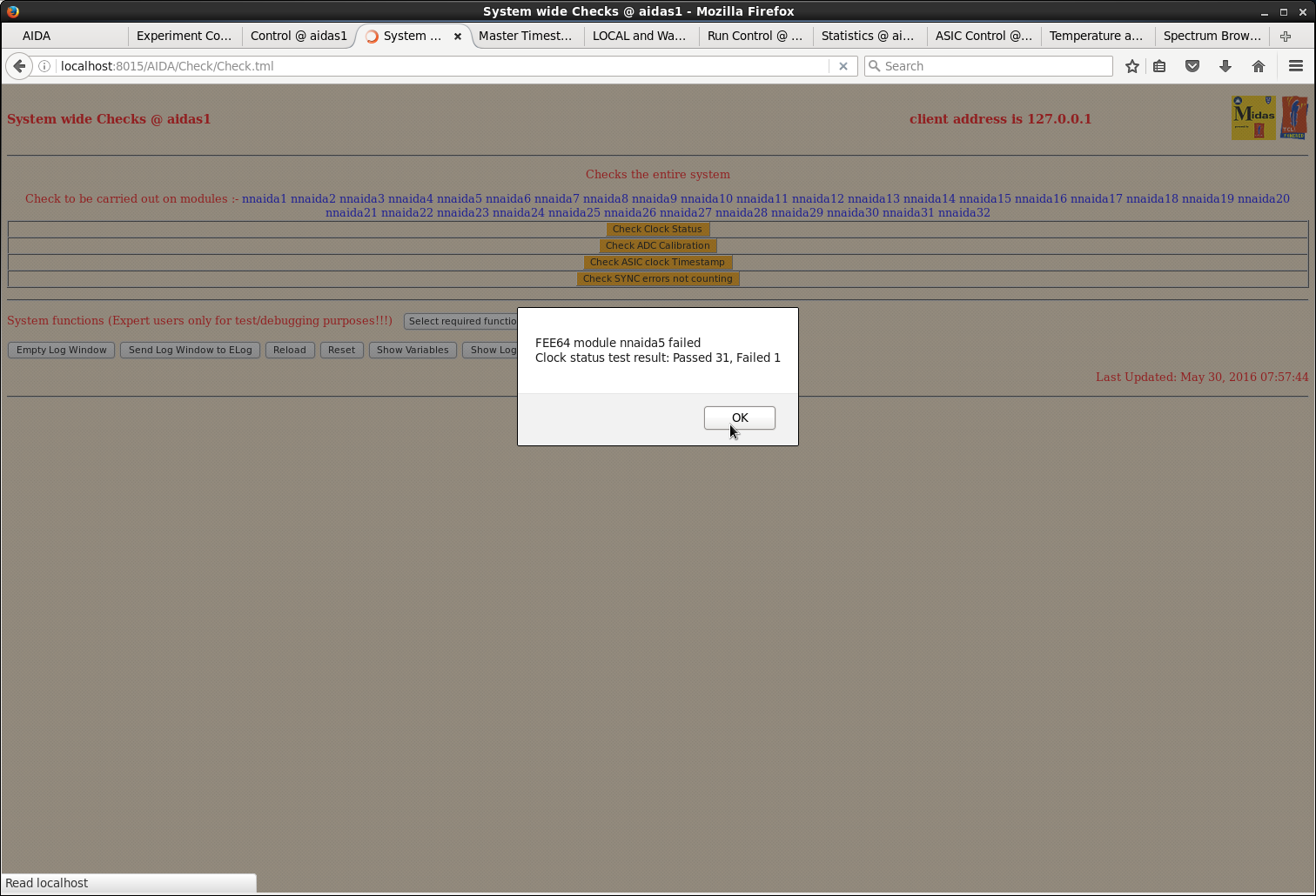

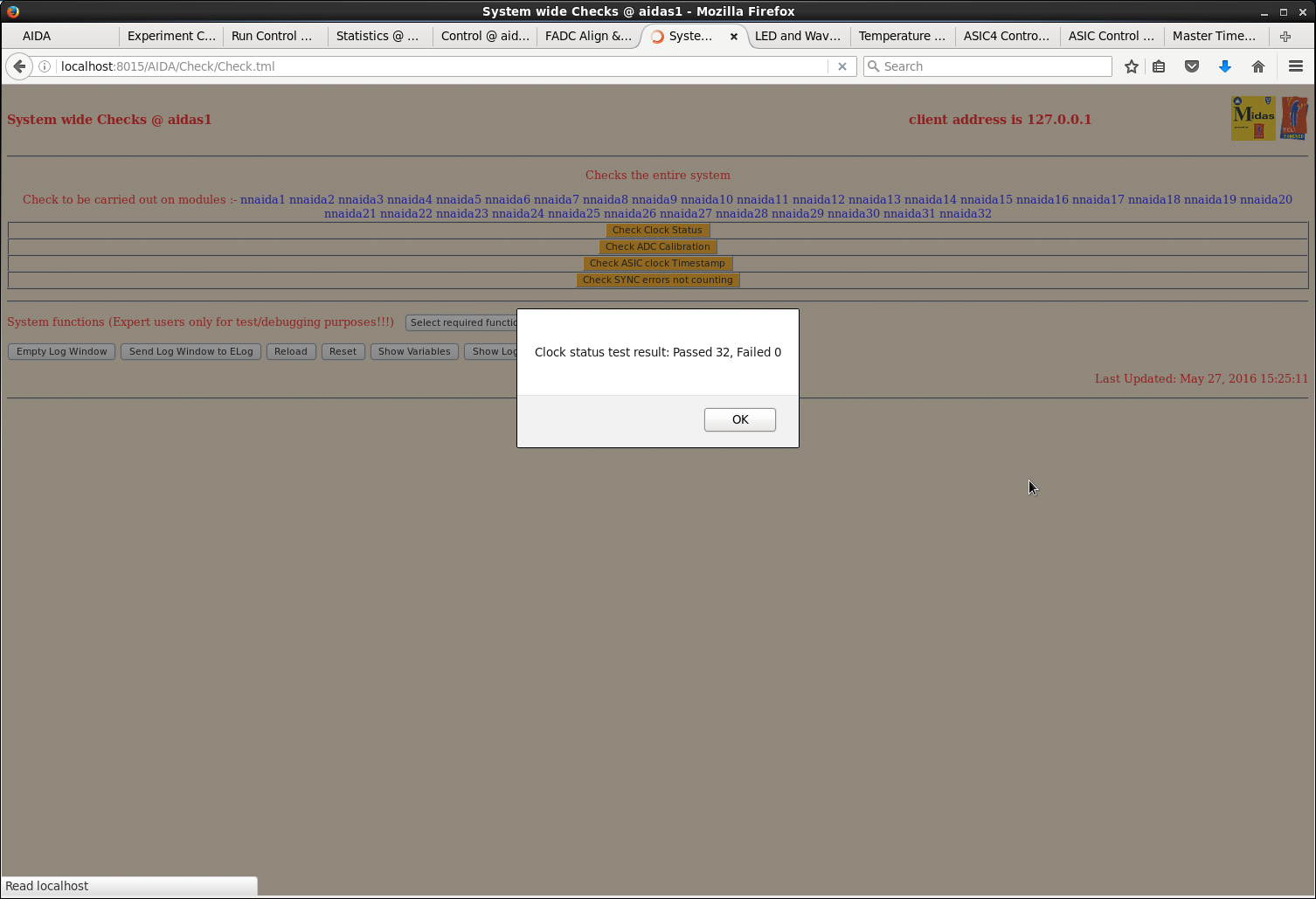

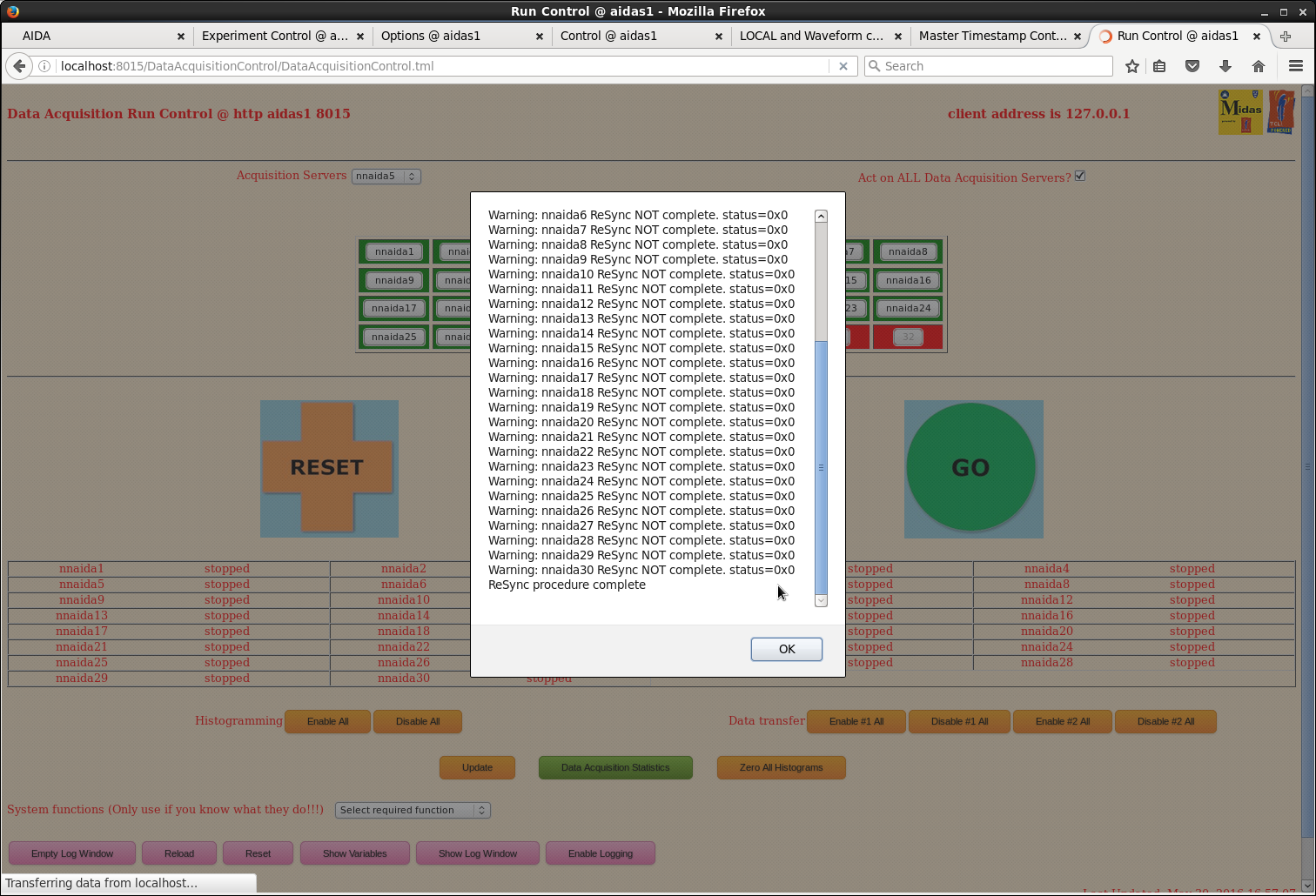

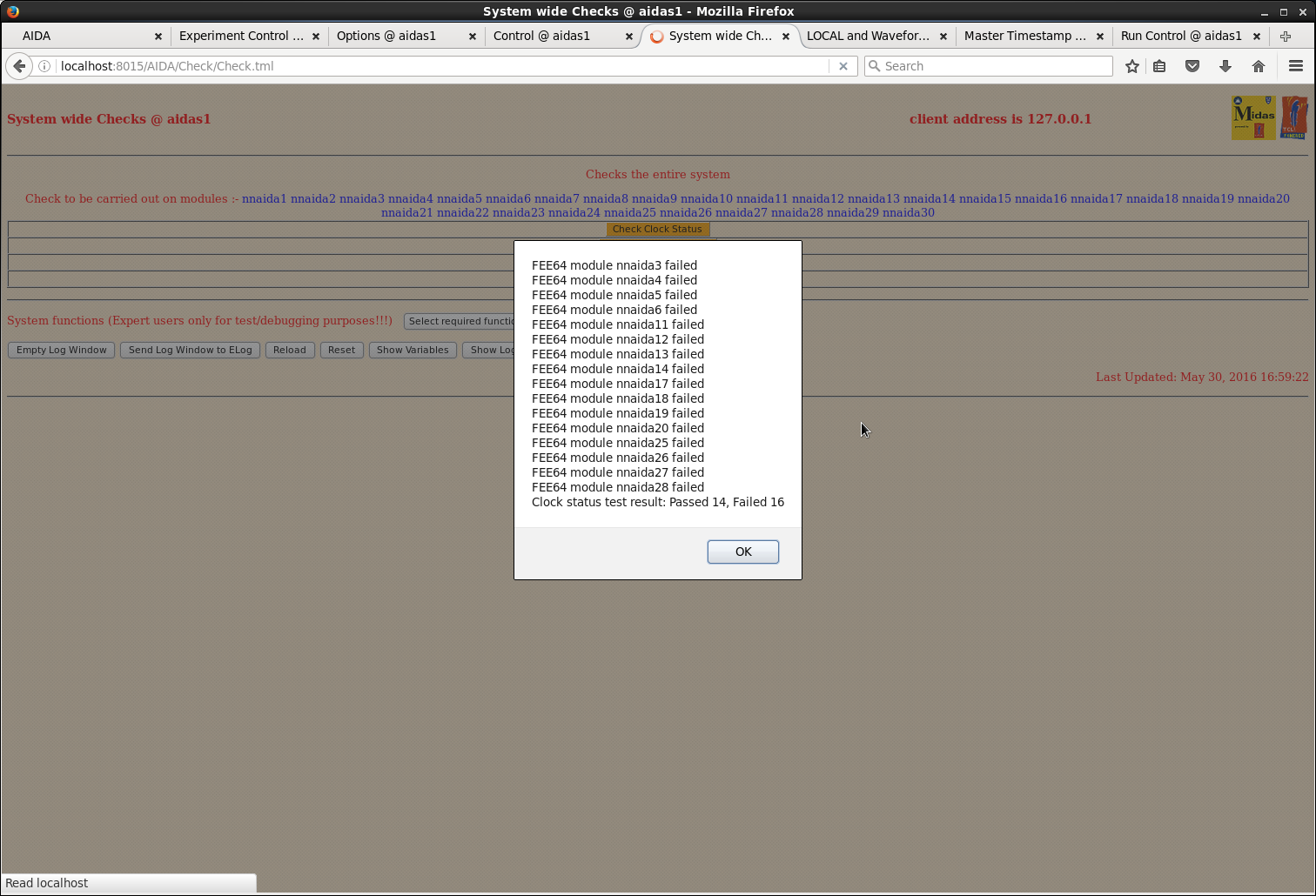

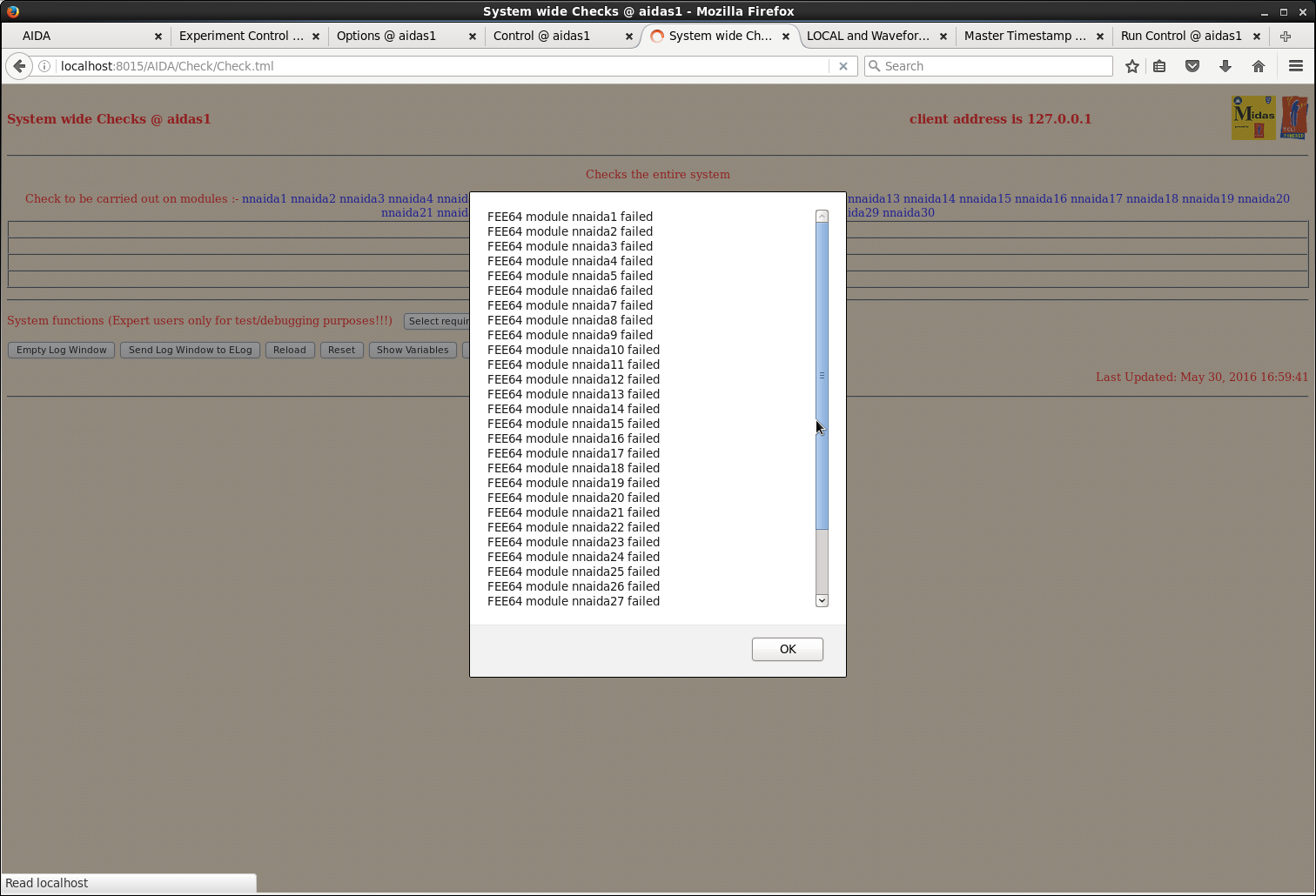

00.56 All system-wide checks OK - except clock status - see attachment 12

Note - clock status fails show bit 2 set

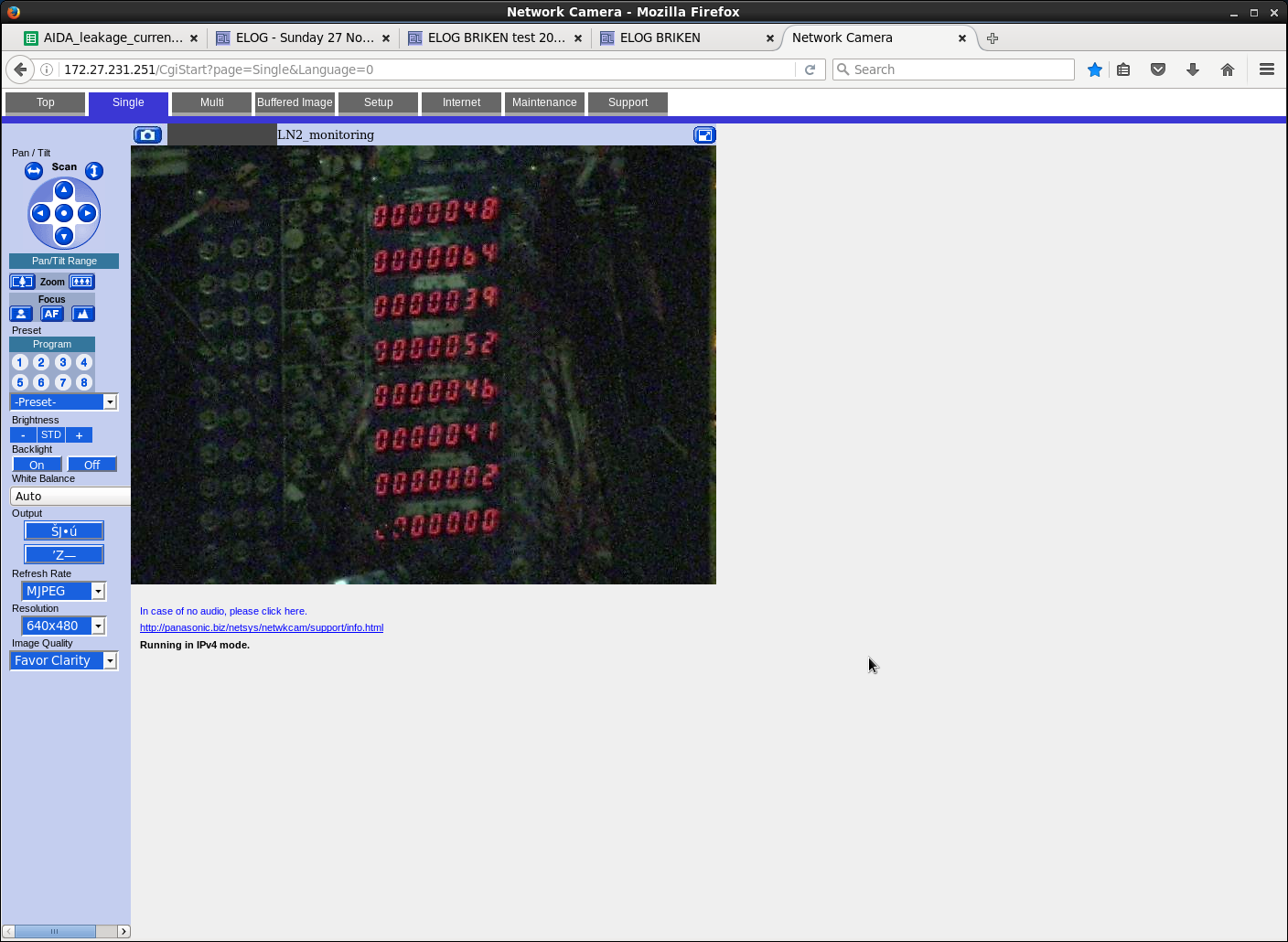

01.02 Visual scaler - see attachment 13

03.00 Beam stopped temporarily.

File R10_142 @ ~ 1.5Gb.

Beam returned ~03.06. Near end of file R10_147.

05.57 Bias and leakage currents ok (attachments 14+15).

06.25 R10 (@R10_211) stopped in anticipation of LN2 fill.

07.11 Successfully restarted DAQ after LN2 fill.

Started run R11.

07.18 Beam stopped to change stripper foil.

End of R11_1.

DAQ also stopped as I typed this.

07.53 Beam returned.

08.01 R12 started on 1GeV setting to look at suspicious data in high LEC/low HEC ranges.

Will run this for ~30mins.

(NB: Threshold of 0x20 was not changed so...)

(DK arrives on shift)

08.21 Data size of R12 very small, but maybe to be expected as the low gain usually contains ~10k counts which

is now suppressed?

Offline analysis show no implants, even in the low gain portion. Strange!

Redo this test again later today if possible

08.50 Stop R12

Change the medium energy back to low energy

08.55 Start R13 with low and high energy modes

The data stops writing to disk for some reason

09.05 Switch the degrader condition: was degraders 2 & 3, now degraders 1 & 2

Liu and Alfredo had found one 40Mg event (it seems we have about 1 such event per hour)

However, it was only implanted into DSSD #1, so we want to implant 40Mg deeper (N=1 statistics, woohoo)

So now, 0.5 mm W (+1 mm Al) and 0.3 mm W (+1 mm Al)

09.14 Run takes a moment to begin (data transfer links on FEE 3 and 4 dropped out briefly). R14 now.

09.39 Data writing stopped. We re-sequence the merger (toggle data transfer on all FEE64s), and start run R15.

09.43 R15 stops writing to disc. All system checks still passed, but not writing.

Restart merger but lose contact with nnaida14.

09.50 Power cycle FEEs.

10.20 Start run R16 -- garbage

nnaida13 refuses to calibrate ADCs

Maybe miscommunication with BRIKEN team?

When we restart, they need to reload parameters, and then they cannot see our sync (or we are actually not

sending it?)

10.25 Start run R17

Still the time stamp from AIDA is not visible on the sync check?

One of the Check ASIC Control tests returned something other than OK

(sorry, we did not copy it)

But trying it again (w/o other changes), then it returned the default OK values.

BRIKEN is not synced with BigRIPS? They don't know if it gets syncs from AIDA or not

All AIDA sync checks appear as normal, however

10.36 BRIKEN and AIDA seem to now be synchronized (we did nothing on the AIDA side)

It is unclear if we are sync'd with BigRIPS.

Stop this run to get aligned with BRIKEN

10.41 Start R18. Checks on ASICs and SYNC come back good.

Degrader settings (not changed): 3 mm Pb,; 0.5 mm W (+1 mm Al); 0.3 mm W (+1 mm Al)

F11 plastic rate 8 cps

BigRIPS run 1026; started 10:27

(CG leaves shift)

(TD arrives)

12.28: BigRIPS run number 1028

12.58 Checking the synchronization, and it is not correct.

R18_28: BRIKEN issues a new synchronization signal

13.25 Merger stops

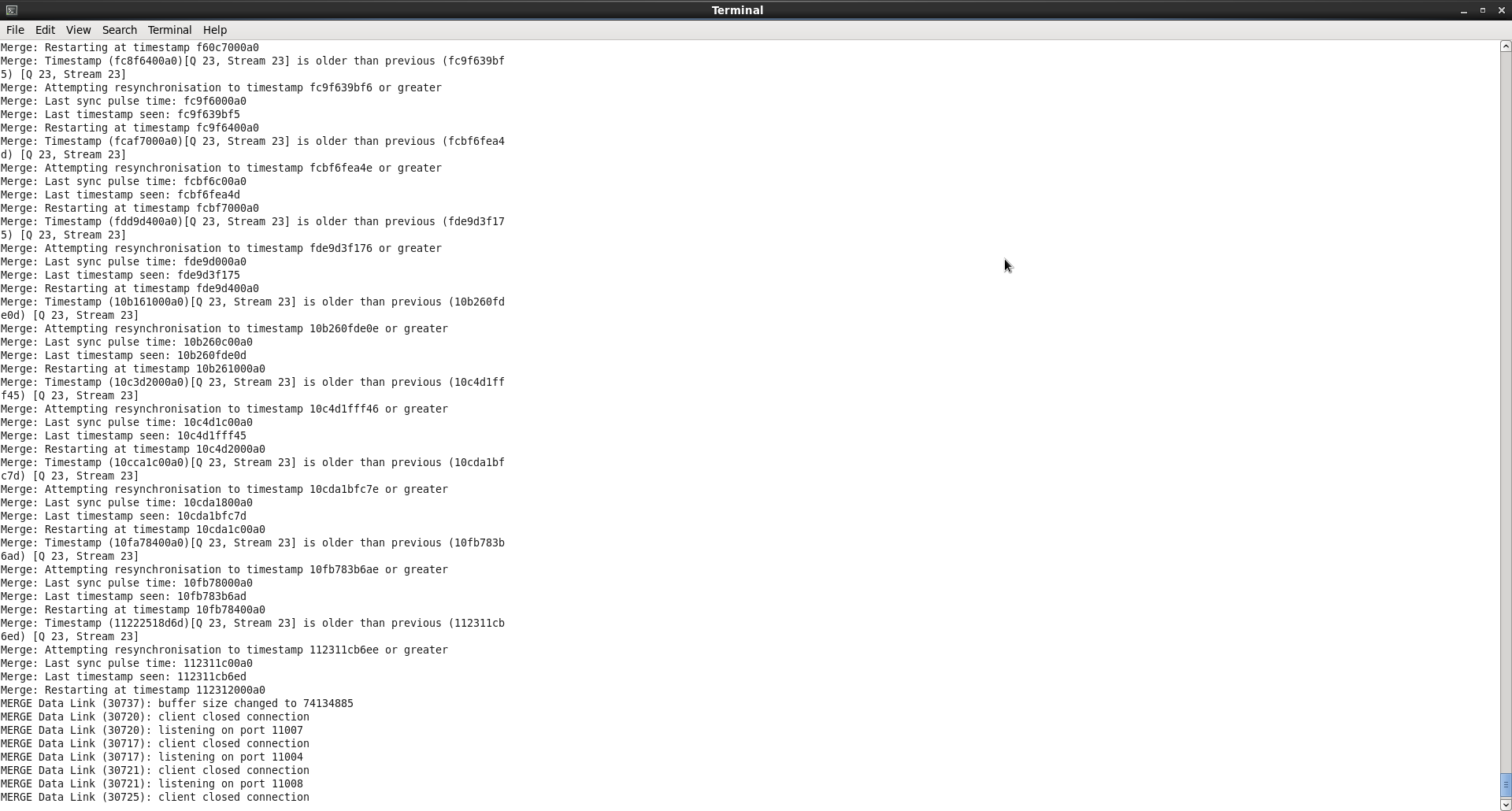

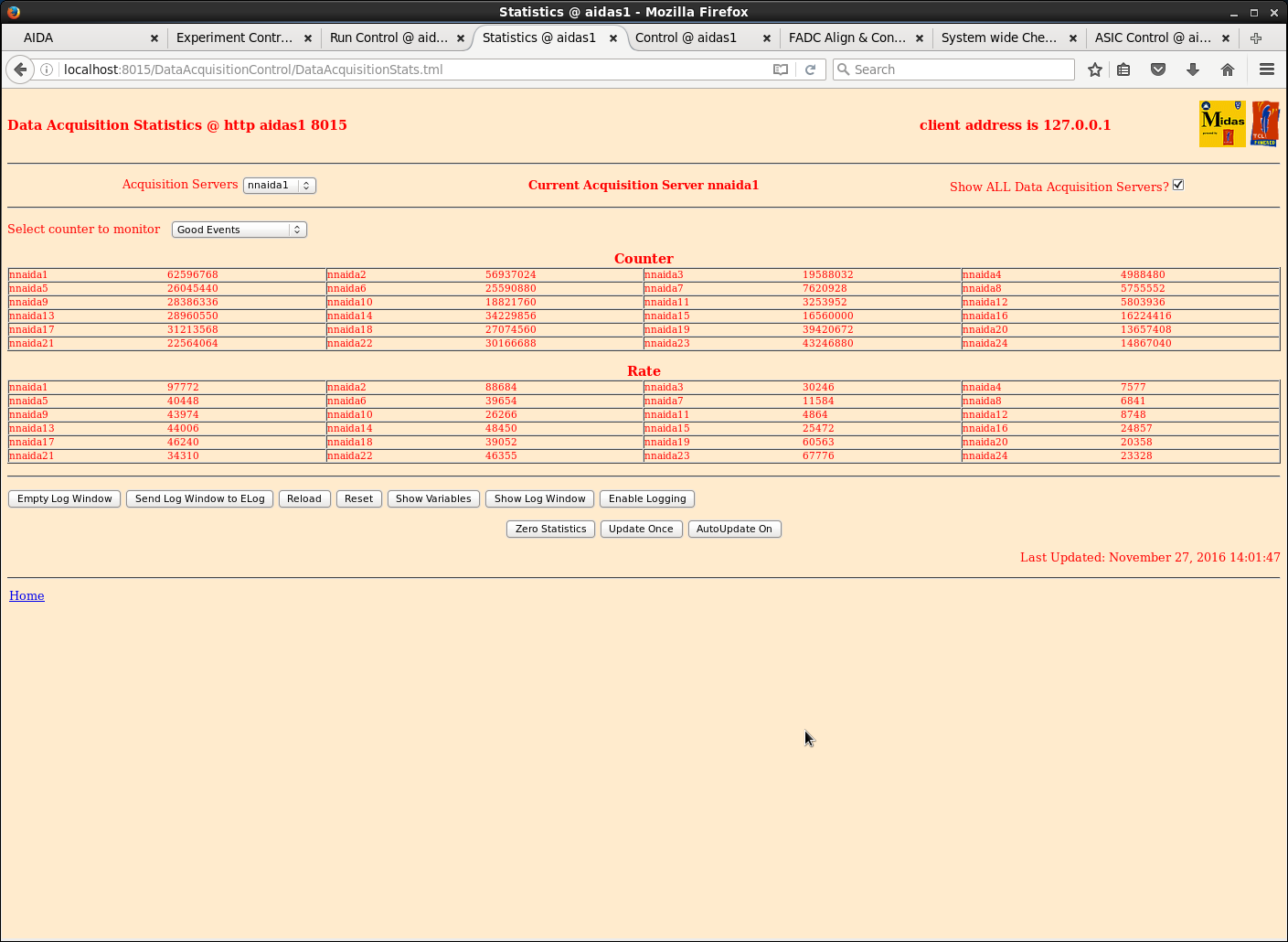

Merger error messages for Q 23 (nnaida24) - see attachment 16

nnaida24 reboots c. 13:31 - see attachment 17

Request DAQ STOP, restart Merger

DAQ stops OK

Request DAQ RESET & SETUP

R19 started for AIDA, but we never get the full data links (junk)

13.54 nnaida15 did not show data transfer -> merger restarted

Now R20_0, DAQs look good, BRIKEN issued resync

BigRIPS run 1028 still

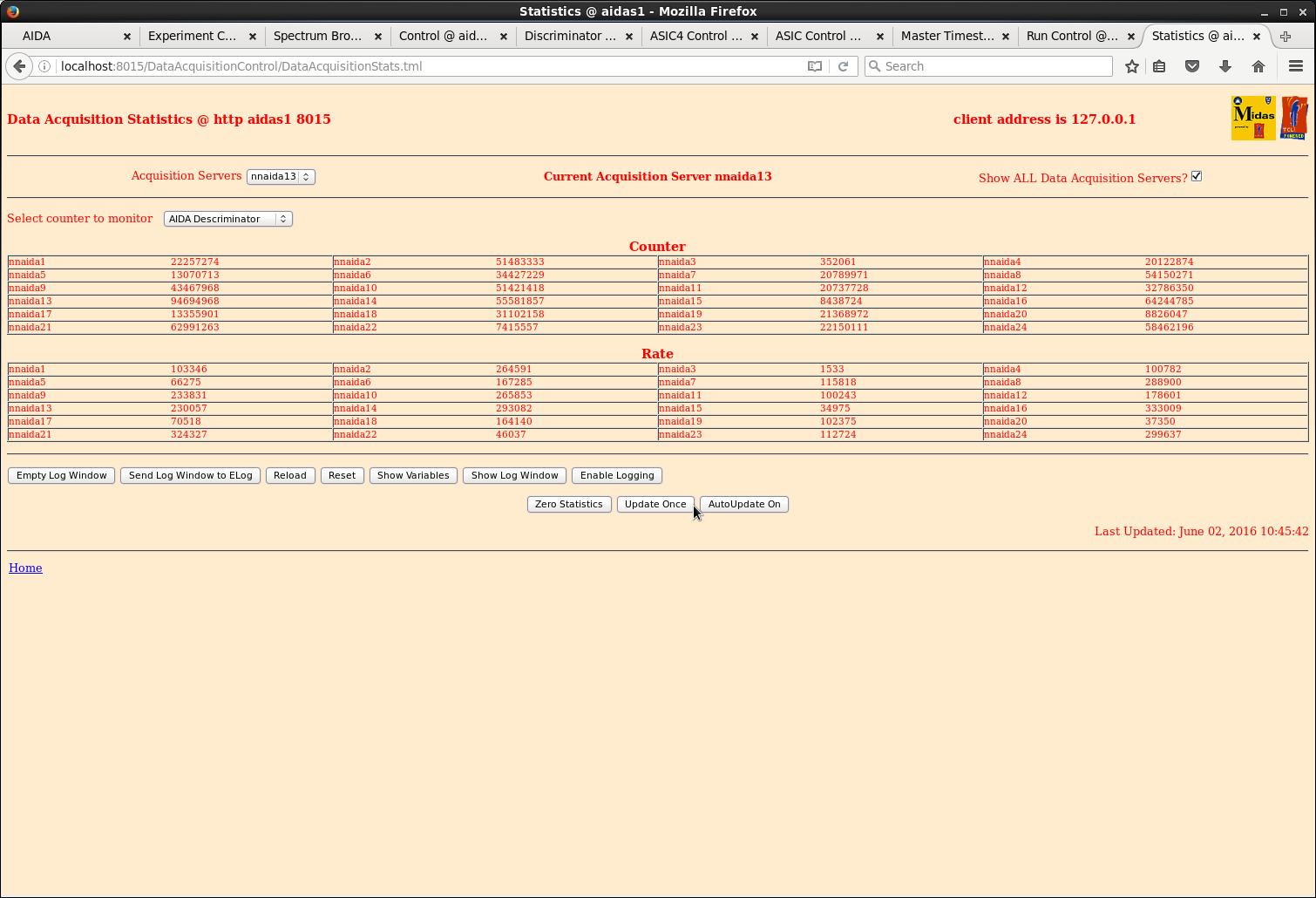

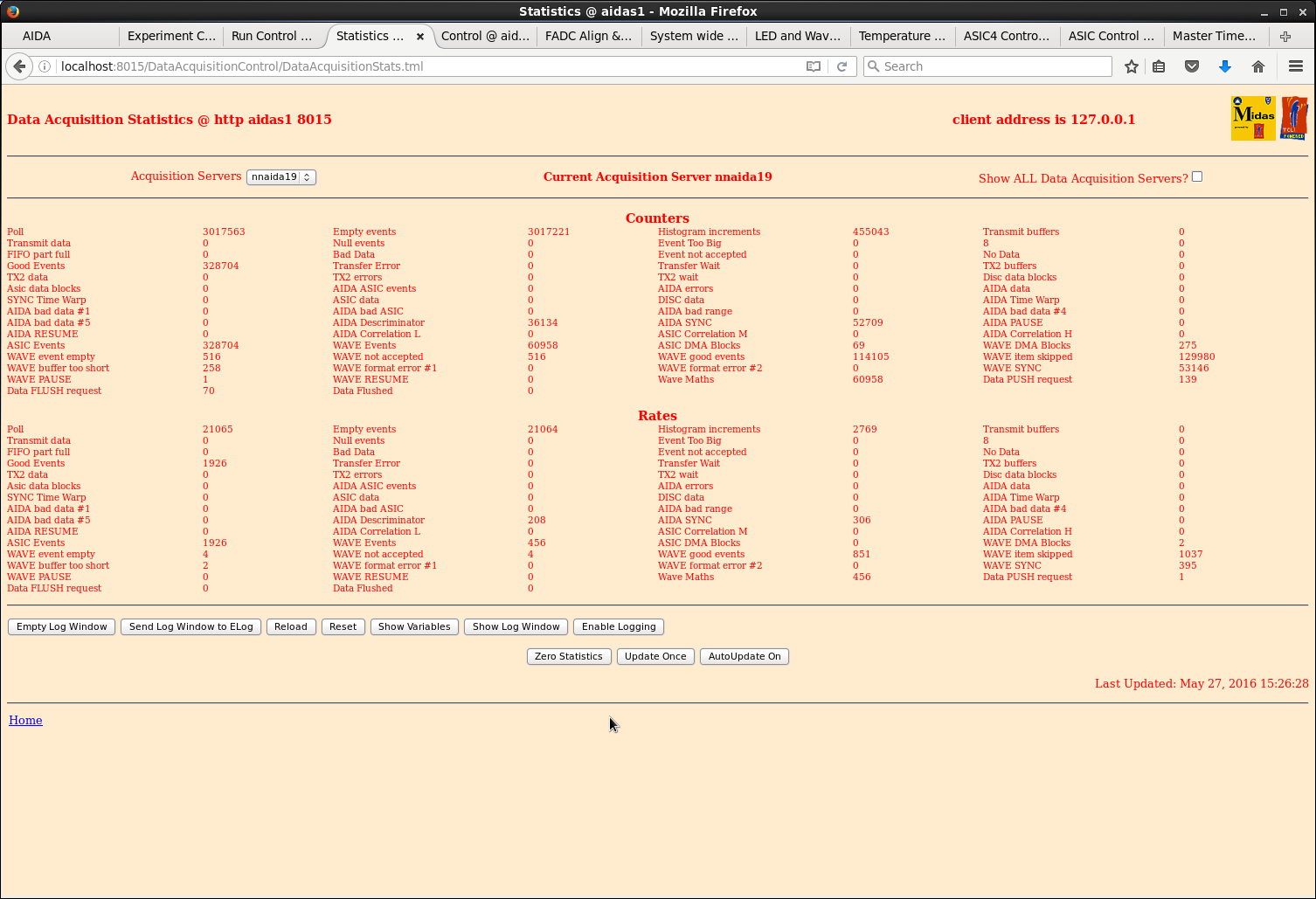

14.00 SyncCheck see attachment 18

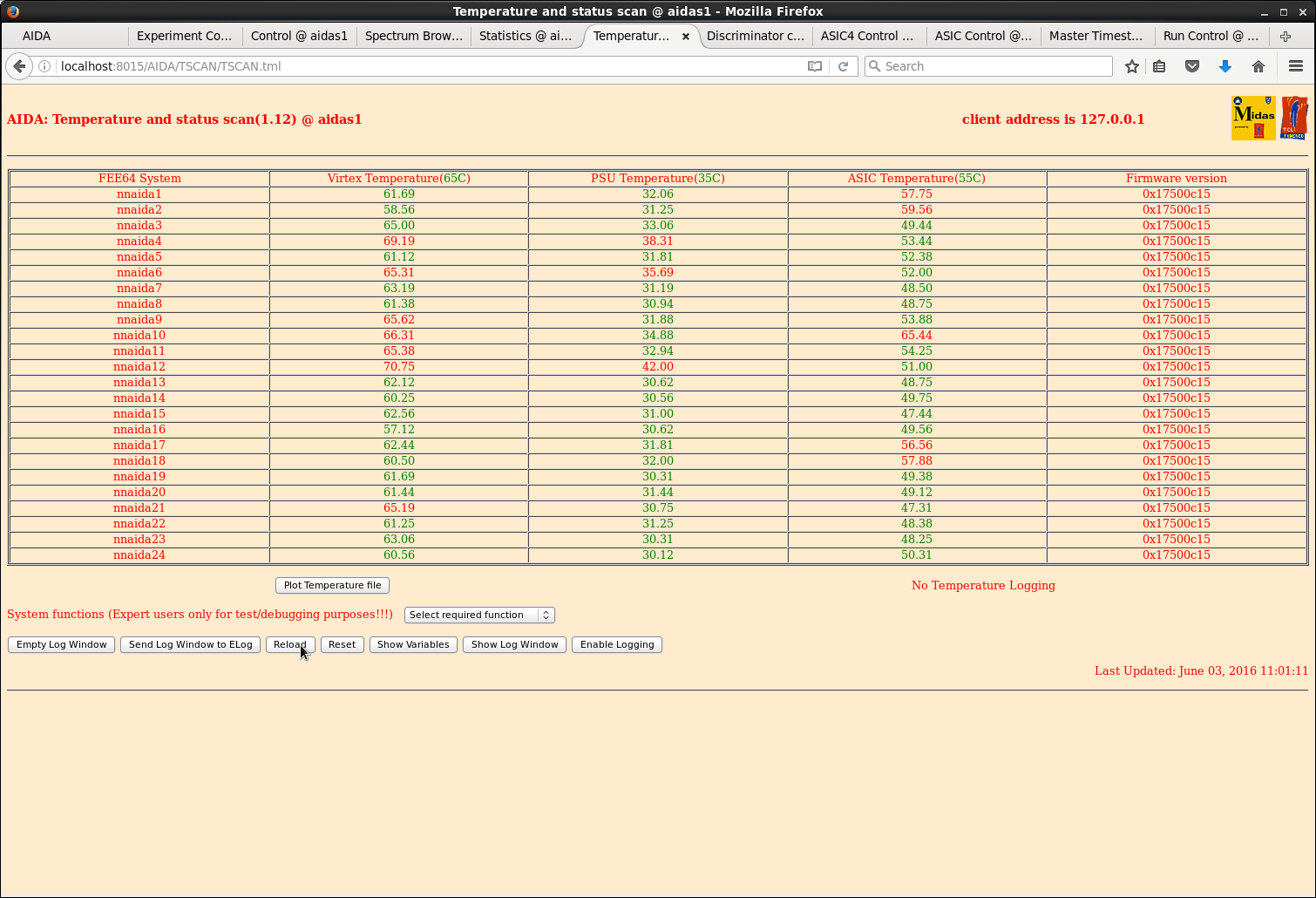

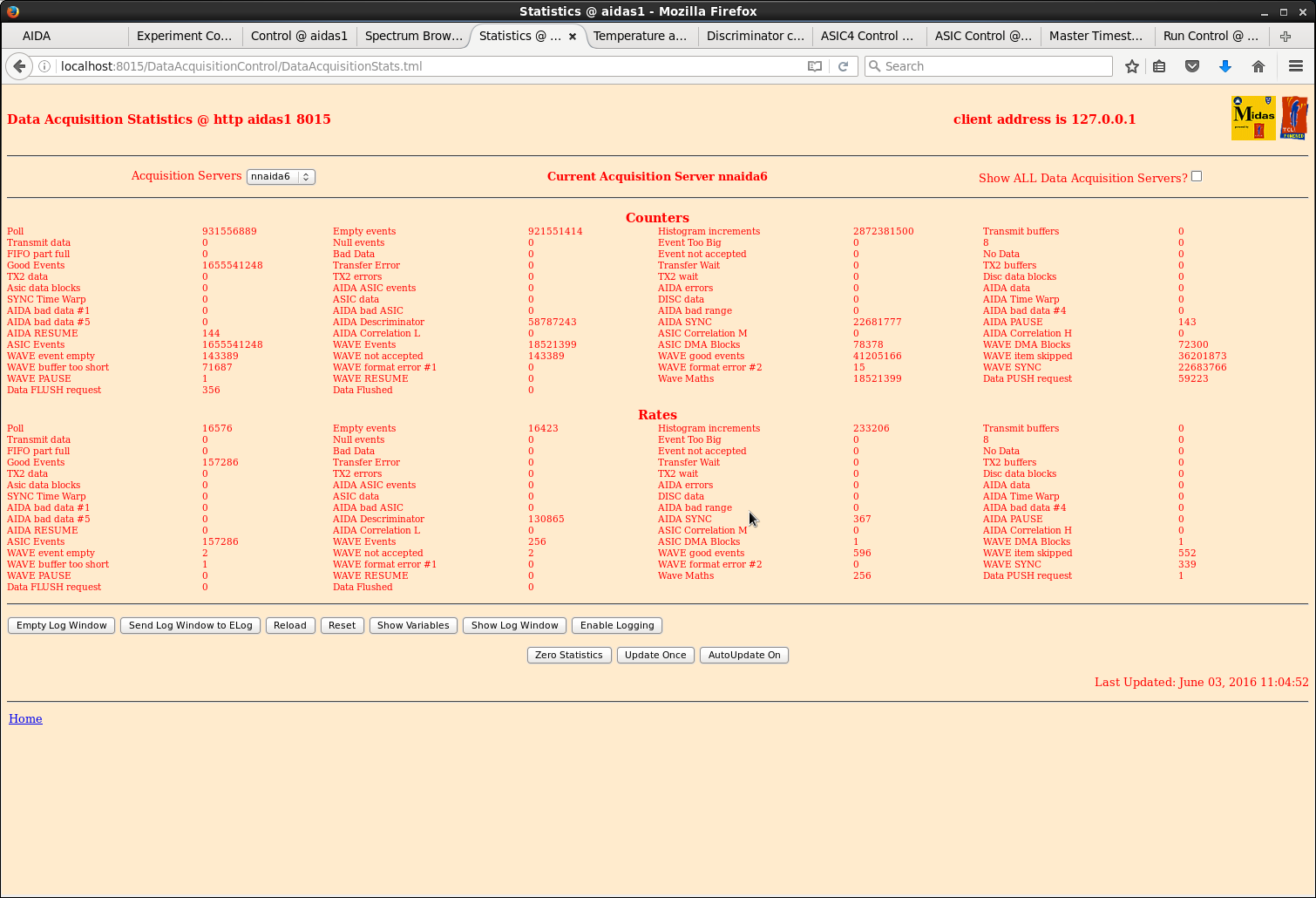

good events statistics - see attachment 19 - rates lower than observed yesterday, not clear why

|

| Attachment 1: 1.png

|

|

| Attachment 2: 2.png

|

|

| Attachment 3: 3.png

|

|

| Attachment 4: 4.png

|

|

| Attachment 5: synccheck.png

|

|

| Attachment 6: 10.png

|

|

| Attachment 7: 11.png

|

|

| Attachment 8: 12.png

|

|

| Attachment 9: 13.png

|

|

| Attachment 10: 14.png

|

|

| Attachment 11: 15.png

|

|

| Attachment 12: 6.png

|

|

| Attachment 13: 7.png

|

|

| Attachment 14: bias1.png

|

|

| Attachment 15: bias2.png

|

|

| Attachment 16: 100.png

|

|

| Attachment 17: 101.png

|

|

| Attachment 18: 33.png

|

|

| Attachment 19: 102.png

|

|

|

|

270

|

Thu Jun 2 01:33:13 2016 |

TD, AE, CG & DK | Thursday 2 June 2016 |

09.30 DAQ left running overnight

AIDA SYNCs on all FEE64s this morning

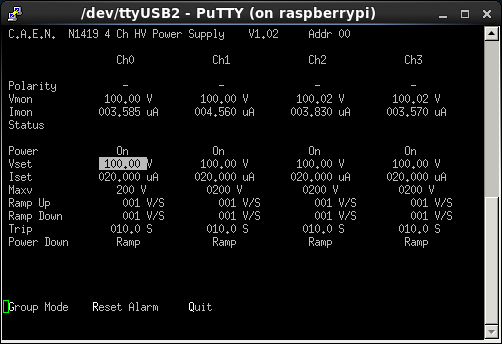

DSSSD#1 -#6 bias and leakage currents OK - see attachments 1-2

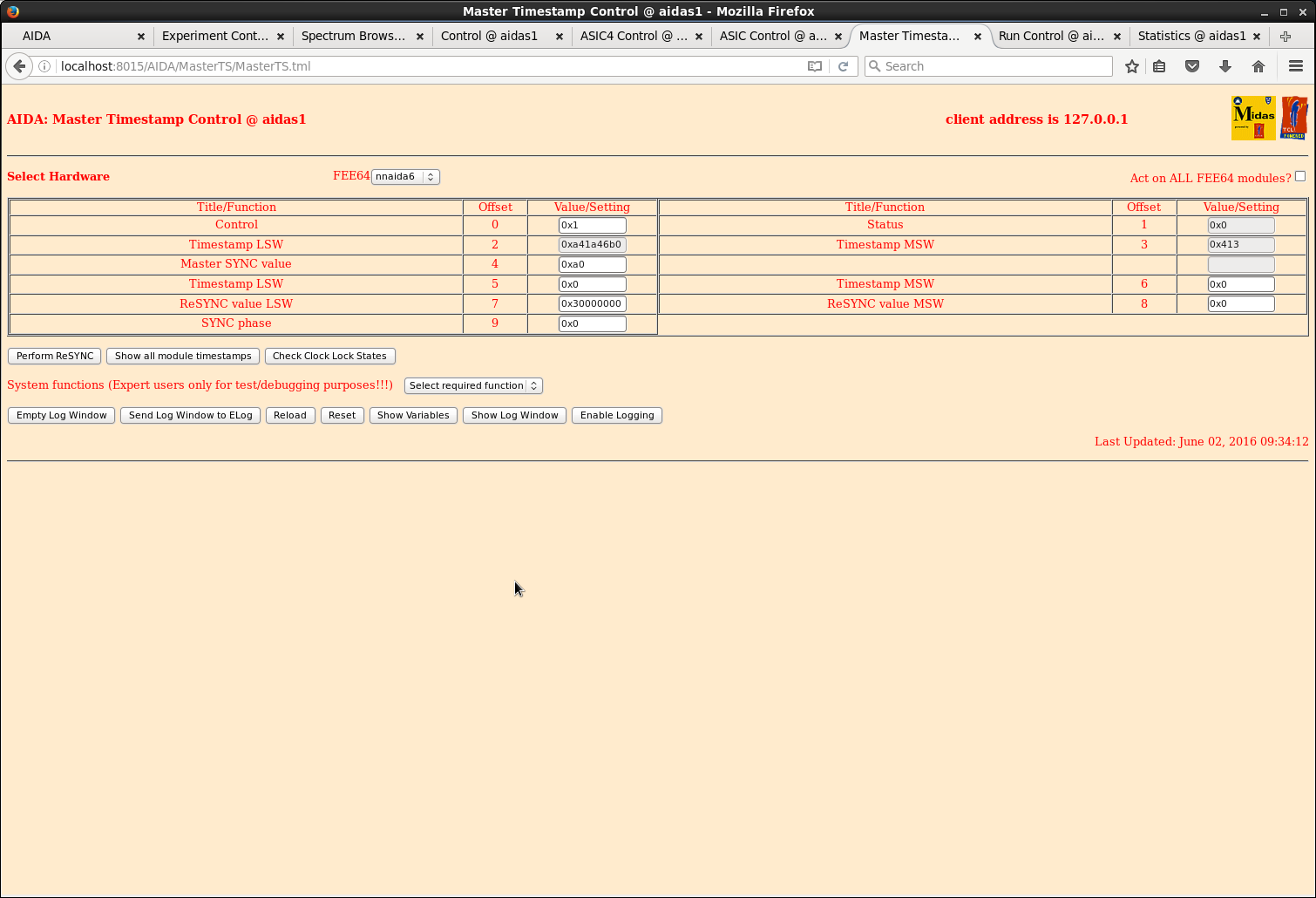

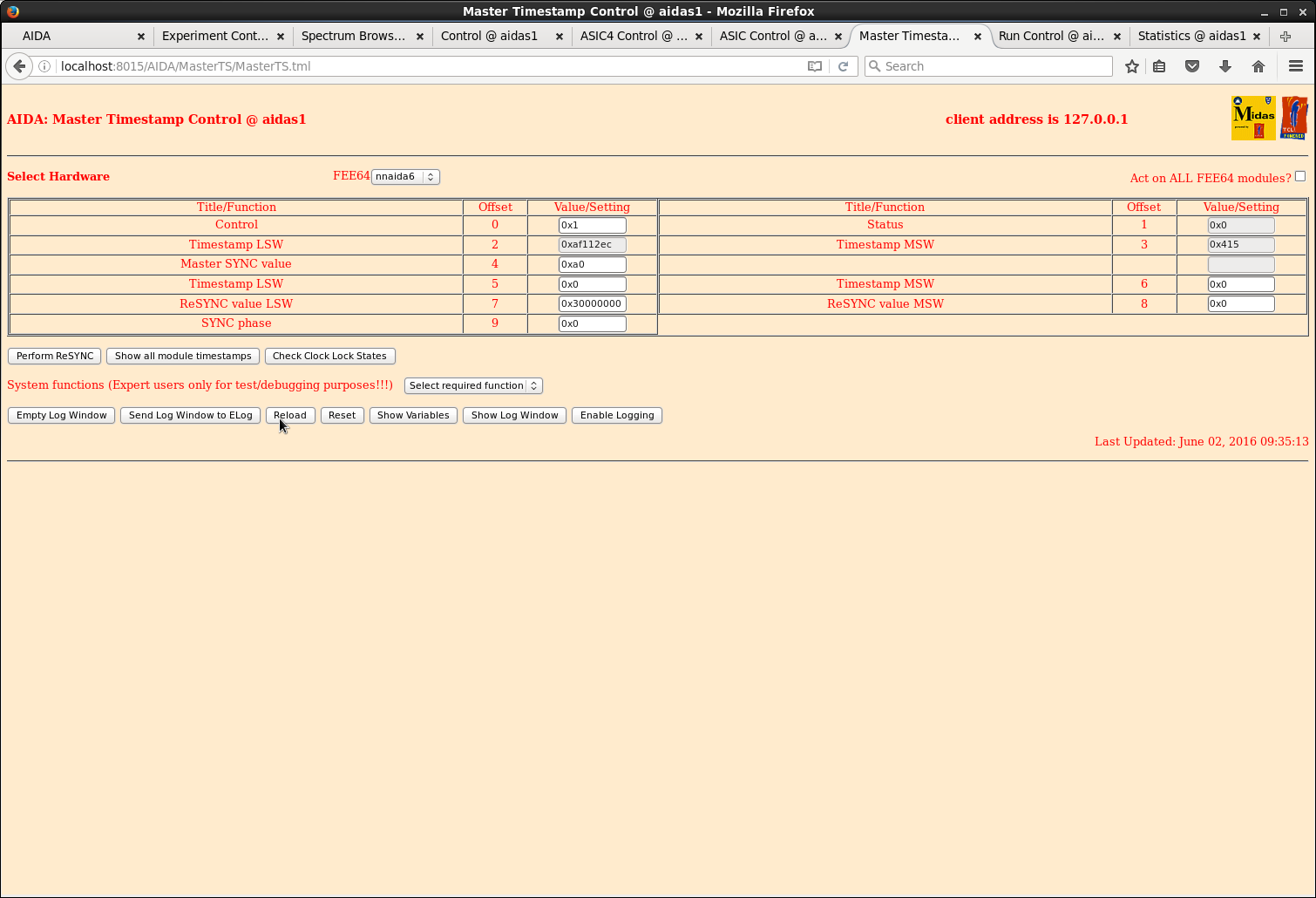

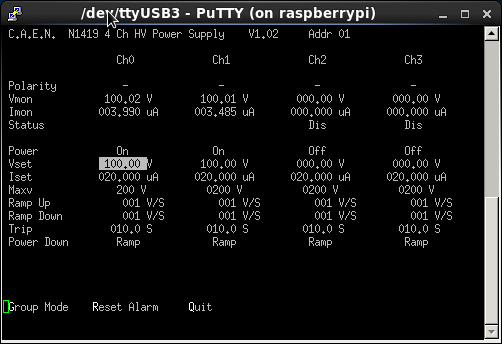

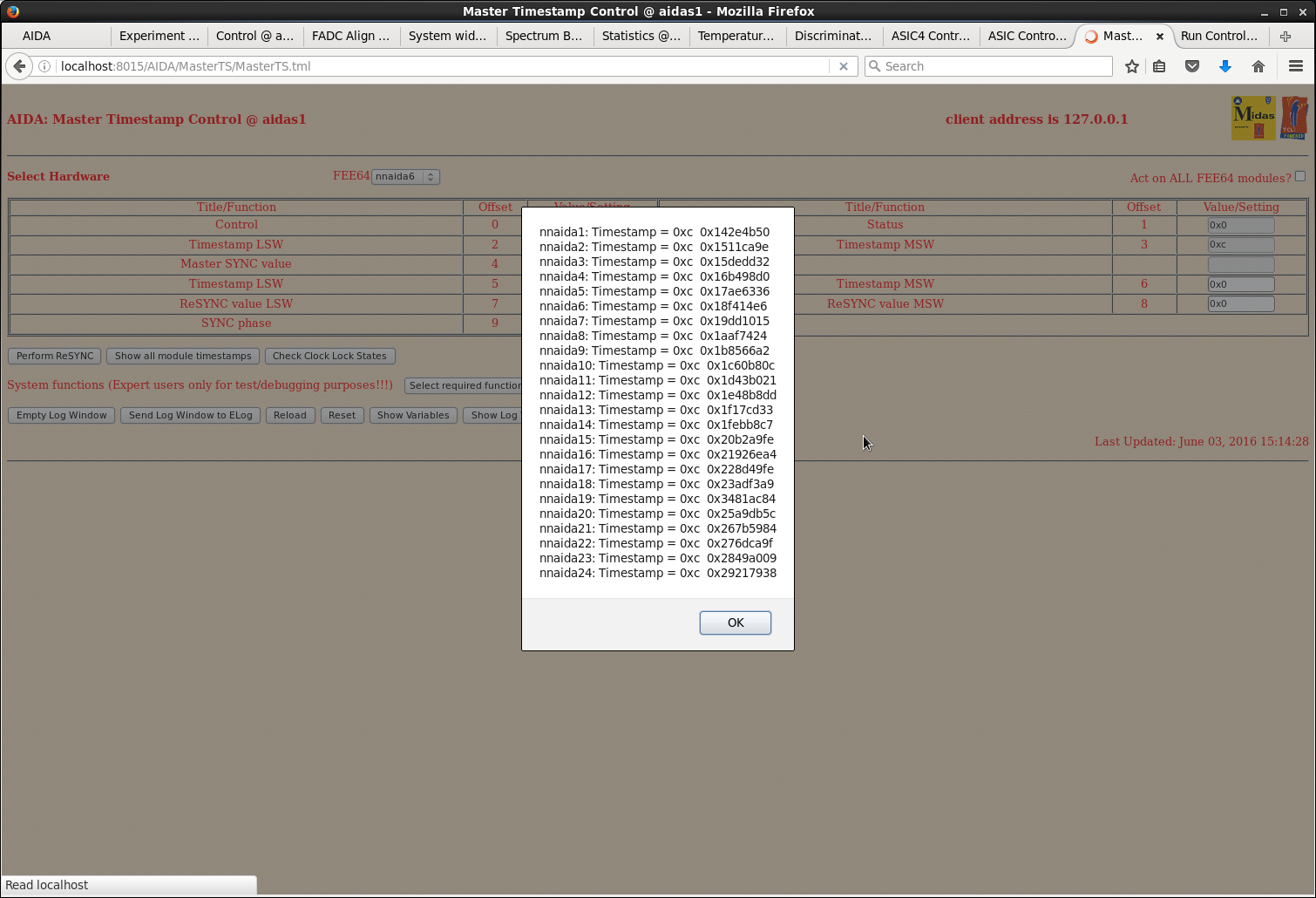

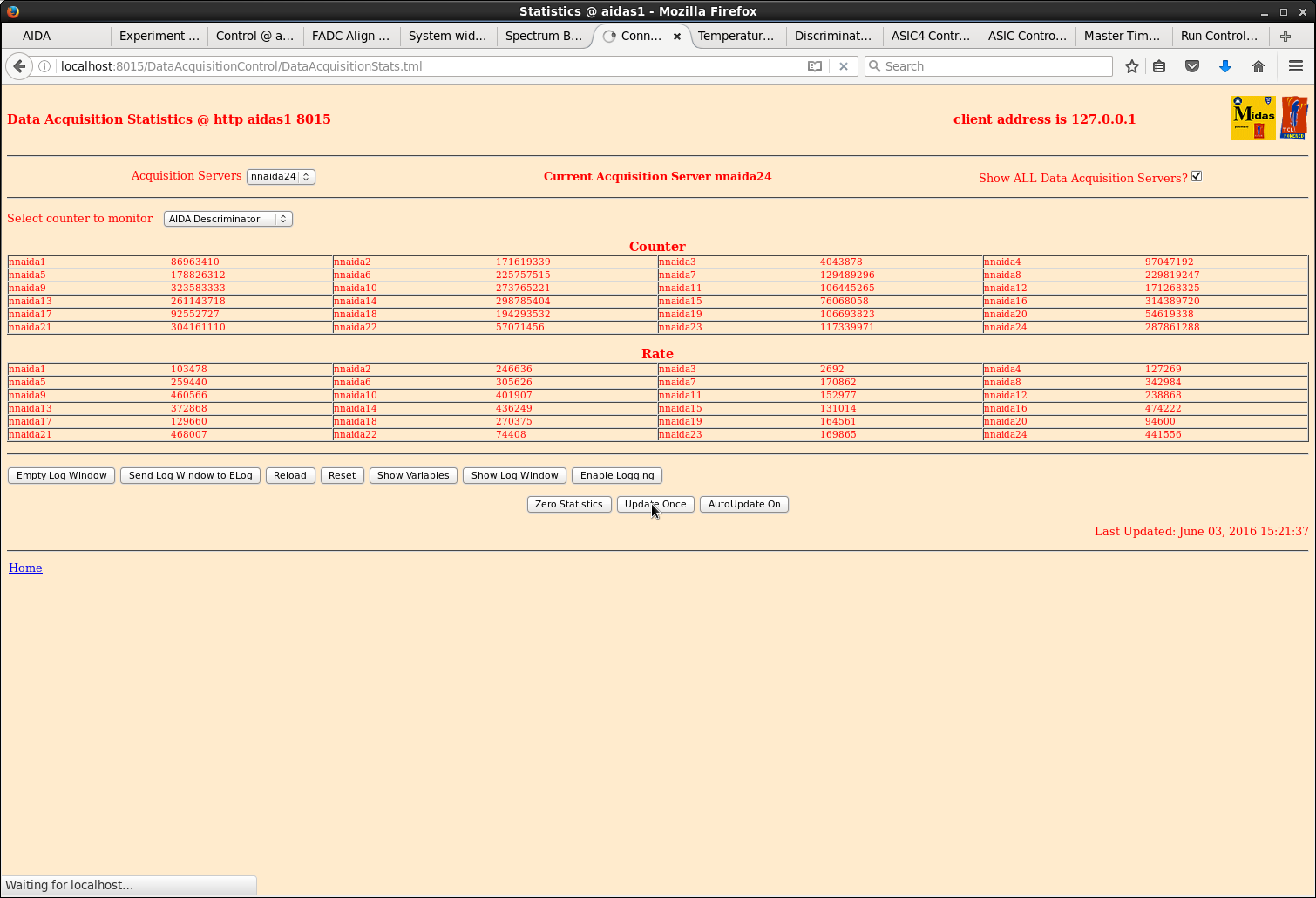

09.39 Estimation of AIDA timestamp clock frequency

See attachments 3-4

nnaida6 (master) timestamp 0x415 0x0af112ec - 0x413 0xa41a46b0 = 0x166d6cc3c = 6020320316 (dec)

elapsed time = 61s => 98.694MHz

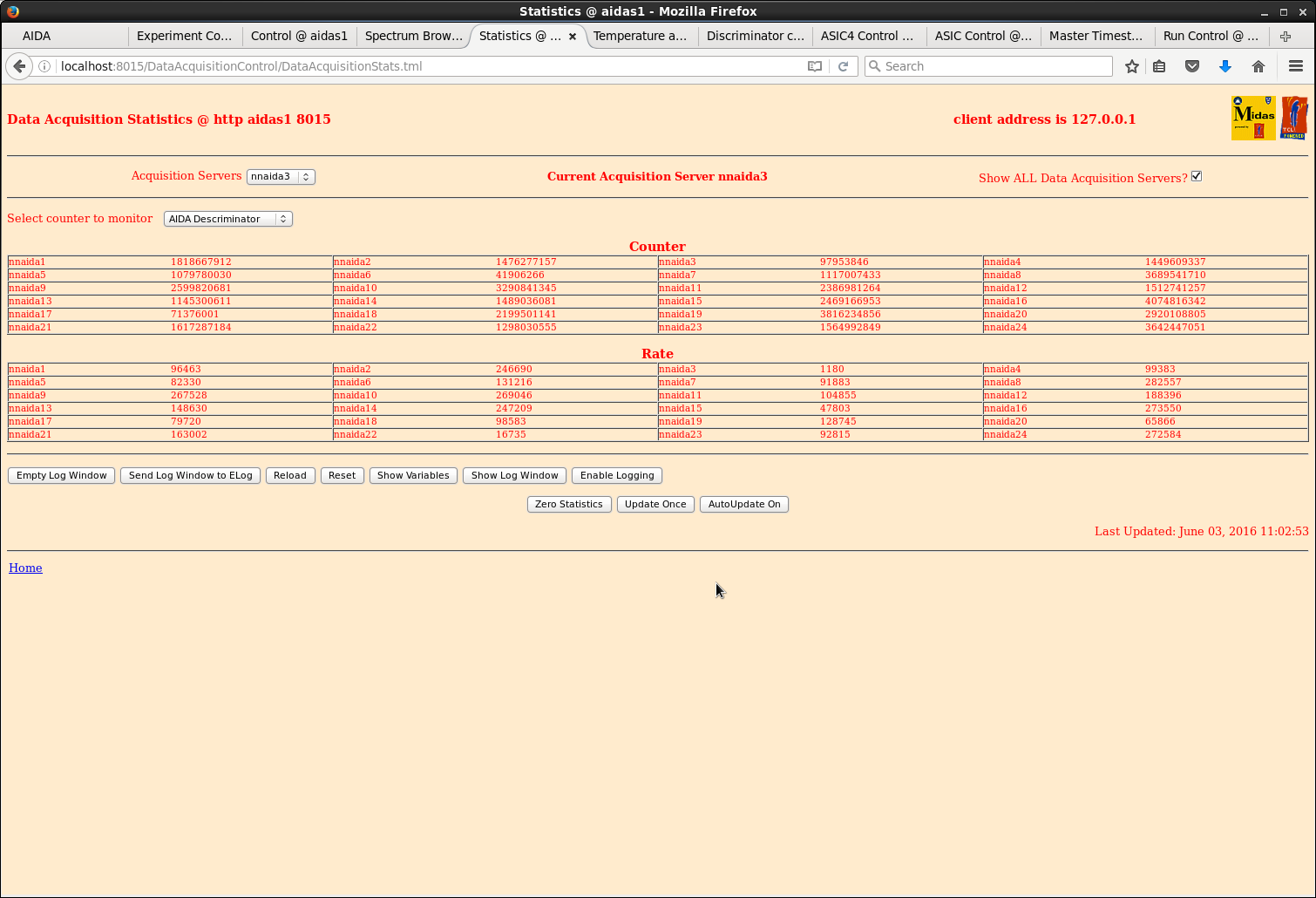

10.50 Lower LEC/MEC fast discriminator thresholds from 0xa to 0x4/0x5

AIDA discriminator rates shown attachment 5

Rates <300kHz |

| Attachment 1: 1.png

|

|

| Attachment 2: 2.png

|

|

| Attachment 3: 3.png

|

|

| Attachment 4: 4.png

|

|

| Attachment 5: 5.png

|

|

|

|

272

|

Fri Jun 3 03:10:55 2016 |

TD, AE, CG & DK | Friday 3 June 2016 | 11.00 Detector biases and leakage currents - see attachments 1-2

FEE64 temperatures - see attachment 3

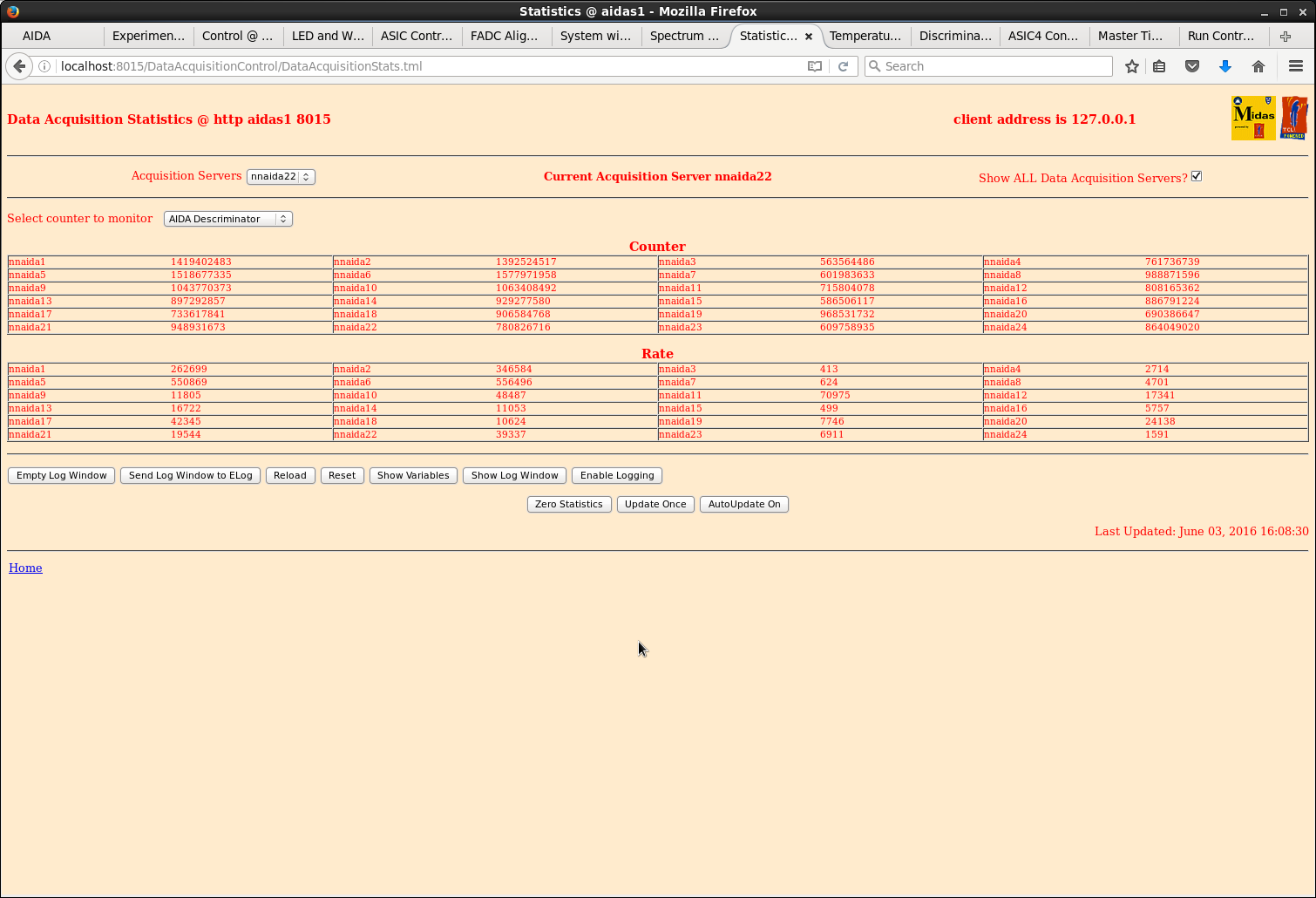

DAQ ran overnight without problem - statistics - attachments 4-8

Plan for today

1) Develop AIDA external trigger output for fast LEC/MEC discriminator threshold 0x4, or lower

2) Replace non-rev B MACB with rev B MACB in master timestamp chain (NIM module #2)

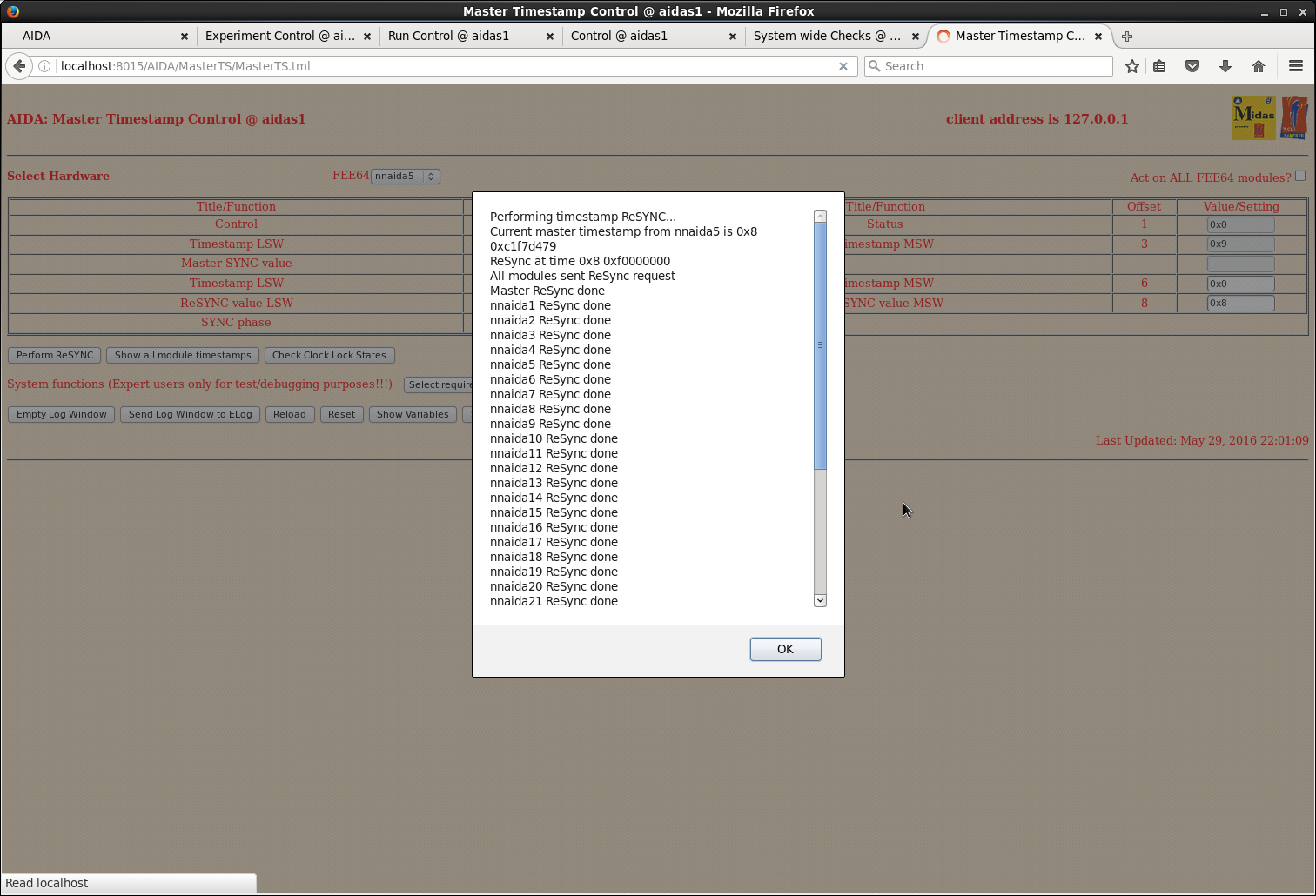

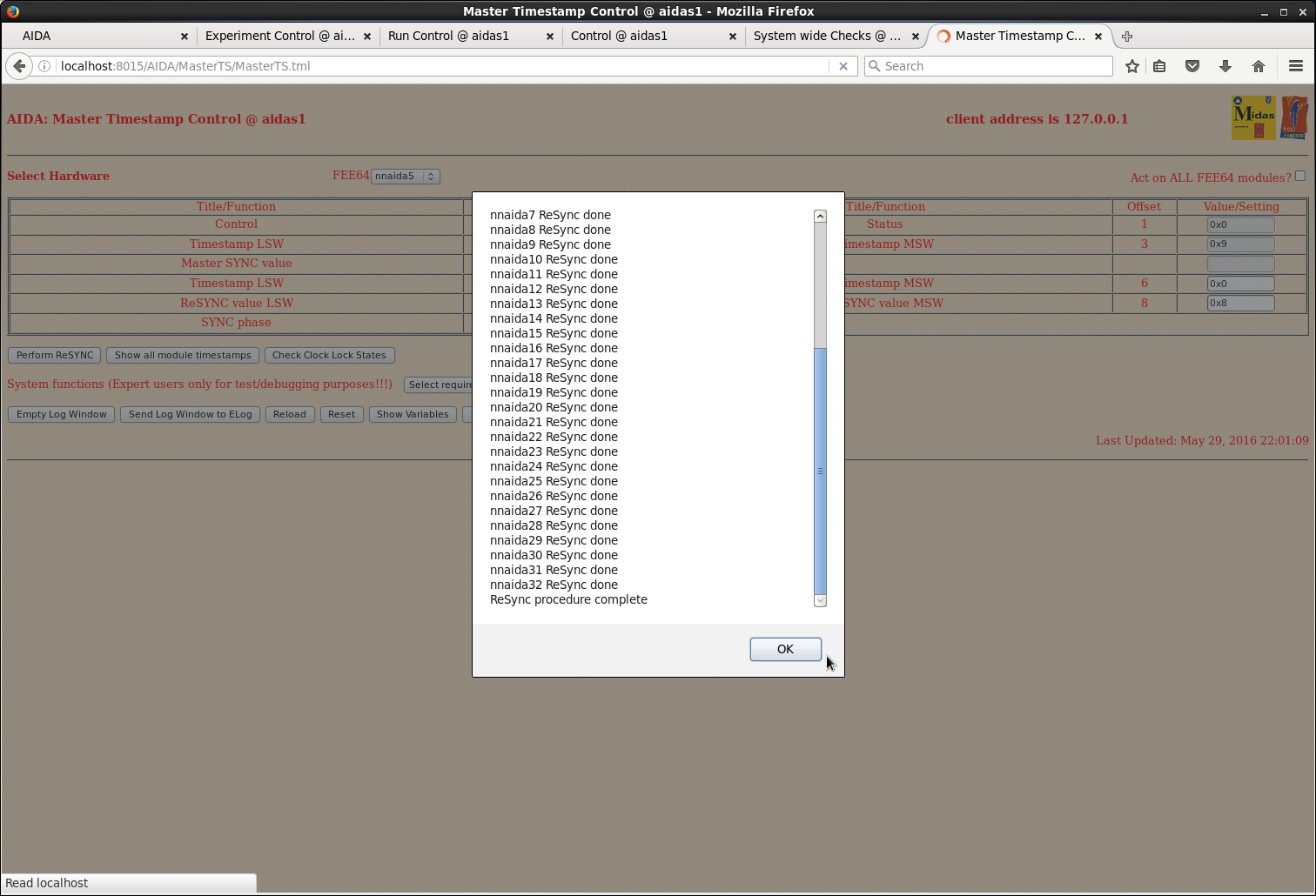

16.15 Non-rev B MACB in master timestamp chain replaced with rev B MACB module

FEE64s power cycled and rebooted.

System ReSYNC'd successfully

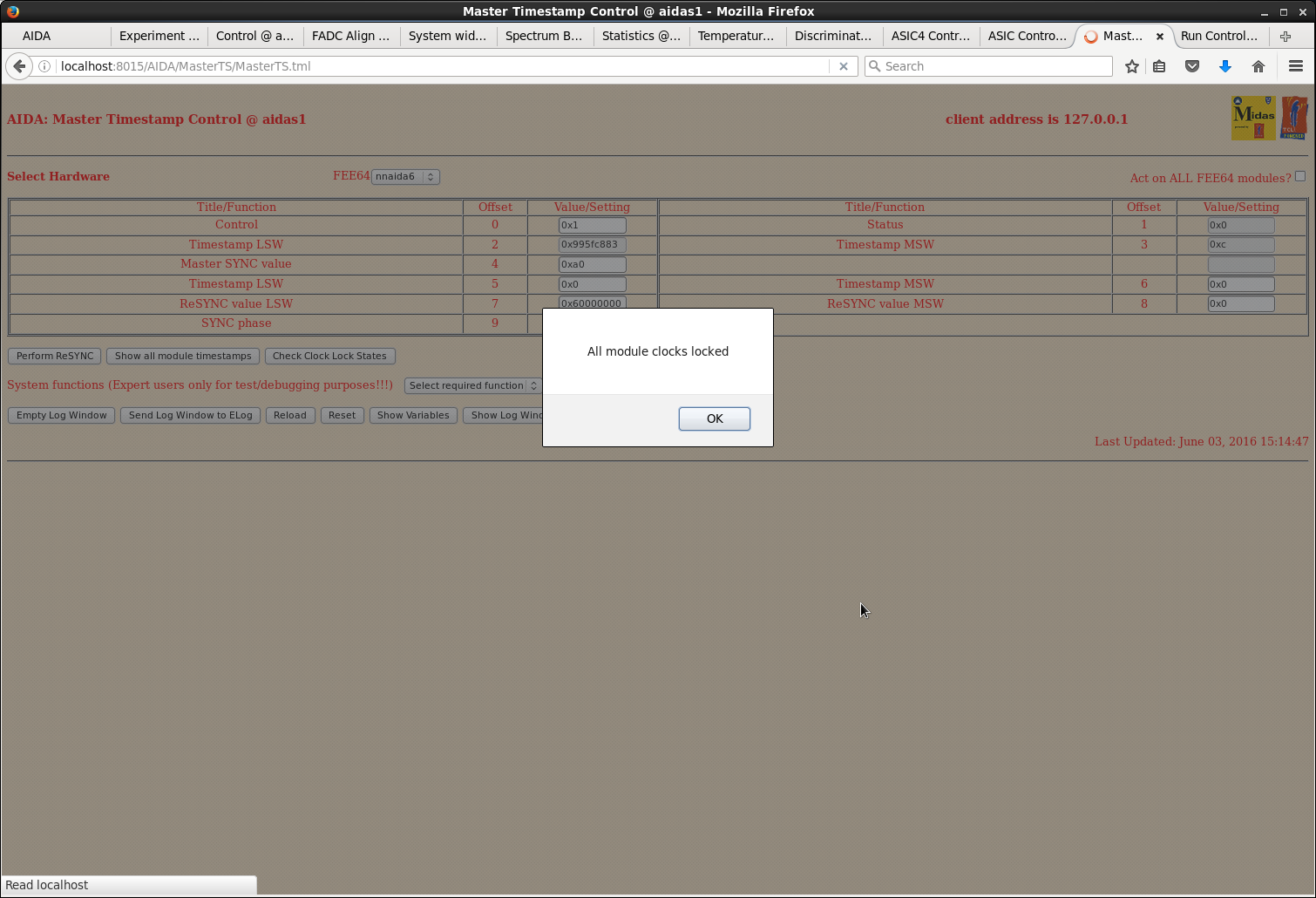

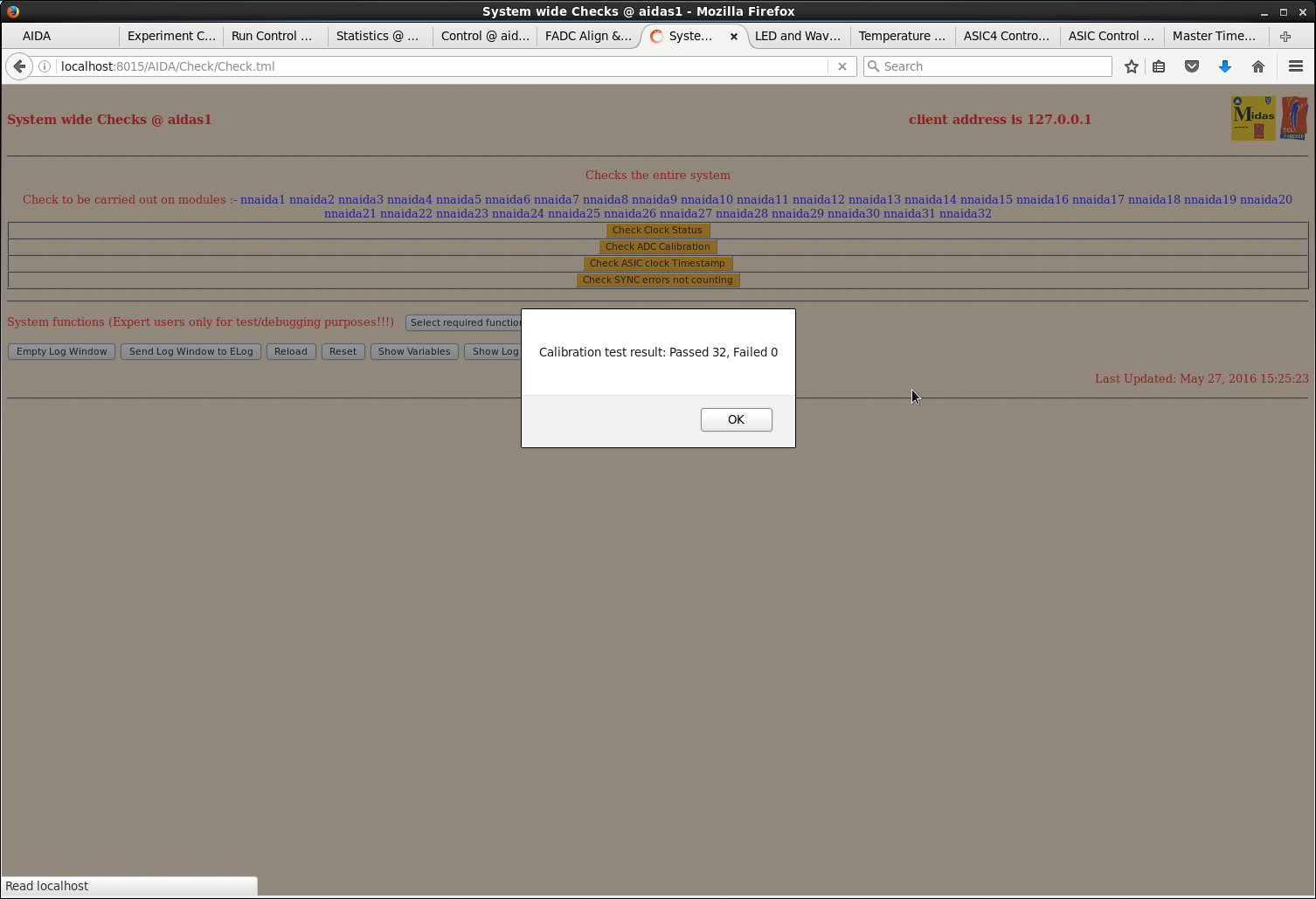

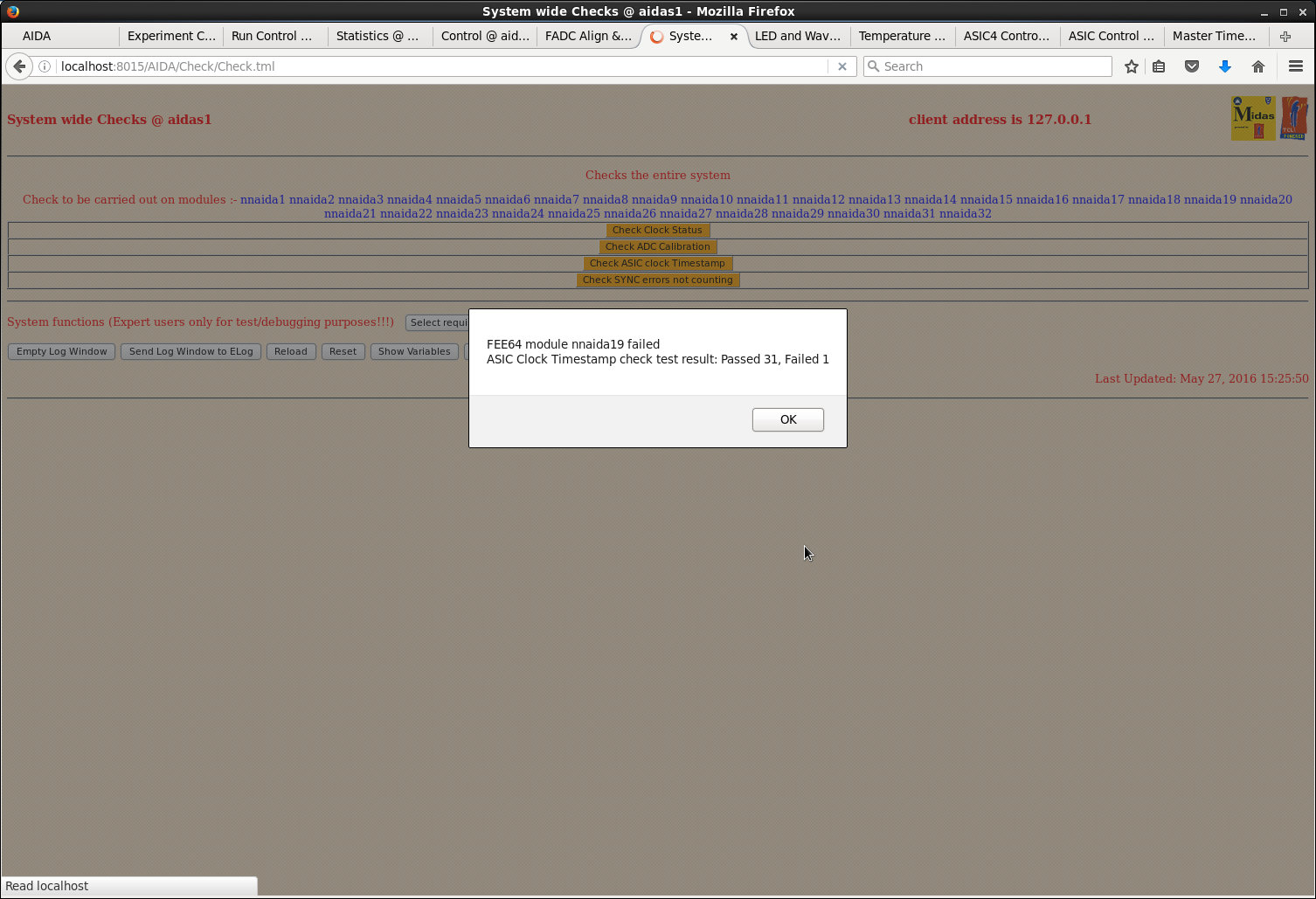

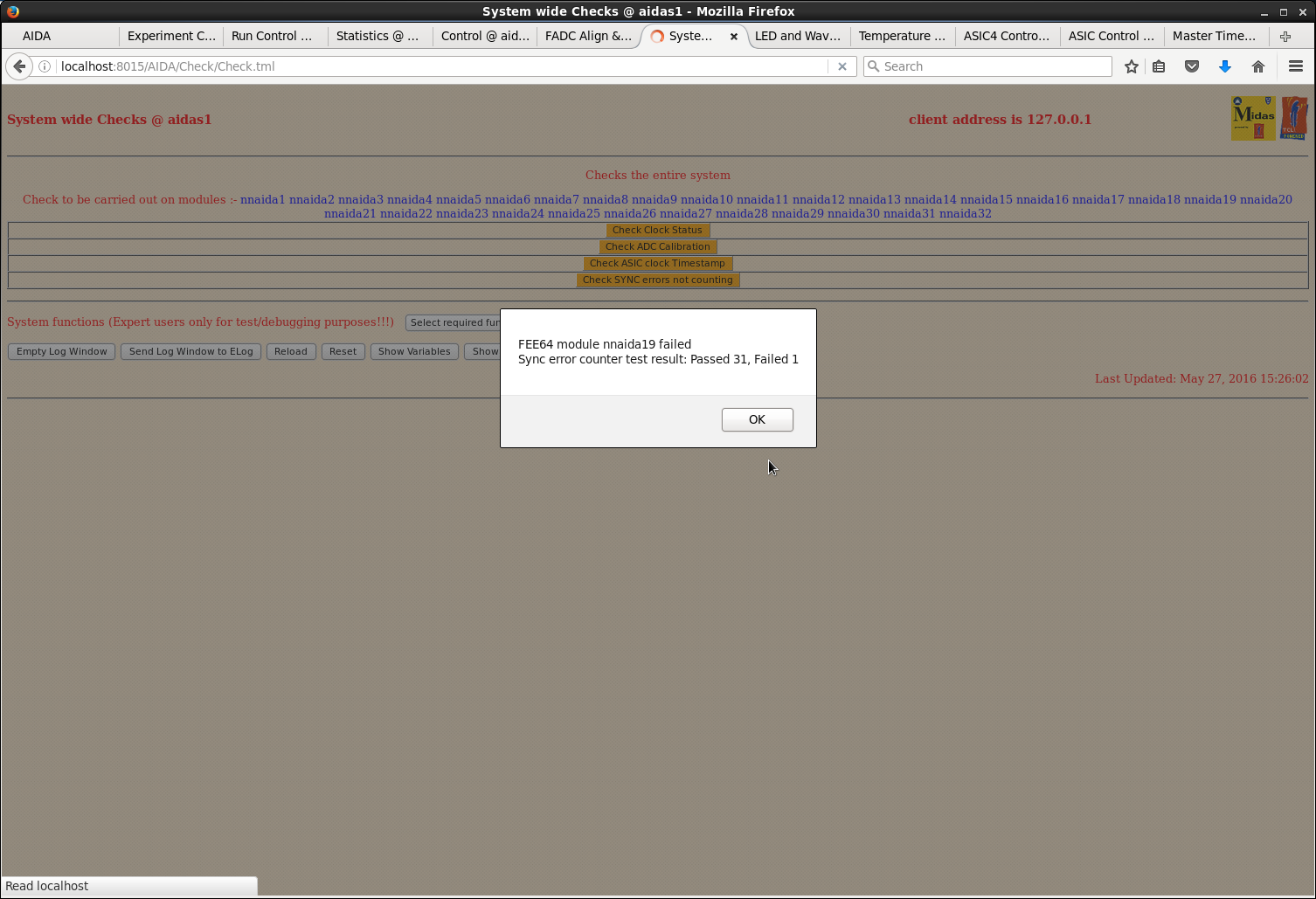

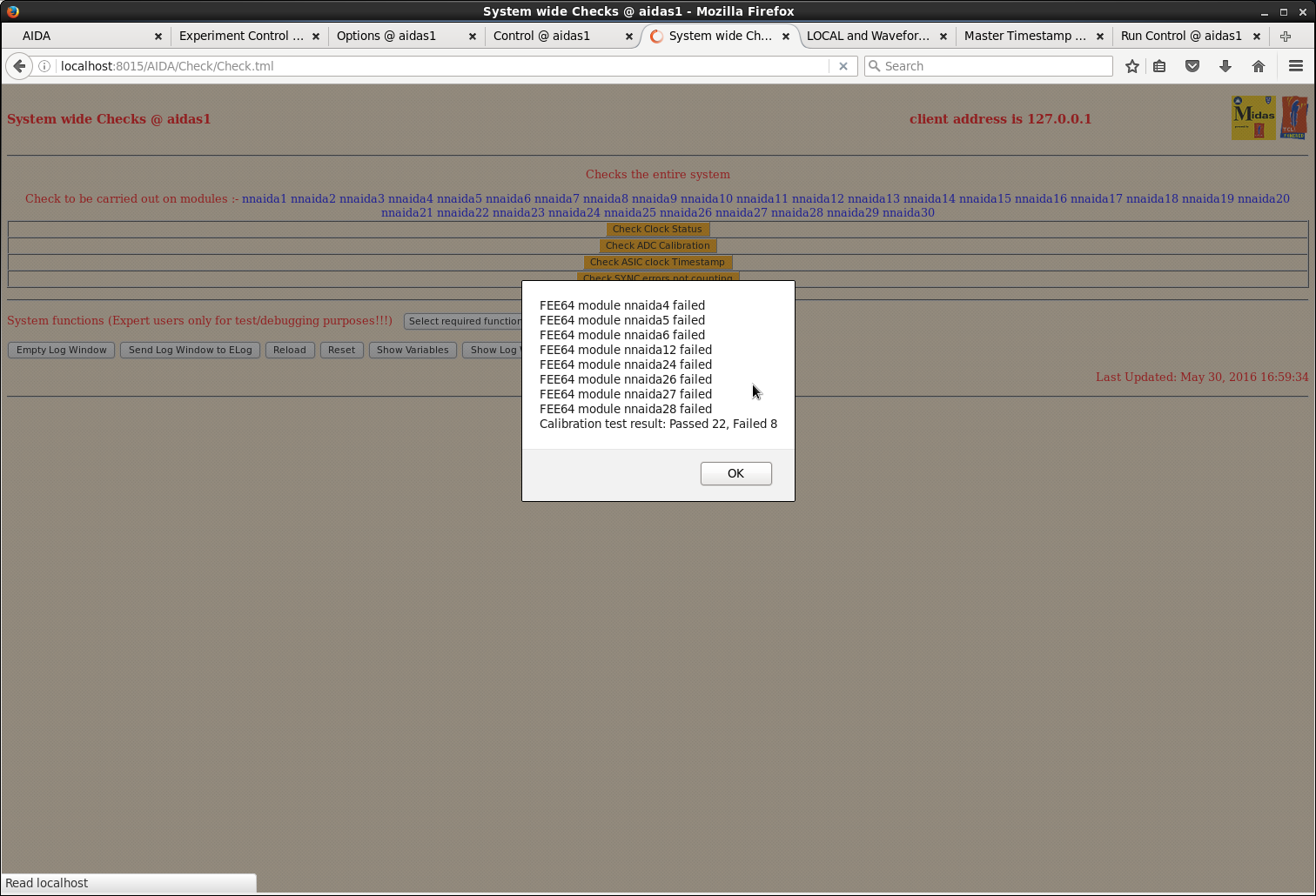

System-wide tests

clock states 24/24 pass

adc calibration 24/24 pass

ASIC clock timestamp check 23/24 pass, nnaida19 fails

SYNC errors not counting 23/24 pass, nnaida19 fails

N.B. We obtained the same nnaida19 errors before rpelacing non-rev B MACB *and* with FEE64

previously installed as nnaida19

Module timestamps - see attachment 9

Master timestamp module nnaida6 - all clocks locked

Fitted ground jumpers to front and rear field plate connections on all four adaptor PCBs

for each of DSSSD#2 - #5, i.e. DSSSD#1 - #6 now have field plate ground jumpers fitted.

See attachments 10 & 11 showing discriminator rates before and after fitting these additional

ground jumpers (LEC/MEC fast discriminator threshold 0x4 or 0x5)

18.25 NP1306 R58

207Bi + 60Co LEC/MEC disc threshold test

ASIC settings 2016Jun03-21.03.42

21.05 End R58

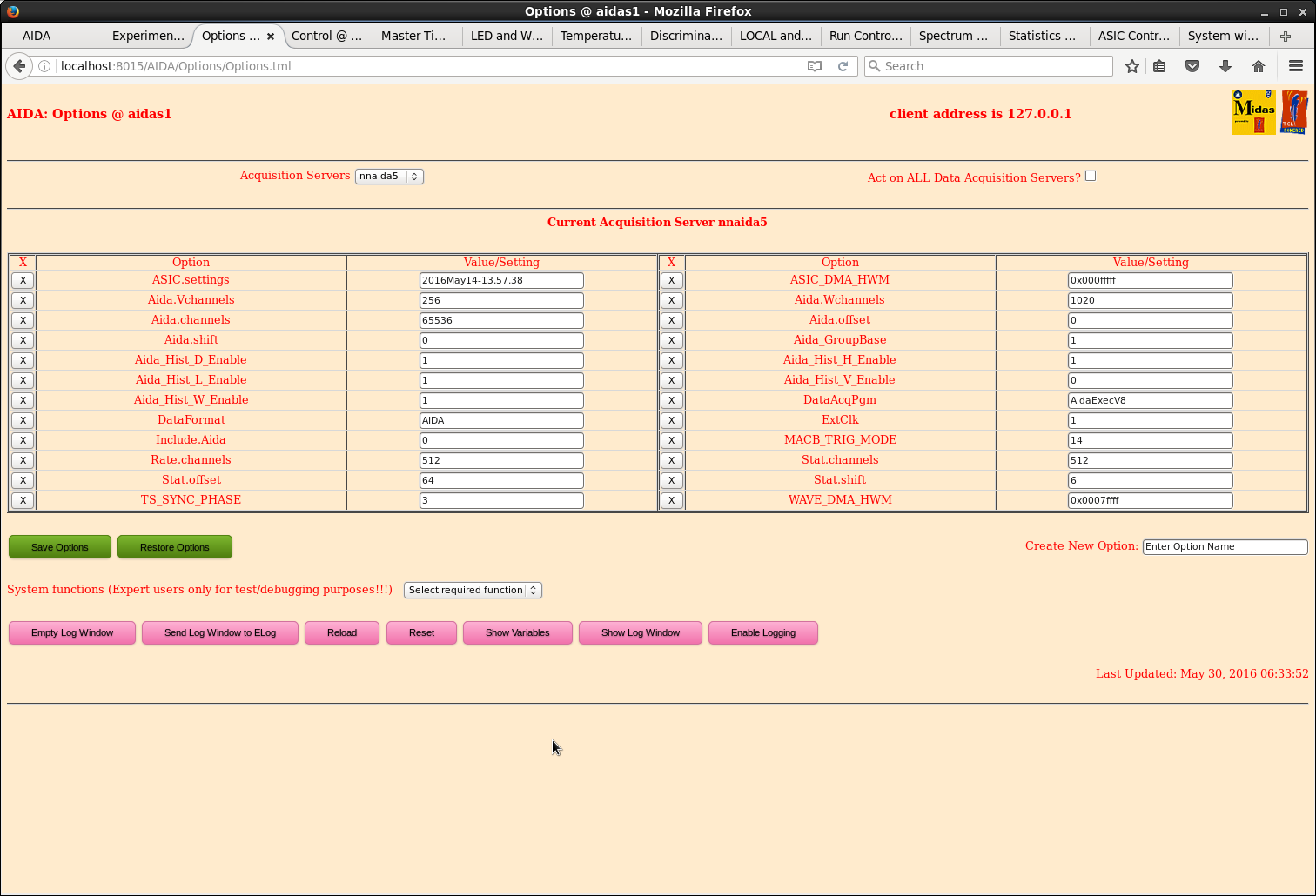

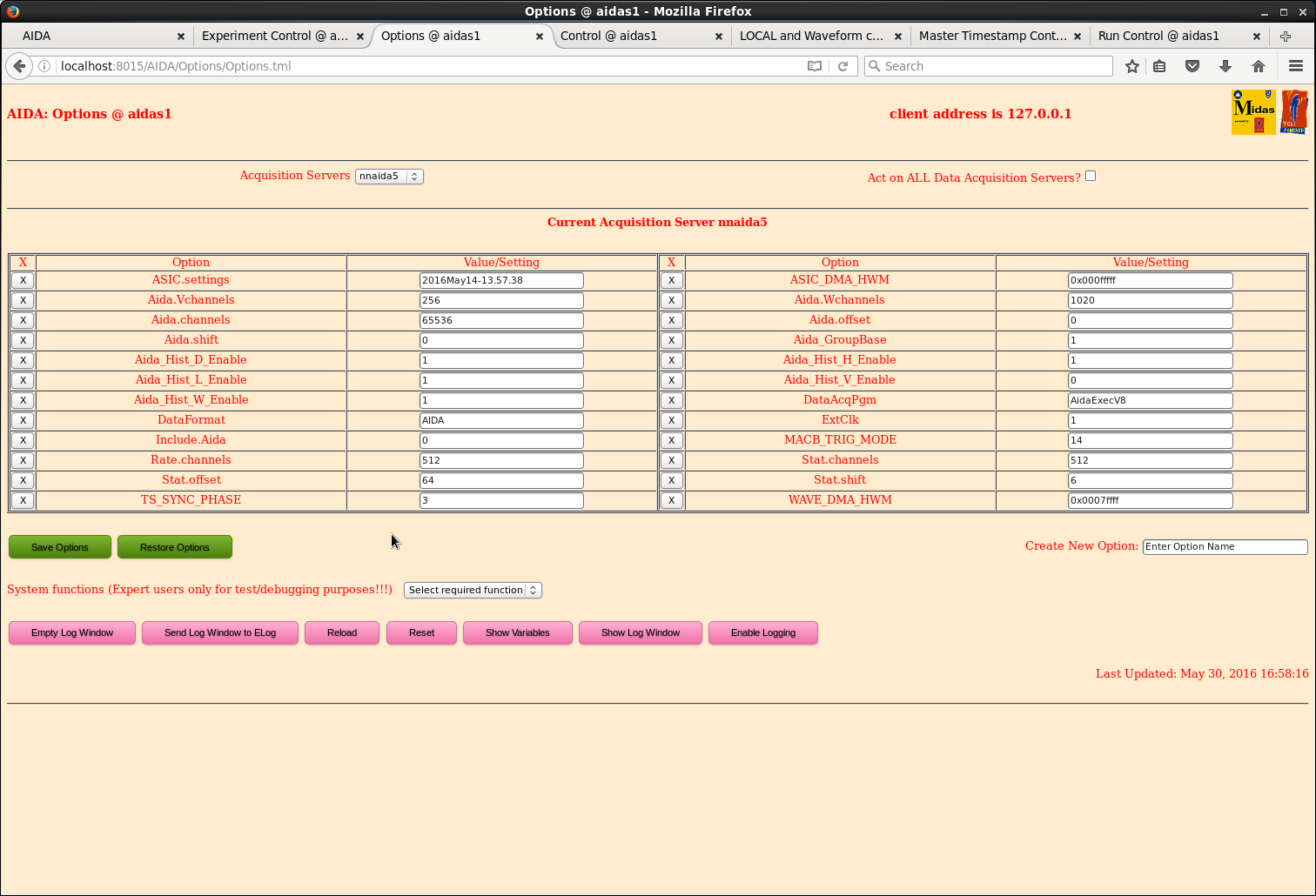

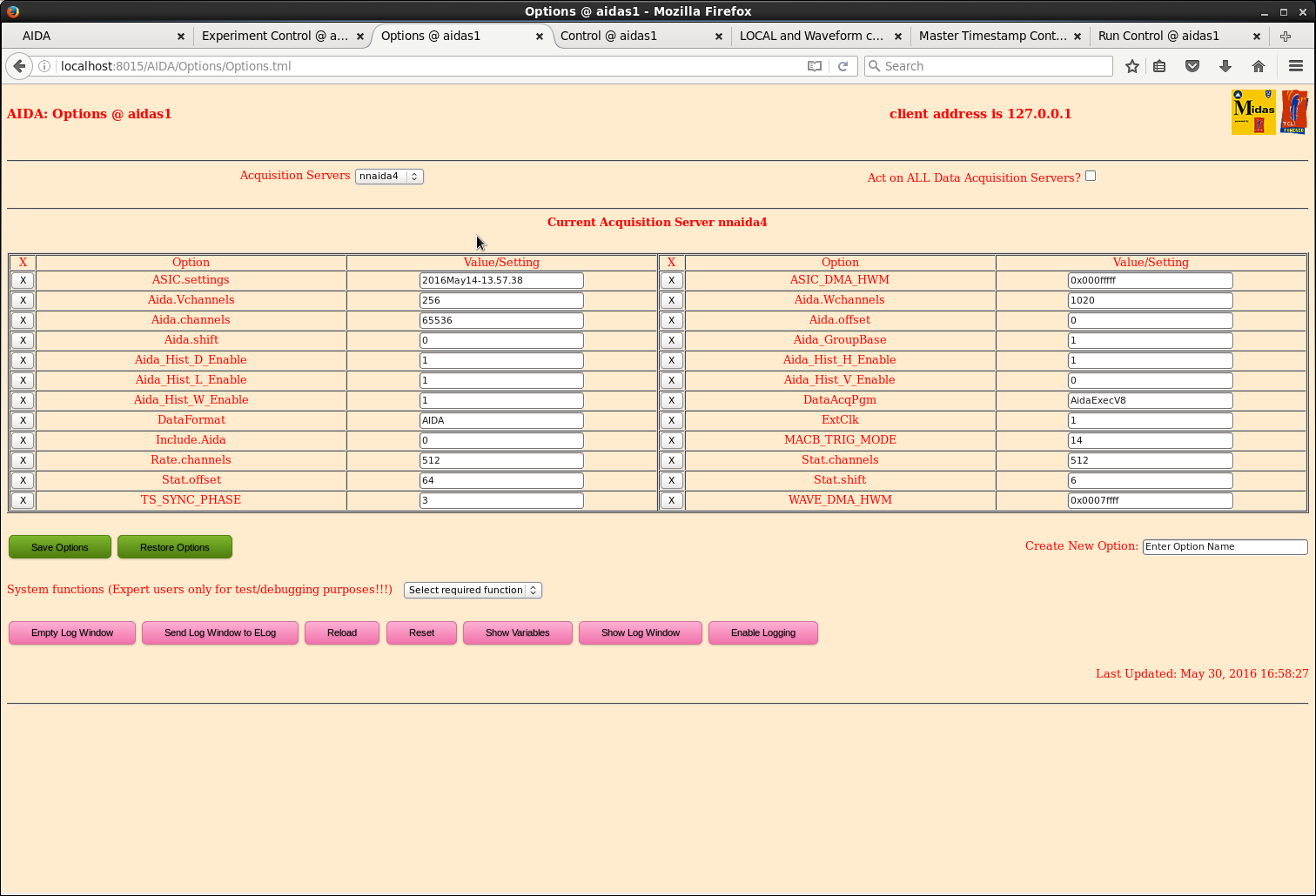

21.30 Moved extant data acquisition server options files to /MIDAS/DB/EXPERIMENT/AIDA/nnaida?/CONTENTS.BAK-030616

Saved options for all data acquisition servers with

TS_SYNC_PHASE = 0x3

MACB_TRIG_MODE = 0x4

ASIC Settings DB key 2016Jun03-21.03.42

(all LEC/MEC fast disc settings 0x5 *except* nnaida5 & nnaida6 = 0x20)

|

| Attachment 1: 1.png

|

|

| Attachment 2: 2.png

|

|

| Attachment 3: 3.png

|

|

| Attachment 4: 4.png

|

|

| Attachment 5: 5.png

|

|

| Attachment 6: 6.png

|

|

| Attachment 7: 7.png

|

|

| Attachment 8: 8.png

|

|

| Attachment 9: 10.png

|

|

| Attachment 10: 11.png

|

|

| Attachment 11: 12.png

|

|

| Attachment 12: 13.png

|

|

|

|

277

|

Sun Jun 5 02:14:10 2016 |

TD, AE, CG & DK | Sunday 5 June 2016 | 10.10 Detector biases & leakage currents - OK - see attachments 1-2

10.40 Detector biases & leakage currents - OK - see attachments 3-4

30 minutes ~2000Hz highenergy heavy ions during BigRIPS tuning

17.35 Detector biases & leakage currents - OK - see attachments 5-6

Rates DSSSD #1 - #6 ~500Hz per DSSSD

19.30 AIDA SYNCs lost

FEE64s power cycled and rebooted

22.30 Detector biases & leakage currents - OK - see attachments 7-8

Rates DSSSD #1 - #6 ~1kHz per DSSSD

23.00 2mm plate removed from fixed degrader, 1mm installed => net removal of 1mm

Variable degrader No. 2 in beam, all others out. |

| Attachment 1: 200.png

|

|

| Attachment 2: 201.png

|

|

| Attachment 3: 202.png

|

|

| Attachment 4: 203.png

|

|

| Attachment 5: 300.png

|

|

| Attachment 6: 301.png

|

|

| Attachment 7: 310.png

|

|

| Attachment 8: 311.png

|

|

|

|

248

|

Sun May 29 20:06:15 2016 |

TD, AE & CG - reply PJCS | Sunday 29 May 2016 | > Throughout day:

> DSSD2 (3058-25) would not bias, either short circuit or suspiciously low leakage current.

> Carried out some test in situ which were inconclusive.

> Removed snout and took DSSD2 out.

> Measuring the resistance across the two pins providing the n+n bias yielded 20 Ohms.

> For the p+n the same measurement saw an open circuit => at least one of the bond wires broken.

>

> DSSD1 (3131-9) was moved into the DSSD2 position and DSSD1 is now BB18-1000 3058-4.

>

> All detectors were biased downstairs and all looked fine - leakage currents of 3.1 - 3.8 uA.

>

> First detector sits 54.5cm from Al base plate and 10cm from the upstream end of the snout.

> 9mm between each of the DSSDs.

>

> Stack now:

> | 3058-4

> b | 3131-9

> e | 2998-23

> a | 3058-5

> m | 3058-6

> V 3058-7

>

> 207Bi source installed at end of snout.

>

> Snout moved upstairs and mounted.

> DSSD2 would not bias. This was due to the HV cable providing bias for this DSSD having a short to ground.

> Replaced with HV cable 7 and biased successfully.

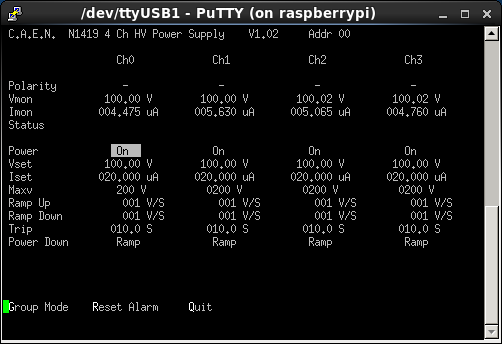

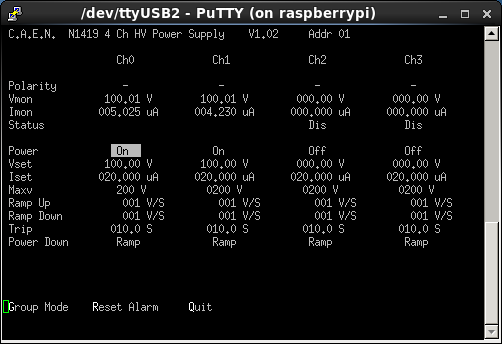

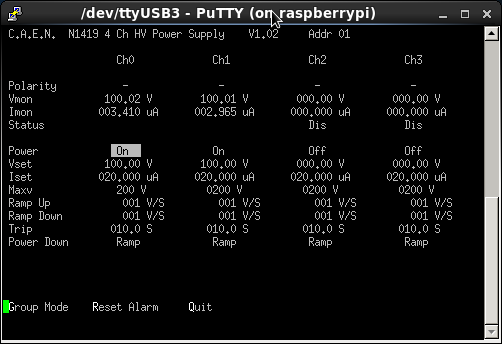

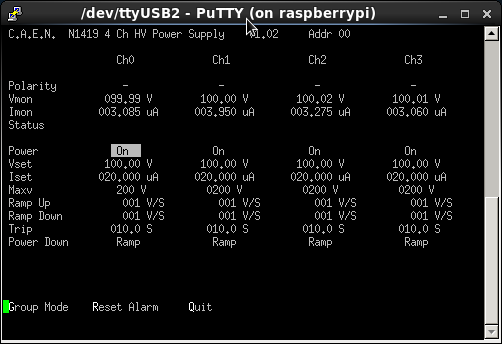

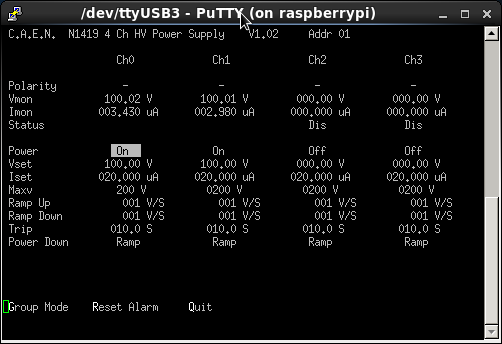

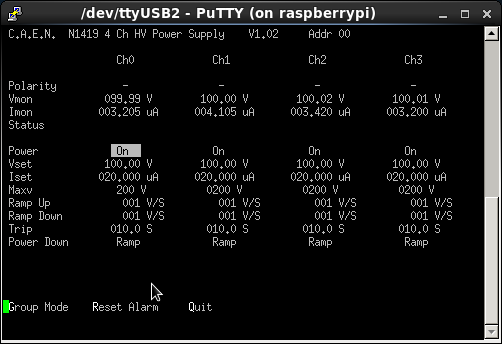

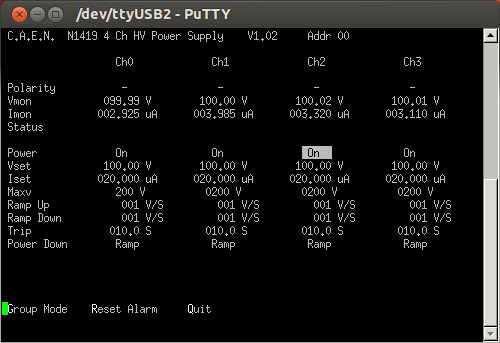

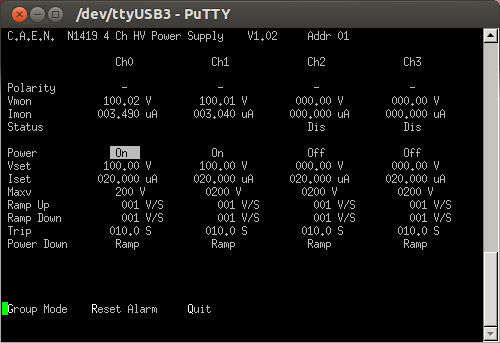

> All DSSDs now bias. Screenshots of leakage currents attached (attachments 4+5) at room temp 25.3oC.

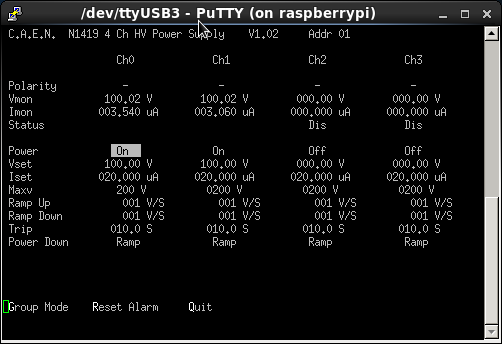

> Caen module Addr 00 provides bias to DSSDs 1, 2, 3 and 4 via channels 0, 1, 2 and 3 respectively.

> Module Addr 01 provides bias to DSSDs 5 and 6 on channels 0 and 1, respectively.

>

> Snout pushed in to EURICA.

>

> 22.05 nnaida17 ASIC parameters not loading

> power cycle & reboot

>

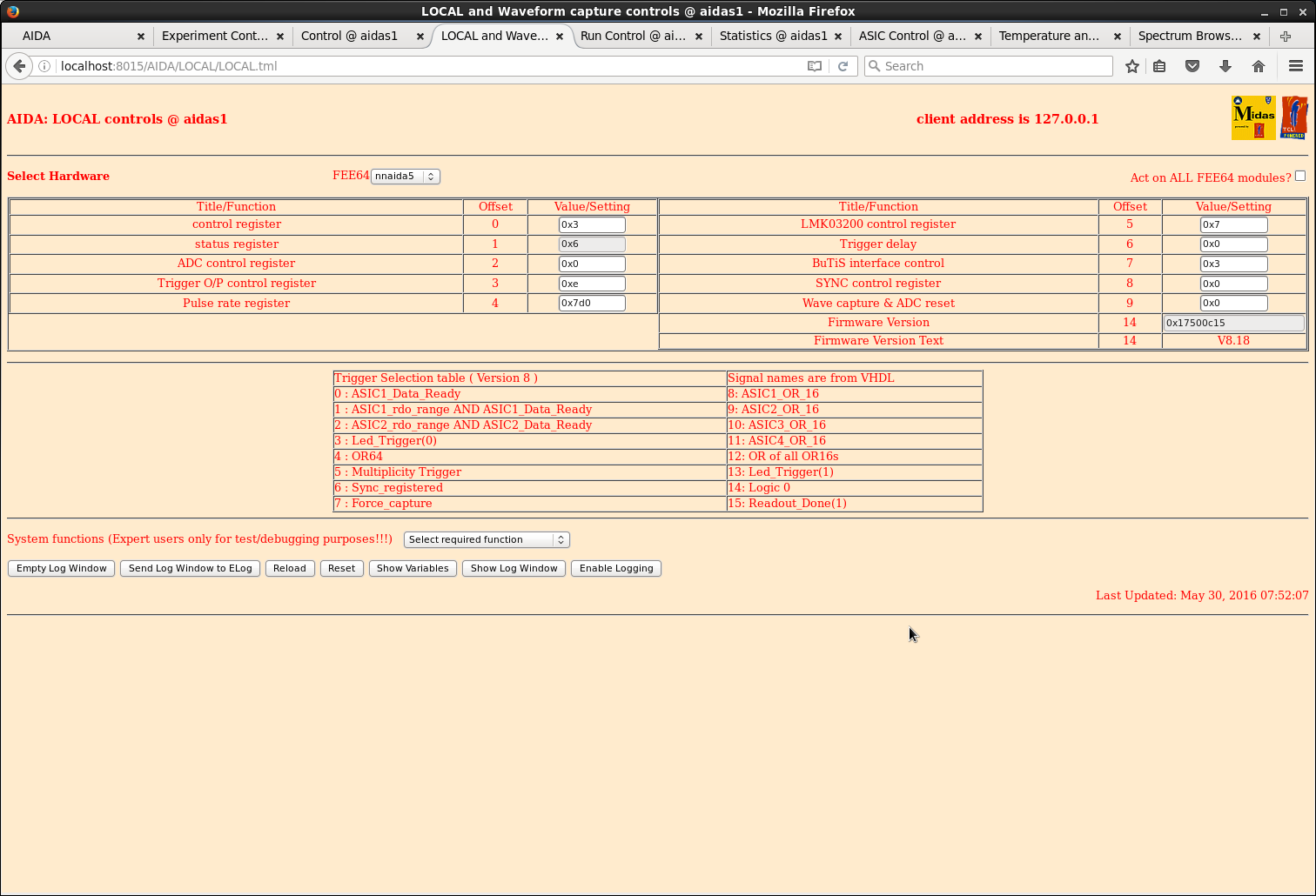

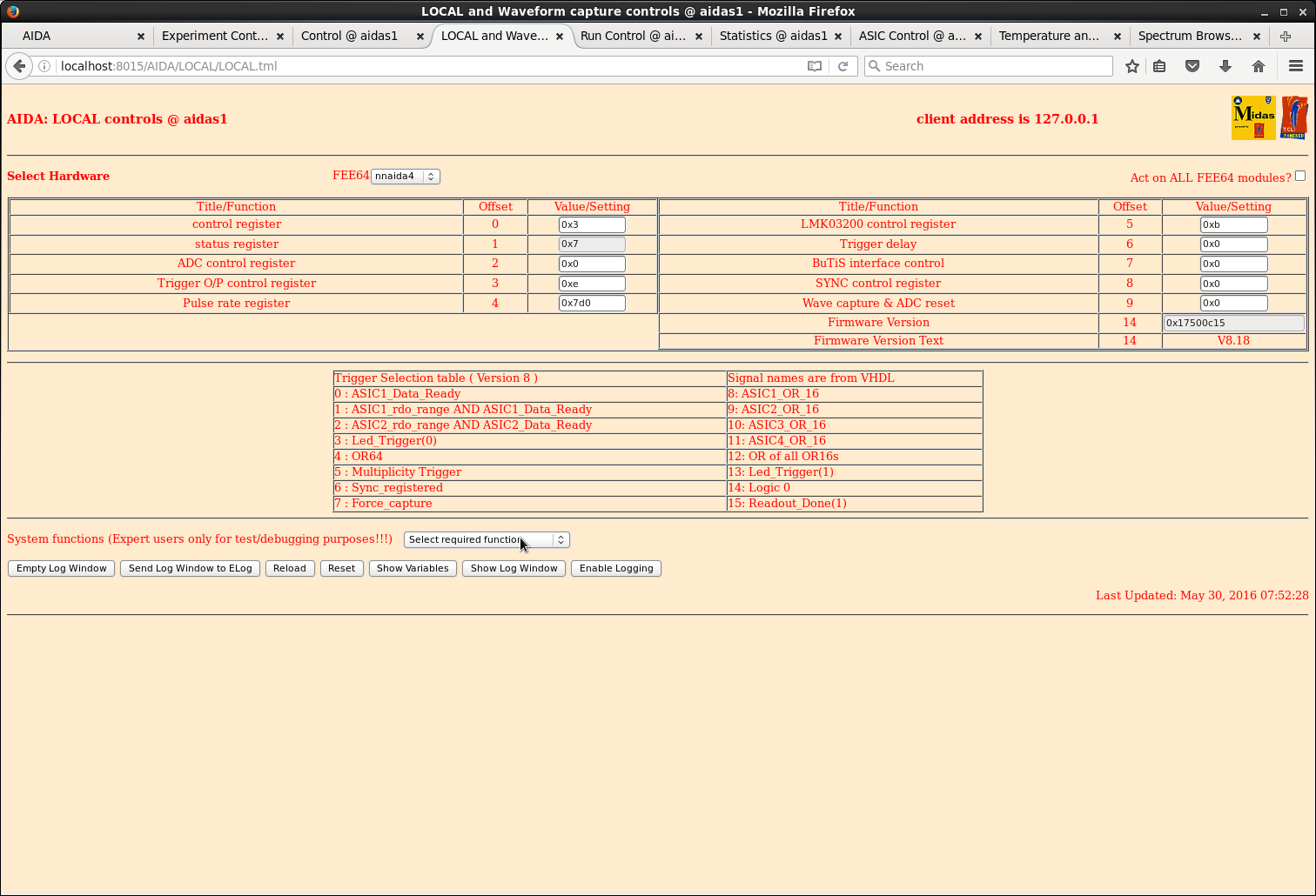

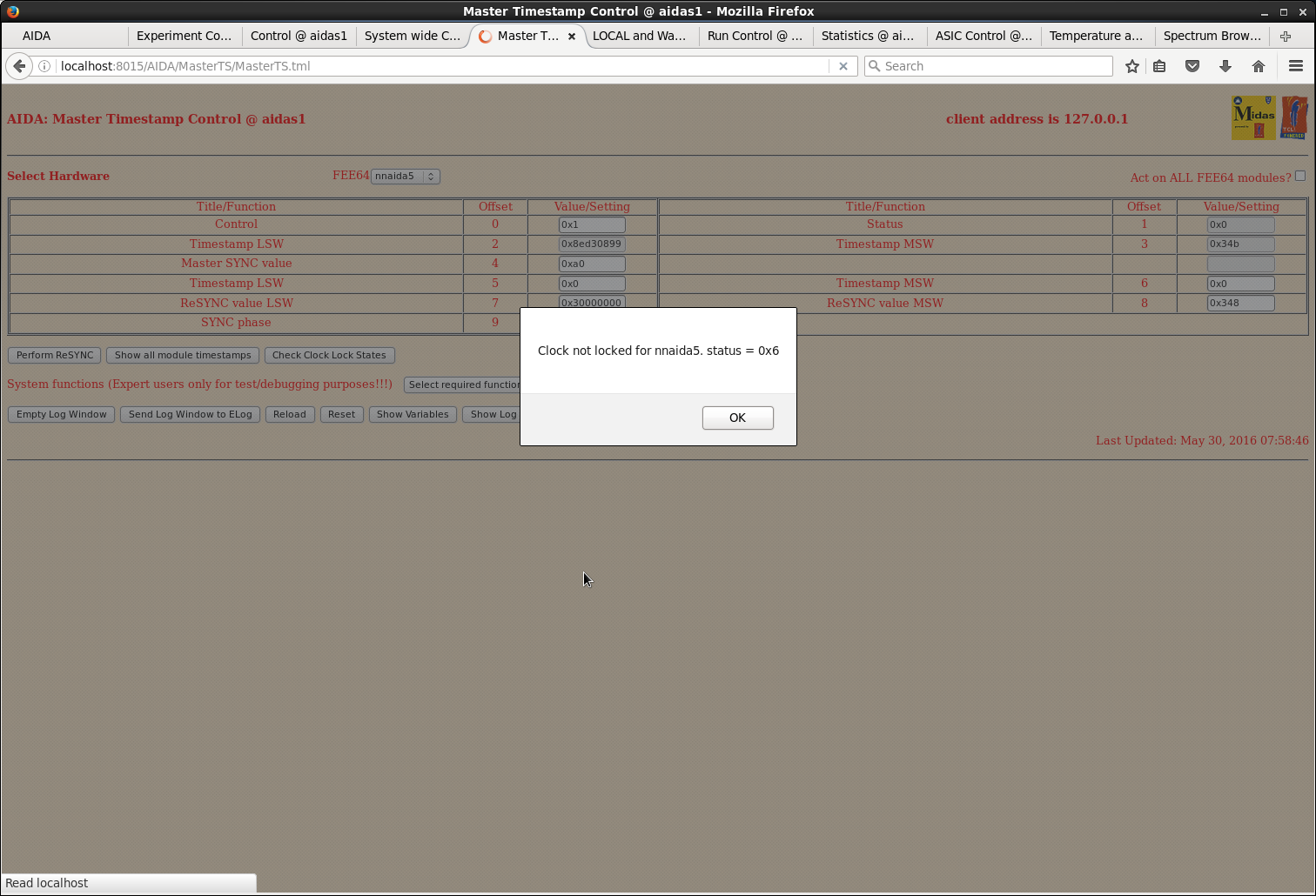

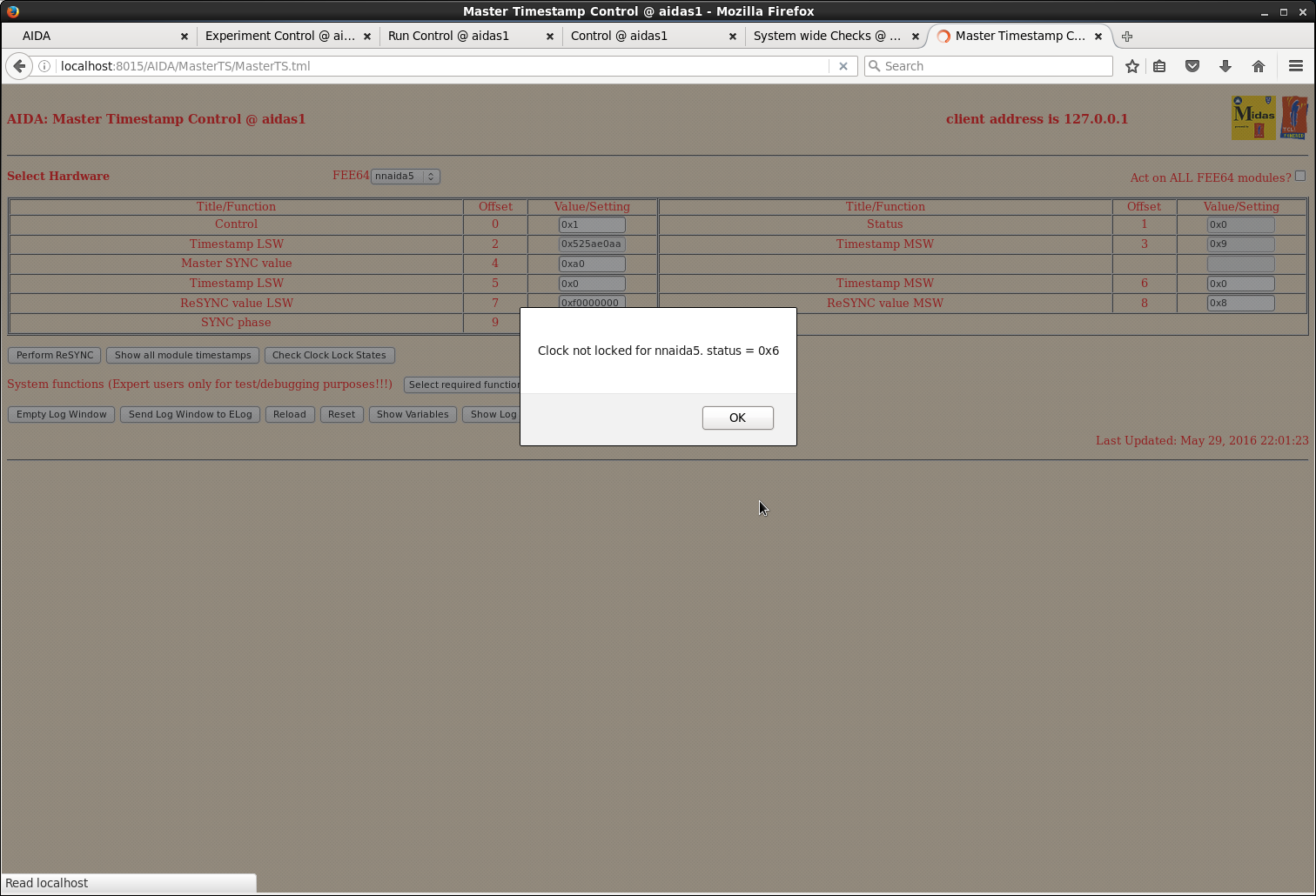

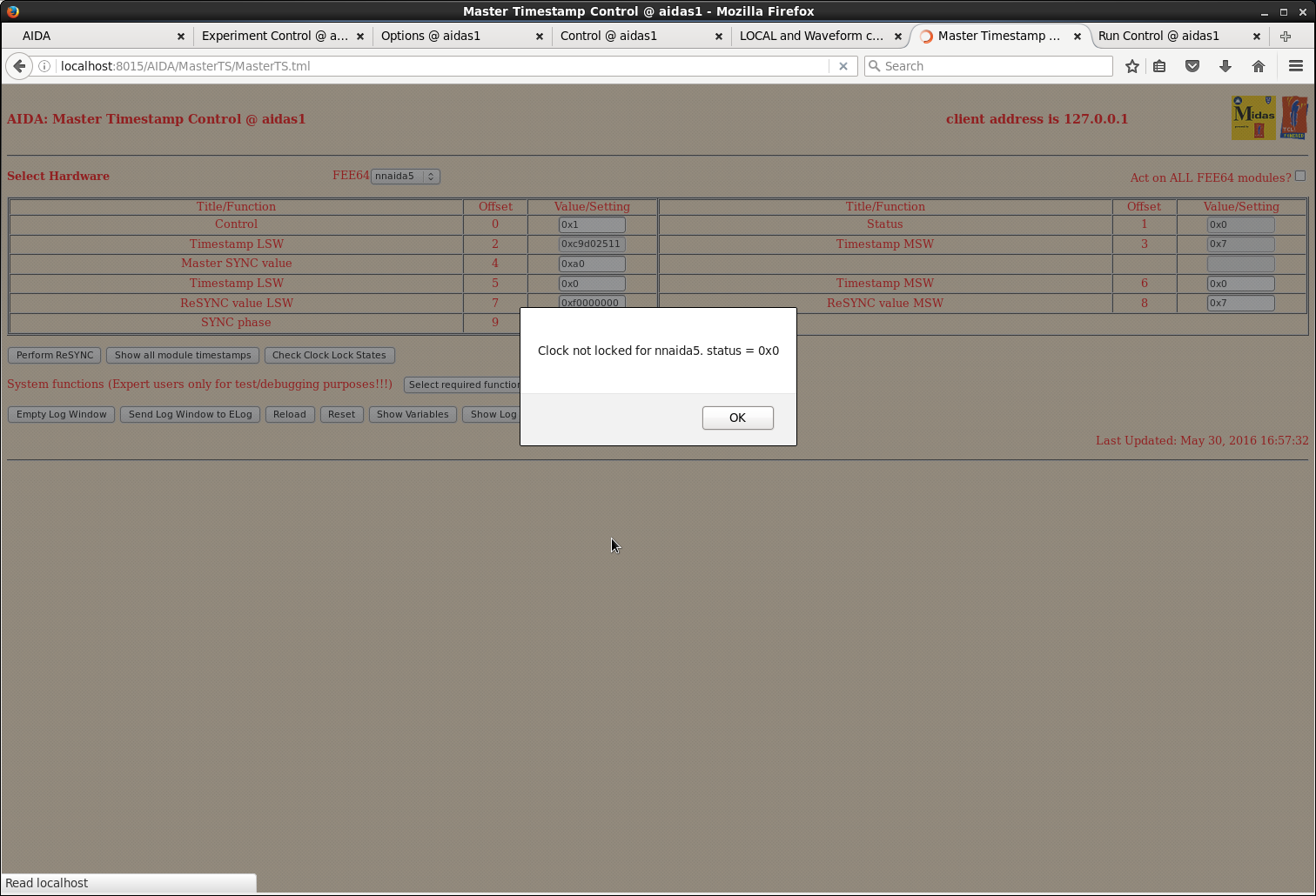

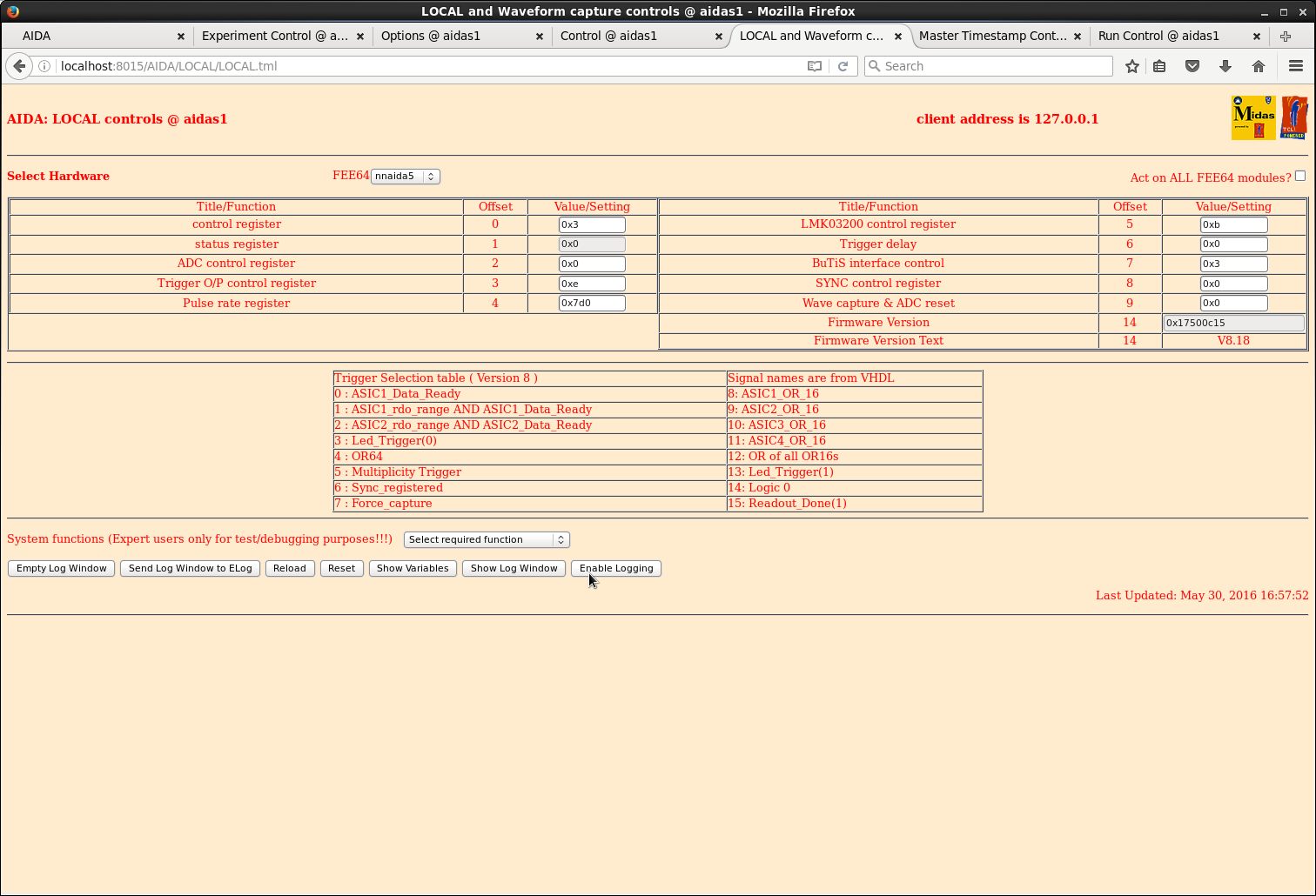

> nnaida5 (master) clock not locked - status 0x6 - see attachments 1-3

I suggest you check the hdmi hasn't been disturbed in the Macb or the FEE64.. Since the others are ok. I suggest it is the cable from the

Macb

to the FEE64 #5. If this fails to correct then please send a screen shot of the Local Controls status for nnaida5. |

|

|

249

|

Sun May 29 22:35:25 2016 |

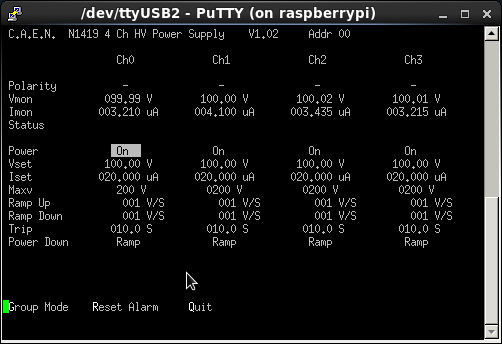

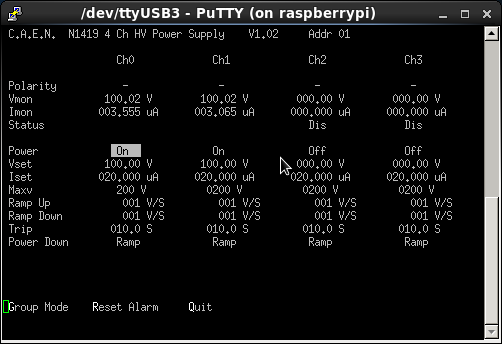

TD, AE & CG - reply PJCS | Sunday 29 May 2016 |

> > 22.05 nnaida17 ASIC parameters not loading

> > power cycle & reboot

> >

> > nnaida5 (master) clock not locked - status 0x6 - see attachments 1-3

>

> I suggest you check the hdmi hasn't been disturbed in the Macb or the FEE64.. Since the others are ok. I

suggest it is the cable from the

> Macb

> to the FEE64 #5. If this fails to correct then please send a screen shot of the Local Controls status for

nnaida5.

See enclosed. |

| Attachment 1: 70.png

|

|

| Attachment 2: 71.png

|

|

| Attachment 3: 72.png

|

|

|

|

250

|

Sun May 29 23:28:56 2016 |

TD, AE & CG - reply PJCS | Sunday 29 May 2016 | >

> > > 22.05 nnaida17 ASIC parameters not loading

> > > power cycle & reboot

> > >

> > > nnaida5 (master) clock not locked - status 0x6 - see attachments 1-3

> >

> > I suggest you check the hdmi hasn't been disturbed in the Macb or the FEE64.. Since the others are ok. I

> suggest it is the cable from the

> > Macb

> > to the FEE64 #5. If this fails to correct then please send a screen shot of the Local Controls status for

> nnaida5.

>

> See enclosed.

The LMK3200 control register looks wrong.

Look at another FEE and I think it should be 0x1b |

|

|

251

|

Sun May 29 23:55:15 2016 |

TD, AE & CG - reply PJCS | Sunday 29 May 2016 | > >

> > > > 22.05 nnaida17 ASIC parameters not loading

> > > > power cycle & reboot

> > > >

> > > > nnaida5 (master) clock not locked - status 0x6 - see attachments 1-3

> > >

> > > I suggest you check the hdmi hasn't been disturbed in the Macb or the FEE64.. Since the others are ok. I

> > suggest it is the cable from the

> > > Macb

> > > to the FEE64 #5. If this fails to correct then please send a screen shot of the Local Controls status for

> > nnaida5.

> >

> > See enclosed.

>

> The LMK3200 control register looks wrong.

> Look at another FEE and I think it should be 0x1b

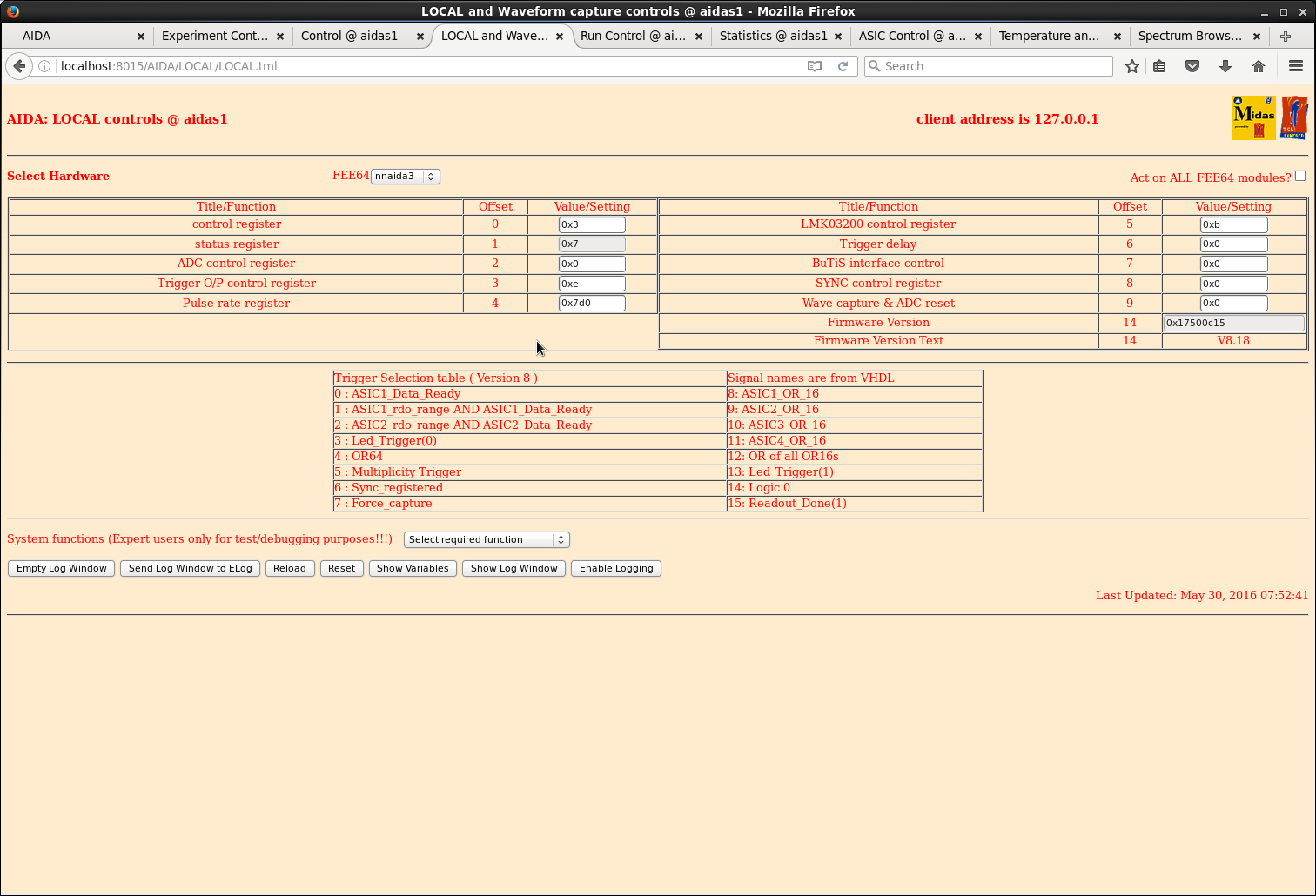

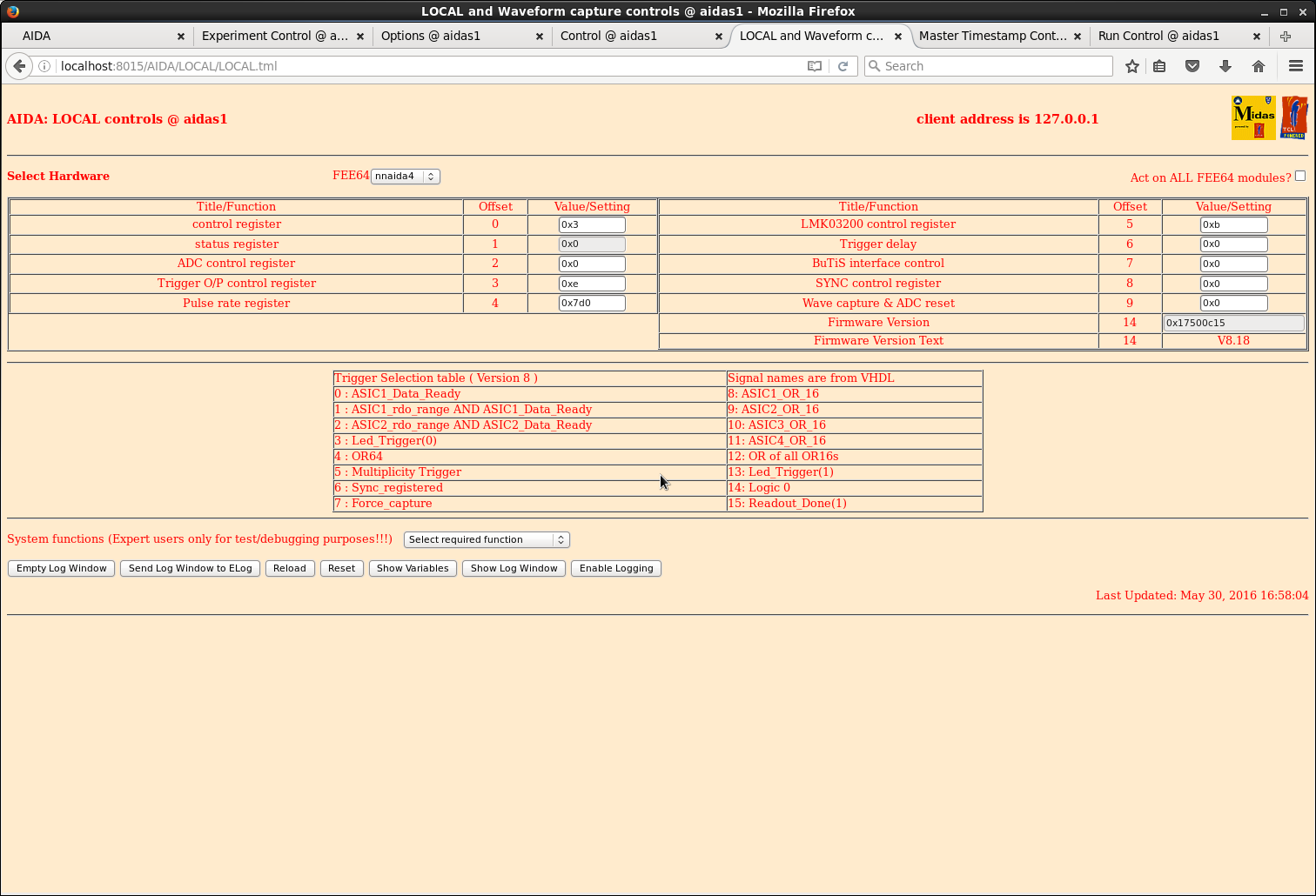

nnaida1-4 LMK03200 control register 0xb cf. nnaida5 0x7 |

| Attachment 1: 80.png

|

|

| Attachment 2: 81.png

|

|

| Attachment 3: 82.png

|

|

| Attachment 4: 83.png

|

|

| Attachment 5: 84.png

|

|

|

|

252

|

Mon May 30 00:01:23 2016 |

TD, AE & CG - reply PJCS | Sunday 29 May 2016 | > > >

> > > > > 22.05 nnaida17 ASIC parameters not loading

> > > > > power cycle & reboot

> > > > >

> > > > > nnaida5 (master) clock not locked - status 0x6 - see attachments 1-3

> > > >

> > > > I suggest you check the hdmi hasn't been disturbed in the Macb or the FEE64.. Since the others are ok. I

> > > suggest it is the cable from the

> > > > Macb

> > > > to the FEE64 #5. If this fails to correct then please send a screen shot of the Local Controls status for

> > > nnaida5.

> > >

> > > See enclosed.

> >

> > The LMK3200 control register looks wrong.

> > Look at another FEE and I think it should be 0x1b

>

> nnaida1-4 LMK03200 control register 0xb cf. nnaida5 0x7

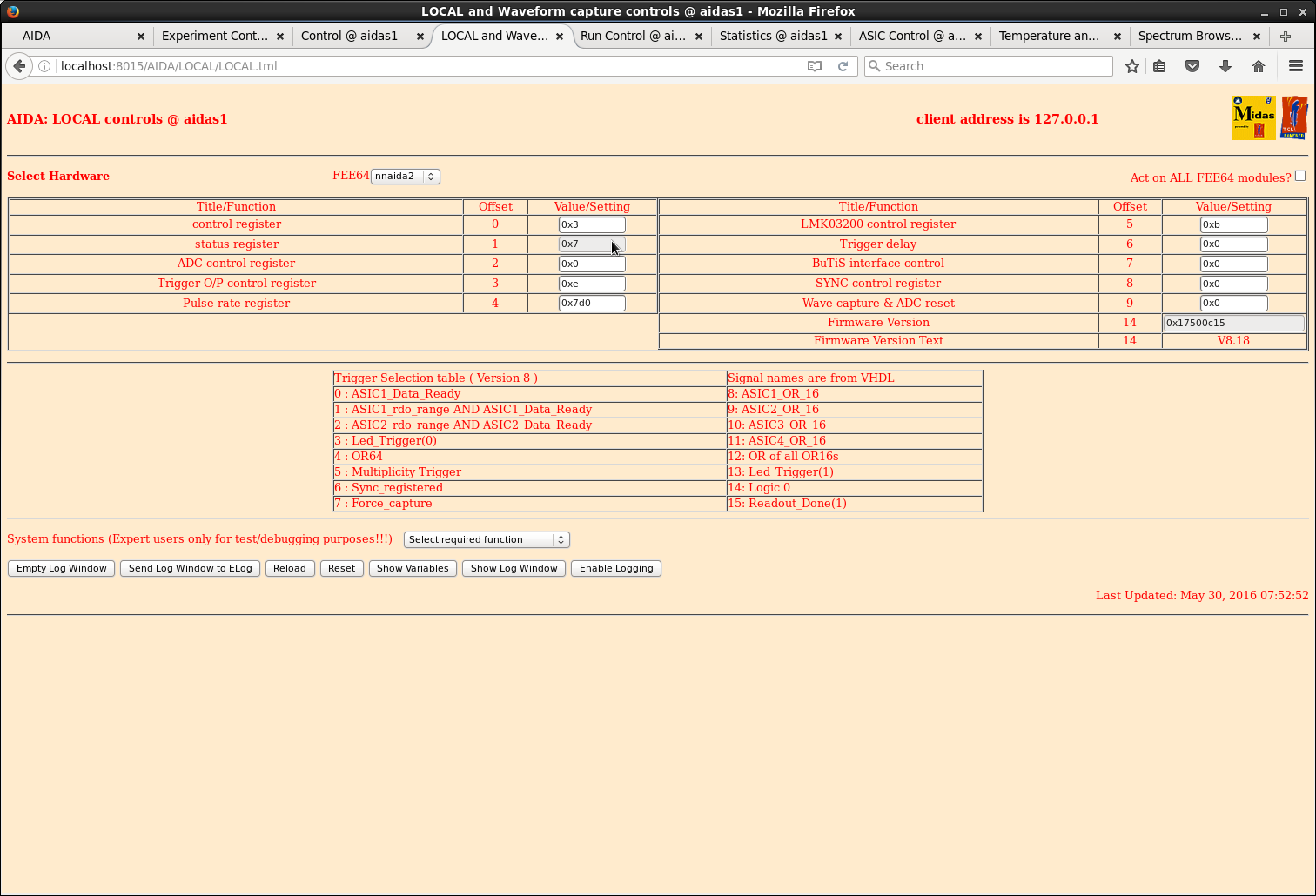

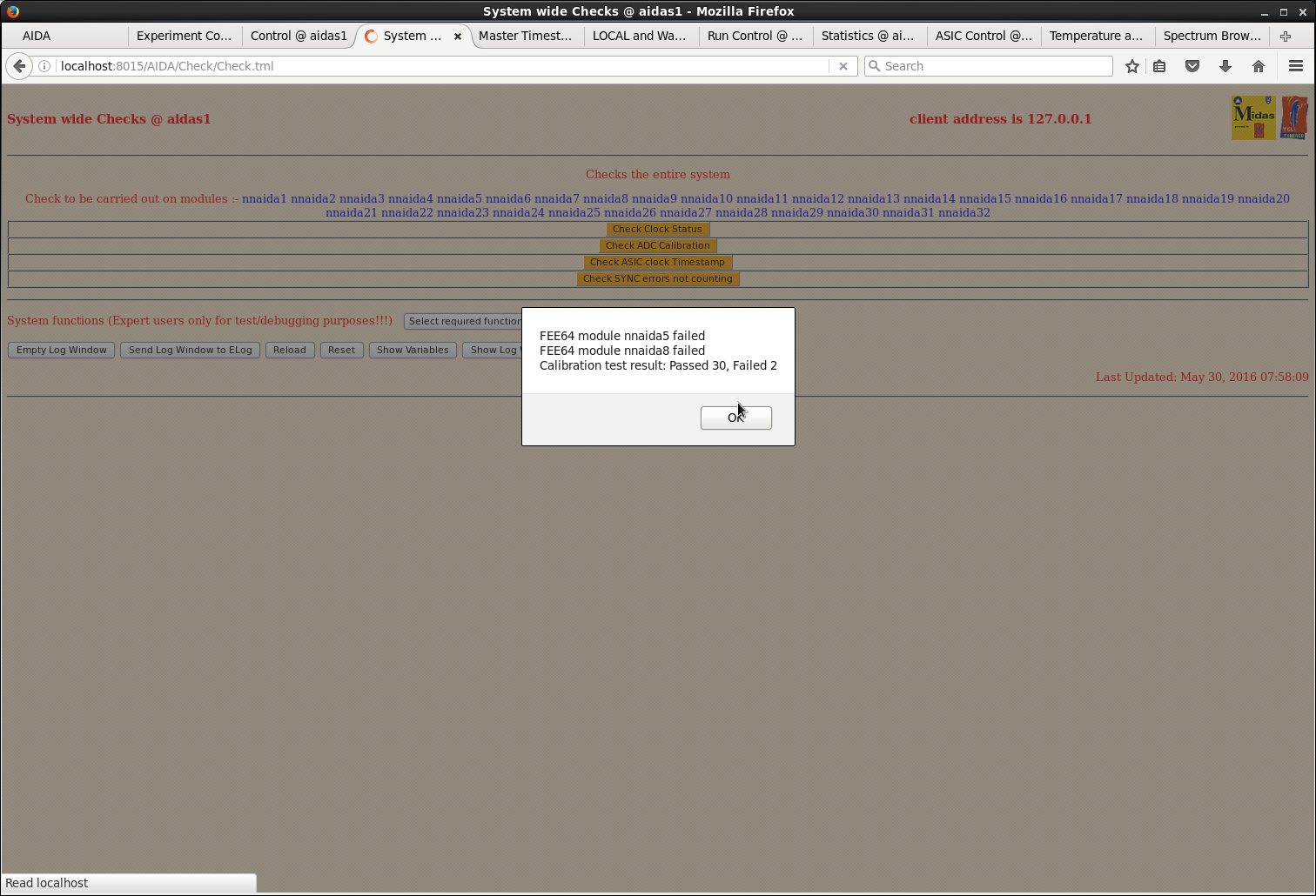

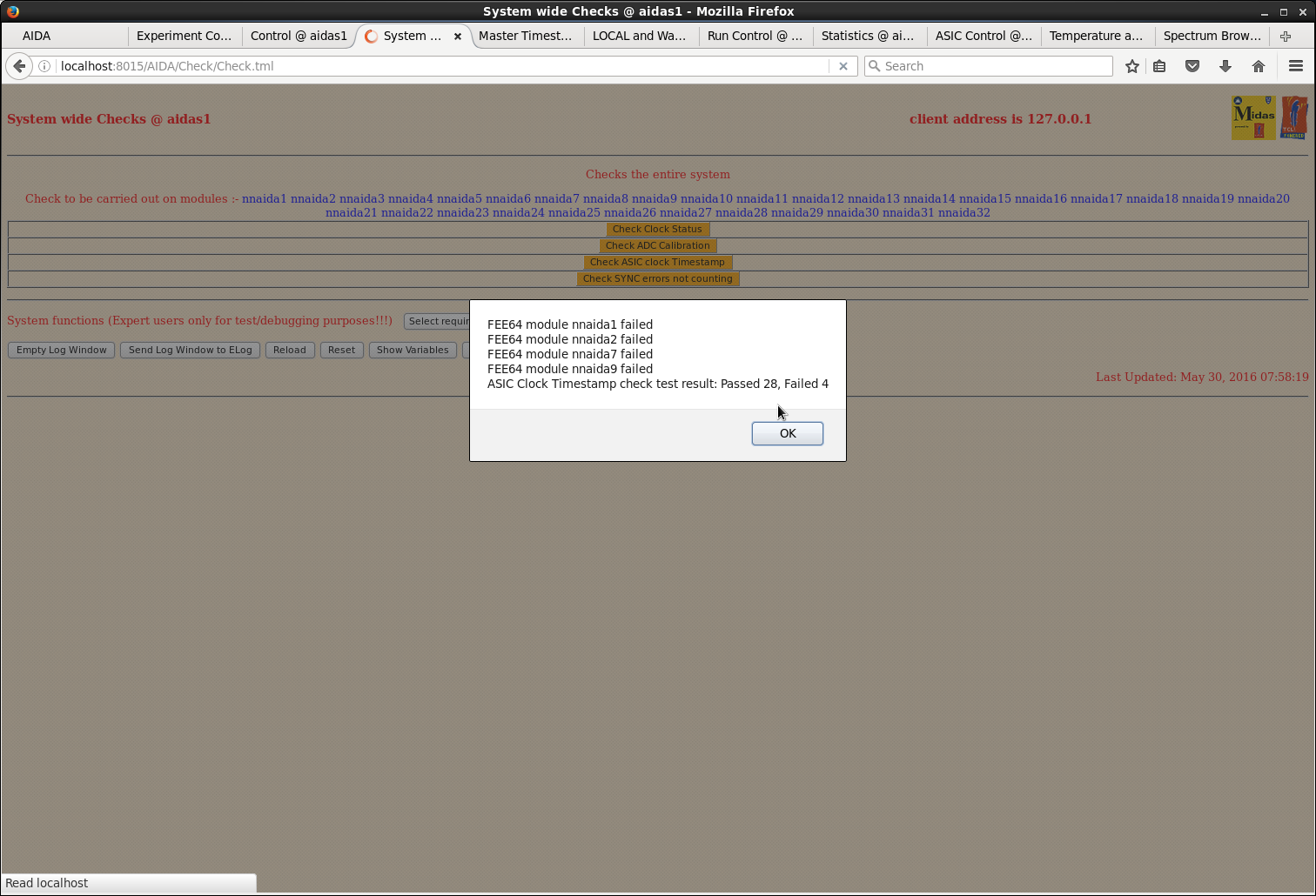

Changing nnaida5 LMK03200 control register 0x7 -> 0xb does not help - see attached - system wide checks

and clock lock status 0x6 (unchanged) |

| Attachment 1: 90.png

|

|

| Attachment 2: 91.png

|

|

| Attachment 3: 92.png

|

|

| Attachment 4: 93.png

|

|

| Attachment 5: 94.png

|

|

|

|

253

|

Mon May 30 00:07:56 2016 |

TD, AE & CG - reply PJCS | Sunday 29 May 2016 | > > > >

> > > > > > 22.05 nnaida17 ASIC parameters not loading

> > > > > > power cycle & reboot

> > > > > >

> > > > > > nnaida5 (master) clock not locked - status 0x6 - see attachments 1-3

> > > > >

> > > > > I suggest you check the hdmi hasn't been disturbed in the Macb or the FEE64.. Since the others are ok. I

> > > > suggest it is the cable from the

> > > > > Macb

> > > > > to the FEE64 #5. If this fails to correct then please send a screen shot of the Local Controls status for

> > > > nnaida5.

> > > >

> > > > See enclosed.

> > >

> > > The LMK3200 control register looks wrong.

> > > Look at another FEE and I think it should be 0x1b

> >

> > nnaida1-4 LMK03200 control register 0xb cf. nnaida5 0x7

>

> Changing nnaida5 LMK03200 control register 0x7 -> 0xb does not help - see attached - system wide checks

> and clock lock status 0x6 (unchanged)

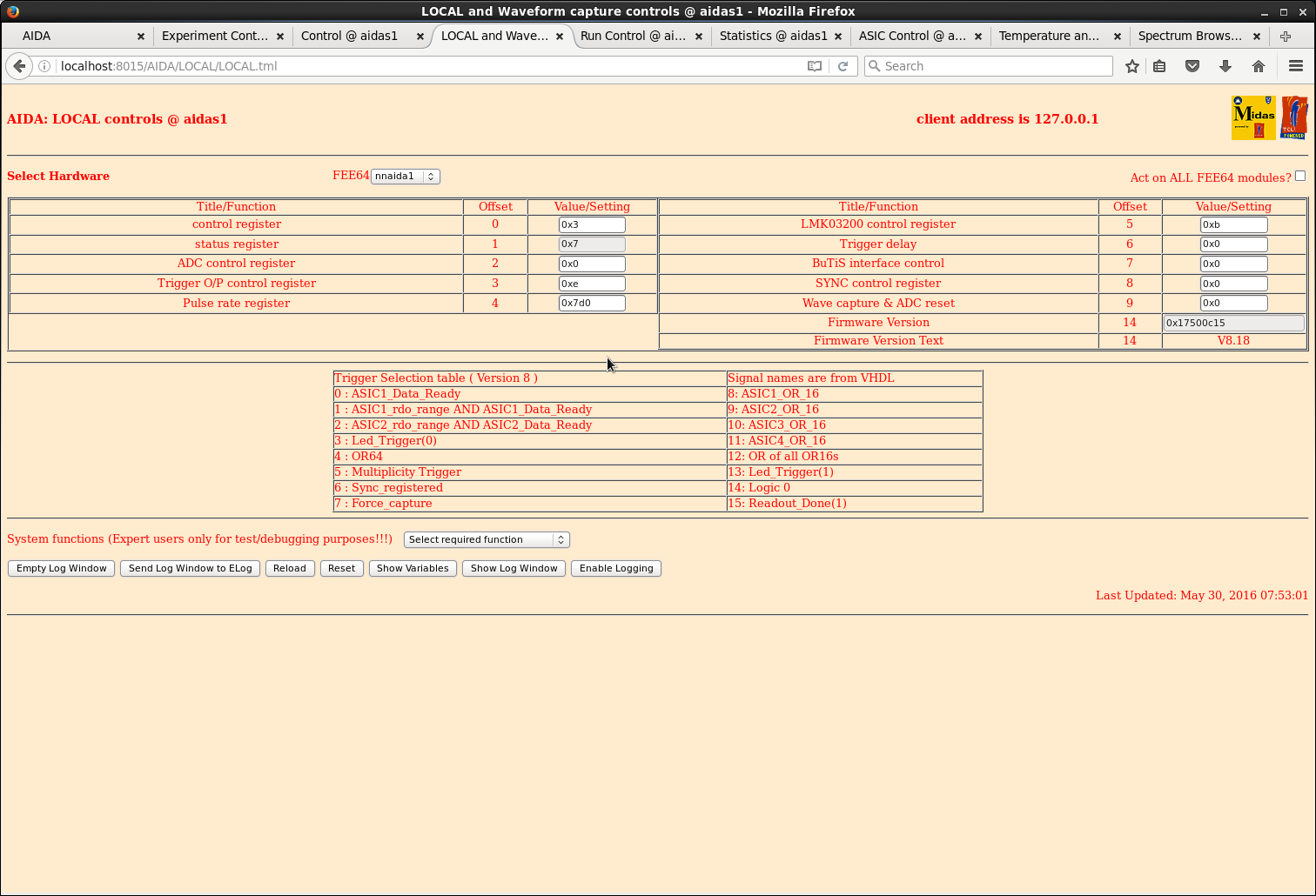

Changing nnaida5 LMK03200 control register 0x7 -> 0x1b does not help - nnaida5 fails 'check clock status'

and check clock lock *not* locked status *0x0* |

|

|

45

|

Mon Feb 23 07:03:10 2015 |

TD, AE & CG | Monday 23 February 2015 | 14.30 Saved nnaida1-16 ASIC + Waveform configurations to directory (Data Base Key)

2015Feb23-12.11.40

(directory aidas1:/MIDAS/DB/EXPERIMENTS/AIDA/2015Feb23-12.11.40)

nnaida 1-2, 5-6, 9-10, 13-14 positive input ( front p+n junction strips )

nnaida 3-4, 7-8, 11-12, 15-16 negative input ( back n+n ohmic strips )

Standard ASIC configurations except

- shaping time 0xb (6,5us)

- peaking time 0x8 (16us)

- slow comparator 0x10 (~160keV)

- fast comparator (LEC/MEC) 0xff

- fast comparator (HEC) 0xff

nnaida 1-2, 5-6, 9-10, 13-14 negative input ( AIDA ASIC preamp output inverts input,

i.e. preamp with positive input produces negative input for sampling ADC )

nnaida 3-4, 7-8, 11-12, 15-16 positive input

Standard Waveform configurations except

- threshold 1000

- pre-trigger 0x100

- all channels disabled

2015Feb23-12.11.40 is now the default configuration file

Note: The directory (Data Base Key) which will contain the saved settings is created uid: npg, gid: npgstaff, perms 755.

However, its contents are written uid: nfsnobody, gid nfsnobody, perms 777. The default directory (Data Base Key) permissions

do not work - it is necessary to change the directory (Data Base Key) to perms 777 after its creation and before saving the

individual FEE64 configuration directories/files to it.

|

|

|

238

|

Thu May 26 03:46:41 2016 |

TD, AE & CG | Thursday 26 May 2016 | 11.45 AIDA discriminator rates - see attachment 1

Today's rates similar to yesterday's rates

14.00 Commence positioning of AIDA. Adjust stand height using laser scanner and aligned to wall

references. Determine that the most forward position AIDA DSSSD#1 is ~3cm downstream of

EURICA centre. Need to move DSSSDs ~6cm upstream and lengthen DSSSD - AIDA adpptor PCB

cabling. In progress.

20.50 Update /etc/dhcp/dhcpd.conf

nnaida19 is faulty, nnaida28 is not used - see https://elog.ph.ed.ac.uk/AIDA/193

We have swapped FEE modules for nnaida19/20 for nnaida27/28 such that nnaida19 -> 28, nnaida20 -> 27,

nnaida27 -> 19, nnaida28 -> 20.

The power cables for nnaida19 and nnaida28 have also been swapped - the power cable to nnaida19

*might* be faulty as we have experienced problems at this crate position before. Also swapped

AIDA FEE PSU outlets to ensure pairs of FEE64 cards are powered from the same PSU outlet.

[root@aidas1 dhcp]# diff dhcpd.conf dhcpd.conf.BAK-260516

205,206c205,206

< host nnaida19 {

< hardware ethernet 00:04:a3:2a:ed:9a;

---

> host nnaida19 {

> hardware ethernet 00:04:a3:2b:09:e7;

210,211c210,211

< host nnaida20 {

< hardware ethernet 00:04:a3:2b:11:c5;

---

> host nnaida20 {

> hardware ethernet 00:04:a3:2b:22:55;

225,226c225,227

< host nnaida27 {

< hardware ethernet 00:04:a3:2b:22:55;

---

> # 2 of 2 scratch FEE modules assembled by PJCS April 2016

> host nnaida27 {

> hardware ethernet 00:04:a3:2a:ed:9a;

230,232c231,232

< # 2 of 2 scratch FEE modules assembled by PJCS April 2016

< host nnaida28 {

< hardware ethernet 00:04:a3:2b:09:e7;

---

> host nnaida28 {

> hardware ethernet 00:04:a3:2b:11:c5;

[root@aidas1 dhcp]# cat dhcpd.conf

#

# DHCP Server Configuration file.

# see /usr/share/doc/dhcp*/dhcpd.conf.sample

#

authoritative;

ddns-update-style none; ddns-updates off;

max-lease-time 691200;

option domain-search code 119 = string;

subnet 10.1.1.0 netmask 255.255.255.0 {

option subnet-mask 255.255.255.0;

option broadcast-address 10.1.1.255;

option routers 10.1.1.250;

pool {

range 10.1.1.100 10.1.1.249;

}

}

subnet 10.1.2.0 netmask 255.255.255.0 {

option subnet-mask 255.255.255.0;

option broadcast-address 10.1.2.255;

option routers 10.1.2.250;

pool {

range 10.1.2.100 10.1.2.249;

}

}

subnet 10.1.3.0 netmask 255.255.255.0 {

option subnet-mask 255.255.255.0;

option broadcast-address 10.1.3.255;

option routers 10.1.3.250;

pool {

range 10.1.3.100 10.1.3.249;

}

}

subnet 10.1.4.0 netmask 255.255.255.0 {

option subnet-mask 255.255.255.0;

option broadcast-address 10.1.4.255;

option routers 10.1.4.250;

pool {

range 10.1.4.100 10.1.4.249;

}

}

subnet 10.1.5.0 netmask 255.255.255.0 {

option subnet-mask 255.255.255.0;

option broadcast-address 10.1.5.255;

option routers 10.1.5.250;

pool {

range 10.1.5.100 10.1.5.249;

}

}

group {

use-host-decl-names true;

default-lease-time 3600;

max-lease-time 14400;

server-name "10.1.1.250";

next-server 10.1.1.250;

host nnrpi1 {

hardware ethernet b8:27:eb:78:ee:44;

fixed-address 10.1.1.251;

}

host nnaida1 {

hardware ethernet 00:04:a3:2a:d0:1b;

fixed-address 10.1.1.1;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida1,tcp";

}

host nnaida2 {

hardware ethernet 00:04:a3:2a:d9:e1;

fixed-address 10.1.1.2;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida2,tcp";

}

host nnaida5 {

hardware ethernet 00:04:a3:2a:d0:10;

fixed-address 10.1.1.5;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida5,tcp";

}

host nnaida6 {

hardware ethernet 00:04:a3:2a:d4:b7;

fixed-address 10.1.1.6;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida6,tcp";

}

host nnaida9 {

hardware ethernet 00:04:a3:2a:d9:ad;

fixed-address 10.1.1.9;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida9,tcp";

}

host nnaida10 {

hardware ethernet 00:04:a3:2a:f7:07;

fixed-address 10.1.1.10;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida10,tcp";

}

host nnaida13 {

hardware ethernet 00:04:a3:2b:11:b9;

fixed-address 10.1.1.13;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida13,tcp";

}

host nnaida14 {

hardware ethernet 00:04:a3:2b:11:b8;

fixed-address 10.1.1.14;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida14,tcp";

}

host nnaida17 {

hardware ethernet 00:04:a3:2a:d9:cc;

fixed-address 10.1.1.17;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida17,tcp";

}

host nnaida18 {

hardware ethernet 00:04:a3:2a:b2:b2;

fixed-address 10.1.1.18;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida18,tcp";

}

host nnaida21 {

hardware ethernet 00:04:a3:2b:27:23;

fixed-address 10.1.1.21;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida21,tcp";

}

host nnaida22 {

hardware ethernet 00:04:a3:2a:f6:e9;

fixed-address 10.1.1.22;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida22,tcp";

}

host nnaida25 {

hardware ethernet 00:04:a3:2a:d0:11;

fixed-address 10.1.1.25;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida25,tcp";

}

host nnaida26 {

hardware ethernet 00:04:a3:2b:27:54;

fixed-address 10.1.1.26;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida26,tcp";

}

host nnaida29 {

hardware ethernet 00:04:a3:2a:d0:06;

fixed-address 10.1.1.29;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida29,tcp";

}

host nnaida30 {

hardware ethernet 00:04:a3:2a:d9:b6;

fixed-address 10.1.1.30;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida30,tcp";

}

}

group {

use-host-decl-names true;

default-lease-time 3600;

max-lease-time 14400;

server-name "10.1.2.250";

next-server 10.1.2.250;

host nnaida3 {

hardware ethernet 00:04:a3:2a:f7:06;

fixed-address 10.1.2.3;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida3,tcp";

}

host nnaida4 {

hardware ethernet 00:04:a3:2a:ed:b8;

fixed-address 10.1.2.4;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida4,tcp";

}

host nnaida7 {

hardware ethernet 00:04:a3:2a:b8:8d;

fixed-address 10.1.2.7;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida7,tcp";

}

host nnaida8 {

hardware ethernet 00:04:a3:2a:9c:07;

fixed-address 10.1.2.8;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida8,tcp";

}

host nnaida11 {

hardware ethernet 00:04:a3:2b:11:af;

fixed-address 10.1.2.11;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida11,tcp";

}

host nnaida12 {

hardware ethernet 00:04:a3:2a:d0:2f;

fixed-address 10.1.2.12;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida12,tcp";

}

host nnaida15 {

hardware ethernet 00:04:a3:2a:f3:ac;

fixed-address 10.1.2.15;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida15,tcp";

}

host nnaida16 {[root@aidas1 aidas1]# diff startup.tcl startup.tcl.BAK-260516

31,32c31,32

< variable PACQSERVERS; set PACQSERVERS { nnaida1 nnaida2 nnaida5 nnaida6 nnaida9 nnaida10 nnaida13

nnaida14 nnaida17 nnaida18 nnaida21 nnaida22 nnaida25 nnaida26 nnaida29 nnaida30 }

< variable NACQSERVERS; set NACQSERVERS { nnaida3 nnaida4 nnaida7 nnaida8 nnaida11 nnaida12 nnaida15

nnaida16 nnaida19 nnaida20 nnaida23 nnaida24 nnaida27 nnaida28 nnaida31 nnaida32 }

---

> variable PACQSERVERS; set PACQSERVERS { nnaida1 nnaida2 nnaida5 nnaida6 nnaida9 nnaida10 nnaida13

nnaida14 nnaida17 nnaida18 nnaida21 nnaida22 nnaida25 nnaida29 nnaida30 }

> variable NACQSERVERS; set NACQSERVERS { nnaida3 nnaida4 nnaida7 nnaida8 nnaida11 nnaida12 nnaida15

nnaida16 nnaida20 nnaida23 nnaida24 nnaida27 nnaida28 nnaida31 nnaida32 }

33a34

> # startup.tcl.BAK-130516 has all 32 NNAIDA modules included

52c53

< lappend ACQSERVERS nnaida19

---

> # lappend ACQSERVERS nnaida19

59c60

< lappend ACQSERVERS nnaida26

---

> # lappend ACQSERVERS nnaida26

hardware ethernet 00:04:a3:2a:9c:0e;

fixed-address 10.1.2.16;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida16,tcp";

}

# 1 of 2 scratch FEE modules assembled by PJCS April 2016

host nnaida19 {

hardware ethernet 00:04:a3:2a:ed:9a;

fixed-address 10.1.2.19;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida19,tcp";

}

host nnaida20 {

hardware ethernet 00:04:a3:2b:11:c5;

fixed-address 10.1.2.20;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida20,tcp";

}

host nnaida23 {

hardware ethernet 00:04:a3:2a:b8:90;

fixed-address 10.1.2.23;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida23,tcp";

}

host nnaida24 {

hardware ethernet 00:04:a3:2a:b6:45;

fixed-address 10.1.2.24;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida24,tcp";

}

host nnaida27 {

hardware ethernet 00:04:a3:2b:22:55;

fixed-address 10.1.2.27;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida27,tcp";

}

# 2 of 2 scratch FEE modules assembled by PJCS April 2016

host nnaida28 {

hardware ethernet 00:04:a3:2b:09:e7;

fixed-address 10.1.2.28;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida28,tcp";

}

host nnaida31 {

hardware ethernet 00:04:a3:2b:11:ae;

fixed-address 10.1.2.31;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida31,tcp";

}

host nnaida32 {

hardware ethernet 00:04:a3:2a:ed:b9;

fixed-address 10.1.2.32;

option root-path "/MIDAS@aidas/XilinxLinux/ppc_4xx/rfs/nnaida32,tcp";

}

}

group {

# 8 days

default-lease-time 691200;

# option dhcp-client-identifier "\0foo";

host nndhcp052 {

# Analysis server

hardware ethernet 00:22:19:50:02:40;

fixed-address 10.1.1.252;

}

}

DAQ server configuration file /MIDAS/config/TclHttpd/aidas1/startup.tcl update - see attachment 2

[root@aidas1 aidas1]# diff startup.tcl startup.tcl.BAK-260516

31,32c31,32

< variable PACQSERVERS; set PACQSERVERS { nnaida1 nnaida2 nnaida5 nnaida6 nnaida9 nnaida10 nnaida13

nnaida14 nnaida17 nnaida18 nnaida21 nnaida22 nnaida25 nnaida26 nnaida29 nnaida30 }

< variable NACQSERVERS; set NACQSERVERS { nnaida3 nnaida4 nnaida7 nnaida8 nnaida11 nnaida12 nnaida15

nnaida16 nnaida19 nnaida20 nnaida23 nnaida24 nnaida27 nnaida28 nnaida31 nnaida32 }

---

> variable PACQSERVERS; set PACQSERVERS { nnaida1 nnaida2 nnaida5 nnaida6 nnaida9 nnaida10 nnaida13

nnaida14 nnaida17 nnaida18 nnaida21 nnaida22 nnaida25 nnaida29 nnaida30 }

> variable NACQSERVERS; set NACQSERVERS { nnaida3 nnaida4 nnaida7 nnaida8 nnaida11 nnaida12 nnaida15

nnaida16 nnaida20 nnaida23 nnaida24 nnaida27 nnaida28 nnaida31 nnaida32 }

33a34

> # startup.tcl.BAK-130516 has all 32 NNAIDA modules included

52c53

< lappend ACQSERVERS nnaida19

---

> # lappend ACQSERVERS nnaida19

59c60

< lappend ACQSERVERS nnaida26

---

> # lappend ACQSERVERS nnaida26

Need to update nnaida19 and nnaida26 to latest firmware version - see https://elog.ph.ed.ac.uk/AIDA/237 |

| Attachment 1: 72.png

|

|

| Attachment 2: startup.tcl

|

Setting BGColor "BlanchedAlmond"

Setting TextColor "red"

Setting ProjectName AIDA

Setting ProjectImage AIDA.gif

Setting ProjectURL "http://npg.dl.ac.uk/NPG/Projects/Fair.html"

Setting Option1Name STFC

Setting Option1URL "stfc.ac.uk"

Setting Option1Image stfc.jpg

global MessageLoggerServerHost

set MessageLoggerServerHost elog.ph.ed.ac.uk

package require MessageLoggerClient

Setting Option3Name "Elog Server"

Setting Option3URL "https://elog.ph.ed.ac.uk/AIDA"

# Install required services

package require XAIDAAccessClient ;# for Client end - ie AIDA server workstation sets MIDAS_XAIDAAccessClient_Exists (SOAP)

package require XAD9252AccessClient ;# for Client end - ie AIDA server workstation sets MIDAS_XAD9252AccessClient_Exists (SOAP)

namespace eval DataAcquisition {

variable PROJECT AIDA

variable ACQSERVERS; set ACQSERVERS {}

variable PACQSERVERS; set PACQSERVERS { nnaida1 nnaida2 nnaida5 nnaida6 nnaida9 nnaida10 nnaida13 nnaida14 nnaida17 nnaida18 nnaida21 nnaida22 nnaida25 nnaida26 nnaida29 nnaida30 }

variable NACQSERVERS; set NACQSERVERS { nnaida3 nnaida4 nnaida7 nnaida8 nnaida11 nnaida12 nnaida15 nnaida16 nnaida19 nnaida20 nnaida23 nnaida24 nnaida27 nnaida28 nnaida31 nnaida32 }

lappend ACQSERVERS nnaida1

lappend ACQSERVERS nnaida2

lappend ACQSERVERS nnaida3

lappend ACQSERVERS nnaida4

lappend ACQSERVERS nnaida5

lappend ACQSERVERS nnaida6

lappend ACQSERVERS nnaida7

lappend ACQSERVERS nnaida8

lappend ACQSERVERS nnaida9

lappend ACQSERVERS nnaida10

lappend ACQSERVERS nnaida11

lappend ACQSERVERS nnaida12

lappend ACQSERVERS nnaida13

lappend ACQSERVERS nnaida14

lappend ACQSERVERS nnaida15

lappend ACQSERVERS nnaida16

lappend ACQSERVERS nnaida17

lappend ACQSERVERS nnaida18

lappend ACQSERVERS nnaida19

lappend ACQSERVERS nnaida20

lappend ACQSERVERS nnaida21

lappend ACQSERVERS nnaida22

lappend ACQSERVERS nnaida23

lappend ACQSERVERS nnaida24

lappend ACQSERVERS nnaida25

lappend ACQSERVERS nnaida26

lappend ACQSERVERS nnaida27

lappend ACQSERVERS nnaida28

lappend ACQSERVERS nnaida29

lappend ACQSERVERS nnaida30

lappend ACQSERVERS nnaida31

lappend ACQSERVERS nnaida32

variable DataTransferStreams; set DataTransferStreams 2

}

namespace eval AIDA {

variable ModuleMenu; set ModuleMenu $::DataAcquisition::ACQSERVERS

variable TSMaster; set TSMaster nnaida5

variable FEE64 [first $ModuleMenu]

variable ConfigBase; set ConfigBase [file join $env(MIDASBASE) config TclHttpd]

}

Setting DataBaseRoot "/MIDAS/DB"

package require DataBaseAccessServer

package require NetVarsServer 1.1

package require SigTaskServer

package require MemSasServer

# Install services for Run Control

namespace eval $::DataAcquisition::PROJECT {

variable DBRootName [file join EXPERIMENTS AIDA]

variable DBNodeBase 2012

}

package require AIDARunControl

Setting Option7Name "Project Home Page"

Setting Option7URL "http://npg.dl.ac.uk/NPG/Projects/Fair.html"

Setting Option8Name "Server Software Home Page"

Setting Option8URL "http://npg.dl.ac.uk/MIDAS/download/WebServices.html"

|

|

|

241

|

Fri May 27 06:38:27 2016 |

TD, AE & CG | Friday 27 May 2016 | 14.30 DSSSD stack moved upstream to position DSSSD#3 at centre of EURICA.

Initial tests of detector bias with DSSSD #1-6 were Ok. Unfortunately we were unable to bias

DSSSD #7 obtaining either open or short circuit depending on which of the two p+n junction

side and n+n ohmic side detector bias bus lines we connected to.

Demonstrated that short circuit was upstream, of AIDA adaptor PCB by disconnecting Kapton

LH couplers.

Remove DSSSD stack and replace DSSSD #7. In progress.

15.50 Startup AIDA with DSSSDs disconnected

Temperatures & firmware version - see attachment 1

AIDA SYNCs - attachment 2

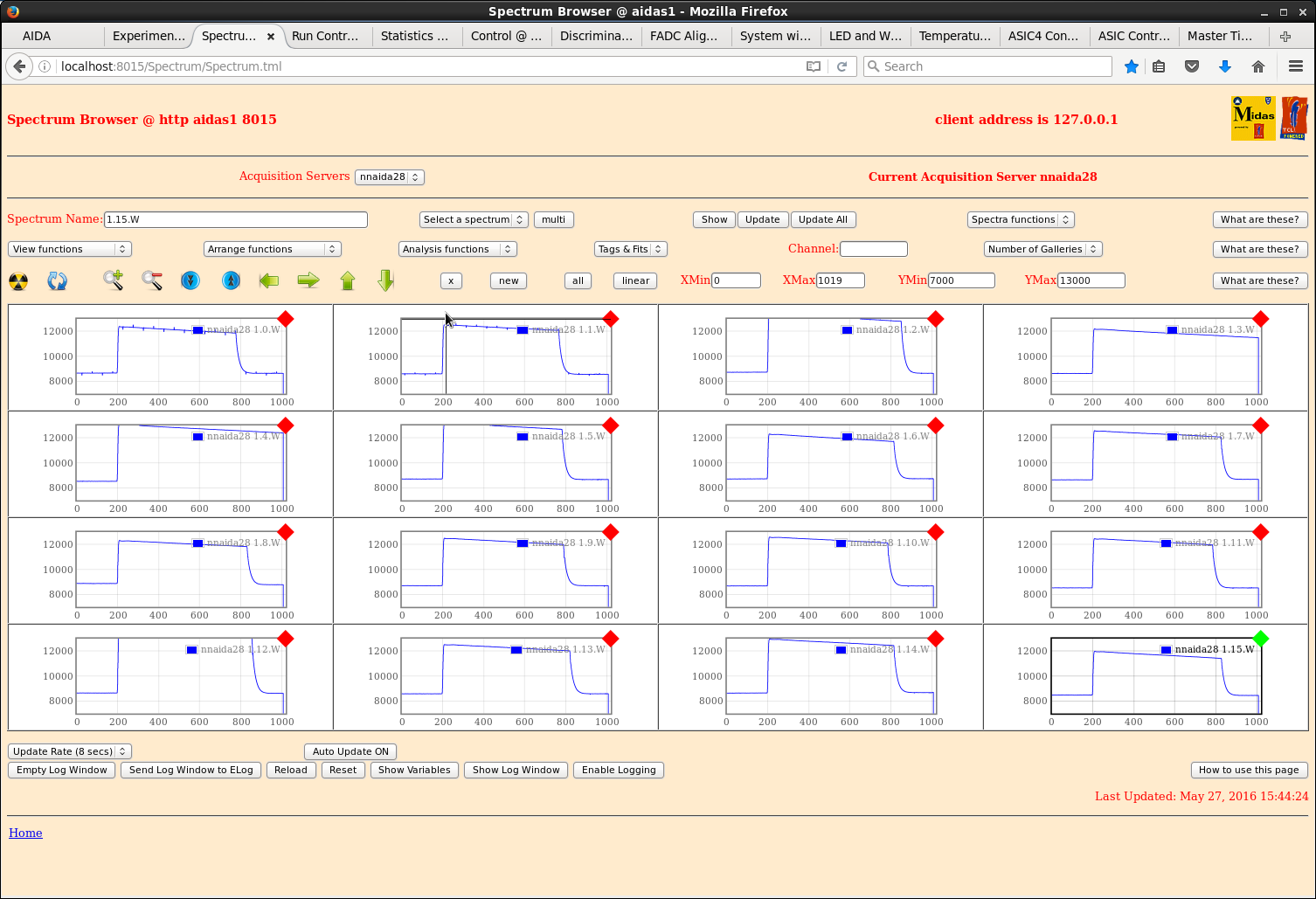

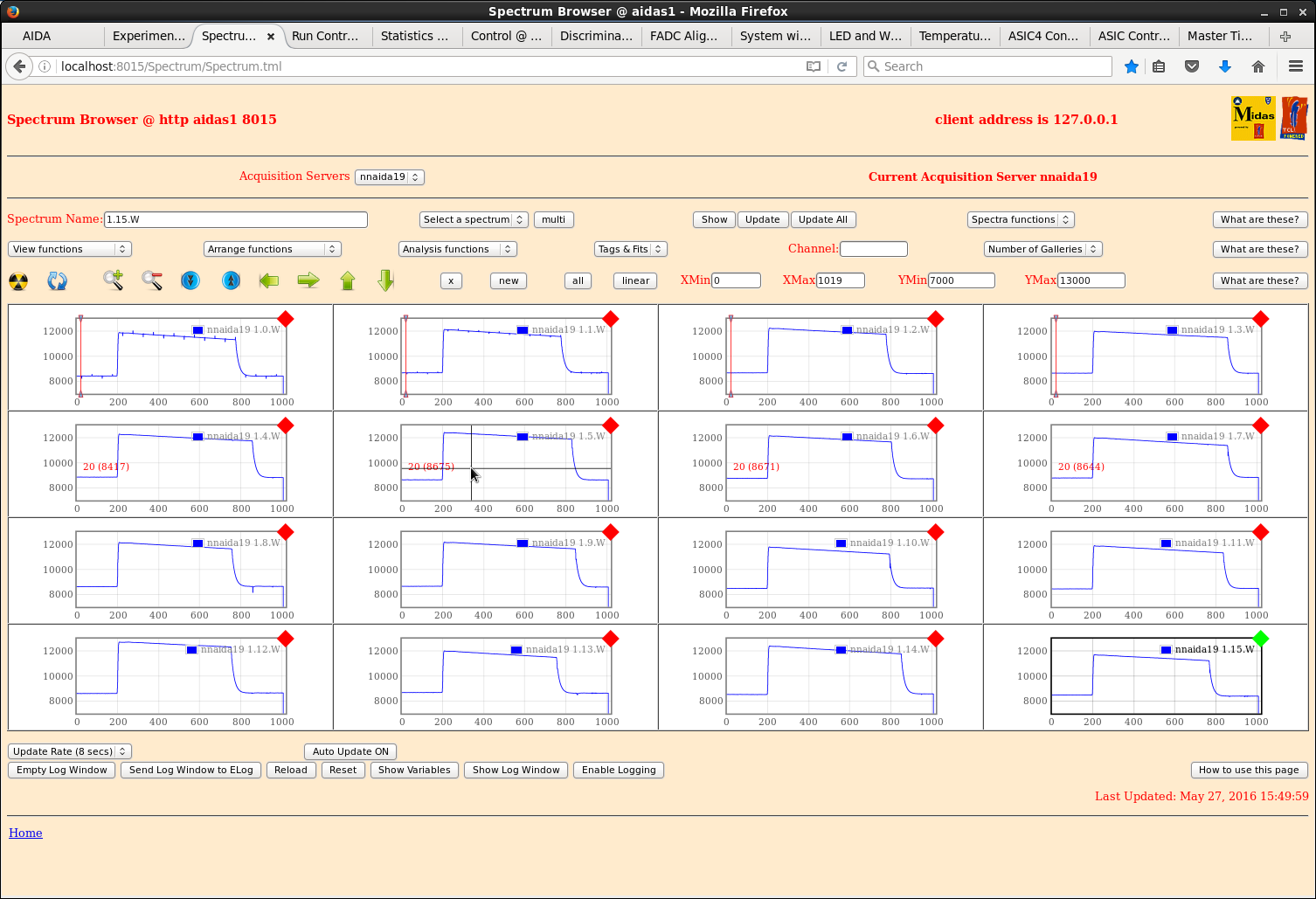

System wide checks - attachments 3-6 - note persistent nnaida19 ASIC clock and SYNC errors

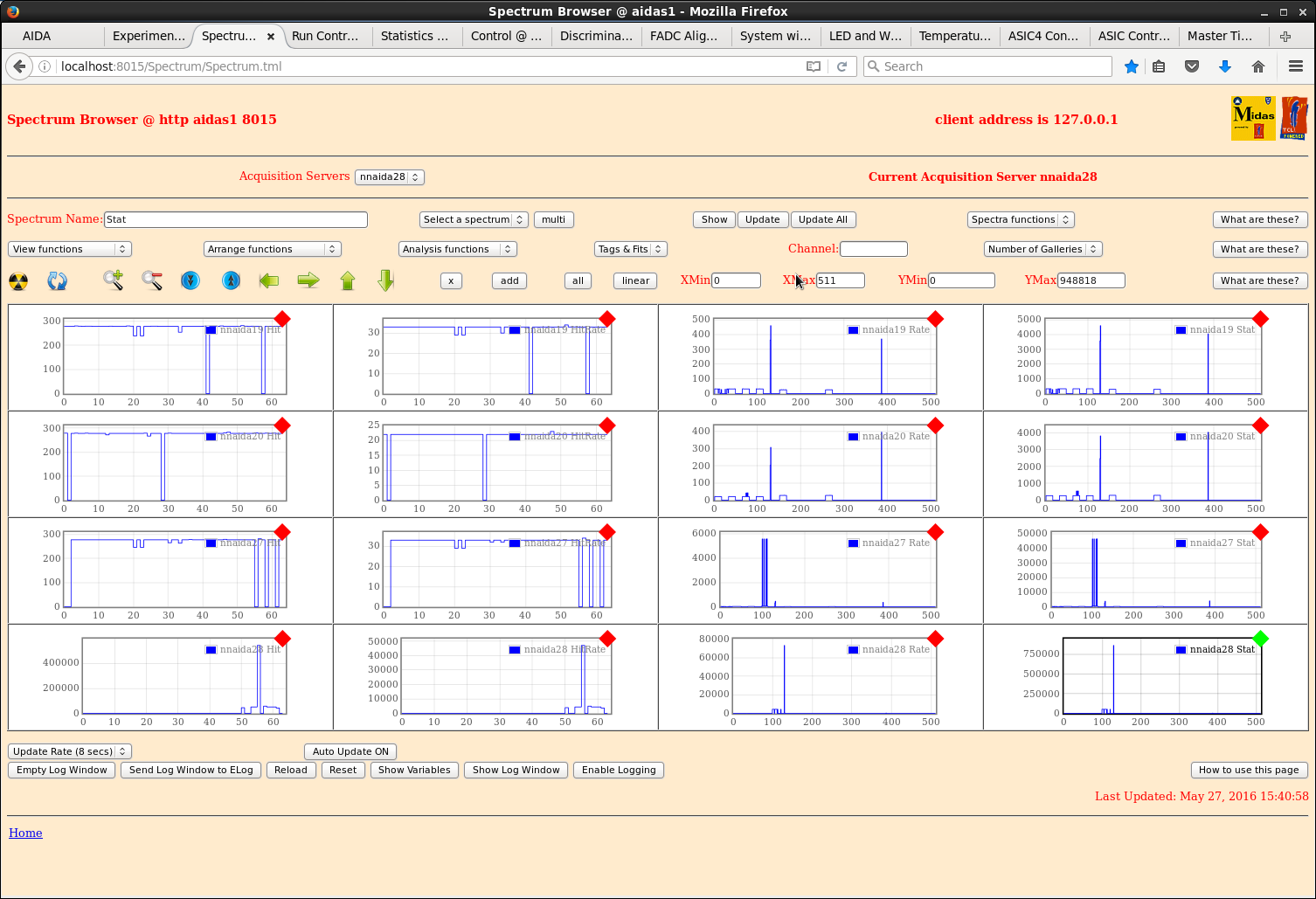

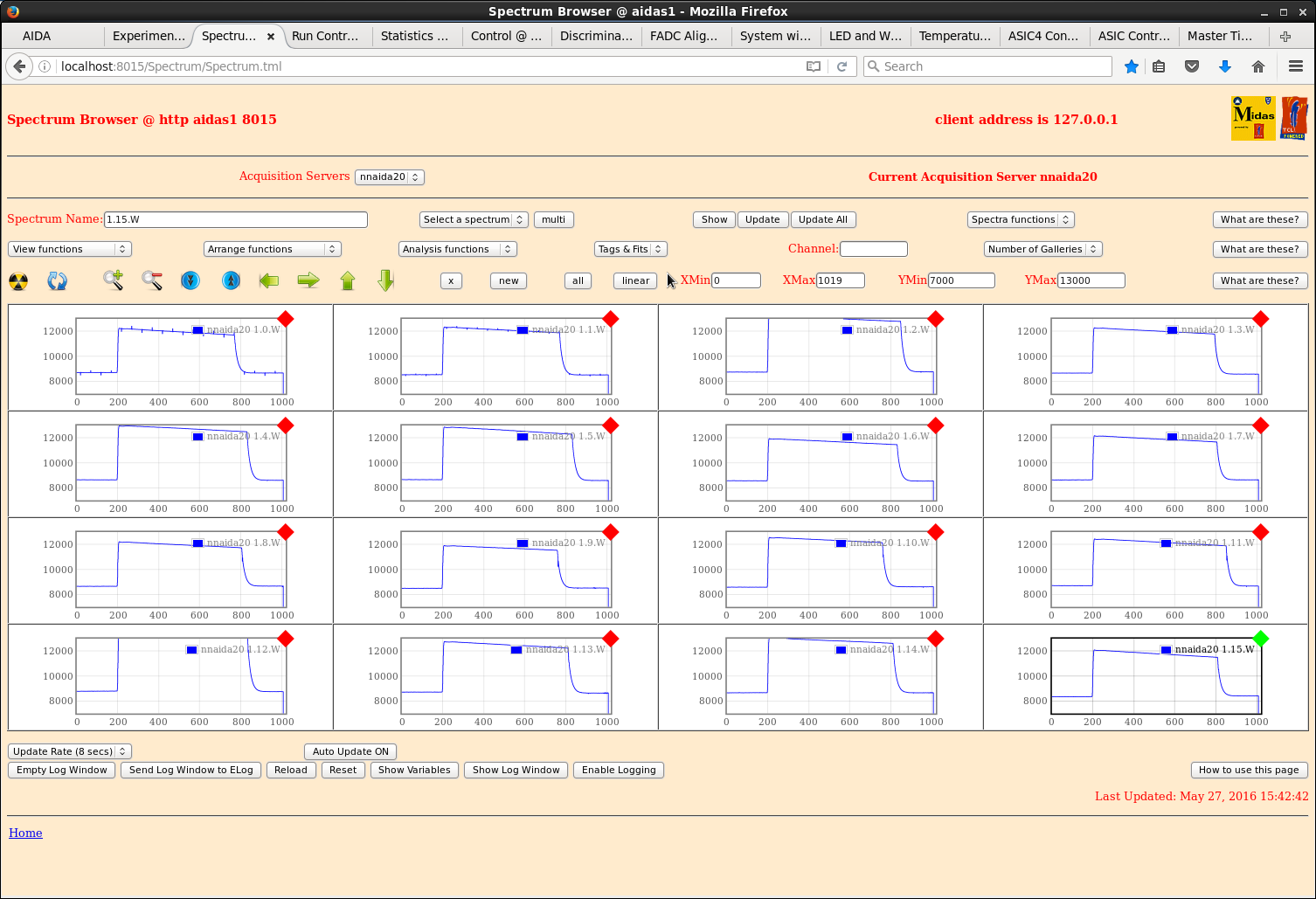

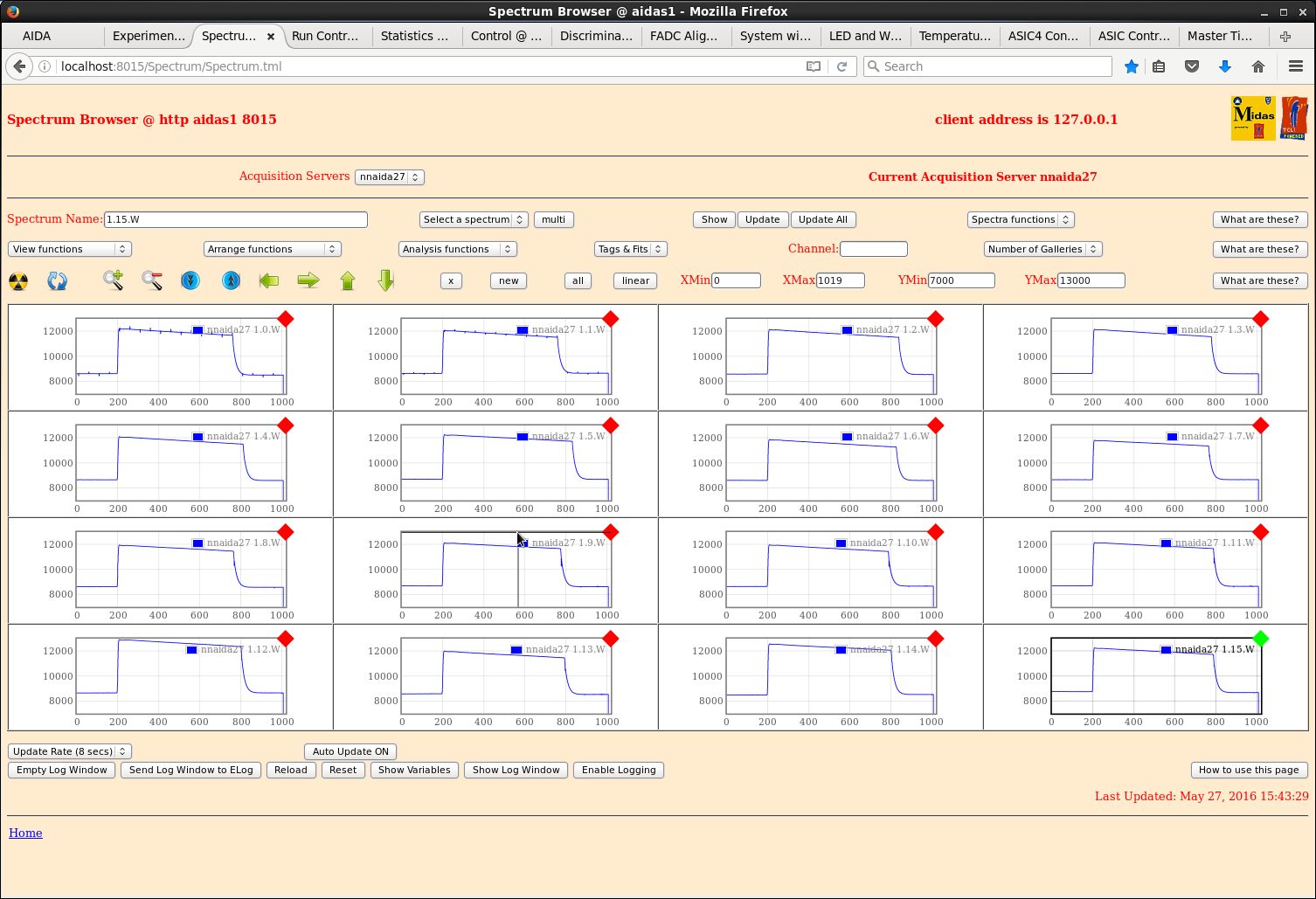

Statistics nnaida19, 20 - attachments 7-8

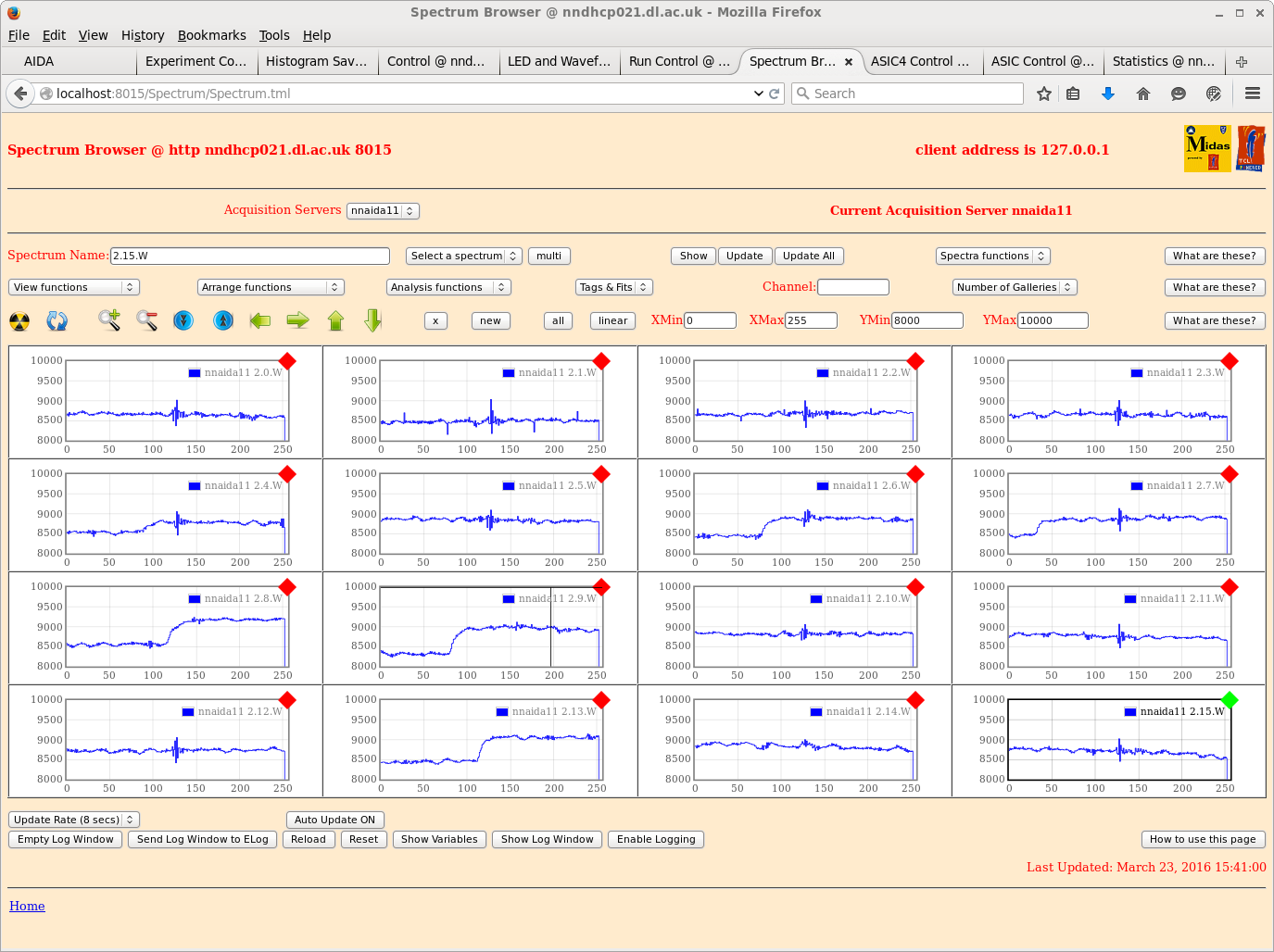

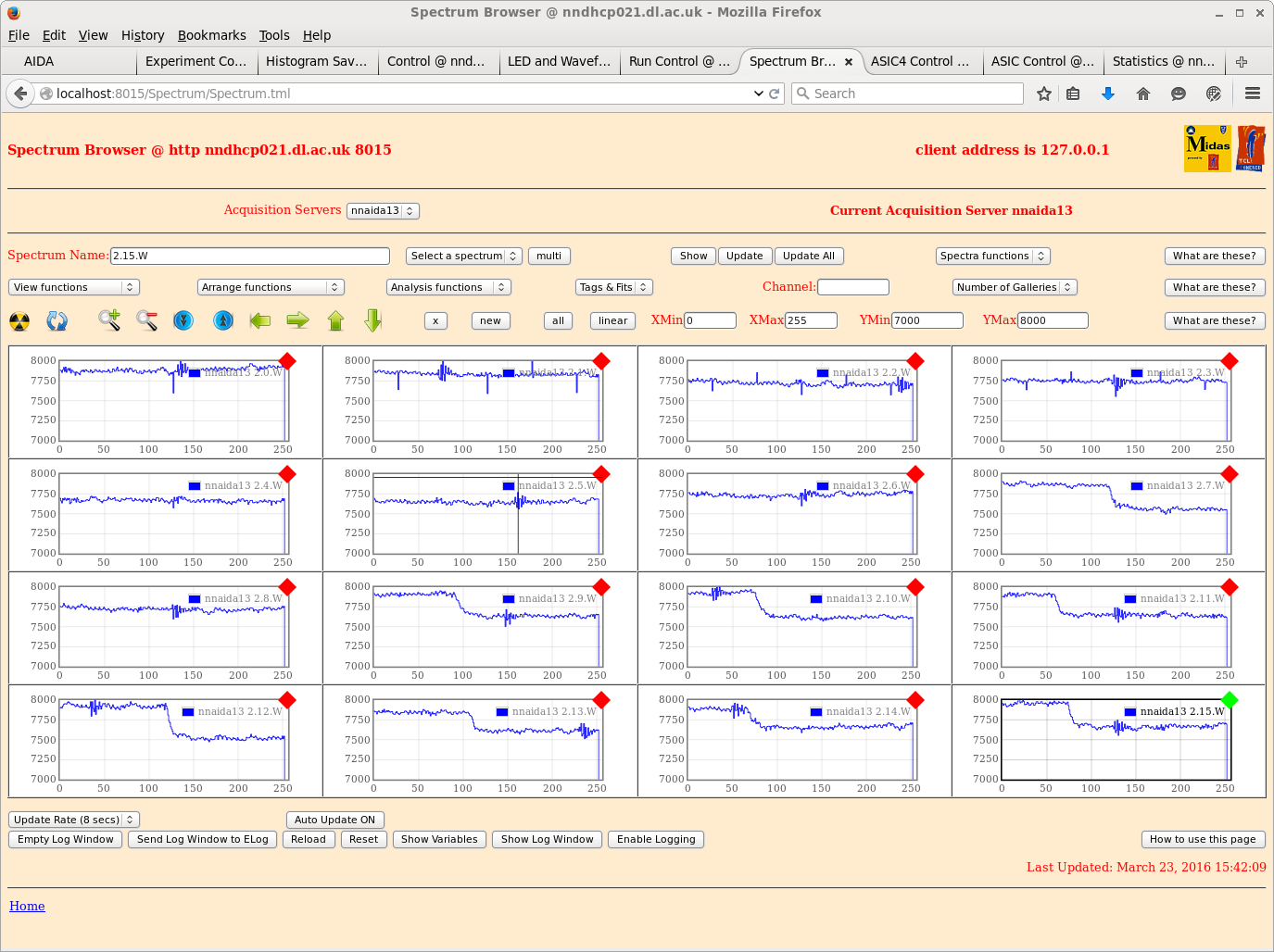

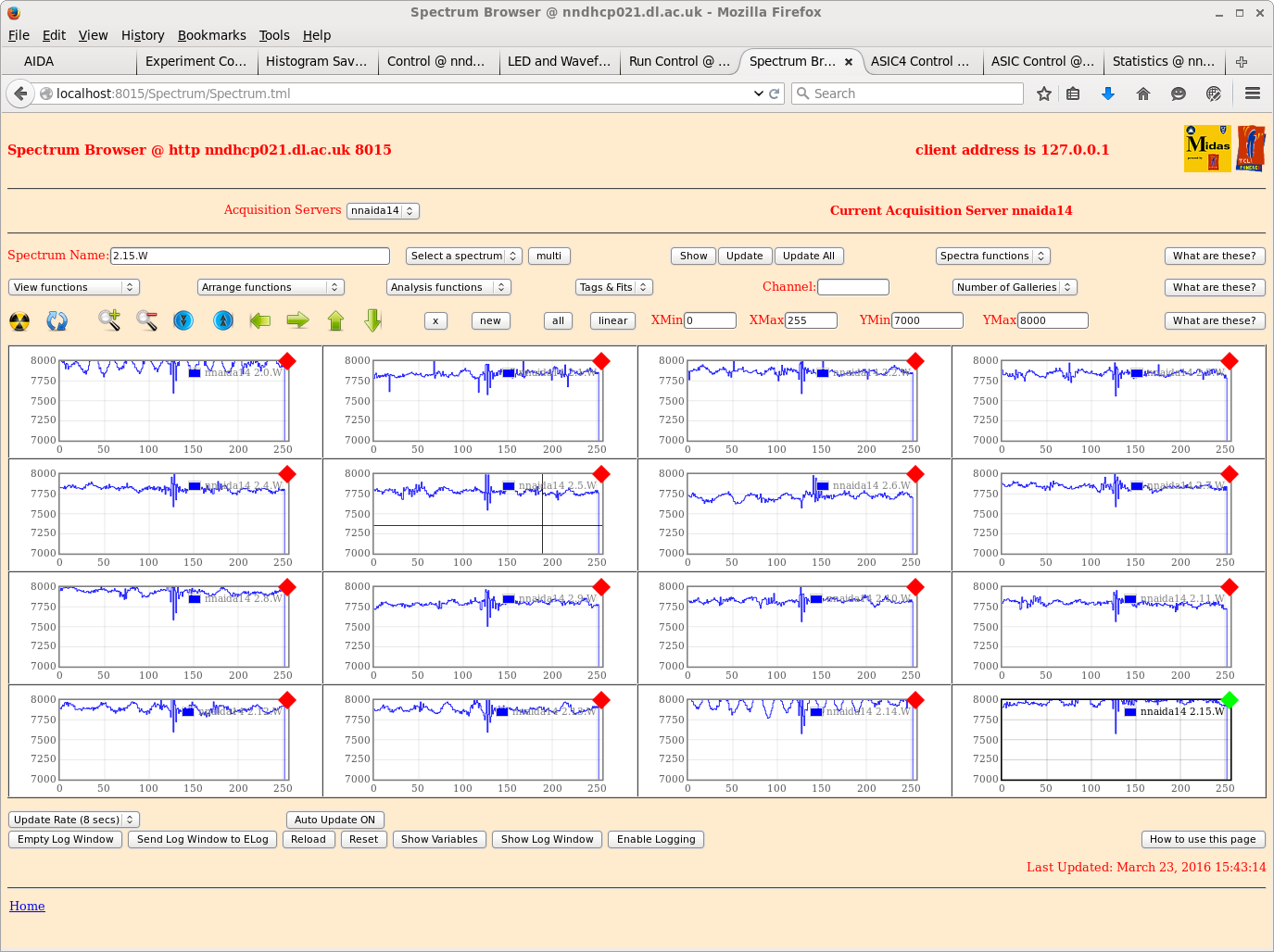

nnaida19, 20, 27 & 28 hit pattern and waveform spectra - see attachments 9-13

Some nnaida19 system wide errors above and noisy ASIC#4 hit channel for nnaida28 - otherwise OK |

| Attachment 1: 80.png

|

|

| Attachment 2: 81.png

|

|

| Attachment 3: 83.png

|

|

| Attachment 4: 84.png

|

|

| Attachment 5: 85.png

|

|

| Attachment 6: 86.png

|

|

| Attachment 7: 87.png

|

|

| Attachment 8: 88.png

|

|

| Attachment 9: 90.png

|

|

| Attachment 10: 94.png

|

|

| Attachment 11: 95.png

|

|

| Attachment 12: 96.png

|

|

| Attachment 13: 91.png

|

|

|

|

247

|

Sun May 29 14:06:31 2016 |

TD, AE & CG | Sunday 29 May 2016 | Throughout day:

DSSD2 (3058-25) would not bias, either short circuit or suspiciously low leakage current.

Carried out some test in situ which were inconclusive.

Removed snout and took DSSD2 out.

Measuring the resistance across the two pins providing the n+n bias yielded 20 Ohms.

For the p+n the same measurement saw an open circuit => at least one of the bond wires broken.

DSSD1 (3131-9) was moved into the DSSD2 position and DSSD1 is now BB18-1000 3058-4.

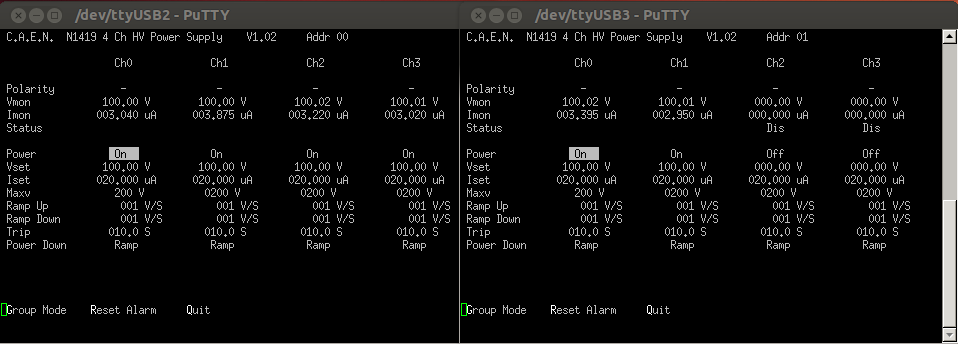

All detectors were biased downstairs and all looked fine - leakage currents of 3.1 - 3.8 uA.

First detector sits 54.5cm from Al base plate and 10cm from the upstream end of the snout.

9mm between each of the DSSDs.

Stack now:

| 3058-4

b | 3131-9

e | 2998-23

a | 3058-5

m | 3058-6

V 3058-7

207Bi source installed at end of snout.

Snout moved upstairs and mounted.

DSSD2 would not bias. This was due to the HV cable providing bias for this DSSD having a short to ground.

Replaced with HV cable 7 and biased successfully.

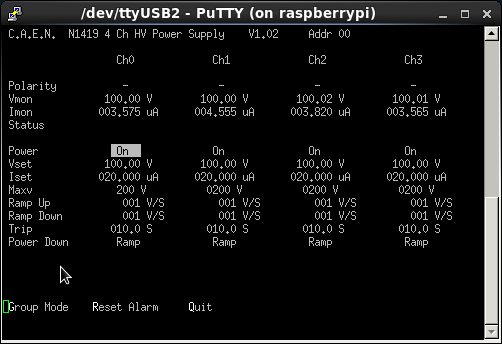

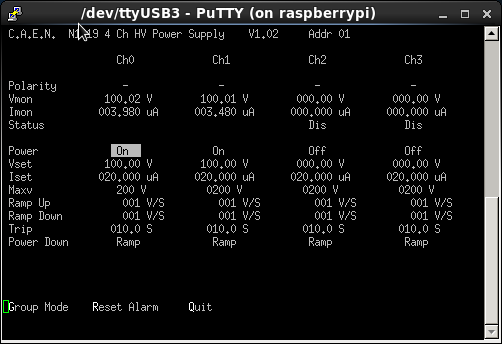

All DSSDs now bias. Screenshots of leakage currents attached (attachments 4+5) at room temp 25.3oC.

Caen module Addr 00 provides bias to DSSDs 1, 2, 3 and 4 via channels 0, 1, 2 and 3 respectively.

Module Addr 01 provides bias to DSSDs 5 and 6 on channels 0 and 1, respectively.

Snout pushed in to EURICA.

22.05 nnaida17 ASIC parameters not loading

power cycle & reboot

nnaida5 (master) clock not locked - status 0x6 - see attachments 1-3 |

| Attachment 1: 62.png

|

|

| Attachment 2: 63.png

|

|

| Attachment 3: 64.png

|

|

| Attachment 4: caen_addr0_290616_2244.png

|

|

| Attachment 5: caen_addr1_290616_2244.png

|

|

|

|

259

|

Mon May 30 09:03:07 2016 |

TD, AE & CG | timstamping - state of play |

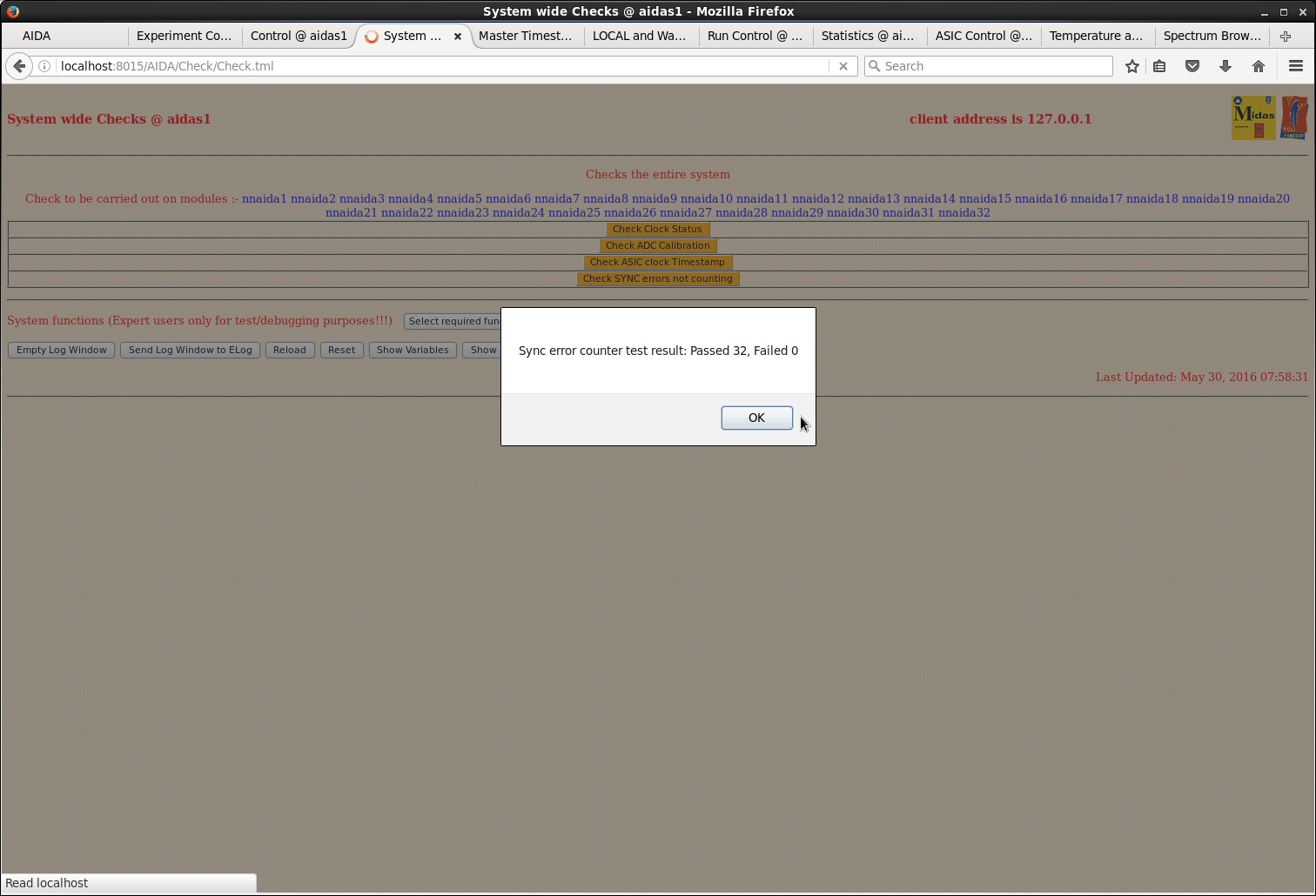

Current error messages and status - see attachments |

| Attachment 1: 1.png

|

|

| Attachment 2: 2.png

|

|

| Attachment 3: 3.png

|

|

| Attachment 4: 4.png

|

|

| Attachment 5: 5.png

|

|

| Attachment 6: 6.png

|

|

| Attachment 7: 7.png

|

|

| Attachment 8: 8.png

|

|

| Attachment 9: 9.png

|

|

| Attachment 10: 11.png

|

|

| Attachment 11: 12.png

|

|

|

|

262

|

Tue May 31 08:06:43 2016 |

TD, AE & CG | Tuesday 31 May 2016 |

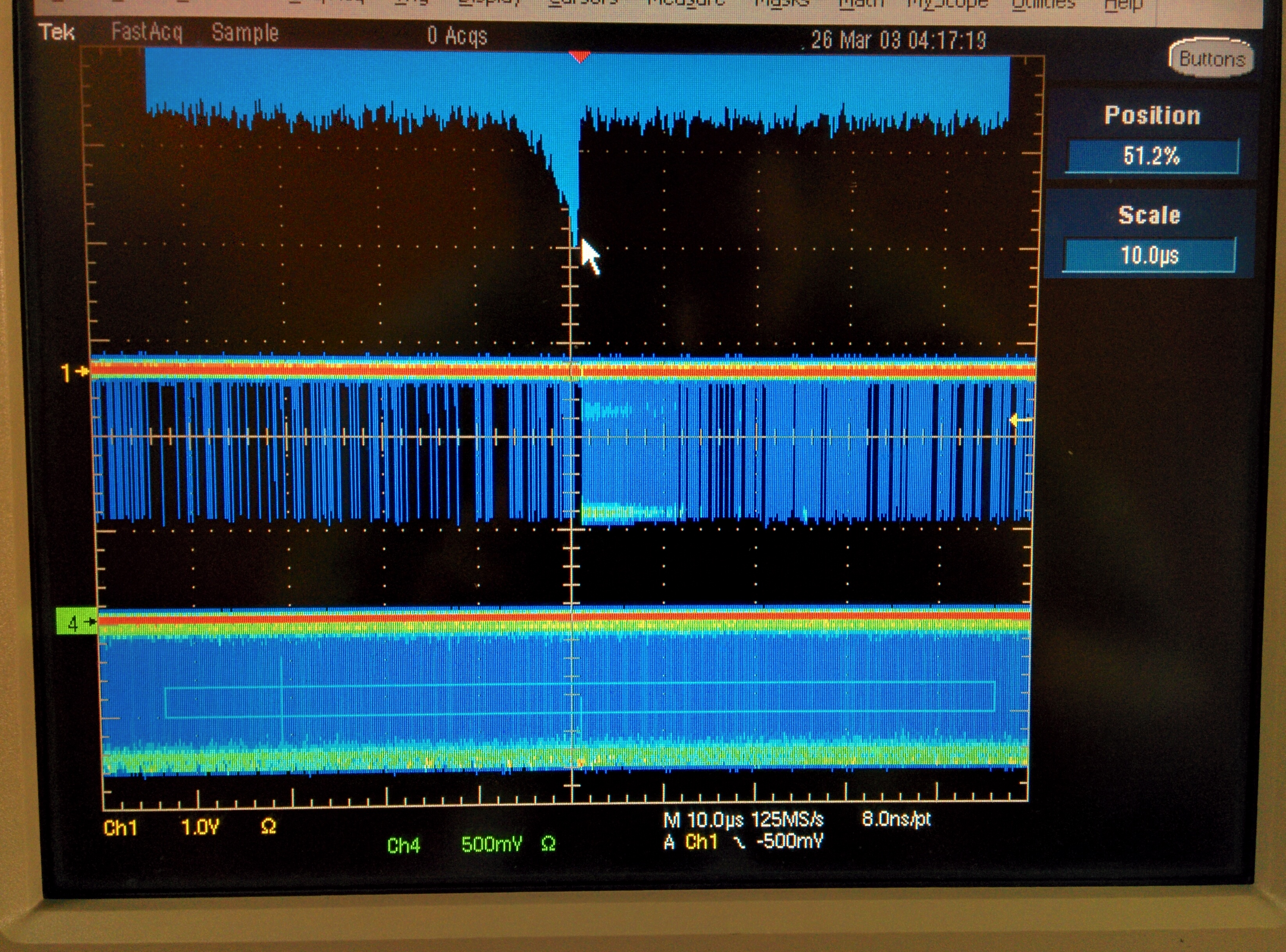

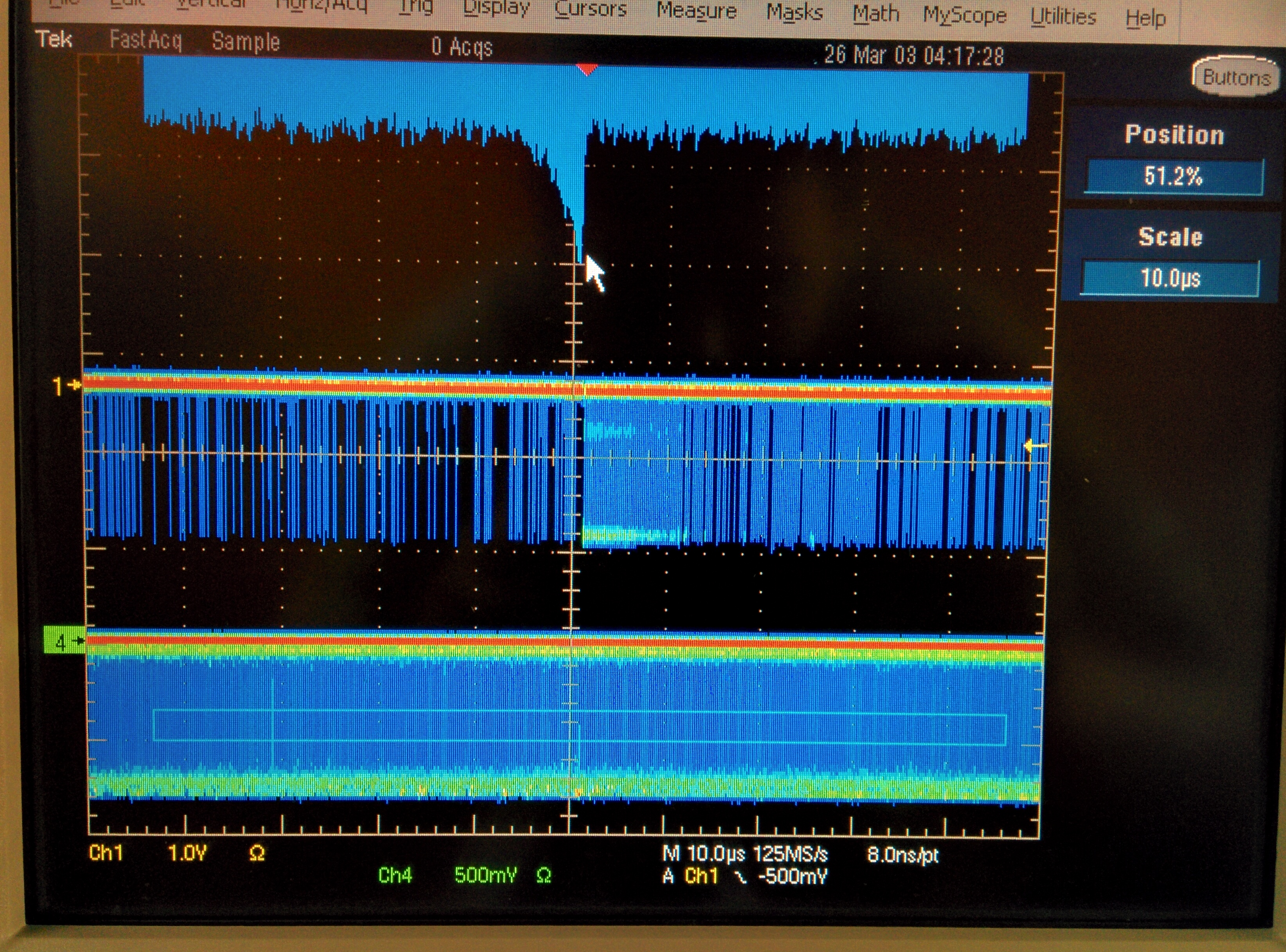

Attachment 3 - AIDA discriminator with pulser ~5Hz

standard ASIC settings (tau=8us, slow comparator 0x10, LEC/MEC comparator 0x9)

17.30 Added jumpers to the front/rear field plate connections (Lk 2/4 + 6/8) on all FEEs corresponding to DSSDs

1 and 6

Saw significant reduction in size of noise peak in waveforms as well as in the fast discriminator rate

from all FEEs.

18.50 R13 (AIDA) + BiCocal_run0012.lmd (EURICA)

207Bi beta-gamma correlation test

Standard ASIC settings (tau=8us, slow comparator 0x10, LEC/MEC comparator 0x9)

BNC PB-4 pulser OFF

Settings DB key 2016May31-18.55.42

Attachment 4 - statistics AIDA discriminators

Attachments 6-7 - time correlation for 207Bi beta-gamma coincidences between EURICA Ge Or and

DSSSD#1 trigger ( .OR.X strips .AND. OR.Y strips ) |

| Attachment 1: 101.png

|

|

| Attachment 2: 102.png

|

|

| Attachment 3: 103.png

|

|

| Attachment 4: 105.png

|

|

| Attachment 5: biasVoltages_31May1904_R12.png

|

|

| Attachment 6: 2016-05-31_18.58.01.jpg

|

|

| Attachment 7: 2016-05-31_18.58.11.jpg

|

|

|

|

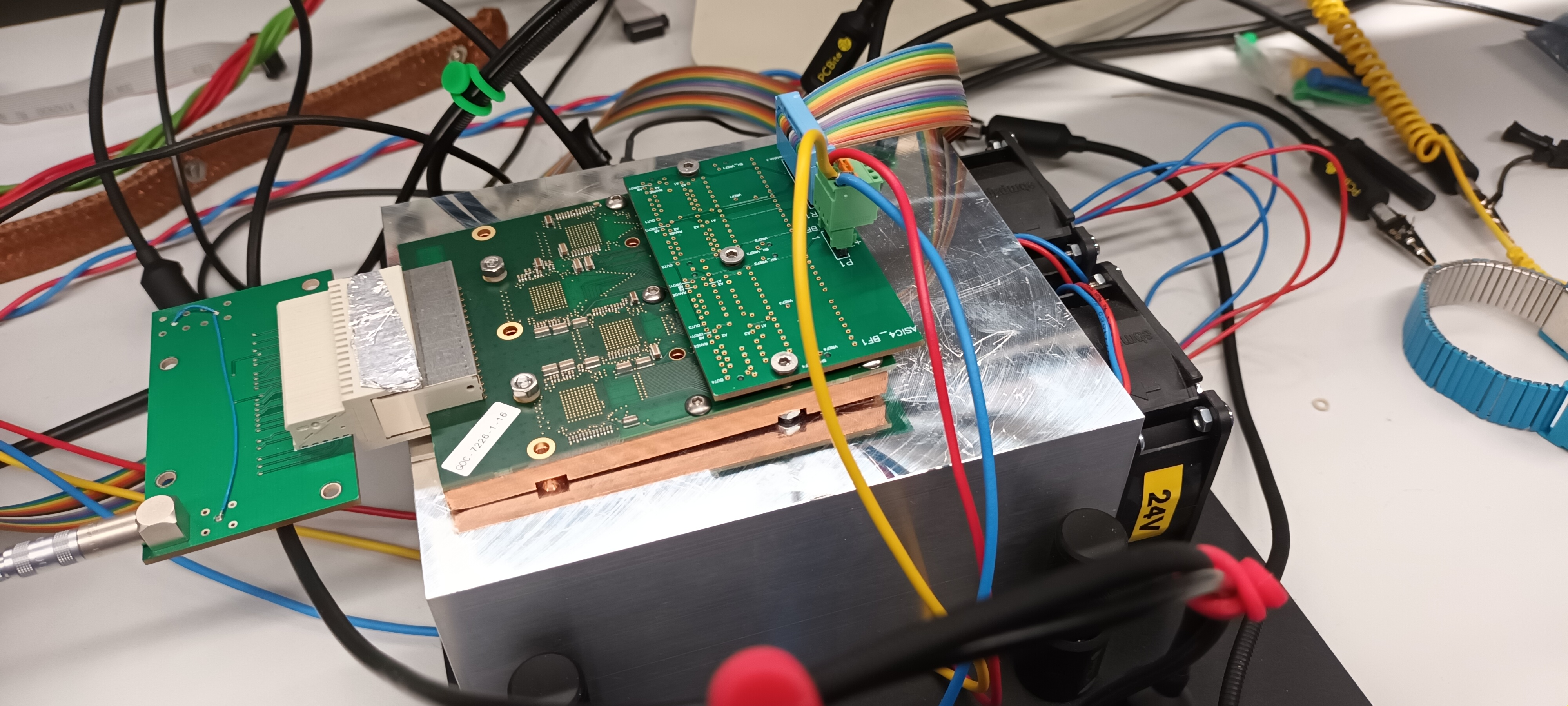

864

|

Thu Feb 23 16:15:31 2023 |

TD PJCS | Bench test of AIDA FEE64 mezzanines |

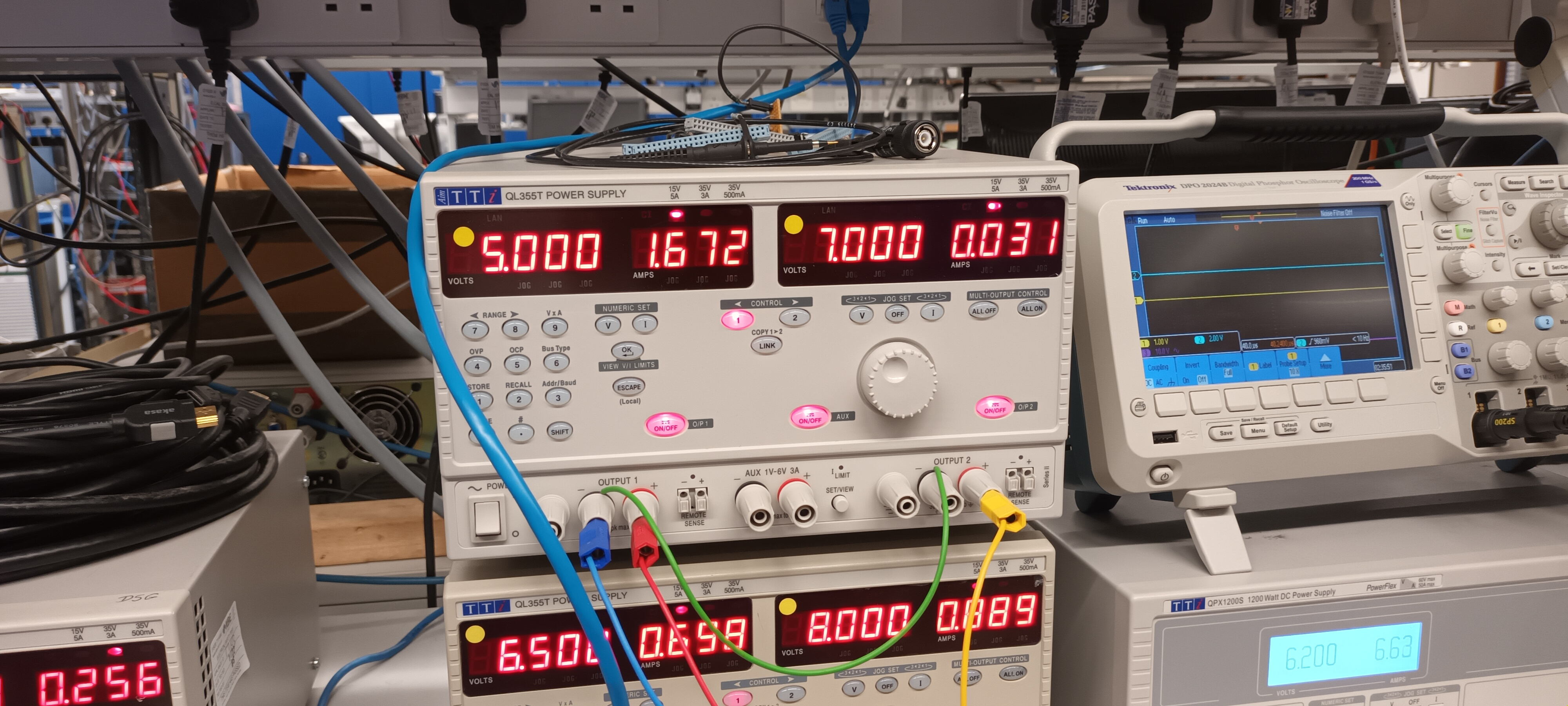

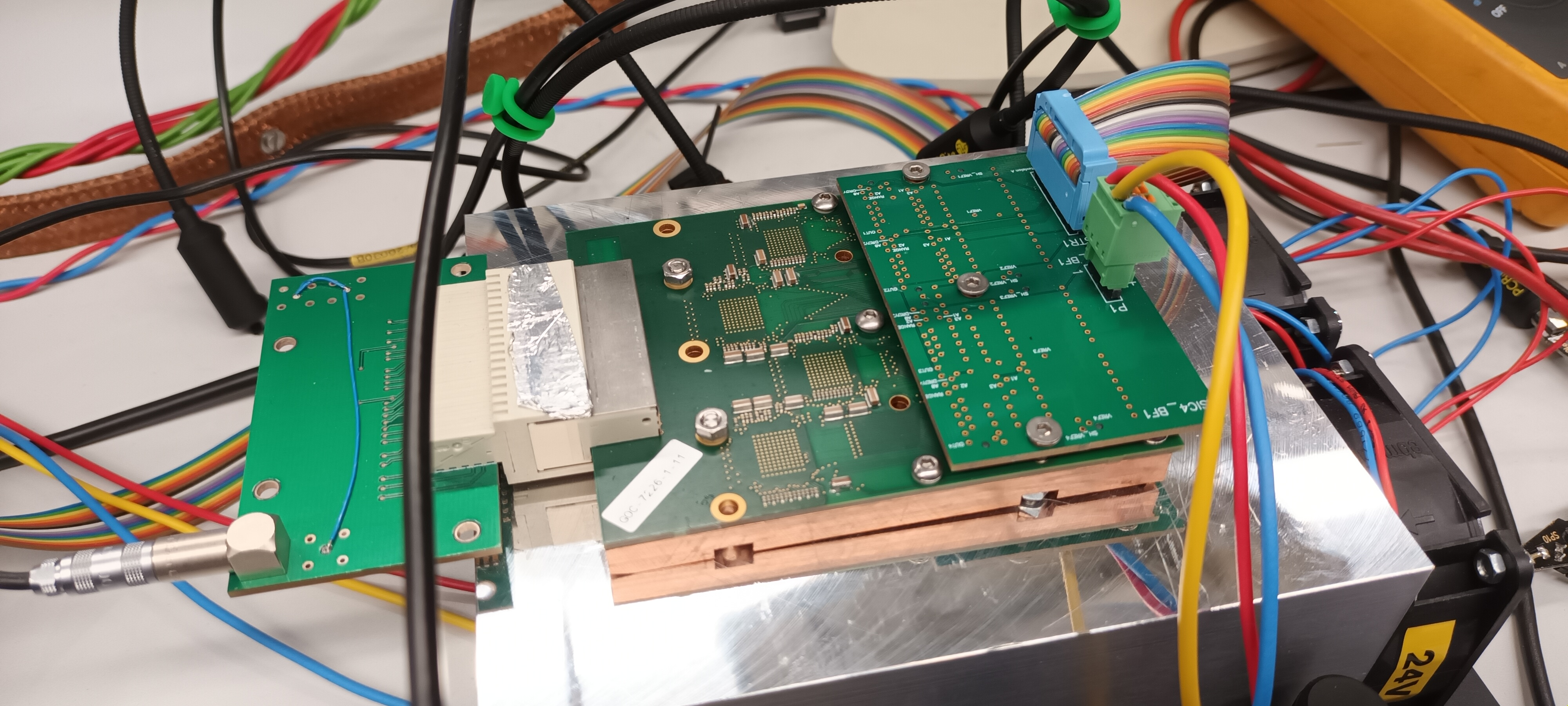

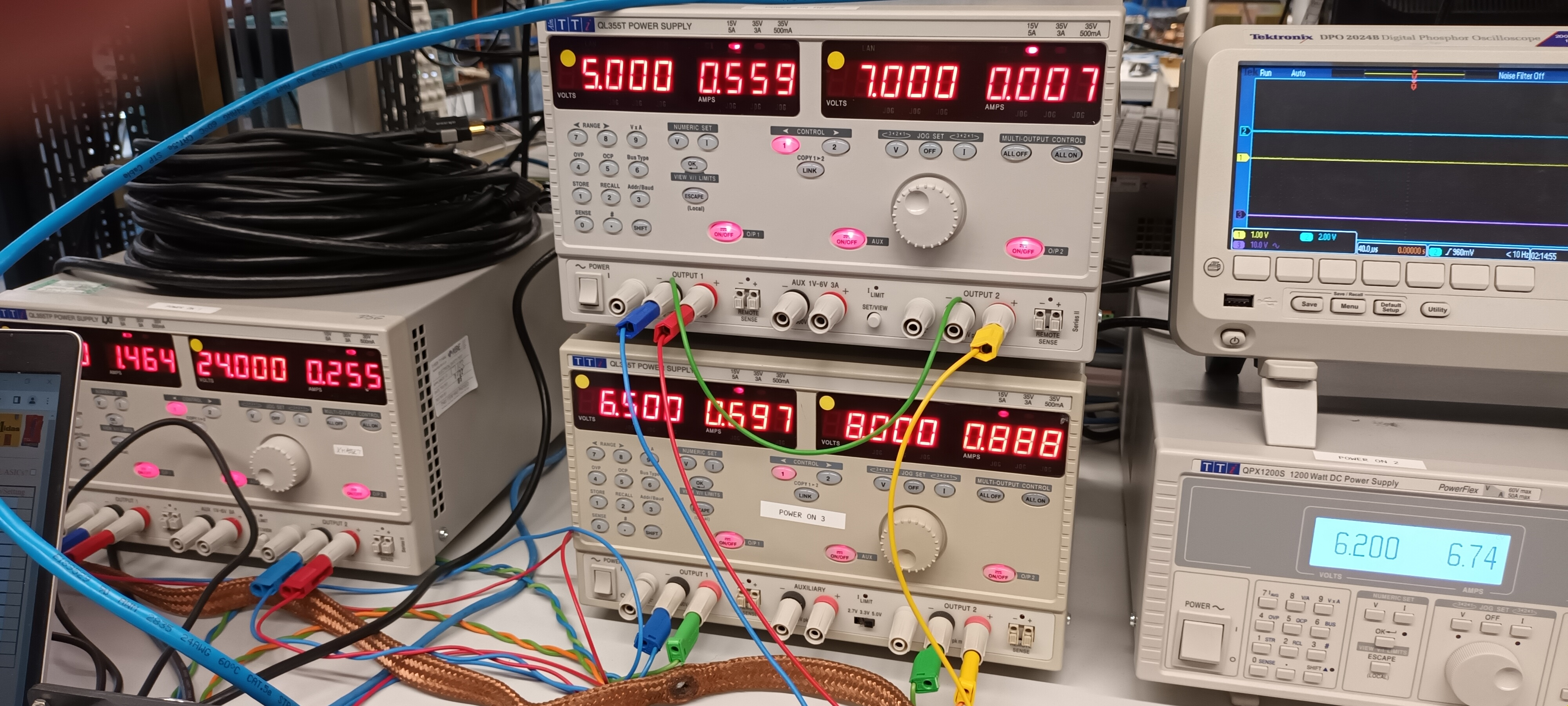

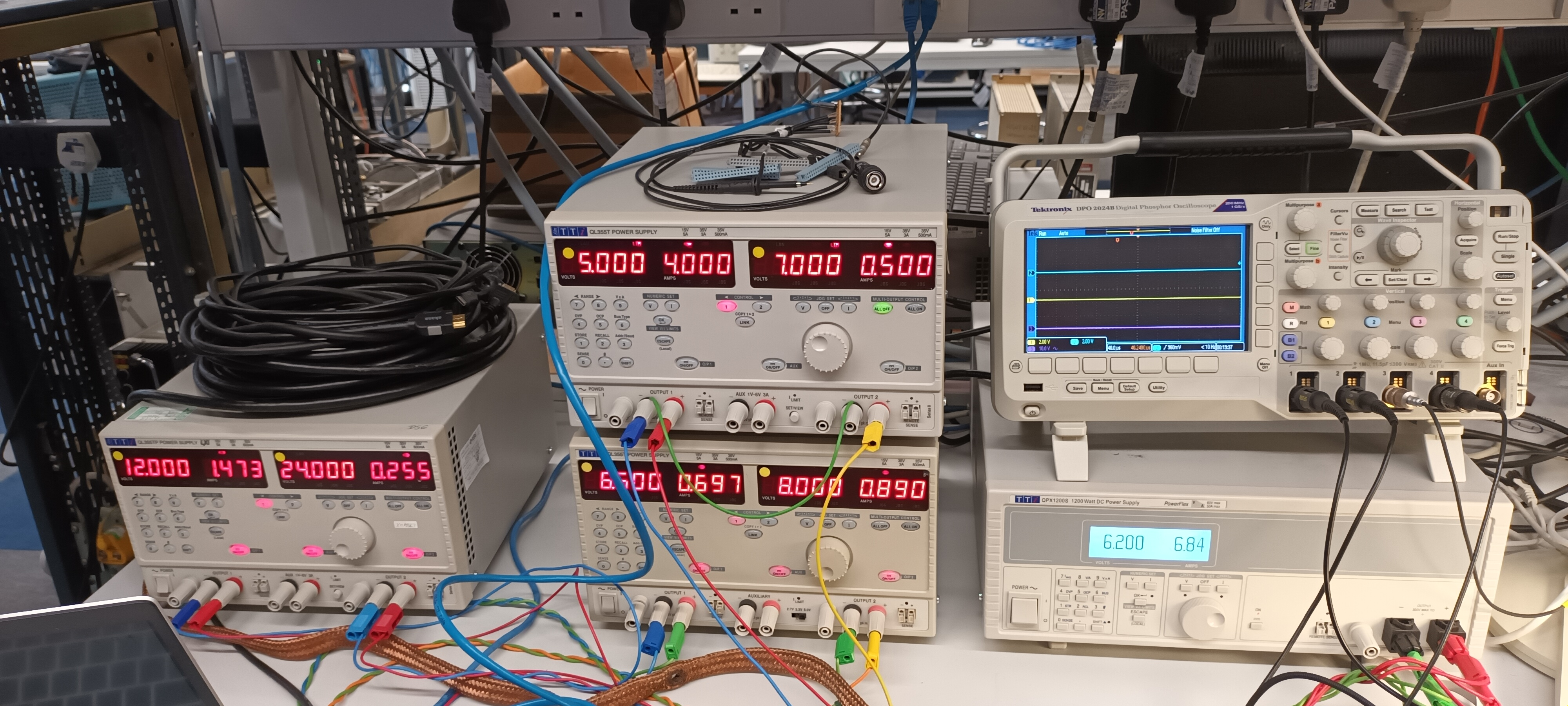

Attachments 2 & 7 AIDA FEE64 mezzanine with

1) adaptor PCB connected to ERNI input connector

2) test PCB to provide power & control to FEE64 mezzanine

plus probe points for (per ASIC) Data Ready, A0-A3, MUX output, 16x fast comparator, 16x buffered preamp output etc.

Attachments 1, 3 & 4 AIDA FEE64 power (middle & right) and fan power (left)

N.B.

Attachment 1 - mid-upper TTi QL355T FEE64 PSU shows nominal current load ( 5V/1.672A 7V/0.031A ) for configured ASICs

Attachment 5 - AIDA FEE64 mezzanines in T9 AIDA cupboard

left - 2x boxes with U/S FEE64 mezzanines (labelled)

right - 2x boxes with bench test OK FEE64 mezzanines

bottom - untested FEE64 mezzanines

Attachment 6 - AIDA FEE64 mezzanines to be re-tested

Summary of AIDA FEE64 mezzanine bench tests (see Mezzanine logbooks for details)

Garner Osborn Batch 7226-1

9 pass

11 pass

15 fail no signals?

16 fail power?

17 fail power?

19 pass

23 pass

24 fail asic#4

27 fail power?

30 fail power?

37 pass

39 pass

40 fail power?

Batch 0213110101

26 fail asic#2

27 fail asic#3

29 pass

Batch 0216240101

8 pass

It is possible that the mezzanines have dirty electrical contacts - they should be cleaned and re-tested |

| Attachment 1: 20230215_132009.jpg

|

|

| Attachment 2: 20230215_130352.jpg

|

|

| Attachment 3: 20230216_125916.jpg

|

|

| Attachment 4: 20230215_110356.jpg

|

|

| Attachment 5: 20230217_132218.jpg

|

|

| Attachment 6: 20230217_132223.jpg

|

|

| Attachment 7: 20230216_125909.jpg

|

|

|

|

176

|

Thu Mar 10 16:35:39 2016 |

TD : PJCS | Report - high - AIDA timestamps | > Version 8 firmware

>

> Analysing R37_* data files (see https://elog.ph.ed.ac.uk/AIDA/160)

>

> Usinmg MIDASsort, I generate a spectrum showing the time difference (10ns clock cycles)

> between sequential ADC data items. There is an offset of 1000.

>

> I observe peaks at 1000, 1200, 1400 etc - as expected

>

> I also observe peaks at +/-10 clock cycles relative to these main peaks - not expected

>

> I also observe some discrete intermediate peaks - not expected

I have investigated this timing using a sort program and R37_0.

If I only work with data from one module there is no problem. Peaks in the time difference spectrum are the

expected 200 apart.

If I then include a second module's ADC data the time difference spectrum starts to look as the one Tom attached

but with a fixed 45 ticks offset from the '200' peaks.

I conclude the spectra appearance is due to the 500KHz ASIC readout clocks not being synchronized between the

different FEE64 modules. |

| Attachment 1: Time_Difference_FEE13to14.png

|

|

|

|

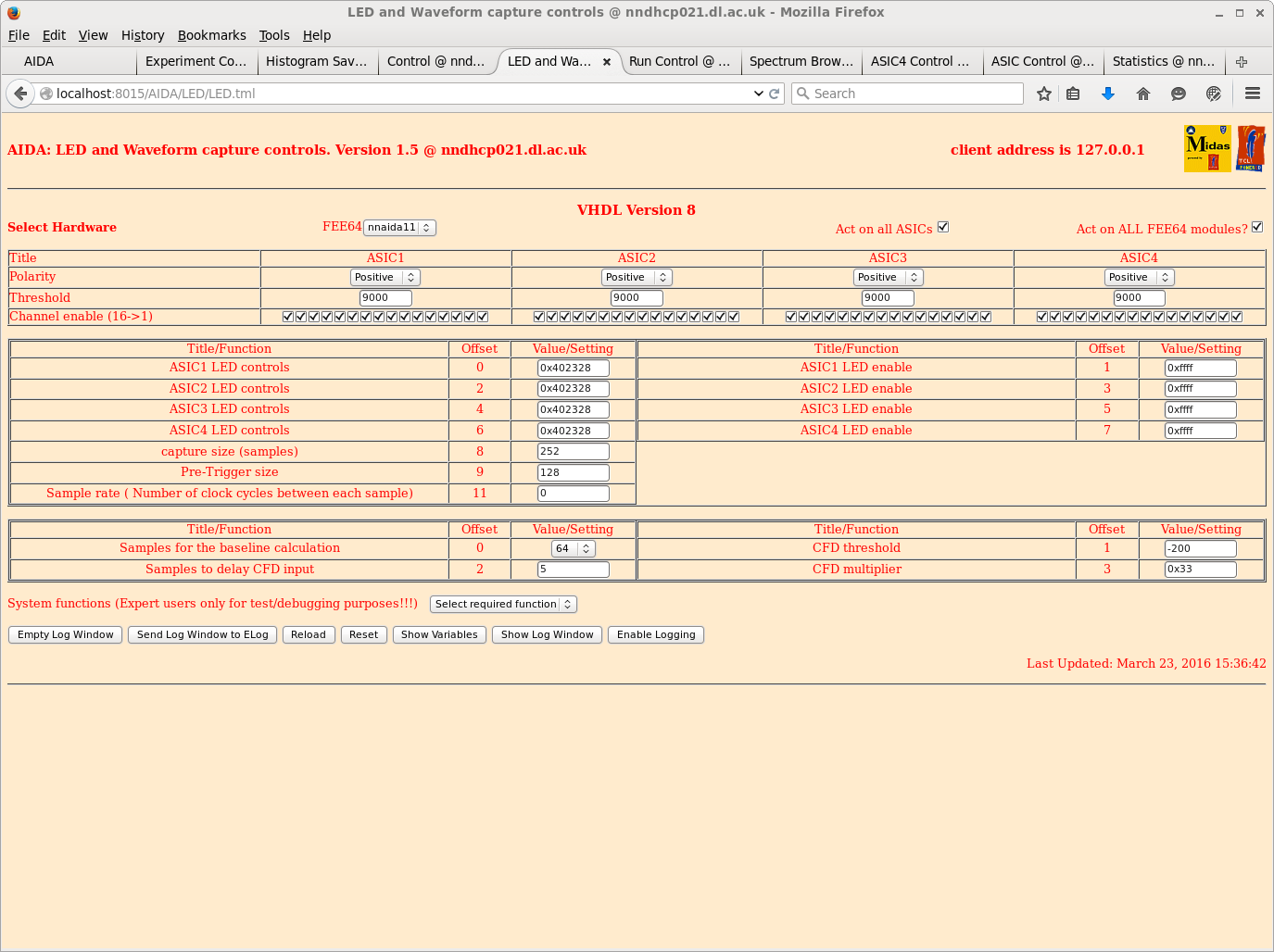

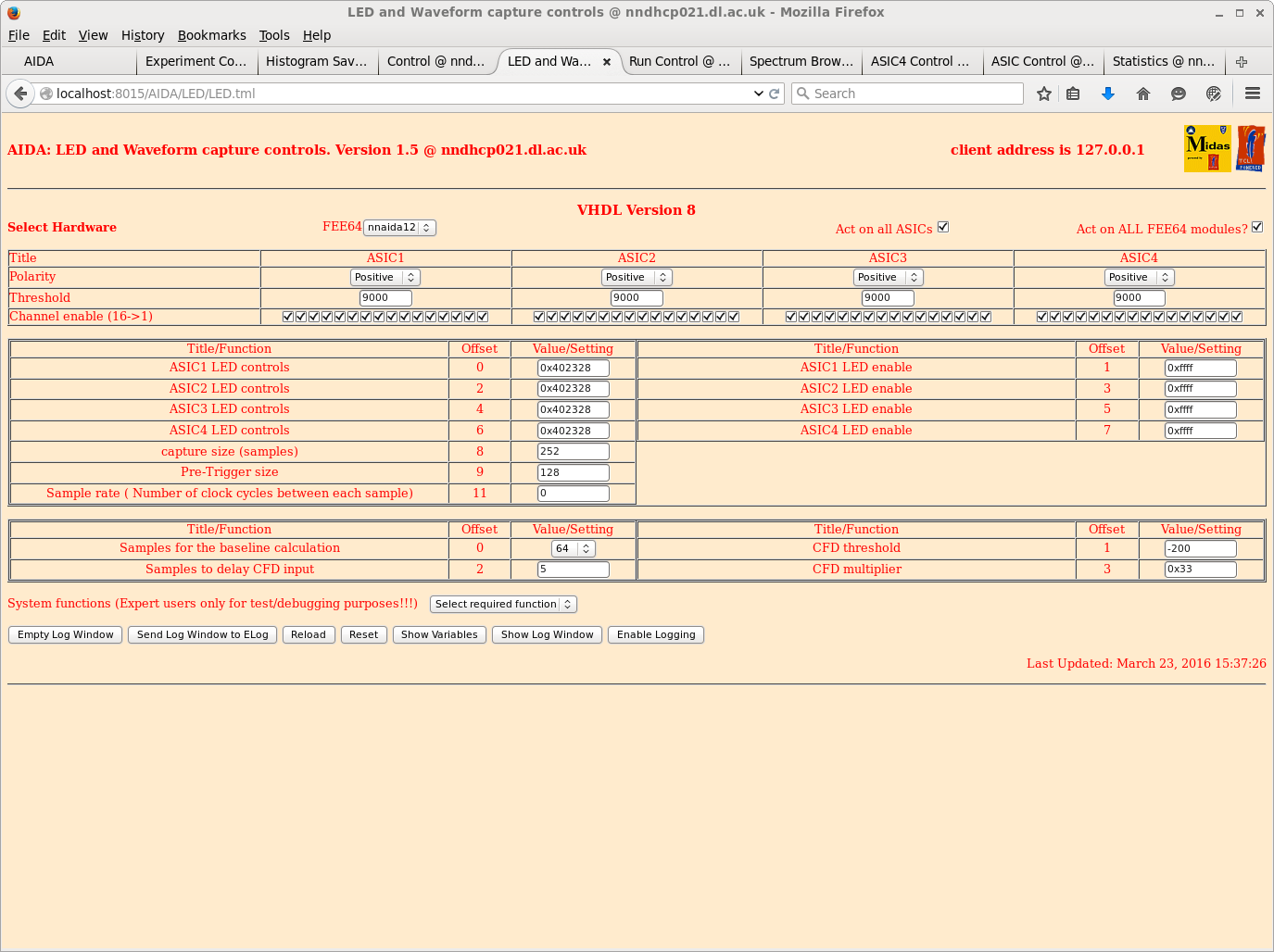

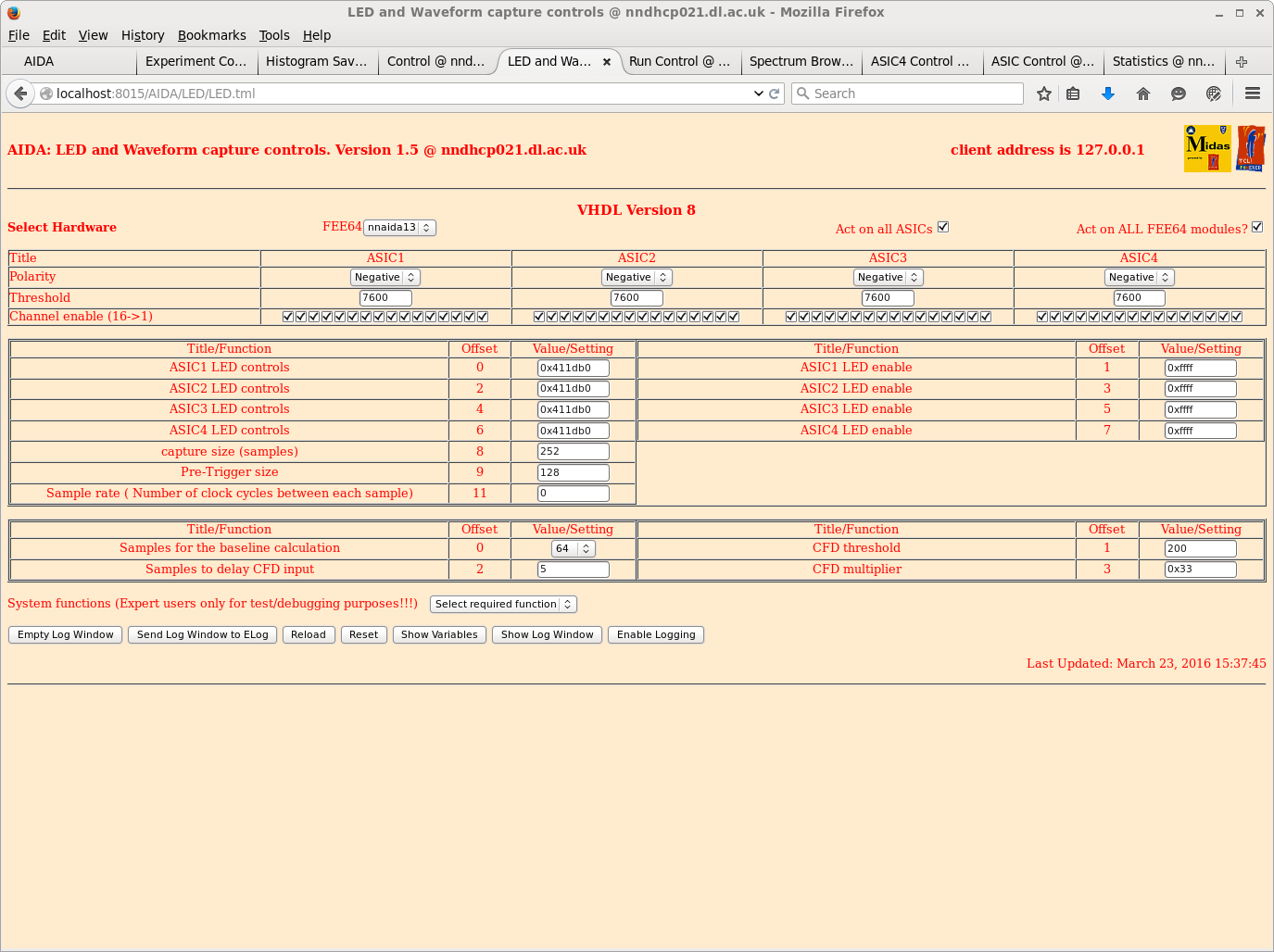

182

|

Tue Mar 22 10:59:52 2016 |

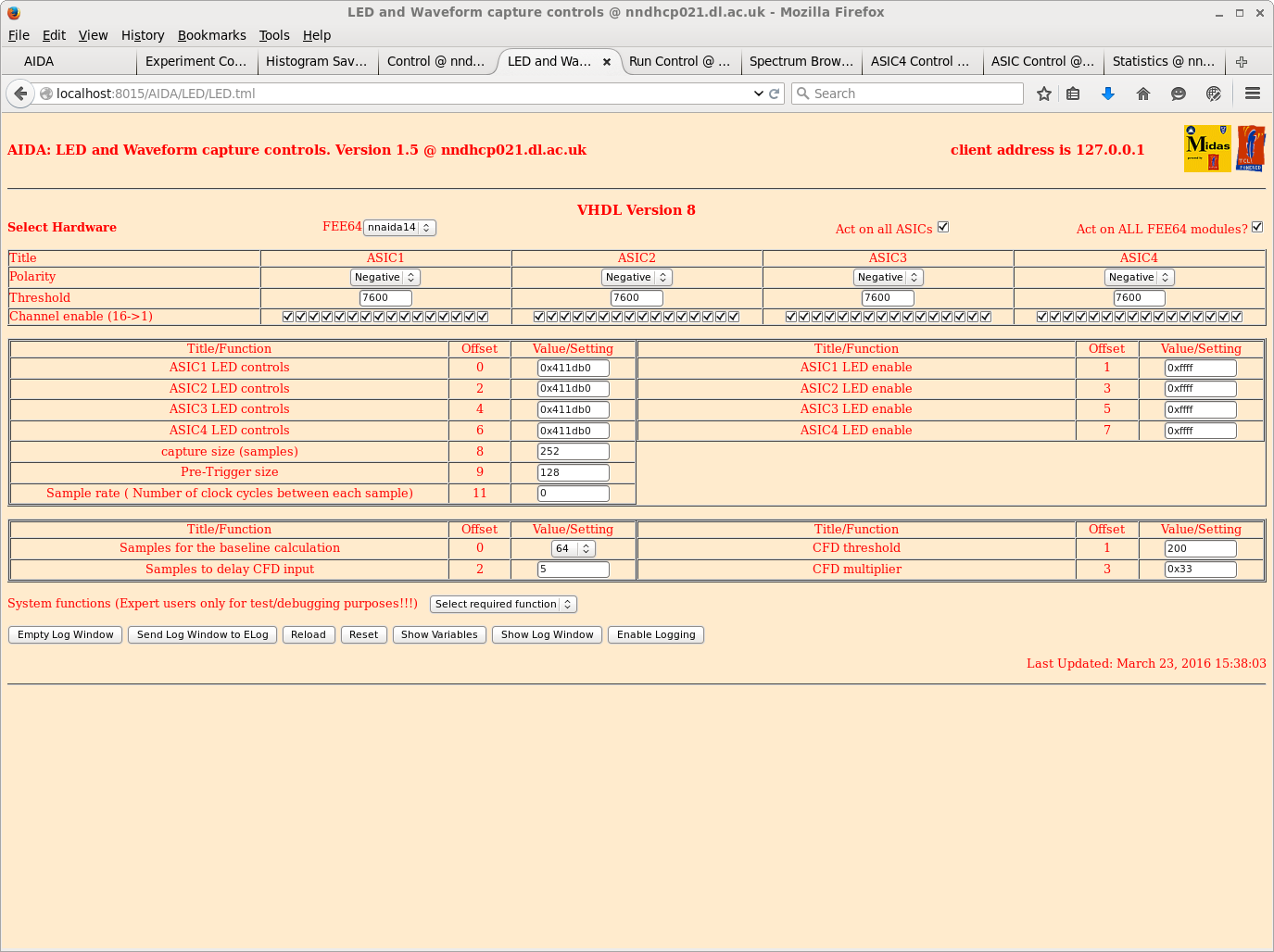

TD : PJCS | Tuesday 22 March | MSL type BB18(DS)-1000 serial 2998-22

Bias +200V, I_L +=5.515uA, ambient temperature +19.8 deg C

DSSSD - AIDA adaptor PCB cabling

4 off LH Coupler (Kapton PCB, 5cm), 2x 34-way Samtec ribbon cable (45cm), RH coupler(Kapton PCB, 10cm)

+ 3M 1245 1.4mil copper foil screen ribbon cables + RH coupler only (i.e. not LH coupler)

+ drain wires -> gold-plated Lemo-00 test input connectors

nnaida 11 & 12 AIDA adaptor PCB rev B

nnaida 13 & 14 AIDA adaptor PCB rev C (LK1 fitted)

ground links LK3 & LK7 fitted to nnaida11-14 AIDA adaptor PCBs

Heavy duty copper cable connects copper front end frames of FEE modules

Nitto 5011N conductive gasket between FEE module and front end frames

Standard ASIC settings

nnaida 11 & 12 - negative input

nnaida 13 & 14 - positive input

Pulser BNC PB-5

Fall time 1.0ms

Rate 100Hz

Delay 250ns

Ampl 5.00000V

Polarity +

Pulse top Tail

Atten 10x

Clamp ON

- polarity via Cooknell SA1 Summing Amplifier

207Bi source, approx centred on DSSSD, approx 3cm from DSSSD

AIDA FEE firmware version 8

+ sync 500kHz ASIC clock

File R53

shaping time 8uS

slow comparator 10 (dec)

LEC/MEC fast comparator 16 (dec)

start: 10.50 stop: 13.30 23.3.16

spectra saved to disk 14.30 (BST) (sic)

Pulser OFF

nnaida 11 disc # 55 disabled

12 disc # 2 & 55 disabled

13 & 14 *no* discs disabled

nnaida14 sampling ADCs not calibrated for previous run *but* no wavfeform data streams enabled so not a

problem

new PCS diagnostics indicate FEE ASIC clocks aligned & synchronised - check!

File R53

shaping time 8uS

slow comparator 10 (dec)

LEC/MEC fast comparator 10 (dec)

start: 14.30 23.3.16 stop:

spectra saved to disk

Pulser OFF

nnaida 11 disc # 55 disabled

12 disc # 2 & 55 disabled

13 & 14 *no* discs disabled

nnaida11, 12, 13 & 14 waveforms & verniers enabled - see attachments 1-7

(data queue for nnaida12 waveforms & verniers disabled to avoid problems merger even though nnaida

produces WAVE SYNCs)

R54 stopped at 16:54. disc full. |

| Attachment 1: 20.png

|

|

| Attachment 2: 21.png

|

|

| Attachment 3: 22.png

|

|

| Attachment 4: 23.png

|

|

| Attachment 5: 24.png

|

|

| Attachment 6: 25.png

|

|

| Attachment 7: 26.png

|

|

|

|

267

|

Wed Jun 1 09:00:13 2016 |

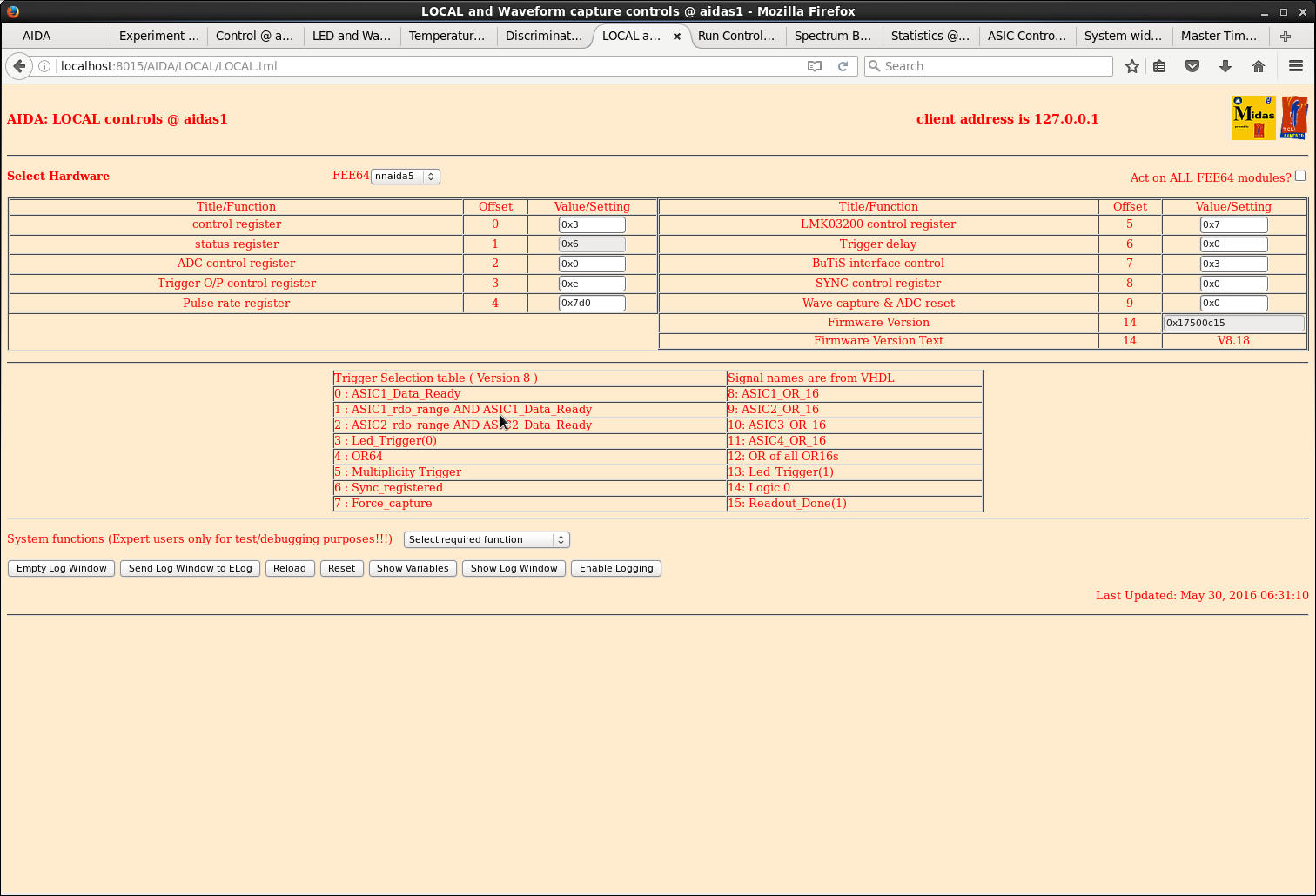

TD - Reply PJCS | Wednesday 1 June 2016 | > 09.30 Detector biases and leakage currents - ambient temp +24.9 deg C - attachments 1-2

>

> 10.08 Connection lost to nnaida27 and nnaida28

> Most recent save of settings DB key 2016May31-23.32.46

>

> 12.00 Replaced nnaida17 & nnaida18 with FEE module previously used for nnaida31 & nnaida32

>

> Pulser walkthrough

>

> BNC PB-4 settings

>

> 90,000 - 10,000 @ 10,000 step

> x5 attenuator (was x10 previously)

> t_r = 50ns tau_d = 50us

> polarity -

> rate ~ 150Hz

> INT, delay MIN

>

> polarity + by EG&G Ortec 433A

>

> N.B. - polarity terminated at end of AIDA adaptor chain, + polarity not terminated

>

> Spectra saved 12.32 ( to directories tagged around June 1, 2016 05.29 )

>

> BNC PB4 pulser rate set to ~5Hz

>

> 207Bi source at front of snout and 2x 60Co sources above DSSD3

>

> 14.00 Rebooted aidas1 to cleanup merge

>

> Changed config to 24 FEE64s

>

> Clock issues with nnaida23 - clock not locked status 0x6 - see attachments 3-9

Check the Local Controls for the setting of the LMK3200 control rgister.

If you recall from the problem with nnaida5 the value should be 0xB.

If the clock still doesn't lock then maybe it's an HDMI cable problem like nnaida5.

Since the other FEE64 are ok then it is likely to be just the MACB to nnaida23. |

|