| ID |

Date |

Author |

Subject |

|

568

|

Tue Apr 9 09:04:07 2024 |

TD | [How To] Remote control of BNC PB-5 |

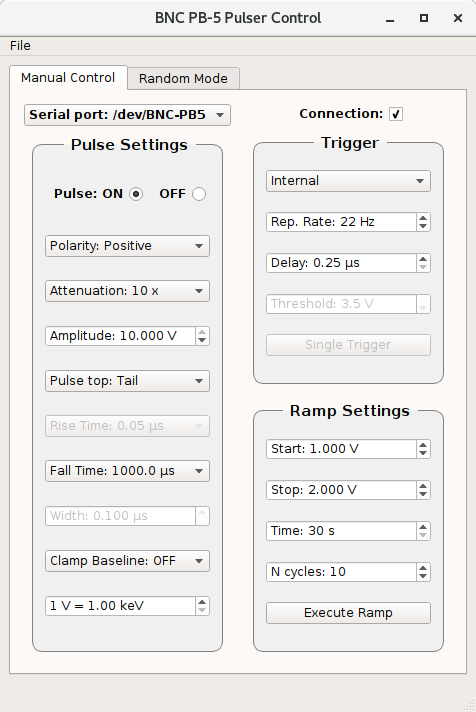

BNC PB-5 set to remote control

Login to RPi nnrpi2

ssh -X nnrpi2 -l pi

Start PB-5 app - attachment 1

./BNC-PB-5/pb5.py |

| Attachment 1: Screenshot_from_2024-04-09_10-03-42.png

|

|

|

567

|

Tue Apr 9 08:37:47 2024 |

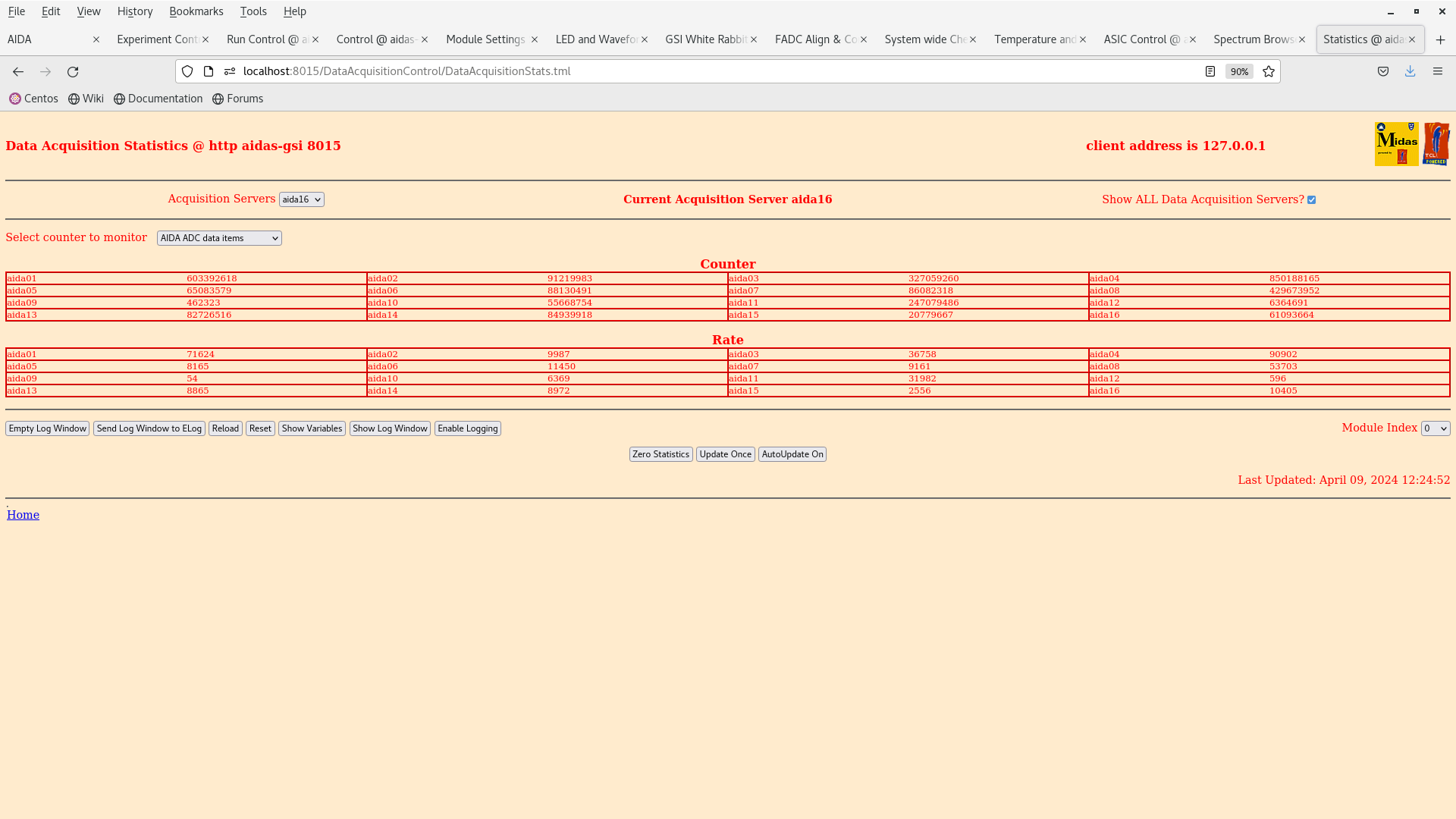

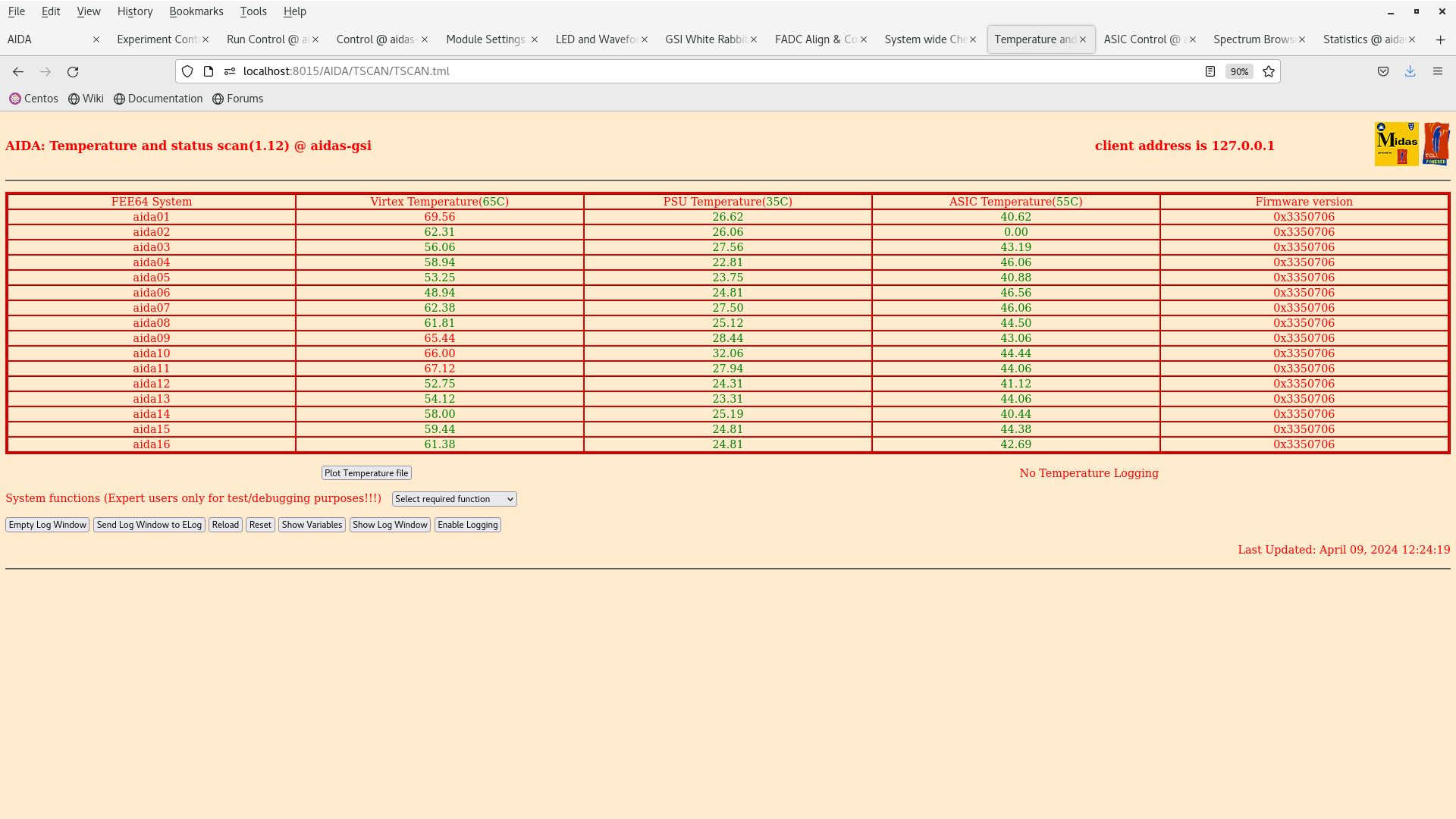

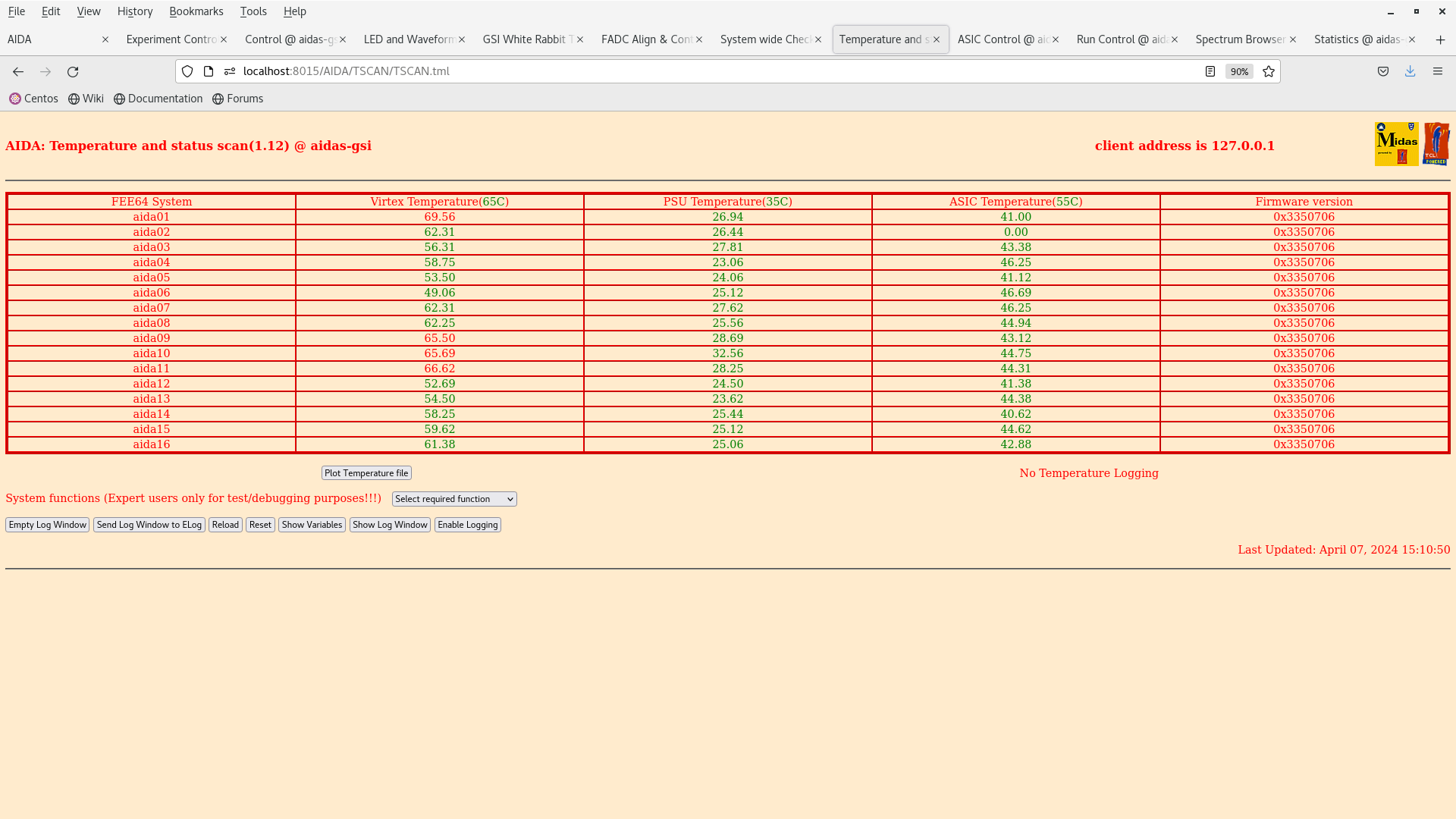

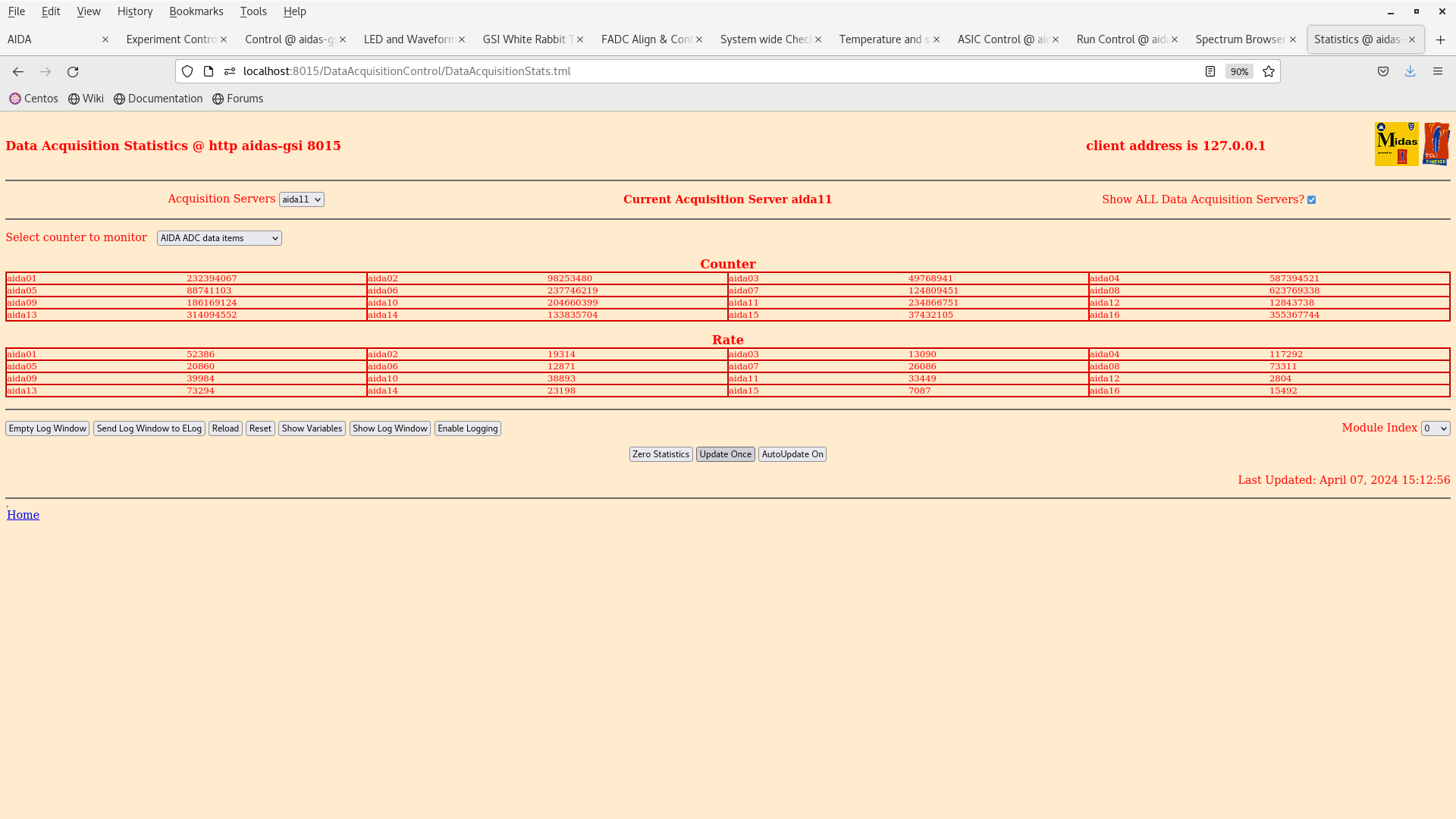

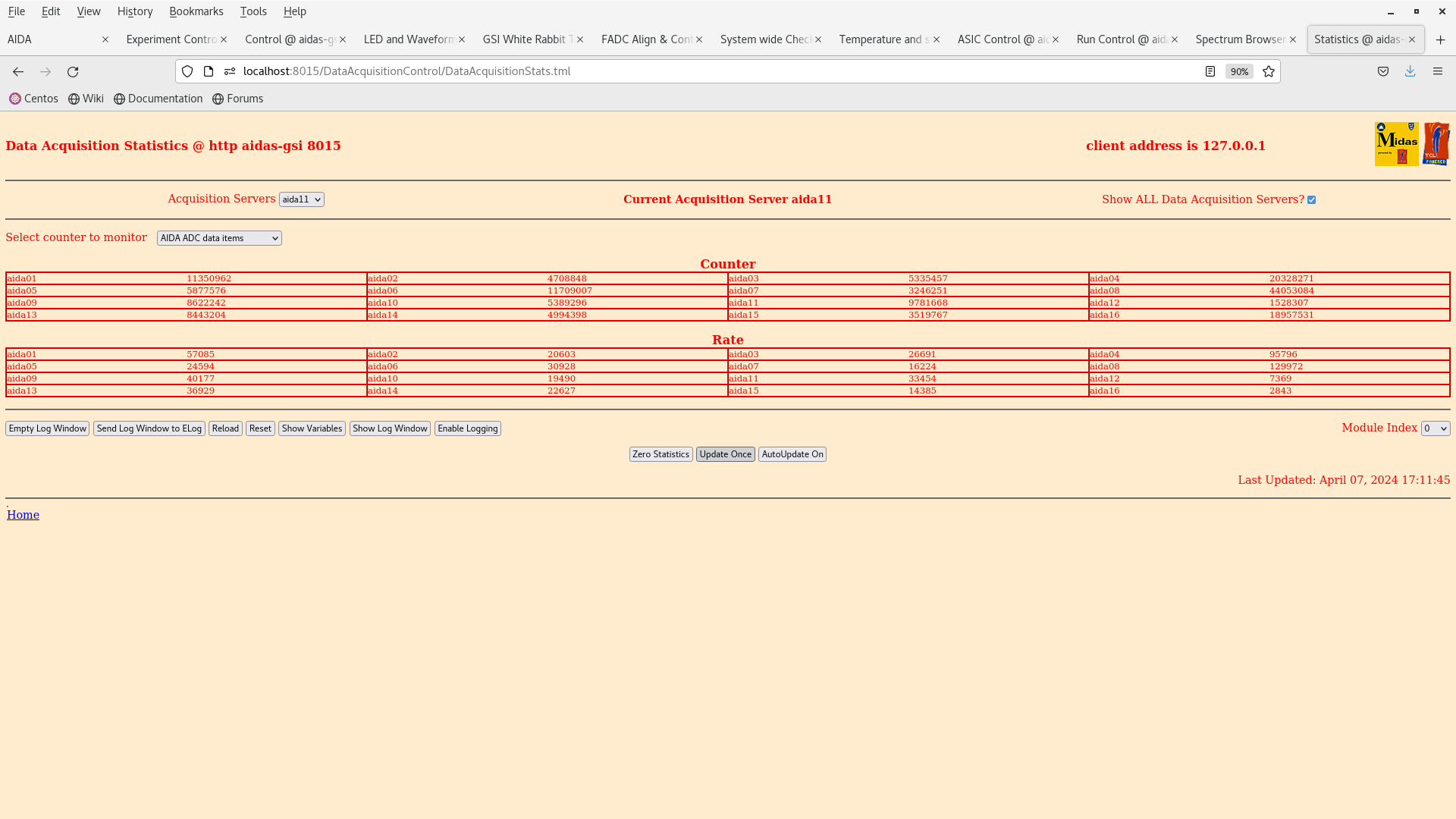

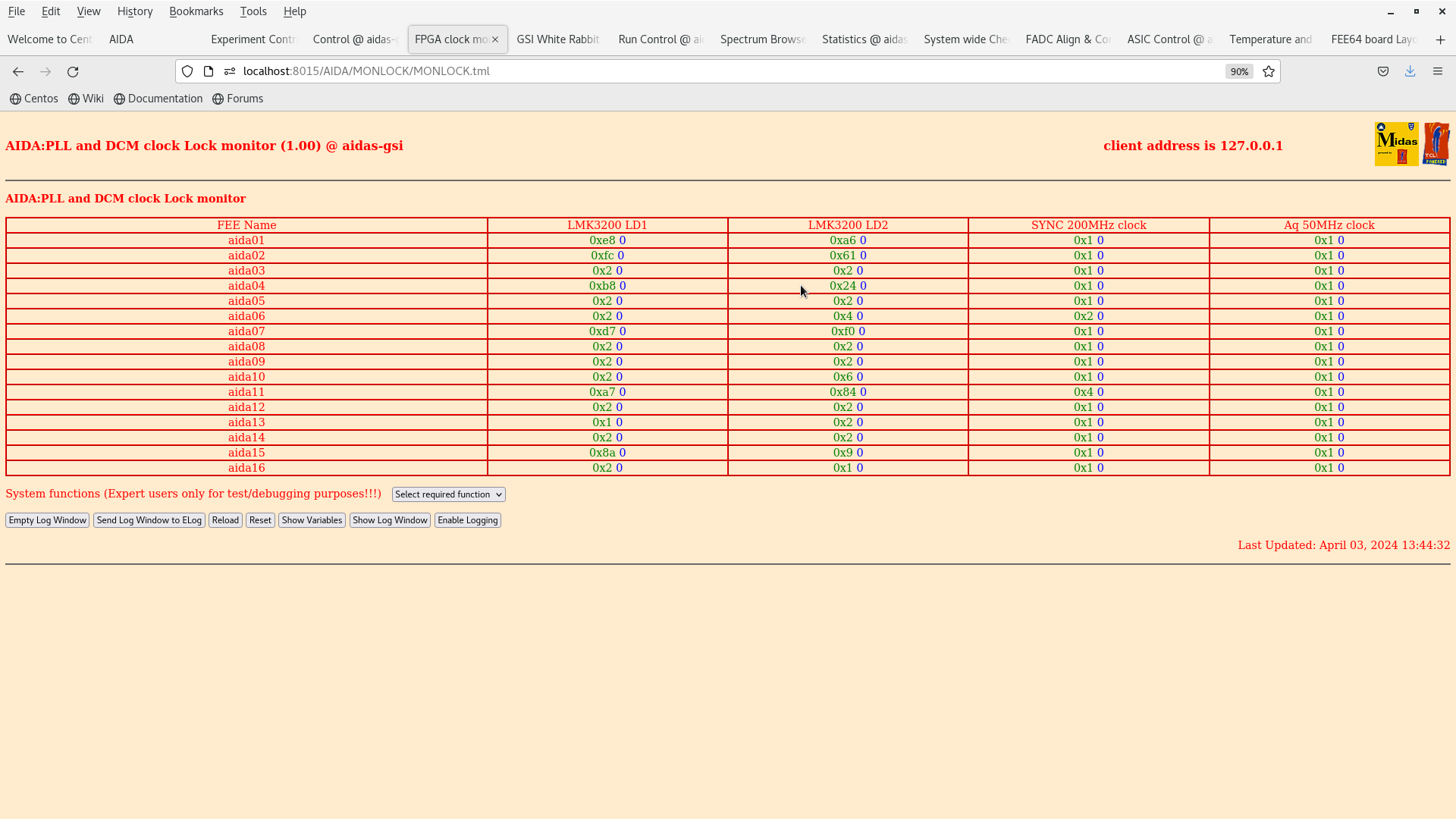

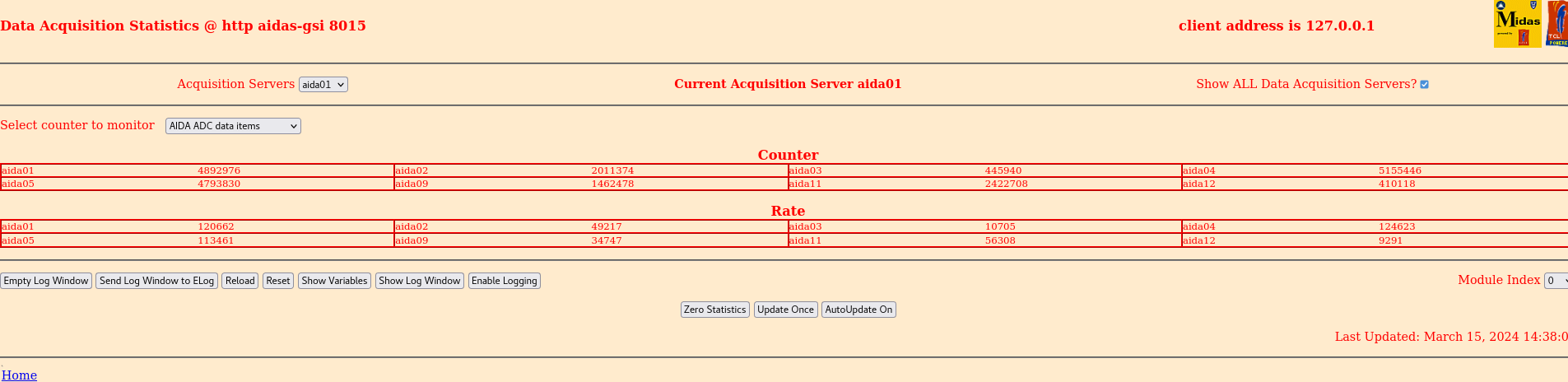

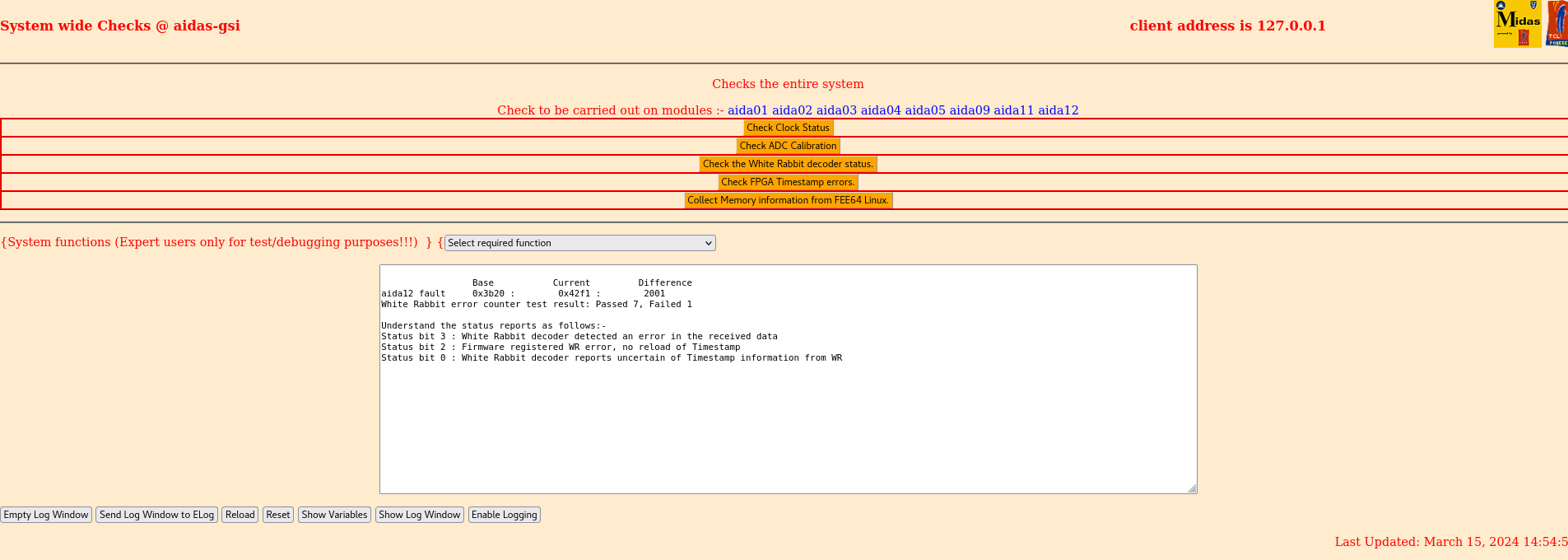

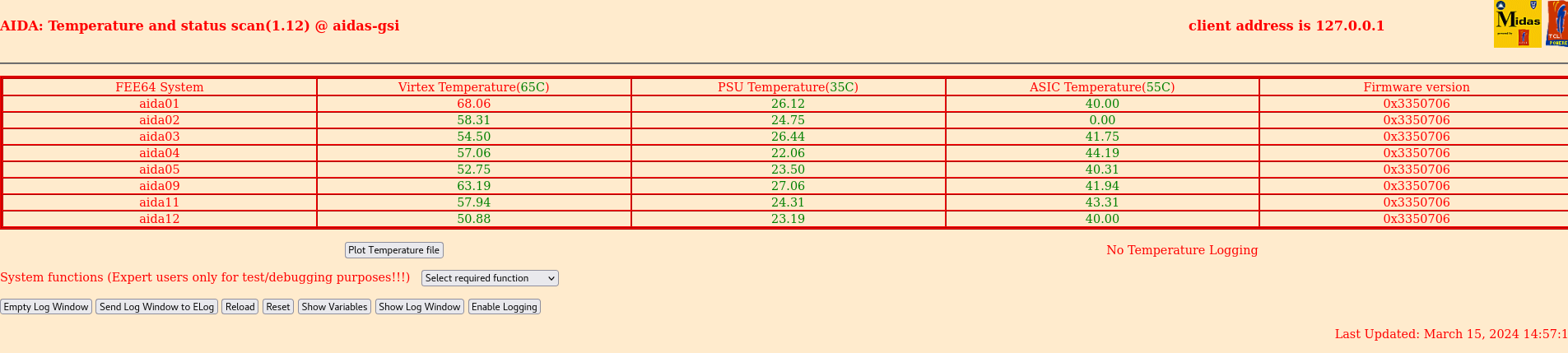

TD | Tuesday 9 April |

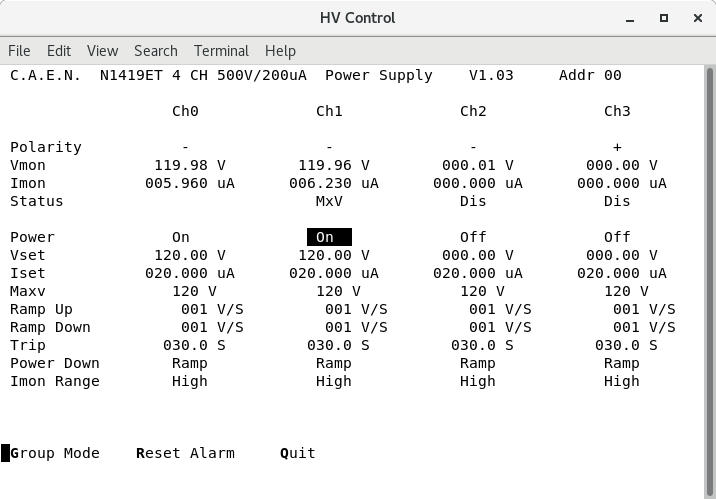

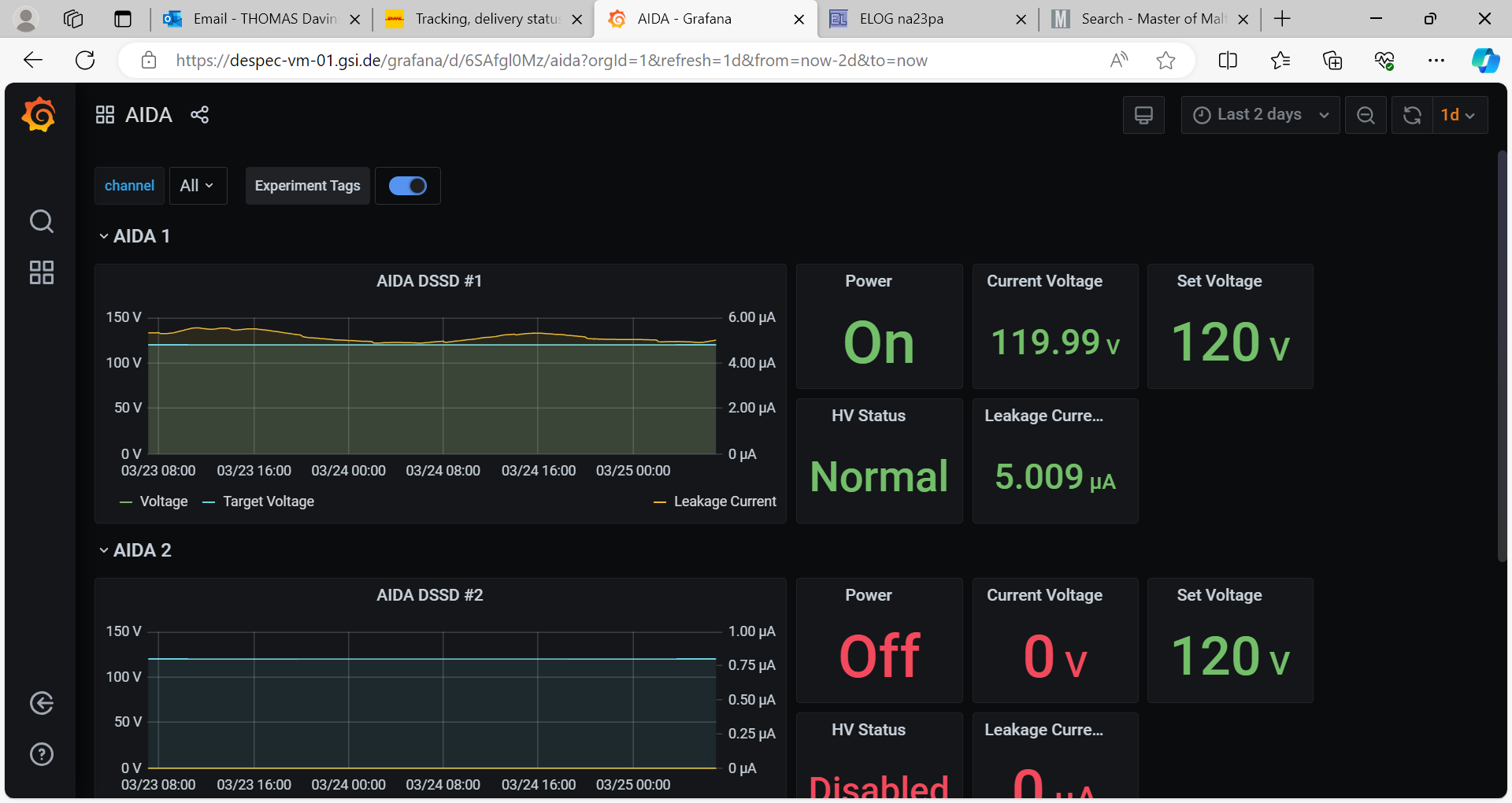

09.36 Cooling water temperature and flow OK

FEE64 power ON

DSSSD bias & leakage current OK - attachment 1

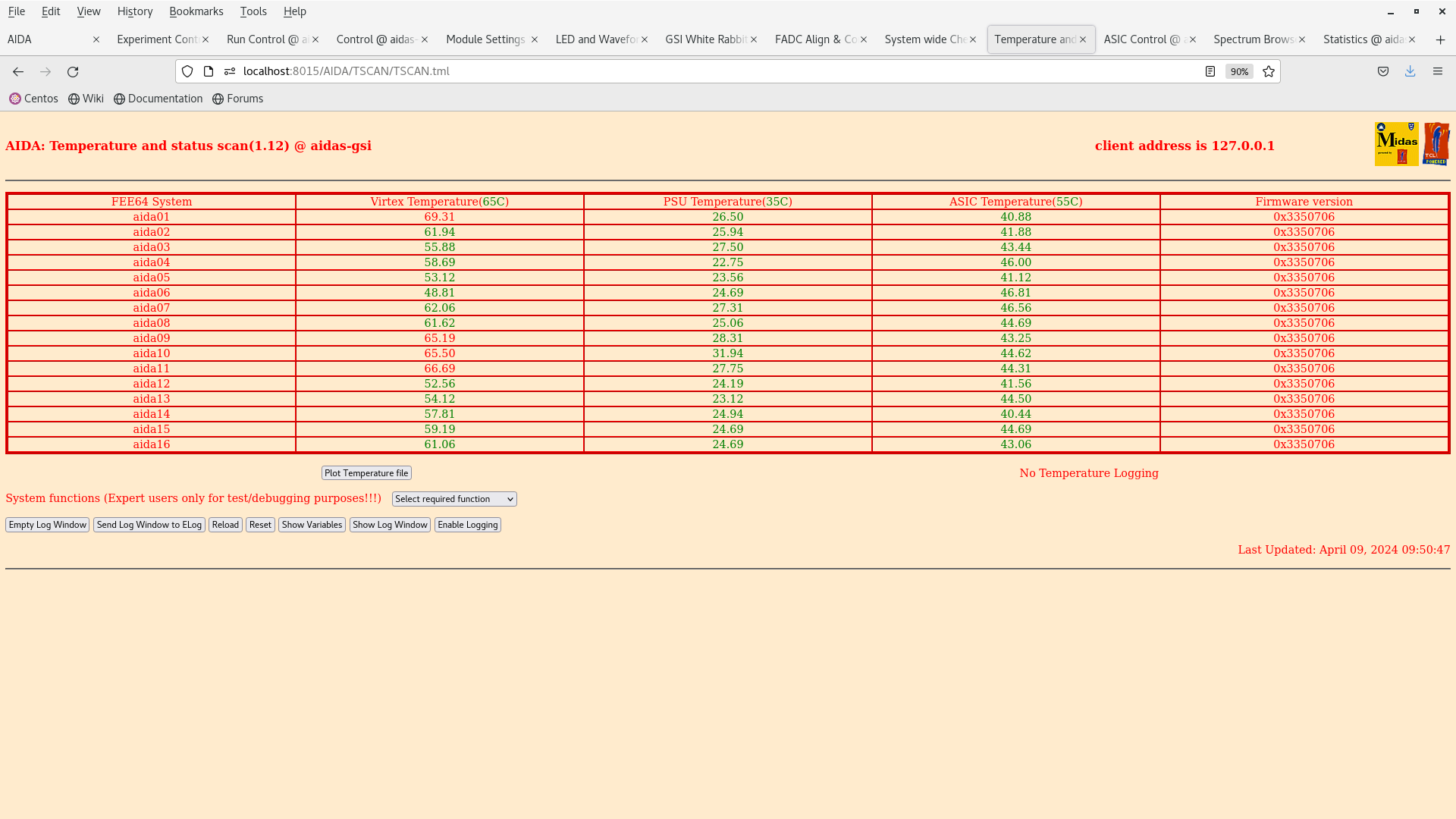

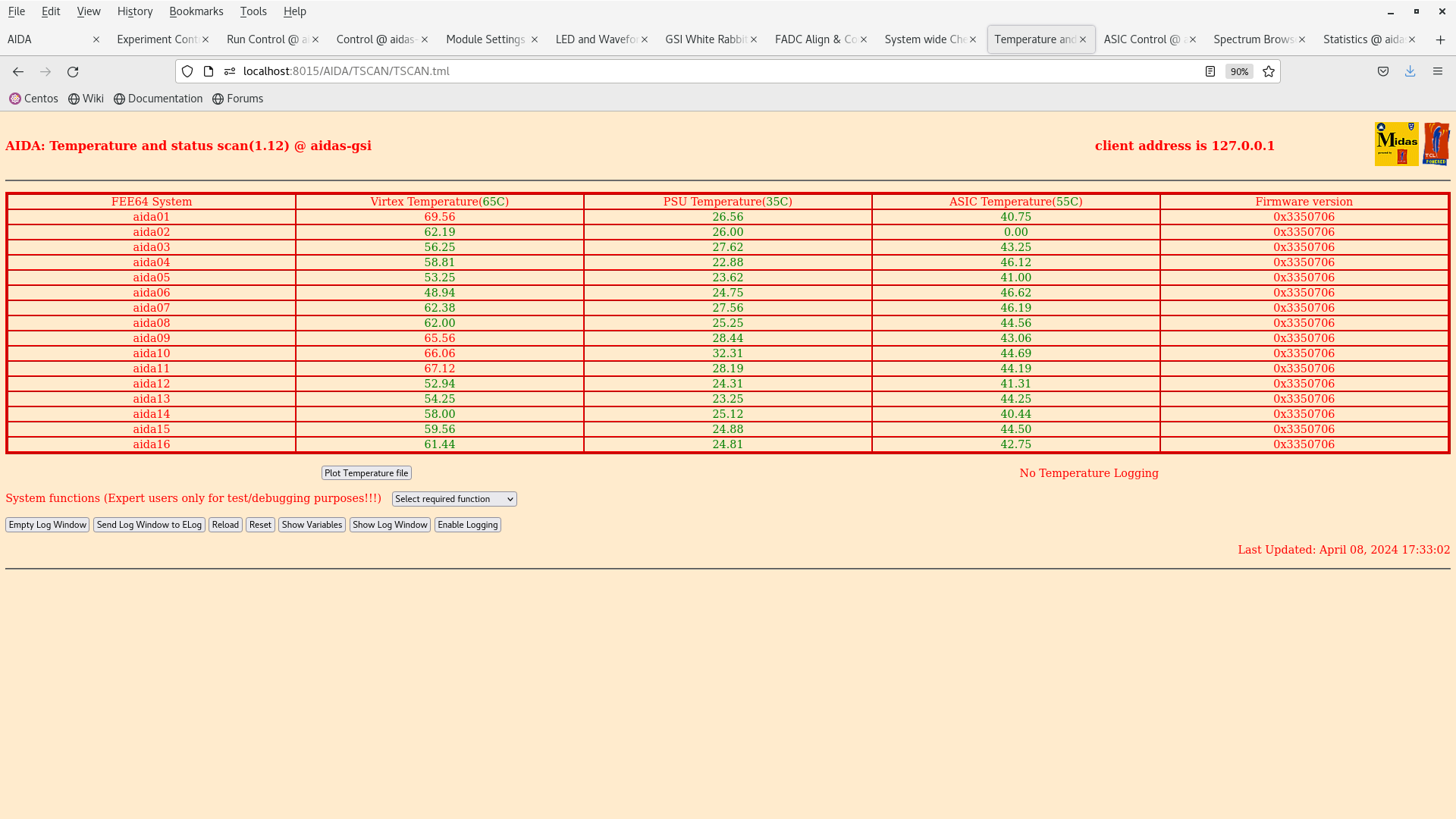

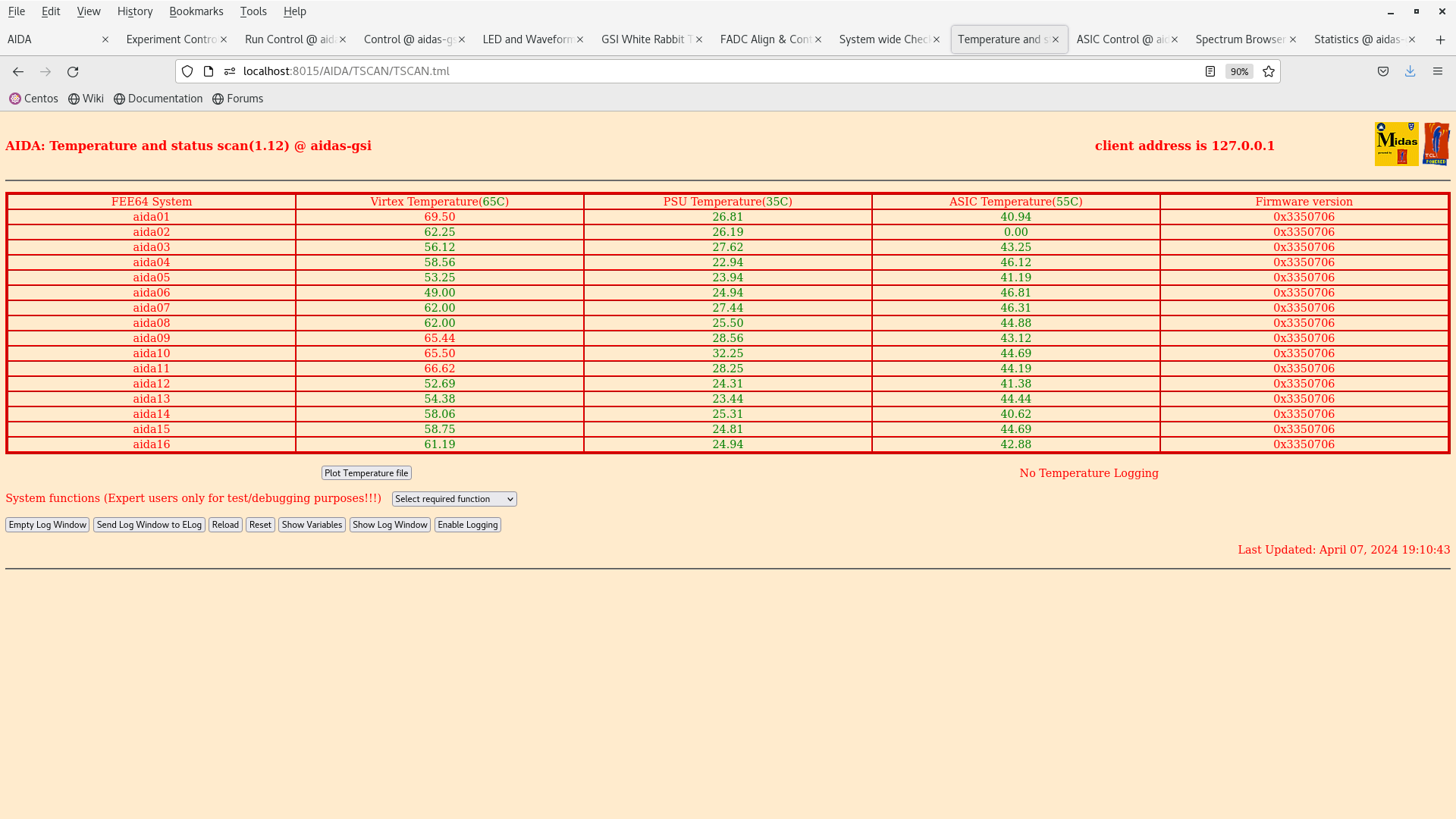

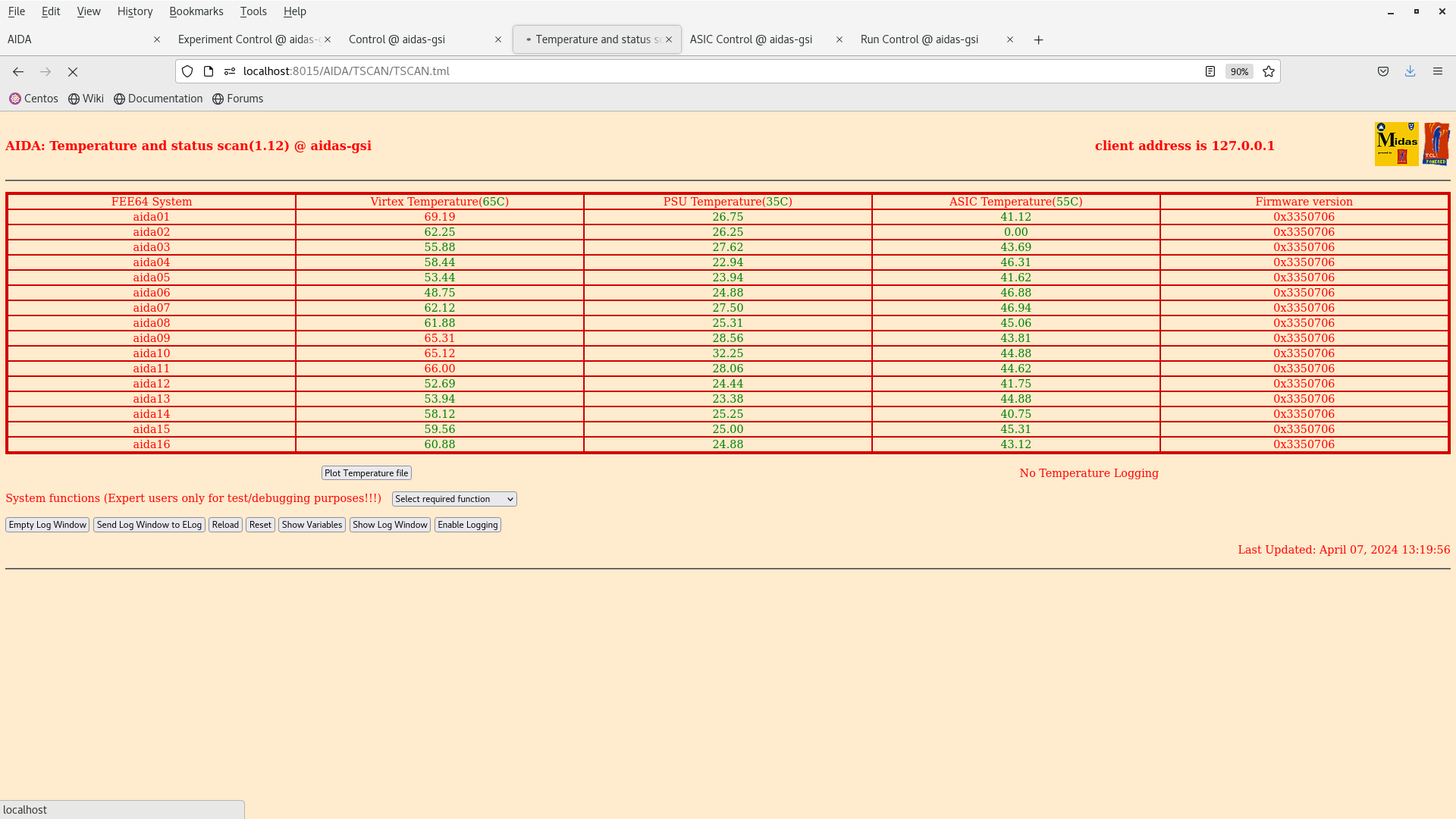

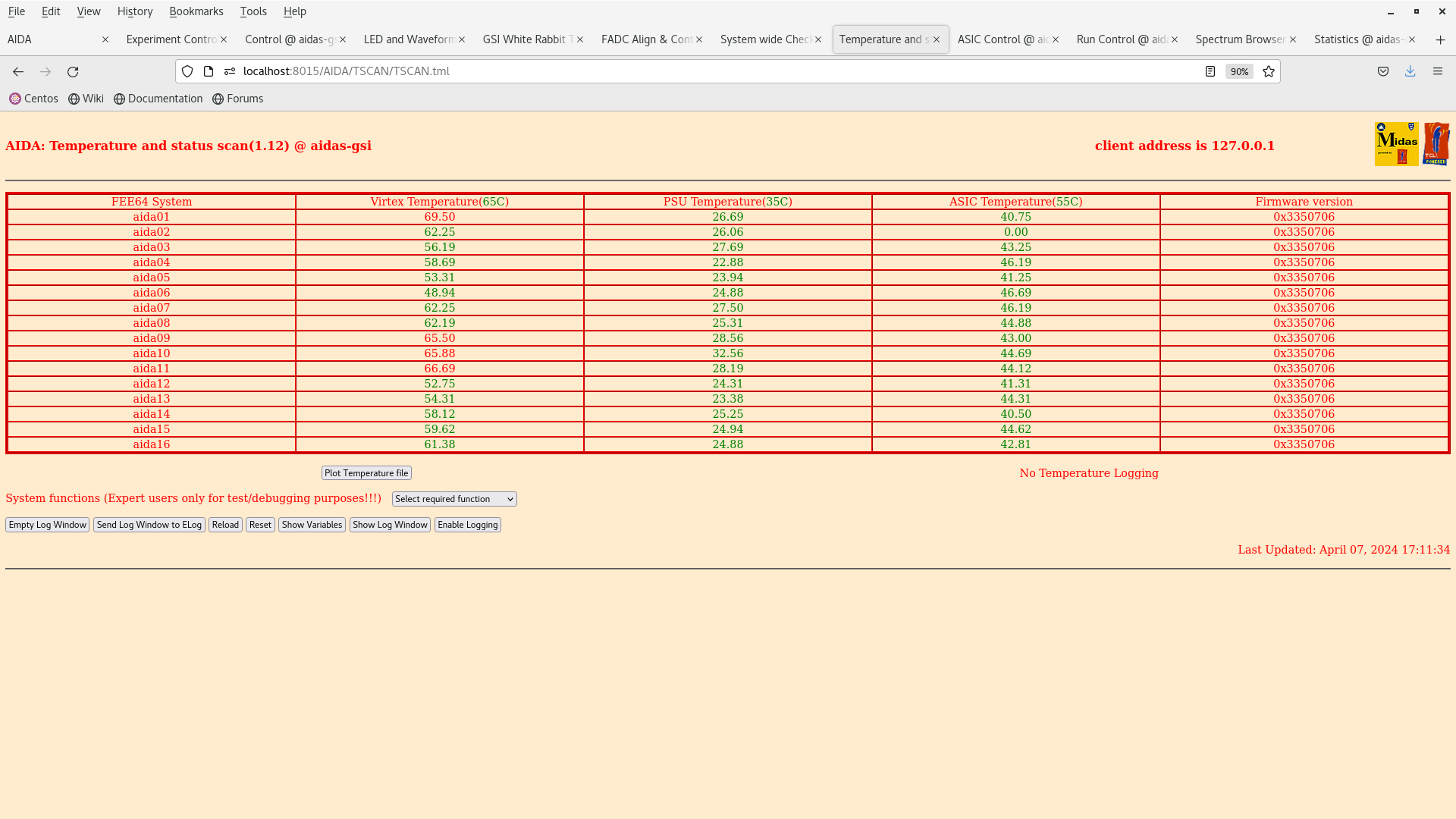

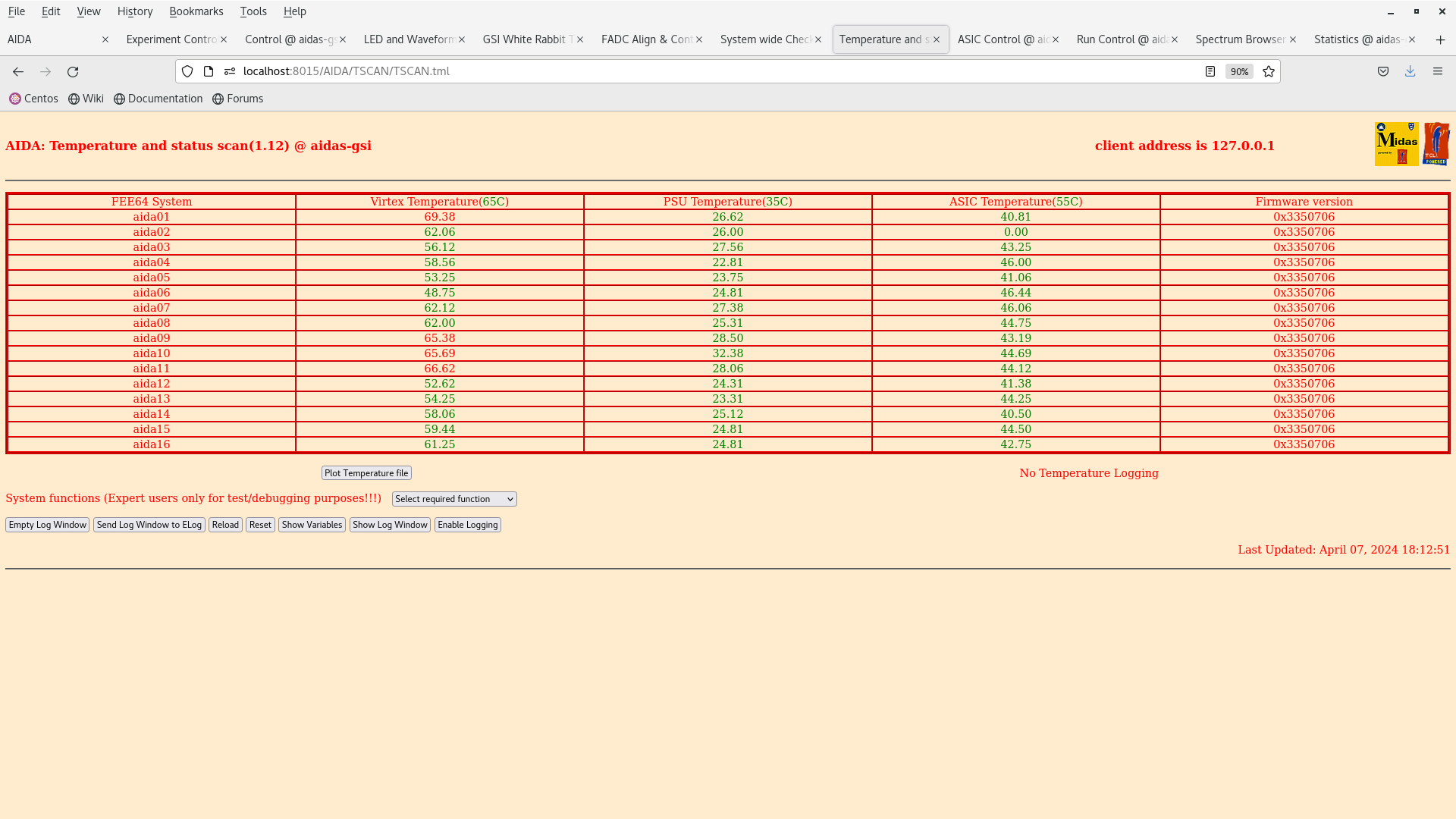

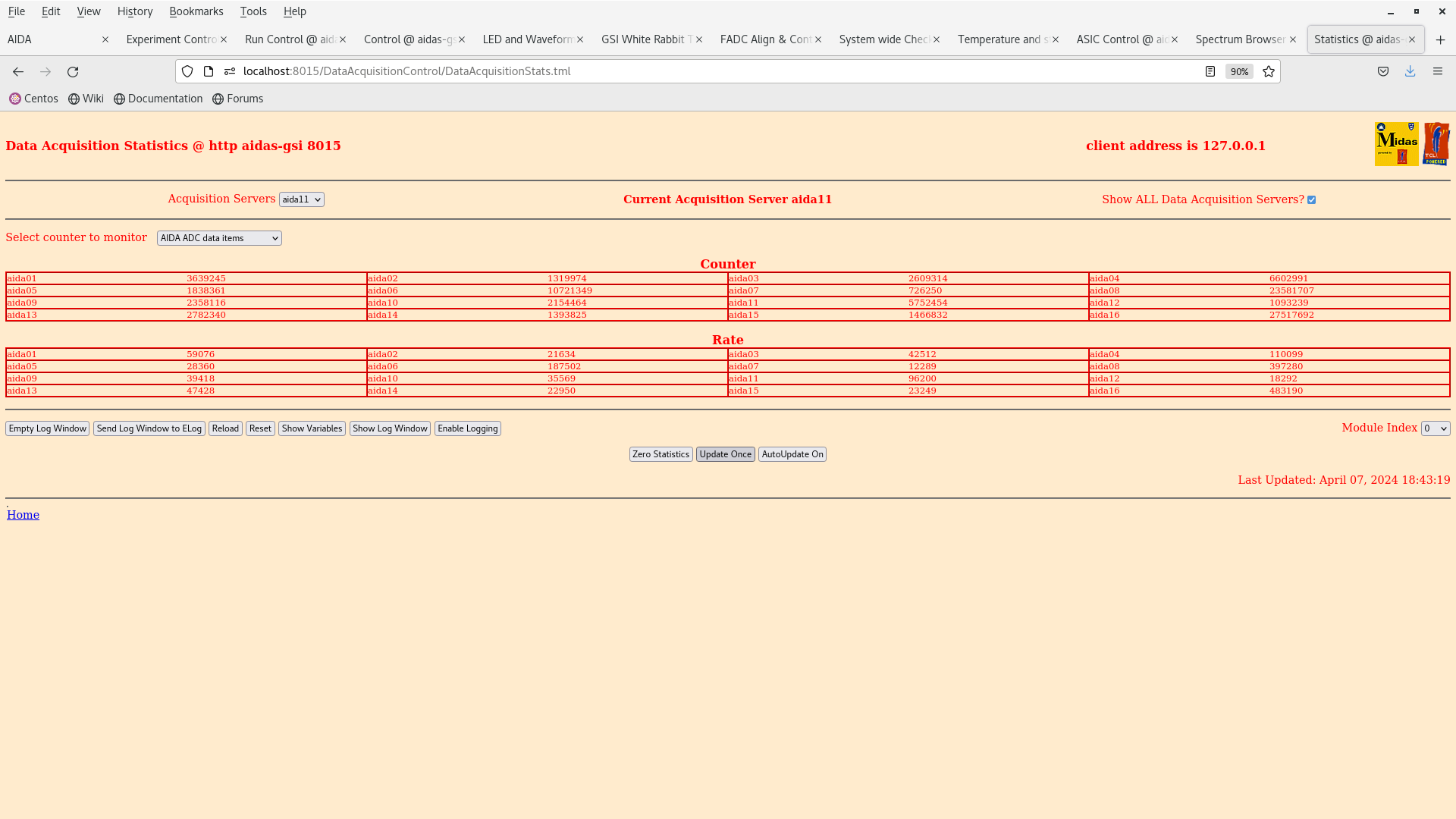

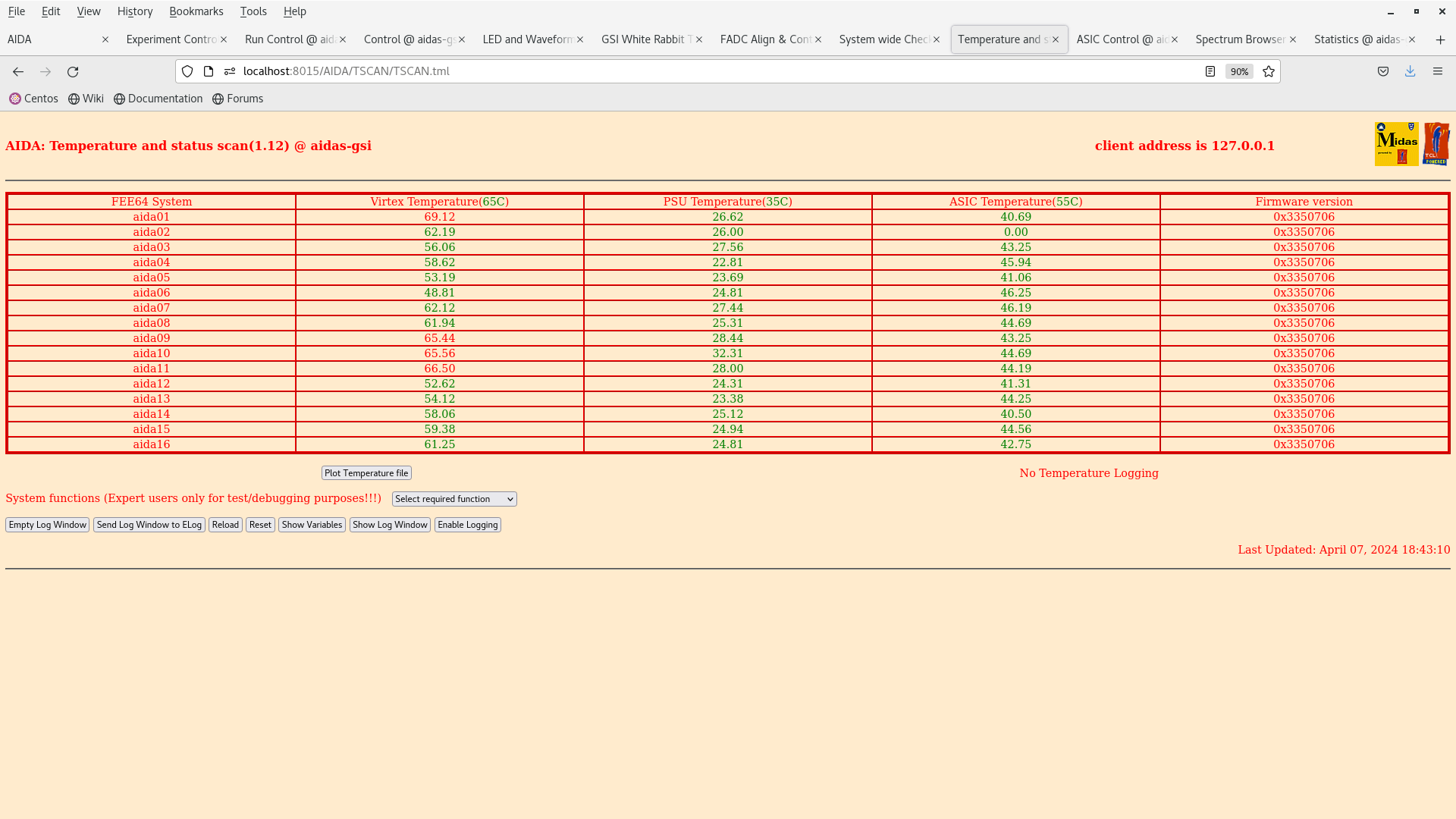

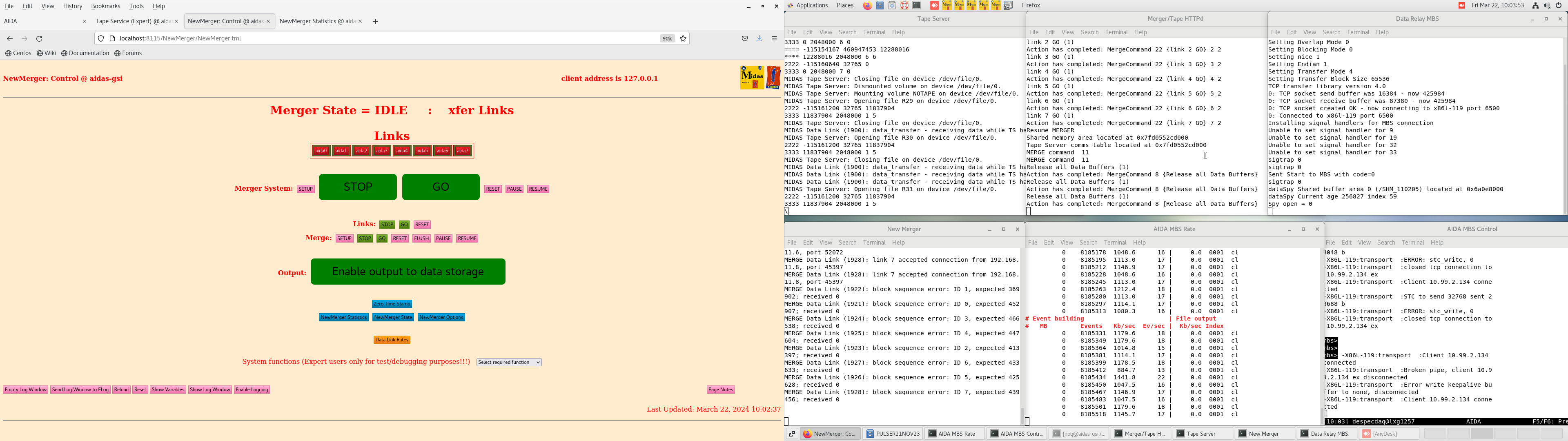

FEE64 temps OK - attachment 2

*except* aida02 ASIC temp which is known to be u/s

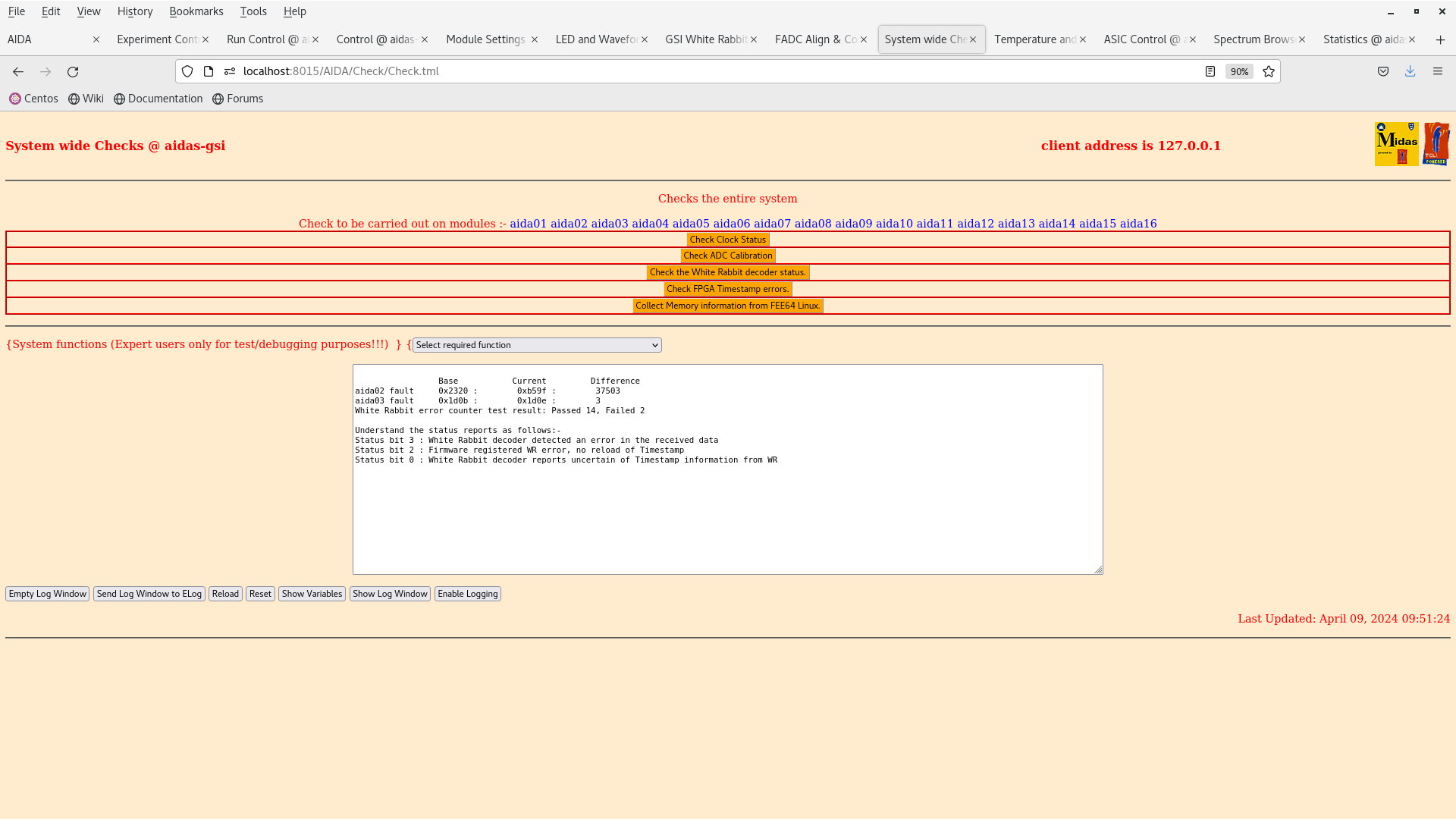

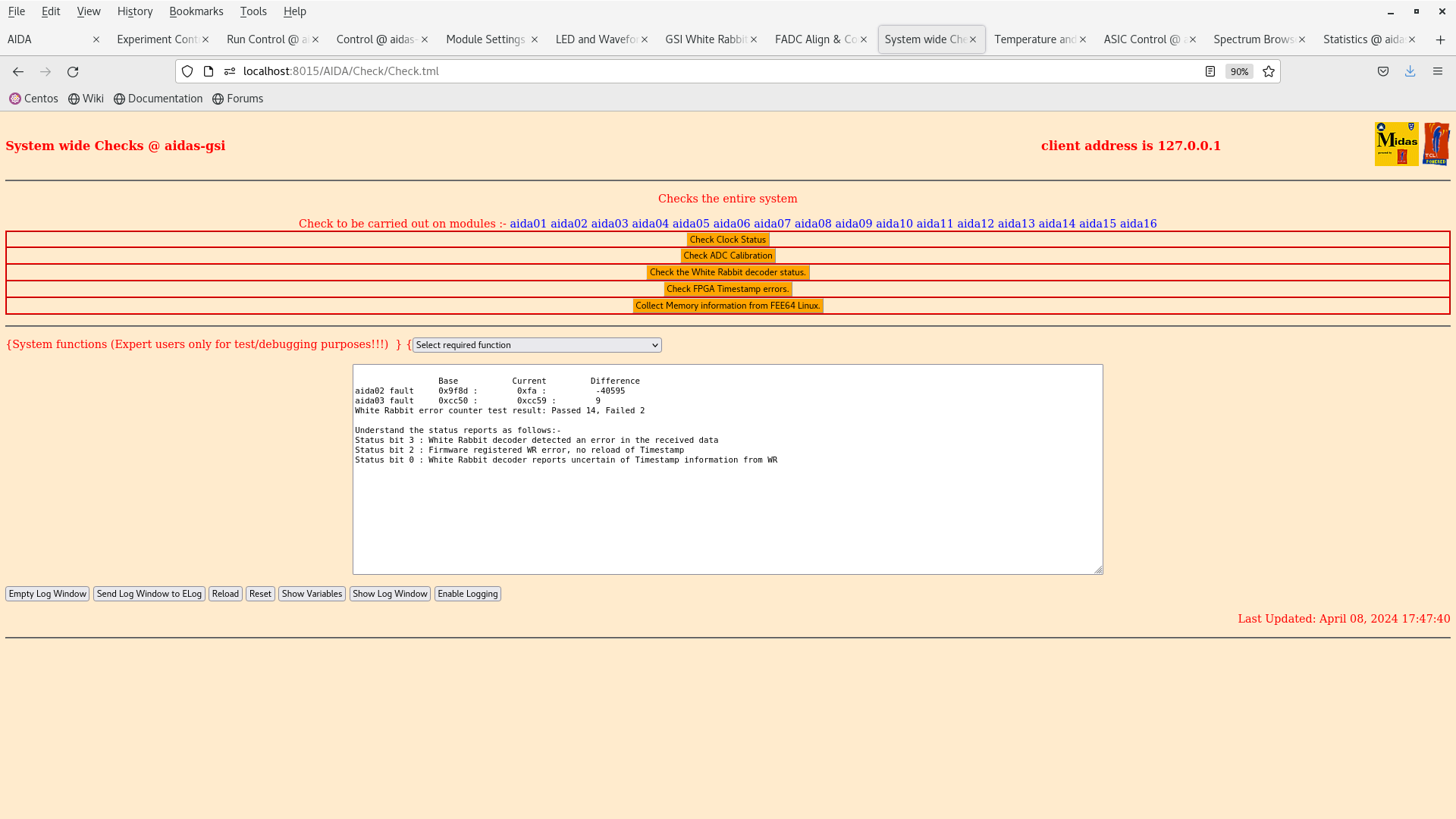

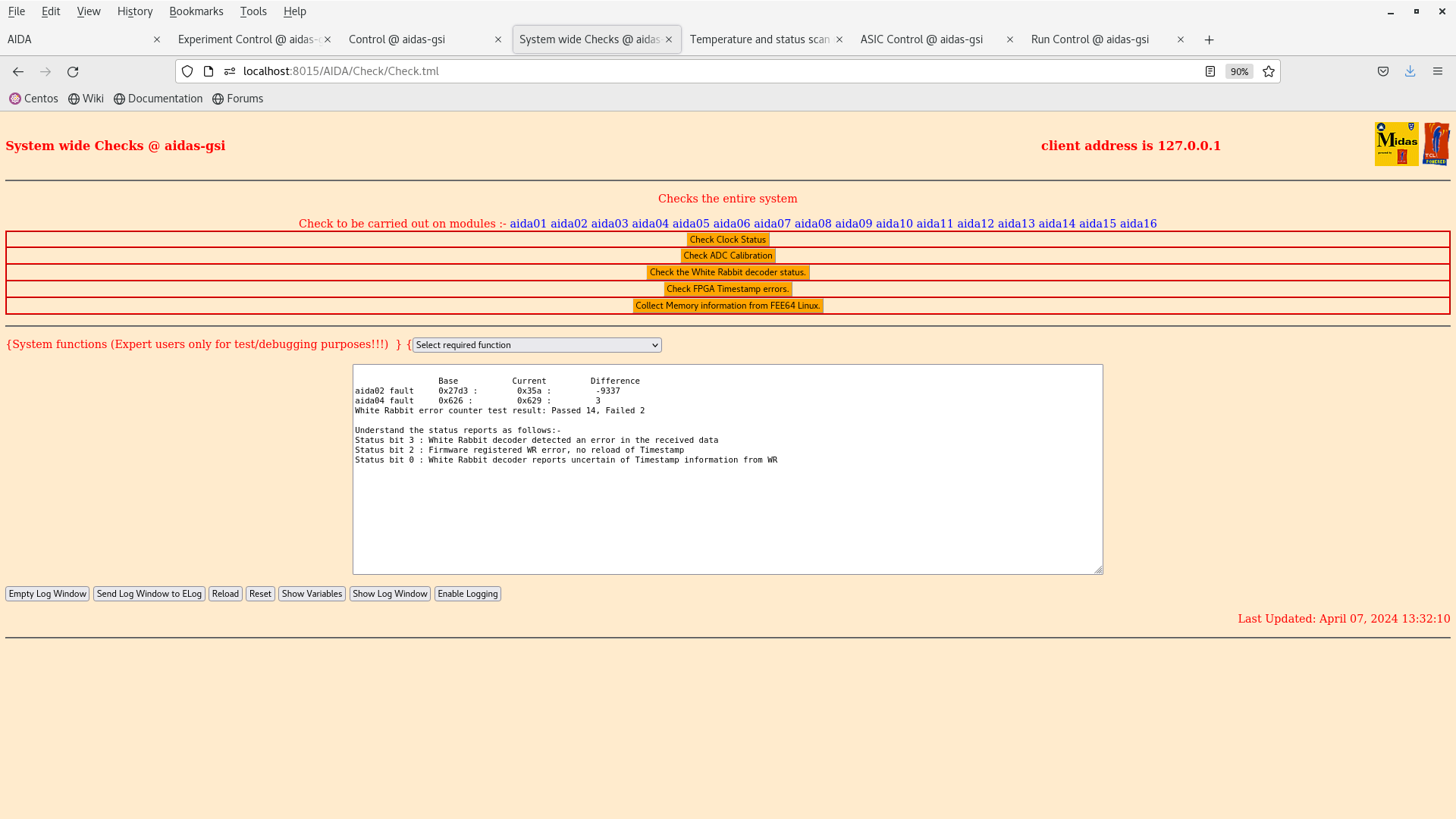

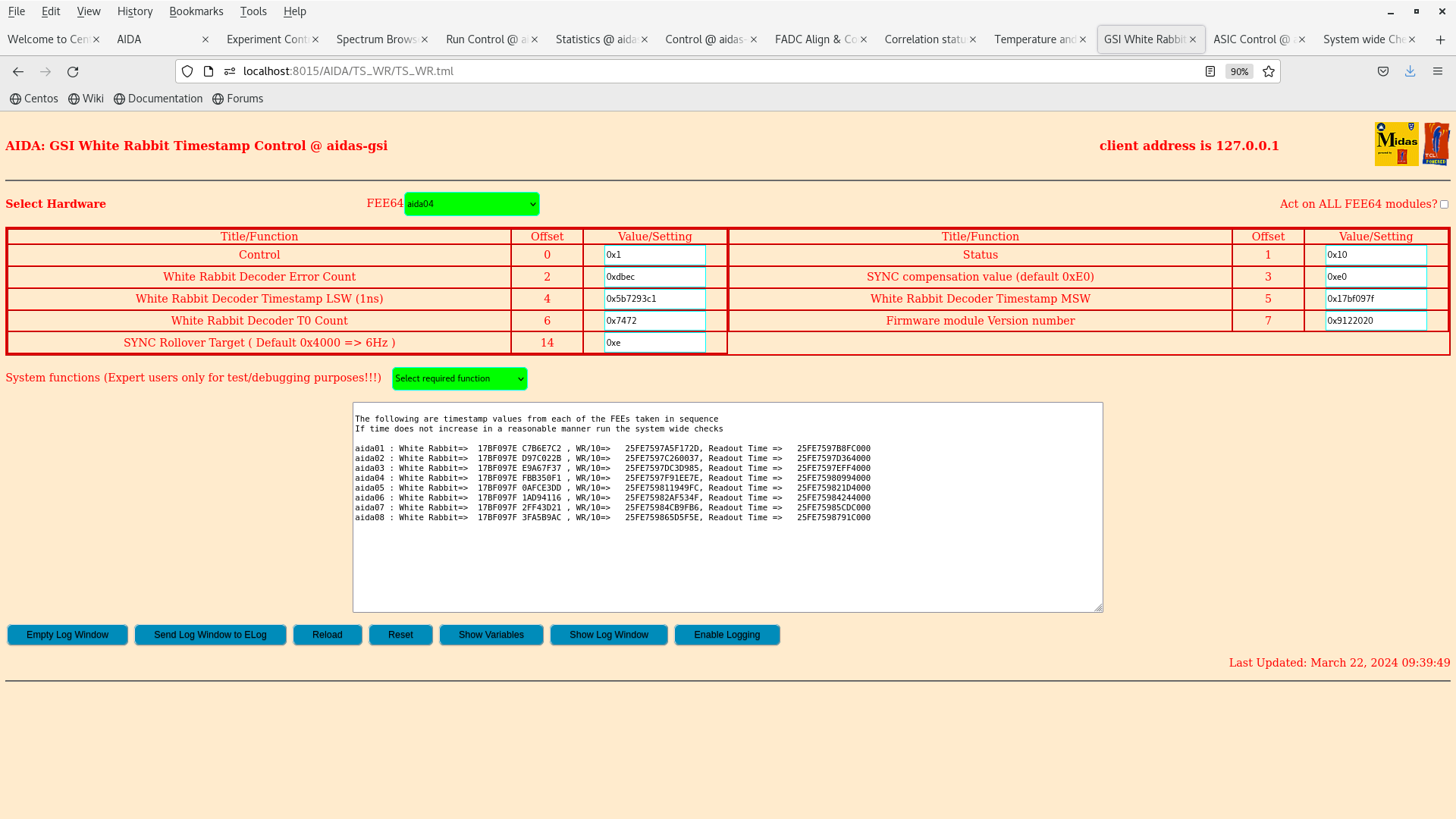

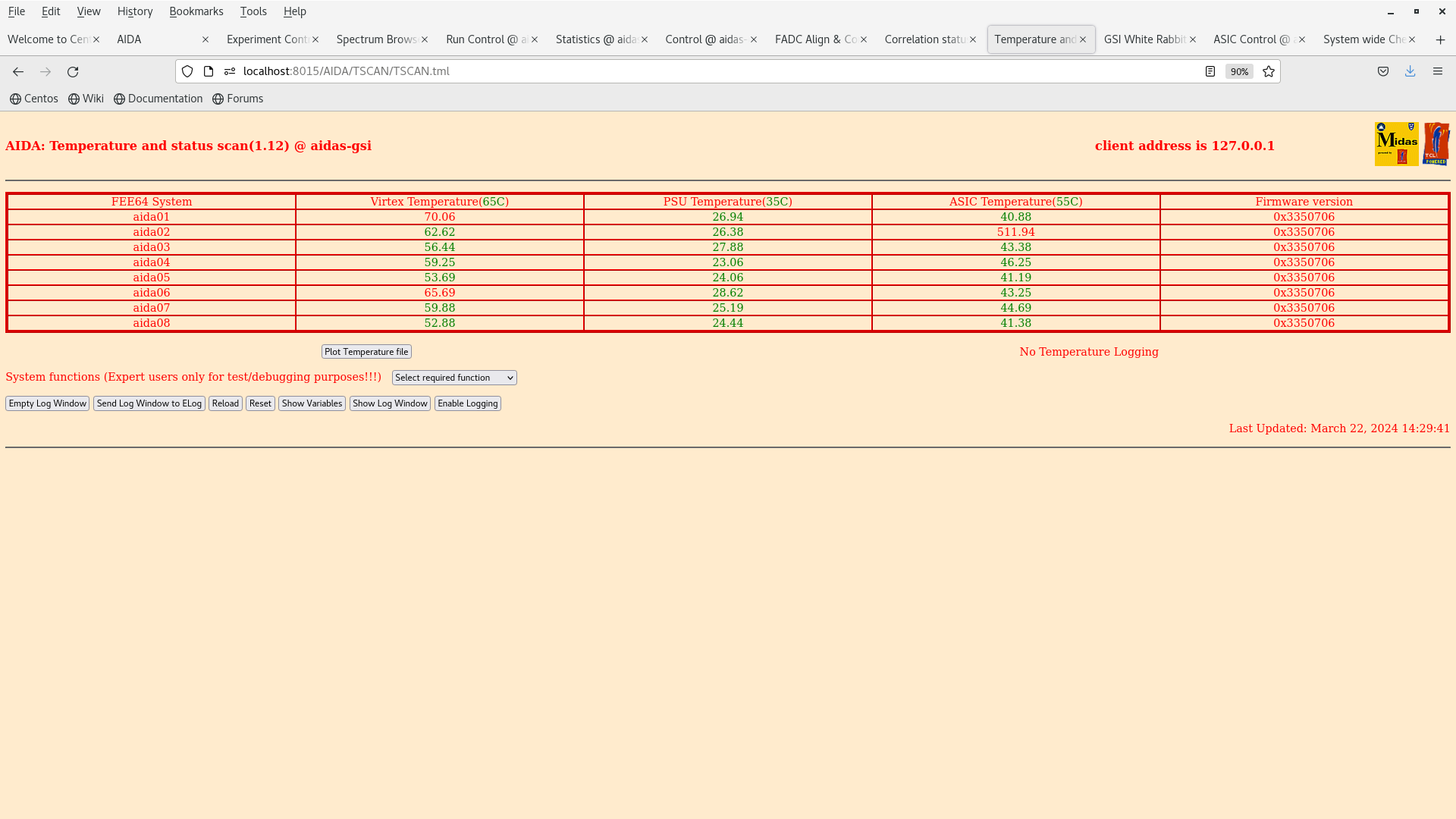

All system wide checks OK *except* aida02 and aida03 WR decoder status - attachment 3

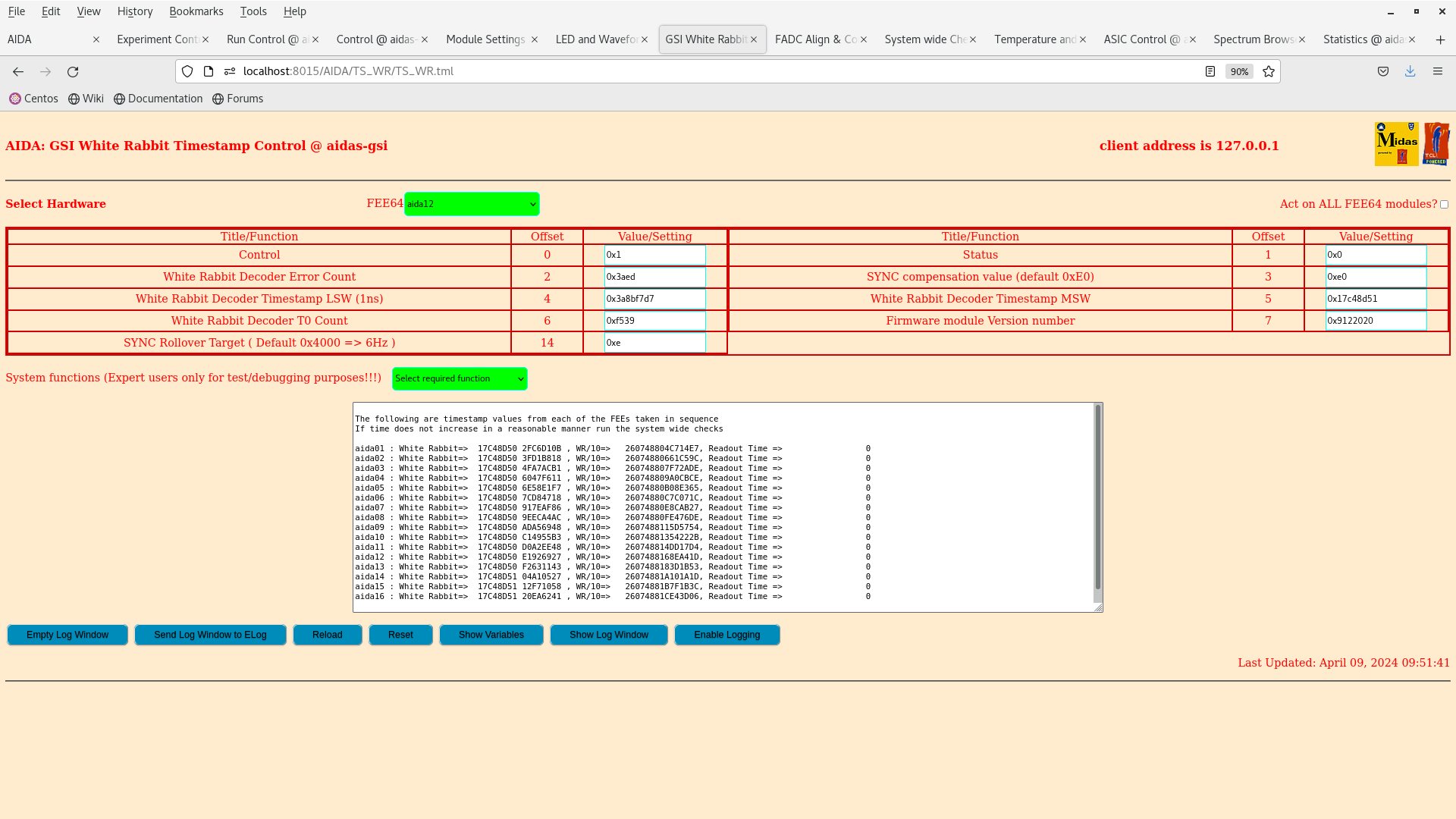

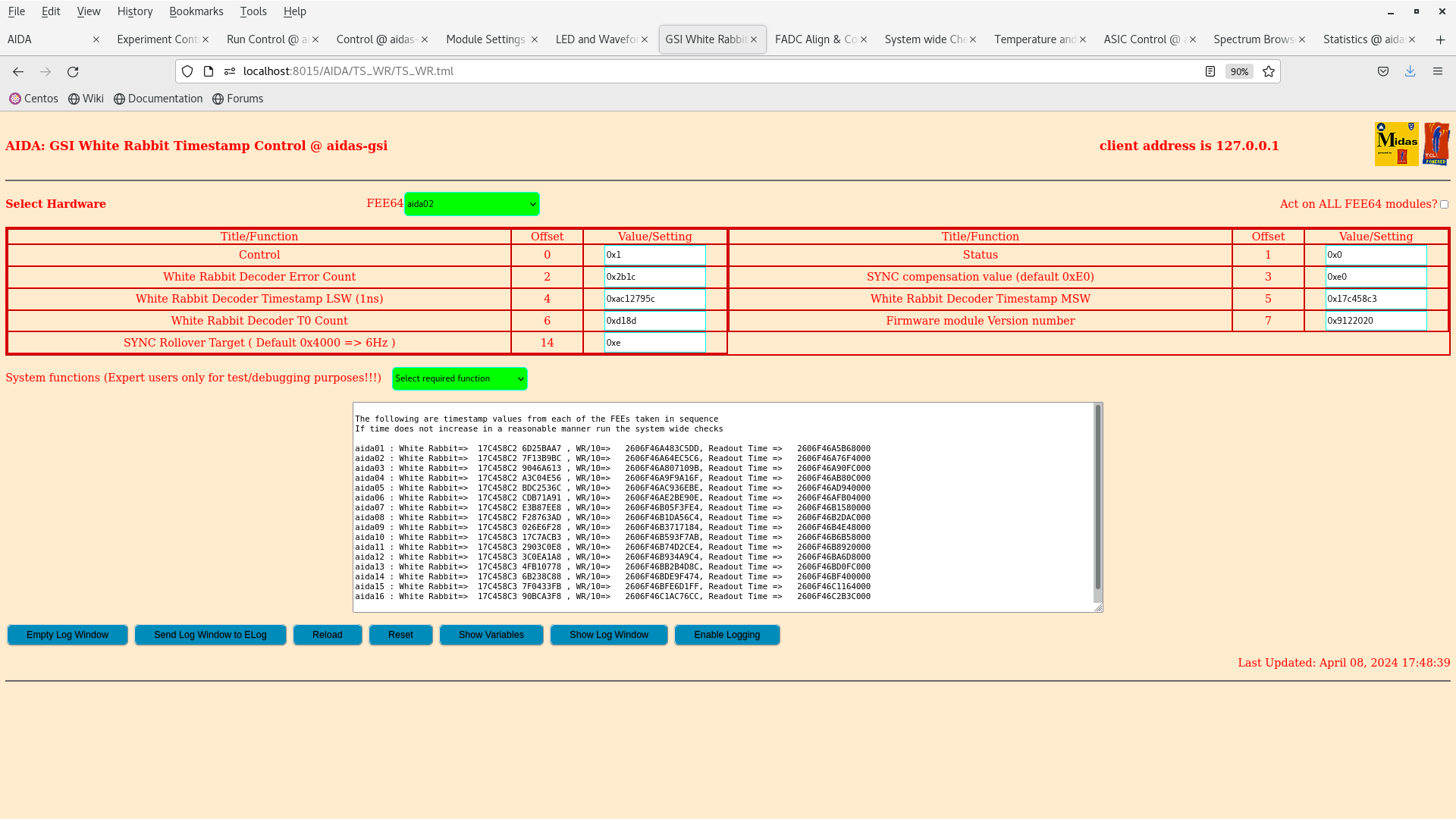

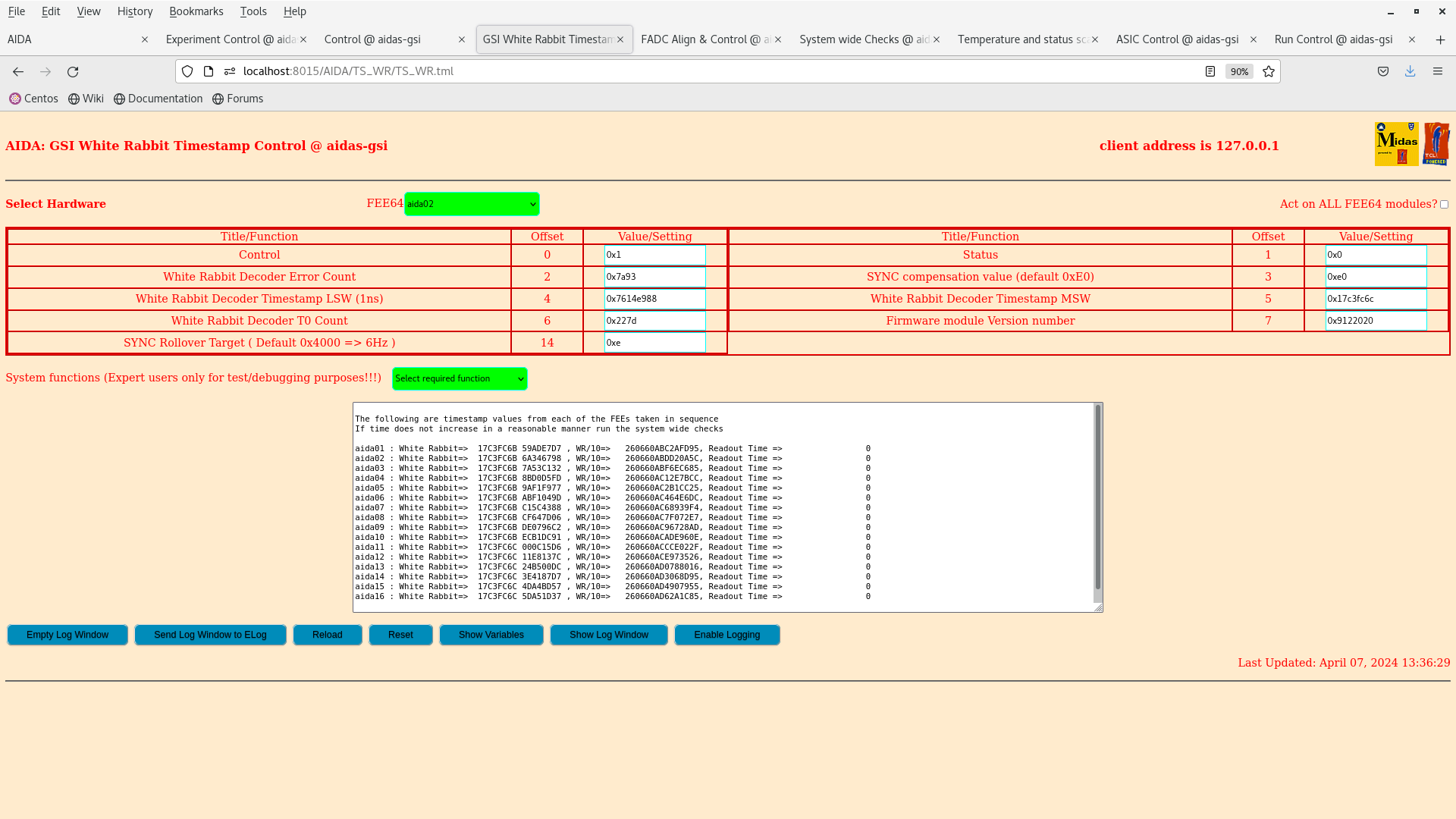

WR timestamps OK - attachment 4

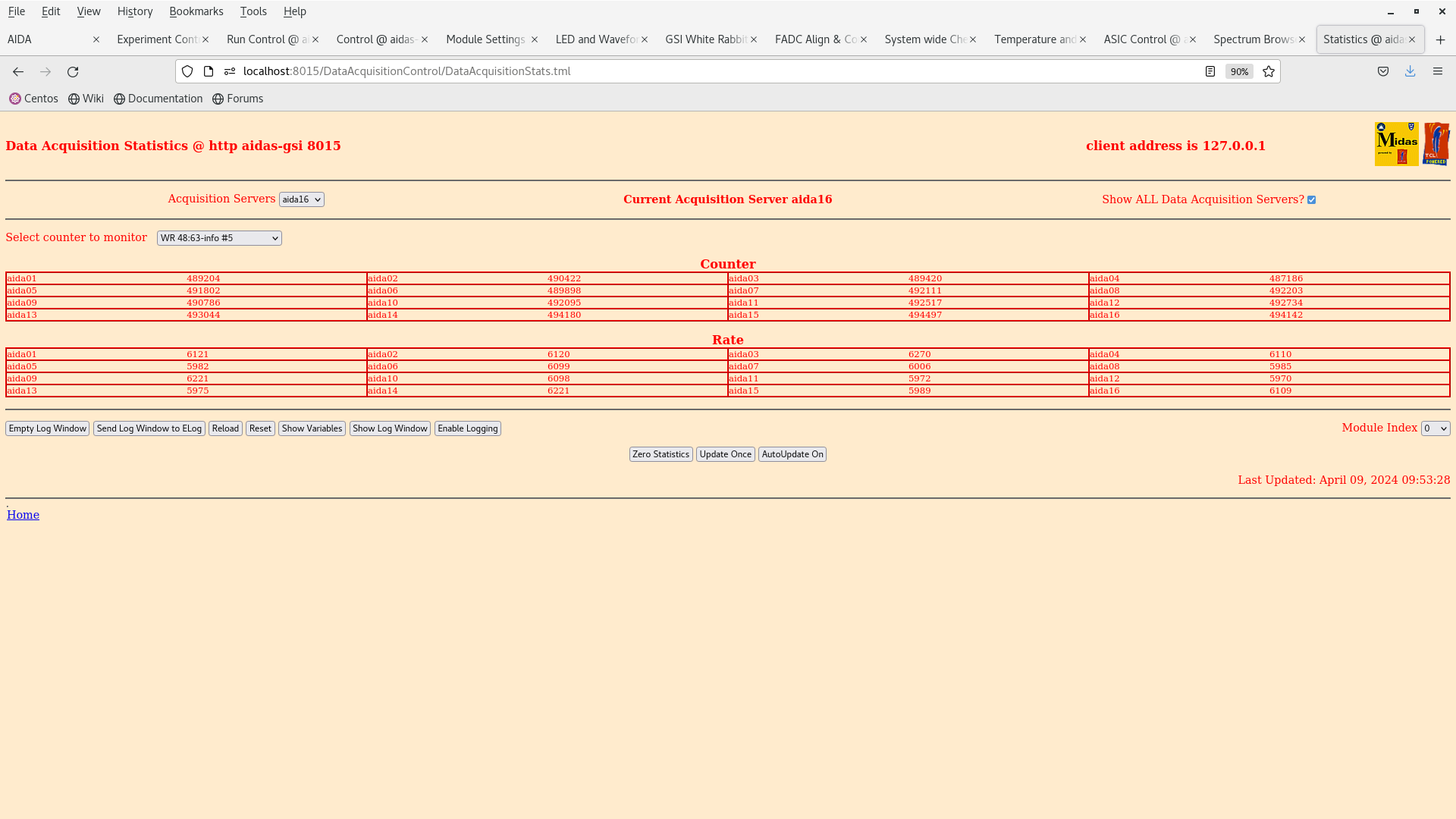

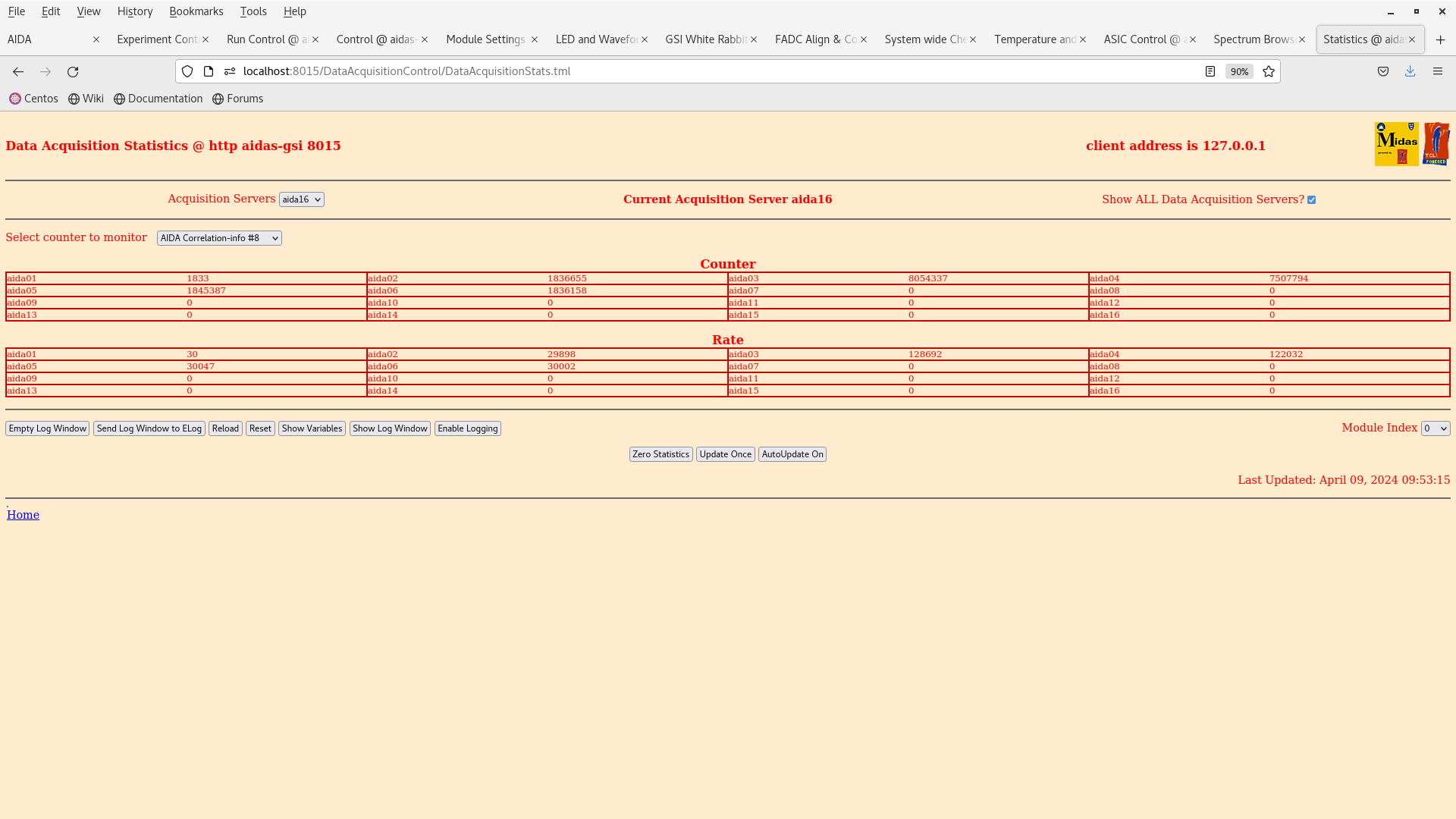

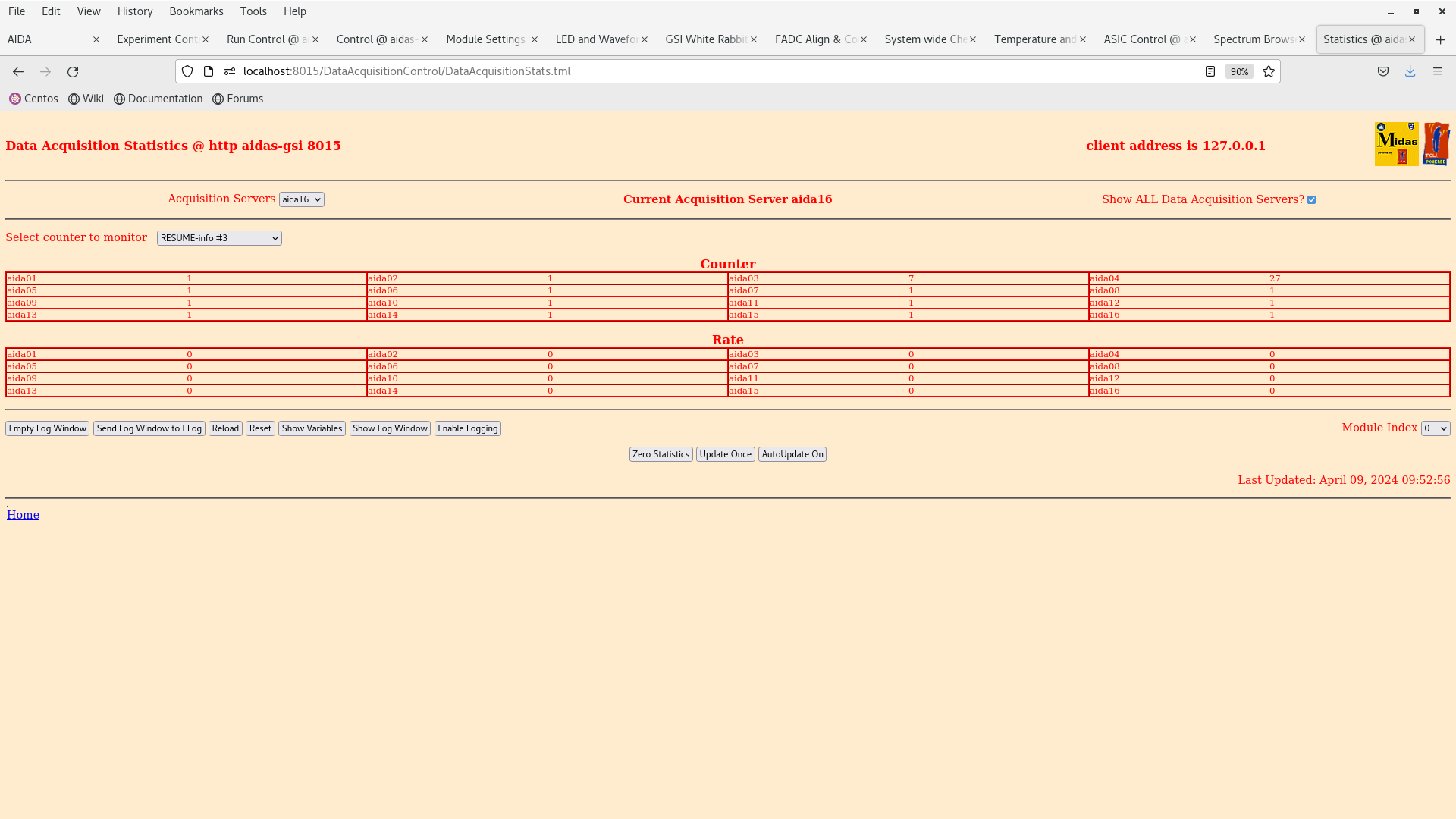

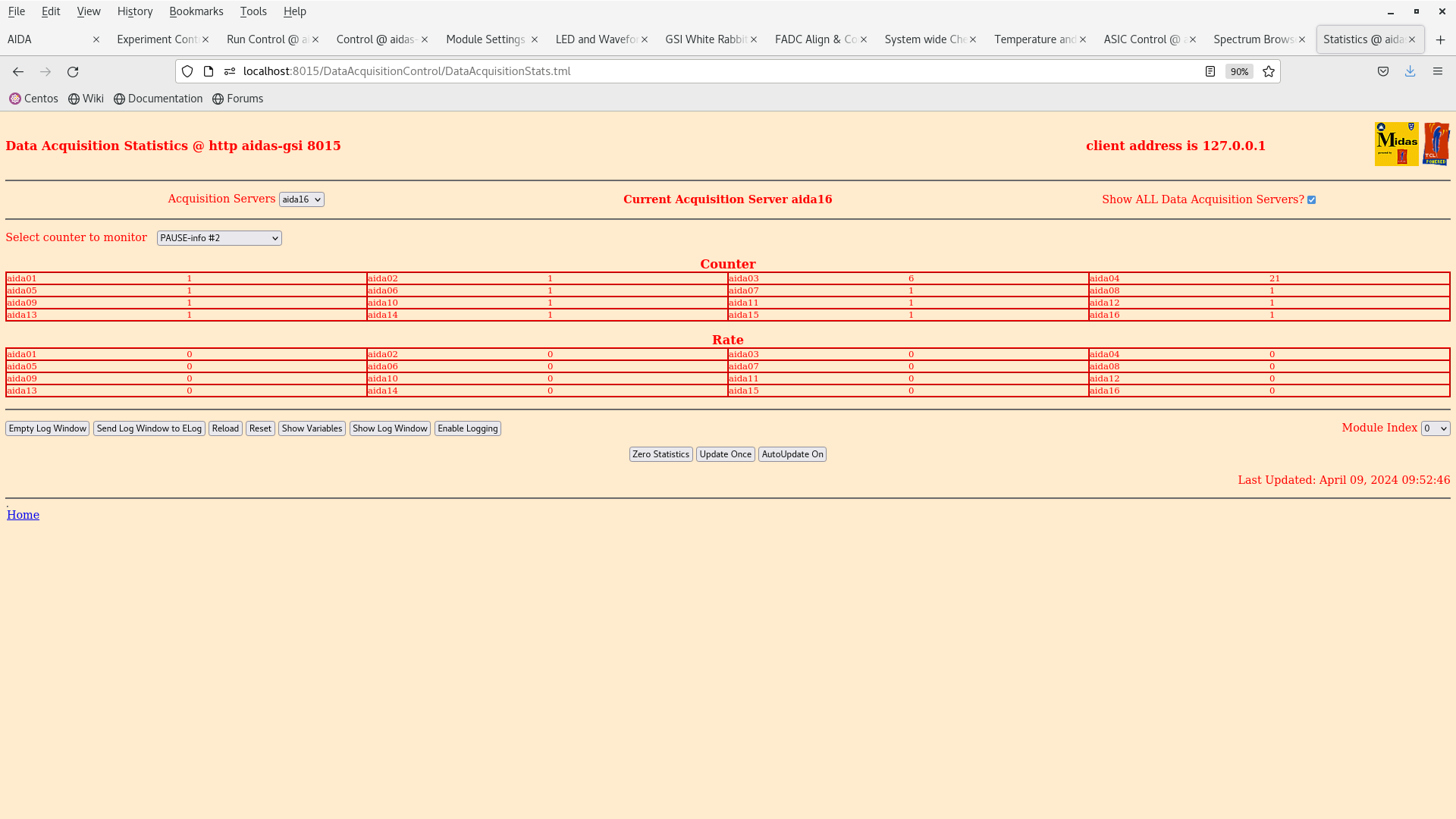

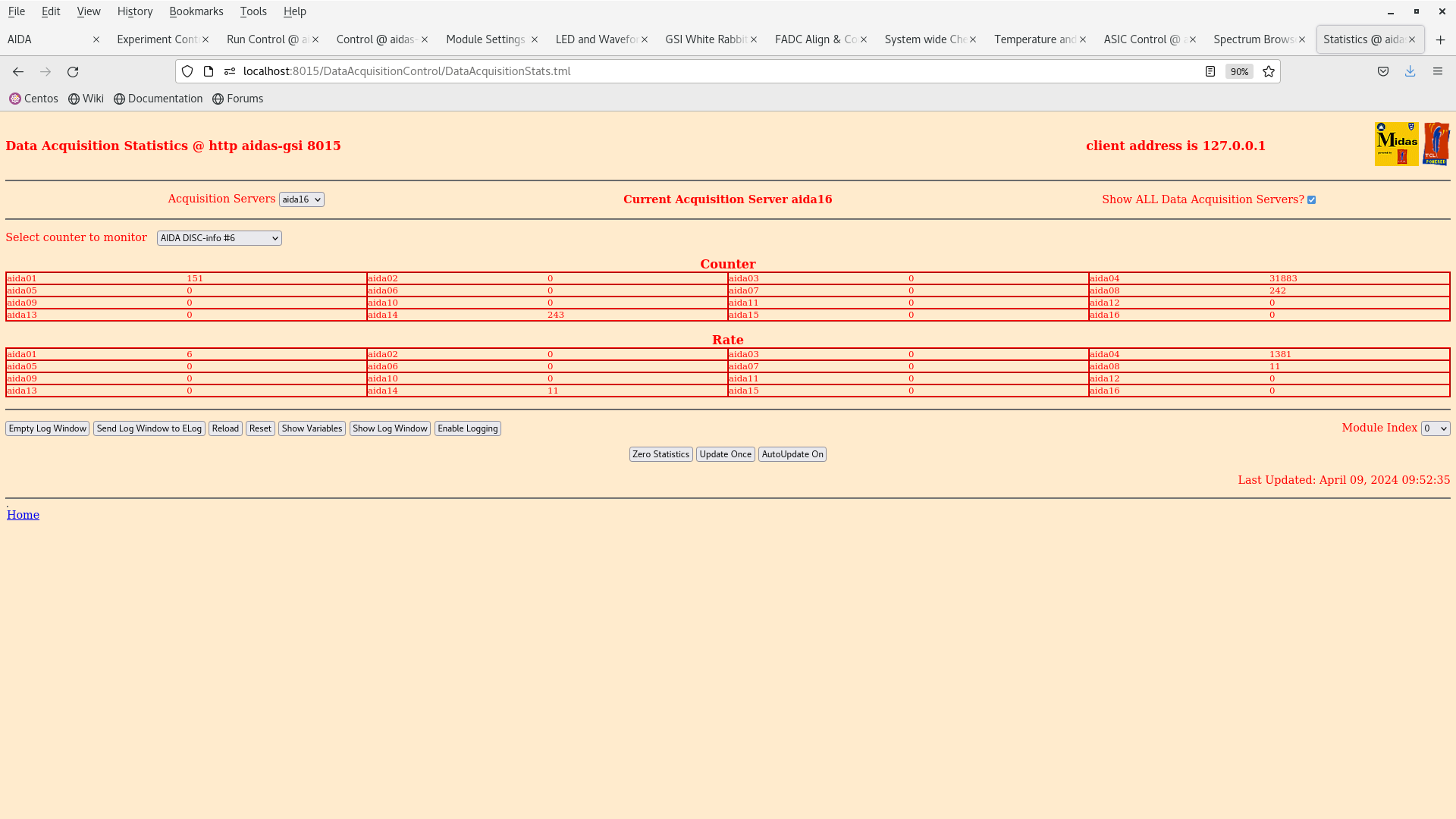

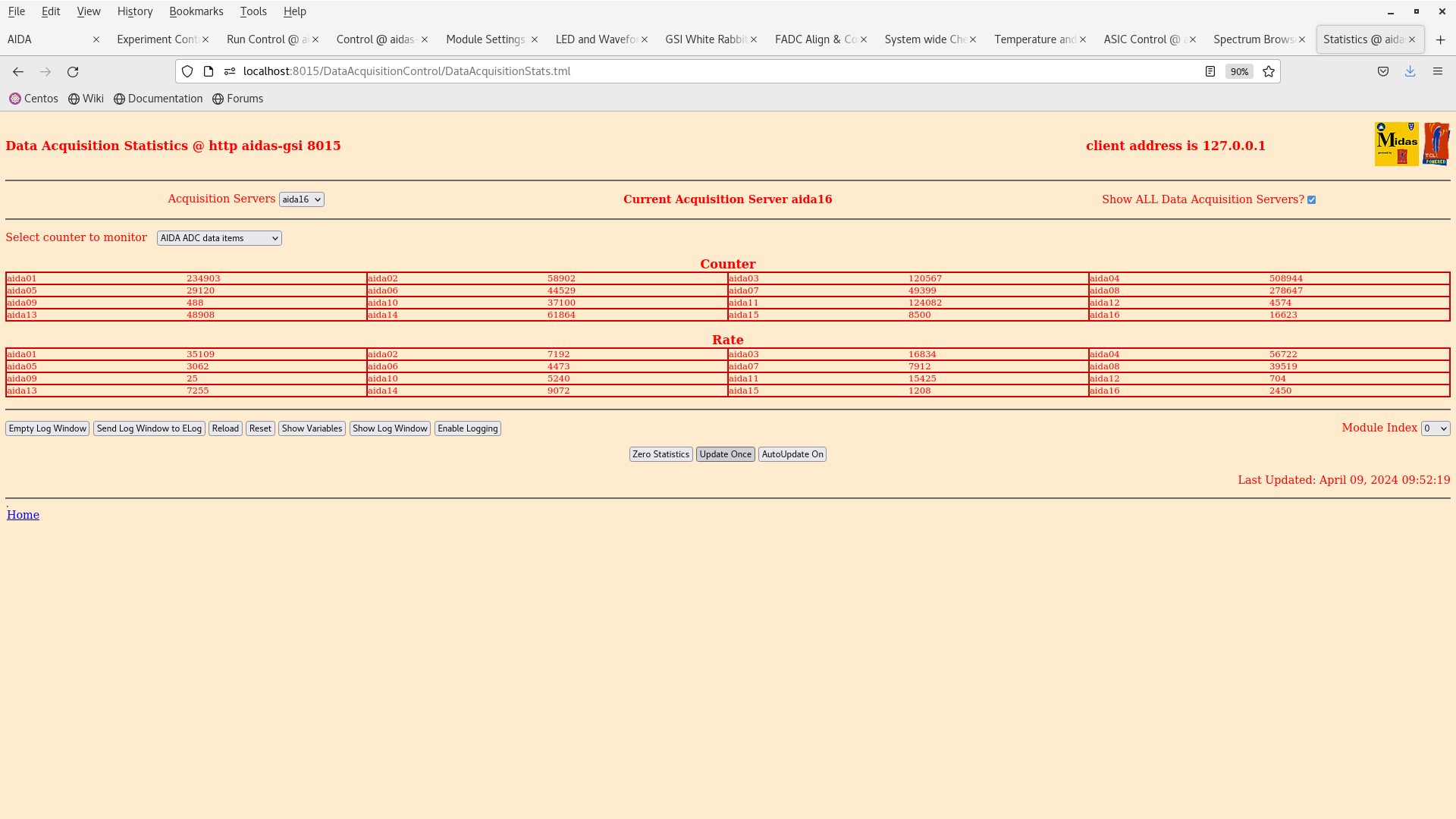

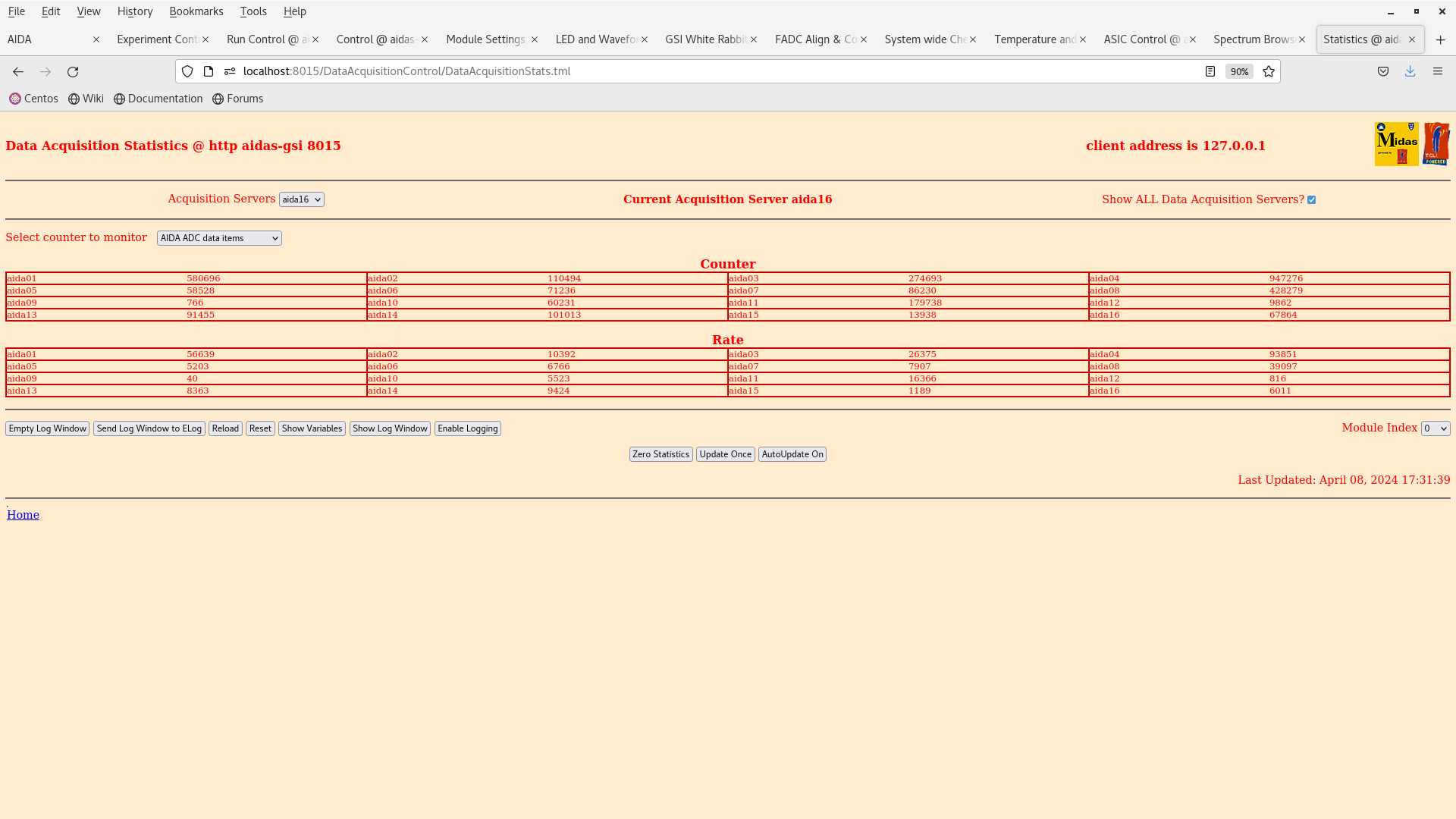

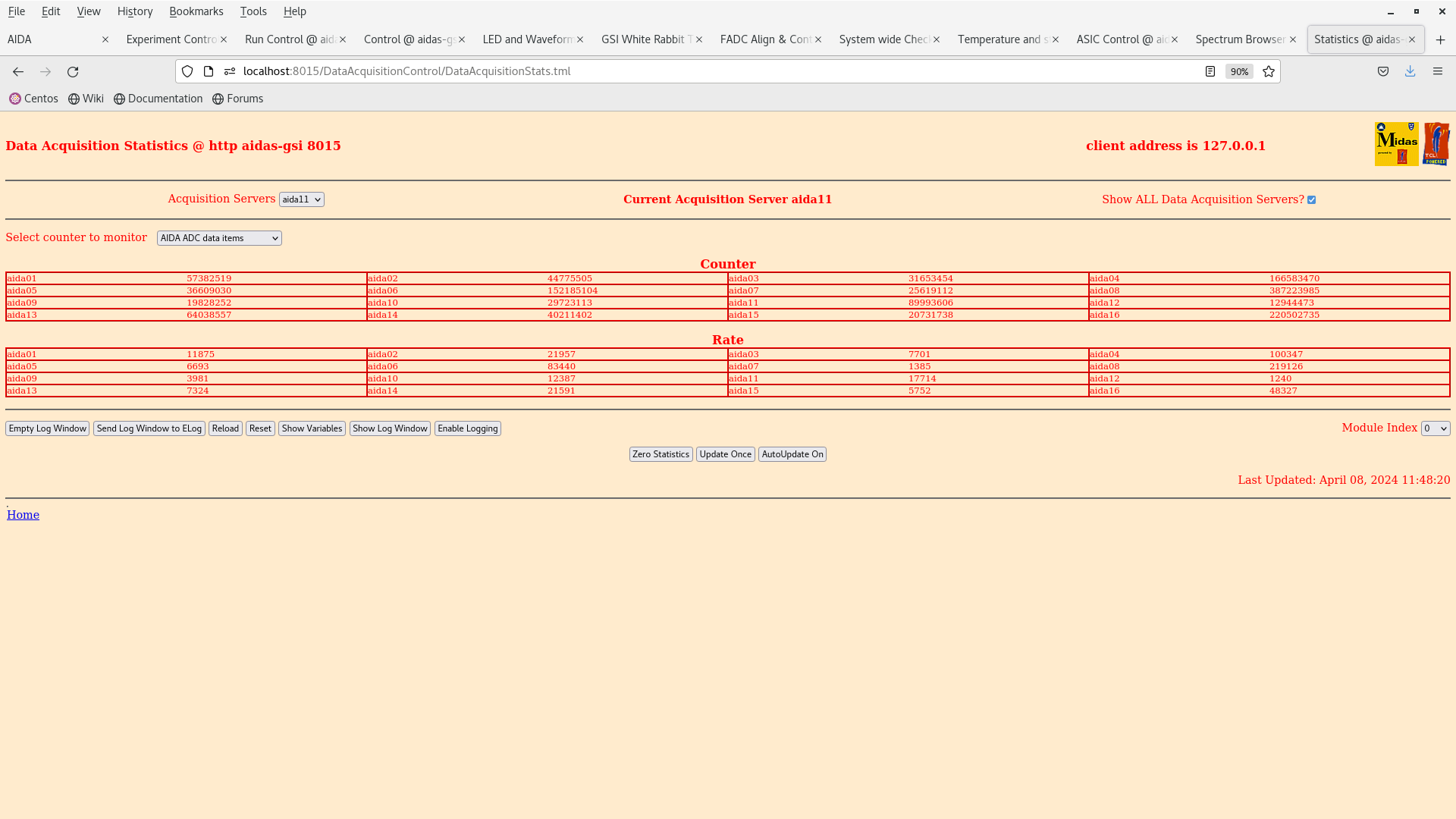

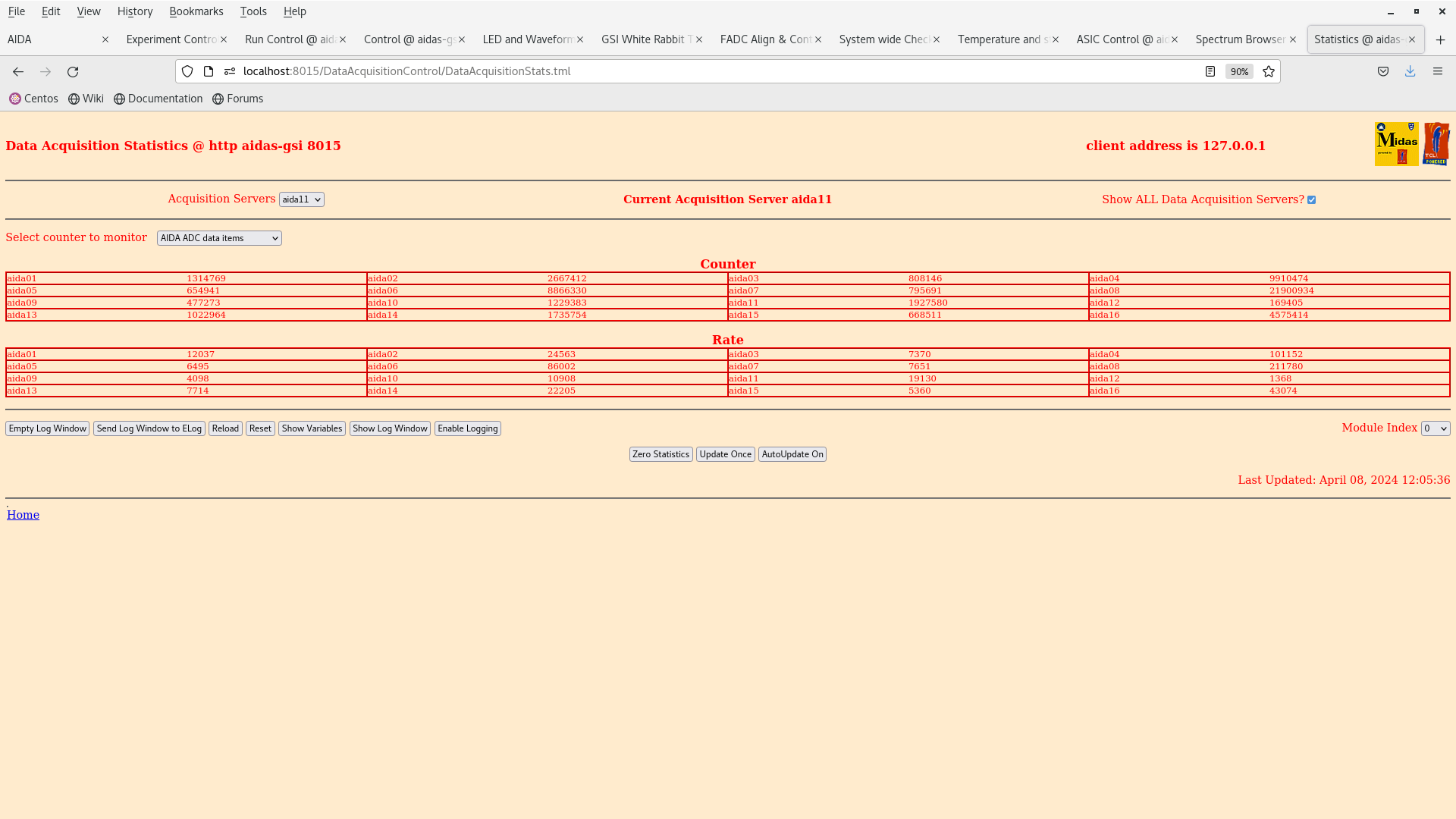

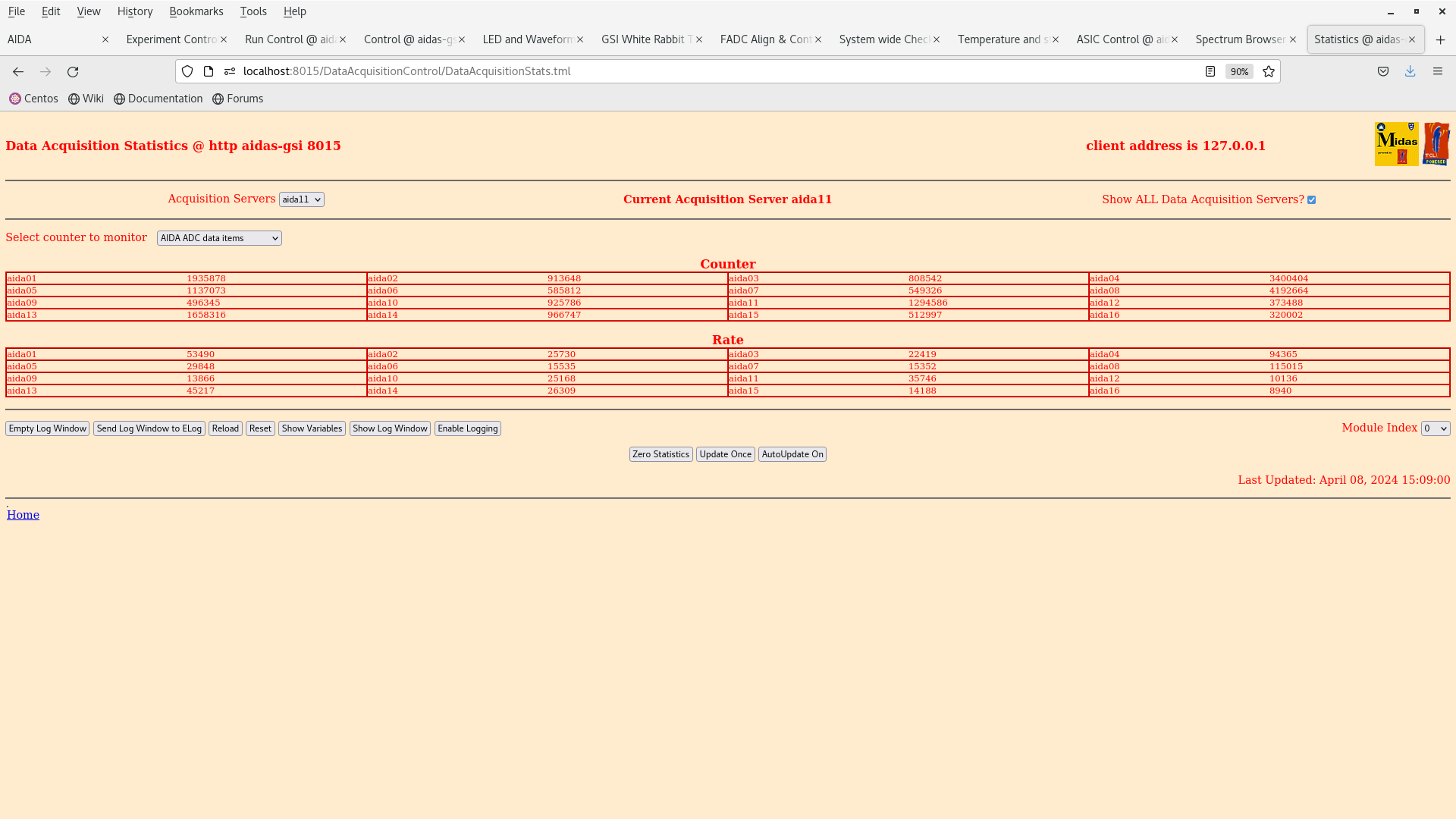

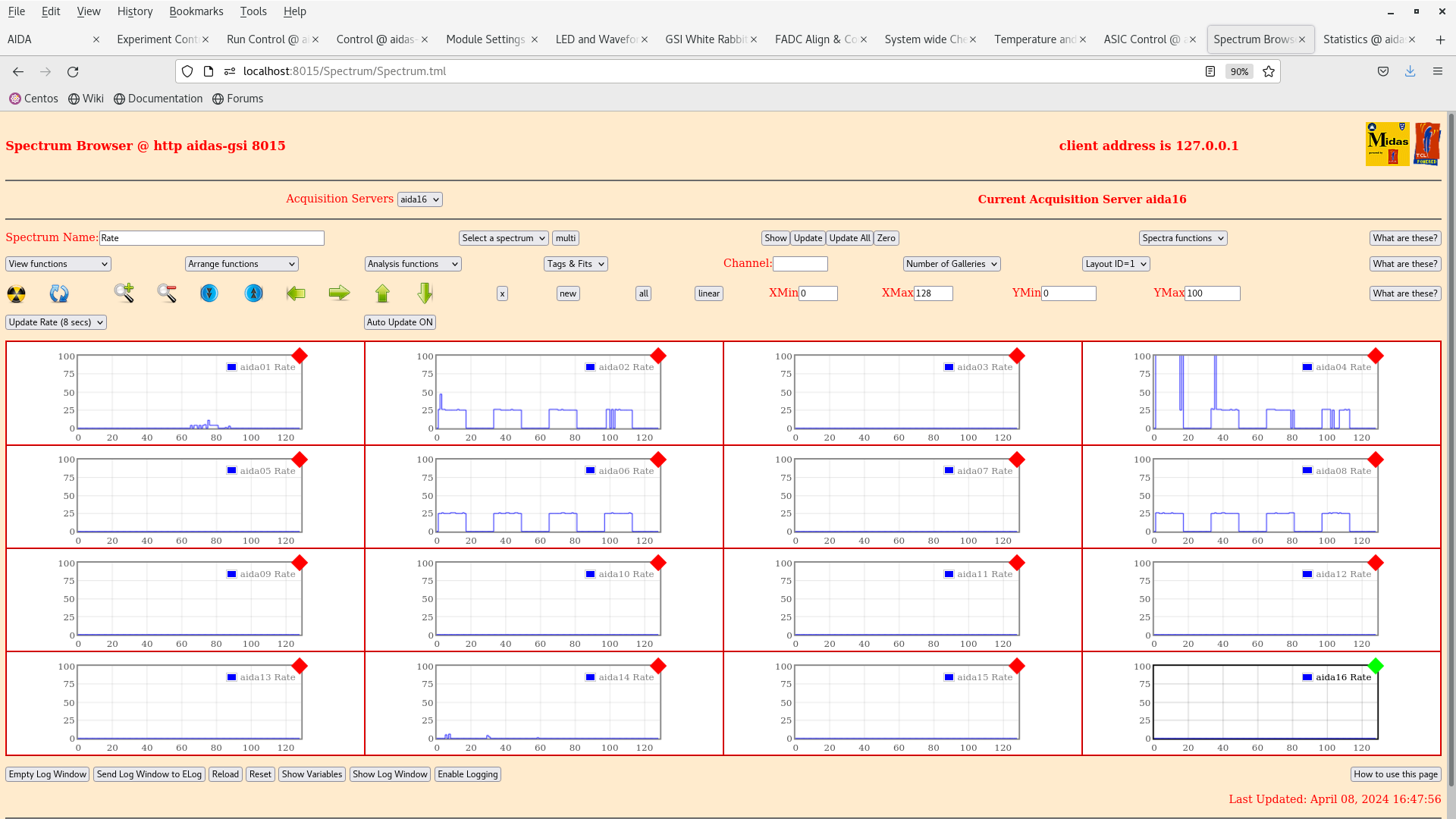

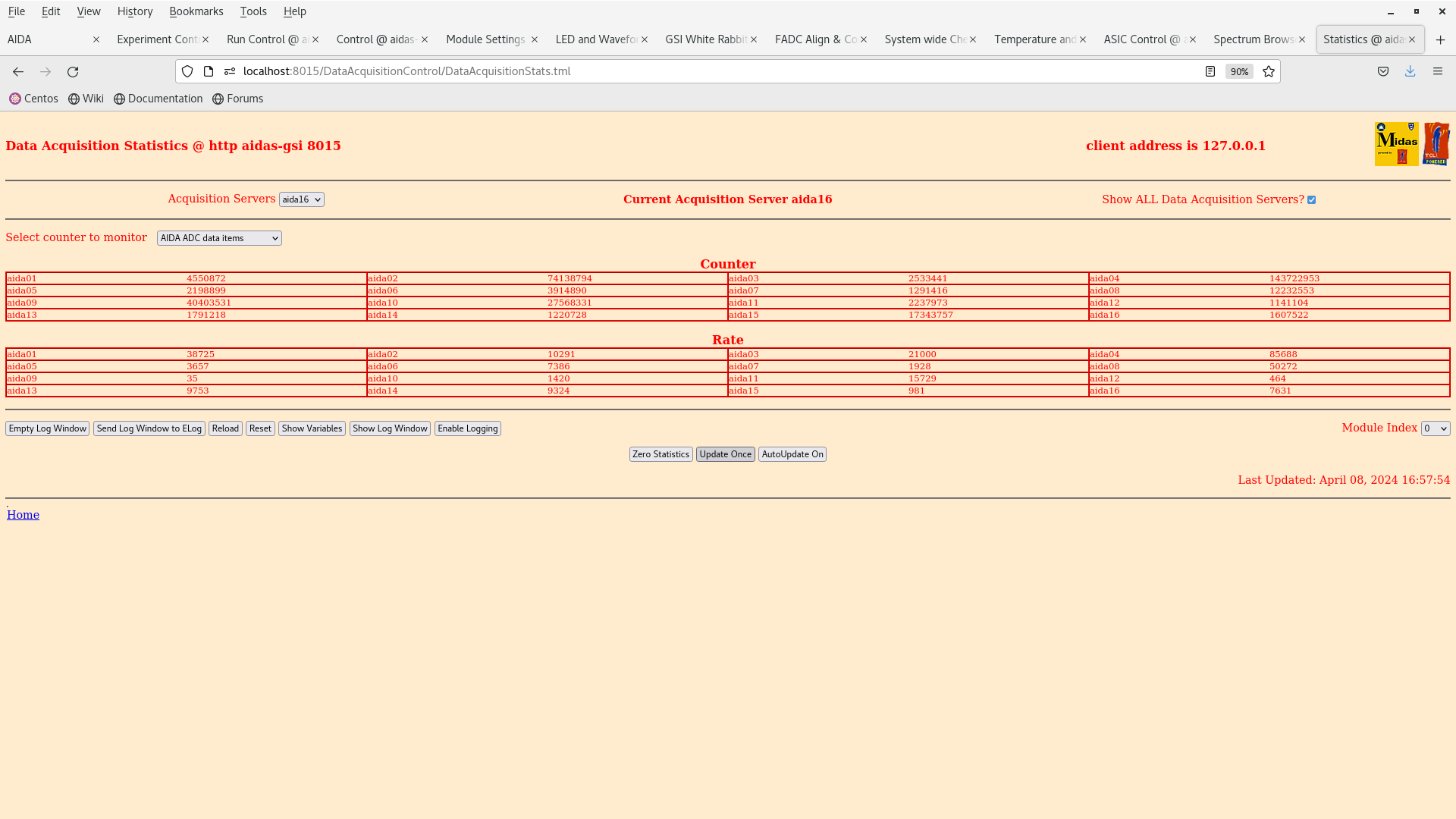

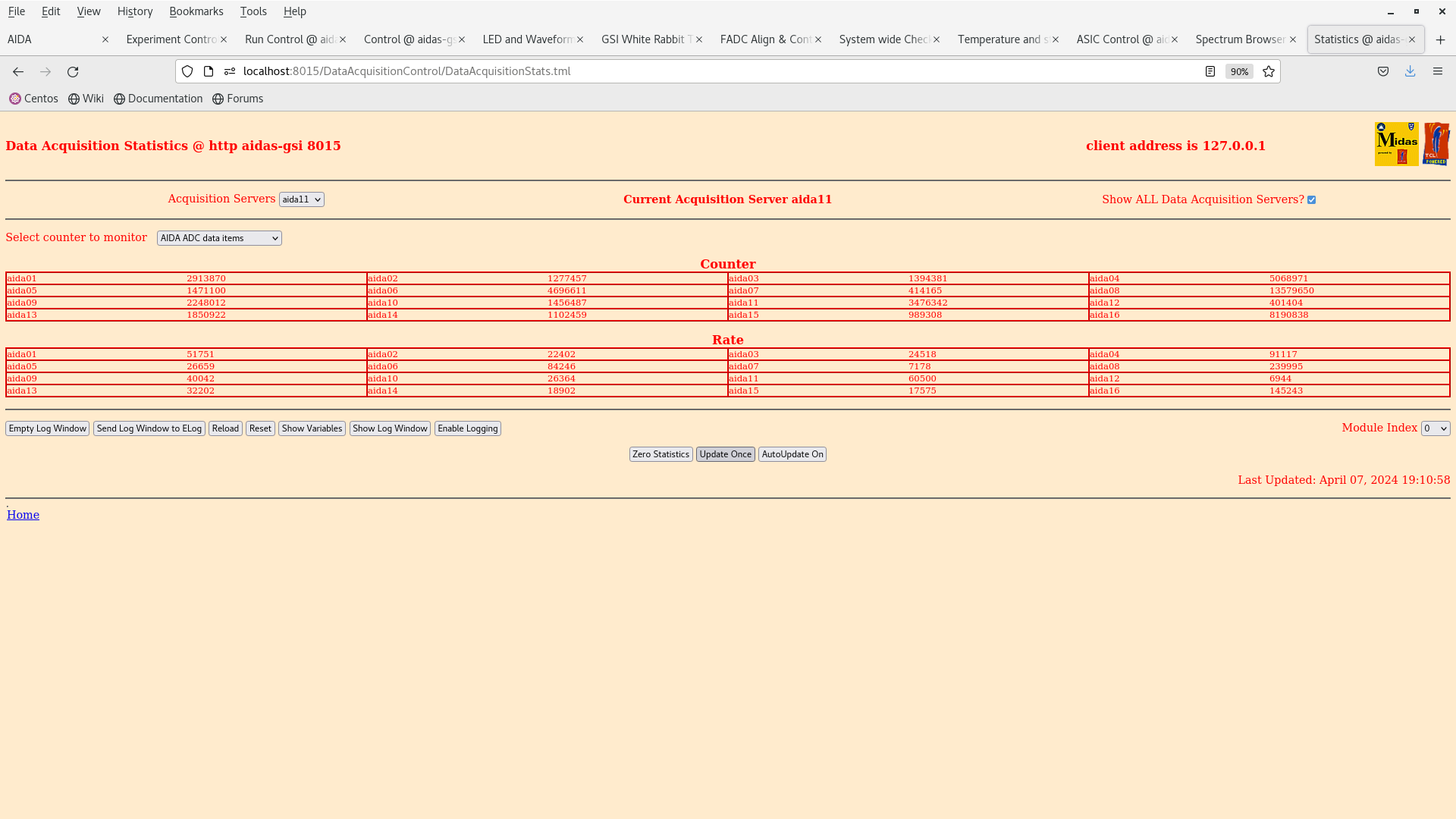

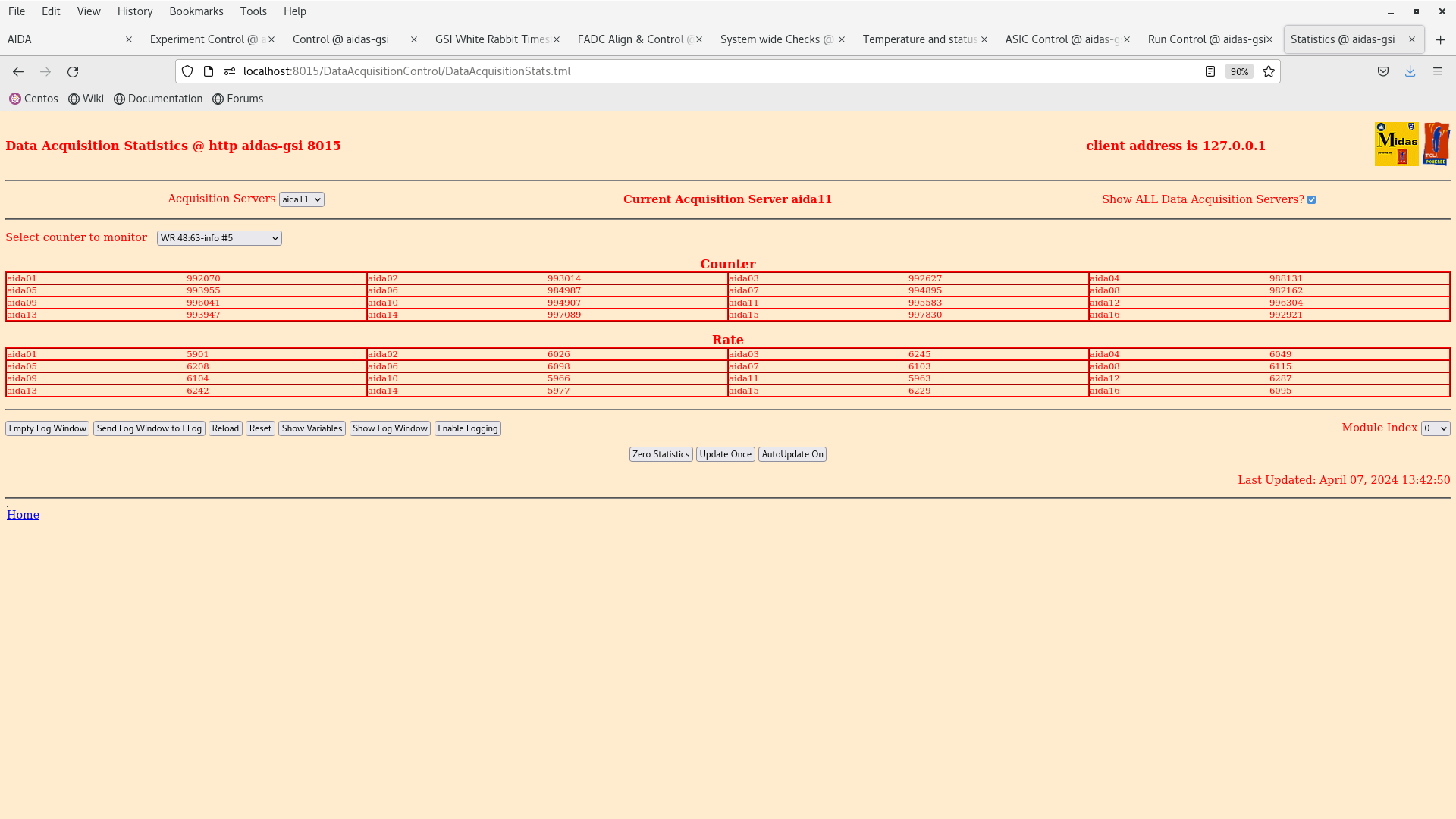

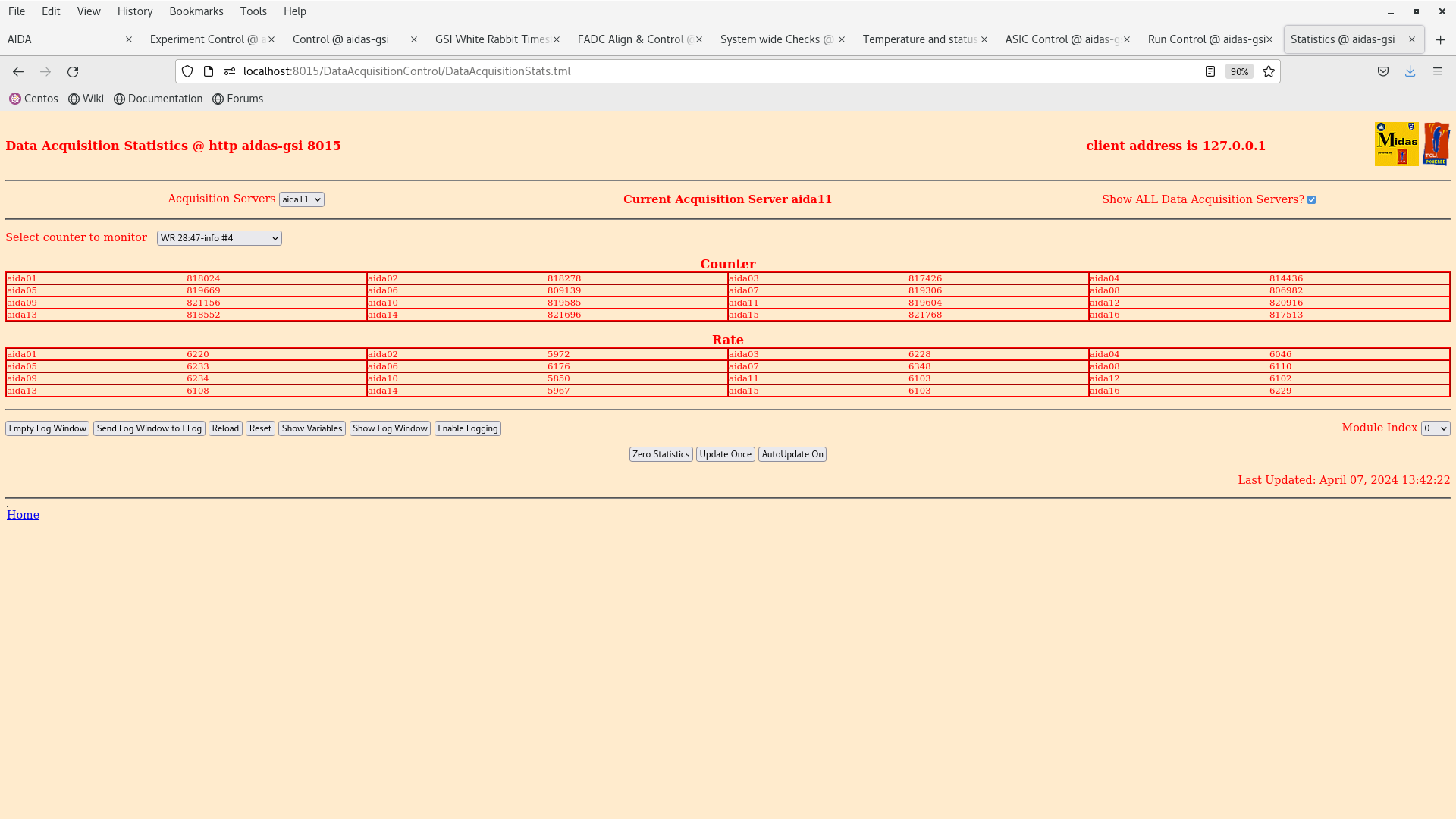

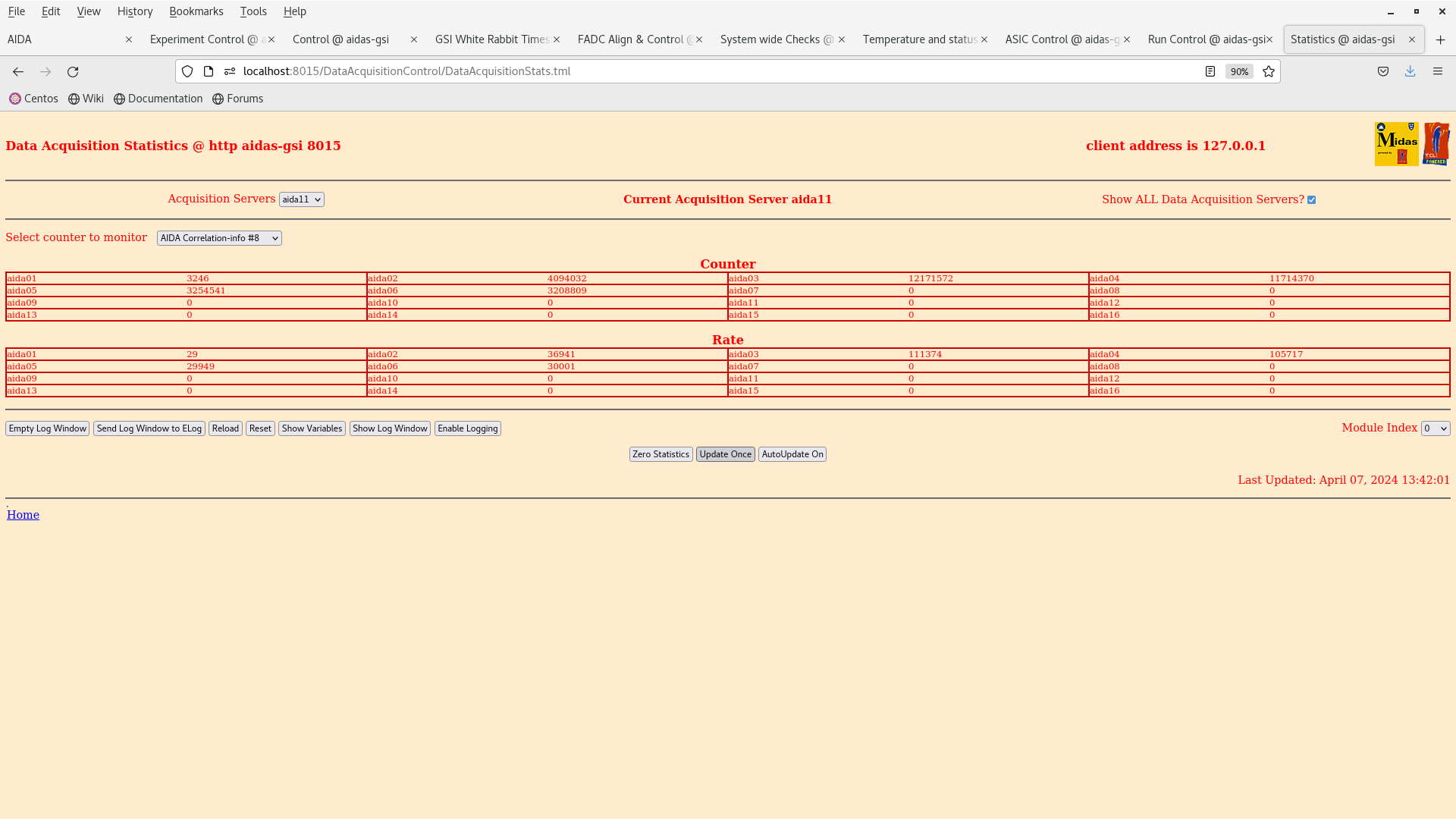

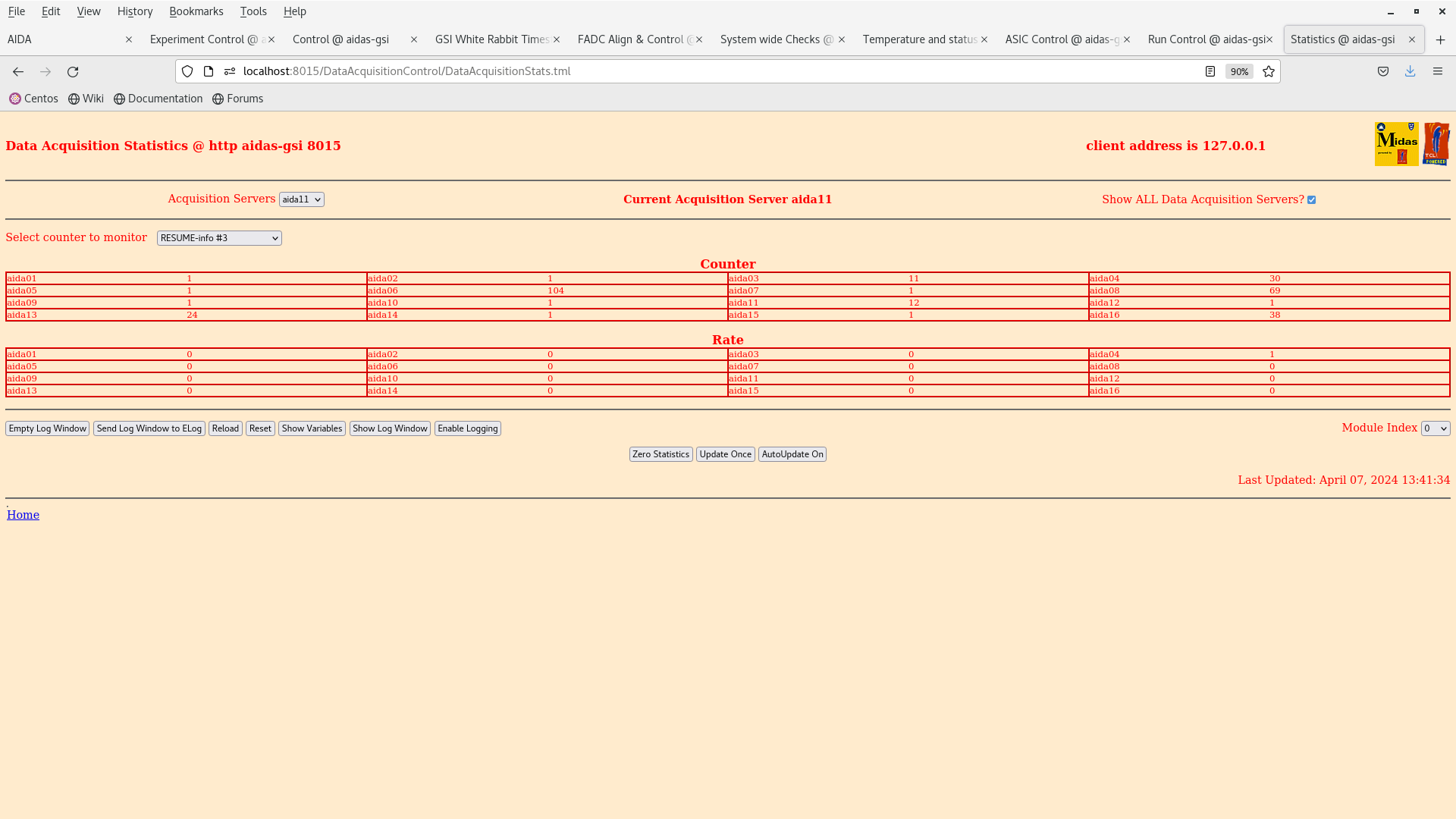

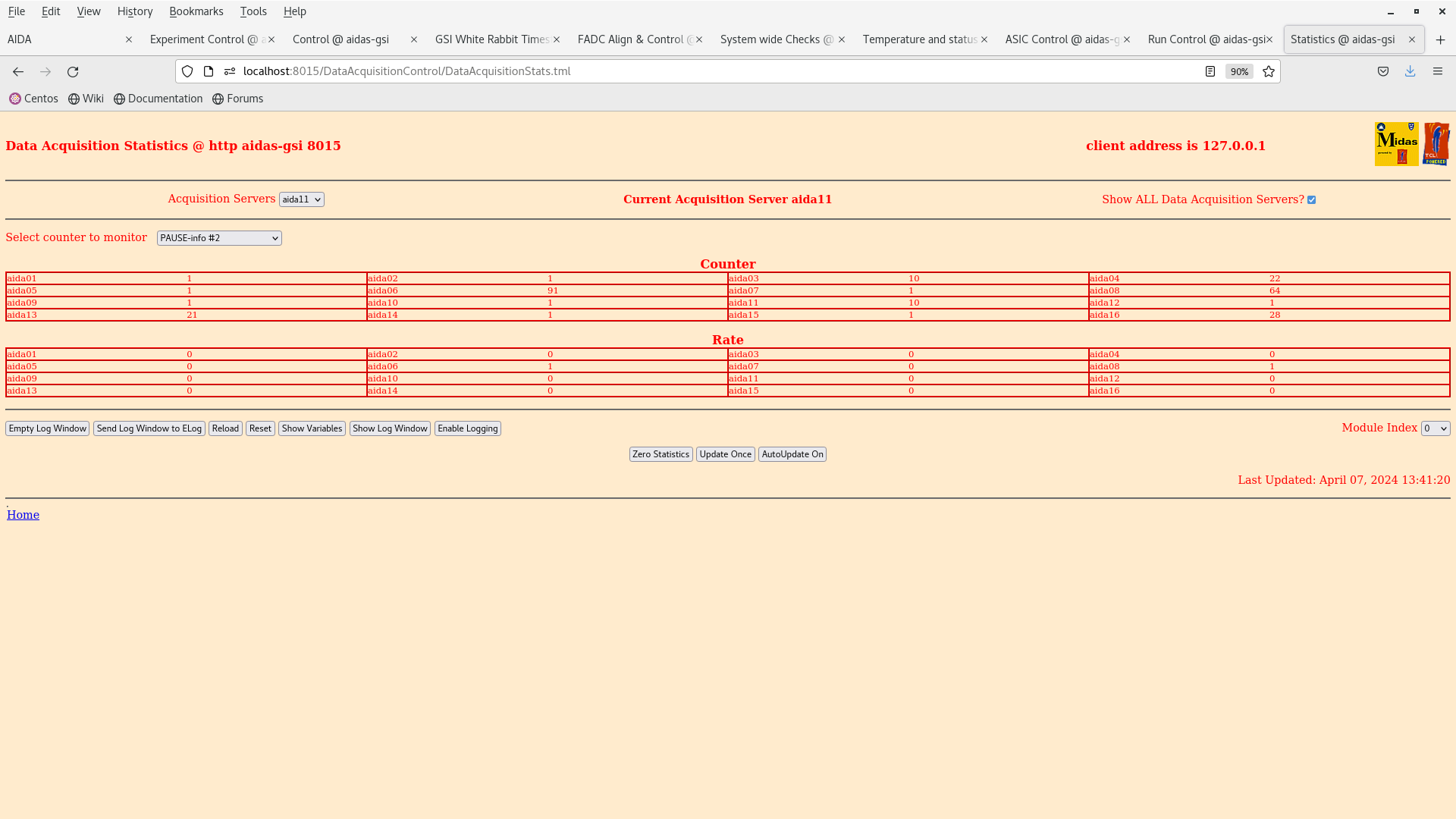

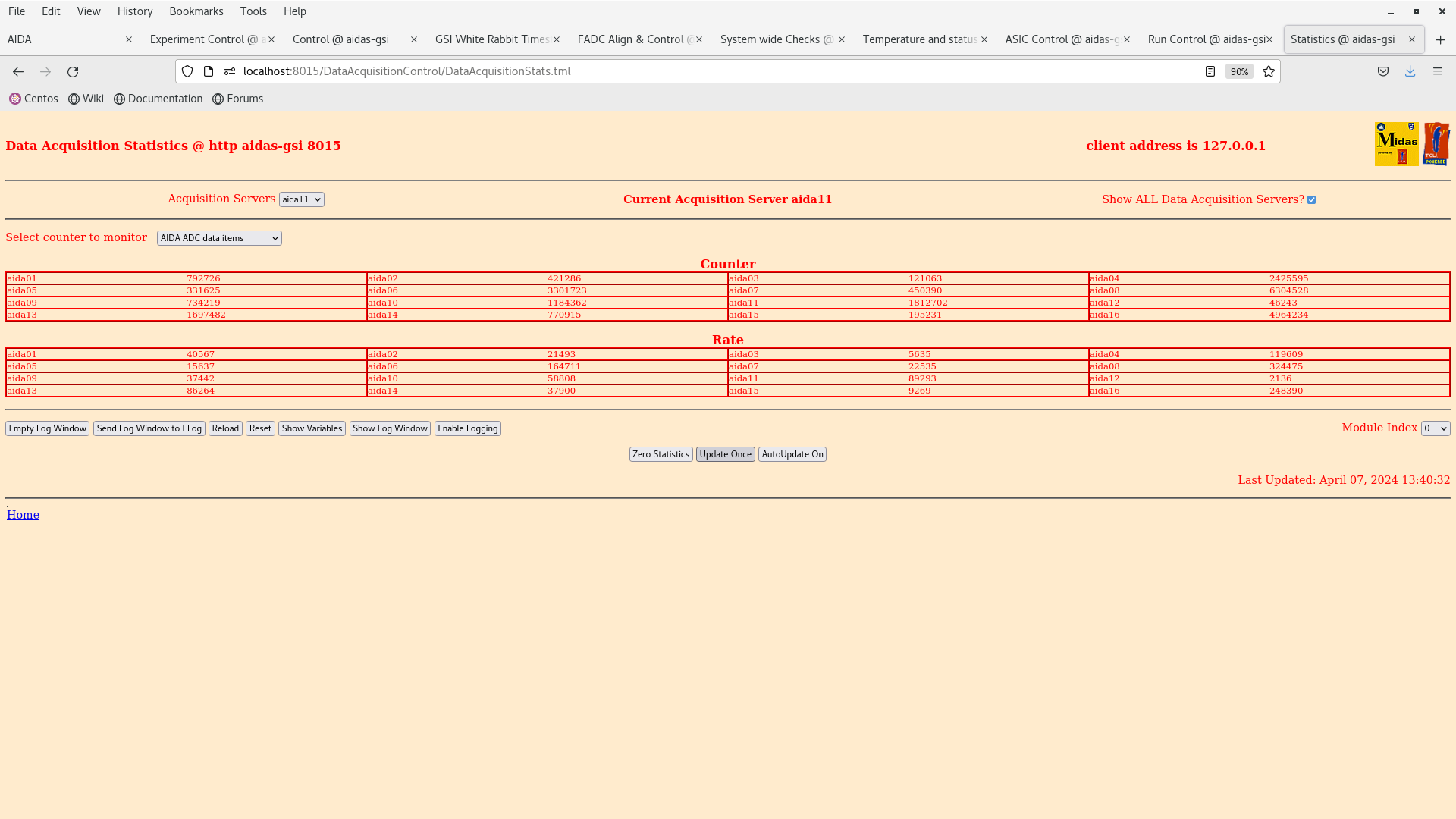

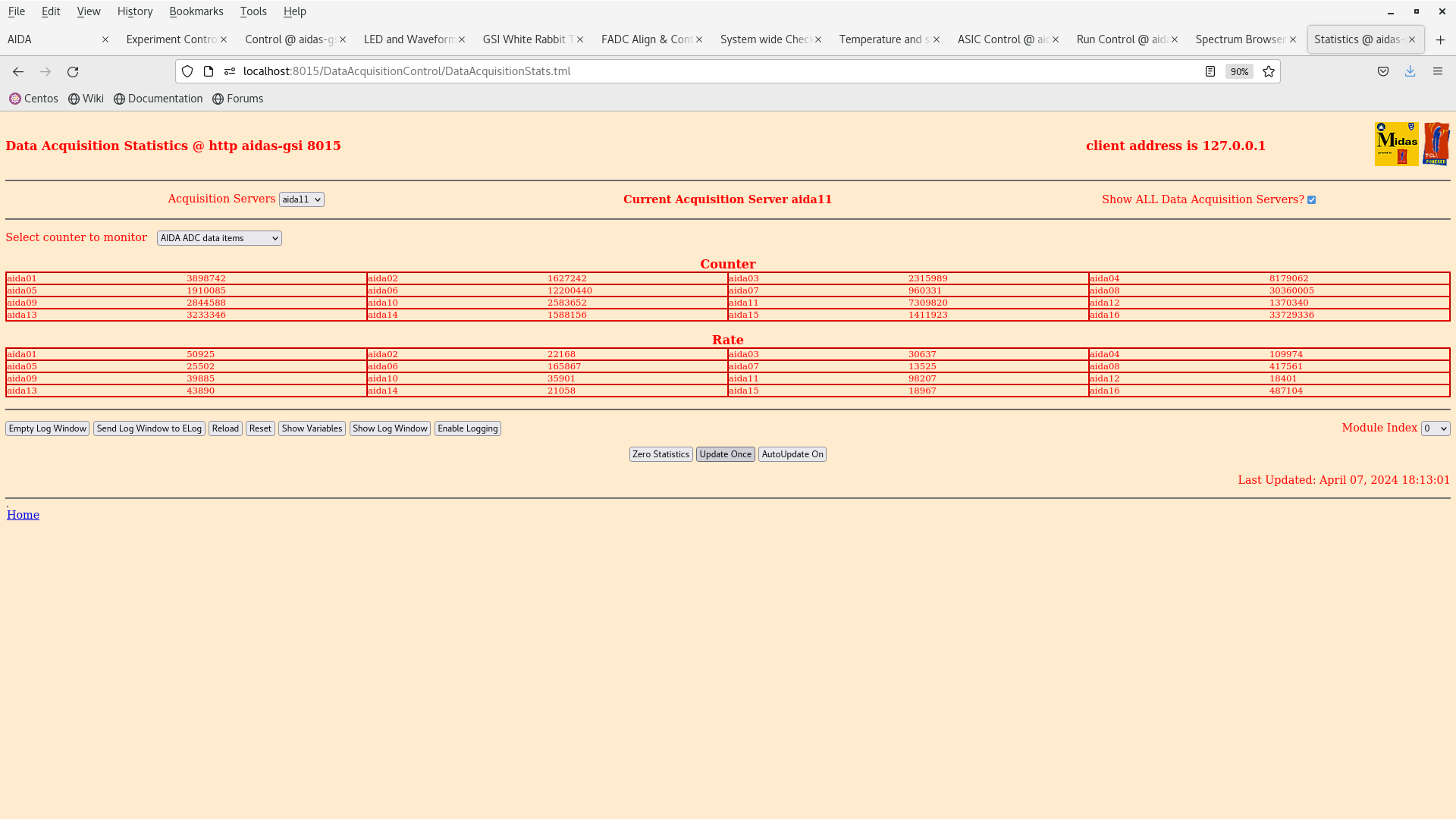

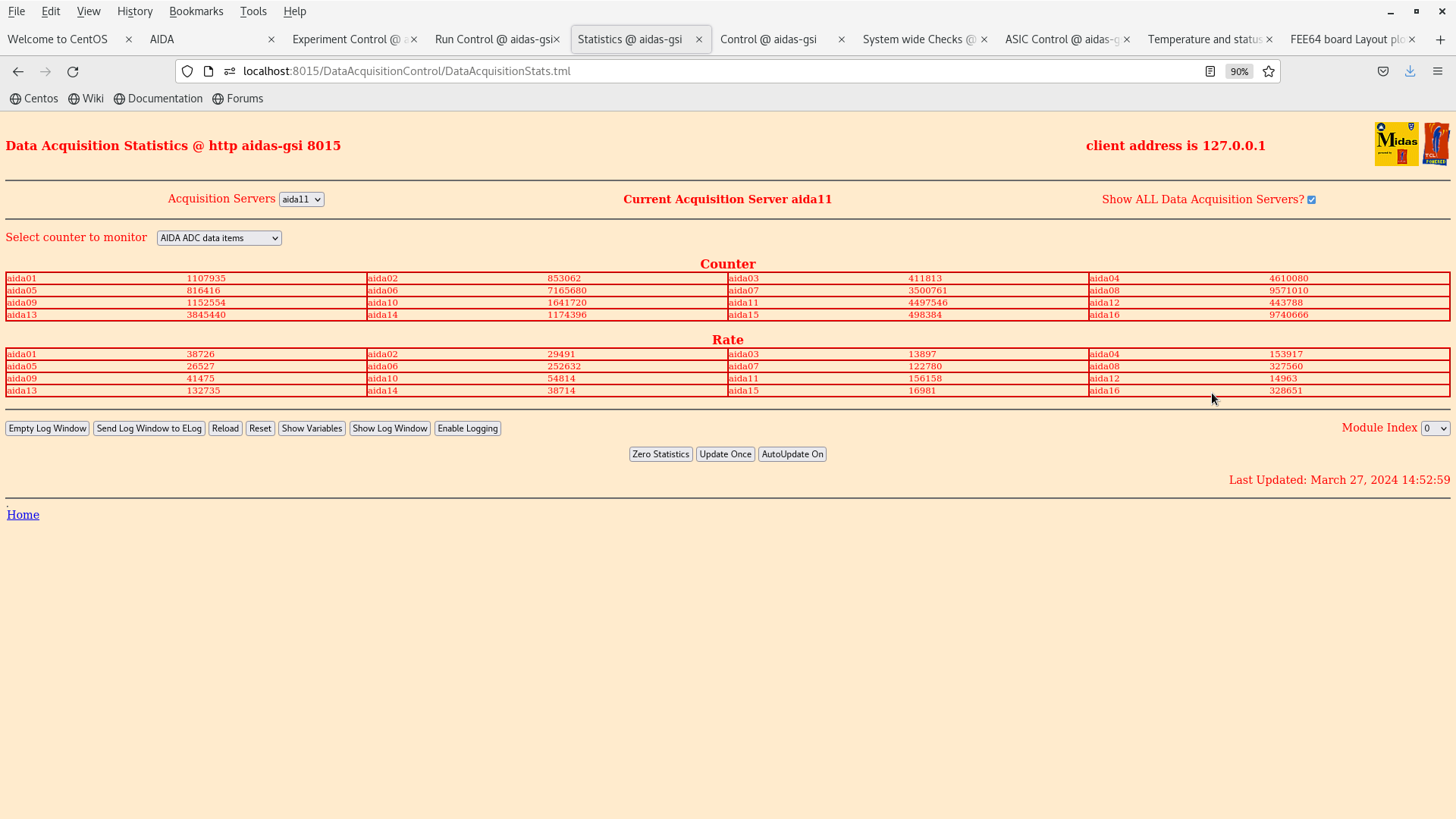

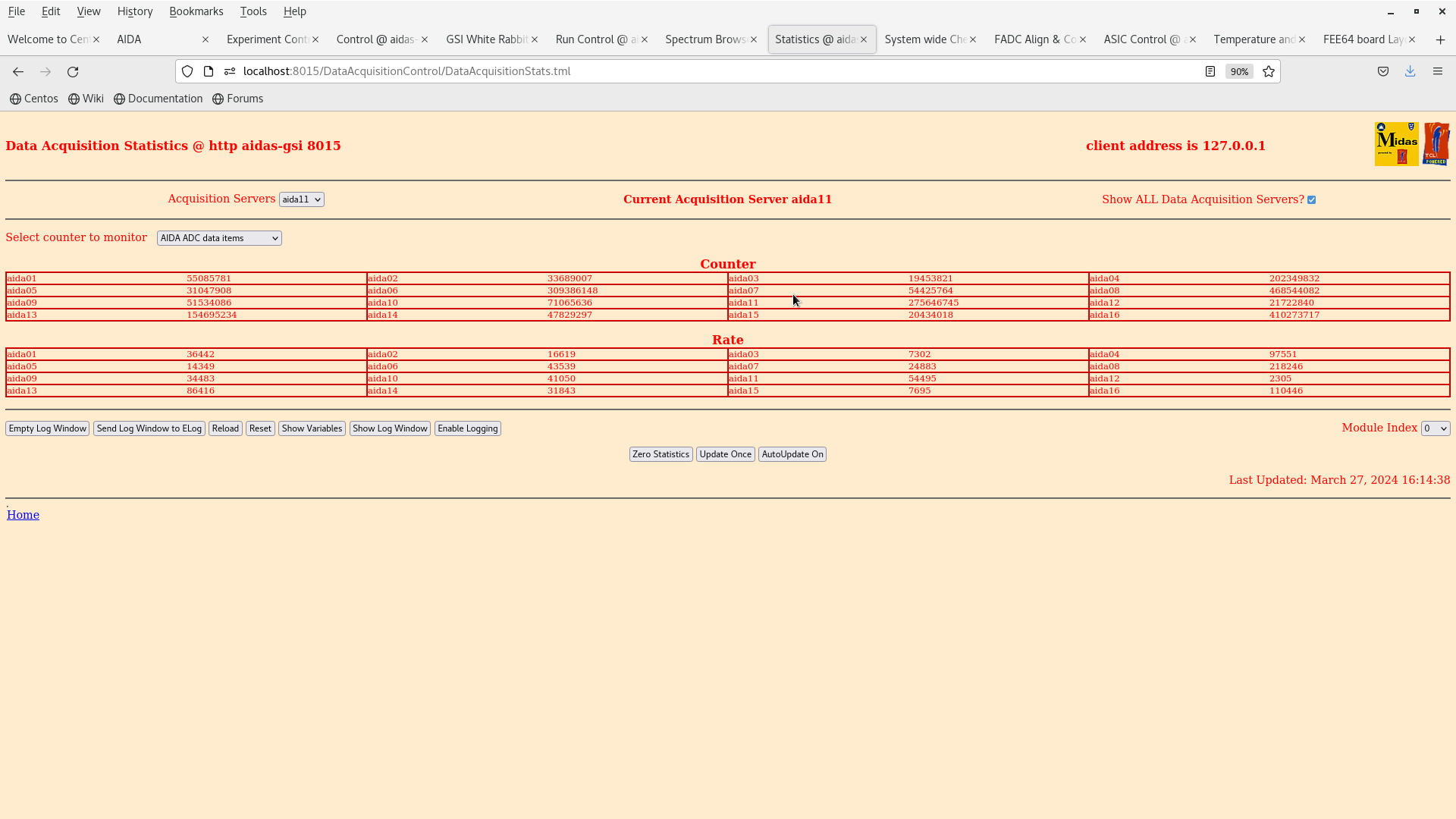

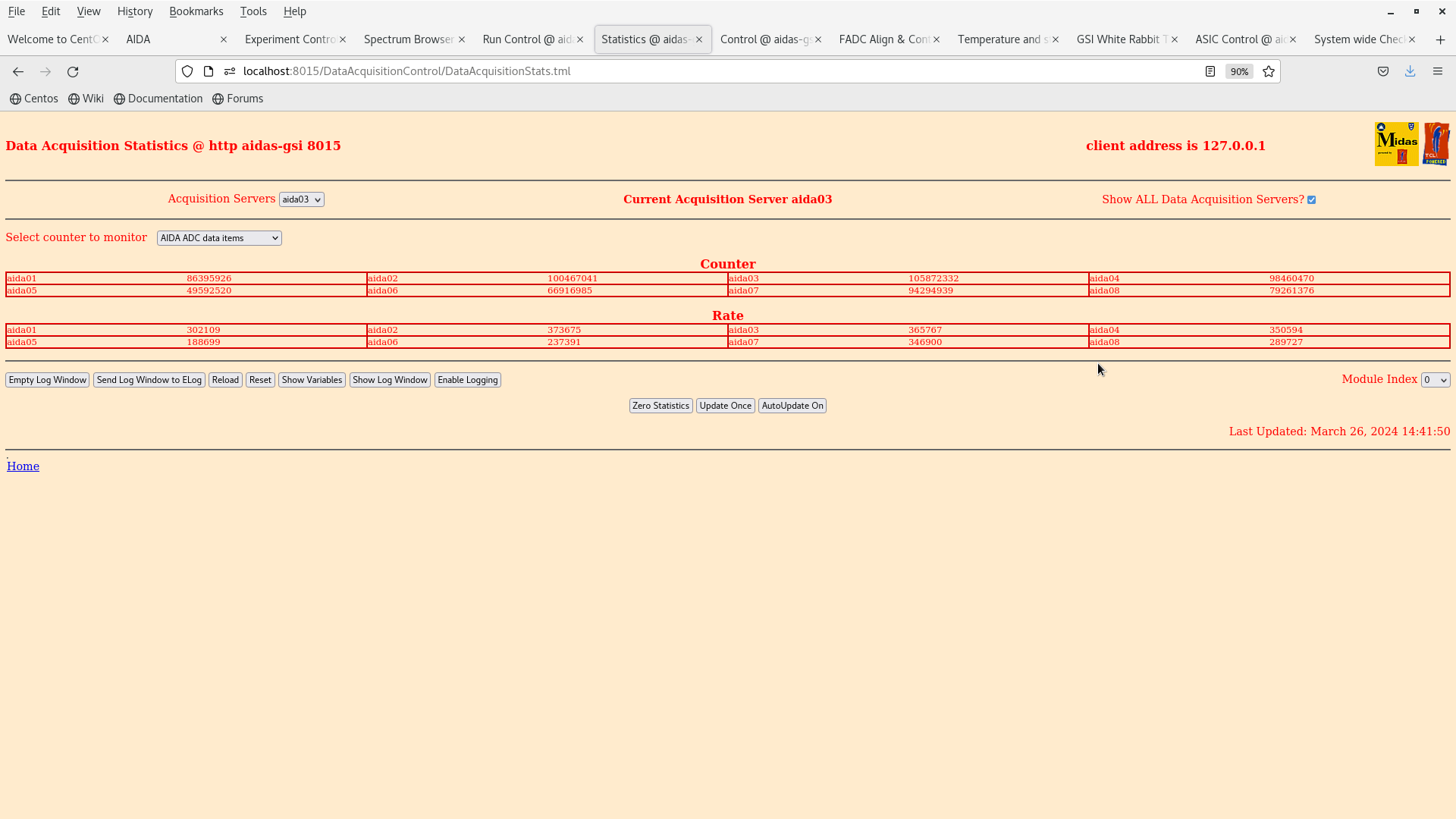

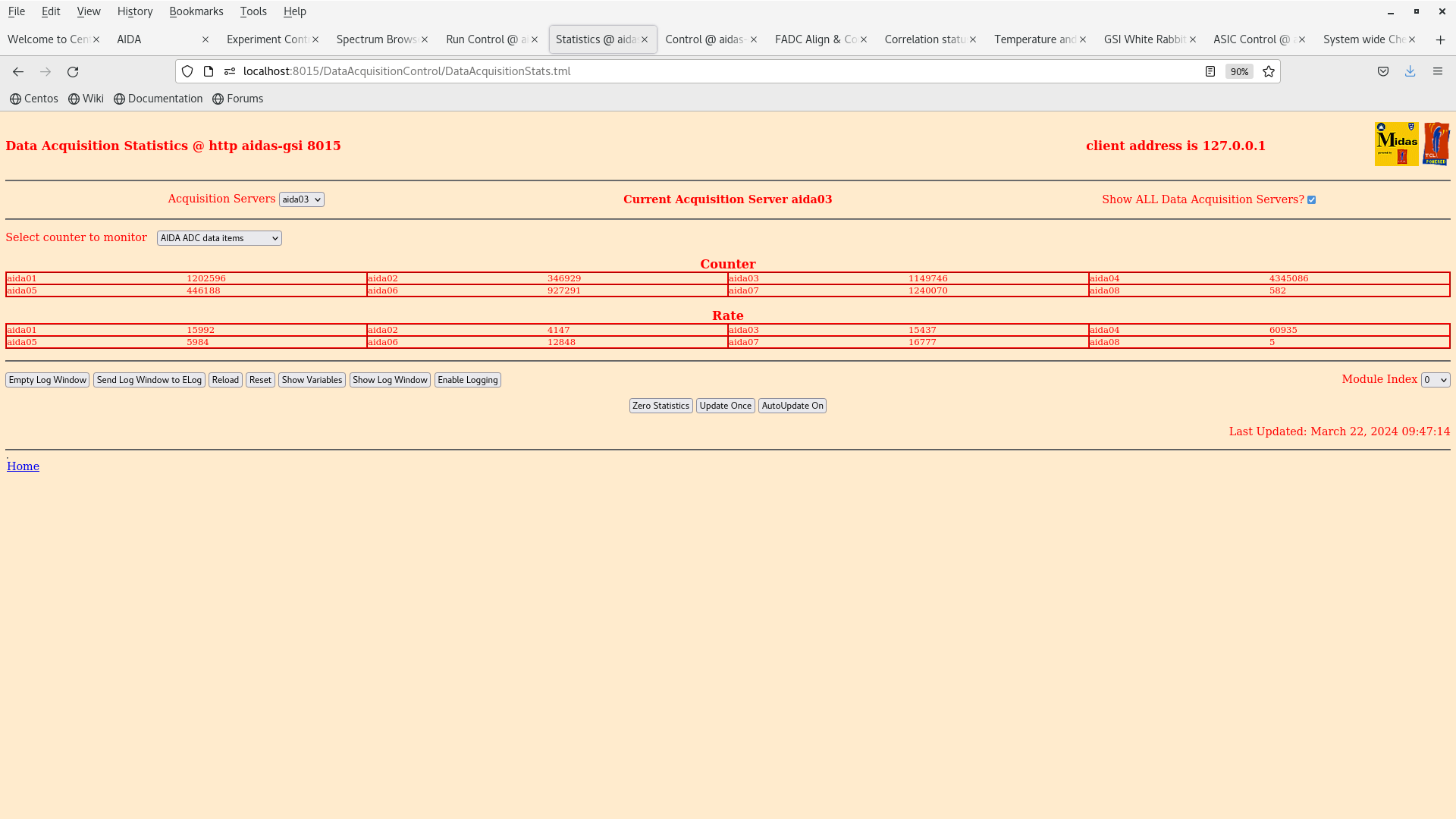

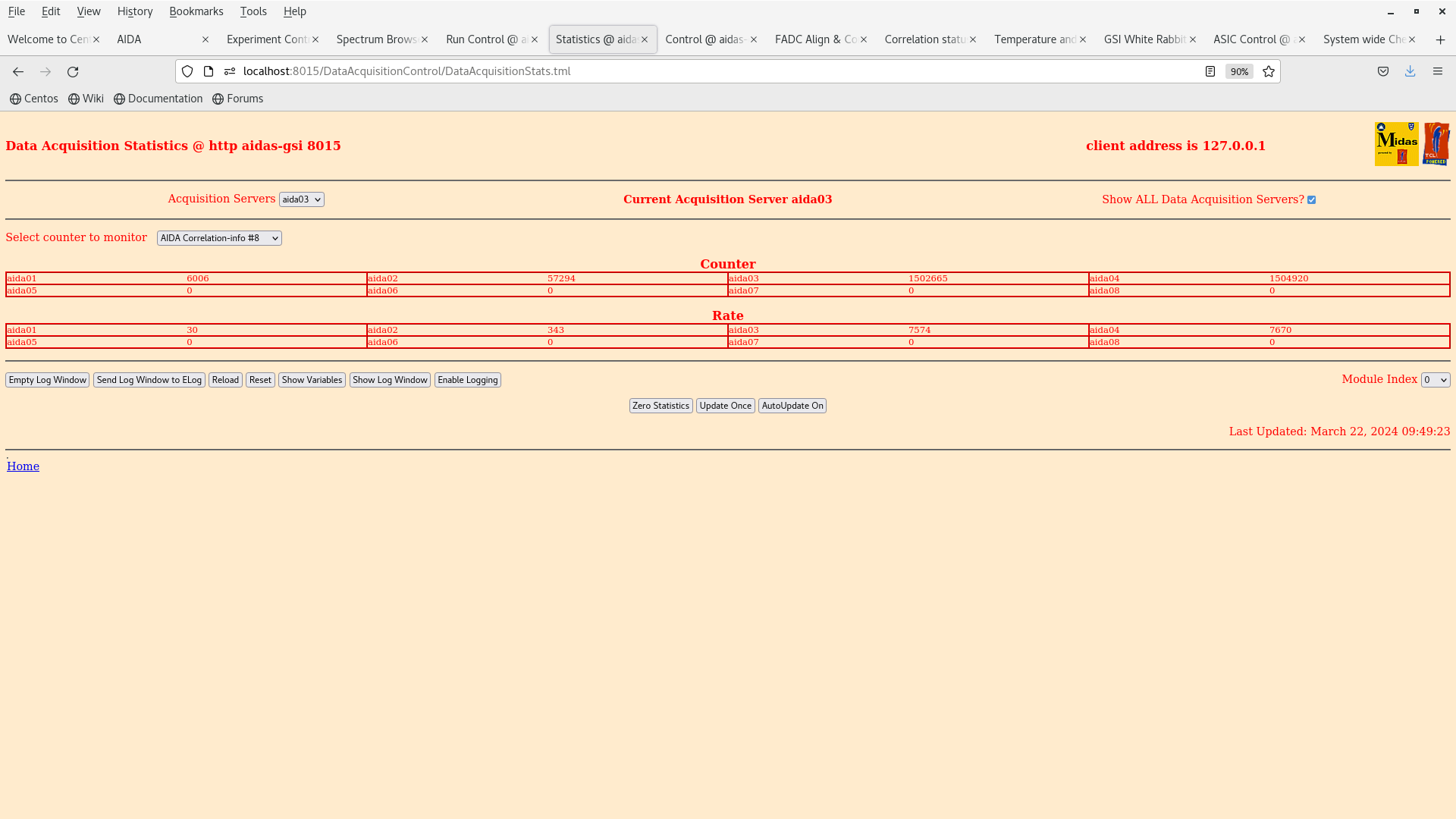

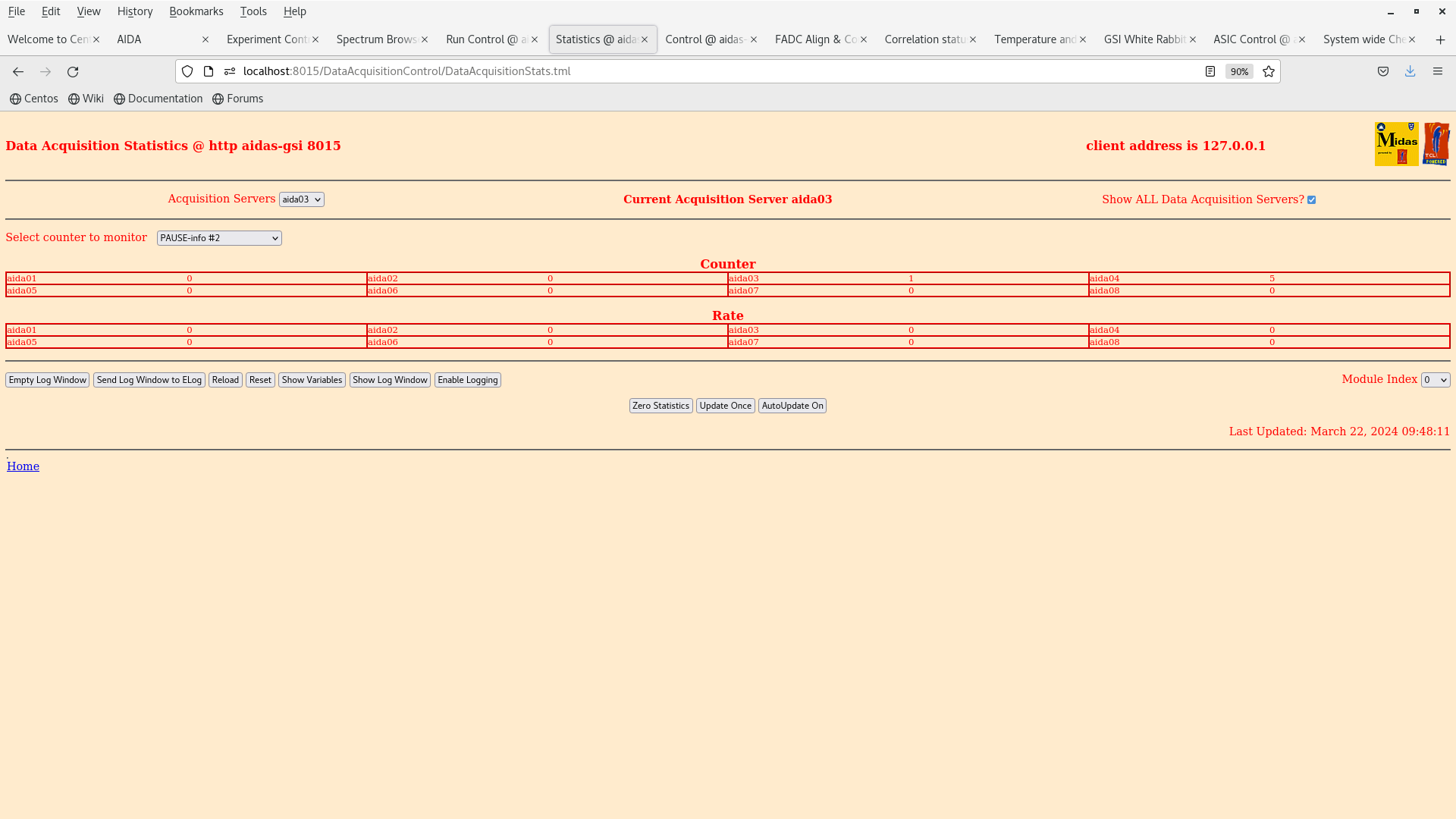

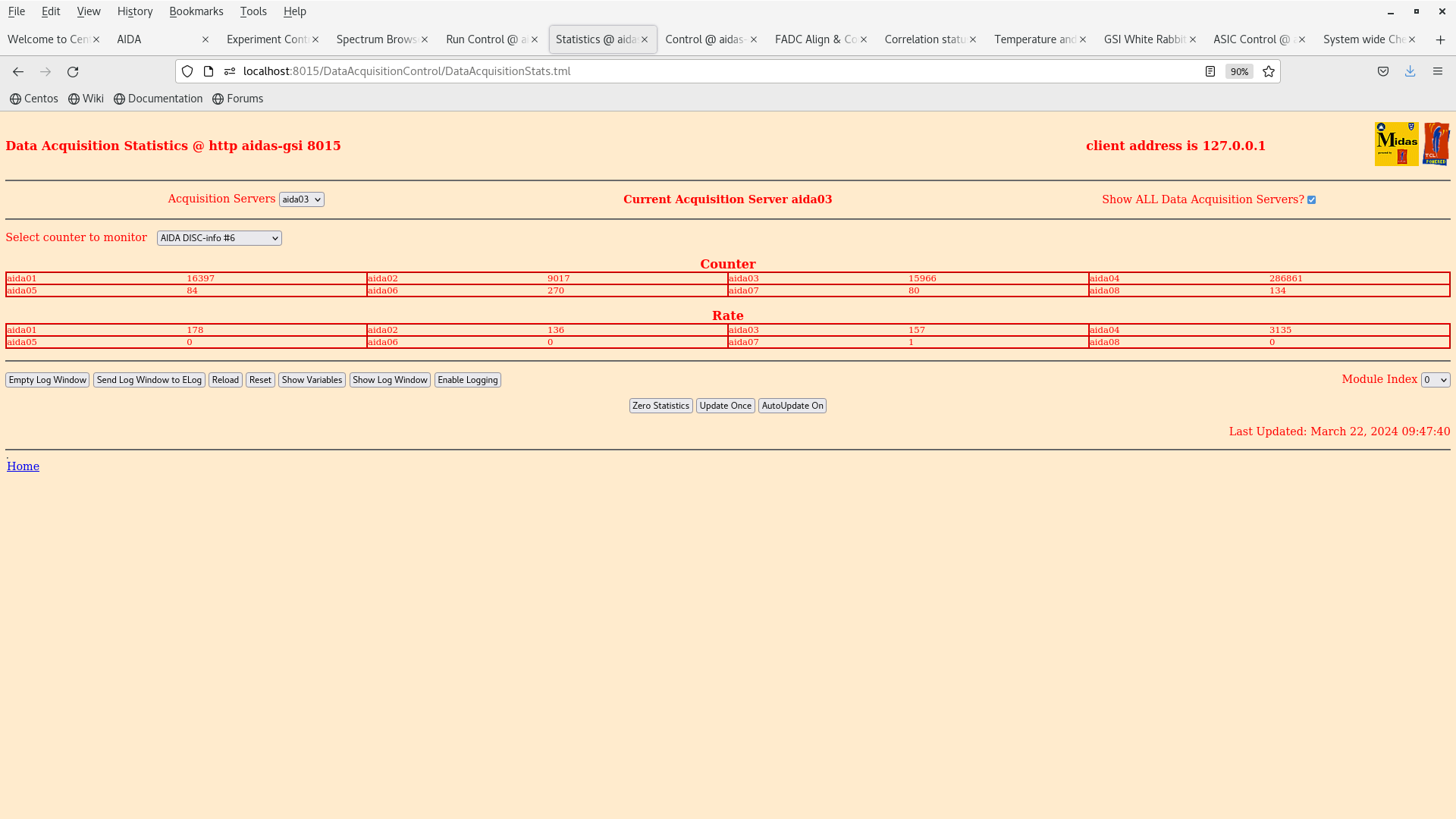

info code 4, correlation scaler, PAUSE, RESUME, DISC, ADC data item stats - attachments 5-10

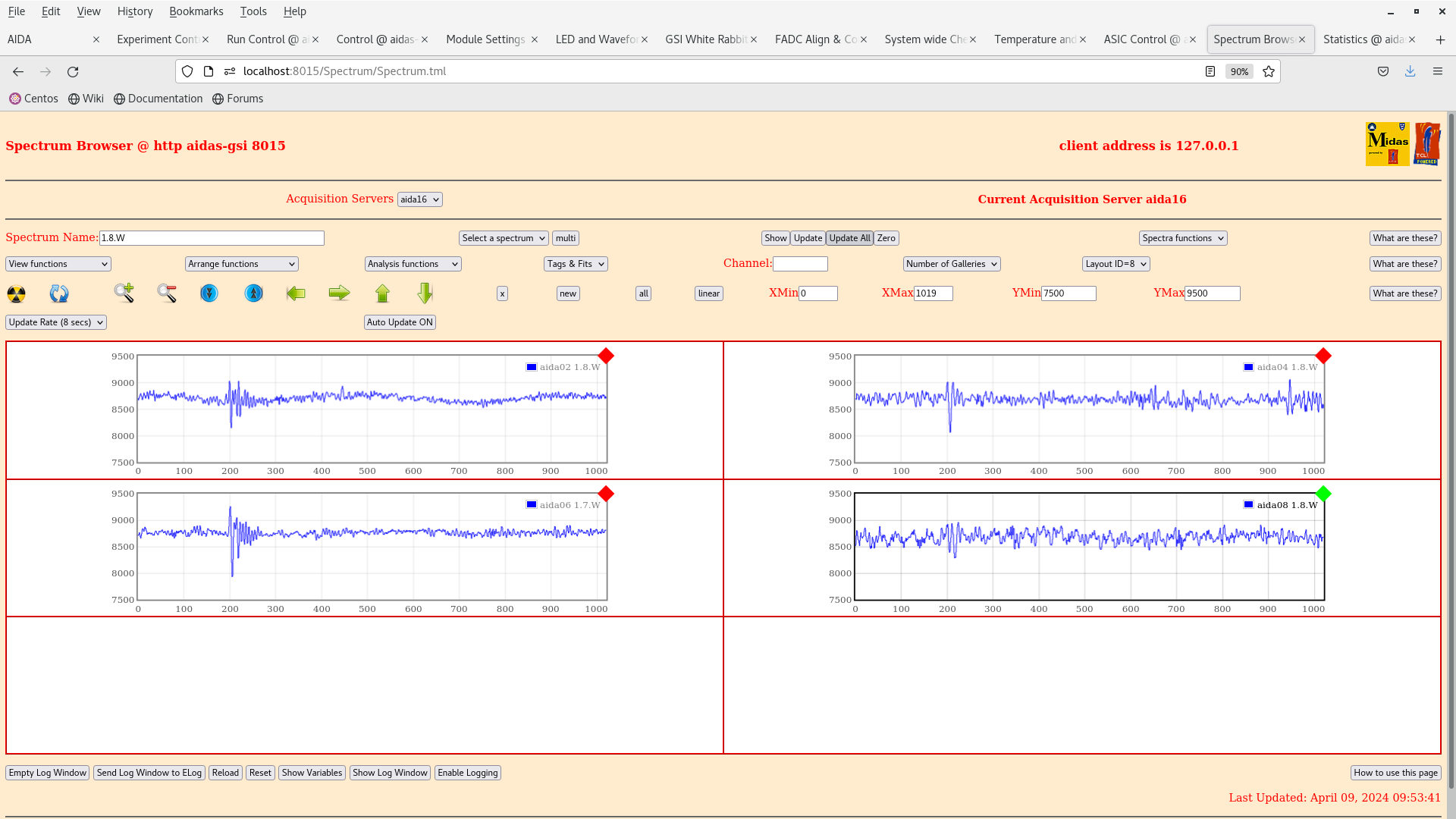

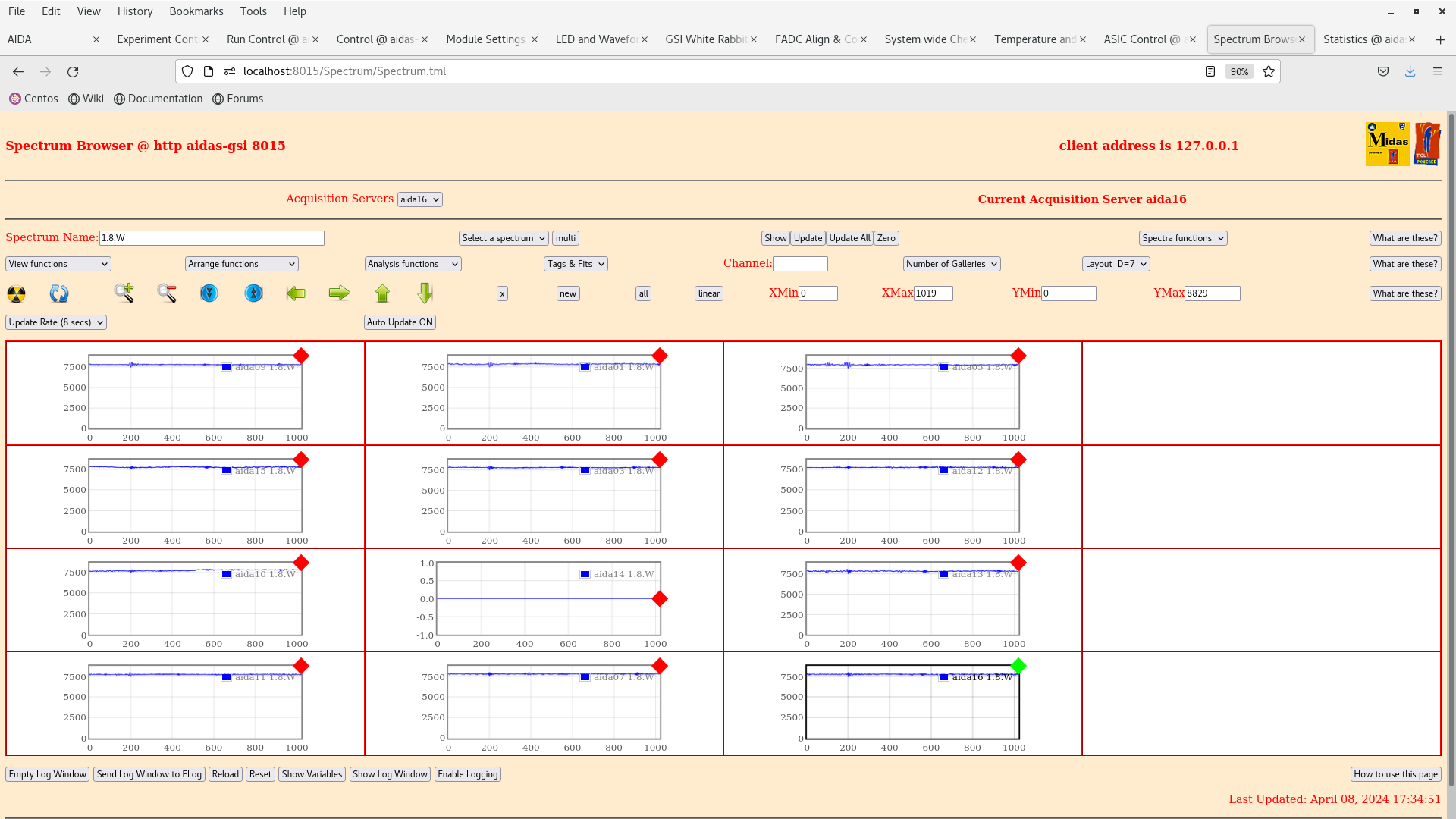

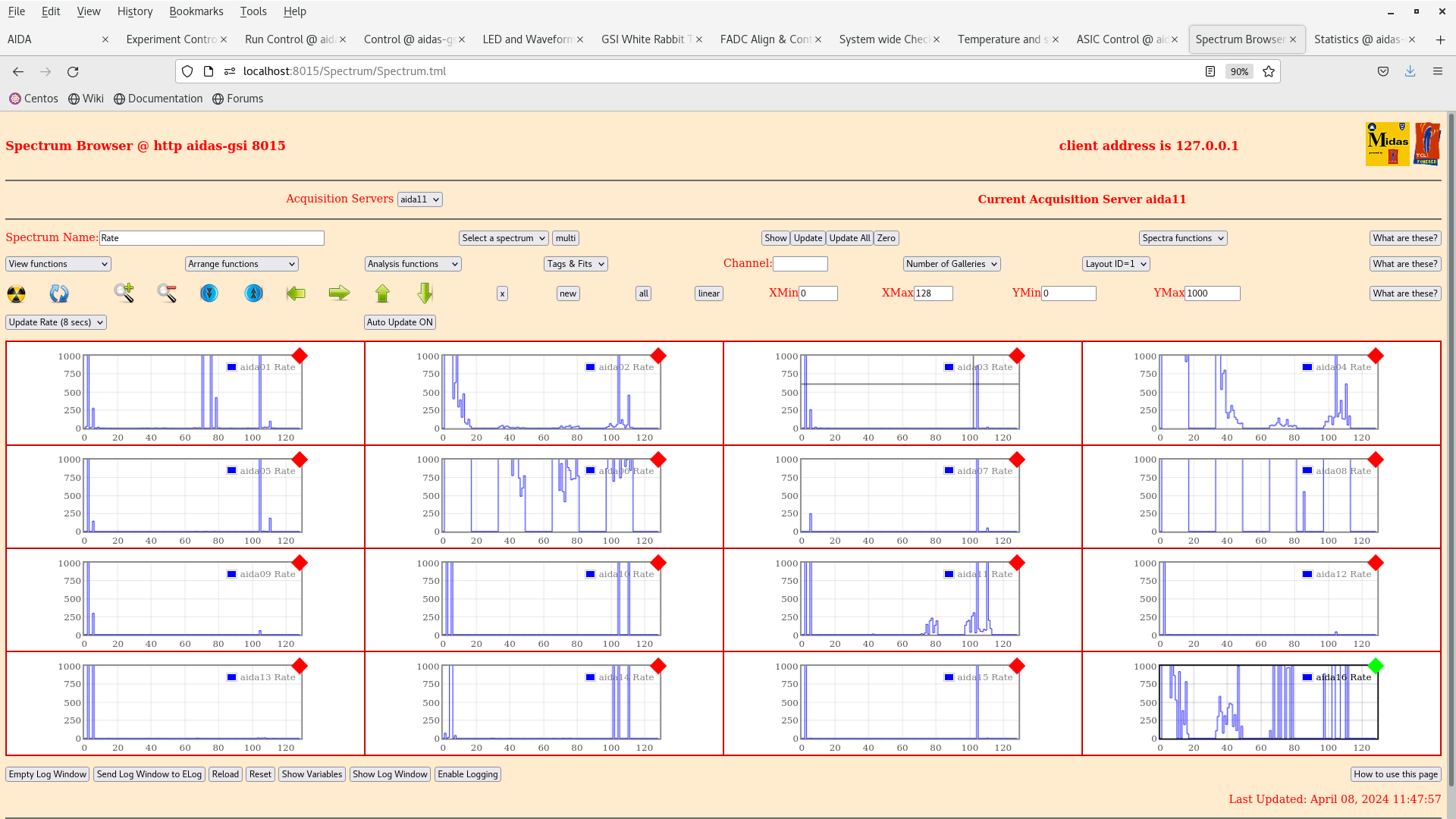

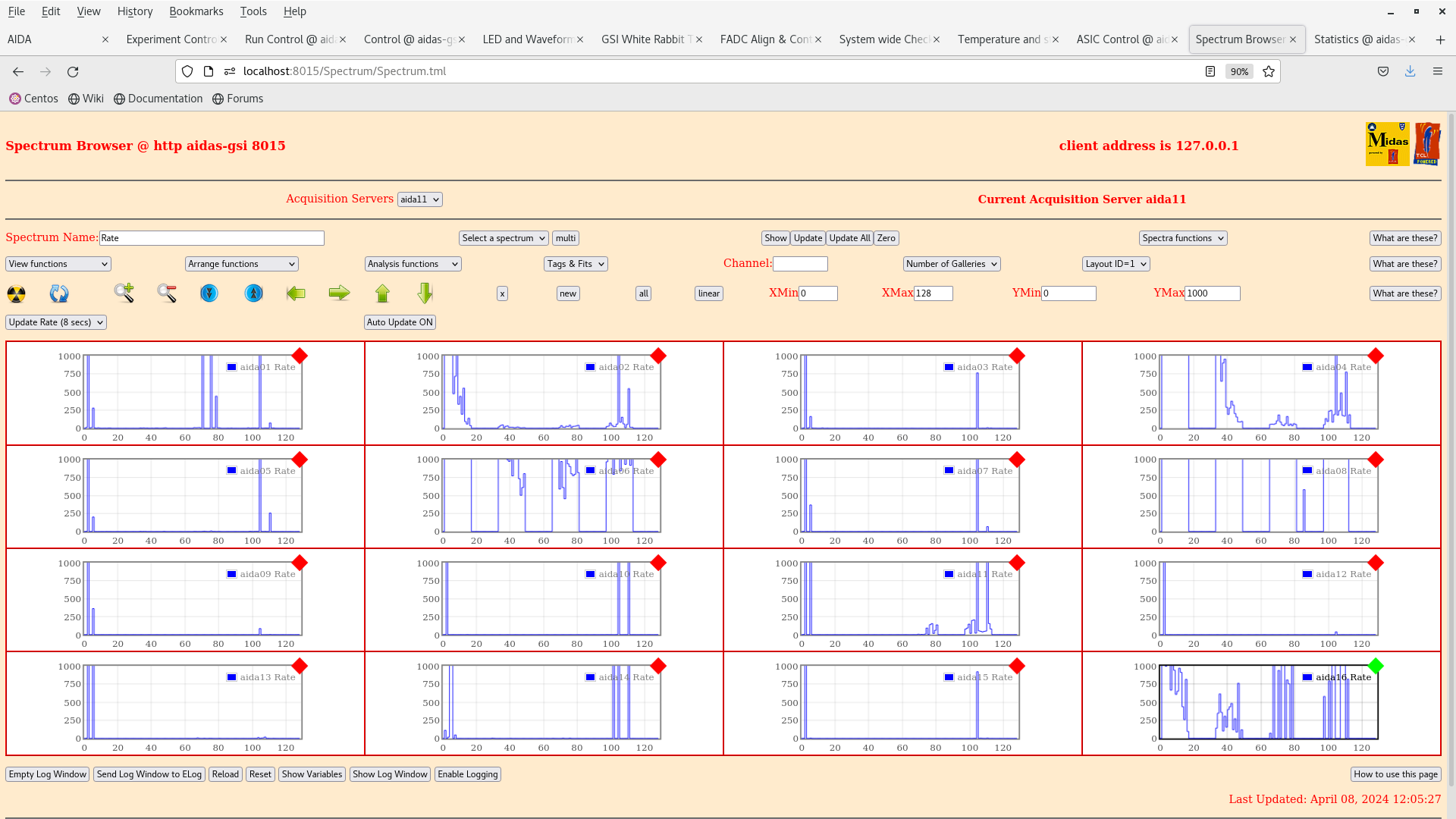

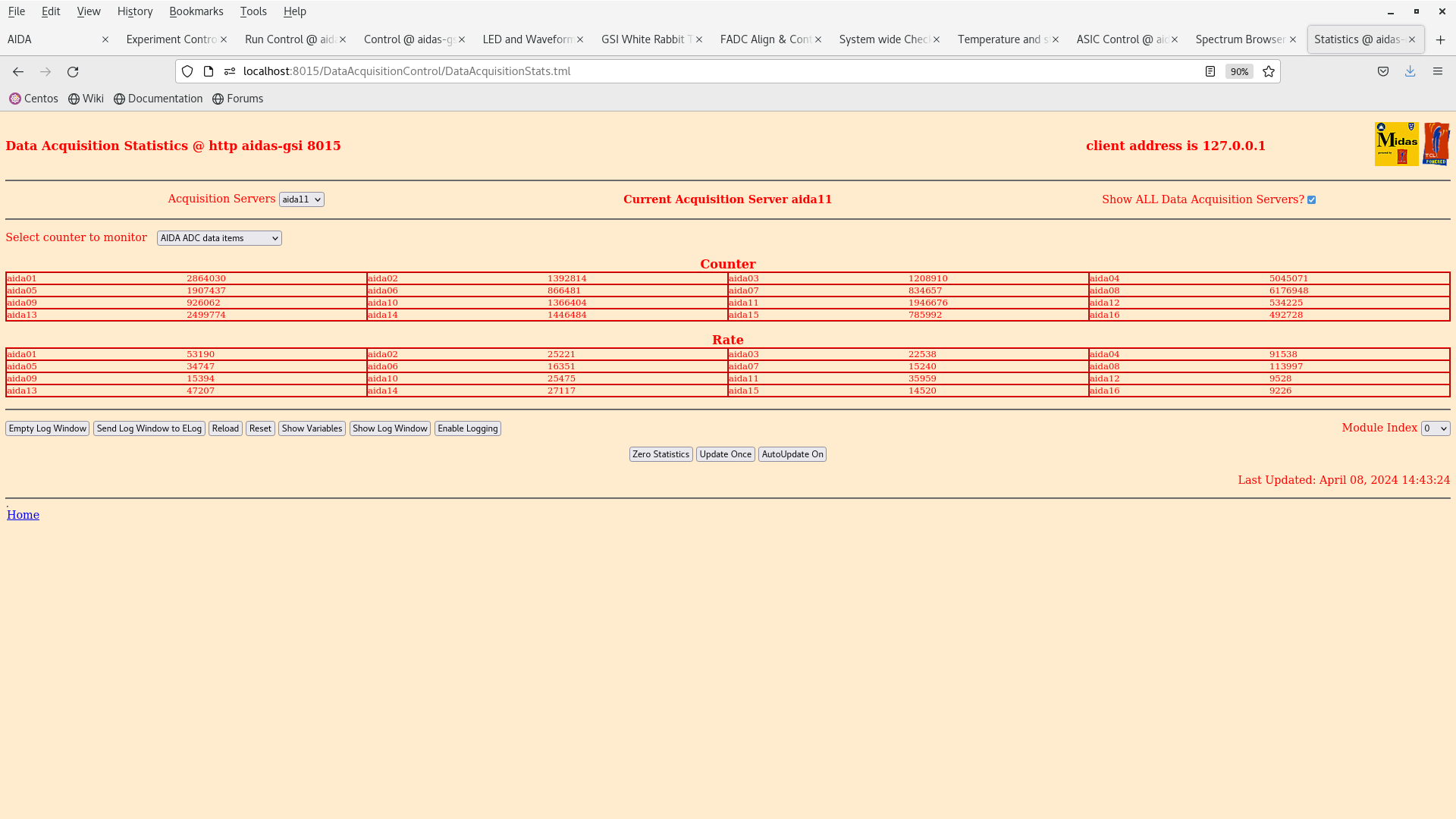

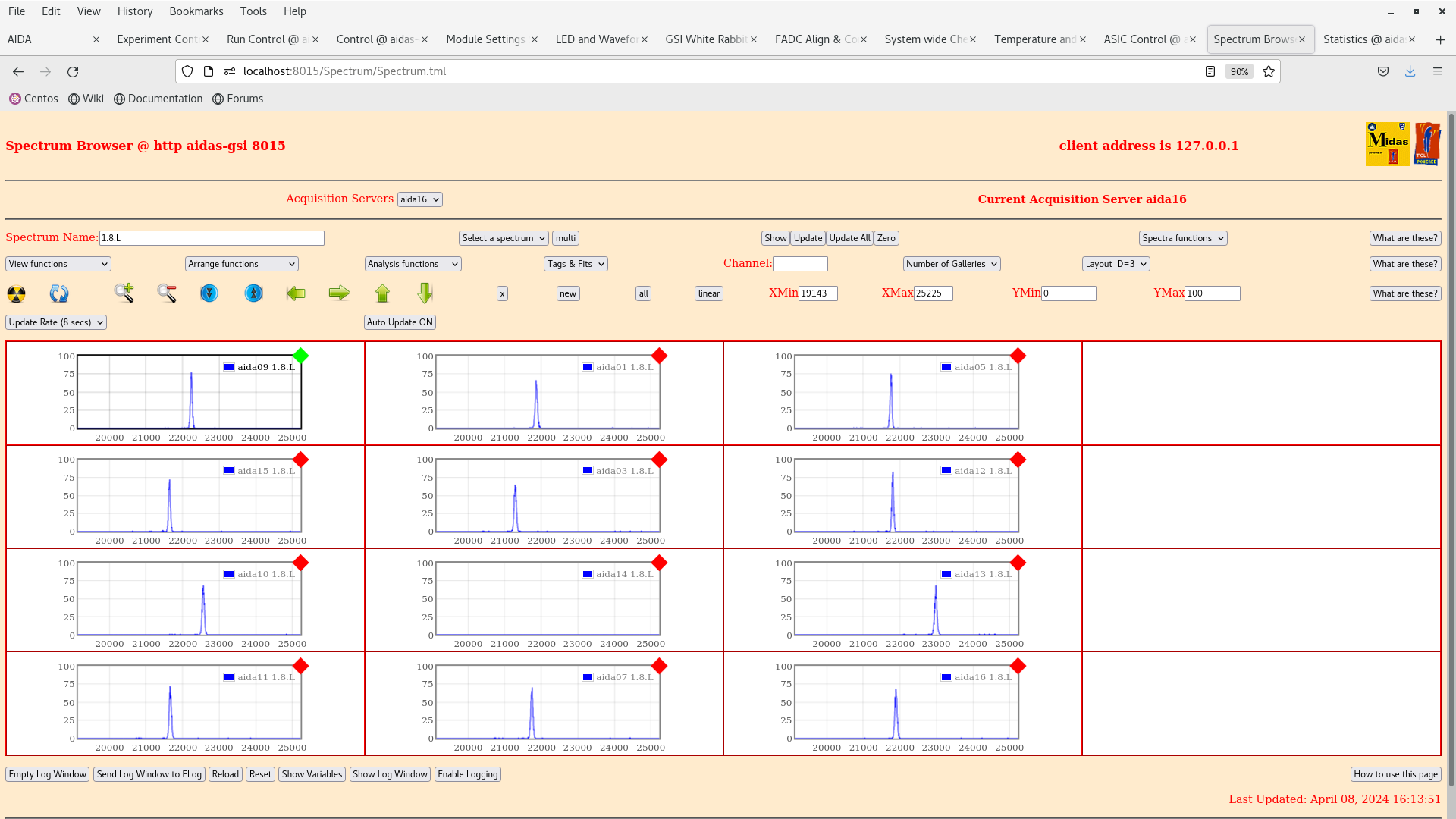

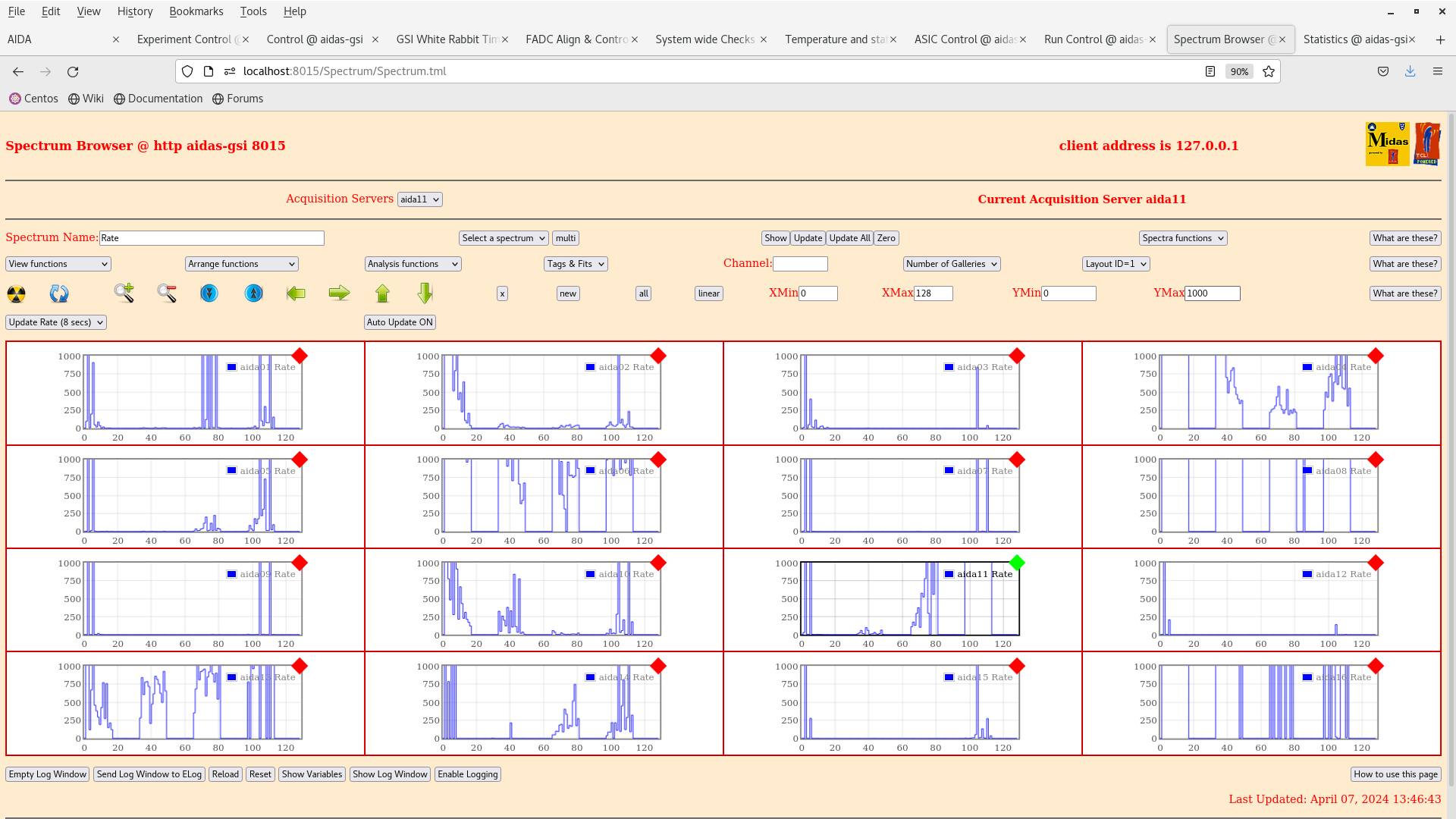

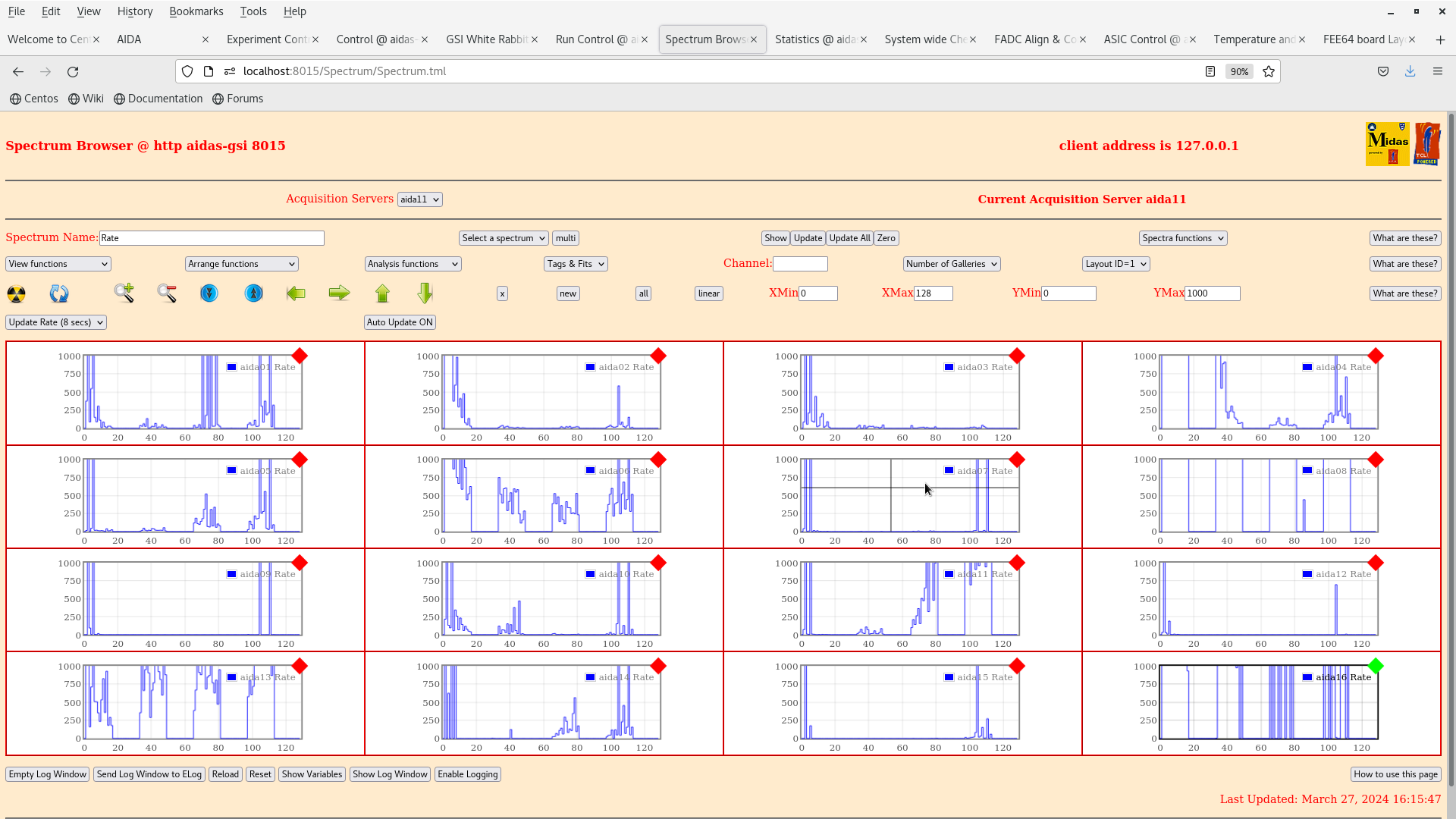

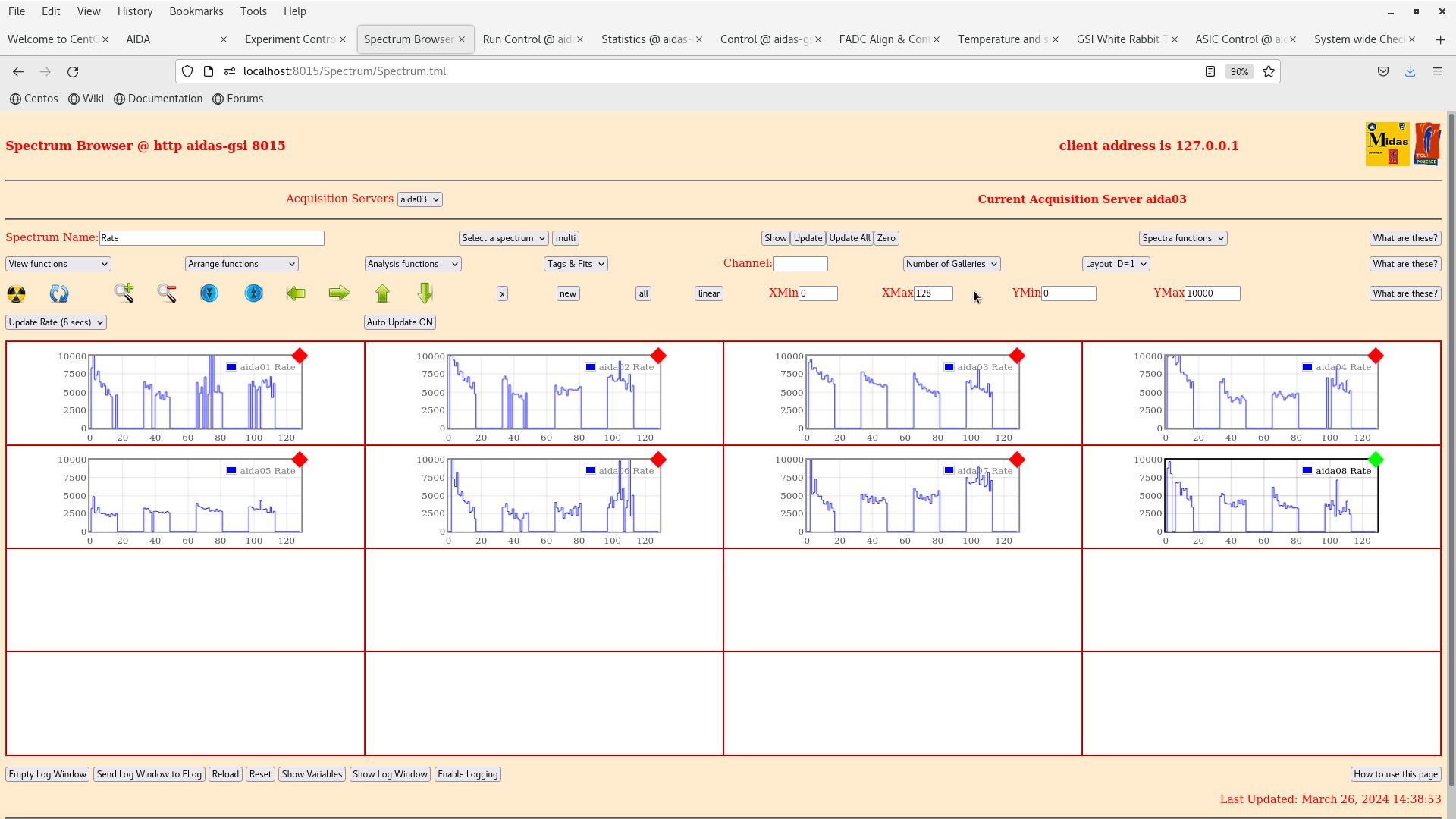

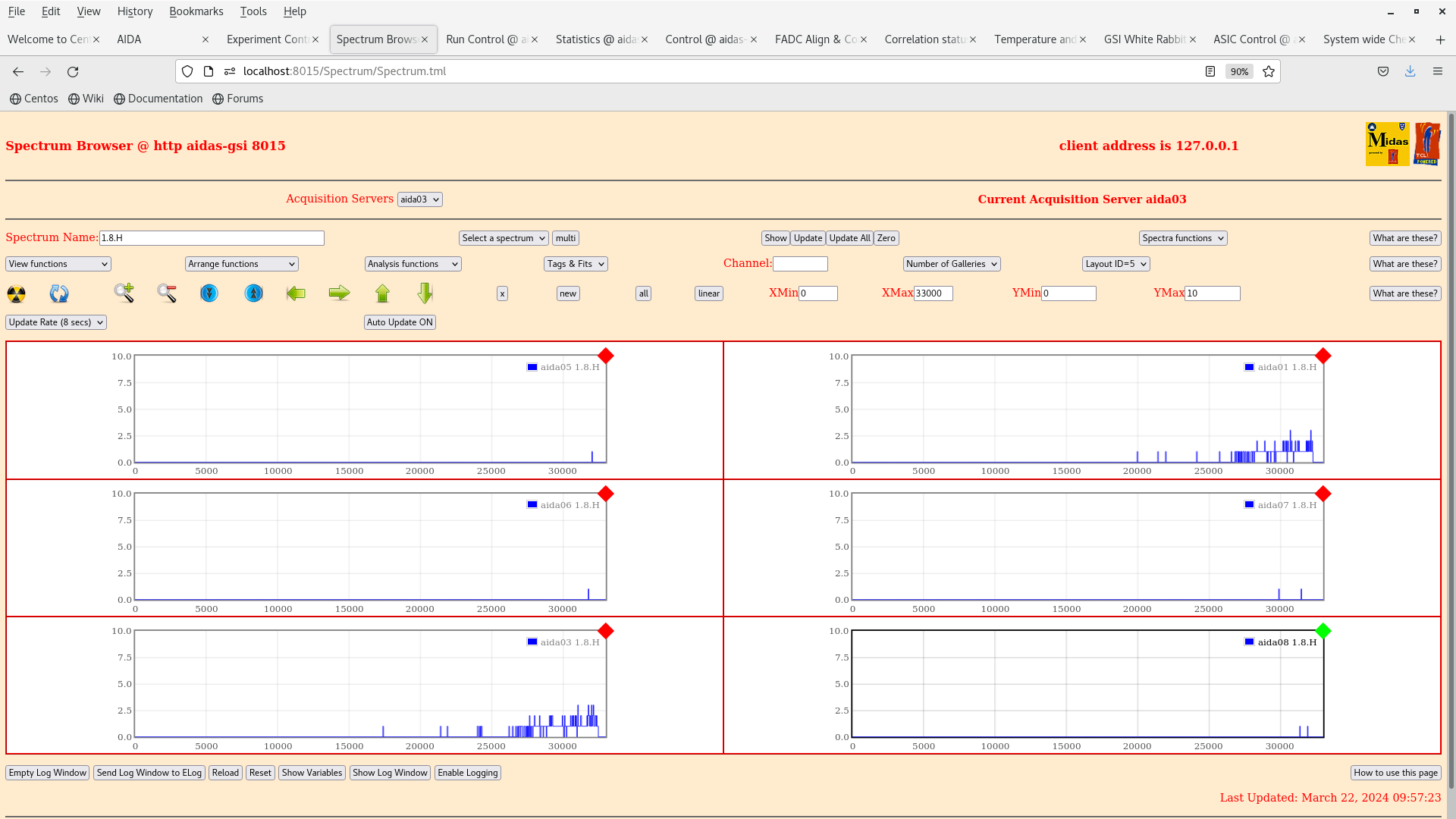

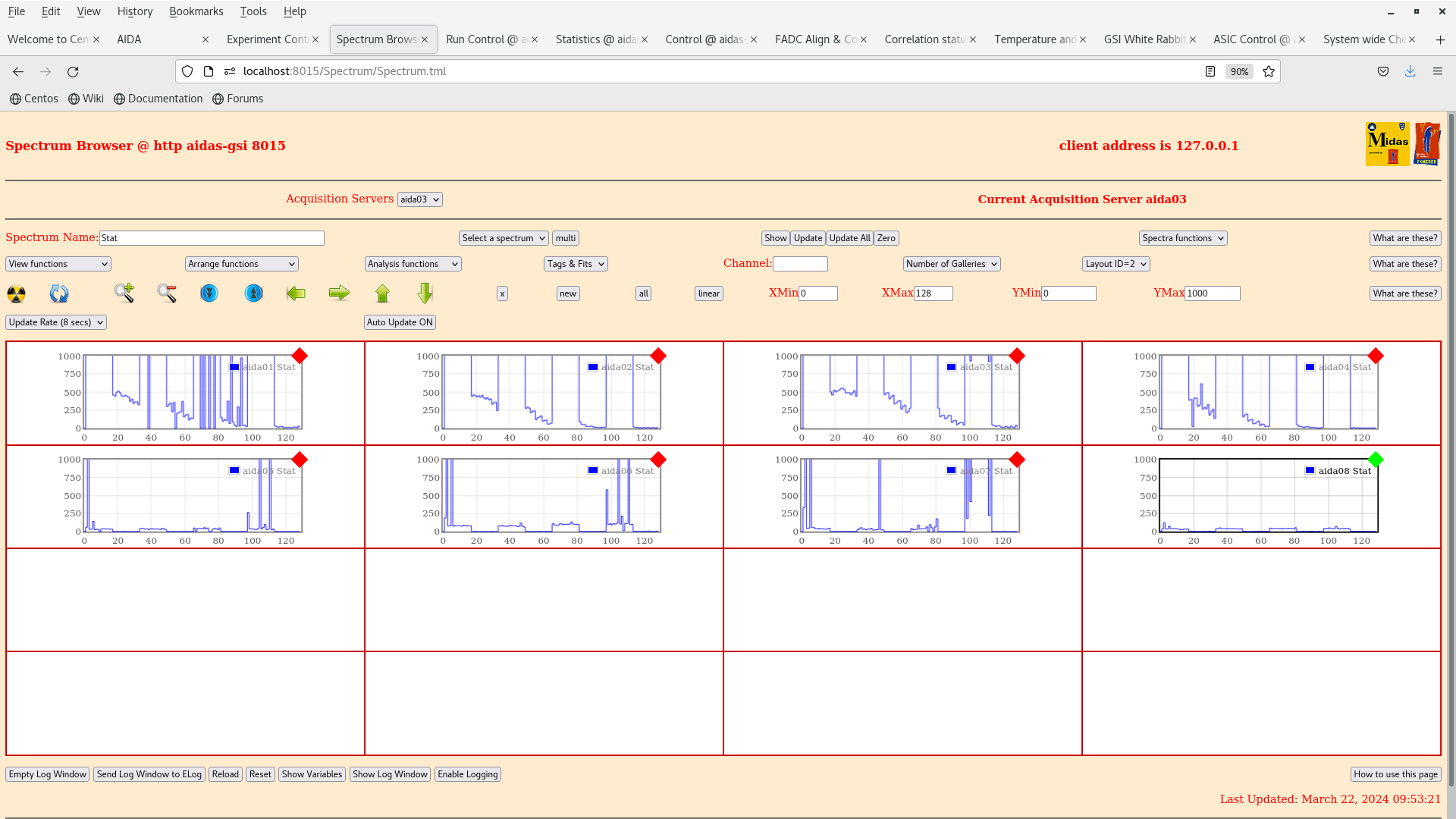

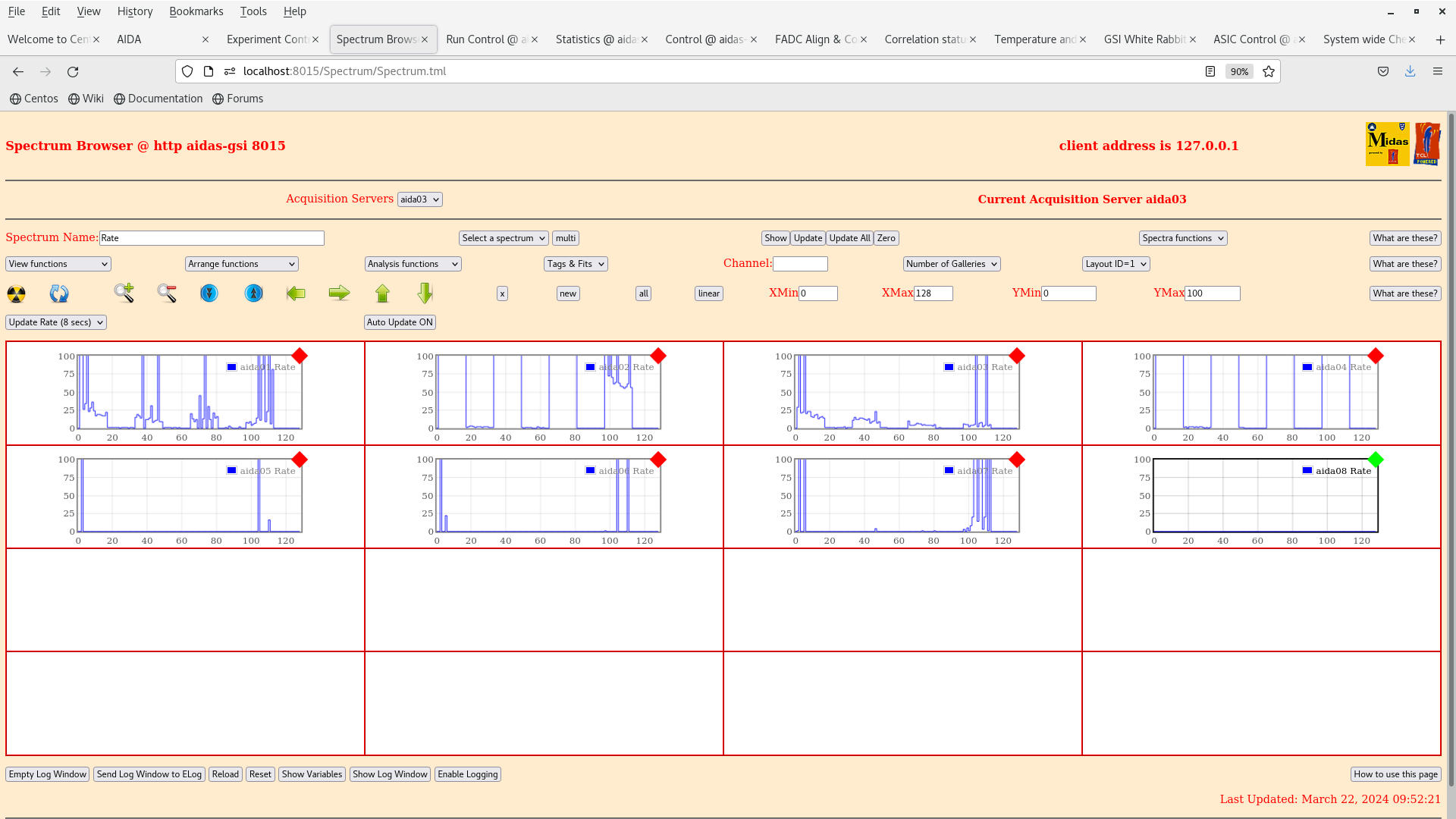

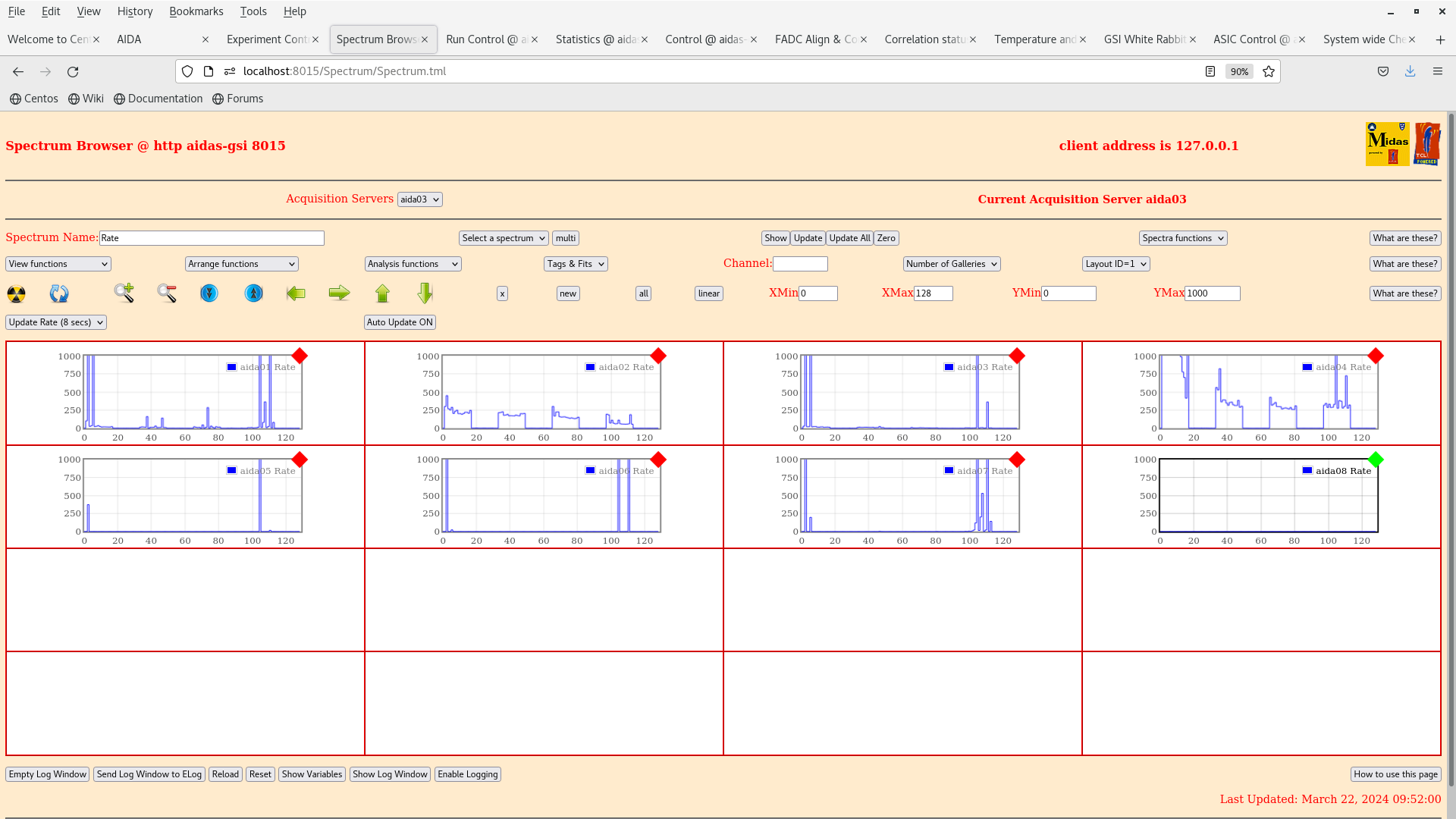

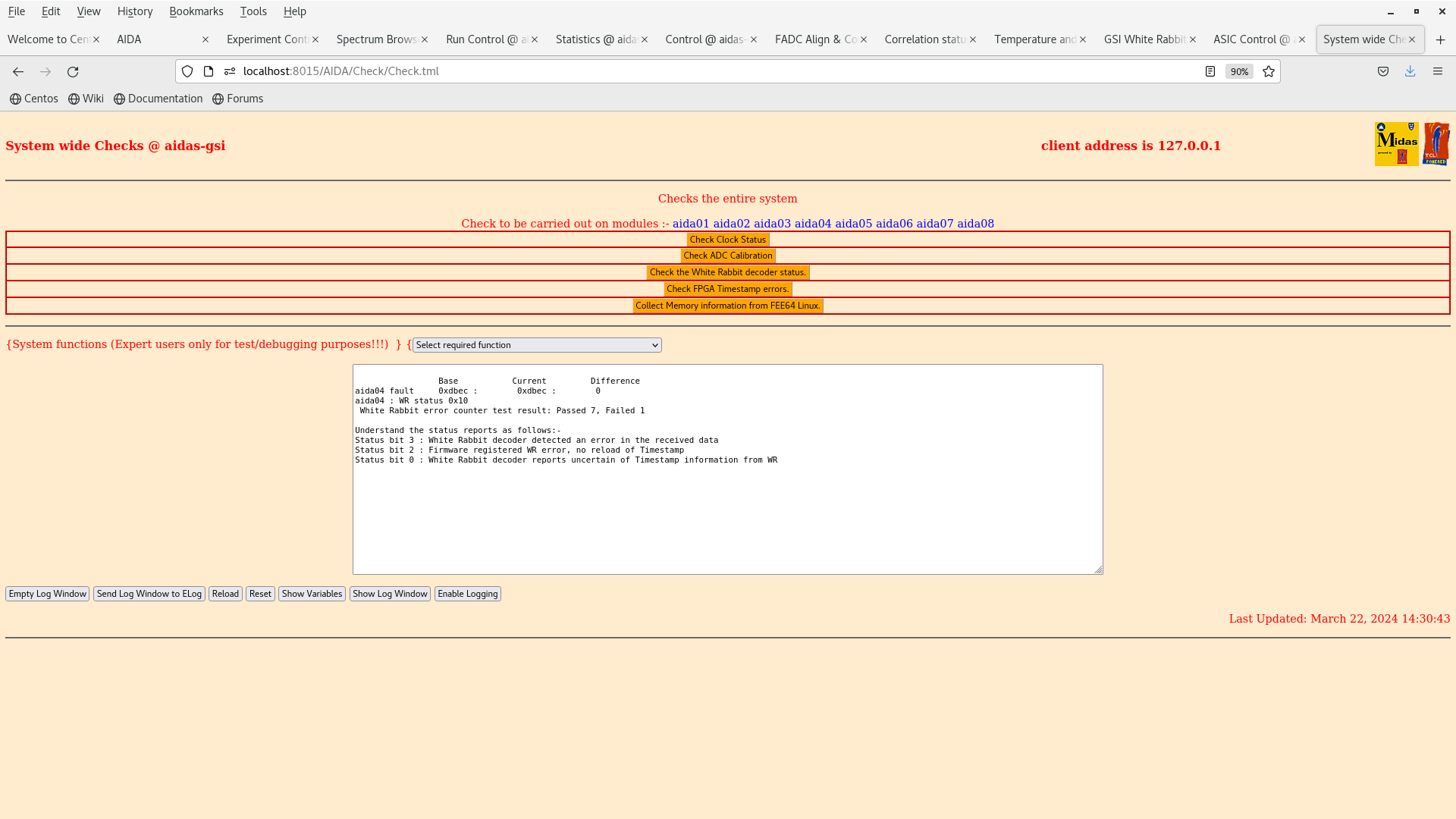

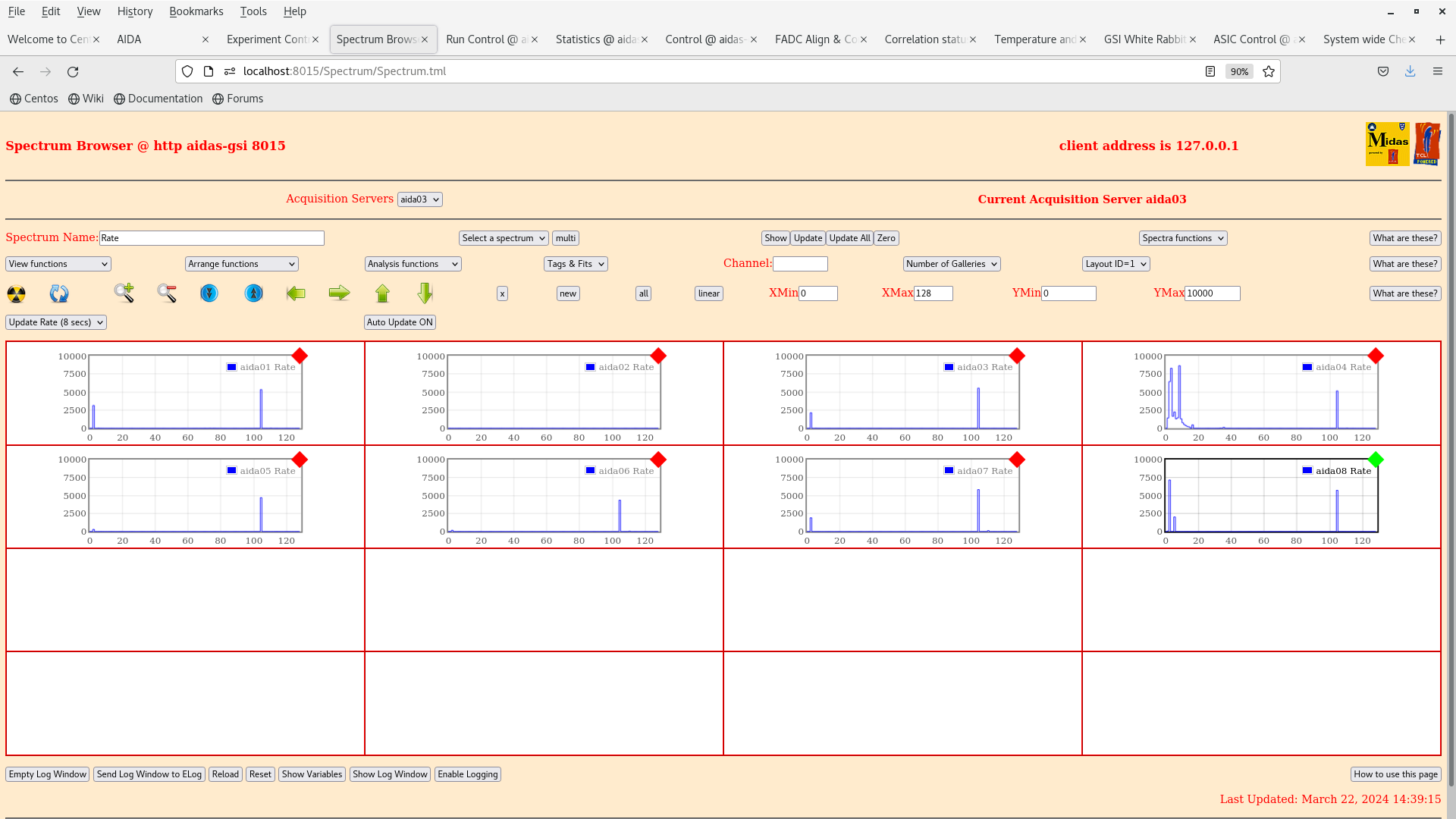

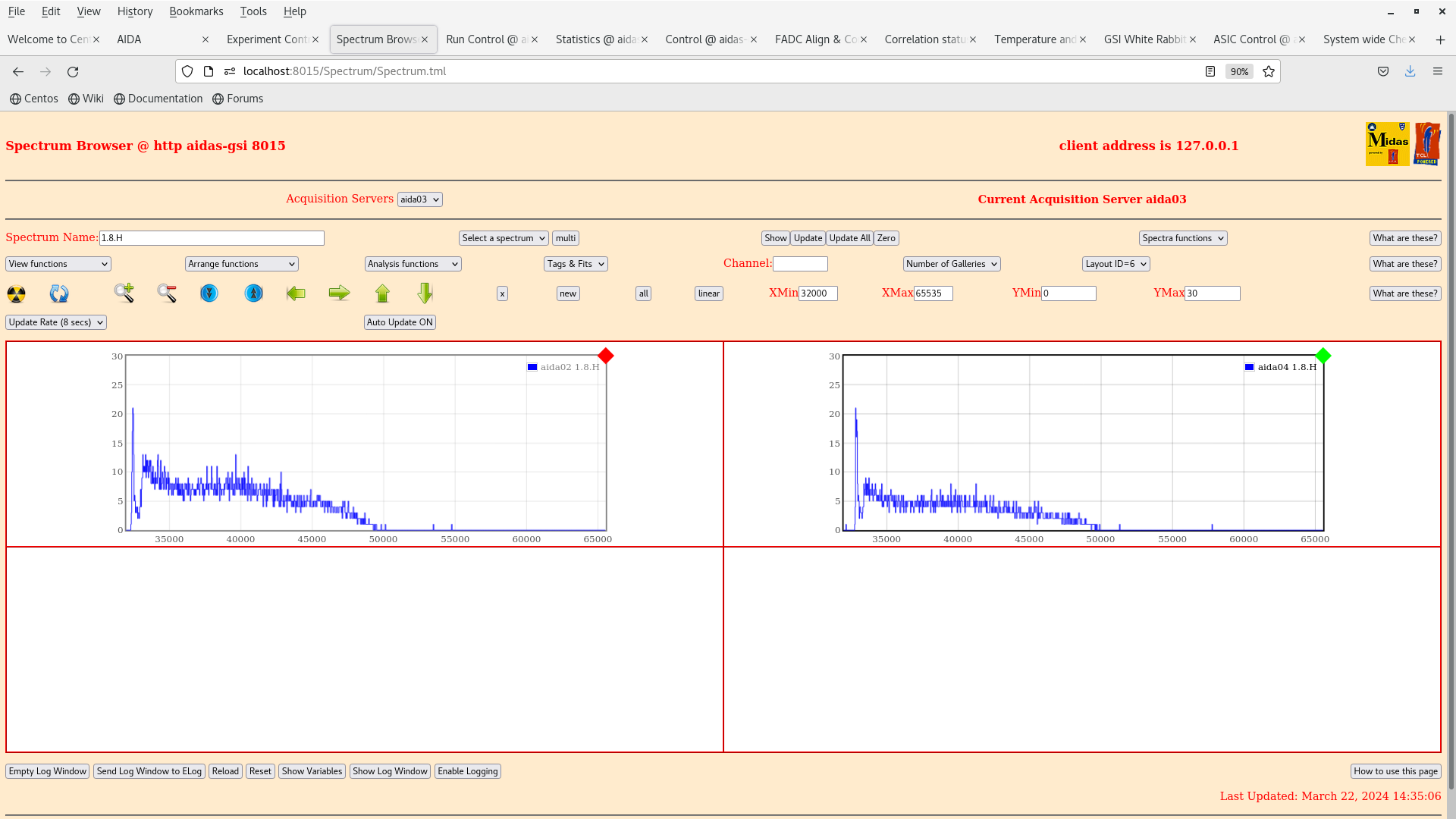

per FEE64 Rate spectra - attachments 11

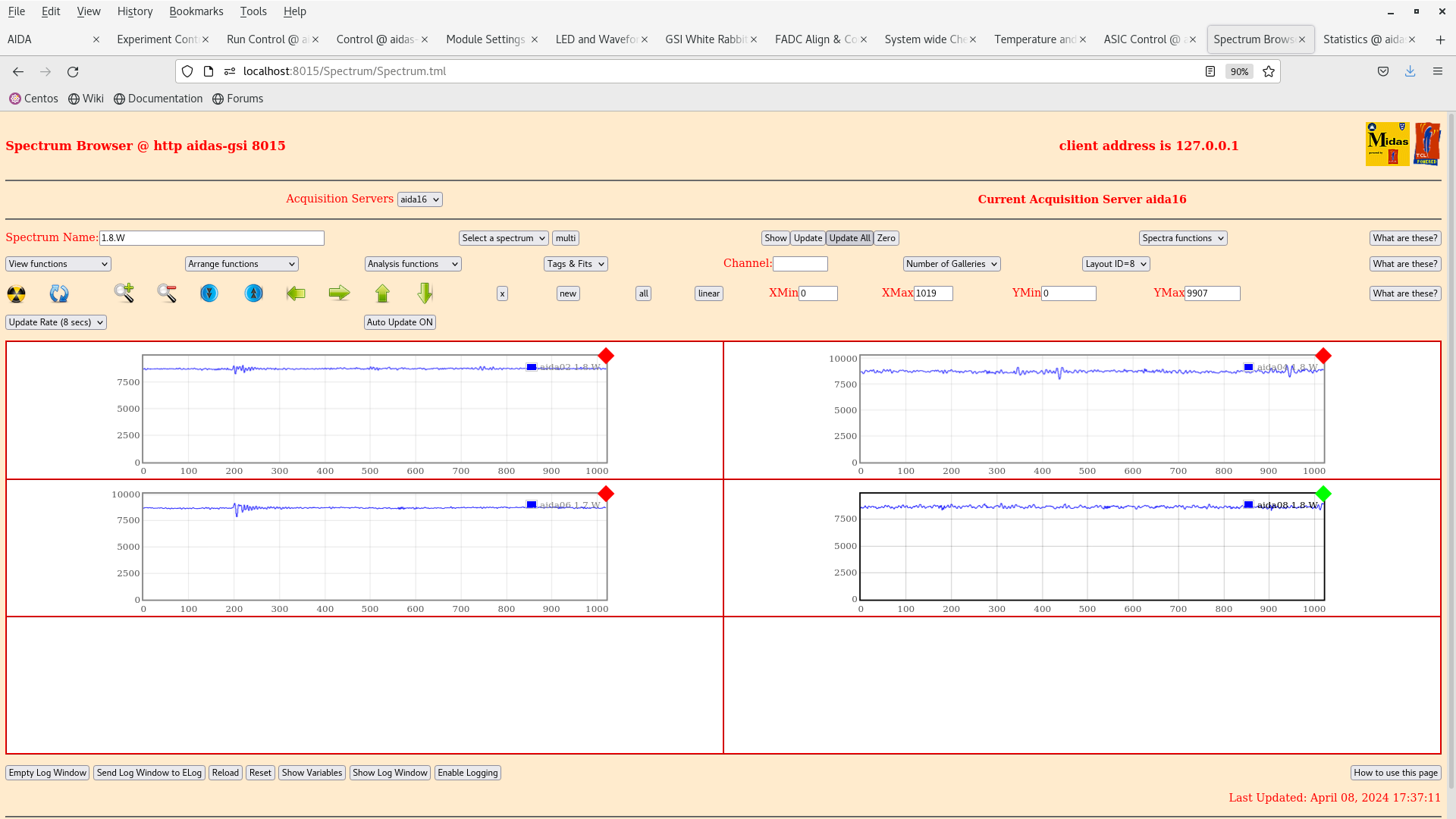

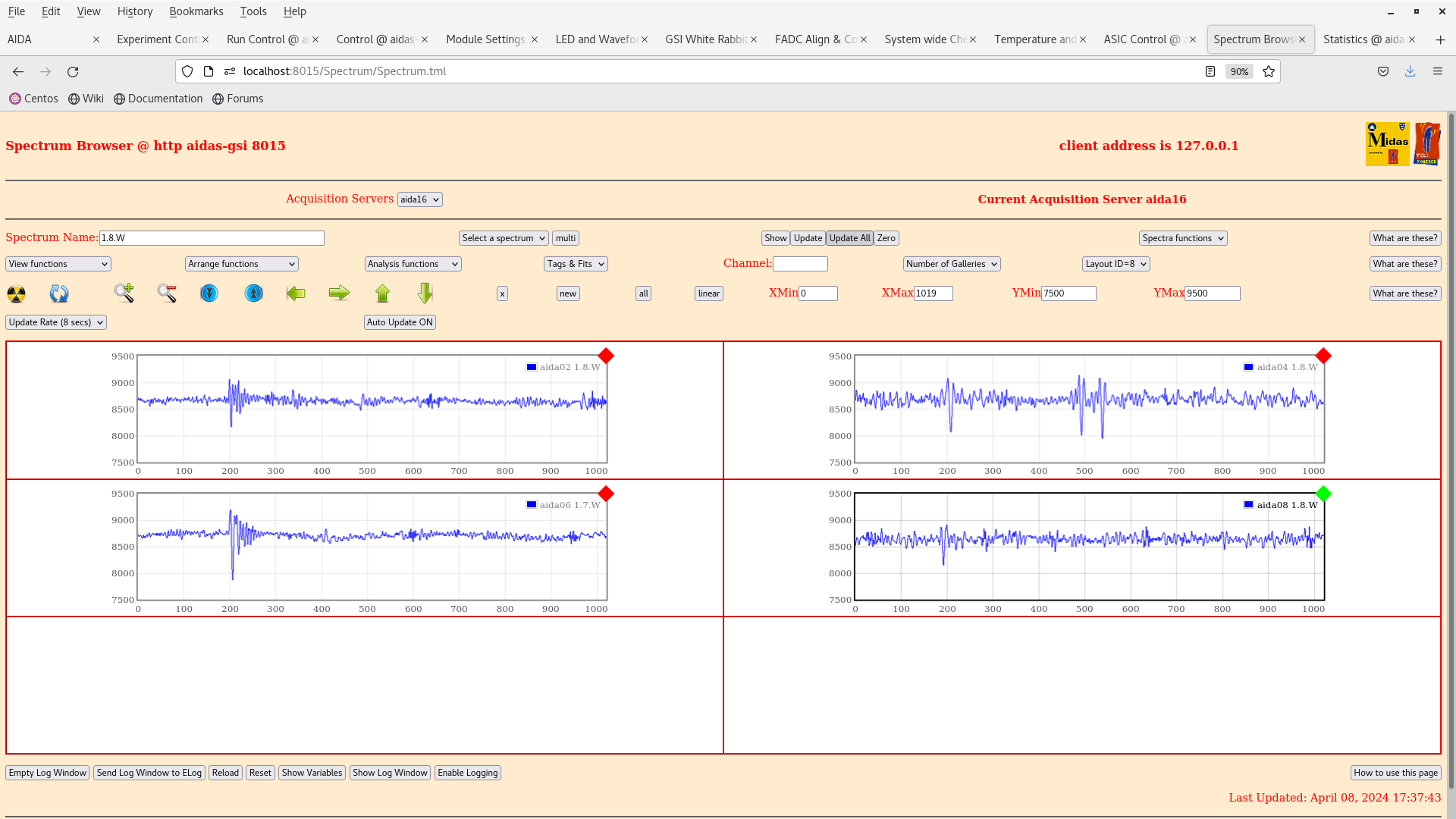

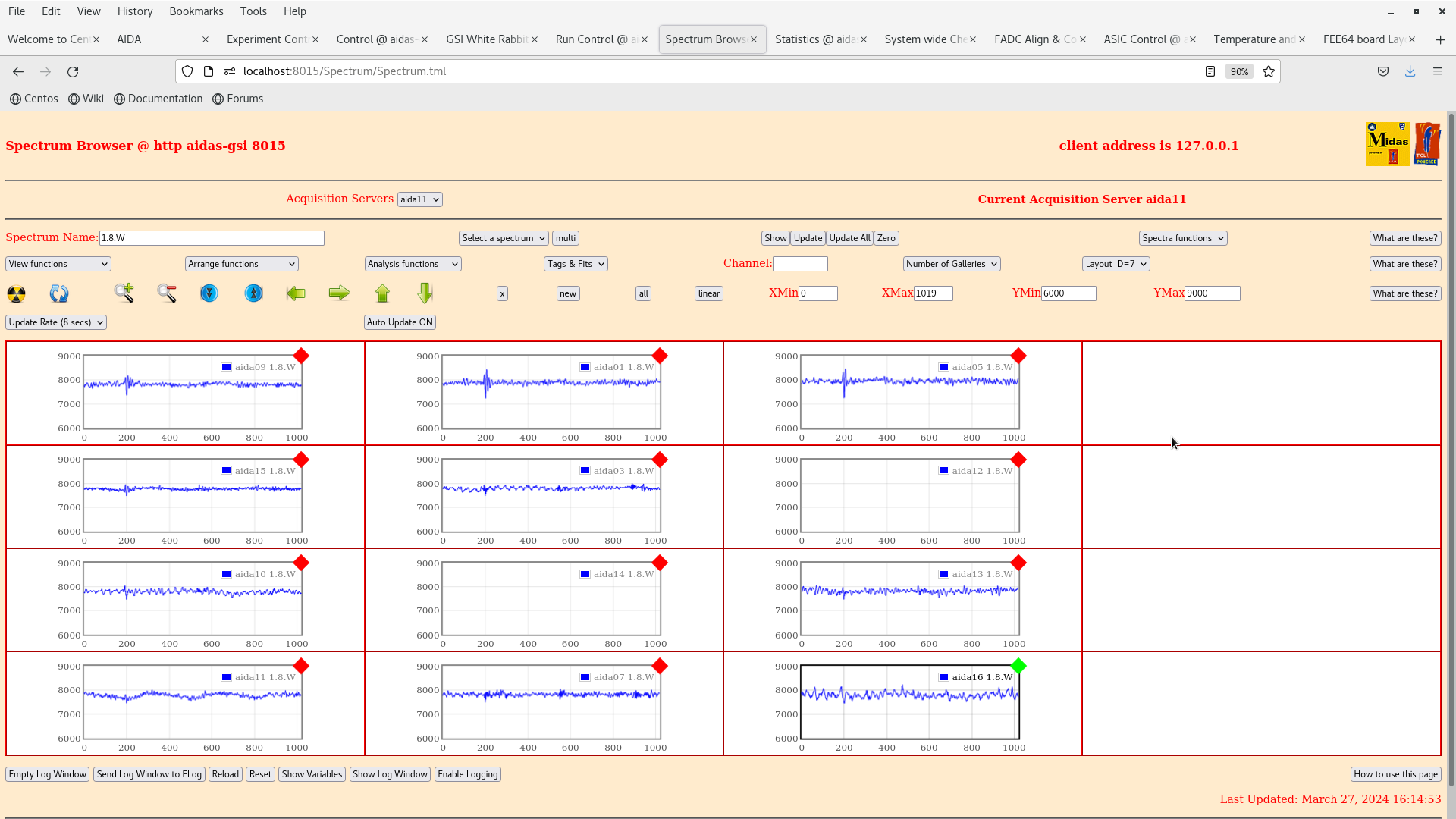

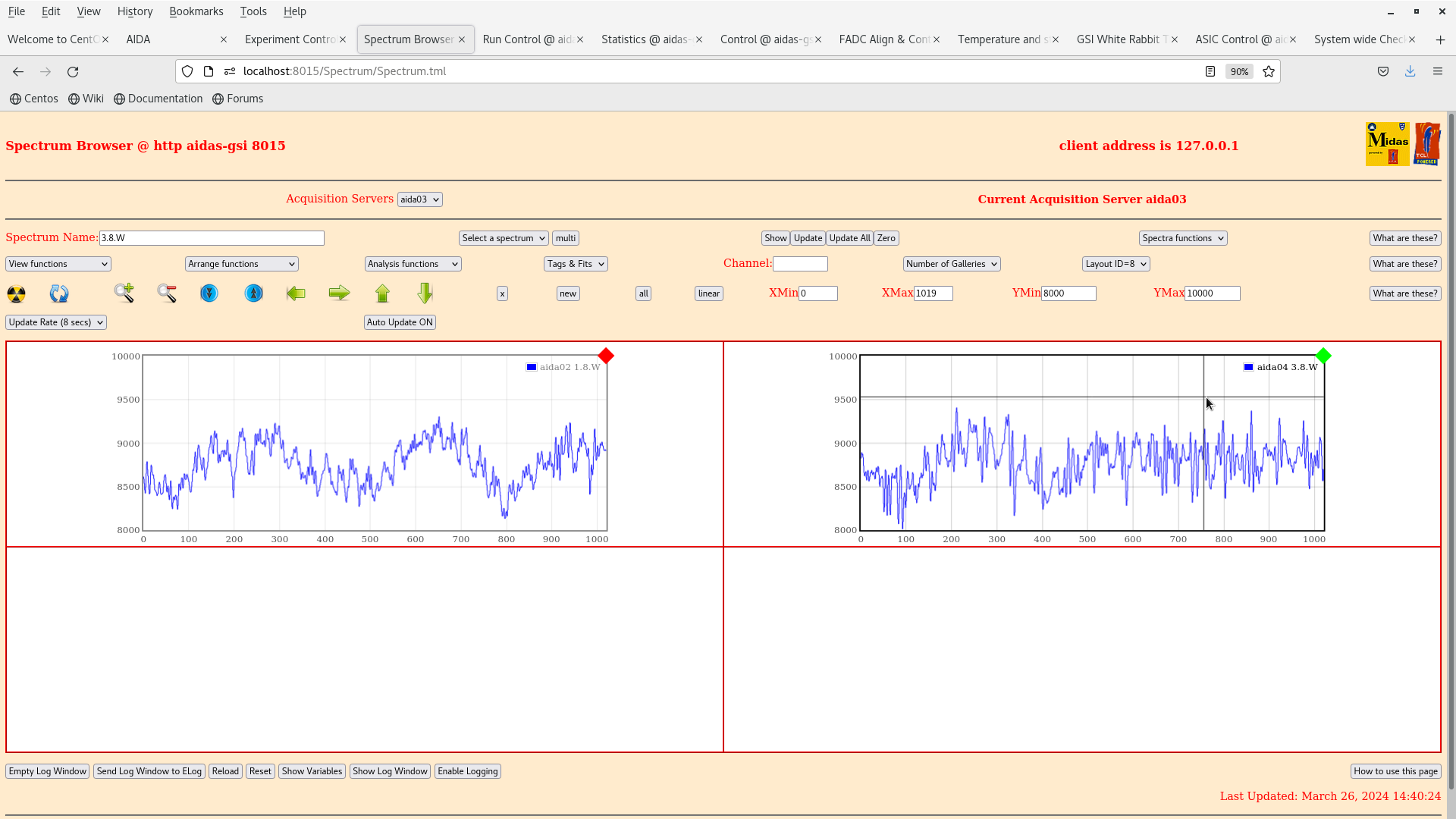

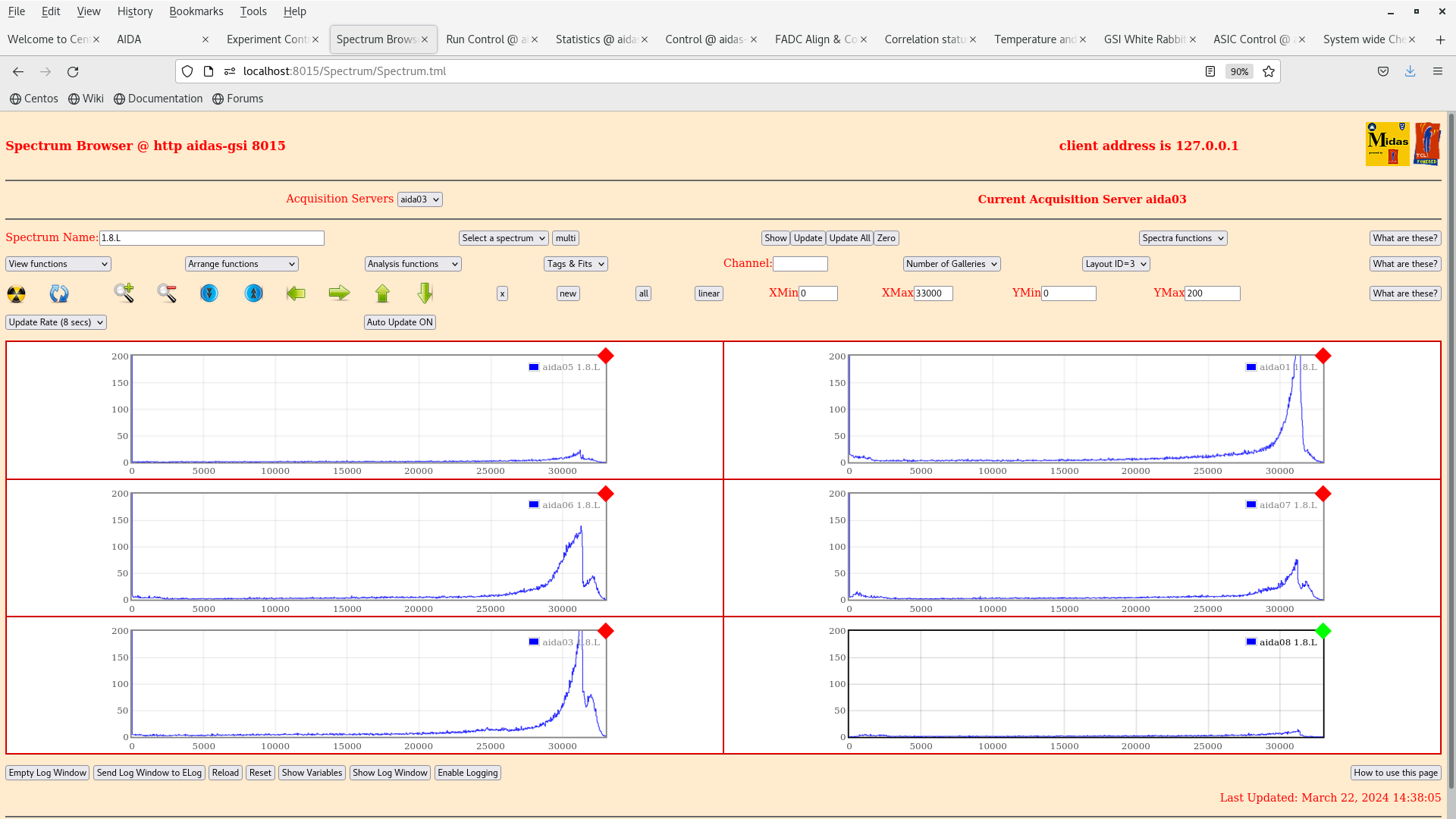

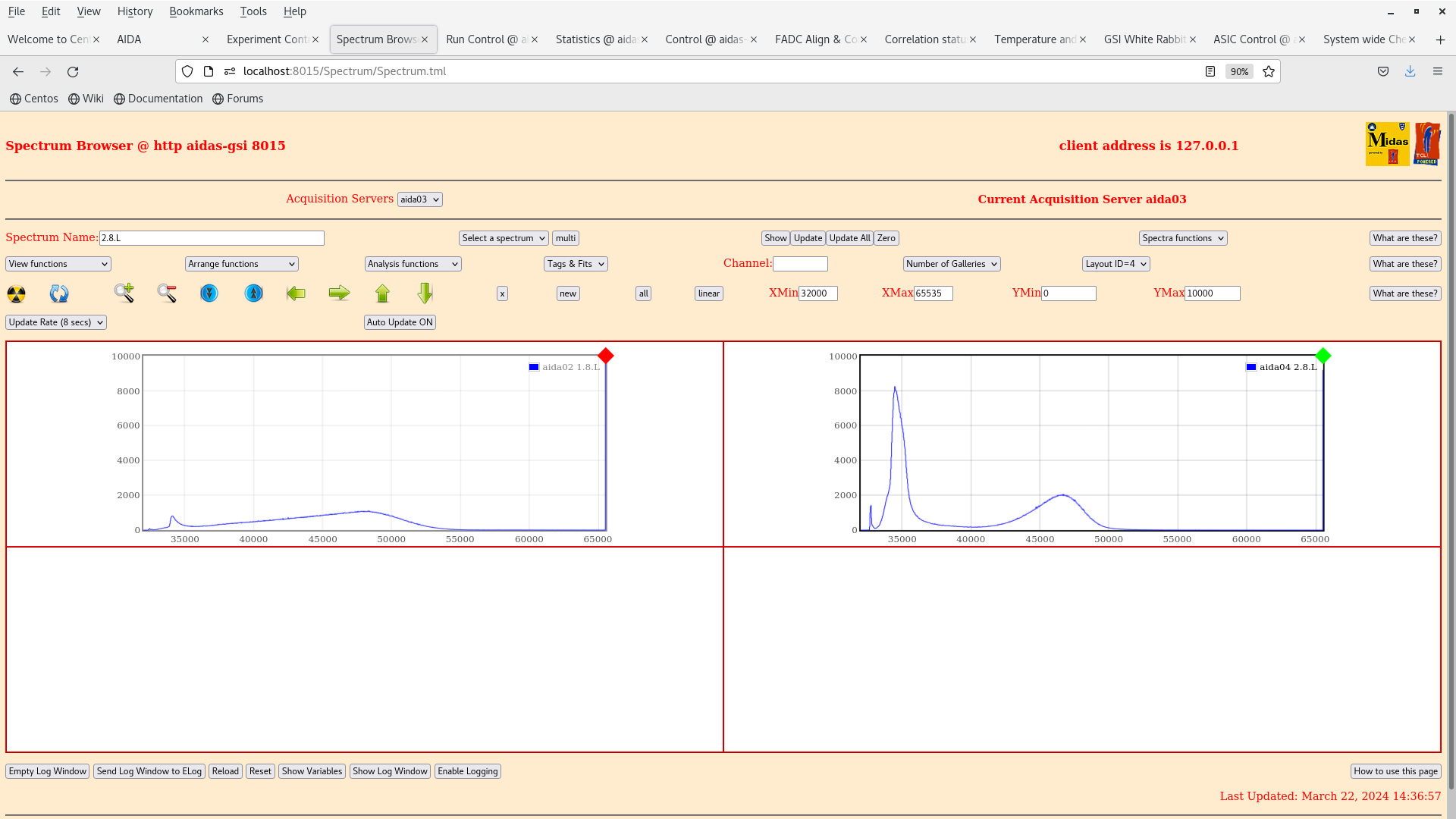

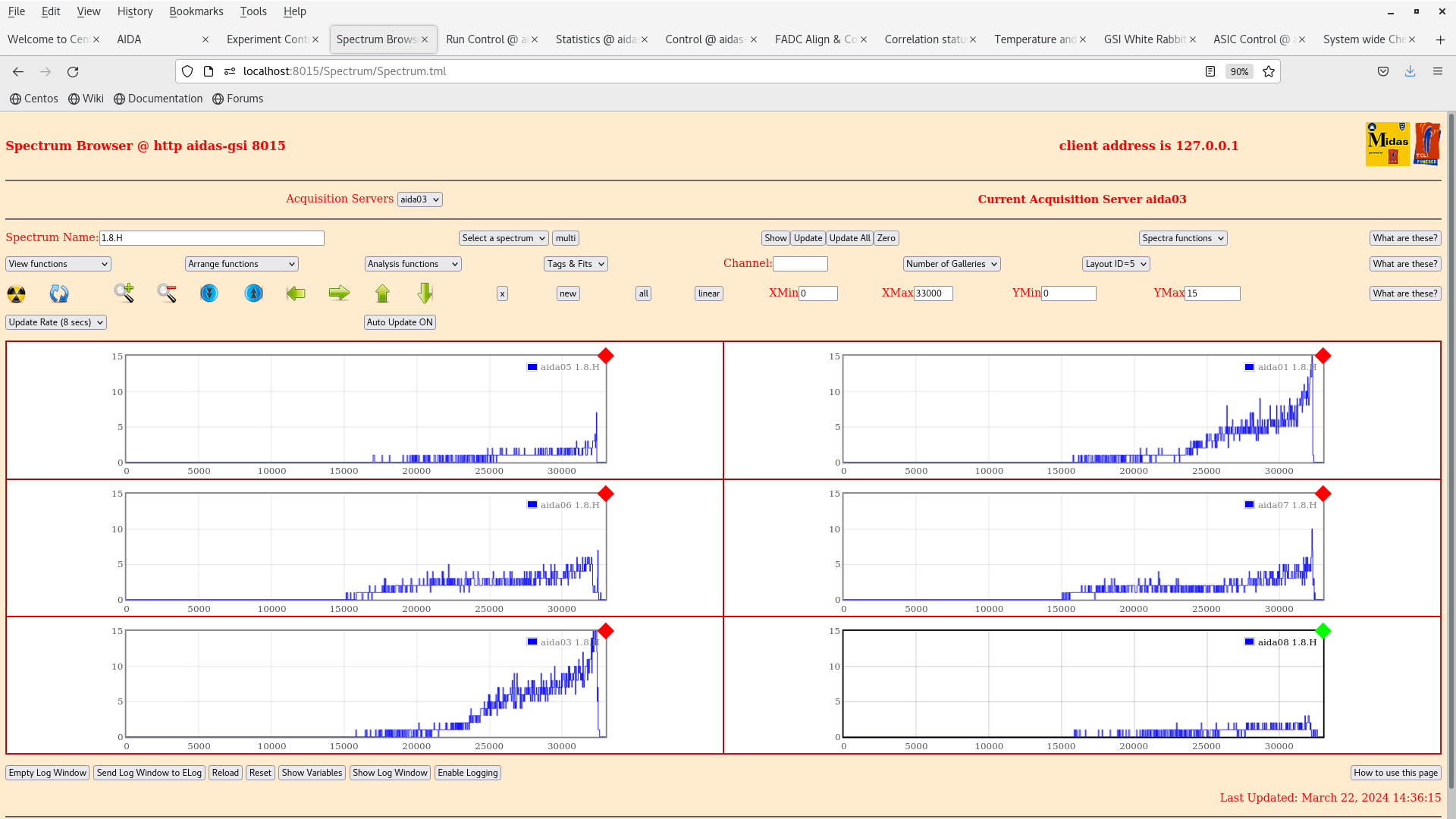

per 1.8.W spectra - 20us FSR - attachments 12-13

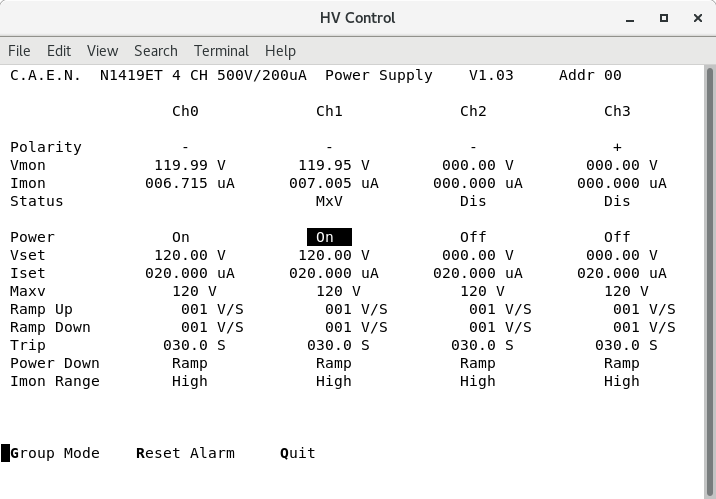

12.25 DSSSD bias & leakage current OK - attachment 16

FEE64 temps OK - attachment 15

*except* aida02 ASIC temp which is known to be u/s

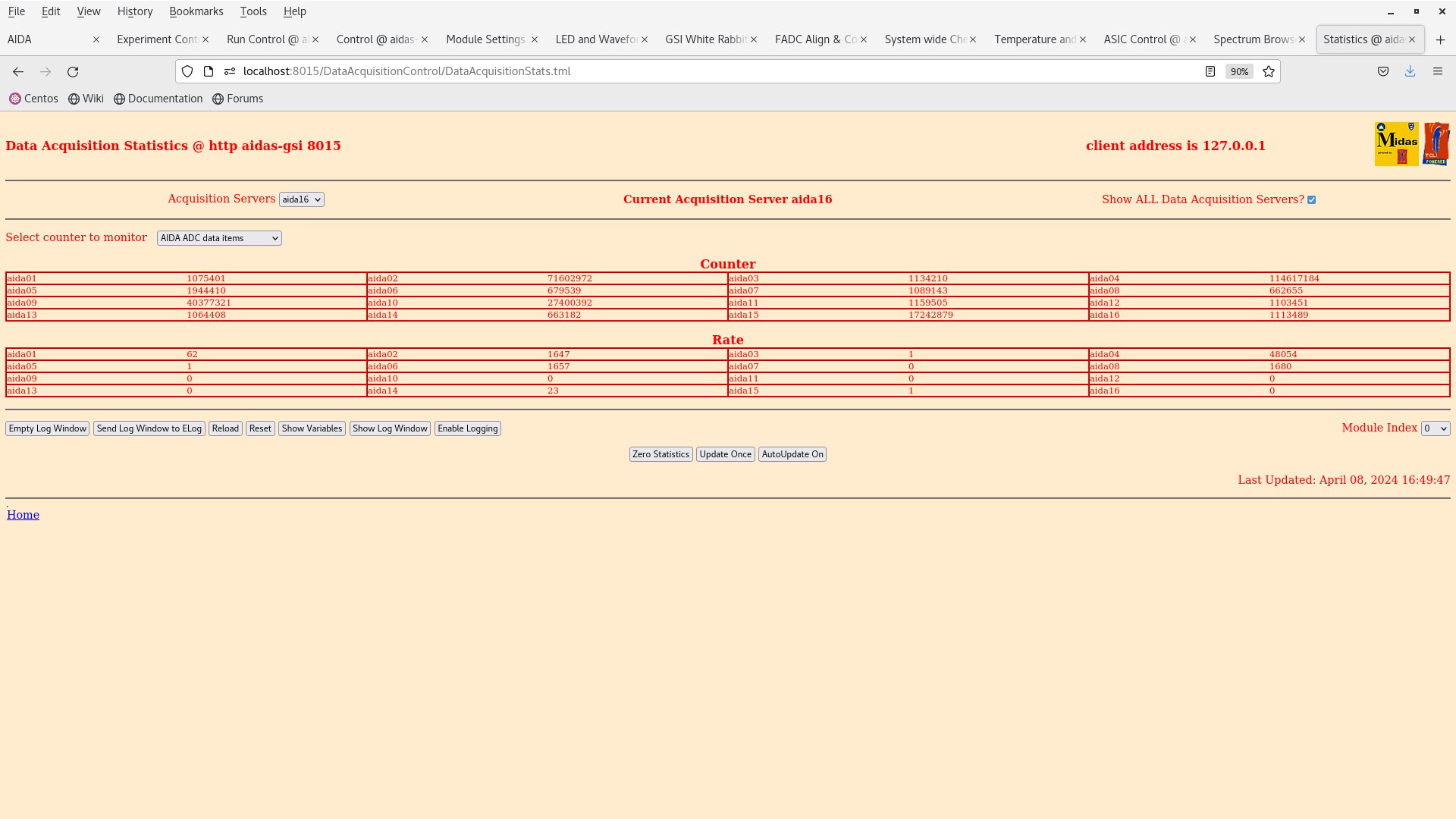

ADC data item stats - attachments 14

system stable |

| Attachment 1: Screenshot_from_2024-04-09_09-50-58.png

|

|

| Attachment 2: Screenshot_from_2024-04-09_09-51-07.png

|

|

| Attachment 3: Screenshot_from_2024-04-09_09-51-26.png

|

|

| Attachment 4: Screenshot_from_2024-04-09_09-51-56.png

|

|

| Attachment 5: Screenshot_from_2024-04-09_09-53-31.png

|

|

| Attachment 6: Screenshot_from_2024-04-09_09-53-19.png

|

|

| Attachment 7: Screenshot_from_2024-04-09_09-52-58.png

|

|

| Attachment 8: Screenshot_from_2024-04-09_09-52-48.png

|

|

| Attachment 9: Screenshot_from_2024-04-09_09-52-38.png

|

|

| Attachment 10: Screenshot_from_2024-04-09_09-52-25.png

|

|

| Attachment 11: Screenshot_from_2024-04-09_09-55-57.png

|

|

| Attachment 12: Screenshot_from_2024-04-09_09-54-17.png

|

|

| Attachment 13: Screenshot_from_2024-04-09_09-53-45.png

|

|

| Attachment 14: Screenshot_from_2024-04-09_12-24-55.png

|

|

| Attachment 15: Screenshot_from_2024-04-09_12-24-43.png

|

|

| Attachment 16: Screenshot_from_2024-04-09_12-24-38.png

|

|

|

566

|

Mon Apr 8 16:39:00 2024 |

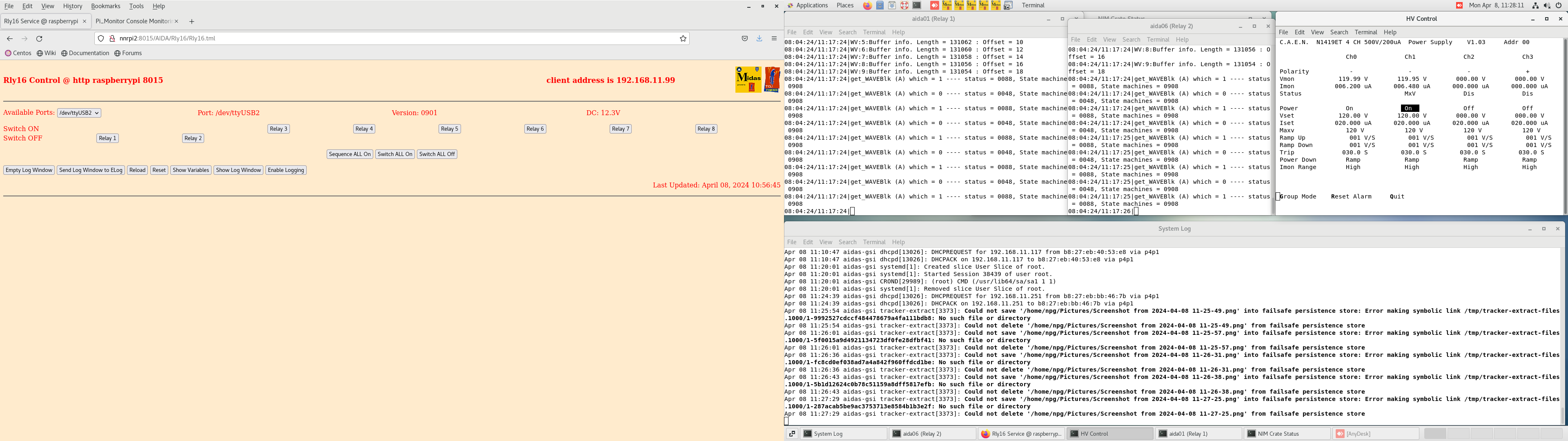

JB, CC, TD | Monday 8 April |

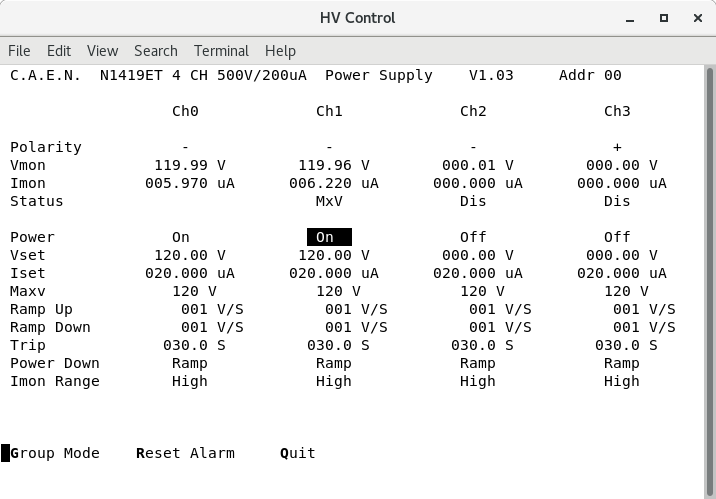

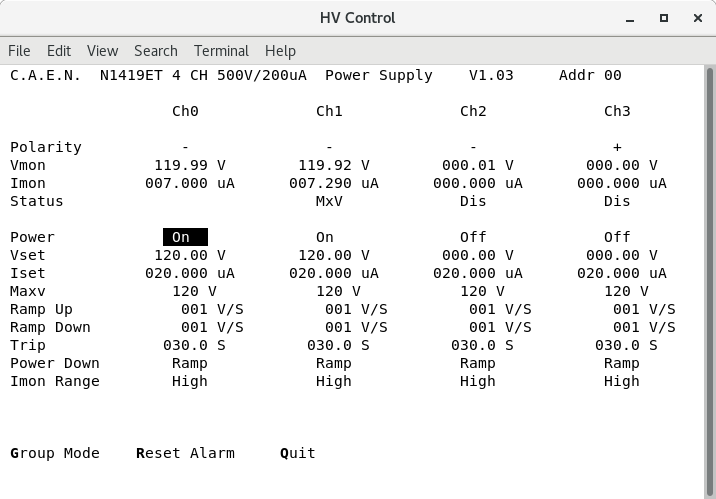

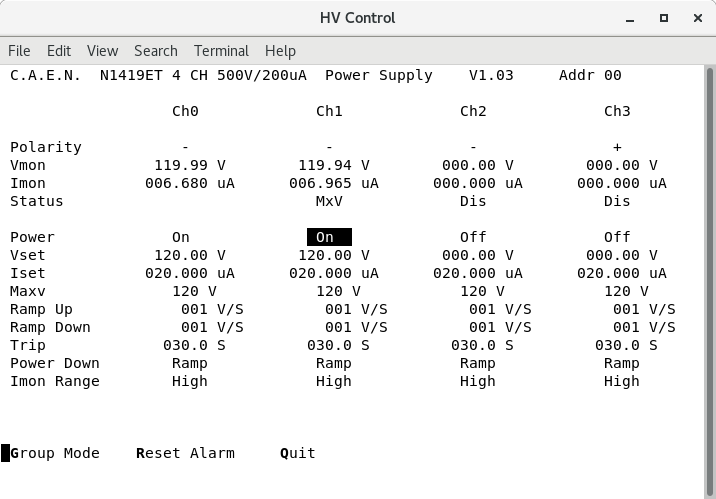

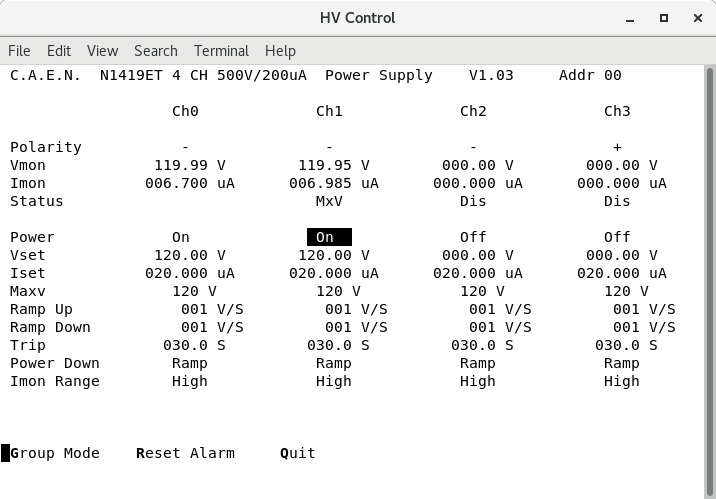

17.32 Power and detector bias cycle

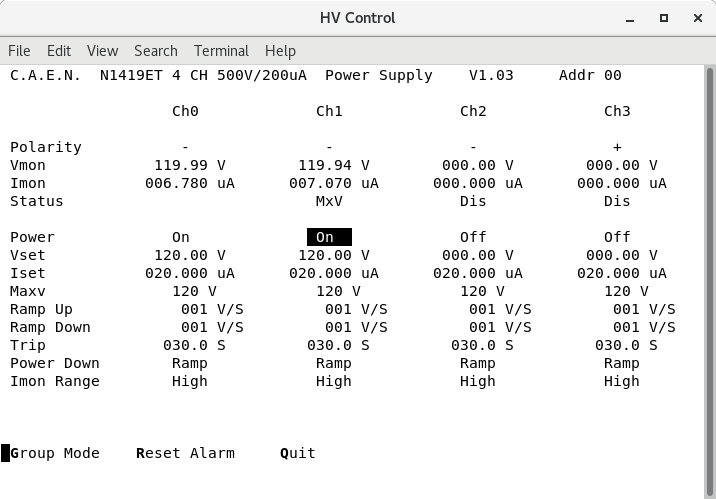

DSSSD bias & leakage current OK - attachment 1

FEE64 temperatures OK - attachment 2

*except* aida02 ASIC temp u/s

ASIC settings 2024Mar27-11.25.32

slow comparator p+n FEE64s 0xa (100keV), n+n FEE64s 0xf (150keV)

BNC PB-5 pulser

amplitude 10.0V

attenuation x10

frequency 25Hz

polarity -

tau_d 1ms

tail pulse

test - distributed by daisy chain to n+n FEE64s - chain terminated by 50 Ohm - currently connected to pulser

test + distributed by daisy chain to p+n FEE64s - chain terminated by 50 Ohm - currently disconnected from pulser

All system wide checks OK *except* aida02 & aida03 WR decoder status errors - attachment 10

WR timestamps OK - attachment 11

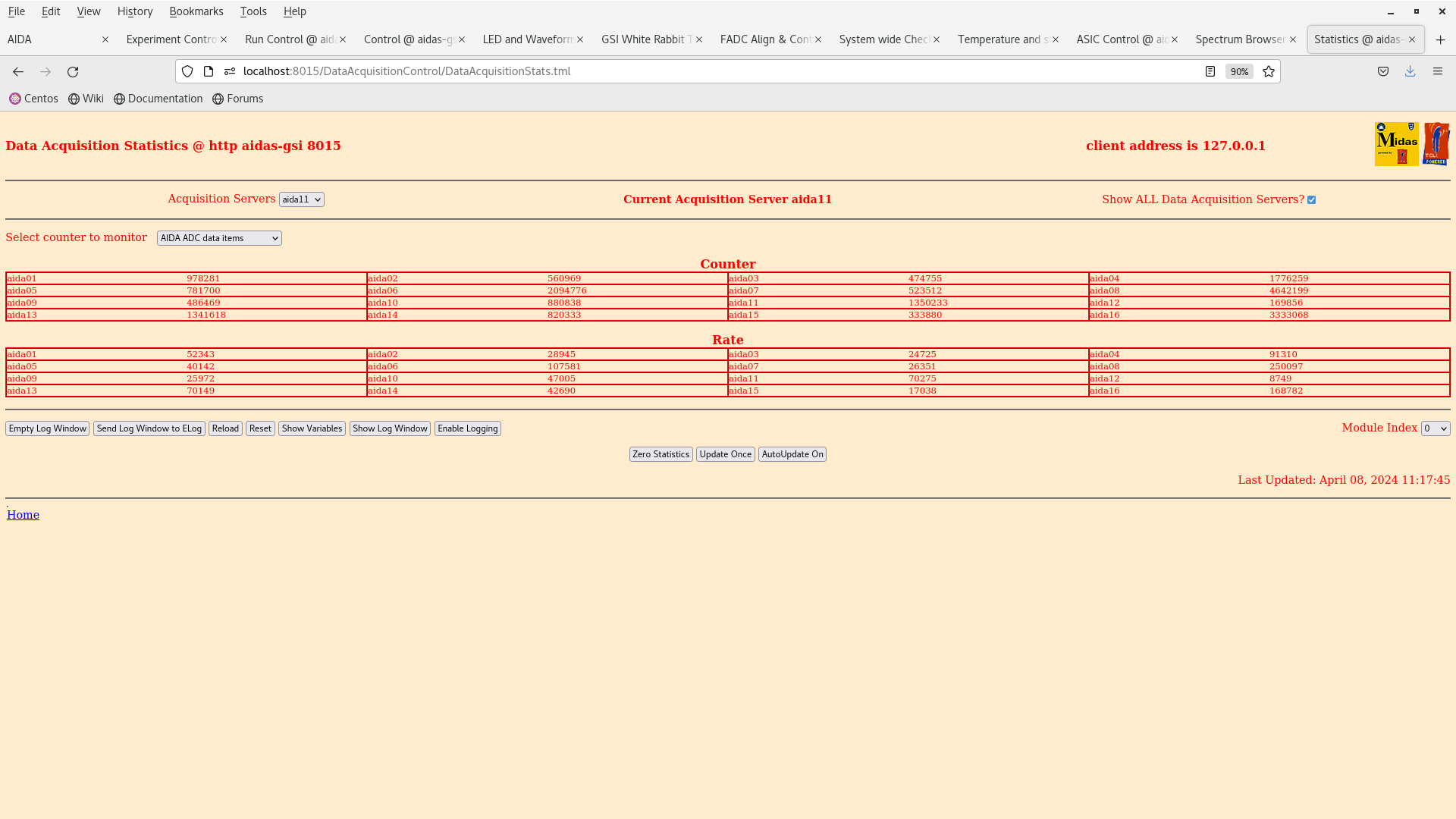

ADC data item stats - attachment 3

12 of 16 < 20k, all < 100k

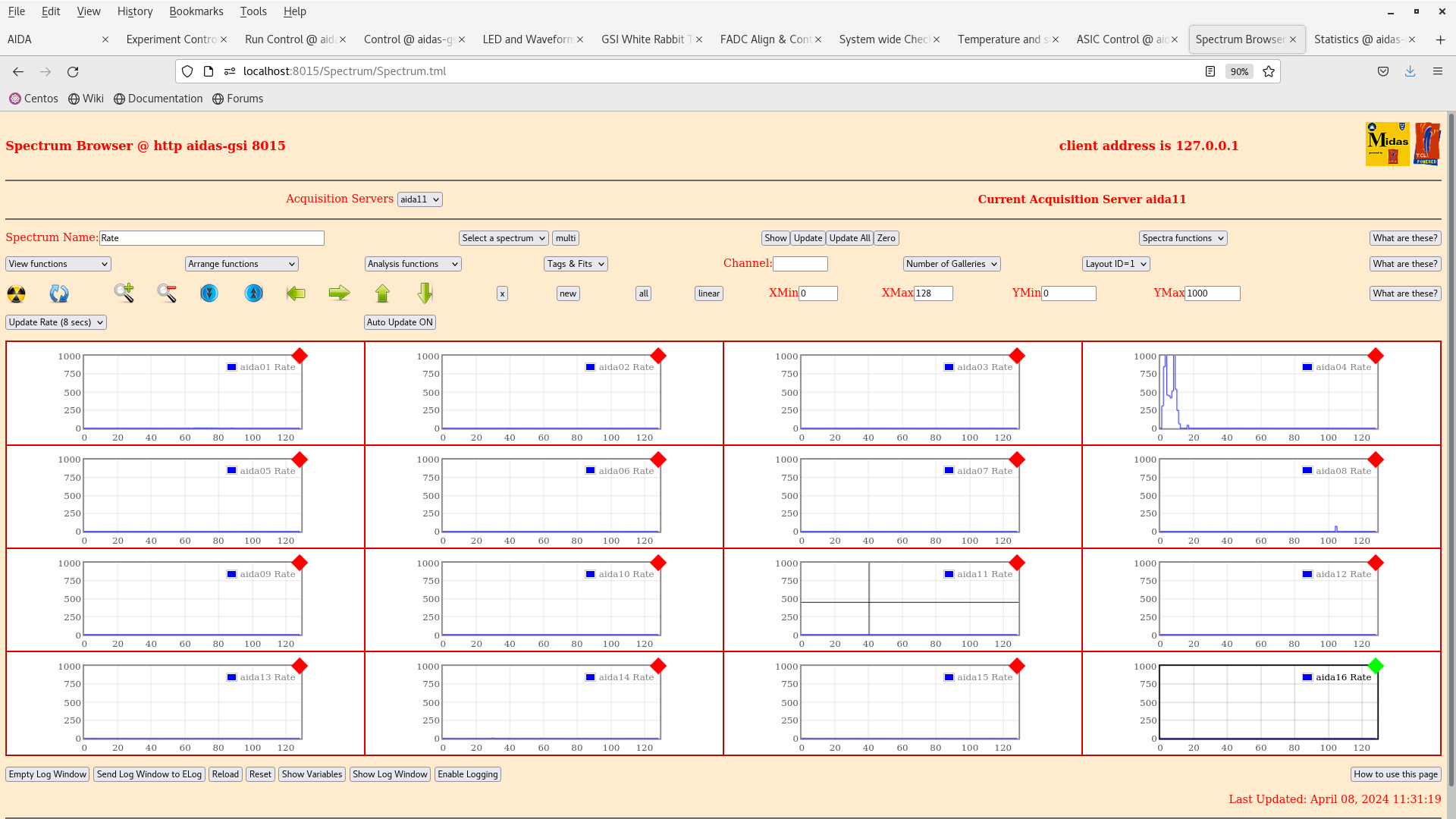

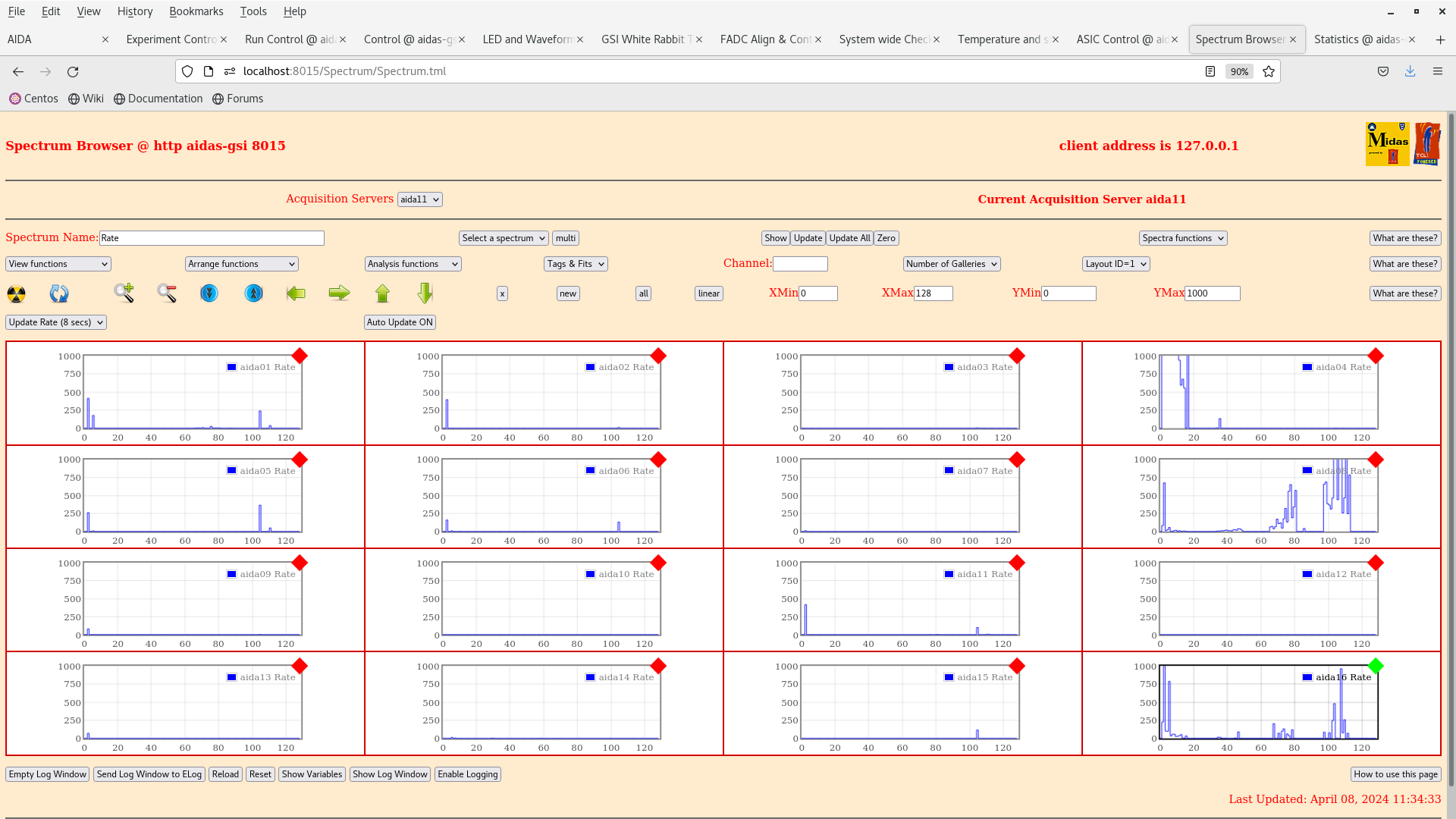

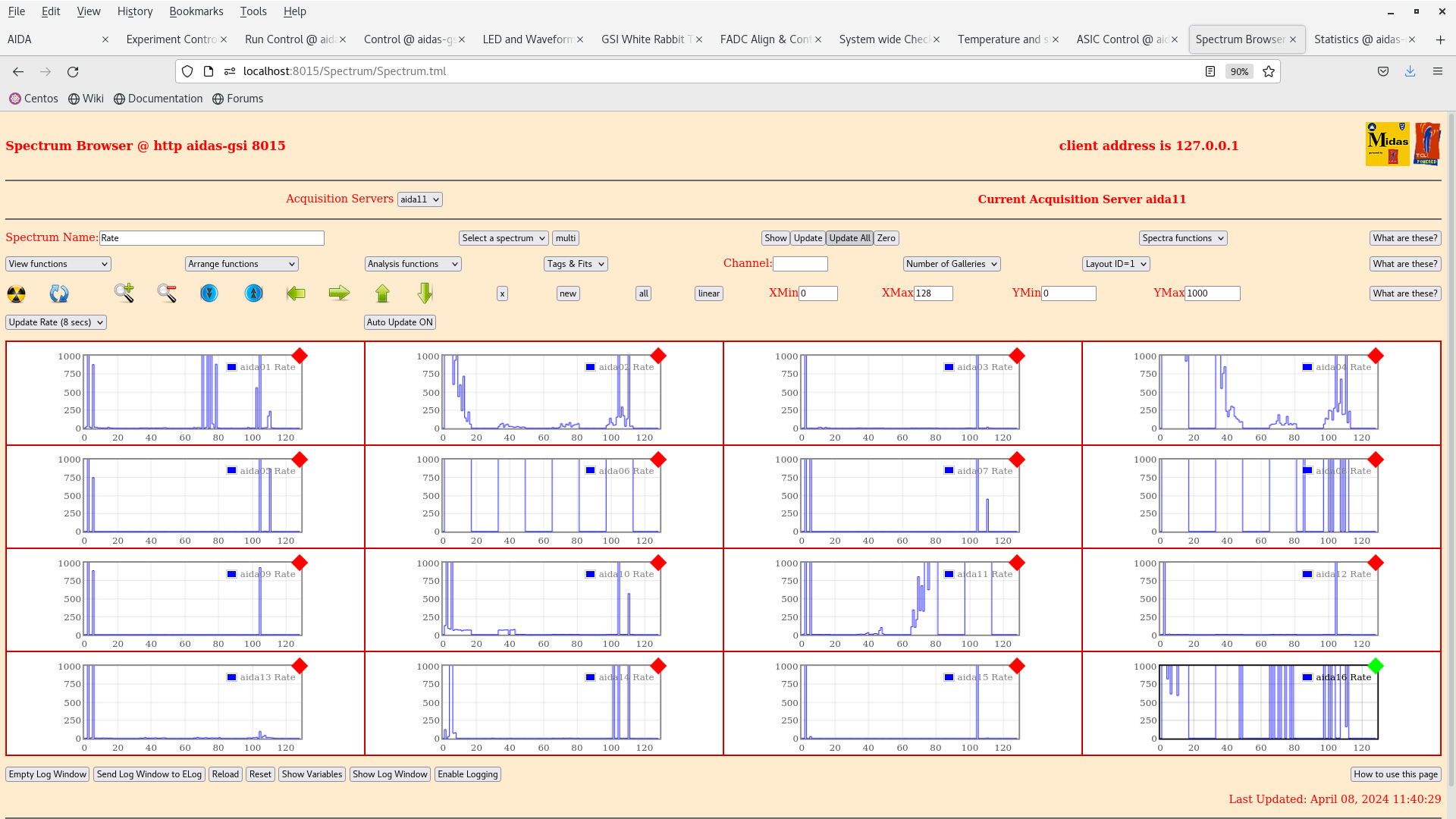

per FEE64 Rate spectra - attachment 4

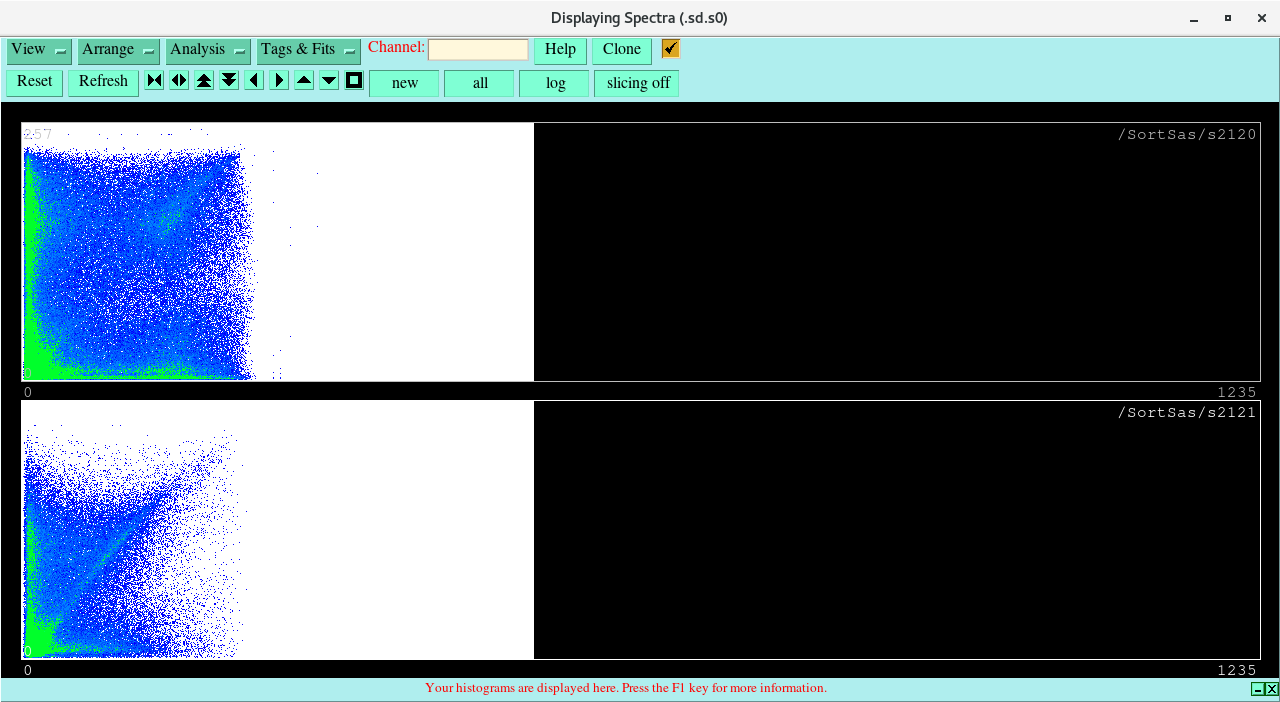

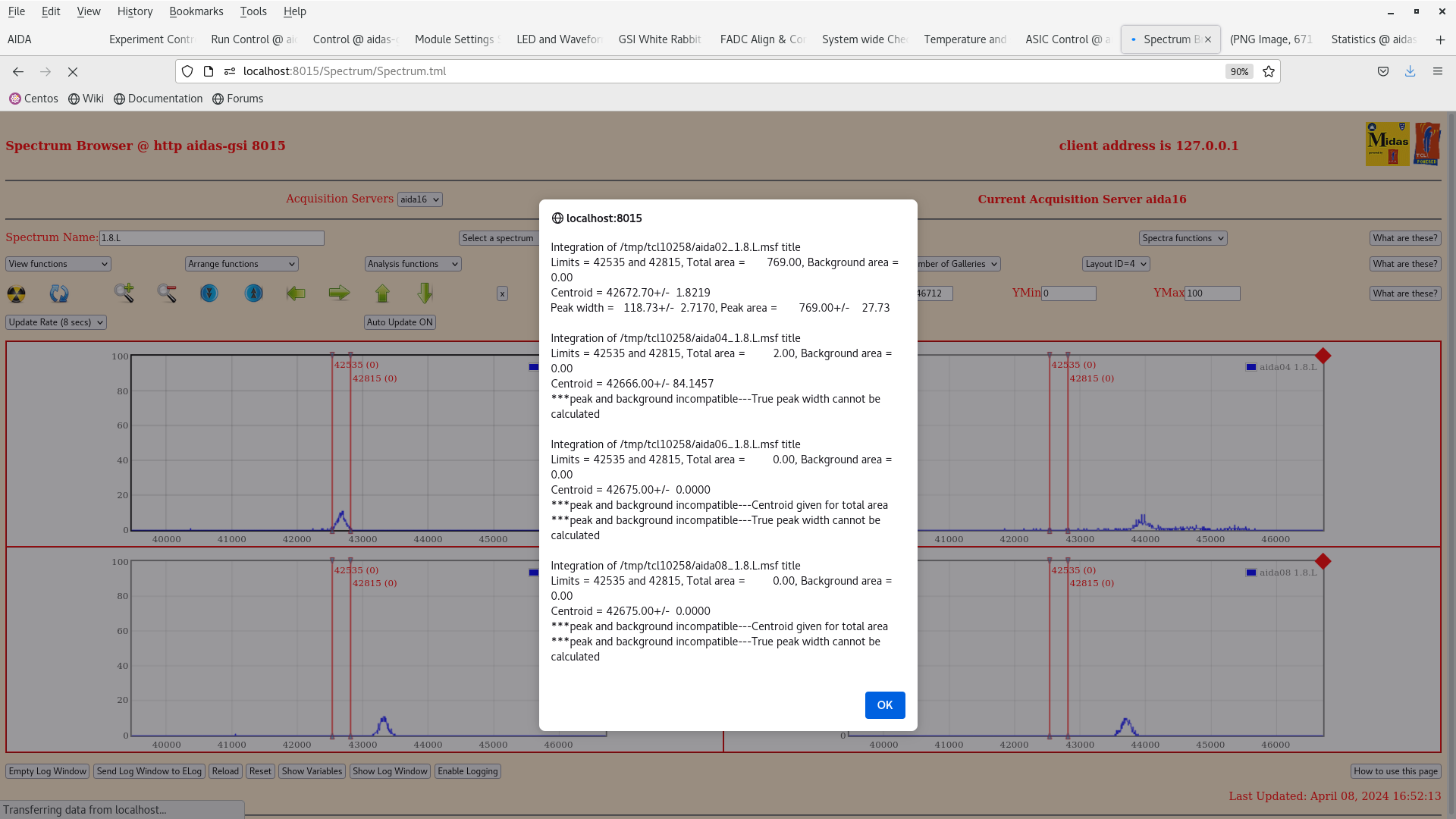

per n+n FEE64 1.8.L spectra - attachment 5

1.8.W spectra - 20us FSR - attachments 6-9

preamplifier output noise generally very good

*Current ground configuration*

CAEN N1419ET LK fitted (non floating outputs)

ground cable from aida04-aida12-aida02-aida09-aida01-aida05

HV#0 aida12-aida03-aida15

ground cable from aida08-aida16-aida06-aida10-aida14-aida13

HV#1 aida16-aida07-aida11

LK3 fitted aida03, aida07

LK1 fitted aida02, aida04, aid06, aida08

test - distributed by daisy chain to n+n FEE64s - chain terminated by 50 Ohm - currently connected to pulser

test + distributed by daisy chain to p+n FEE64s - chain terminated by 50 Ohm - currently disconnected from pulser

all DSSSD ribbon cable drain wires grounded to their resepctive AIDA adaptor PCBs

JB observed open circuit between AIDA Al snout and AIDA support frame ( as expected )

AIDA PSU cabling as reported https://elog.ph.ed.ac.uk/DESPEC/560

Snout configuration:

- all bPlast cables are disconnected and floating.

- CC taped up all the cables and exit points in snout.

- CC, JB covered the exit of the snout with two additional layers of aluminium foil which were also taped shut.

To Do:

- repower detector, see if similar conditions persist.

- disconnect test - pulser, again see if conditions persist.

- aida04 asic#1 investigate noise

- aida14 asic #1 & asic #2 u/s? replace ASIC mezzanine?

|

| Attachment 1: Screenshot_from_2024-04-08_17-32-49.png

|

|

| Attachment 2: Screenshot_from_2024-04-08_17-33-10.png

|

|

| Attachment 3: Screenshot_from_2024-04-08_17-33-14.png

|

|

| Attachment 4: Screenshot_from_2024-04-08_17-33-33.png

|

|

| Attachment 5: Screenshot_from_2024-04-08_17-34-40.png

|

|

| Attachment 6: Screenshot_from_2024-04-08_17-35-00.png

|

|

| Attachment 7: Screenshot_from_2024-04-08_17-35-19.png

|

|

| Attachment 8: Screenshot_from_2024-04-08_17-37-28.png

|

|

| Attachment 9: Screenshot_from_2024-04-08_17-37-56.png

|

|

| Attachment 10: Screenshot_from_2024-04-08_17-48-23.png

|

|

| Attachment 11: Screenshot_from_2024-04-08_17-48-49.png

|

|

|

565

|

Mon Apr 8 11:18:19 2024 |

TD | S505 offline analysis data file R3_150 |

DRG quotes ( from Elog ) S505 FEE64 configuration as

"Configuration: Single/Narrow - 8 FEEs, 2 DSSDs

DSSD 1:

X 0-63 = 3 (HV -ve)

X 64-127 = 1

Y 0-63 = 4 (HV 0v)

Y 64-127 = 2

DSSD 2:

X 0-63 = 7 (HV -ve)

X 64-127 = 5

Y 0-63 = 8 (HV 0v)

Y 64-127 = 6

Scalers:

1 - Pulser

2 - n/c

3 - Time Machine Original

4 - Time Machine Delayed

5 - n/c

6 - n/c

7 - SC41 L

8 - SC41 R"

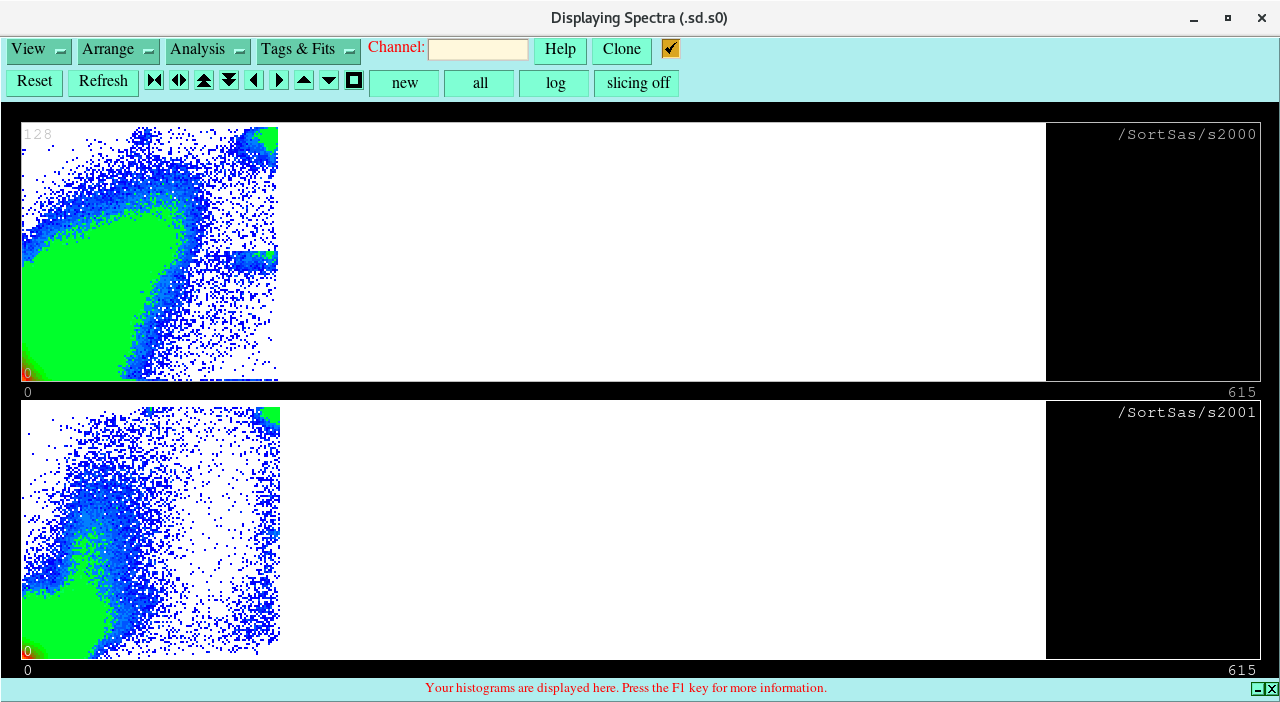

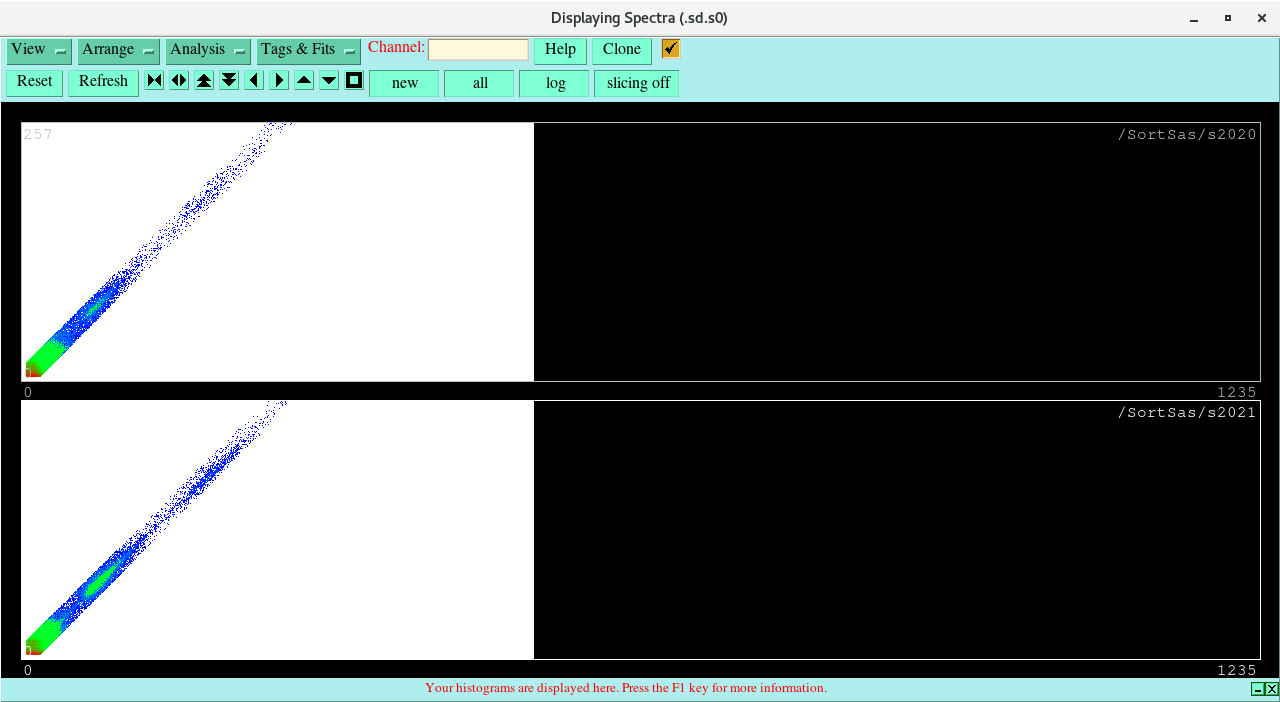

LEC (20MeV FSR) spectra

attachment 1 m_p versus m_n DSSSD#1 & DSSSD#2

attachment 2 E_p versus E_n DSSSD#1 & DSSSD#2

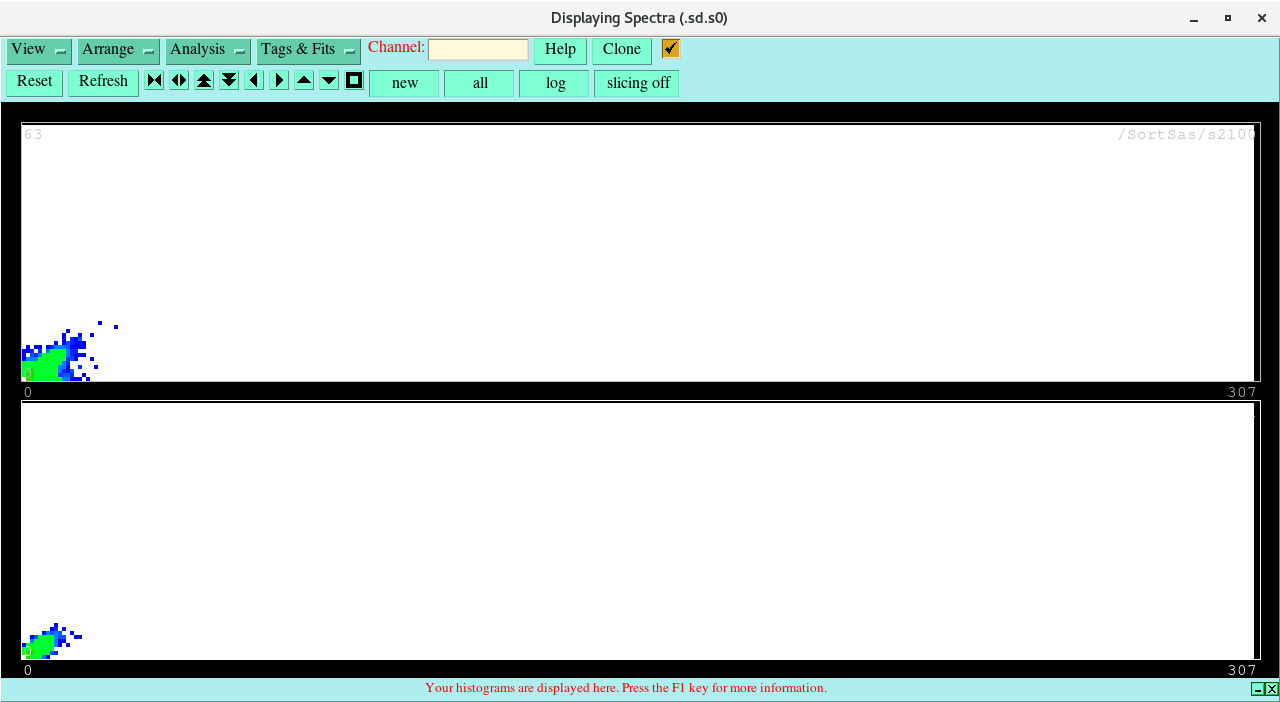

HEC (20GeV FSR) spectra

attachment 3 m_p versus m_n DSSSD#1 & DSSSD#2

attachment 4 E_p versus E_n DSSSD#1 & DSSSD#2

attachment variables.dat ( ADC offsets, e_diff windows & FEE64 onfiguration ) NAMELIST I/O format |

| Attachment 1: Screenshot_from_2024-03-29_20-21-07.png

|

|

| Attachment 2: Screenshot_from_2024-03-29_20-21-45.png

|

|

| Attachment 3: Screenshot_from_2024-03-29_20-22-29.png

|

|

| Attachment 4: Screenshot_from_2024-03-29_20-23-06.png

|

|

| Attachment 5: variables.dat

|

$variables

offset( 0) = 28.32

offset( 1) = 17.71

offset( 2) = -9.75

offset( 3) = -5.24

offset( 4) = -10.84

offset( 5) = 0.13

offset( 6) = 28.59

offset( 7) = 28.54

offset( 8) = 0.83

offset( 9) = -12.15

offset( 10) = 29.36

offset( 11) = -50.47

offset( 12) = 10.03

offset( 13) = -26.90

offset( 14) = 12.49

offset( 15) = 10.57

offset( 16) = 9.29

offset( 17) = 1.09

offset( 18) = 21.86

offset( 19) = -0.32

offset( 20) = 22.59

offset( 21) = -9999.99

offset( 22) = -20.22

offset( 23) = 6.61

offset( 24) = -8.80

offset( 25) = -1.15

offset( 26) = 13.08

offset( 27) = -9.03

offset( 28) = -2.67

offset( 29) = -9.42

offset( 30) = 8.07

offset( 31) = 19.01

offset( 32) = 6.86

offset( 33) = 15.16

offset( 34) = -3.89

offset( 35) = -18.80

offset( 36) = 17.79

offset( 37) = 16.45

offset( 38) = -0.74

offset( 39) = 0.69

offset( 40) = -14.59

offset( 41) = -10.02

offset( 42) = 11.38

offset( 43) = -2.57

offset( 44) = 15.48

offset( 45) = 14.57

offset( 46) = 2.95

offset( 47) = 30.70

offset( 48) = -12.55

offset( 49) = -15.61

offset( 50) = -6.61

offset( 51) = -7.10

offset( 52) = -33.20

offset( 53) = 21.42

offset( 54) = -4.07

offset( 55) = -18.23

offset( 56) = 8.83

offset( 57) = -22.74

offset( 58) = 11.47

offset( 59) = 10.67

offset( 60) = -28.65

offset( 61) = 15.29

offset( 62) = 5.76

offset( 63) = -11.57

offset( 64) = 1.95

offset( 65) = -9999.99

offset( 66) = 22.52

offset( 67) = 42.10

offset( 68) = -0.20

offset( 69) = 9.78

offset( 70) = -11.48

offset( 71) = -0.03

offset( 72) = -12.50

offset( 73) = 25.08

offset( 74) = 12.77

offset( 75) = -2.76

offset( 76) = 7.90

offset( 77) = 9.85

offset( 78) = 5.20

offset( 79) = -13.91

offset( 80) = 18.82

offset( 81) = -8.25

offset( 82) = -8.40

offset( 83) = 13.67

offset( 84) = -10.37

offset( 85) = 28.32

offset( 86) = 11.42

offset( 87) = 2.74

offset( 88) = -24.88

offset( 89) = 11.28

offset( 90) = -26.69

offset( 91) = 0.91

offset( 92) = 8.04

offset( 93) = 7.64

offset( 94) = 10.10

offset( 95) = -20.71

offset( 96) = 6.72

offset( 97) = -12.63

offset( 98) = 10.27

offset( 99) = 16.05

offset( 100) = 8.96

offset( 101) = 33.57

offset( 102) = 28.81

offset( 103) = 23.49

offset( 104) = 7.96

offset( 105) = 6.07

offset( 106) = 21.57

offset( 107) = 13.06

offset( 108) = 0.82

offset( 109) = -3.55

offset( 110) = -5.21

offset( 111) = 11.48

offset( 112) = 16.21

offset( 113) = -0.10

offset( 114) = 3.87

offset( 115) = 19.76

offset( 116) = -9.11

offset( 117) = 24.64

offset( 118) = 1.82

offset( 119) = -9999.99

offset( 120) = 22.80

offset( 121) = -7.37

offset( 122) = -18.32

offset( 123) = -24.74

offset( 124) = -4.71

offset( 125) = 19.64

offset( 126) = 53.61

offset( 127) = 6.57

offset( 128) = 3.21

offset( 129) = 7.20

offset( 130) = 5.55

offset( 131) = -3.40

offset( 132) = -16.40

offset( 133) = -1.71

offset( 134) = -14.85

offset( 135) = -29.53

offset( 136) = 0.68

offset( 137) = -0.41

offset( 138) = 17.59

offset( 139) = -28.92

offset( 140) = -8.79

offset( 141) = 11.69

offset( 142) = -5.80

offset( 143) = -8.21

offset( 144) = 13.90

offset( 145) = 11.27

offset( 146) = -17.02

offset( 147) = -8.19

offset( 148) = 6.14

offset( 149) = -13.13

offset( 150) = 15.41

offset( 151) = 0.12

offset( 152) = -5.02

offset( 153) = 4.25

offset( 154) = 3.84

offset( 155) = 13.34

offset( 156) = 16.79

offset( 157) = -36.21

offset( 158) = -2.18

offset( 159) = 12.94

offset( 160) = 2.05

offset( 161) = -17.31

offset( 162) = 18.38

offset( 163) = -7.17

offset( 164) = 6.59

offset( 165) = -13.36

offset( 166) = -12.11

offset( 167) = -3.91

offset( 168) = 10.97

offset( 169) = -25.72

offset( 170) = -11.53

offset( 171) = 1.94

offset( 172) = -12.76

offset( 173) = 18.55

offset( 174) = 13.49

offset( 175) = -9.45

offset( 176) = -10.19

offset( 177) = 18.69

offset( 178) = 24.49

offset( 179) = 30.44

offset( 180) = 41.95

offset( 181) = 1.55

offset( 182) = 20.88

offset( 183) = 4.76

offset( 184) = 15.80

offset( 185) = 12.37

offset( 186) = -13.03

offset( 187) = 15.64

offset( 188) = -8.44

offset( 189) = -3.02

offset( 190) = 10.57

offset( 191) = 6.88

offset( 192) = -17.81

offset( 193) = -5.77

offset( 194) = -18.29

offset( 195) = 17.62

offset( 196) = -30.66

offset( 197) = -7.37

offset( 198) = 36.32

offset( 199) = 3.42

offset( 200) = -21.92

offset( 201) = 15.88

offset( 202) = -17.33

offset( 203) = -2.71

offset( 204) = -21.06

offset( 205) = -4.53

offset( 206) = -1.59

offset( 207) = -9.54

offset( 208) = -0.04

offset( 209) = 23.57

offset( 210) = 13.83

offset( 211) = -9.28

offset( 212) = 12.42

offset( 213) = 23.85

offset( 214) = 7.90

offset( 215) = -7.29

offset( 216) = 26.18

offset( 217) = 33.05

offset( 218) = 32.10

offset( 219) = -8.10

offset( 220) = 16.16

offset( 221) = 3.94

offset( 222) = -18.22

offset( 223) = -16.84

offset( 224) = 5.79

offset( 225) = 21.07

offset( 226) = 45.18

offset( 227) = -13.85

offset( 228) = 6.76

offset( 229) = 13.59

offset( 230) = 8.28

offset( 231) = -9.32

offset( 232) = 21.30

offset( 233) = 7.02

offset( 234) = 24.11

offset( 235) = 16.26

offset( 236) = 11.46

offset( 237) = 2.16

offset( 238) = 7.19

offset( 239) = 18.45

offset( 240) = 6.65

offset( 241) = 6.56

offset( 242) = -33.59

offset( 243) = 14.71

offset( 244) = 21.28

offset( 245) = -0.73

offset( 246) = -10.29

offset( 247) = 28.50

offset( 248) = -11.37

offset( 249) = -18.92

offset( 250) = 23.12

offset( 251) = 8.87

offset( 252) = 9.64

offset( 253) = 16.43

offset( 254) = -2.70

offset( 255) = 26.14

offset( 256) = -4.99

offset( 257) = -10.88

offset( 258) = 27.41

offset( 259) = -3.48

offset( 260) = -11.18

offset( 261) = 12.60

offset( 262) = 22.19

offset( 263) = -20.16

offset( 264) = 20.32

offset( 265) = 9.66

offset( 266) = 13.30

offset( 267) = -12.64

offset( 268) = 53.69

offset( 269) = 23.15

offset( 270) = 43.60

offset( 271) = 48.58

offset( 272) = -13.12

offset( 273) = -12.57

offset( 274) = 35.19

offset( 275) = 14.84

offset( 276) = 33.05

offset( 277) = 13.73

offset( 278) = 45.45

offset( 279) = 55.49

offset( 280) = 48.13

offset( 281) = 3.86

offset( 282) = 28.44

offset( 283) = 23.73

offset( 284) = 11.53

offset( 285) = -19.46

offset( 286) = 10.81

offset( 287) = 17.23

offset( 288) = -13.85

offset( 289) = 30.17

offset( 290) = 10.70

offset( 291) = 28.06

offset( 292) = -14.35

offset( 293) = 23.46

offset( 294) = 15.16

offset( 295) = -25.15

offset( 296) = -15.03

offset( 297) = -24.74

offset( 298) = -5.94

... 228 more lines ...

|

|

564

|

Mon Apr 8 10:23:16 2024 |

TD, JB | AIDA Noise optimisation |

In the morning we reinstalled FEE64s aida06, aida13, aida07. The rails of the FEE64 boards were found to be incorrect (that of the rails that were used in CARME).

After replacing the rails on the abovementioned FEE64s we powercycled AIDA and found the following results in the histograms and statistics.

As can be seen in attachement 4, aida16 has a noisy waveform and we are going to investigate this further.

When setting the threshold to 0x64 (1 MeV) on the slow comparator threshold we saw that the low energy branch of aida04 was still noisy. (Attachment 6)

- Setting the slow comparator threshold to 0x32 (0.5 MeV) introduced noise into aida08, aida16 and substantially more noise in aida04. (Attachment 7)

- Setting the slow comparator threshold to 0x14 (0.2 MeV) introduced noise into aida11 and substantially more noise in aida04, aida08, aida16 and aida06. (Attachment 8)

- Setting the slow comparator threshold to 0xf (0.15 MeV) introduced more noise into the same aforementioned channels aida04, aida06, aida08, aida11, aida16 (additionally aida02), barring hot strips. (Attachment 9)

We covered the end of the snout with a black cloth and this reduced the noise in some of the channels (Attachment 10 and 11).

- We covered the end of the snout with two layers of aluminium foil - this produced the same result as covering the snout with the black cloth (Attachment 12, 13, 14 & 15).

We resumed after lunch.

- Replaced the aida16 adaptor PCB with a spare, and this produced a much more sensible rate and hitpattern in aida16, which could lead us to believe that the aida adapter card was faulty or misaligned. (Attachment 16, 17, 18 & 19).

- Placed two LK1 back on the n+n side of both DSSSDs on aida06 and aida02. The noise and rate did not change at all. (Attachment 20 & 21)

Pulser tests:

- The test + pulser was connected to the p+n sides (top and bottom) at 25 Hz.

- After checking the ASIC control 2 times over, the pulser seems to be ok for all p+n channels excluding aida01, aida13 and aida14. (Attachment 23)

- The pulser peak width of aida09 1.8.L was found to be c. 55 channels FWHM on uncalibrated scale which corresponds to 35 - 40 keV FWHM in energy resolution. (Attachment 24)

- After reseating the adaptor board PCBs we found the same result as before reseating the adaptor boards (Attachment 25).

- Connecting the test - pulser to the n+n side we found that most of the ASICs behaved normally which ASIC 1 in aida04 was showing abnormal behaviour. (Attachment 26, 28). The test + pulser loop is still in place.

- The pulser peak width of aida02 1.8.L was found to be c. 118 channels FWHM on uncalibrated scale which corresponds to 95 - 100 keV FWHM in energy resolution. (Attachment 27)

- We set the thresholds on the n+n side to 0xf and the p+n side to 0xa. Subsequently, we observed improved noise conditions in many of the channels. The still noisy channels are aida01, aida04, aida08. (Attachment 29, 30). This might be because we have introduced an addtional ground loop with the pusler tests, but could also mean that the ground loop that is currently being used is not sufficient or poorly implemented.

Summary:

- From the pulser test it is clear that aida14 ASICs 1&2 are not in good shape and appear to be faulty.

- We managed to improve from 1 aida module in the sub 20 kHz rate range to 6 aida modules in the sub 20 kHz rate range by the end of the tests.

- We set the slow comparator thresholds on the n+n side to 0xf and the p+n side to 0xa. Subsequently, we observed improved noise conditions in many of the channels. The still noisy channels are aida01, aida04, aida08. (Attachment 29, 30). This might be because we have introduced an additional ground loop with the pusler tests, but could also mean that the ground loop that is currently being used is not sufficient or poorly implemented.

|

| Attachment 1: Screenshot_from_2024-04-08_11-28-11.png

|

|

| Attachment 2: Screenshot_from_2024-04-08_11-27-25.png

|

|

| Attachment 3: Screenshot_from_2024-04-08_11-26-38.png

|

|

| Attachment 4: Screenshot_from_2024-04-08_11-26-31.png

|

|

| Attachment 5: Screenshot_from_2024-04-08_11-25-57.png

|

|

| Attachment 6: Screenshot_from_2024-04-08_11-31-34.png

|

|

| Attachment 7: Screenshot_from_2024-04-08_11-34-40.png

|

|

| Attachment 8: Screenshot_from_2024-04-08_11-36-50.png

|

|

| Attachment 9: Screenshot_from_2024-04-08_11-40-33.png

|

|

| Attachment 10: Screenshot_from_2024-04-08_11-51-46.png

|

|

| Attachment 11: Screenshot_from_2024-04-08_11-51-50.png

|

|

| Attachment 12: Screenshot_from_2024-04-08_12-09-33.png

|

|

| Attachment 13: Screenshot_from_2024-04-08_12-09-37.png

|

|

| Attachment 14: Screenshot_from_2024-04-08_12-10-20.png

|

|

| Attachment 15: Screenshot_from_2024-04-08_12-10-57.png

|

|

| Attachment 16: Screenshot_from_2024-04-08_15-09-34.png

|

|

| Attachment 17: Screenshot_from_2024-04-08_15-09-08.png

|

|

| Attachment 18: Screenshot_from_2024-04-08_14-45-49.png

|

|

| Attachment 19: Screenshot_from_2024-04-08_14-45-05.png

|

|

| Attachment 20: Screenshot_from_2024-04-08_14-44-19.png

|

|

| Attachment 21: Screenshot_from_2024-04-08_14-44-14.png

|

|

| Attachment 22: Screenshot_from_2024-04-08_16-03-19.png

|

|

| Attachment 23: Screenshot_from_2024-04-08_16-07-48.png

|

|

| Attachment 24: Screenshot_from_2024-04-08_16-13-53.png

|

|

| Attachment 25: Screenshot_from_2024-04-08_16-38-15.png

|

|

| Attachment 26: Screenshot_from_2024-04-08_16-48-25.png

|

|

| Attachment 27: Screenshot_from_2024-04-08_16-52-17.png

|

|

| Attachment 28: Screenshot_from_2024-04-08_16-50-12.png

|

|

| Attachment 29: Screenshot_from_2024-04-08_17-00-38.png

|

|

| Attachment 30: Screenshot_from_2024-04-08_16-58-25.png

|

|

|

563

|

Sun Apr 7 18:13:56 2024 |

TD | Sunday 7 April contd. |

19.10 CAEN N1419ET LK fitted

power cycle

attachments 1-6 |

| Attachment 1: Screenshot_from_2024-04-07_19-13-19.png

|

|

| Attachment 2: Screenshot_from_2024-04-07_19-12-40.png

|

|

| Attachment 3: Screenshot_from_2024-04-07_19-11-24.png

|

|

| Attachment 4: Screenshot_from_2024-04-07_19-11-09.png

|

|

| Attachment 5: Screenshot_from_2024-04-07_19-10-45.png

|

|

| Attachment 6: Screenshot_from_2024-04-07_19-10-30.png

|

|

|

562

|

Sun Apr 7 13:08:52 2024 |

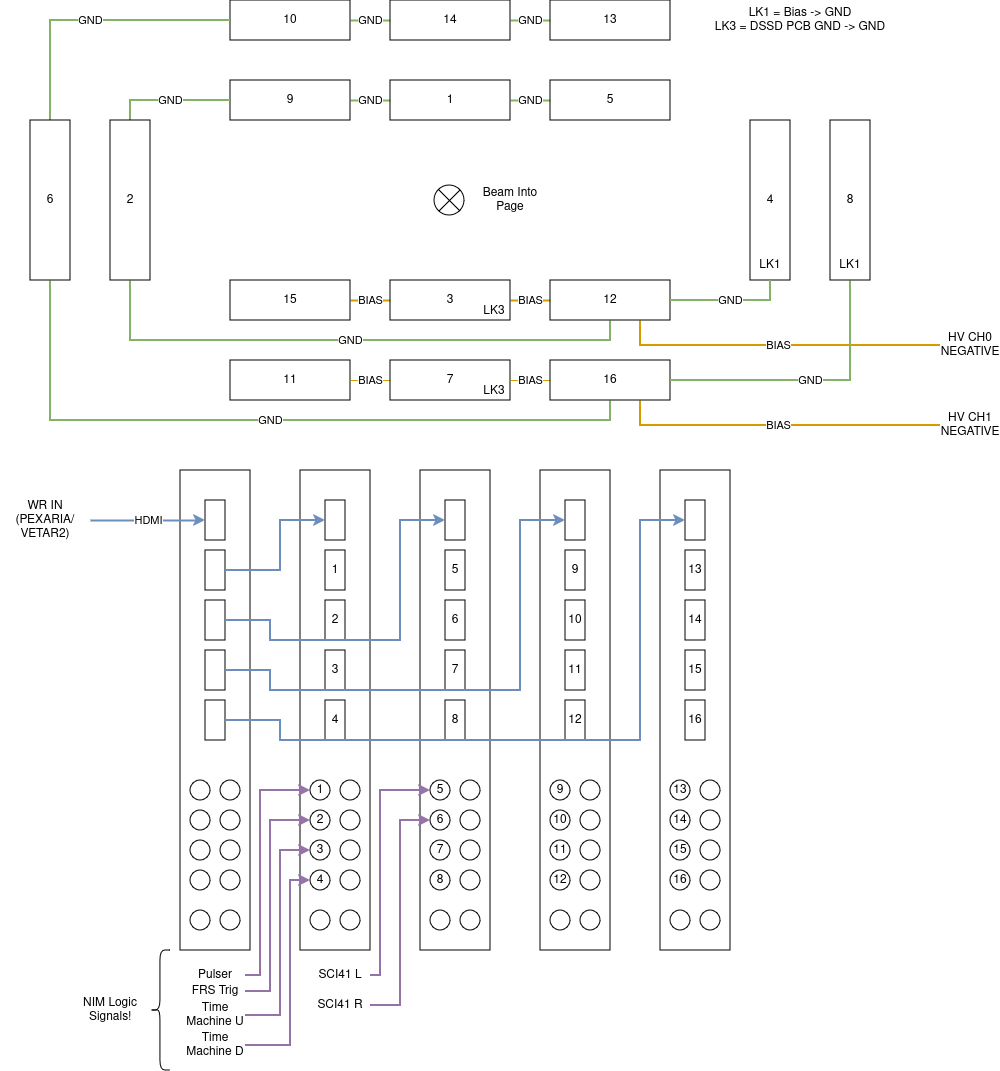

TD | FEE64 configuration |

FEE64 configuration per https://elog.gsi.de/despec/S100/6

Configuration: Wide - 16 FEEs, 2 DSSD

DSSD 1:

X 0-63 = 15

X 63-127 = 9

X 128-191 = 3

X 192-255 = 1

X 256-319 = 12

X 320-385 = 5

Y 0-63 = 4

Y 63-127 = 2

DSSD 2:

X 0-63 = 11

X 63-127 = 10

X 128-191 = 7

X 192-255 = 14

X 256-319 = 16

X 320-385 = 13

Y 0-63 = 8

Y 63-127 = 6

Scalers:

1 - Pulser

2 - FRS Accepted

3 - Time Machine Undelayed

4 - Time Machine Delayed

5 - SC41 L

6 - SC41 R

Thresholds (Slow / Fast / Implant)

DSSD 1 p+n : 0xA (100 keV) / 0xFF (disabled) / 0x02 (200 MeV)

DSSD 1 n+n : 0xF (150 keV) / 0xFF (disabled) / 0x02 (200 MeV) |

| Attachment 1: AIDA_S100_WiringPlan.drawio.png

|

|

|

561

|

Sun Apr 7 12:16:27 2024 |

TD | aida06 system console log |

ISOL Version 1.00 Date 9th January 2017

Flash base address=FC000000

Set Flash to ASync Mode

XST_SUCCESS:07:47|

Finished copying zImage to RAM

07:04:24/13:07:48|

Found 0 errors checking kernel image

07:04:24/13:07:49|VHDL version number 0X03350706

Based on AIDA Bootloader version number 1.2.0 -- 16th August 2012

Starting LMK 3200 setup

07:04:24/13:07:49|

Setting LMK03200 to standard clock settings -- External Clock 23Nov15

.... SPI Base Address=0x81400000

clk_control_reg=0x4

07:04:24/13:07:49|Next step is SPIconfig

Control 32(0x81400000)=0x180

SlaveSel(0x81400000)=0x3

Ctrl(0x81400000)=0xE6

Ctrl(0x81400000)=0x86

07:04:24/13:07:49|SPIconfig done now to set up the LMK3200 registers

07:04:24/13:07:49|LMK #0 : regInit[0]=0x80000000

07:04:24/13:07:49|LMK #0 : regInit[1]=0x10070600

07:04:24/13:07:49|LMK #0 : regInit[2]=0x60601

07:04:24/13:07:50|LMK #0 : regInit[3]=0x60602

07:04:24/13:07:50|LMK #0 : regInit[4]=0x60603

07:04:24/13:07:50|LMK #0 : regInit[5]=0x70624

07:04:24/13:07:50|LMK #0 : regInit[6]=0x70605

07:04:24/13:07:50|LMK #0 : regInit[7]=0x70606

07:04:24/13:07:50|LMK #0 : regInit[8]=0x70627

07:04:24/13:07:50|LMK #0 : regInit[9]=0x10000908

07:04:24/13:07:50|LMK #0 : regInit[10]=0xA0022A09

07:04:24/13:07:50|LMK #0 : regInit[11]=0x82800B

07:04:24/13:07:50|LMK #0 : regInit[12]=0x28C800D

07:04:24/13:07:50|LMK #0 : regInit[13]=0x830020E

07:04:24/13:07:50|LMK #0 : regInit[14]=0xC800180F

Calibrate completed at 943 counts

Setting Clock Control =0x0000000B, to set GOE and sync bit

Ctrl @ SPIstop (0x81400000)=0x186

Timeout waiting for Lock detect Stage 2 (Zero Delay), PWR_DWN=0x00000004

07:04:24/13:07:50|

Finished Clock setup LMK03200

completed LMK 3200 setup

Loaded all four ASICs with default settings

Setting the ADCs into calibration mode

07:04:24/13:07:50|

Control 32(0x81400400)=0x180

SlaveSel(0x81400400)=0xFF

Ctrl(0x81400400)=0xE6

Ctrl(0x81400400)=0x86

Init : Config of AD9252 SPI ok

07:04:24/13:07:50|

Ctrl @ SPIstop (0x81400400)=0x186ADCs initialised

Cal not completed

ADC calibrate failed

Jumping to kernel simpleboot...

07:04:24/13:07:51|

zImage starting: loaded at 0x00a00000 (sp: 0x00bc4eb0)

Allocating 0x3b78cc bytes for kernel ...

gunzipping (0x00000000 <- 0x00a0f000:0x00bc380e)...done 0x39604c bytes

07:04:24/13:07:54|

Linux/PowerPC load: console=ttyS0 root=/dev/nfs ip=on rw mem=112M

Finalizing device tree... flat tree at 0xbd1300

Probing IIC bus for MAC... MAC address = 0xd8 0x80 0x39 0x41 0xee 0x71

07:04:24/13:08:00|Using Xilinx Virtex440 machine description

07:04:24/13:08:01|Linux version 2.6.31 (nf@nnlxb.dl.ac.uk) (gcc version 4.2.2) #34 PREEMPT Tue Nov 15 15:57:04 GMT 2011

07:04:24/13:08:01|Zone PFN ranges:

07:04:24/13:08:01| DMA 0x00000000 -> 0x00007000

07:04:24/13:08:01| Normal 0x00007000 -> 0x00007000

07:04:24/13:08:01|Movable zone start PFN for each node

07:04:24/13:08:01|early_node_map[1] active PFN ranges

07:04:24/13:08:01| 0: 0x00000000 -> 0x00007000

07:04:24/13:08:01|MMU: Allocated 1088 bytes of context maps for 255 contexts

07:04:24/13:08:01|Built 1 zonelists in Zone order, mobility grouping on. Total pages: 28448

07:04:24/13:08:02|Kernel command line: console=ttyS0 root=/dev/nfs ip=on rw mem=112M

07:04:24/13:08:02|PID hash table entries: 512 (order: 9, 2048 bytes)

07:04:24/13:08:02|Dentry cache hash table entries: 16384 (order: 4, 65536 bytes)

07:04:24/13:08:02|Inode-cache hash table entries: 8192 (order: 3, 32768 bytes)

07:04:24/13:08:02|Memory: 109680k/114688k available (3500k kernel code, 4852k reserved, 144k data, 130k bss, 168k init)

07:04:24/13:08:02|Kernel virtual memory layout:

07:04:24/13:08:02| * 0xffffe000..0xfffff000 : fixmap

07:04:24/13:08:02| * 0xfde00000..0xfe000000 : consistent mem

07:04:24/13:08:02| * 0xfde00000..0xfde00000 : early ioremap

07:04:24/13:08:02| * 0xd1000000..0xfde00000 : vmalloc & ioremap

07:04:24/13:08:02|NR_IRQS:512

07:04:24/13:08:02|clocksource: timebase mult[a00000] shift[22] registered

07:04:24/13:08:02|Console: colour dummy device 80x25

07:04:24/13:08:02|Mount-cache hash table entries: 512

07:04:24/13:08:02|NET: Registered protocol family 16

07:04:24/13:08:02|PCI: Probing PCI hardware

07:04:24/13:08:02|bio: create slab <bio-0> at 0

07:04:24/13:08:02|NET: Registered protocol family 2

07:04:24/13:08:02|IP route cache hash table entries: 1024 (order: 0, 4096 bytes)

07:04:24/13:08:02|TCP established hash table entries: 4096 (order: 3, 32768 bytes)

07:04:24/13:08:03|TCP bind hash table entries: 4096 (order: 2, 16384 bytes)

07:04:24/13:08:03|TCP: Hash tables configured (established 4096 bind 4096)

07:04:24/13:08:03|TCP reno registered

07:04:24/13:08:03|NET: Registered protocol family 1

07:04:24/13:08:03|ROMFS MTD (C) 2007 Red Hat, Inc.

07:04:24/13:08:03|msgmni has been set to 214

07:04:24/13:08:03|io scheduler noop registered

07:04:24/13:08:03|io scheduler anticipatory registered

07:04:24/13:08:03|io scheduler deadline registered

07:04:24/13:08:03|io scheduler cfq registered (default)

07:04:24/13:08:03|Serial: 8250/16550 driver, 4 ports, IRQ sharing disabled

07:04:24/13:08:03|83e00000.serial: ttyS0 at MMIO 0x83e01003 (irq = 16) is a 16550

07:04:24/13:08:03|console [ttyS0] enabled

07:04:24/13:08:03|brd: module loaded

07:04:24/13:08:03|loop: module loaded

07:04:24/13:08:03|Device Tree Probing 'ethernet'

07:04:24/13:08:03|xilinx_lltemac 81c00000.ethernet: MAC address is now d8:80:39:41:ee:71

07:04:24/13:08:03|xilinx_lltemac 81c00000.ethernet: XLlTemac: using DMA mode.

07:04:24/13:08:03|XLlTemac: DCR address: 0x80

07:04:24/13:08:03|XLlTemac: buffer descriptor size: 32768 (0x8000)

07:04:24/13:08:03|XLlTemac: Allocating DMA descriptors with kmalloc

07:04:24/13:08:03|XLlTemac: (buffer_descriptor_init) phy: 0x6938000, virt: 0xc6938000, size: 0x8000

07:04:24/13:08:04|XTemac: PHY detected at address 7.

07:04:24/13:08:04|xilinx_lltemac 81c00000.ethernet: eth0: Xilinx TEMAC at 0x81C00000 mapped to 0xD1024000, irq=17

07:04:24/13:08:04|fc000000.flash: Found 1 x16 devices at 0x0 in 16-bit bank

07:04:24/13:08:04| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:08:04| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:08:04| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:08:04| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:08:04| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:08:04| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:08:04|Using buffer write method

07:04:24/13:08:04|cfi_cmdset_0001: Erase suspend on write enabled

07:04:24/13:08:04|cmdlinepart partition parsing not available

07:04:24/13:08:04|RedBoot partition parsing not available

07:04:24/13:08:04|Creating 5 MTD partitions on "fc000000.flash":

07:04:24/13:08:04|0x000000000000-0x000000500000 : "golden_firmware"

07:04:24/13:08:04|0x000000500000-0x000000800000 : "golden_kernel"

07:04:24/13:08:04|0x000000800000-0x000000d00000 : "user_firmware"

07:04:24/13:08:04|0x000000d00000-0x000000fe0000 : "user_kernel"

07:04:24/13:08:04|0x000000fe0000-0x000001000000 : "env_variables"

07:04:24/13:08:05|xilinx-xps-spi 81400400.hd-xps-spi: at 0x81400400 mapped to 0xD1028400, irq=20

07:04:24/13:08:05|SPI: XIlinx spi: bus number now 32766

07:04:24/13:08:05|xilinx-xps-spi 81400000.xps-spi: at 0x81400000 mapped to 0xD102C000, irq=21

07:04:24/13:08:05|SPI: XIlinx spi: bus number now 32765

07:04:24/13:08:05|mice: PS/2 mouse device common for all mice

07:04:24/13:08:05|Device Tree Probing 'i2c'

07:04:24/13:08:05| #0 at 0x81600000 mapped to 0xD1030000, irq=22

07:04:24/13:08:05|at24 0-0050: 1024 byte 24c08 EEPROM (writable)

07:04:24/13:08:05|TCP cubic registered

07:04:24/13:08:05|NET: Registered protocol family 17

07:04:24/13:08:05|RPC: Registered udp transport module.

07:04:24/13:08:05|RPC: Registered tcp transport module.

07:04:24/13:08:05|eth0: XLlTemac: Options: 0x3fa

07:04:24/13:08:06|eth0: XLlTemac: allocating interrupt 19 for dma mode tx.

07:04:24/13:08:06|eth0: XLlTemac: allocating interrupt 18 for dma mode rx.

07:04:24/13:08:06|eth0: XLlTemac: speed set to 1000Mb/s

07:04:24/13:08:08|eth0: XLlTemac: Send Threshold = 24, Receive Threshold = 4

07:04:24/13:08:08|eth0: XLlTemac: Send Wait bound = 254, Receive Wait bound = 254

07:04:24/13:08:08|Sending DHCP requests .

07:04:24/13:08:10|eth0: XLlTemac: PHY Link carrier lost.

07:04:24/13:08:10|..... timed out!

07:04:24/13:09:39|IP-Config: Reopening network devices...

07:04:24/13:09:39|eth0: XLlTemac: Options: 0x3fa

07:04:24/13:09:40|eth0: XLlTemac: allocating interrupt 19 for dma mode tx.

07:04:24/13:09:40|eth0: XLlTemac: allocating interrupt 18 for dma mode rx.

07:04:24/13:09:40|eth0: XLlTemac: speed set to 1000Mb/s

07:04:24/13:09:42|eth0: XLlTemac: Send Threshold = 24, Receive Threshold = 4

07:04:24/13:09:42|eth0: XLlTemac: Send Wait bound = 254, Receive Wait bound = 254

07:04:24/13:09:42|Sending DHCP requests ...... timed out!

07:04:24/13:11:15|IP-Config: Auto-configuration of network failed.

07:04:24/13:11:15|Root-NFS: No NFS server available, giving up.

07:04:24/13:11:15|VFS: Unable to mount root fs via NFS, trying floppy.

07:04:24/13:11:15|VFS: Cannot open root device "nfs" or unknown-block(2,0)

07:04:24/13:11:15|Please append a correct "root=" boot option; here are the available partitions:

07:04:24/13:11:15|Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(2,0)

07:04:24/13:11:15|Call Trace:

07:04:24/13:11:15|[c6827ed0] [c0005de8] show_stack+0x44/0x16c (unreliable)

07:04:24/13:11:15|[c6827f10] [c00345bc] panic+0x94/0x168

07:04:24/13:11:15|[c6827f60] [c0341d34] mount_block_root+0x12c/0x244

07:04:24/13:11:15|[c6827fb0] [c03420d8] prepare_namespace+0x17c/0x208

07:04:24/13:11:15|[c6827fd0] [c0341220] kernel_init+0x104/0x130

07:04:24/13:11:15|[c6827ff0] [c000e140] kernel_thread+0x4c/0x68

07:04:24/13:11:15|Rebooting in 180 seconds..

ISOL Version 1.00 Date 9th January 2017

Flash base address=FC000000

Set Flash to ASync Mode

XST_SUCCESS:14:15|

Finished copying zImage to RAM

07:04:24/13:14:16|

Found 0 errors checking kernel image

07:04:24/13:14:17|VHDL version number 0X03350706

Based on AIDA Bootloader version number 1.2.0 -- 16th August 2012

Starting LMK 3200 setup

07:04:24/13:14:17|

Setting LMK03200 to standard clock settings -- External Clock 23Nov15

.... SPI Base Address=0x81400000

clk_control_reg=0x4

07:04:24/13:14:17|Next step is SPIconfig

Control 32(0x81400000)=0x180

SlaveSel(0x81400000)=0x3

Ctrl(0x81400000)=0xE6

Ctrl(0x81400000)=0x86

07:04:24/13:14:17|SPIconfig done now to set up the LMK3200 registers

07:04:24/13:14:17|LMK #0 : regInit[0]=0x80000000

07:04:24/13:14:18|LMK #0 : regInit[1]=0x10070600

07:04:24/13:14:18|LMK #0 : regInit[2]=0x60601

07:04:24/13:14:18|LMK #0 : regInit[3]=0x60602

07:04:24/13:14:18|LMK #0 : regInit[4]=0x60603

07:04:24/13:14:18|LMK #0 : regInit[5]=0x70624

07:04:24/13:14:18|LMK #0 : regInit[6]=0x70605

07:04:24/13:14:18|LMK #0 : regInit[7]=0x70606

07:04:24/13:14:18|LMK #0 : regInit[8]=0x70627

07:04:24/13:14:18|LMK #0 : regInit[9]=0x10000908

07:04:24/13:14:18|LMK #0 : regInit[10]=0xA0022A09

07:04:24/13:14:18|LMK #0 : regInit[11]=0x82800B

07:04:24/13:14:18|LMK #0 : regInit[12]=0x28C800D

07:04:24/13:14:18|LMK #0 : regInit[13]=0x830020E

07:04:24/13:14:18|LMK #0 : regInit[14]=0xC800180F

Calibrate completed at 941 counts

Setting Clock Control =0x0000000B, to set GOE and sync bit

Ctrl @ SPIstop (0x81400000)=0x186

Timeout waiting for Lock detect Stage 2 (Zero Delay), PWR_DWN=0x00000004

07:04:24/13:14:18|

Finished Clock setup LMK03200

completed LMK 3200 setup

Loaded all four ASICs with default settings

Setting the ADCs into calibration mode

07:04:24/13:14:18|

Control 32(0x81400400)=0x180

SlaveSel(0x81400400)=0xFF

Ctrl(0x81400400)=0xE6

Ctrl(0x81400400)=0x86

Init : Config of AD9252 SPI ok

07:04:24/13:14:19|

Ctrl @ SPIstop (0x81400400)=0x186ADCs initialised

Cal DCMs not locked

ADC calibrate failed

Jumping to kernel simpleboot...

07:04:24/13:14:19|

zImage starting: loaded at 0x00a00000 (sp: 0x00bc4eb0)

Allocating 0x3b78cc bytes for kernel ...

gunzipping (0x00000000 <- 0x00a0f000:0x00bc380e)...done 0x39604c bytes

07:04:24/13:14:22|

Linux/PowerPC load: console=ttyS0 root=/dev/nfs ip=on rw mem=112M

Finalizing device tree... flat tree at 0xbd1300

Probing IIC bus for MAC... MAC address = 0xd8 0x80 0x39 0x41 0xee 0x71

07:04:24/13:14:28|Using Xilinx Virtex440 machine description

07:04:24/13:14:29|Linux version 2.6.31 (nf@nnlxb.dl.ac.uk) (gcc version 4.2.2) #34 PREEMPT Tue Nov 15 15:57:04 GMT 2011

07:04:24/13:14:29|Zone PFN ranges:

07:04:24/13:14:29| DMA 0x00000000 -> 0x00007000

07:04:24/13:14:29| Normal 0x00007000 -> 0x00007000

07:04:24/13:14:29|Movable zone start PFN for each node

07:04:24/13:14:29|early_node_map[1] active PFN ranges

07:04:24/13:14:29| 0: 0x00000000 -> 0x00007000

07:04:24/13:14:29|MMU: Allocated 1088 bytes of context maps for 255 contexts

07:04:24/13:14:29|Built 1 zonelists in Zone order, mobility grouping on. Total pages: 28448

07:04:24/13:14:29|Kernel command line: console=ttyS0 root=/dev/nfs ip=on rw mem=112M

07:04:24/13:14:30|PID hash table entries: 512 (order: 9, 2048 bytes)

07:04:24/13:14:30|Dentry cache hash table entries: 16384 (order: 4, 65536 bytes)

07:04:24/13:14:30|Inode-cache hash table entries: 8192 (order: 3, 32768 bytes)

07:04:24/13:14:30|Memory: 109680k/114688k available (3500k kernel code, 4852k reserved, 144k data, 130k bss, 168k init)

07:04:24/13:14:30|Kernel virtual memory layout:

07:04:24/13:14:30| * 0xffffe000..0xfffff000 : fixmap

07:04:24/13:14:30| * 0xfde00000..0xfe000000 : consistent mem

07:04:24/13:14:30| * 0xfde00000..0xfde00000 : early ioremap

07:04:24/13:14:30| * 0xd1000000..0xfde00000 : vmalloc & ioremap

07:04:24/13:14:30|NR_IRQS:512

07:04:24/13:14:30|clocksource: timebase mult[a00000] shift[22] registered

07:04:24/13:14:30|Console: colour dummy device 80x25

07:04:24/13:14:30|Mount-cache hash table entries: 512

07:04:24/13:14:30|NET: Registered protocol family 16

07:04:24/13:14:30|PCI: Probing PCI hardware

07:04:24/13:14:30|bio: create slab <bio-0> at 0

07:04:24/13:14:30|NET: Registered protocol family 2

07:04:24/13:14:30|IP route cache hash table entries: 1024 (order: 0, 4096 bytes)

07:04:24/13:14:30|TCP established hash table entries: 4096 (order: 3, 32768 bytes)

07:04:24/13:14:31|TCP bind hash table entries: 4096 (order: 2, 16384 bytes)

07:04:24/13:14:31|TCP: Hash tables configured (established 4096 bind 4096)

07:04:24/13:14:31|TCP reno registered

07:04:24/13:14:31|NET: Registered protocol family 1

07:04:24/13:14:31|ROMFS MTD (C) 2007 Red Hat, Inc.

07:04:24/13:14:31|msgmni has been set to 214

07:04:24/13:14:31|io scheduler noop registered

07:04:24/13:14:31|io scheduler anticipatory registered

07:04:24/13:14:31|io scheduler deadline registered

07:04:24/13:14:31|io scheduler cfq registered (default)

07:04:24/13:14:31|Serial: 8250/16550 driver, 4 ports, IRQ sharing disabled

07:04:24/13:14:31|83e00000.serial: ttyS0 at MMIO 0x83e01003 (irq = 16) is a 16550

07:04:24/13:14:31|console [ttyS0] enabled

07:04:24/13:14:31|brd: module loaded

07:04:24/13:14:31|loop: module loaded

07:04:24/13:14:31|Device Tree Probing 'ethernet'

07:04:24/13:14:31|xilinx_lltemac 81c00000.ethernet: MAC address is now d8:80:39:41:ee:71

07:04:24/13:14:31|xilinx_lltemac 81c00000.ethernet: XLlTemac: using DMA mode.

07:04:24/13:14:31|XLlTemac: DCR address: 0x80

07:04:24/13:14:31|XLlTemac: buffer descriptor size: 32768 (0x8000)

07:04:24/13:14:31|XLlTemac: Allocating DMA descriptors with kmalloc

07:04:24/13:14:31|XLlTemac: (buffer_descriptor_init) phy: 0x6938000, virt: 0xc6938000, size: 0x8000

07:04:24/13:14:32|XTemac: PHY detected at address 7.

07:04:24/13:14:32|xilinx_lltemac 81c00000.ethernet: eth0: Xilinx TEMAC at 0x81C00000 mapped to 0xD1024000, irq=17

07:04:24/13:14:32|fc000000.flash: Found 1 x16 devices at 0x0 in 16-bit bank

07:04:24/13:14:32| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:14:32| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:14:32| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:14:32| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:14:32| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:14:32| Intel/Sharp Extended Query Table at 0x010A

07:04:24/13:14:32|Using buffer write method

07:04:24/13:14:32|cfi_cmdset_0001: Erase suspend on write enabled

07:04:24/13:14:32|cmdlinepart partition parsing not available

07:04:24/13:14:32|RedBoot partition parsing not available

07:04:24/13:14:32|Creating 5 MTD partitions on "fc000000.flash":

07:04:24/13:14:32|0x000000000000-0x000000500000 : "golden_firmware"

07:04:24/13:14:32|0x000000500000-0x000000800000 : "golden_kernel"

07:04:24/13:14:32|0x000000800000-0x000000d00000 : "user_firmware"

07:04:24/13:14:32|0x000000d00000-0x000000fe0000 : "user_kernel"

07:04:24/13:14:32|0x000000fe0000-0x000001000000 : "env_variables"

07:04:24/13:14:33|xilinx-xps-spi 81400400.hd-xps-spi: at 0x81400400 mapped to 0xD1028400, irq=20

07:04:24/13:14:33|SPI: XIlinx spi: bus number now 32766

07:04:24/13:14:33|xilinx-xps-spi 81400000.xps-spi: at 0x81400000 mapped to 0xD102C000, irq=21

07:04:24/13:14:33|SPI: XIlinx spi: bus number now 32765

07:04:24/13:14:33|mice: PS/2 mouse device common for all mice

07:04:24/13:14:33|Device Tree Probing 'i2c'

07:04:24/13:14:33| #0 at 0x81600000 mapped to 0xD1030000, irq=22

07:04:24/13:14:33|at24 0-0050: 1024 byte 24c08 EEPROM (writable)

07:04:24/13:14:33|TCP cubic registered

07:04:24/13:14:33|NET: Registered protocol family 17

07:04:24/13:14:33|RPC: Registered udp transport module.

07:04:24/13:14:33|RPC: Registered tcp transport module.

07:04:24/13:14:33|eth0: XLlTemac: Options: 0x3fa

07:04:24/13:14:34|eth0: XLlTemac: allocating interrupt 19 for dma mode tx.

07:04:24/13:14:34|eth0: XLlTemac: allocating interrupt 18 for dma mode rx.

07:04:24/13:14:34|eth0: XLlTemac: speed set to 1000Mb/s

07:04:24/13:14:36|eth0: XLlTemac: Send Threshold = 24, Receive Threshold = 4

07:04:24/13:14:36|eth0: XLlTemac: Send Wait bound = 254, Receive Wait bound = 254

07:04:24/13:14:36|Sending DHCP requests ., OK

07:04:24/13:14:37|IP-Config: Got DHCP answer from 192.168.11.99, my address is 192.168.11.6

07:04:24/13:14:37|IP-Config: Complete:

07:04:24/13:14:37| device=eth0, addr=192.168.11.6, mask=255.255.255.0, gw=255.255.255.255,

07:04:24/13:14:37| host=aida06, domain=dl.ac.uk, nis-domain=nuclear.physics,

07:04:24/13:14:37| bootserver=192.168.11.99, rootserver=192.168.11.99, rootpath=/home/Embedded/XilinxLinux/ppc_4xx/rfs/aida06

07:04:24/13:14:37|Looking up port of RPC 100003/2 on 192.168.11.99

07:04:24/13:14:37|Looking up port of RPC 100005/1 on 192.168.11.99

07:04:24/13:14:37|VFS: Mounted root (nfs filesystem) on device 0:12.

07:04:24/13:14:38|Freeing unused kernel memory: 168k init

INIT: version 2.86 booting

07:04:24/13:14:38|Starting sysinit...

07:04:24/13:14:38| Welcome to DENX & STFC Daresbury Embedded Linux Environment

07:04:24/13:14:39| Press 'I' to enter interactive startup.

07:04:24/13:14:39|Setting clock (utc): Sun Apr 7 12:14:39 BST 2024 [ OK ]

07:04:24/13:14:39|Building the cache [ OK ]

07:04:24/13:14:39|Setting hostname aida06: [ OK ]

07:04:24/13:14:41|Mounting local filesystems: [ OK ]

07:04:24/13:14:42|Enabling /etc/fstab swaps: [ OK ]

07:04:24/13:14:45|Finishing sysinit...

INIT: Entering runlevel: 3

07:04:24/13:14:48|Entering non-interactive startup

07:04:24/13:14:48|FATAL: Module ipv6 not found.

07:04:24/13:14:49|Bringing up loopback interface: [ OK ]

07:04:24/13:14:52|FATAL: Module ipv6 not found.

07:04:24/13:14:53|Starting system logger: [ OK ]

07:04:24/13:14:54|Starting kernel logger: [ OK ]

07:04:24/13:14:54|Starting rpcbind: [ OK ]

07:04:24/13:14:56|Mounting NFS filesystems: [ OK ]

07:04:24/13:14:56|Mounting other filesystems: [ OK ]

07:04:24/13:14:56|Starting xinetd: [ OK ]

07:04:24/13:14:57|Starting midas: Starting MIDAS Data Acquisition for aida06

07:04:24/13:14:58|xaida: device parameters: base=0x81000000 size=0x200000

07:04:24/13:15:03|Trying to free nonexistent resource <0000000081000000-00000000811fffff>

07:04:24/13:15:03|xaida: mem region start 0x81000000 for 0x200000 mapped at 0xd2100000

07:04:24/13:15:03|xaida: driver assigned major number 254

07:04:24/13:15:04|Trying to free nonexistent resource <0000000007000000-0000000007ffffff>

07:04:24/13:15:09|AIDAMEM: aidamem: mem region start 0x7000000 for 0x1000000 mapped at 0xd2380000

07:04:24/13:15:09|AIDAMEM: aidamem: driver assigned major number 253

07:04:24/13:15:09|System identified is CPU ppc; Platform is unix; OS is Linux and Version is 2.6.31

07:04:24/13:15:16|Environment selected is CPU ppc; Platform unix; OS Linux and Operating System linux-ppc_4xx

07:04:24/13:15:16|MIDASBASE = /MIDAS and MIDAS_LIBRARY = /MIDAS/TclHttpd/linux-ppc_4xx

07:04:24/13:15:16|PATH = /MIDAS/bin_linux-ppc_4xx:/MIDAS/TclHttpd/linux-ppc_4xx:/MIDAS/linux-ppc_4xx/bin:/MIDAS/linux-ppc_4xx/bin:/sbin:/usr/sbin:/bin:/usr/bin

07:04:24/13:15:16|Computer Name = aida06; Temp Directory = /tmp/tcl361

07:04:24/13:15:21|

07:04:24/13:15:25|AIDA Data Acquisition Program Release 10.0.Jul 6 2022_15:10:57 starting

07:04:24/13:15:25|

07:04:24/13:15:25|Built without pthreads

07:04:24/13:15:25|

07:04:24/13:15:25|Creating NetVars

07:04:24/13:15:25|Output buffer length = 65504; format option = 4; transfer option = 3

07:04:24/13:15:25|EB transfer option = 3

07:04:24/13:15:26|NetVars creaxaida: open:

07:04:24/13:15:26|ted and initialised

07:04:24/13:15:26|StatisticsAIDAMEM: aidamem_open:

07:04:24/13:15:26| thread starting

07:04:24/13:15:26|Data Acquisition task has PID 375

07:04:24/13:15:26|Statistics thread created

07:04:24/13:15:26|Stat/Rate creation thread starting

07:04:24/13:15:26|Stat/Rate creation thread created

07:04:24/13:15:26|Hit/Rate creation thread starting

07:04:24/13:15:26|Hit/Rate creation thread created

07:04:24/13:15:26|AIDA Heartbeat thread starting

07:04:24/13:15:26|Heartbeat thread created

07:04:24/13:15:26|Installing signal handlers

07:04:24/13:15:26|Done

07:04:24/13:15:26|ModuleNum = 0

07:04:24/13:15:26|Aida Initialise complete. AidaExecV10.0: Build Jul 6 2022_15:10:57. HDL version : 03350706

07:04:24/13:15:26|package limit is not available: can't find package limit

07:04:24/13:15:26|Running with default file descriptor limit

07:04:24/13:15:26|Spectra table initialised

07:04:24/13:15:26|AIDA Data Acquisition now all ready to start

07:04:24/13:15:26|SIGBUS, SIGSEGV and SIGPIPE traps setup

07:04:24/13:15:26|package setuid is not available: can't find package setuid

07:04:24/13:15:27|Running as user 0 group 0

07:04:24/13:15:27|[ OK ]

07:04:24/13:15:36|

07:04:24/13:15:36|DENX ELDK version 4.2 build 2008-04-01

07:04:24/13:15:36|Linux 2.6.31 on a ppc

07:04:24/13:15:36|

07:04:24/13:15:36|aida06 login: /debug user |

|

560

|

Sun Apr 7 12:02:23 2024 |

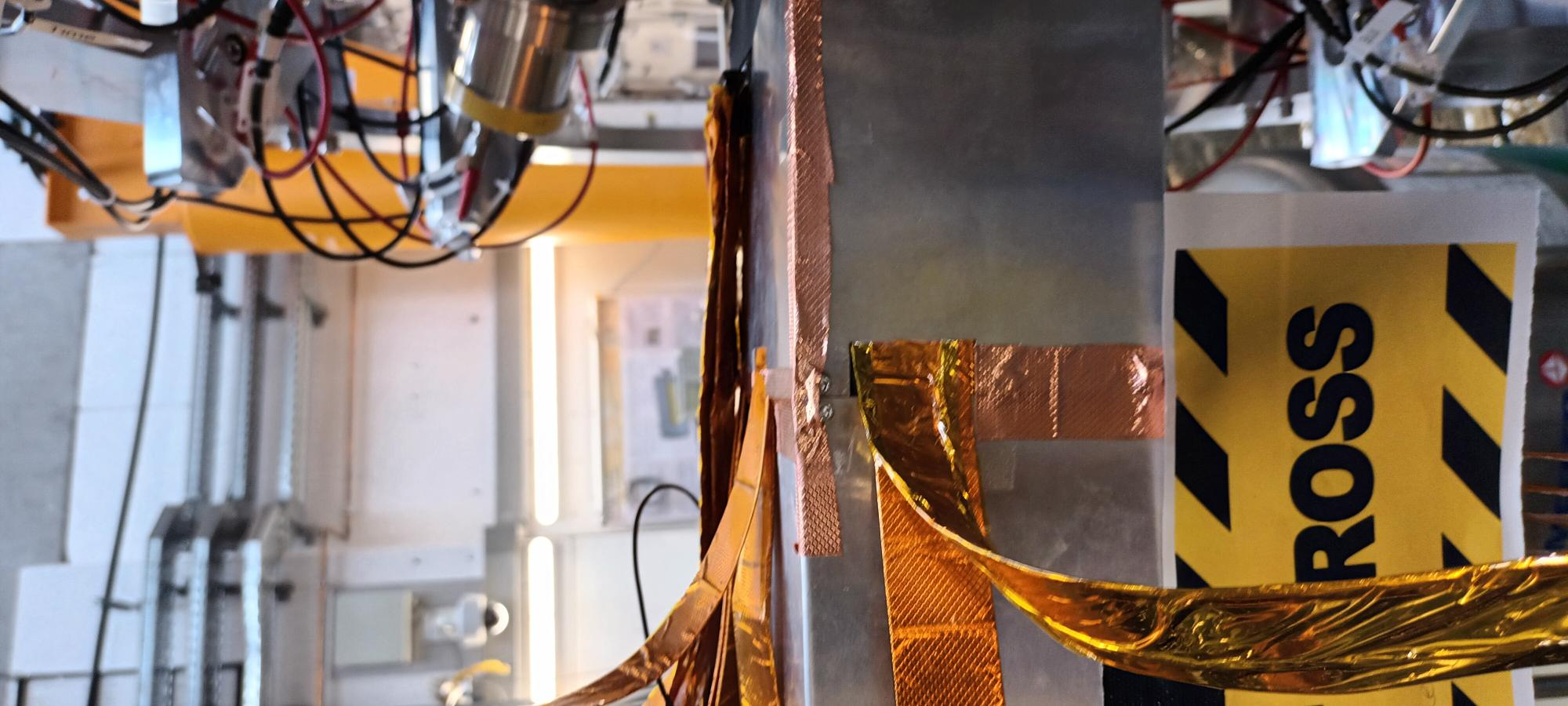

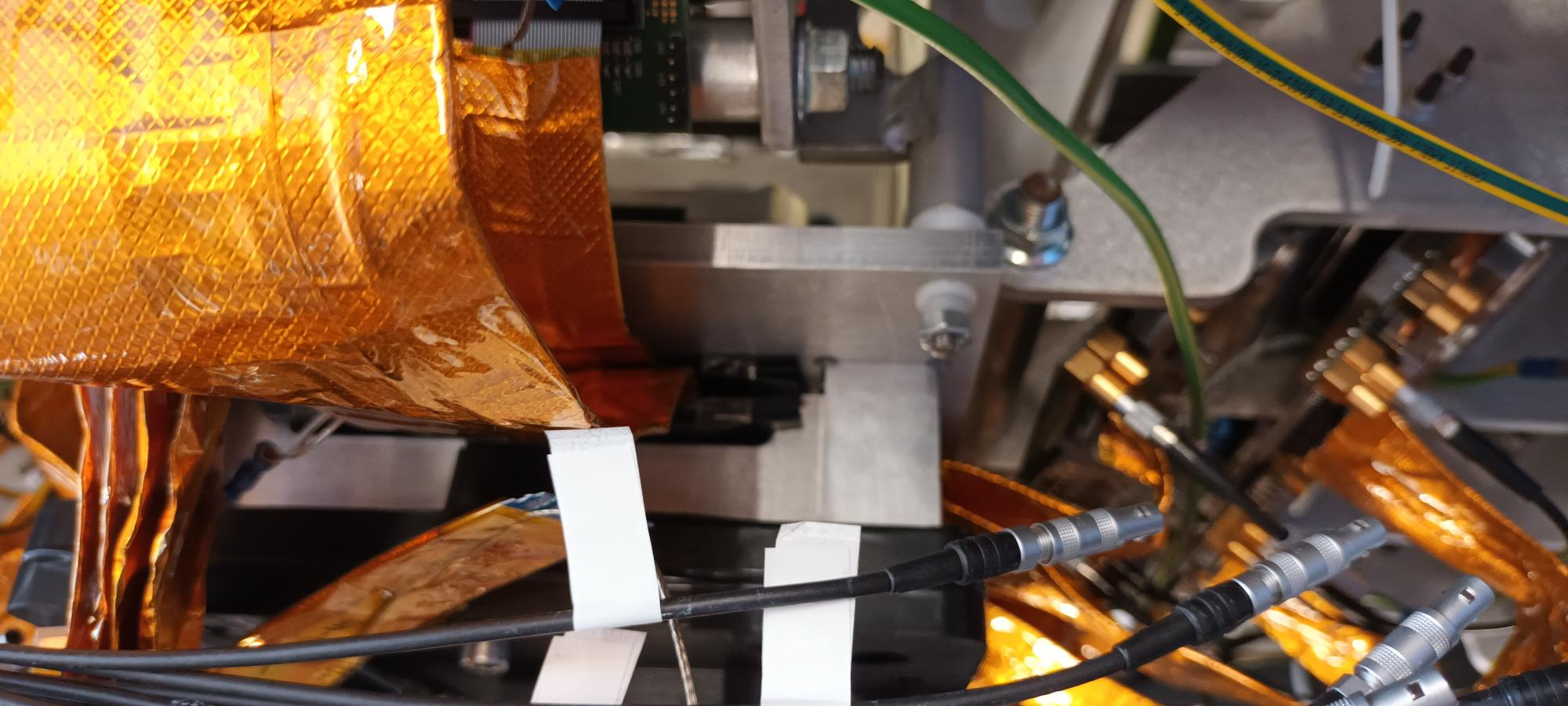

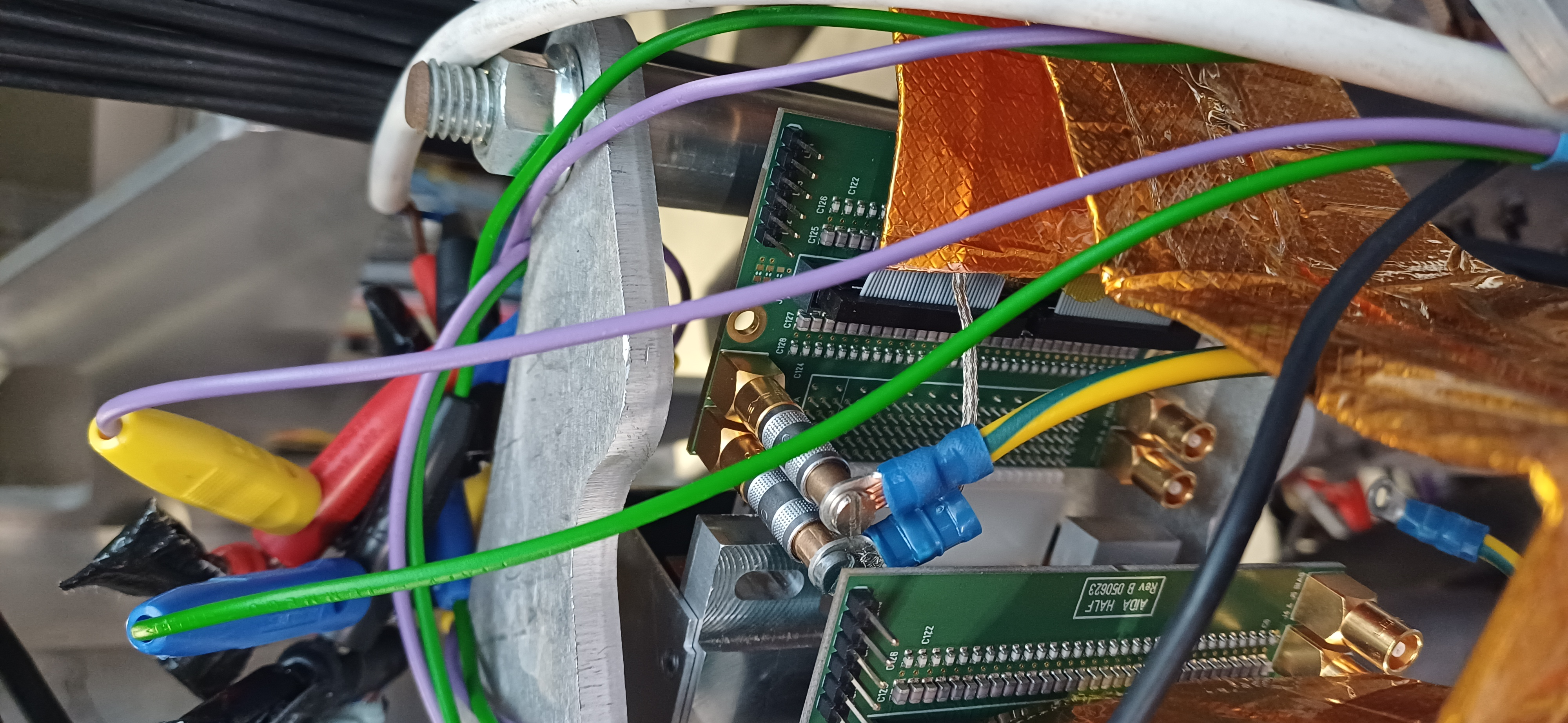

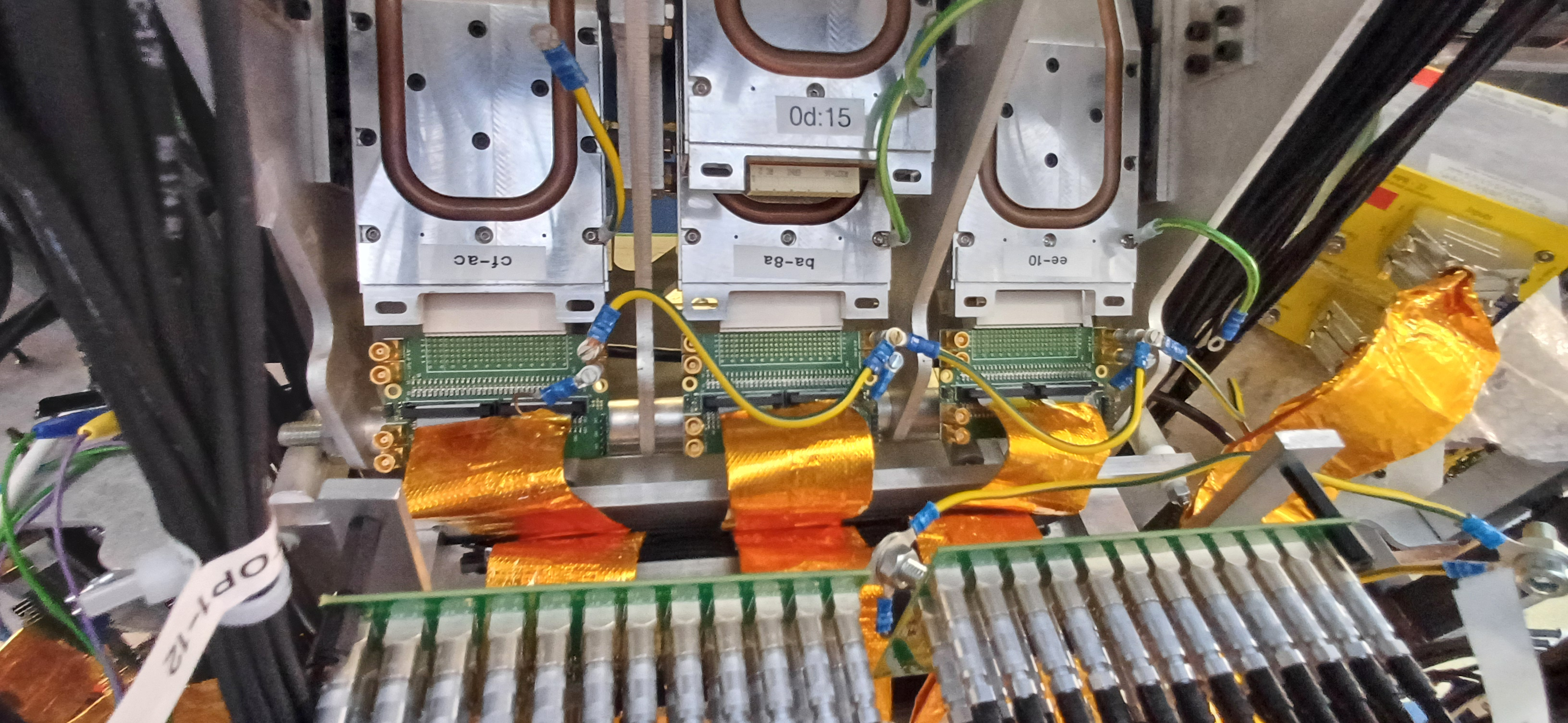

TD | Sunday 7 April |

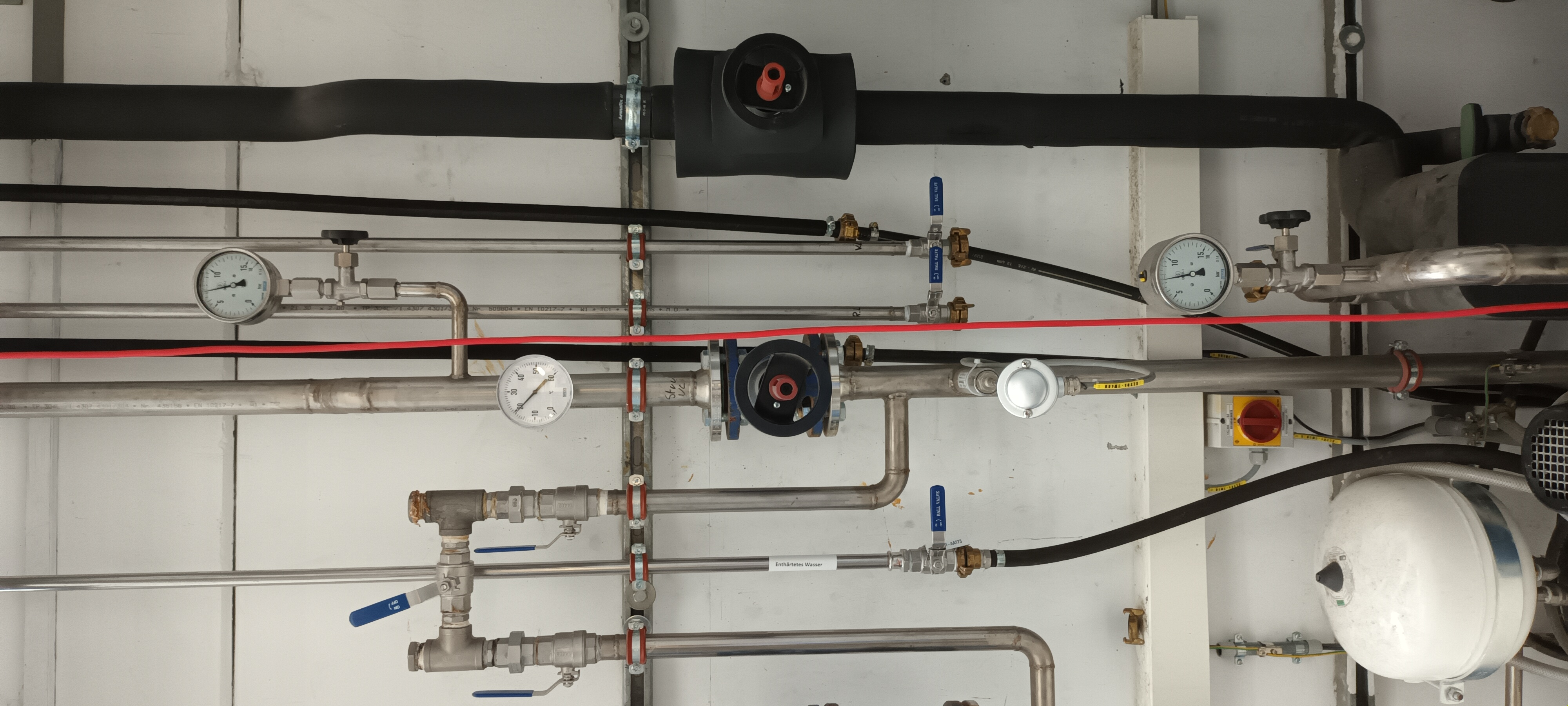

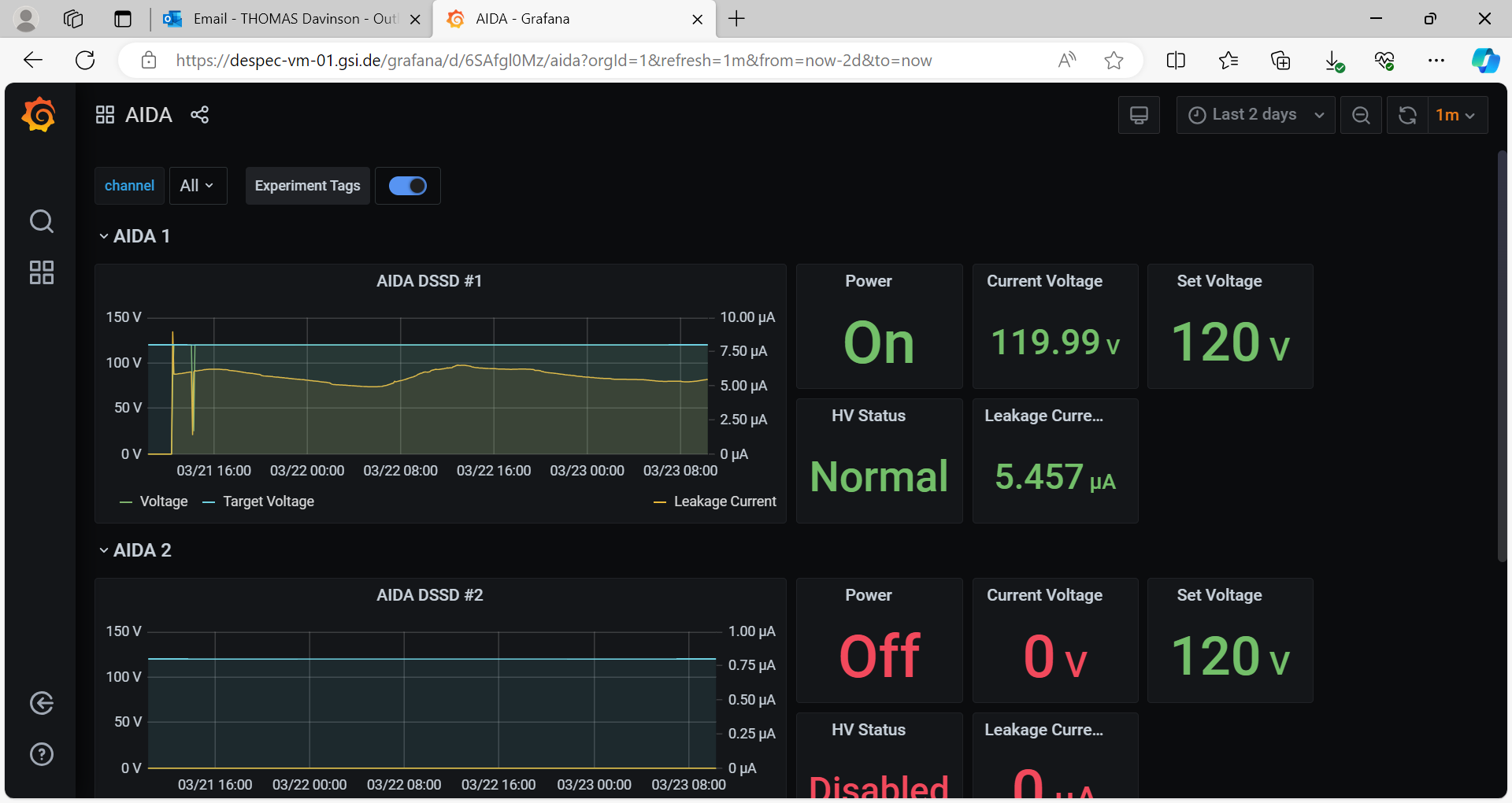

13.00 Cooling water temperature and flow OK - attachment 1

Test of AIDA 2x MSL type BB18(DS)-1000 24cm x 8cm DSSSDs 'as is' ( to be defined later in this Elog )

DSSSD bias & leakage current OK - attachment 2

Ambient temp 24.7 deg C, d.p. 7.1 deg C, RH 32.4%

Leakage current c. 6.6uA => 4nA/cm2/100um ( very good )

FEE64 temps OK - attachment 3

*except* aida02 ASIC temp which is known to be u/s

All system wide checks OK *except* aida02 and aida04 WR decoder status - attachment 4

WR timestamps OK - attachment 5

WR (info code 4 & 5), correlation scaler, PAUSE, RESUME, DISC, ADC data item stats - attachments 6-12

per FEE64 Rate spectra - attachments 13-15

per 1.8.W spectra - 20us FSR - attachments 16-1710129

14.45 FEE64 config check - per https://elog.ph.ed.ac.uk/DESPEC/562

FEE64 # PSU cable # MAC

1 1 ?

2 2 ?

3 3 ?

4 4 41 ee 71

5 5 ?

6 6 ?

7 7 f6 5a

8 8 41 d7 cd

9 ? ?

10 10 41 d0 0e

11 11 41 ee 0f

12 ? ?

13 13 ?

14 ? 0d 15

15 15 ?

16 16 f6 ed

? = no line of sight

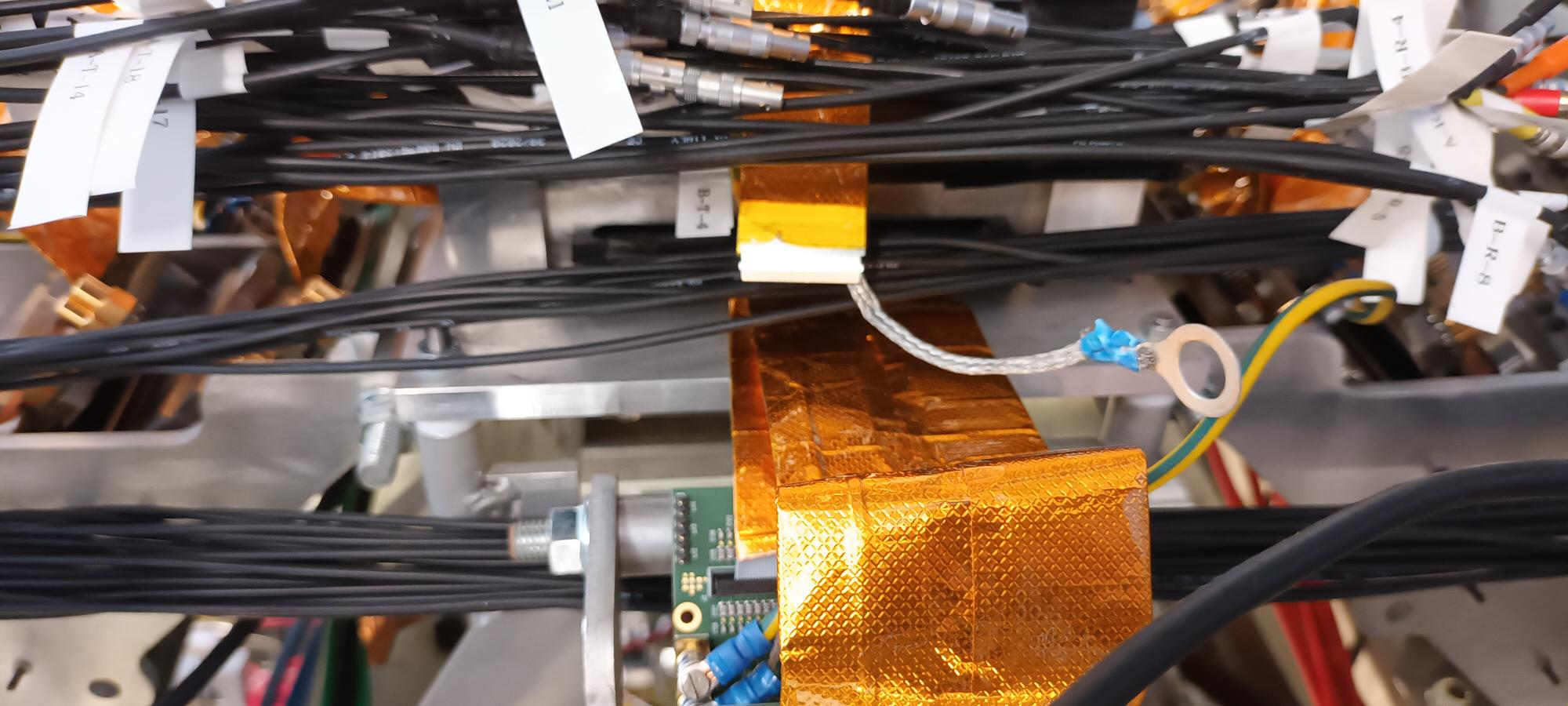

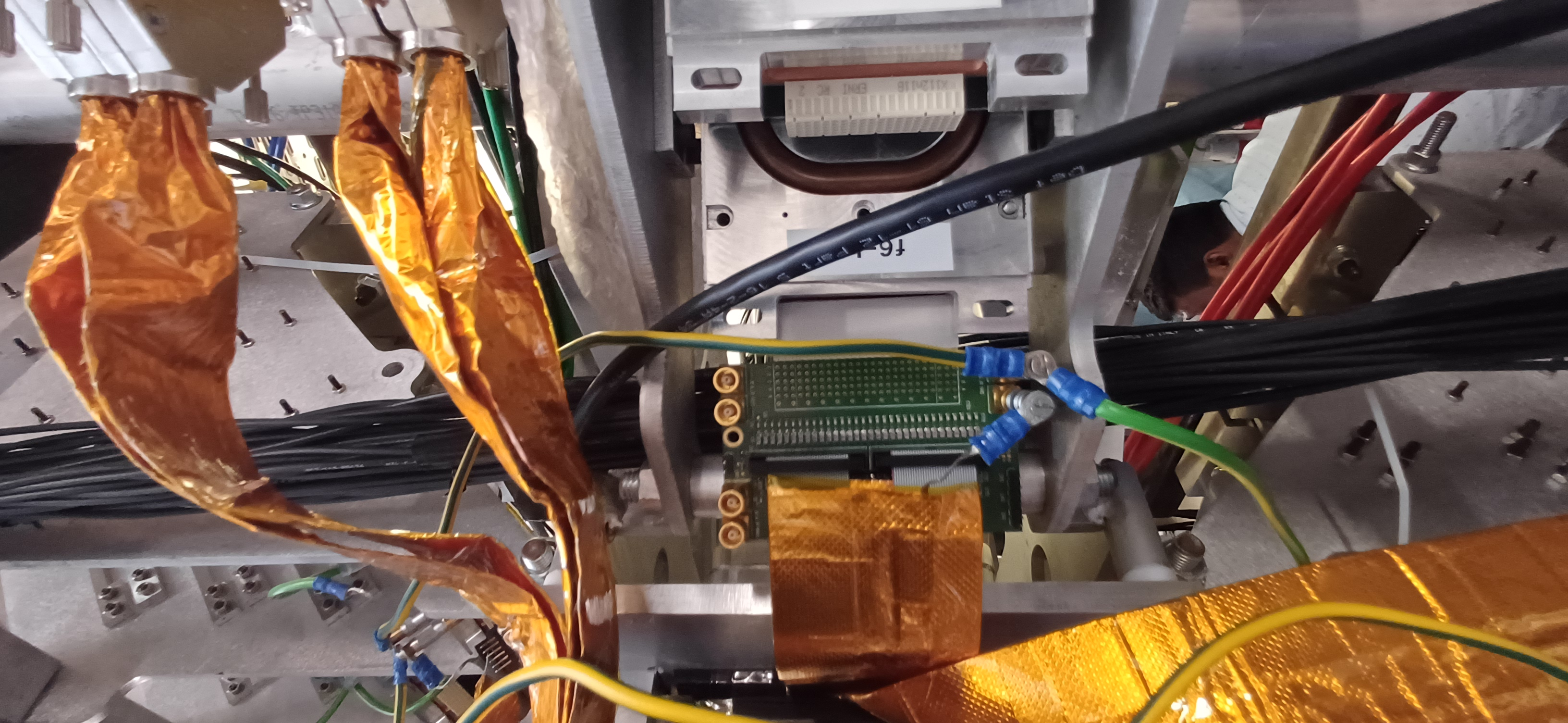

- AIDA FEE64 PSU cabling - see attachment 18

Currently

PSU #1 1-3, 2-4, 9-5, 15-12

PSU #2 14-7, 6-8, 10-13, 11-16

Should be changed to

PSU #1 1-3, 2-4, 9-15, 5-12

PSU #2 14-7, 6-8, 10-11, 13-16

- AIDA snout mount to support frame - attachments 19 & 21

LHS ( looking downstream ) incorrect, RHS OK

- LKs

LK1 fitted aida02, aida04, aida06, aida08

LK3 fitted aida03, aida07, aida01, aida14

Significant gaps in snout ( i.e. possible light leaks ) where bPlas cabling exits snout - attachments 20 & 22

bPlas driver PCBs removed

bPlas ribbon cables, drain wires and Lemo 00.250 cabling disconnected - some cabling/drain wires touching snout etc

15.15 Adjust bPlas ribbon cables/drain wires/Lemo cables to ensure that none are touching snout or AIDA support frame - significant improvement

DSSSD bias & leakage current OK - attachment 23

FEE64 temps OK - attachment 24

ADC data item stats - attachments 25

per FEE64 Rate spectra - attachments 26

6x FEE64s < 20k. all FEE64s < 120k ( cf. 4x FEE64s < 20k, 5x FEE64s > 100k, 1x FEE64 320k earlier - attachment 12 )

per 1.8.W spectra - 20us FSR - attachments 27-28

17.15

LHS top hat washers

LK1, LK3

PSU power cables

tighten gnd screws

attachments 29-34

Note that some of the newly installed FEE64s have the incorrect rails fitted - FEE64s may ground to AIDA support stand

17.55 CAEN N1419ET LK removed -> floating outputs

18.15 +LK1 restored

attachments 35-40

18.40 +pwwer cycle

attachments 41-46 |

| Attachment 1: 20240407_125941.jpg

|

|

| Attachment 2: Screenshot_from_2024-04-07_13-20-57.png

|

|

| Attachment 3: Screenshot_from_2024-04-07_13-29-54.png

|

|

| Attachment 4: Screenshot_from_2024-04-07_13-32-14.png

|

|

| Attachment 5: Screenshot_from_2024-04-07_13-36-47.png

|

|

| Attachment 6: Screenshot_from_2024-04-07_13-42-52.png

|

|

| Attachment 7: Screenshot_from_2024-04-07_13-42-26.png

|

|

| Attachment 8: Screenshot_from_2024-04-07_13-42-04.png

|

|

| Attachment 9: Screenshot_from_2024-04-07_13-41-37.png

|

|

| Attachment 10: Screenshot_from_2024-04-07_13-41-25.png

|

|

| Attachment 11: Screenshot_from_2024-04-07_13-41-03.png

|

|

| Attachment 12: Screenshot_from_2024-04-07_13-40-35.png

|

|

| Attachment 13: Screenshot_from_2024-04-07_13-47-03.png

|

|

| Attachment 14: Screenshot_from_2024-04-07_13-46-47.png

|

|

| Attachment 15: Screenshot_from_2024-04-07_13-46-39.png

|

|

| Attachment 16: Screenshot_from_2024-04-07_13-53-21.png

|

|

| Attachment 17: Screenshot_from_2024-04-07_13-52-25.png

|

|

| Attachment 18: 20240407_143456.jpg

|

|

| Attachment 19: 20240407_143510.jpg

|

|

| Attachment 20: 20240407_143553.jpg

|

|

| Attachment 21: 20240407_143532.jpg

|

|

| Attachment 22: 20240407_143539.jpg

|

|

| Attachment 23: Screenshot_from_2024-04-07_15-10-39.png

|

|

| Attachment 24: Screenshot_from_2024-04-07_15-10-53.png

|

|

| Attachment 25: Screenshot_from_2024-04-07_15-13-00.png

|

|

| Attachment 26: Screenshot_from_2024-04-07_15-12-49.png

|

|

| Attachment 27: Screenshot_from_2024-04-07_15-11-54.png

|

|

| Attachment 28: Screenshot_from_2024-04-07_15-11-06.png

|

|

| Attachment 29: Screenshot_from_2024-04-07_17-14-23.png

|

|

| Attachment 30: Screenshot_from_2024-04-07_17-13-49.png

|

|

| Attachment 31: Screenshot_from_2024-04-07_17-11-59.png

|

|

| Attachment 32: Screenshot_from_2024-04-07_17-11-47.png

|

|

| Attachment 33: Screenshot_from_2024-04-07_17-11-38.png

|

|

| Attachment 34: Screenshot_from_2024-04-07_17-11-19.png

|

|

| Attachment 35: Screenshot_from_2024-04-07_18-12-38.png

|

|

| Attachment 36: Screenshot_from_2024-04-07_18-12-53.png

|

|

| Attachment 37: Screenshot_from_2024-04-07_18-13-03.png

|

|

| Attachment 38: Screenshot_from_2024-04-07_18-14-51.png

|

|

| Attachment 39: Screenshot_from_2024-04-07_18-14-12.png

|

|

| Attachment 40: Screenshot_from_2024-04-07_18-13-10.png

|

|

| Attachment 41: Screenshot_from_2024-04-07_18-44-32.png

|

|

| Attachment 42: Screenshot_from_2024-04-07_18-44-08.png

|

|

| Attachment 43: Screenshot_from_2024-04-07_18-43-30.png

|

|

| Attachment 44: Screenshot_from_2024-04-07_18-43-21.png

|

|

| Attachment 45: Screenshot_from_2024-04-07_18-43-12.png

|

|

| Attachment 46: Screenshot_from_2024-04-07_18-42-56.png

|

|

|

559

|

Wed Apr 3 13:02:19 2024 |

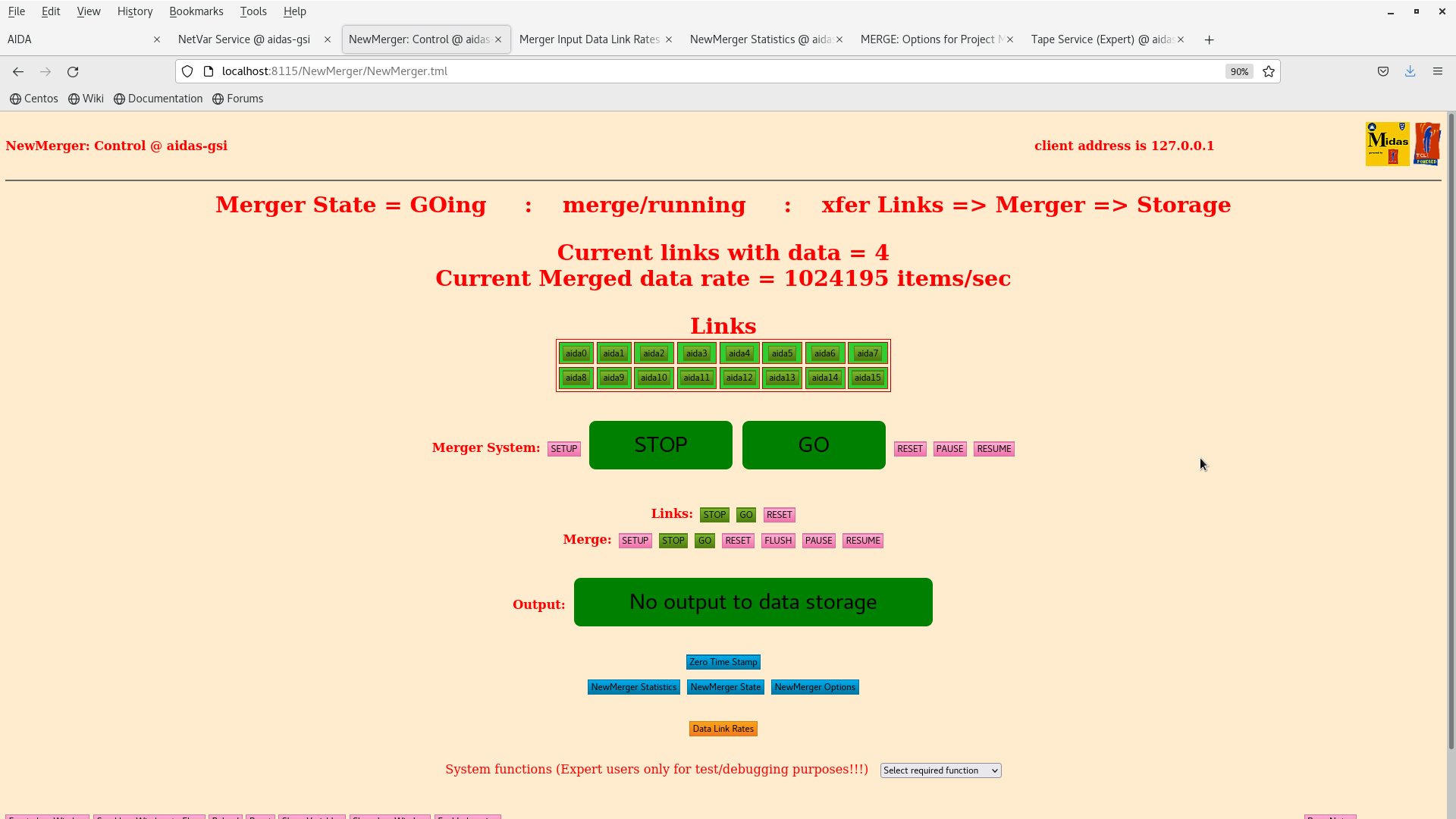

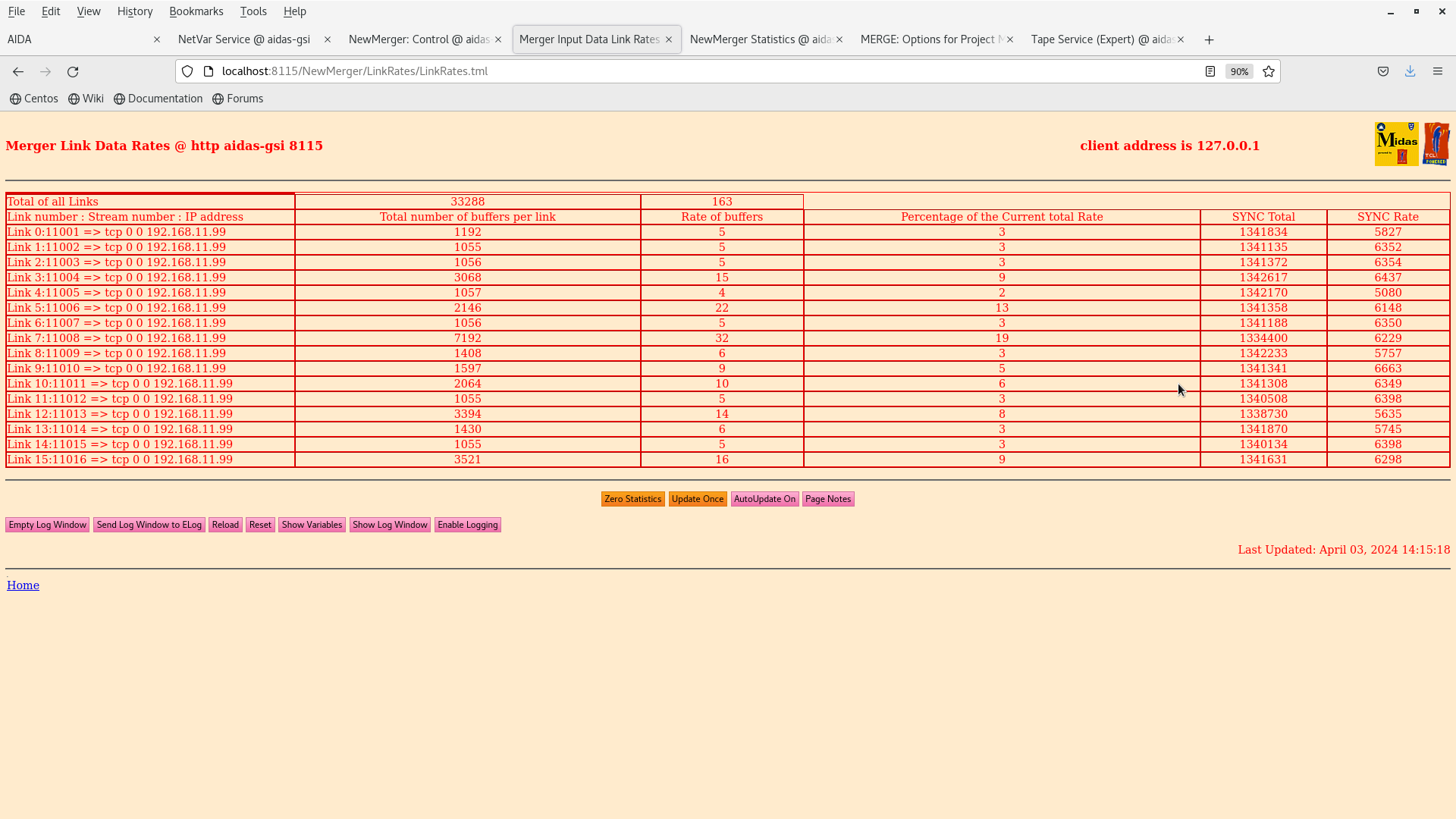

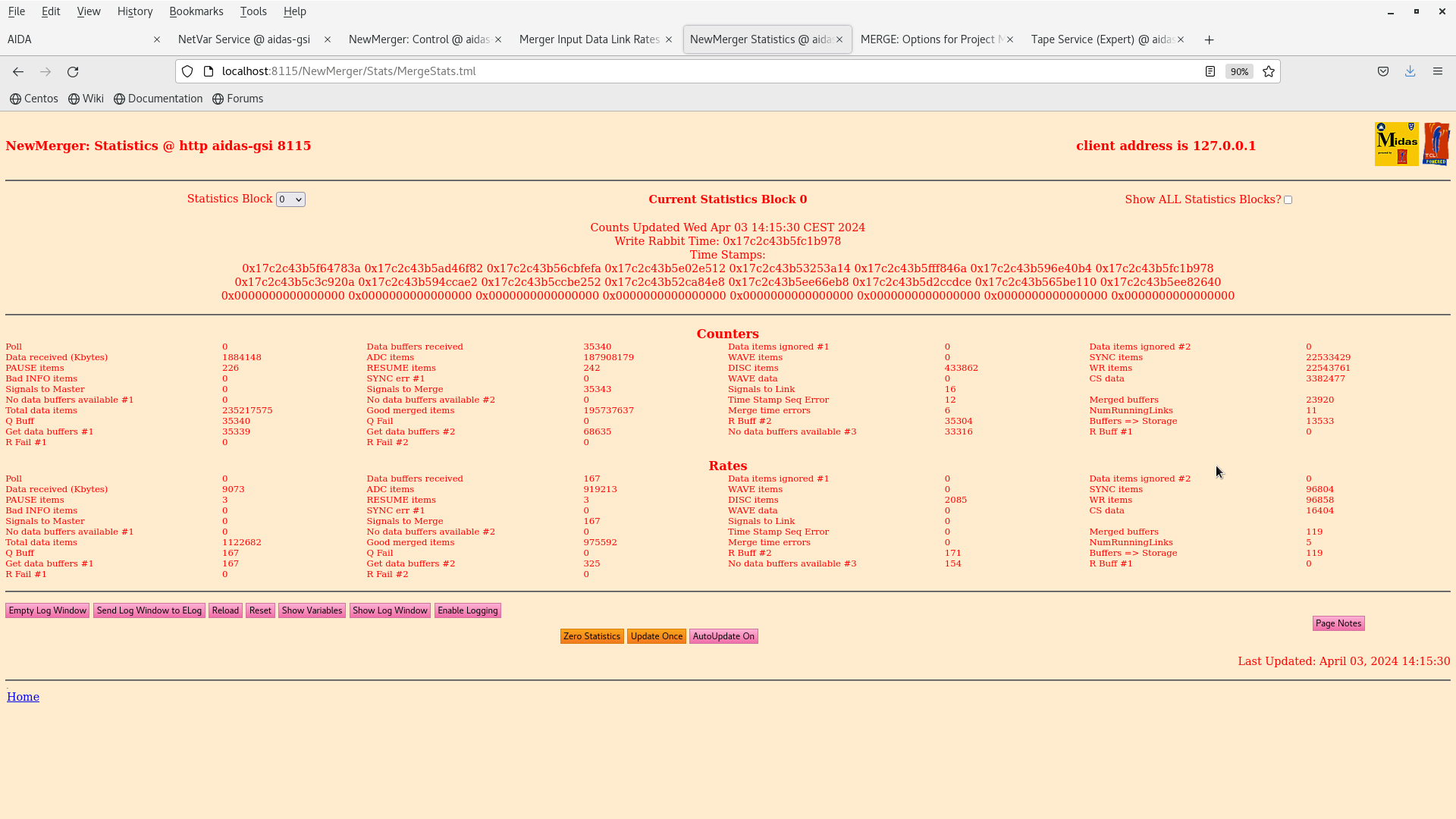

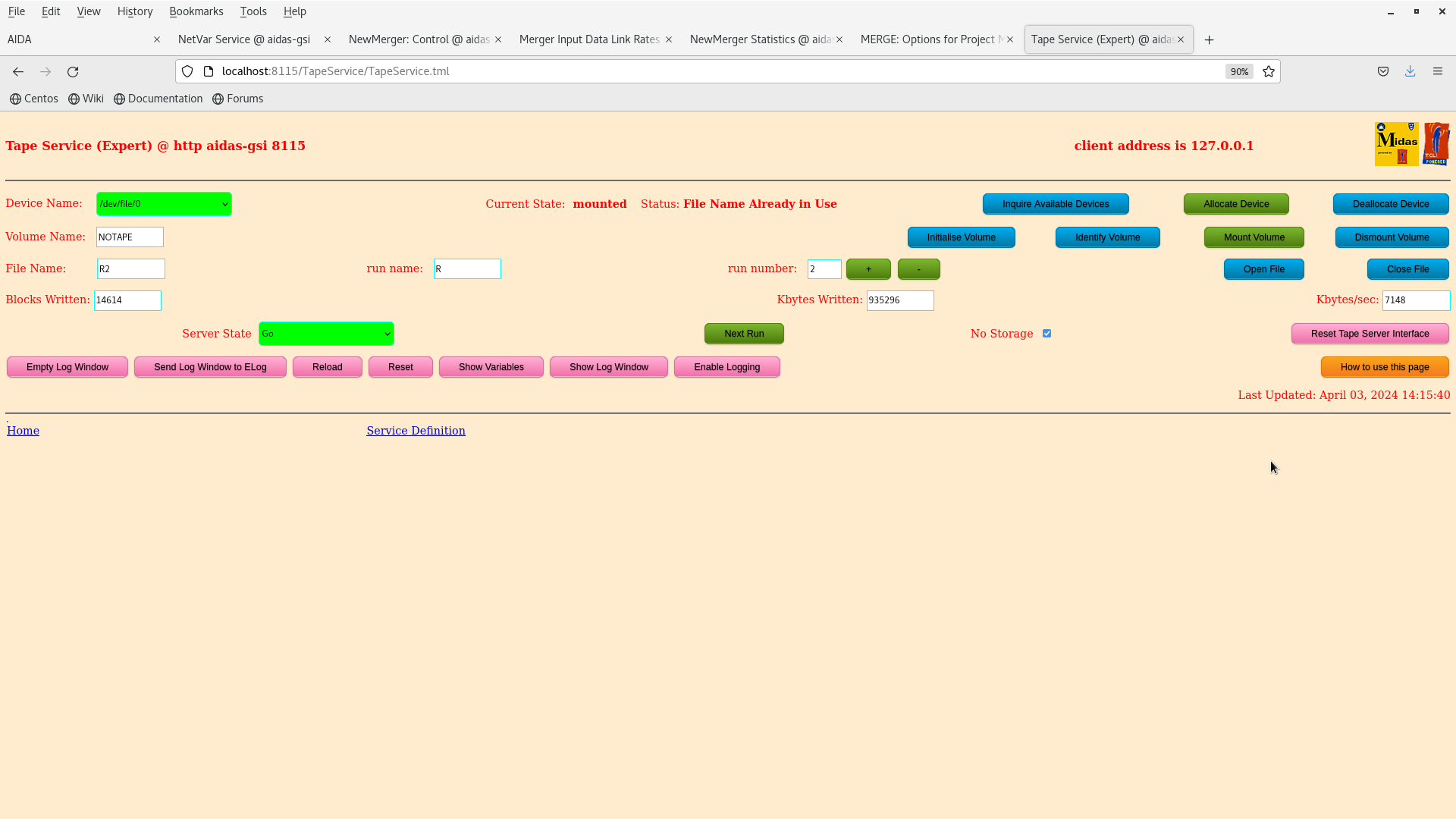

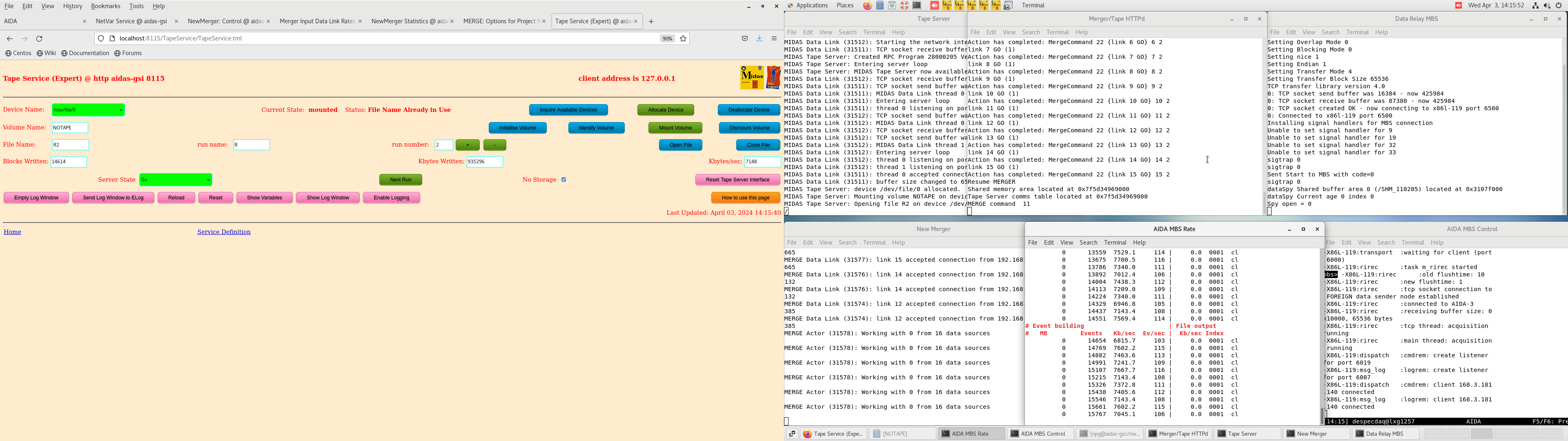

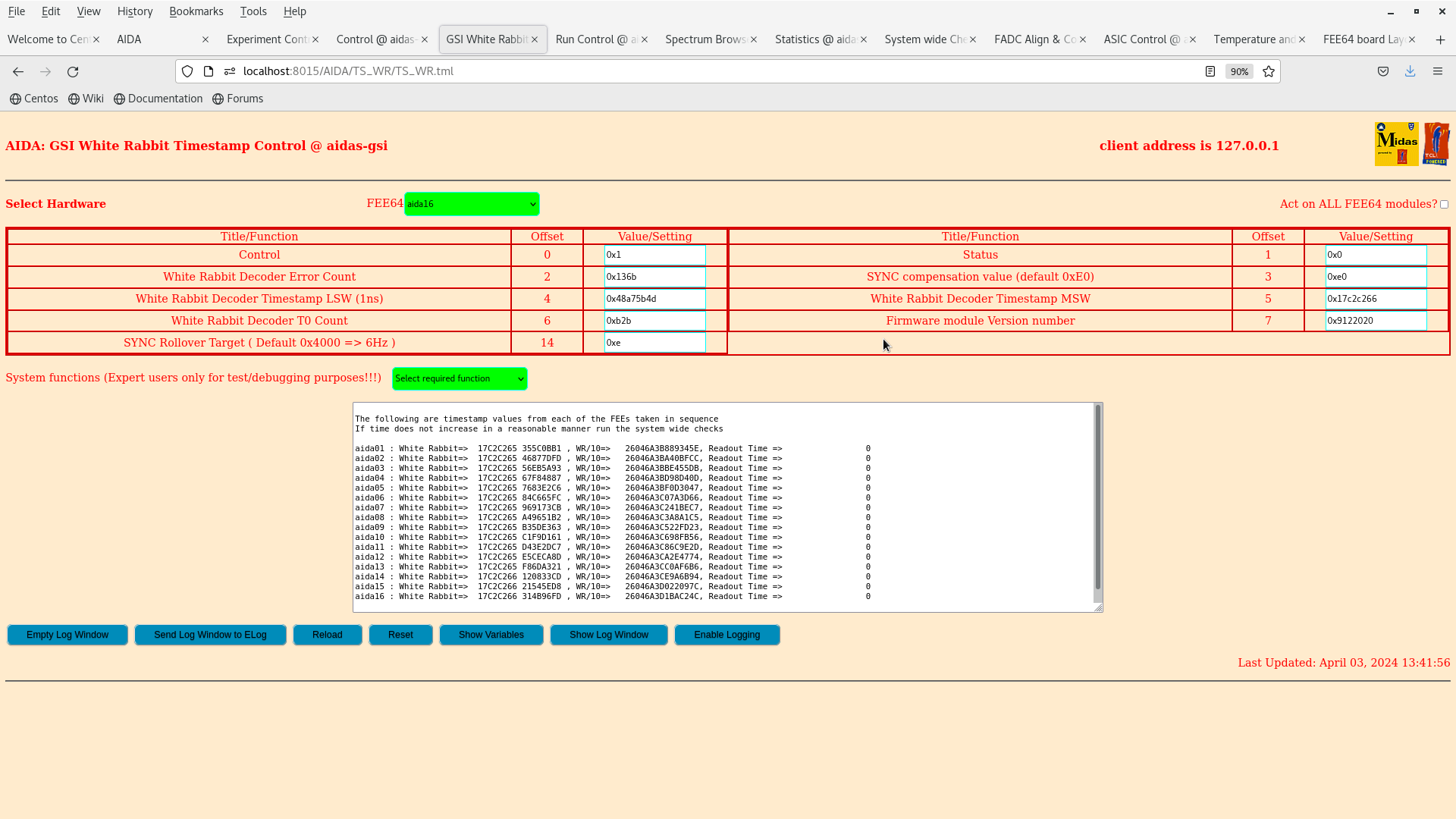

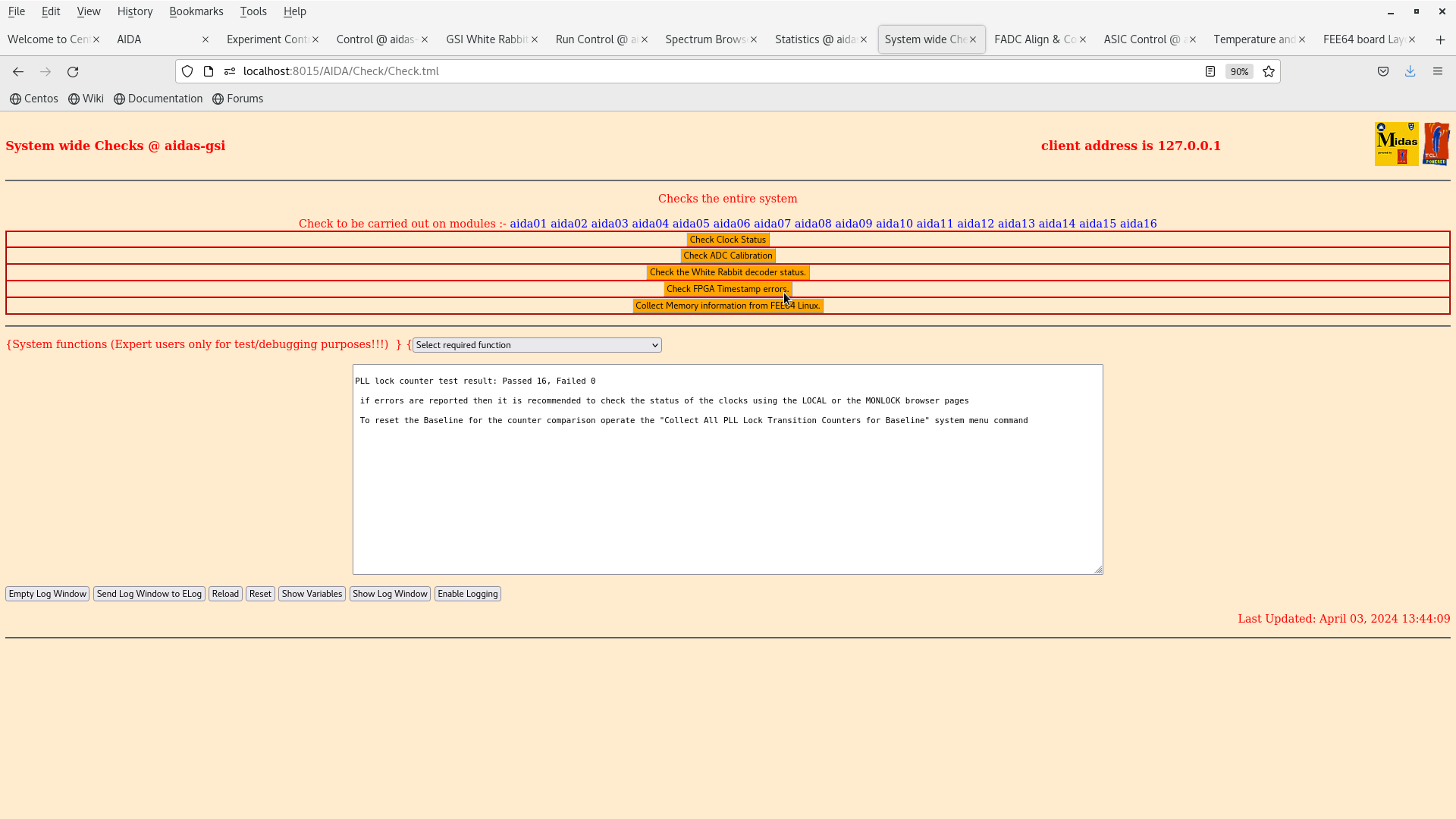

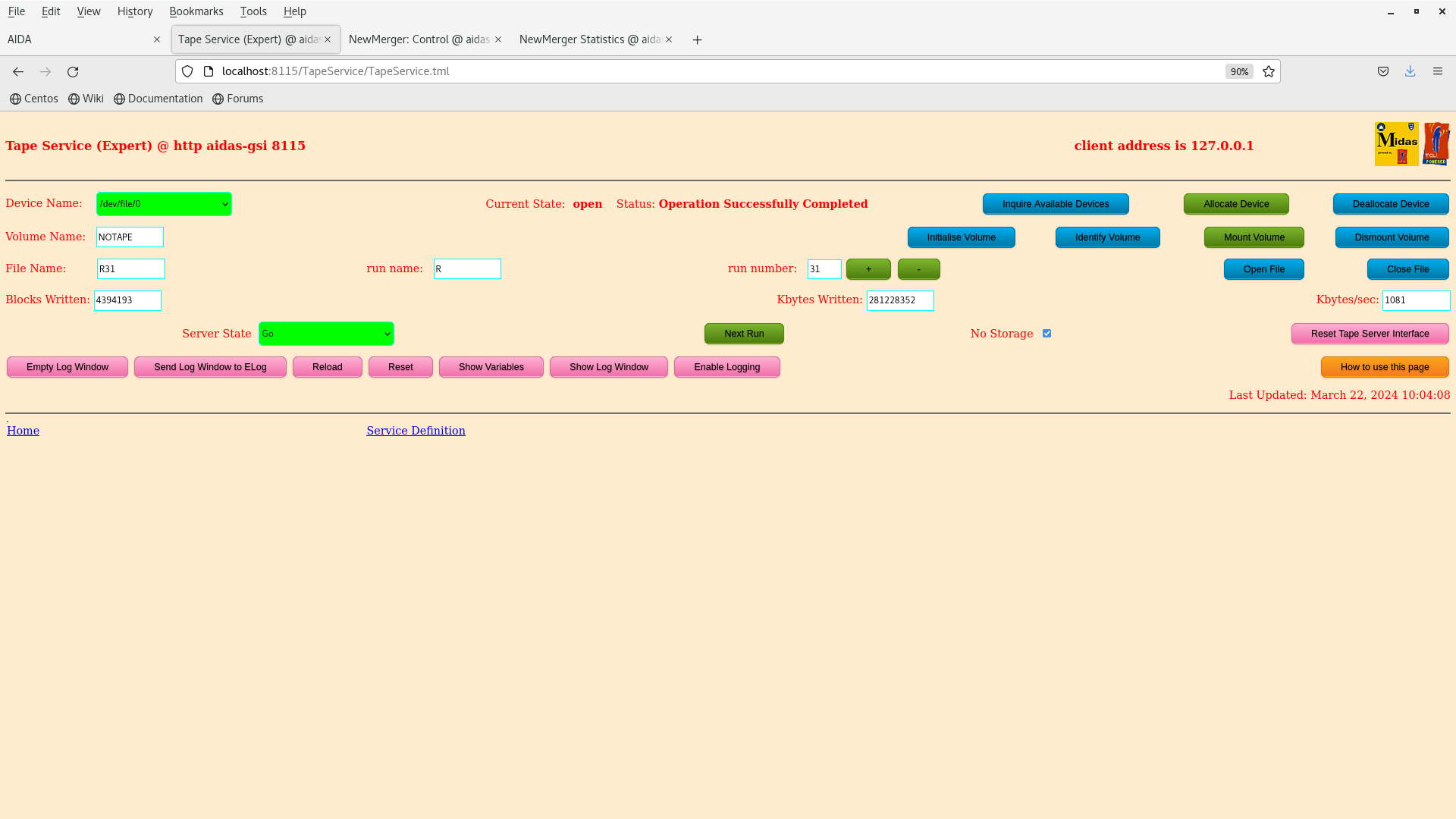

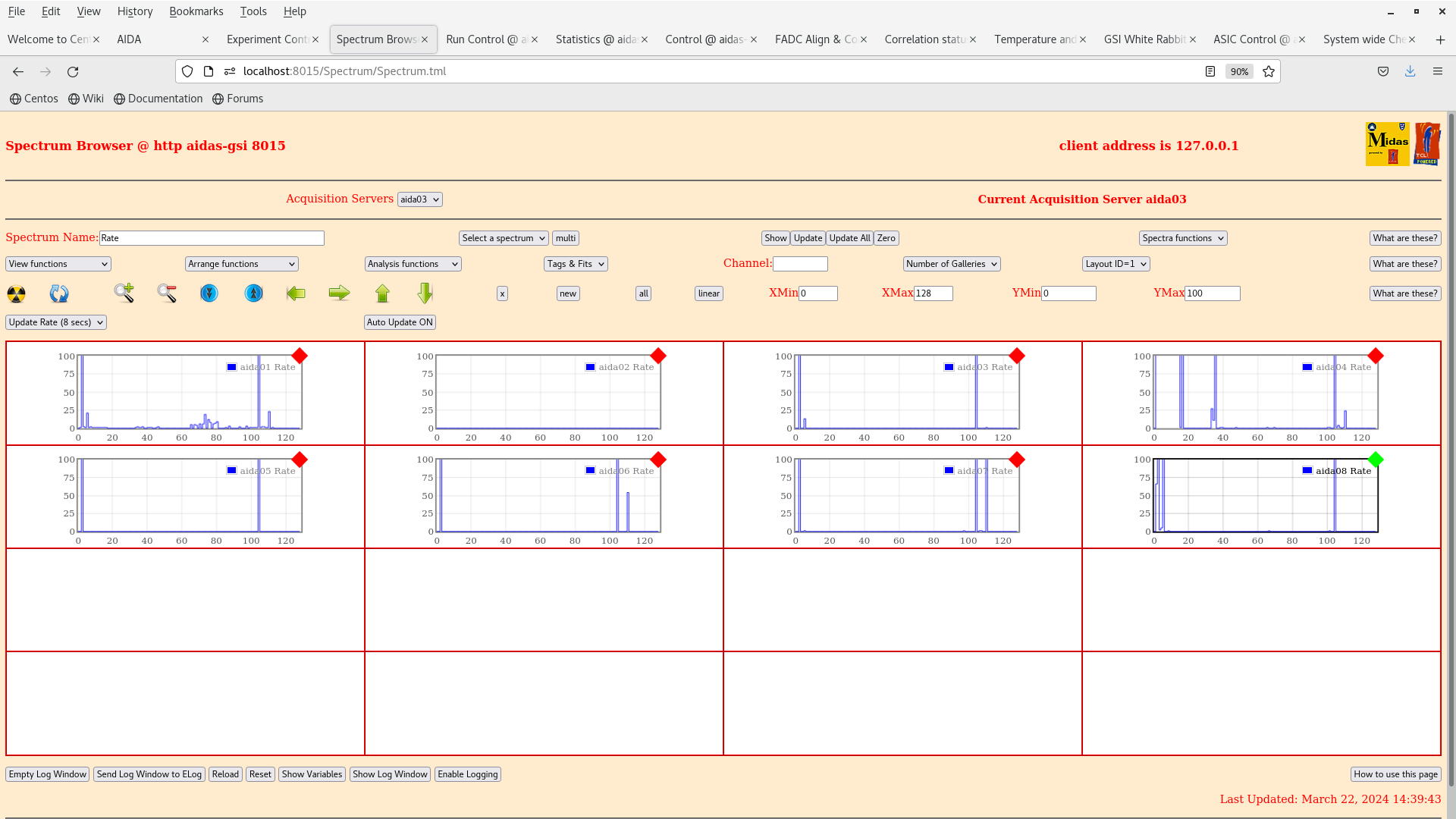

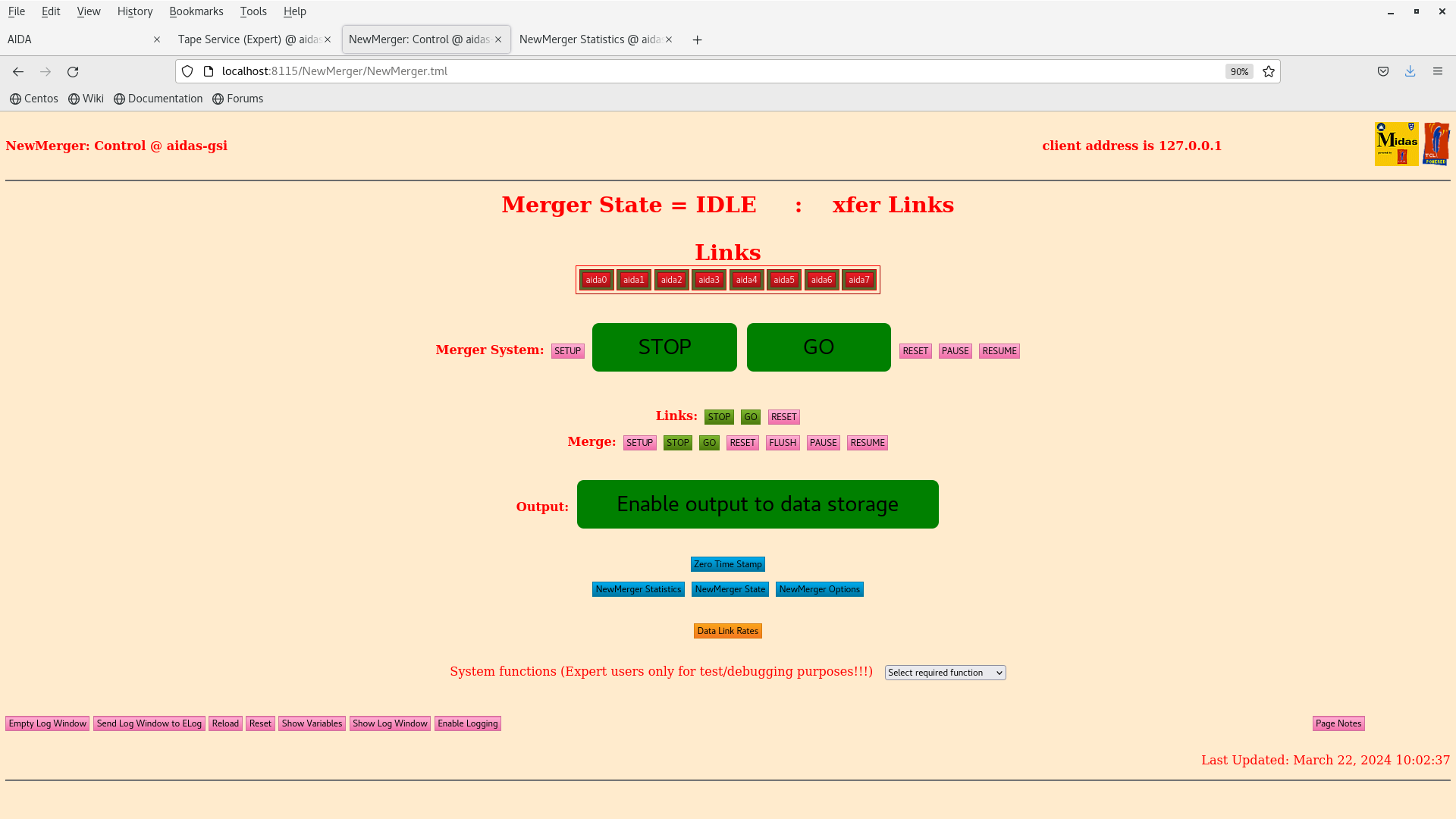

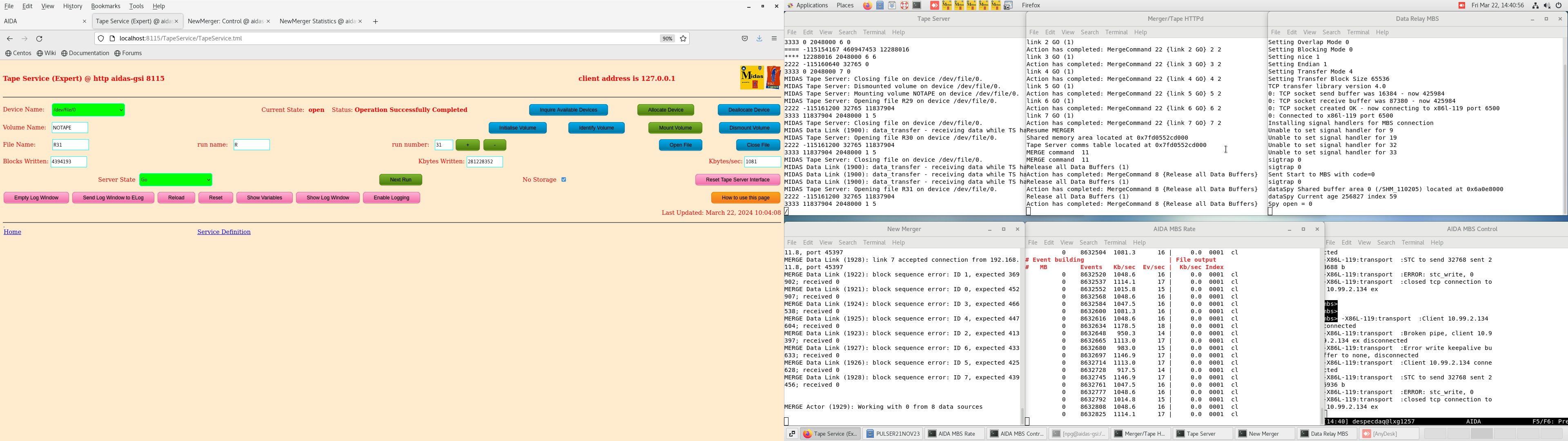

NH | Merger for 16 FEEs |

Changed /MIDAS/Linux/startup/NewMerger

Change parameters -i and -l in master64 to 16 for 16 FEEs

Update NewMerger Options LinksAvailable to 16, LinksInUse to 1%1%1%1%1%1%1%1%1%1%1%1%1%1%1%1%

Fix NetVar RunOptions 1 (was 0)

Restart Merger HTTPd, Tape, Merger, MBS Spy

Reset/Setup/Go

16 Links green and status going, all good?

Bias DSSSDs and turn data transfer on

Merger connected, shows rate and updates... no rate in Tape Server?

.. Oops forget to turn on Output to data storage in merger!

Rate in tape server and to MBS: 7 MB/s

Merger, Tape and MBS working with 16 FEEs |

| Attachment 1: Screenshot_from_2024-04-03_14-15-02.png

|

|

| Attachment 2: Screenshot_from_2024-04-03_14-15-25.png

|

|

| Attachment 3: Screenshot_from_2024-04-03_14-15-36.png

|

|

| Attachment 4: Screenshot_from_2024-04-03_14-15-45.png

|

|

| Attachment 5: Screenshot_from_2024-04-03_14-15-52.png

|

|

|

558

|

Wed Apr 3 12:42:57 2024 |

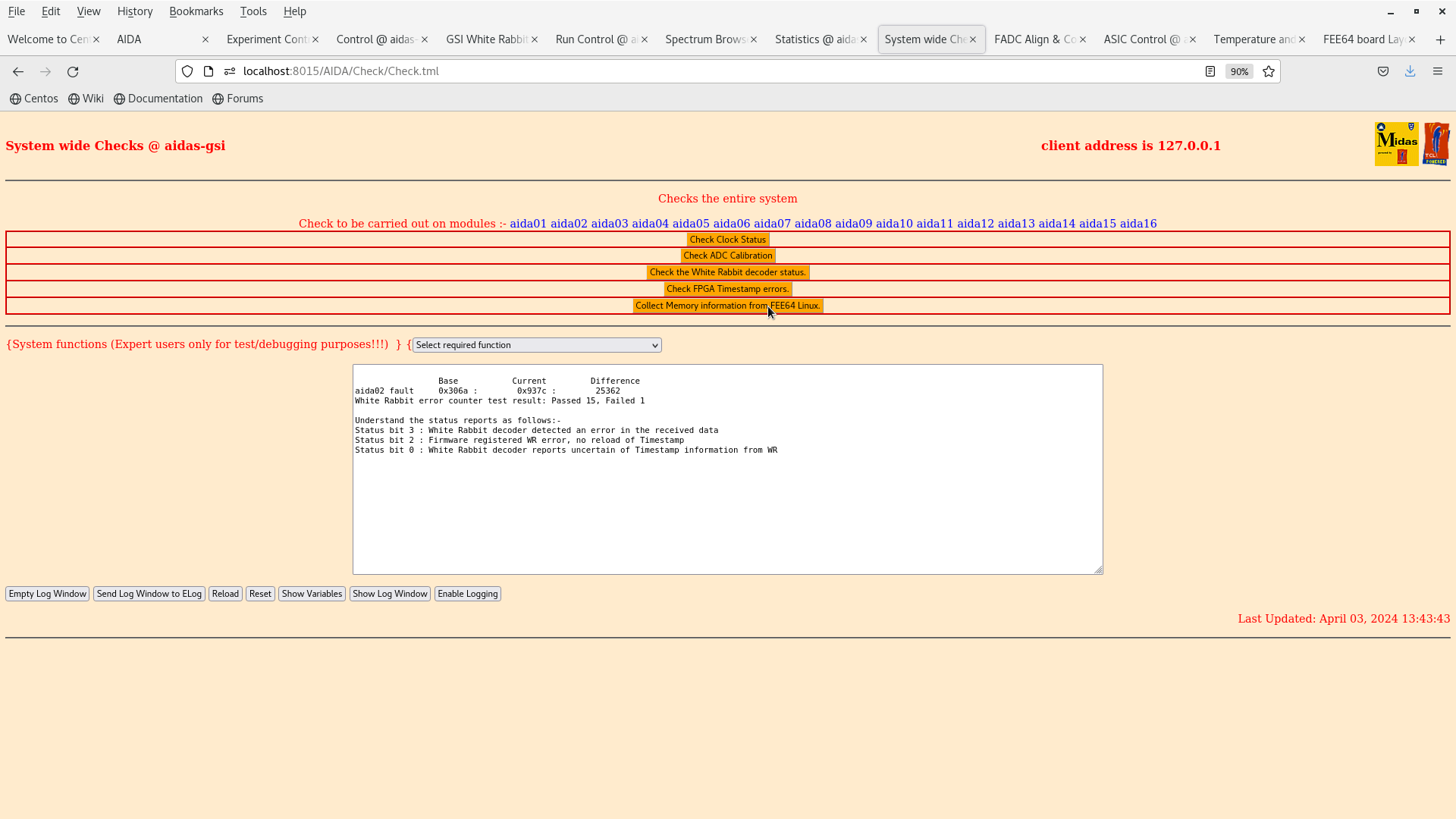

NH | Report aida02 WR errors |

The WR error counter for aida02 seems to consantly rise

Tried reseating cable on both ends, no change

However clock status passed, aida02 has a correct WR timestamp and no FIFO/PLL errors seen

Edit to add: aida02 has the faulty ASIC temperature readout as well, related or coincidence? |

| Attachment 1: Screenshot_from_2024-04-03_13-43-48.png

|

|

| Attachment 2: Screenshot_from_2024-04-03_13-43-38.png

|

|

| Attachment 3: Screenshot_from_2024-04-03_13-43-58.png

|

|

| Attachment 4: Screenshot_from_2024-04-03_13-44-14.png

|

|

| Attachment 5: Screenshot_from_2024-04-03_13-44-36.png

|

|

|

557

|

Wed Apr 3 12:09:47 2024 |

NH | Report - aida06 frequently fails to boot first time (PHY error) |

When booting up AIDA aida06 usually crashes the first time, it fails to get IP from DHCP

After 180 seconds it reboots and seems to connect fine

Log file attached, key part (to me) is this:

27:03:24/14:13:19|Sending DHCP requests .

27:03:24/14:13:21|eth0: XLlTemac: PHY Link carrier lost.

27:03:24/14:13:21|..... timed out!

27:03:24/14:14:33|IP-Config: Reopening network devices...

27:03:24/14:14:33|eth0: XLlTemac: Options: 0x3fa

27:03:24/14:14:34|eth0: XLlTemac: allocating interrupt 19 for dma mode tx.

27:03:24/14:14:34|eth0: XLlTemac: allocating interrupt 18 for dma mode rx.

27:03:24/14:14:34|eth0: XLlTemac: speed set to 1000Mb/s

27:03:24/14:14:36|eth0: XLlTemac: Send Threshold = 24, Receive Threshold = 4

27:03:24/14:14:36|eth0: XLlTemac: Send Wait bound = 254, Receive Wait bound = 254

27:03:24/14:14:36|Sending DHCP requests ......

27:03:24/14:26:16| |

| Attachment 1: ttyUSB15

|

27:03:24/14:12:59|

ISOL Version 1.00 Date 9th January 2017

27:03:24/14:12:59|

Flash base address=FC000000

27:03:24/14:12:59|

Set Flash to ASync Mode

27:03:24/14:12:59|

XST_SUCCESS

27:03:24/14:12:59|

Finished copying zImage to RAM

27:03:24/14:12:59|

27:03:24/14:12:59|

Found 0 errors checking kernel image

27:03:24/14:13:00|VHDL version number 0X03350706

27:03:24/14:13:00|

Based on AIDA Bootloader version number 1.2.0 -- 16th August 2012

27:03:24/14:13:00|

Starting LMK 3200 setup

27:03:24/14:13:00|

27:03:24/14:13:00|

Setting LMK03200 to standard clock settings -- External Clock 23Nov15

27:03:24/14:13:00|

.... SPI Base Address=0x81400000

27:03:24/14:13:00|

clk_control_reg=0x4

27:03:24/14:13:01|Next step is SPIconfig

27:03:24/14:13:01|

Control 32(0x81400000)=0x180

27:03:24/14:13:01|

SlaveSel(0x81400000)=0x3

27:03:24/14:13:01|

Ctrl(0x81400000)=0xE6

27:03:24/14:13:01|

Ctrl(0x81400000)=0x86

27:03:24/14:13:01|SPIconfig done now to set up the LMK3200 registers

27:03:24/14:13:01|LMK #0 : regInit[0]=0x80000000

27:03:24/14:13:01|LMK #0 : regInit[1]=0x10070600

27:03:24/14:13:01|LMK #0 : regInit[2]=0x60601

27:03:24/14:13:01|LMK #0 : regInit[3]=0x60602

27:03:24/14:13:01|LMK #0 : regInit[4]=0x60603

27:03:24/14:13:01|LMK #0 : regInit[5]=0x70624

27:03:24/14:13:01|LMK #0 : regInit[6]=0x70605

27:03:24/14:13:01|LMK #0 : regInit[7]=0x70606

27:03:24/14:13:01|LMK #0 : regInit[8]=0x70627

27:03:24/14:13:01|LMK #0 : regInit[9]=0x10000908

27:03:24/14:13:01|LMK #0 : regInit[10]=0xA0022A09

27:03:24/14:13:01|LMK #0 : regInit[11]=0x82800B

27:03:24/14:13:01|LMK #0 : regInit[12]=0x28C800D

27:03:24/14:13:01|LMK #0 : regInit[13]=0x830020E

27:03:24/14:13:01|LMK #0 : regInit[14]=0xC800180F

27:03:24/14:13:01|

Calibrate completed at 943 counts

27:03:24/14:13:01|

Setting Clock Control =0x0000000B, to set GOE and sync bit

27:03:24/14:13:01|

Ctrl @ SPIstop (0x81400000)=0x186

27:03:24/14:13:01|

Timeout waiting for Lock detect Stage 2 (Zero Delay), PWR_DWN=0x00000004

27:03:24/14:13:01|

27:03:24/14:13:01|

Finished Clock setup LMK03200

27:03:24/14:13:01|

completed LMK 3200 setup

27:03:24/14:13:02|

Loaded all four ASICs with default settings

27:03:24/14:13:02|

Setting the ADCs into calibration mode

27:03:24/14:13:02|

27:03:24/14:13:02|

Control 32(0x81400400)=0x180

27:03:24/14:13:02|

SlaveSel(0x81400400)=0xFF

27:03:24/14:13:02|

Ctrl(0x81400400)=0xE6

27:03:24/14:13:02|

Ctrl(0x81400400)=0x86

27:03:24/14:13:02|

Init : Config of AD9252 SPI ok

27:03:24/14:13:02|

27:03:24/14:13:02|

Ctrl @ SPIstop (0x81400400)=0x186ADCs initialised

27:03:24/14:13:02|

Cal not completed

27:03:24/14:13:02|

ADC calibrate failed

27:03:24/14:13:02|

Jumping to kernel simpleboot...

27:03:24/14:13:02|

27:03:24/14:13:02|

zImage starting: loaded at 0x00a00000 (sp: 0x00bc4eb0)

27:03:24/14:13:02|

Allocating 0x3b78cc bytes for kernel ...

27:03:24/14:13:02|

gunzipping (0x00000000 <- 0x00a0f000:0x00bc380e)...done 0x39604c bytes

27:03:24/14:13:05|

27:03:24/14:13:05|

Linux/PowerPC load: console=ttyS0 root=/dev/nfs ip=on rw mem=112M

27:03:24/14:13:12|

Finalizing device tree... flat tree at 0xbd1300

27:03:24/14:13:12|

Probing IIC bus for MAC... MAC address = 0xd8 0x80 0x39 0x41 0xee 0x71

27:03:24/14:13:12|Using Xilinx Virtex440 machine description

27:03:24/14:13:12|Linux version 2.6.31 (nf@nnlxb.dl.ac.uk) (gcc version 4.2.2) #34 PREEMPT Tue Nov 15 15:57:04 GMT 2011

27:03:24/14:13:12|Zone PFN ranges:

27:03:24/14:13:12| DMA 0x00000000 -> 0x00007000

27:03:24/14:13:12| Normal 0x00007000 -> 0x00007000

27:03:24/14:13:12|Movable zone start PFN for each node

27:03:24/14:13:13|early_node_map[1] active PFN ranges

27:03:24/14:13:13| 0: 0x00000000 -> 0x00007000

27:03:24/14:13:13|MMU: Allocated 1088 bytes of context maps for 255 contexts

27:03:24/14:13:13|Built 1 zonelists in Zone order, mobility grouping on. Total pages: 28448

27:03:24/14:13:13|Kernel command line: console=ttyS0 root=/dev/nfs ip=on rw mem=112M

27:03:24/14:13:13|PID hash table entries: 512 (order: 9, 2048 bytes)

27:03:24/14:13:13|Dentry cache hash table entries: 16384 (order: 4, 65536 bytes)

27:03:24/14:13:13|Inode-cache hash table entries: 8192 (order: 3, 32768 bytes)

27:03:24/14:13:13|Memory: 109680k/114688k available (3500k kernel code, 4852k reserved, 144k data, 130k bss, 168k init)

27:03:24/14:13:13|Kernel virtual memory layout:

27:03:24/14:13:13| * 0xffffe000..0xfffff000 : fixmap

27:03:24/14:13:13| * 0xfde00000..0xfe000000 : consistent mem

27:03:24/14:13:13| * 0xfde00000..0xfde00000 : early ioremap

27:03:24/14:13:13| * 0xd1000000..0xfde00000 : vmalloc & ioremap

27:03:24/14:13:13|NR_IRQS:512

27:03:24/14:13:13|clocksource: timebase mult[a00000] shift[22] registered

27:03:24/14:13:13|Console: colour dummy device 80x25

27:03:24/14:13:13|Mount-cache hash table entries: 512

27:03:24/14:13:13|NET: Registered protocol family 16

27:03:24/14:13:14|PCI: Probing PCI hardware

27:03:24/14:13:14|bio: create slab <bio-0> at 0

27:03:24/14:13:14|NET: Registered protocol family 2

27:03:24/14:13:14|IP route cache hash table entries: 1024 (order: 0, 4096 bytes)

27:03:24/14:13:14|TCP established hash table entries: 4096 (order: 3, 32768 bytes)

27:03:24/14:13:14|TCP bind hash table entries: 4096 (order: 2, 16384 bytes)

27:03:24/14:13:14|TCP: Hash tables configured (established 4096 bind 4096)

27:03:24/14:13:14|TCP reno registered

27:03:24/14:13:14|NET: Registered protocol family 1

27:03:24/14:13:14|ROMFS MTD (C) 2007 Red Hat, Inc.

27:03:24/14:13:14|msgmni has been set to 214

27:03:24/14:13:14|io scheduler noop registered

27:03:24/14:13:14|io scheduler anticipatory registered

27:03:24/14:13:14|io scheduler deadline registered

27:03:24/14:13:14|io scheduler cfq registered (default)

27:03:24/14:13:14|Serial: 8250/16550 driver, 4 ports, IRQ sharing disabled

27:03:24/14:13:14|83e00000.serial: ttyS0 at MMIO 0x83e01003 (irq = 16) is a 16550

27:03:24/14:13:14|console [ttyS0] enabled

27:03:24/14:13:14|brd: module loaded

27:03:24/14:13:14|loop: module loaded

27:03:24/14:13:14|Device Tree Probing 'ethernet'

27:03:24/14:13:14|xilinx_lltemac 81c00000.ethernet: MAC address is now d8:80:39:41:ee:71

27:03:24/14:13:14|xilinx_lltemac 81c00000.ethernet: XLlTemac: using DMA mode.

27:03:24/14:13:15|XLlTemac: DCR address: 0x80

27:03:24/14:13:15|XLlTemac: buffer descriptor size: 32768 (0x8000)

27:03:24/14:13:15|XLlTemac: Allocating DMA descriptors with kmalloc

27:03:24/14:13:15|XLlTemac: (buffer_descriptor_init) phy: 0x6938000, virt: 0xc6938000, size: 0x8000

27:03:24/14:13:15|XTemac: PHY detected at address 7.

27:03:24/14:13:15|xilinx_lltemac 81c00000.ethernet: eth0: Xilinx TEMAC at 0x81C00000 mapped to 0xD1024000, irq=17

27:03:24/14:13:15|fc000000.flash: Found 1 x16 devices at 0x0 in 16-bit bank

27:03:24/14:13:15| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:13:15| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:13:15| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:13:15| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:13:15| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:13:15| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:13:15|Using buffer write method

27:03:24/14:13:15|cfi_cmdset_0001: Erase suspend on write enabled

27:03:24/14:13:15|cmdlinepart partition parsing not available

27:03:24/14:13:15|RedBoot partition parsing not available

27:03:24/14:13:15|Creating 5 MTD partitions on "fc000000.flash":

27:03:24/14:13:15|0x000000000000-0x000000500000 : "golden_firmware"

27:03:24/14:13:16|0x000000500000-0x000000800000 : "golden_kernel"

27:03:24/14:13:16|0x000000800000-0x000000d00000 : "user_firmware"

27:03:24/14:13:16|0x000000d00000-0x000000fe0000 : "user_kernel"

27:03:24/14:13:16|0x000000fe0000-0x000001000000 : "env_variables"

27:03:24/14:13:16|xilinx-xps-spi 81400400.hd-xps-spi: at 0x81400400 mapped to 0xD1028400, irq=20

27:03:24/14:13:16|SPI: XIlinx spi: bus number now 32766

27:03:24/14:13:16|xilinx-xps-spi 81400000.xps-spi: at 0x81400000 mapped to 0xD102C000, irq=21

27:03:24/14:13:16|SPI: XIlinx spi: bus number now 32765

27:03:24/14:13:16|mice: PS/2 mouse device common for all mice

27:03:24/14:13:16|Device Tree Probing 'i2c'

27:03:24/14:13:16| #0 at 0x81600000 mapped to 0xD1030000, irq=22

27:03:24/14:13:16|at24 0-0050: 1024 byte 24c08 EEPROM (writable)

27:03:24/14:13:16|TCP cubic registered

27:03:24/14:13:16|NET: Registered protocol family 17

27:03:24/14:13:16|RPC: Registered udp transport module.

27:03:24/14:13:16|RPC: Registered tcp transport module.

27:03:24/14:13:16|eth0: XLlTemac: Options: 0x3fa

27:03:24/14:13:17|eth0: XLlTemac: allocating interrupt 19 for dma mode tx.

27:03:24/14:13:17|eth0: XLlTemac: allocating interrupt 18 for dma mode rx.

27:03:24/14:13:17|eth0: XLlTemac: speed set to 1000Mb/s

27:03:24/14:13:19|eth0: XLlTemac: Send Threshold = 24, Receive Threshold = 4

27:03:24/14:13:19|eth0: XLlTemac: Send Wait bound = 254, Receive Wait bound = 254

27:03:24/14:13:19|Sending DHCP requests .

27:03:24/14:13:21|eth0: XLlTemac: PHY Link carrier lost.

27:03:24/14:13:21|..... timed out!

27:03:24/14:14:33|IP-Config: Reopening network devices...

27:03:24/14:14:33|eth0: XLlTemac: Options: 0x3fa

27:03:24/14:14:34|eth0: XLlTemac: allocating interrupt 19 for dma mode tx.

27:03:24/14:14:34|eth0: XLlTemac: allocating interrupt 18 for dma mode rx.

27:03:24/14:14:34|eth0: XLlTemac: speed set to 1000Mb/s

27:03:24/14:14:36|eth0: XLlTemac: Send Threshold = 24, Receive Threshold = 4

27:03:24/14:14:36|eth0: XLlTemac: Send Wait bound = 254, Receive Wait bound = 254

27:03:24/14:14:36|Sending DHCP requests ......

27:03:24/14:26:16|

ISOL Version 1.00 Date 9th January 2017

27:03:24/14:26:16|

Flash base address=FC000000

27:03:24/14:26:16|

Set Flash to ASync Mode

27:03:24/14:26:16|

XST_SUCCESS

27:03:24/14:26:16|

Finished copying zImage to RAM

27:03:24/14:26:17|

27:03:24/14:26:17|

Found 0 errors checking kernel image

27:03:24/14:26:18|VHDL version number 0X03350706

27:03:24/14:26:18|

Based on AIDA Bootloader version number 1.2.0 -- 16th August 2012

27:03:24/14:26:18|

Starting LMK 3200 setup

27:03:24/14:26:18|

27:03:24/14:26:18|

Setting LMK03200 to standard clock settings -- External Clock 23Nov15

27:03:24/14:26:18|

.... SPI Base Address=0x81400000

27:03:24/14:26:18|

clk_control_reg=0x4

27:03:24/14:26:18|Next step is SPIconfig

27:03:24/14:26:18|

Control 32(0x81400000)=0x180

27:03:24/14:26:18|

SlaveSel(0x81400000)=0x3

27:03:24/14:26:18|

Ctrl(0x81400000)=0xE6

27:03:24/14:26:18|

Ctrl(0x81400000)=0x86

27:03:24/14:26:18|SPIconfig done now to set up the LMK3200 registers

27:03:24/14:26:18|LMK #0 : regInit[0]=0x80000000

27:03:24/14:26:18|LMK #0 : regInit[1]=0x10070600

27:03:24/14:26:18|LMK #0 : regInit[2]=0x60601

27:03:24/14:26:19|LMK #0 : regInit[3]=0x60602

27:03:24/14:26:19|LMK #0 : regInit[4]=0x60603

27:03:24/14:26:19|LMK #0 : regInit[5]=0x70624

27:03:24/14:26:19|LMK #0 : regInit[6]=0x70605

27:03:24/14:26:19|LMK #0 : regInit[7]=0x70606

27:03:24/14:26:19|LMK #0 : regInit[8]=0x70627

27:03:24/14:26:19|LMK #0 : regInit[9]=0x10000908

27:03:24/14:26:19|LMK #0 : regInit[10]=0xA0022A09

27:03:24/14:26:19|LMK #0 : regInit[11]=0x82800B

27:03:24/14:26:19|LMK #0 : regInit[12]=0x28C800D

27:03:24/14:26:19|LMK #0 : regInit[13]=0x830020E

27:03:24/14:26:19|LMK #0 : regInit[14]=0xC800180F

27:03:24/14:26:19|

Calibrate completed at 943 counts

27:03:24/14:26:19|

Setting Clock Control =0x0000000B, to set GOE and sync bit

27:03:24/14:26:19|

Ctrl @ SPIstop (0x81400000)=0x186

27:03:24/14:26:19|

Timeout waiting for Lock detect Stage 2 (Zero Delay), PWR_DWN=0x00000004

27:03:24/14:26:19|

27:03:24/14:26:19|

Finished Clock setup LMK03200

27:03:24/14:26:19|

completed LMK 3200 setup

27:03:24/14:26:19|

Loaded all four ASICs with default settings

27:03:24/14:26:19|

Setting the ADCs into calibration mode

27:03:24/14:26:19|

27:03:24/14:26:19|

Control 32(0x81400400)=0x180

27:03:24/14:26:19|

SlaveSel(0x81400400)=0xFF

27:03:24/14:26:19|

Ctrl(0x81400400)=0xE6

27:03:24/14:26:19|

Ctrl(0x81400400)=0x86

27:03:24/14:26:19|

Init : Config of AD9252 SPI ok

27:03:24/14:26:19|

27:03:24/14:26:19|

Ctrl @ SPIstop (0x81400400)=0x186ADCs initialised

27:03:24/14:26:20|

ADCs calibrated

27:03:24/14:26:20|

27:03:24/14:26:20|

Control 32(0x81400400)=0x186

27:03:24/14:26:20|

SlaveSel(0x81400400)=0xFF

27:03:24/14:26:20|

Ctrl(0x81400400)=0xE6

27:03:24/14:26:20|

Ctrl(0x81400400)=0x86Config of AD9252 SPI ok

27:03:24/14:26:20|

27:03:24/14:26:20|

Ctrl @ SPIstop (0x81400400)=0x186Jumping to kernel simpleboot...

27:03:24/14:26:20|

27:03:24/14:26:20|

zImage starting: loaded at 0x00a00000 (sp: 0x00bc4eb0)

27:03:24/14:26:20|

Allocating 0x3b78cc bytes for kernel ...

27:03:24/14:26:20|

gunzipping (0x00000000 <- 0x00a0f000:0x00bc380e)...done 0x39604c bytes

27:03:24/14:26:23|

27:03:24/14:26:23|

Linux/PowerPC load: console=ttyS0 root=/dev/nfs ip=on rw mem=112M

27:03:24/14:26:29|

Finalizing device tree... flat tree at 0xbd1300

27:03:24/14:26:29|

Probing IIC bus for MAC... MAC address = 0xd8 0x80 0x39 0x41 0xee 0x71

27:03:24/14:26:30|Using Xilinx Virtex440 machine description

27:03:24/14:26:30|Linux version 2.6.31 (nf@nnlxb.dl.ac.uk) (gcc version 4.2.2) #34 PREEMPT Tue Nov 15 15:57:04 GMT 2011

27:03:24/14:26:30|Zone PFN ranges:

27:03:24/14:26:30| DMA 0x00000000 -> 0x00007000

27:03:24/14:26:30| Normal 0x00007000 -> 0x00007000

27:03:24/14:26:30|Movable zone start PFN for each node

27:03:24/14:26:30|early_node_map[1] active PFN ranges

27:03:24/14:26:30| 0: 0x00000000 -> 0x00007000

27:03:24/14:26:30|MMU: Allocated 1088 bytes of context maps for 255 contexts

27:03:24/14:26:30|Built 1 zonelists in Zone order, mobility grouping on. Total pages: 28448

27:03:24/14:26:31|Kernel command line: console=ttyS0 root=/dev/nfs ip=on rw mem=112M

27:03:24/14:26:31|PID hash table entries: 512 (order: 9, 2048 bytes)

27:03:24/14:26:31|Dentry cache hash table entries: 16384 (order: 4, 65536 bytes)

27:03:24/14:26:31|Inode-cache hash table entries: 8192 (order: 3, 32768 bytes)

27:03:24/14:26:31|Memory: 109680k/114688k available (3500k kernel code, 4852k reserved, 144k data, 130k bss, 168k init)

27:03:24/14:26:31|Kernel virtual memory layout:

27:03:24/14:26:31| * 0xffffe000..0xfffff000 : fixmap

27:03:24/14:26:31| * 0xfde00000..0xfe000000 : consistent mem

27:03:24/14:26:31| * 0xfde00000..0xfde00000 : early ioremap

27:03:24/14:26:31| * 0xd1000000..0xfde00000 : vmalloc & ioremap

27:03:24/14:26:31|NR_IRQS:512

27:03:24/14:26:31|clocksource: timebase mult[a00000] shift[22] registered

27:03:24/14:26:31|Console: colour dummy device 80x25

27:03:24/14:26:31|Mount-cache hash table entries: 512

27:03:24/14:26:31|NET: Registered protocol family 16

27:03:24/14:26:31|PCI: Probing PCI hardware

27:03:24/14:26:31|bio: create slab <bio-0> at 0

27:03:24/14:26:31|NET: Registered protocol family 2

27:03:24/14:26:31|IP route cache hash table entries: 1024 (order: 0, 4096 bytes)

27:03:24/14:26:31|TCP established hash table entries: 4096 (order: 3, 32768 bytes)

27:03:24/14:26:32|TCP bind hash table entries: 4096 (order: 2, 16384 bytes)

27:03:24/14:26:32|TCP: Hash tables configured (established 4096 bind 4096)

27:03:24/14:26:32|TCP reno registered

27:03:24/14:26:32|NET: Registered protocol family 1

27:03:24/14:26:32|ROMFS MTD (C) 2007 Red Hat, Inc.

27:03:24/14:26:32|msgmni has been set to 214

27:03:24/14:26:32|io scheduler noop registered

27:03:24/14:26:32|io scheduler anticipatory registered

27:03:24/14:26:32|io scheduler deadline registered

27:03:24/14:26:32|io scheduler cfq registered (default)

27:03:24/14:26:32|Serial: 8250/16550 driver, 4 ports, IRQ sharing disabled

27:03:24/14:26:32|83e00000.serial: ttyS0 at MMIO 0x83e01003 (irq = 16) is a 16550

27:03:24/14:26:32|console [ttyS0] enabled

27:03:24/14:26:32|brd: module loaded

27:03:24/14:26:32|loop: module loaded

27:03:24/14:26:32|Device Tree Probing 'ethernet'

27:03:24/14:26:32|xilinx_lltemac 81c00000.ethernet: MAC address is now d8:80:39:41:ee:71

27:03:24/14:26:32|xilinx_lltemac 81c00000.ethernet: XLlTemac: using DMA mode.

27:03:24/14:26:32|XLlTemac: DCR address: 0x80

27:03:24/14:26:32|XLlTemac: buffer descriptor size: 32768 (0x8000)

27:03:24/14:26:32|XLlTemac: Allocating DMA descriptors with kmalloc

27:03:24/14:26:32|XLlTemac: (buffer_descriptor_init) phy: 0x6938000, virt: 0xc6938000, size: 0x8000

27:03:24/14:26:33|XTemac: PHY detected at address 7.

27:03:24/14:26:33|xilinx_lltemac 81c00000.ethernet: eth0: Xilinx TEMAC at 0x81C00000 mapped to 0xD1024000, irq=17

27:03:24/14:26:33|fc000000.flash: Found 1 x16 devices at 0x0 in 16-bit bank

27:03:24/14:26:33| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:26:33| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:26:33| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:26:33| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:26:33| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:26:33| Intel/Sharp Extended Query Table at 0x010A

27:03:24/14:26:33|Using buffer write method

27:03:24/14:26:33|cfi_cmdset_0001: Erase suspend on write enabled

27:03:24/14:26:33|cmdlinepart partition parsing not available

27:03:24/14:26:33|RedBoot partition parsing not available

27:03:24/14:26:33|Creating 5 MTD partitions on "fc000000.flash":

27:03:24/14:26:33|0x000000000000-0x000000500000 : "golden_firmware"

27:03:24/14:26:33|0x000000500000-0x000000800000 : "golden_kernel"

... 1850 more lines ...

|

|

556

|

Tue Apr 2 18:37:21 2024 |

TD | S505 ADC offsets |

S505 ADC offsets using pulser walkthrough data from data file R1

ch = channel + ( module * 64 ) + ( range * 2048 )

adc_data( ch ) = INT( RSHIFT( ABS( adc_data( ch ) - 32768 ), 3 ) - offset( ch ) + 0.5 ) |

| Attachment 1: S505_calibration_data.txt

|

$variables

offset( 0) = 28.32

offset( 1) = 17.71

offset( 2) = -9.75

offset( 3) = -5.24

offset( 4) = -10.84

offset( 5) = 0.13

offset( 6) = 28.59

offset( 7) = 28.54

offset( 8) = 0.83

offset( 9) = -12.15

offset( 10) = 29.36

offset( 11) = -50.47

offset( 12) = 10.03

offset( 13) = -26.90

offset( 14) = 12.49

offset( 15) = 10.57

offset( 16) = 9.29

offset( 17) = 1.09

offset( 18) = 21.86

offset( 19) = -0.32

offset( 20) = 22.59

offset( 21) = -9999.99

offset( 22) = -20.22

offset( 23) = 6.61

offset( 24) = -8.80

offset( 25) = -1.15

offset( 26) = 13.08

offset( 27) = -9.03

offset( 28) = -2.67

offset( 29) = -9.42

offset( 30) = 8.07

offset( 31) = 19.01

offset( 32) = 6.86

offset( 33) = 15.16

offset( 34) = -3.89

offset( 35) = -18.80

offset( 36) = 17.79

offset( 37) = 16.45

offset( 38) = -0.74

offset( 39) = 0.69

offset( 40) = -14.59

offset( 41) = -10.02

offset( 42) = 11.38

offset( 43) = -2.57

offset( 44) = 15.48

offset( 45) = 14.57

offset( 46) = 2.95

offset( 47) = 30.70

offset( 48) = -12.55

offset( 49) = -15.61

offset( 50) = -6.61

offset( 51) = -7.10

offset( 52) = -33.20

offset( 53) = 21.42

offset( 54) = -4.07

offset( 55) = -18.23

offset( 56) = 8.83

offset( 57) = -22.74

offset( 58) = 11.47

offset( 59) = 10.67

offset( 60) = -28.65

offset( 61) = 15.29

offset( 62) = 5.76

offset( 63) = -11.57

offset( 64) = 1.95