| ID |

Date |

Author |

Subject |

|

254

|

Tue Apr 20 19:00:00 2021 |

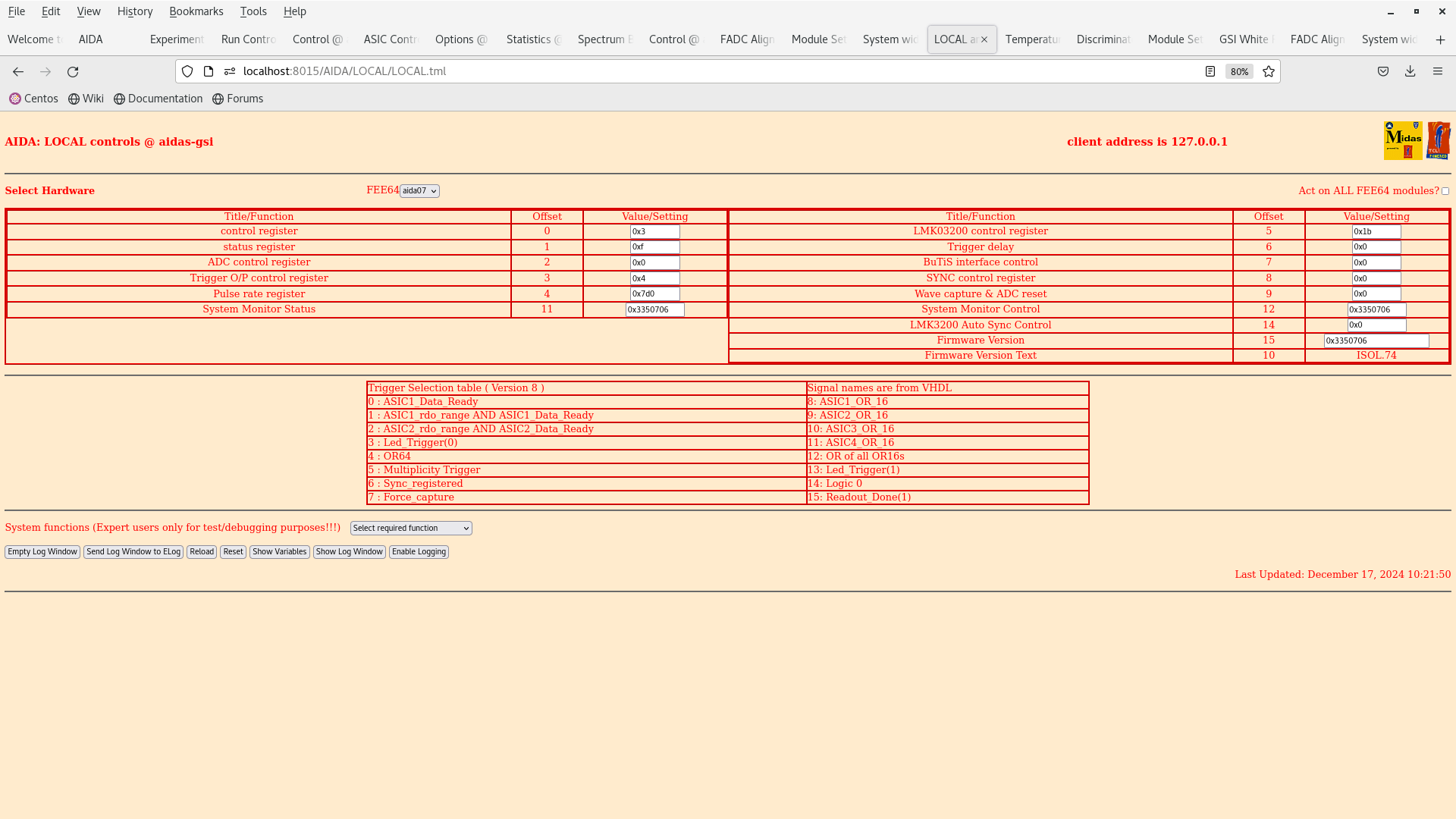

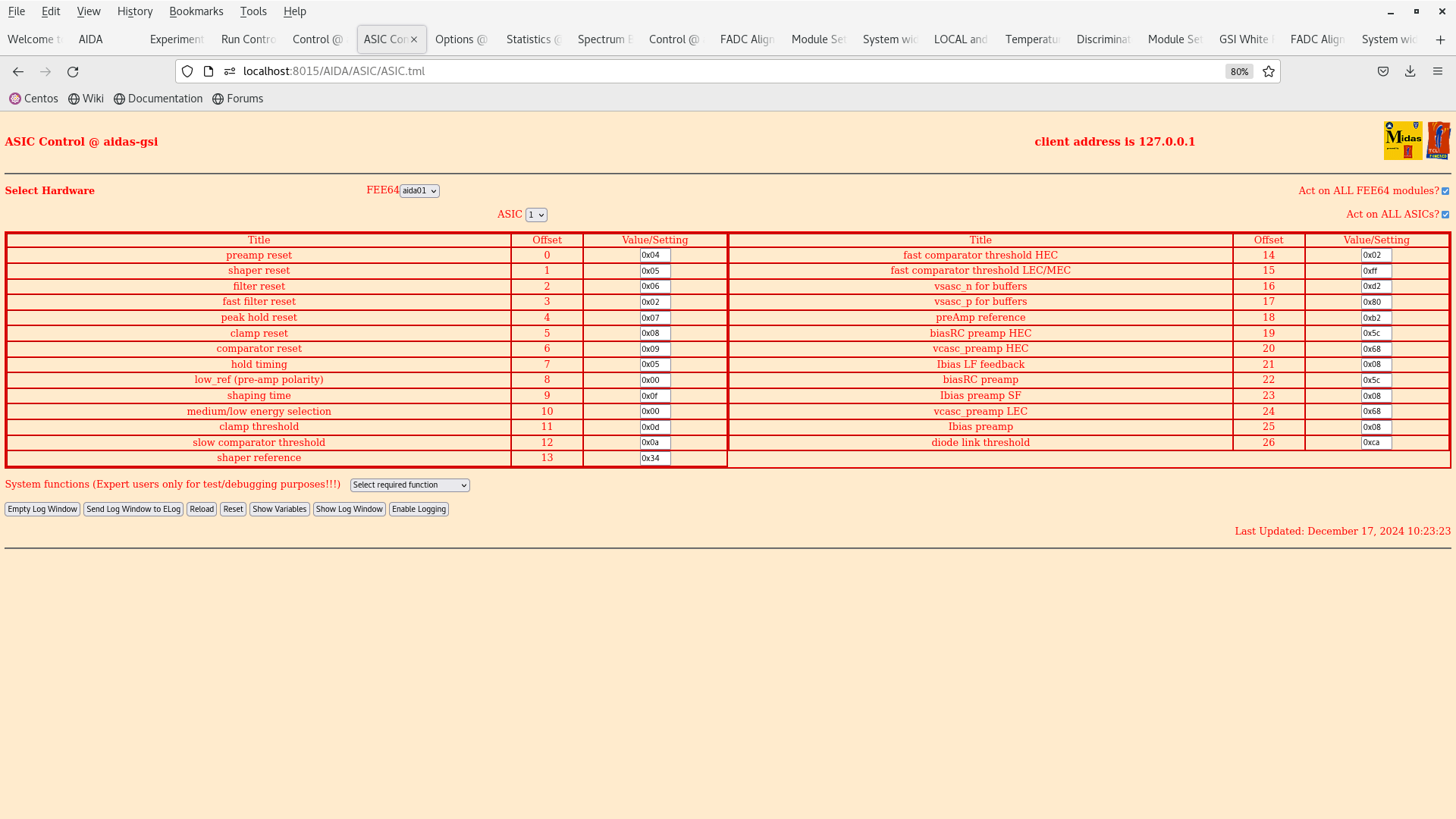

JS | Tuesday 20th 20:00-00:00 |

20:00

Taking over from Liam, all systems good.

20:30

DB No faults.

Stats good

ucesb ok

20:58

DB No faults.

Stats good

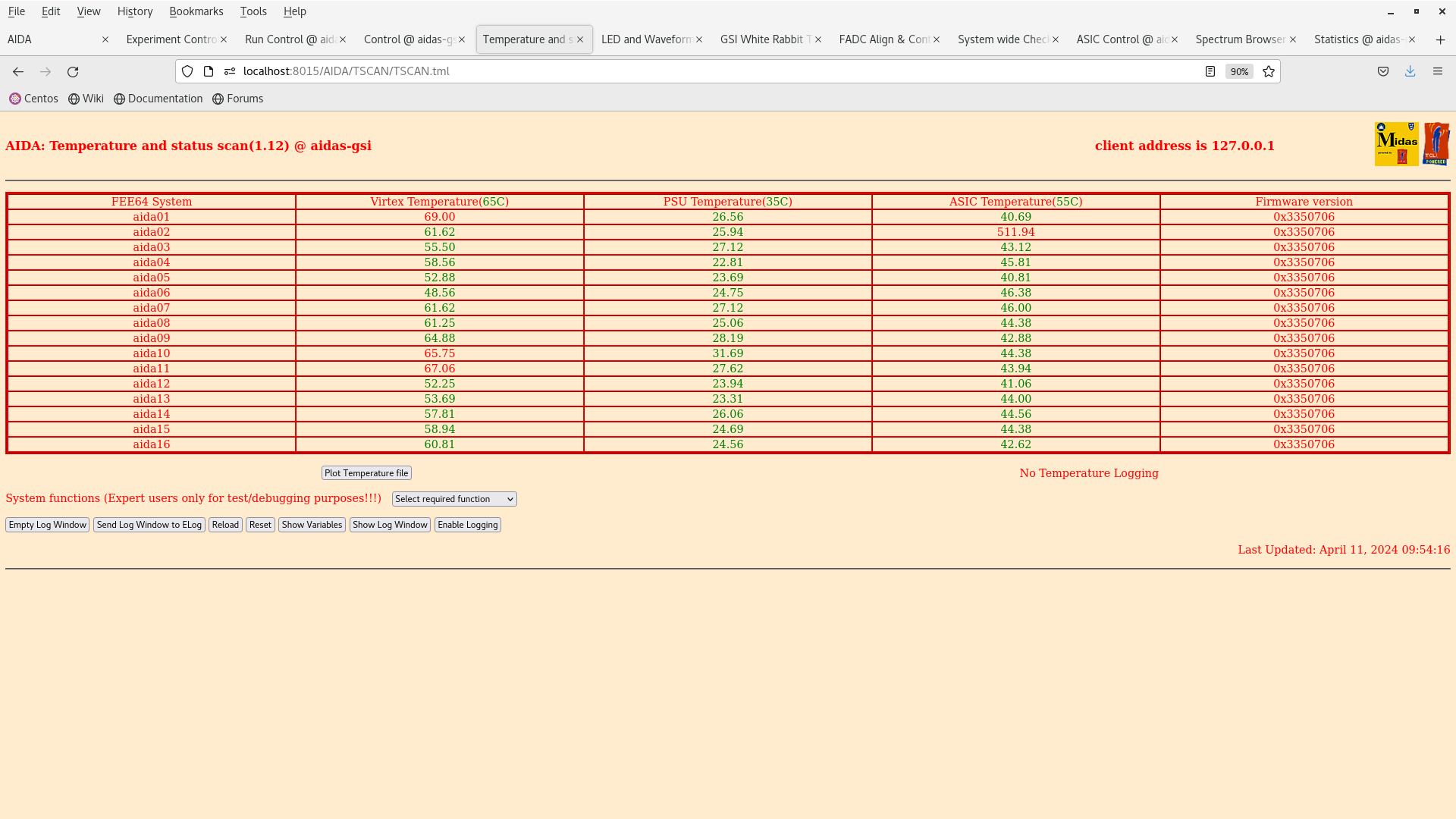

Temps good

ucesb ok

21:31

DB No faults.

Stats good

Temps good

ucesb ok

22:02

DB No faults.

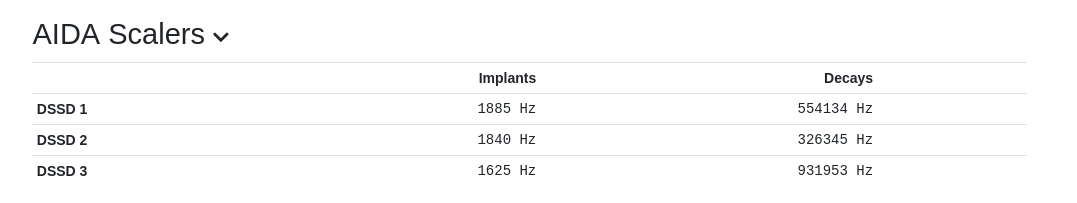

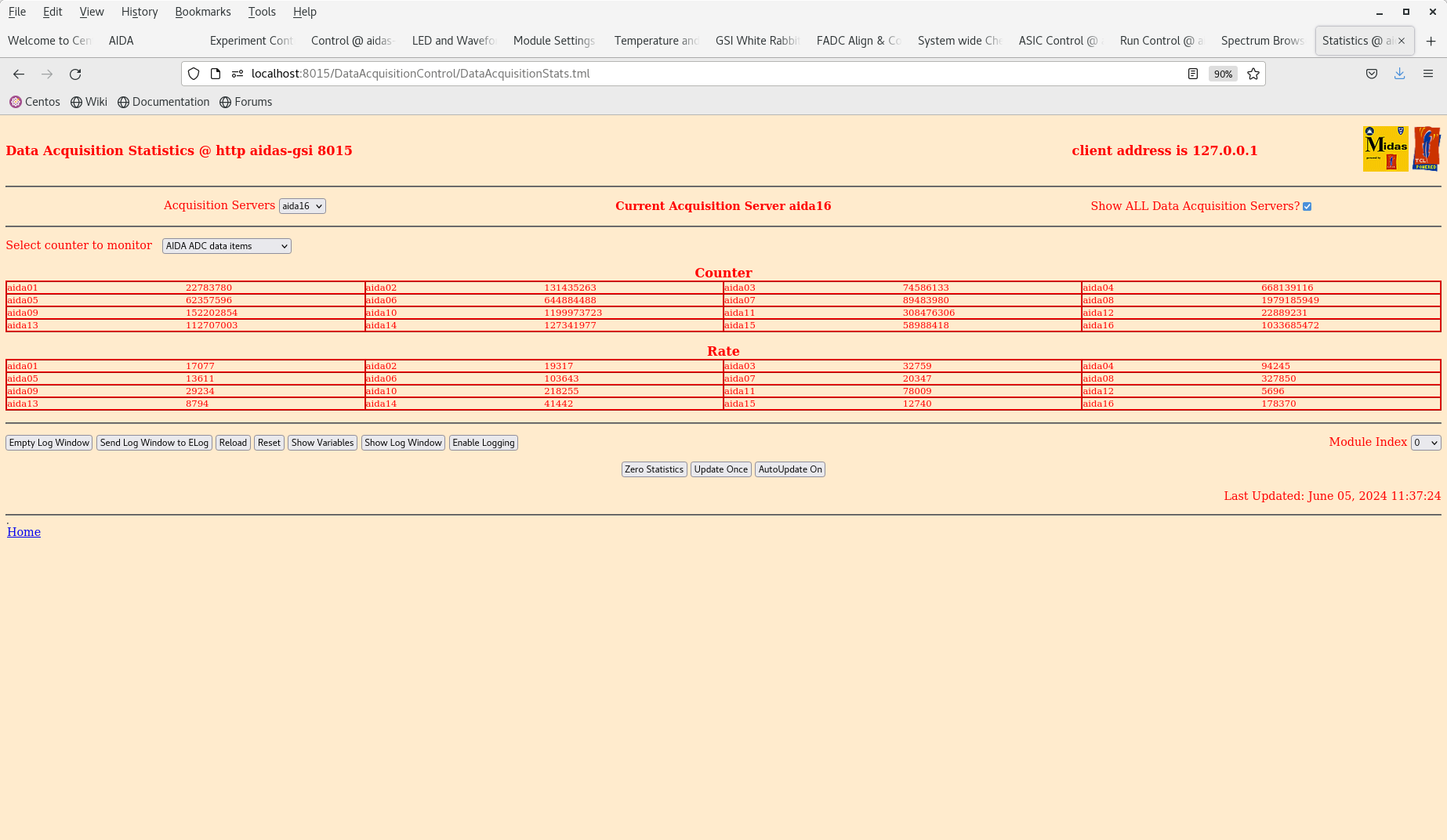

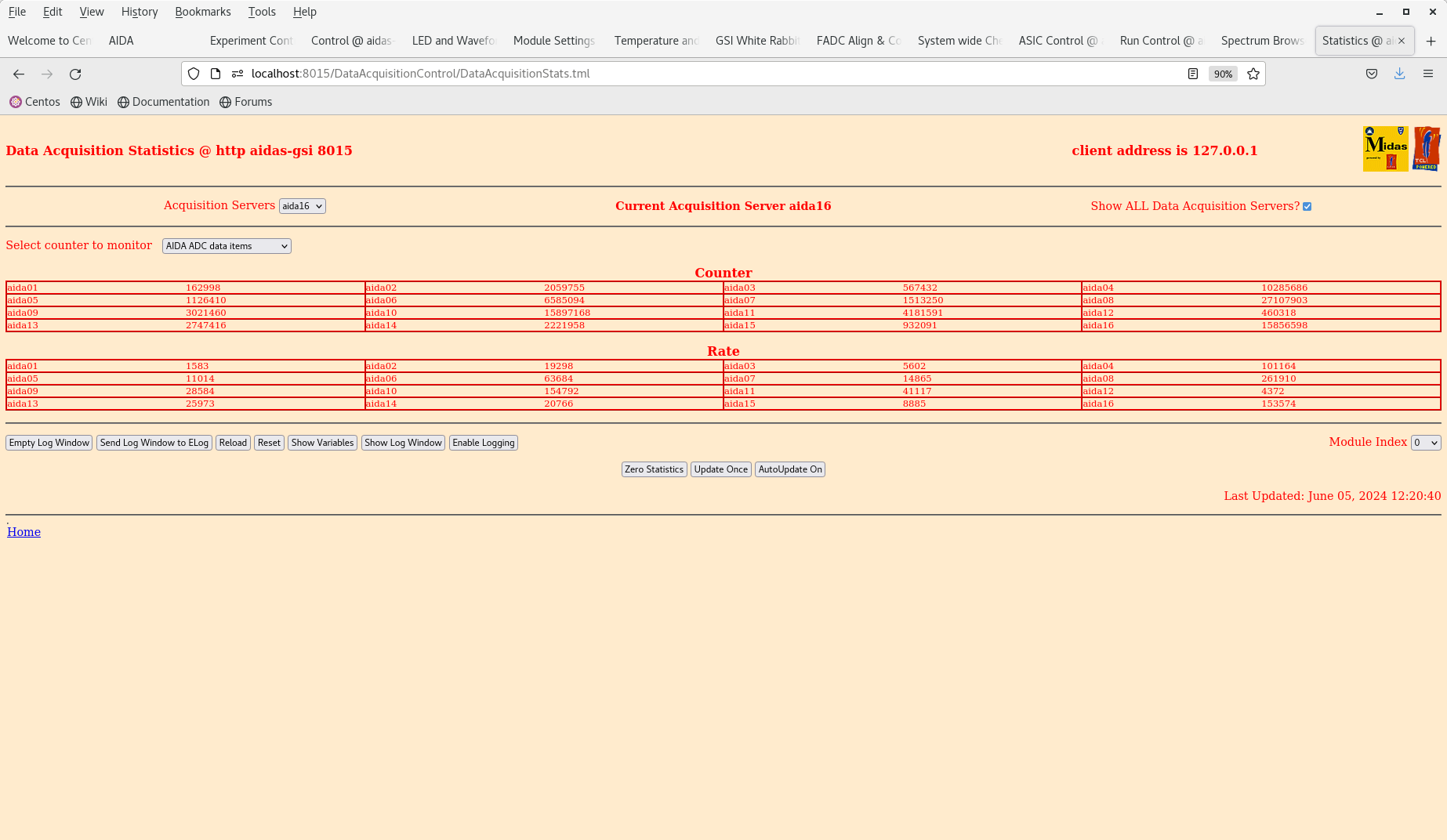

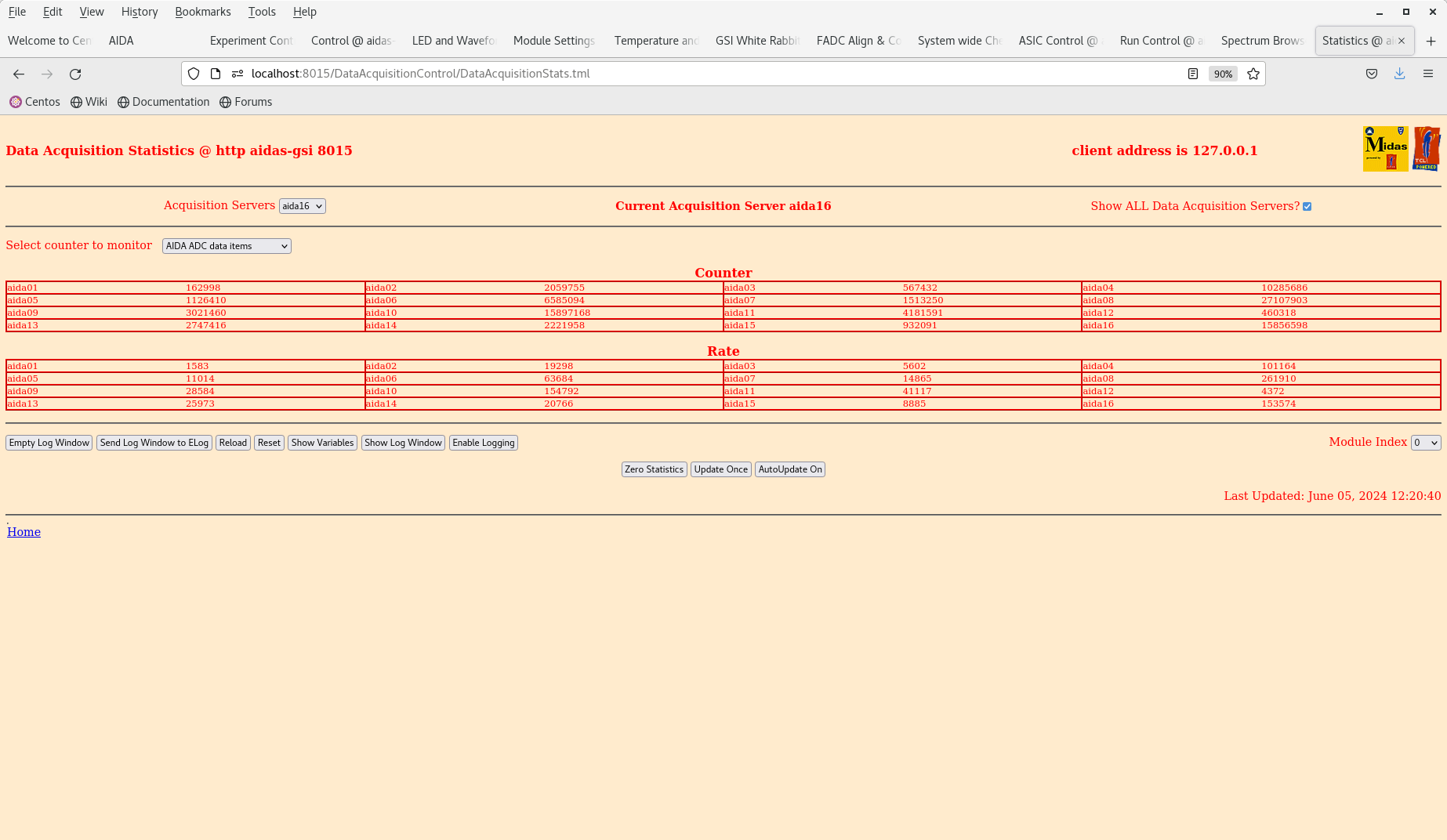

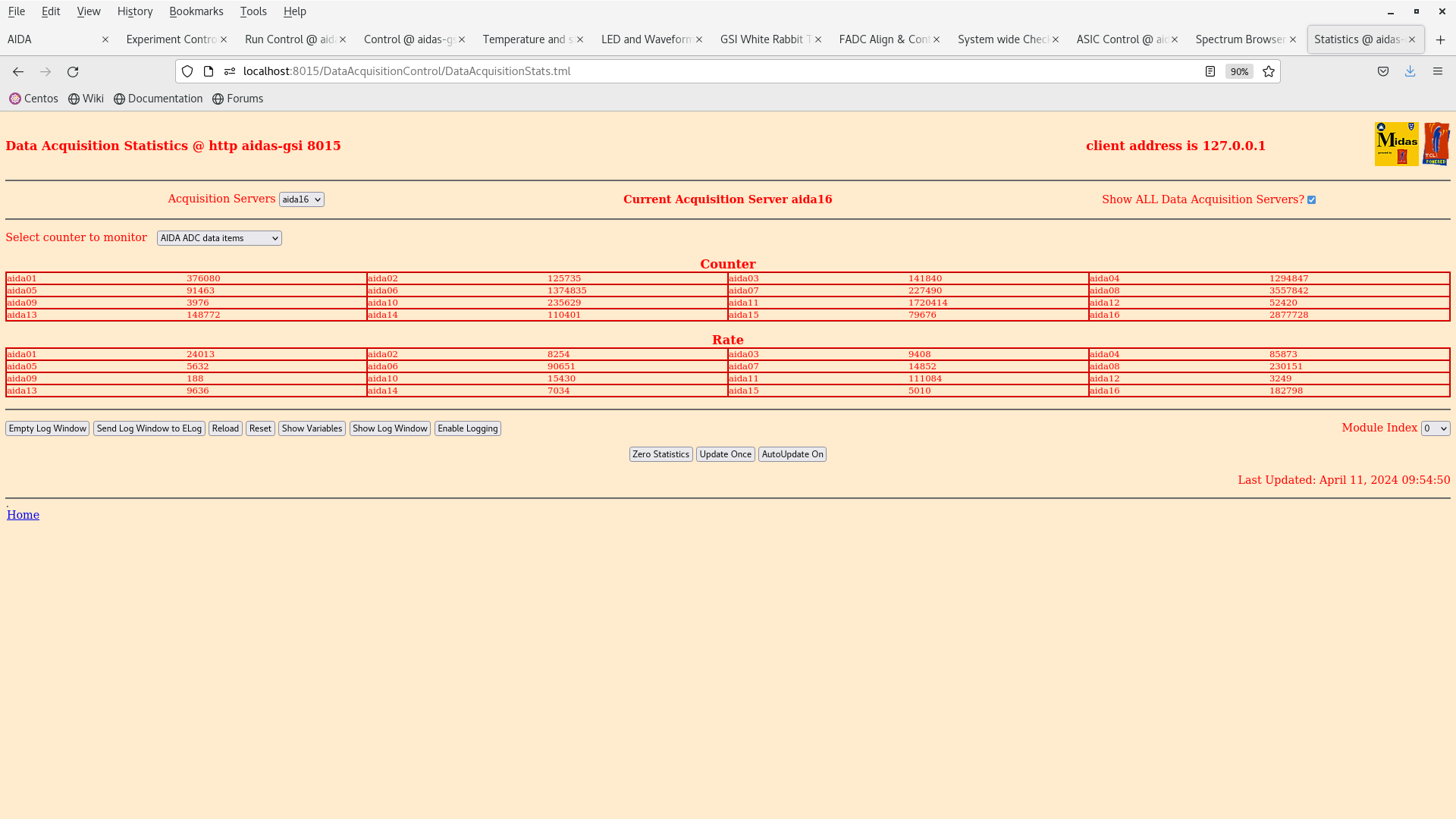

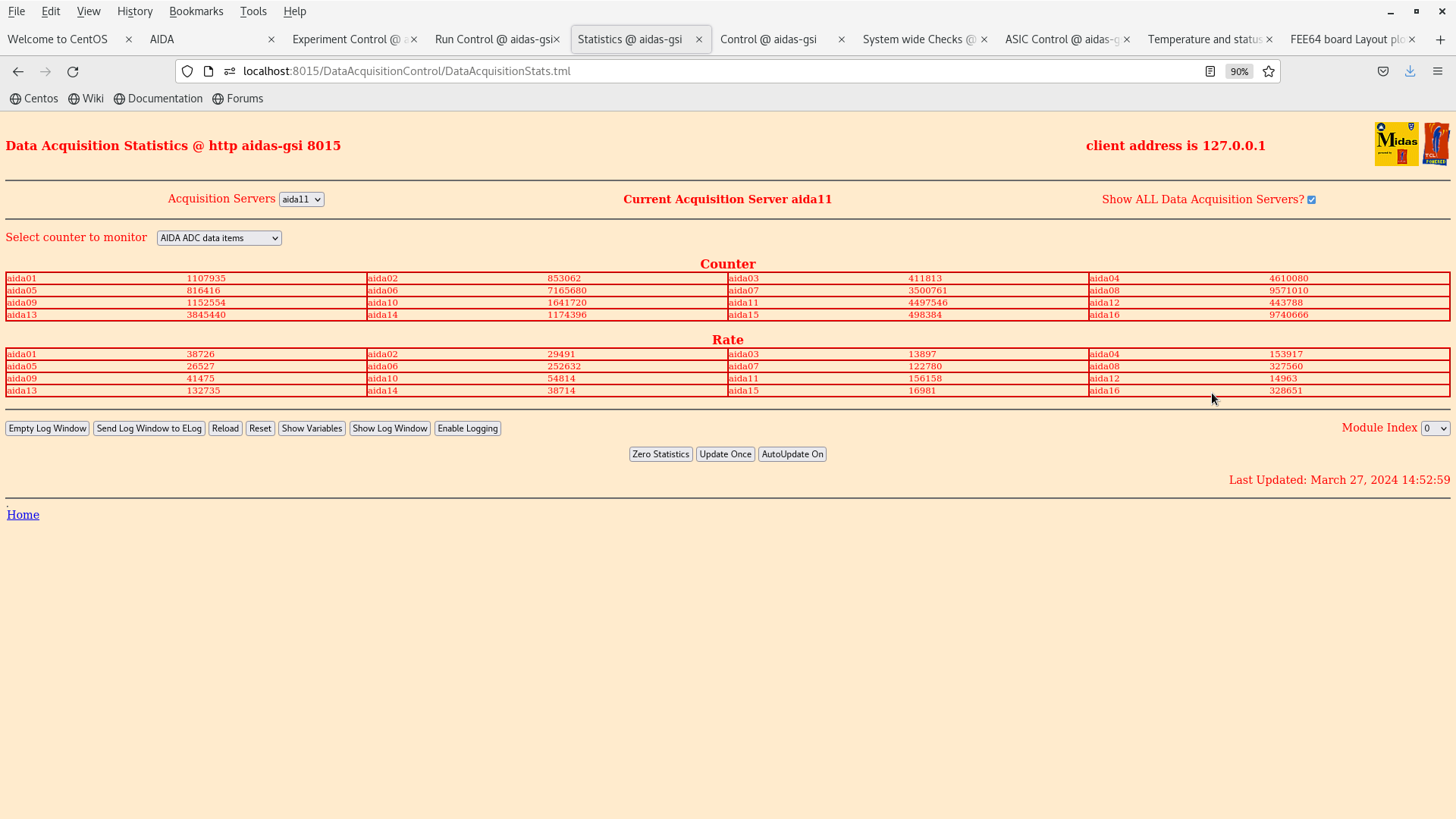

Stats good elog:254/3

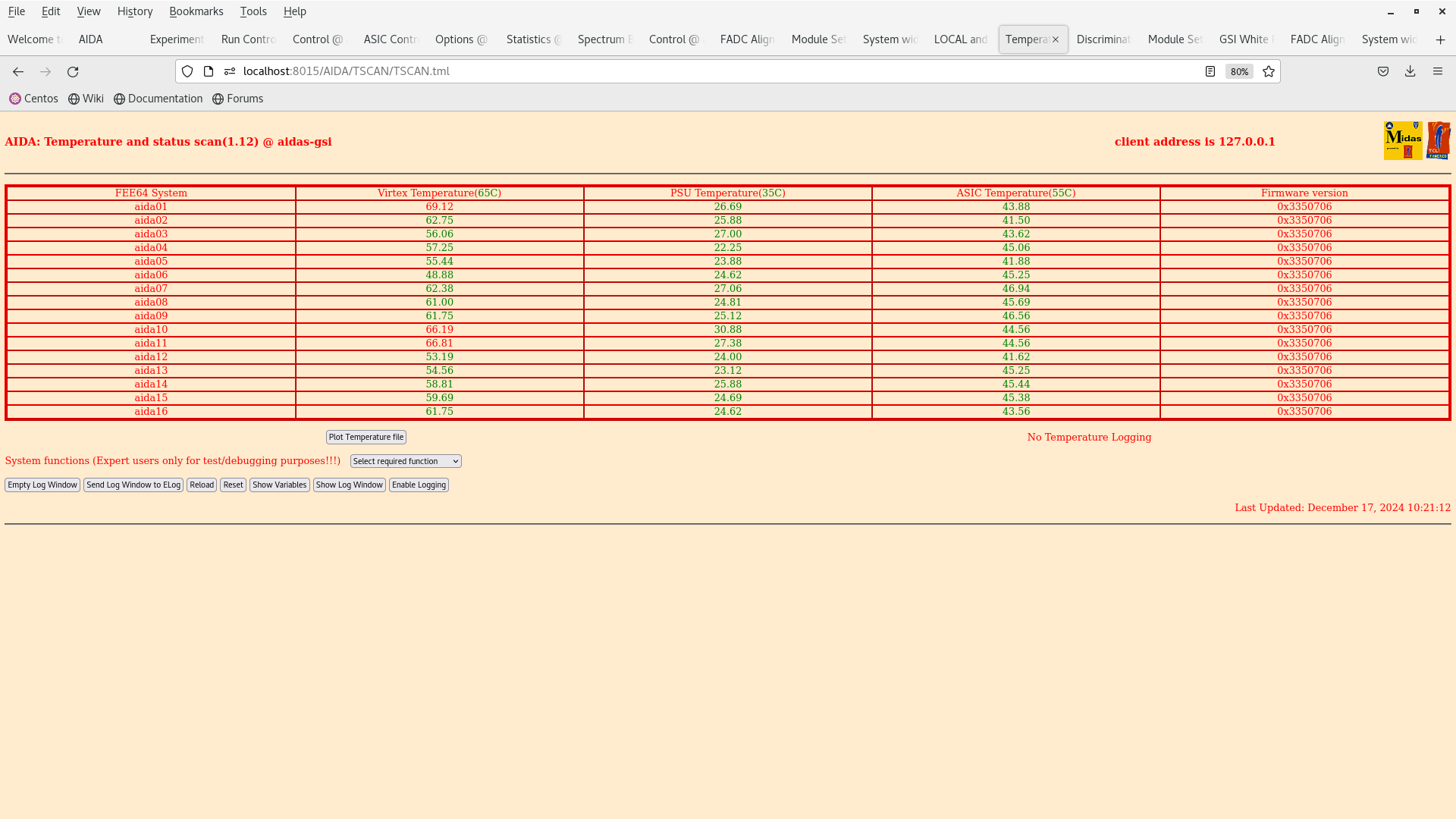

Temps good elog:254/4

ucesb ok elog:254/1

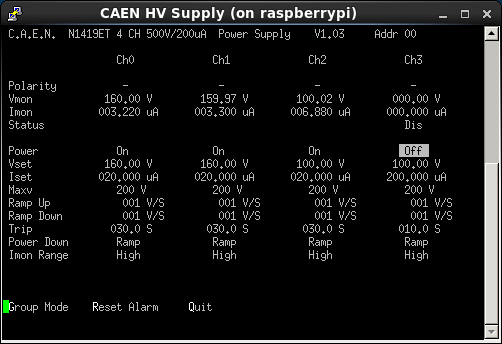

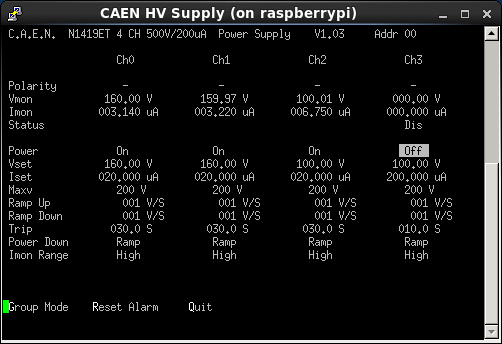

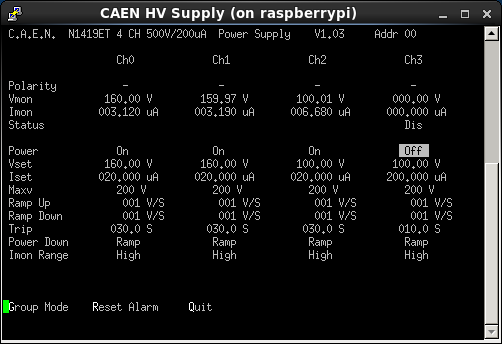

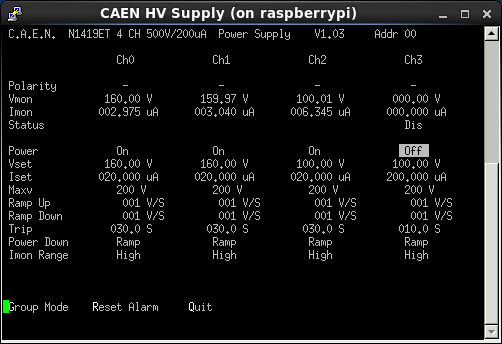

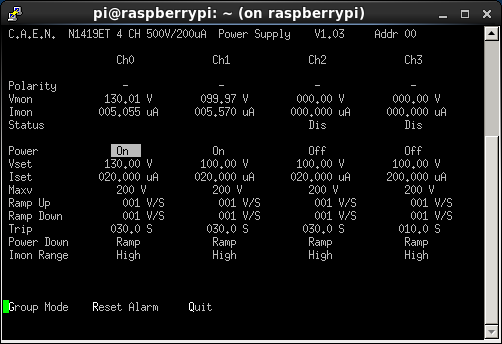

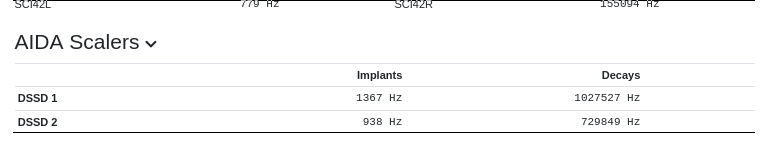

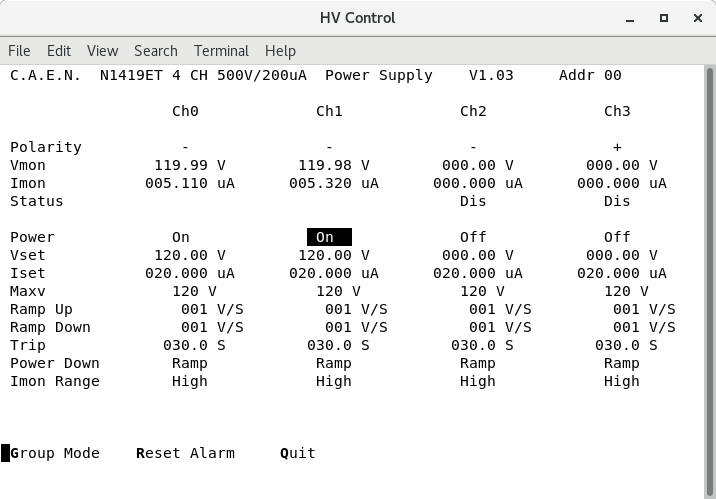

Current ok elog:254/2

ADC Calibration check:

FEE64 module aida06 failed

Calibration test result: Passed 11, Failed 1

22:06 ucesb - DAQ Error - Onsite team checking daq crash

Tape server icon stopped spinning

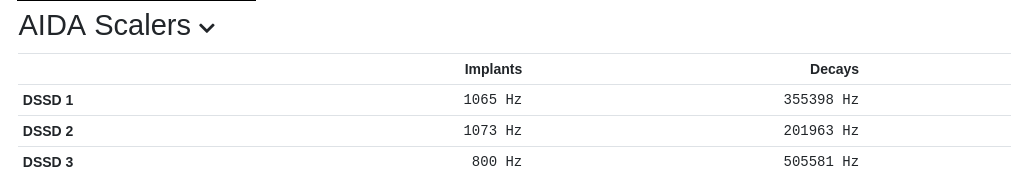

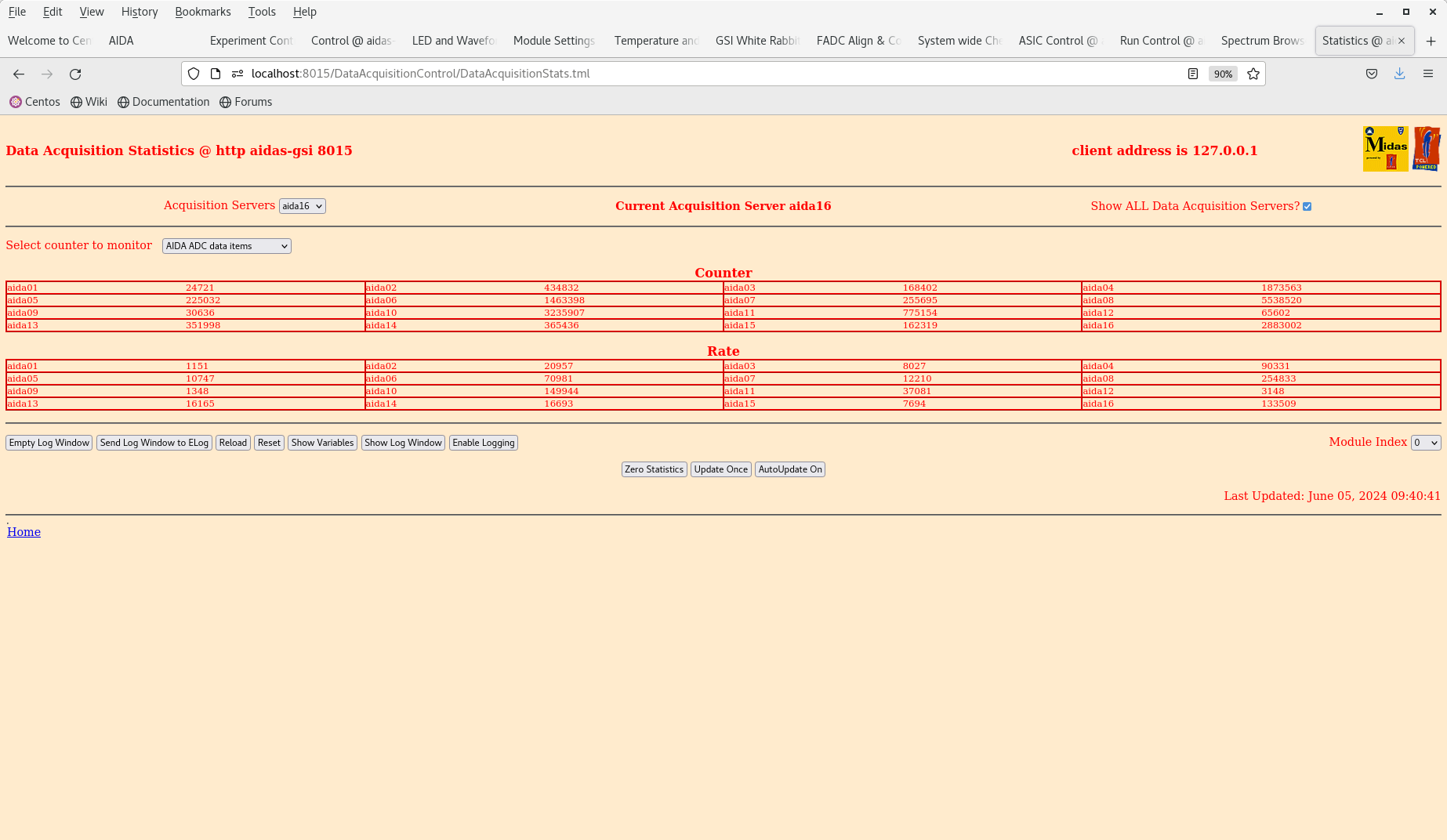

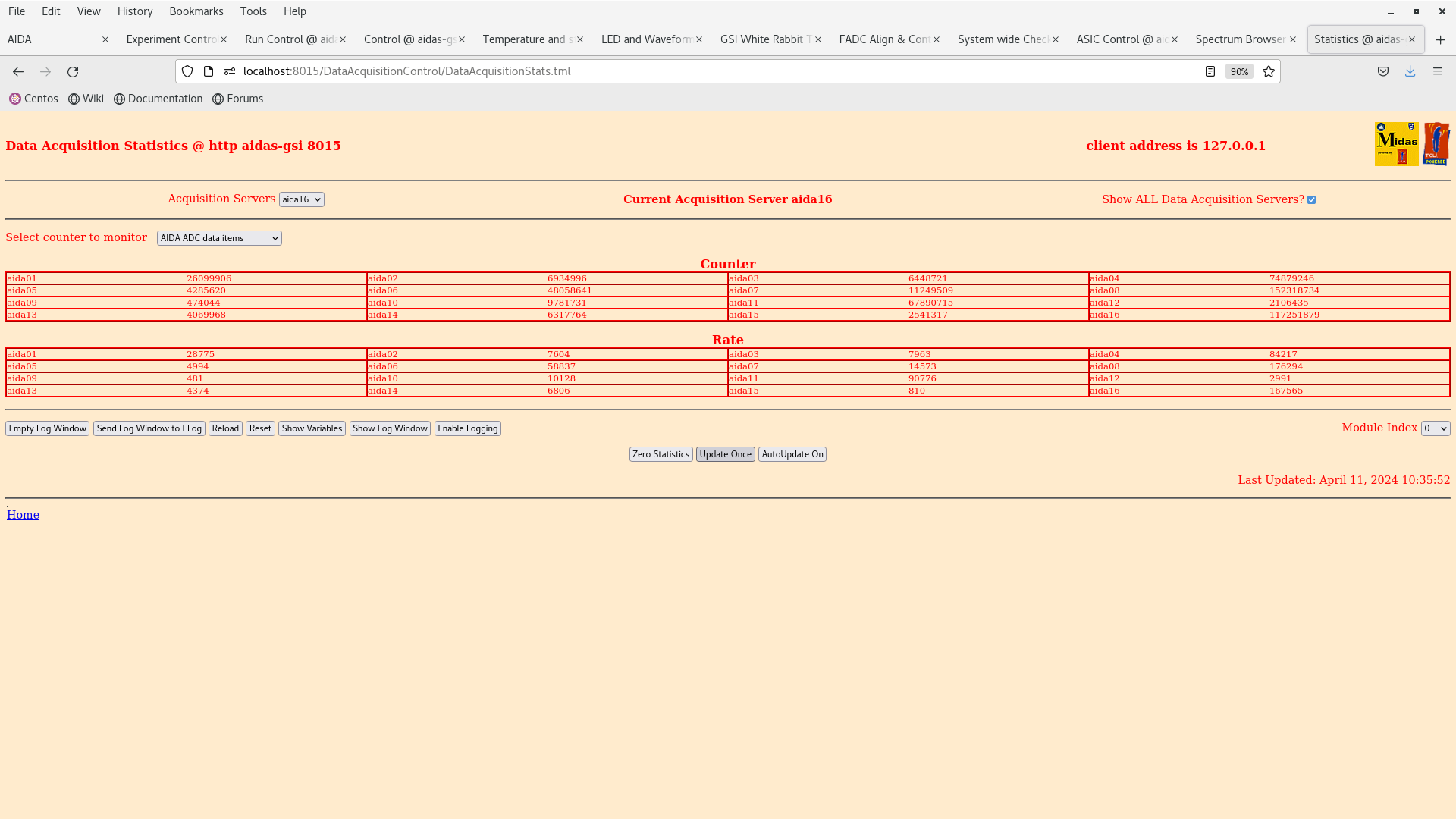

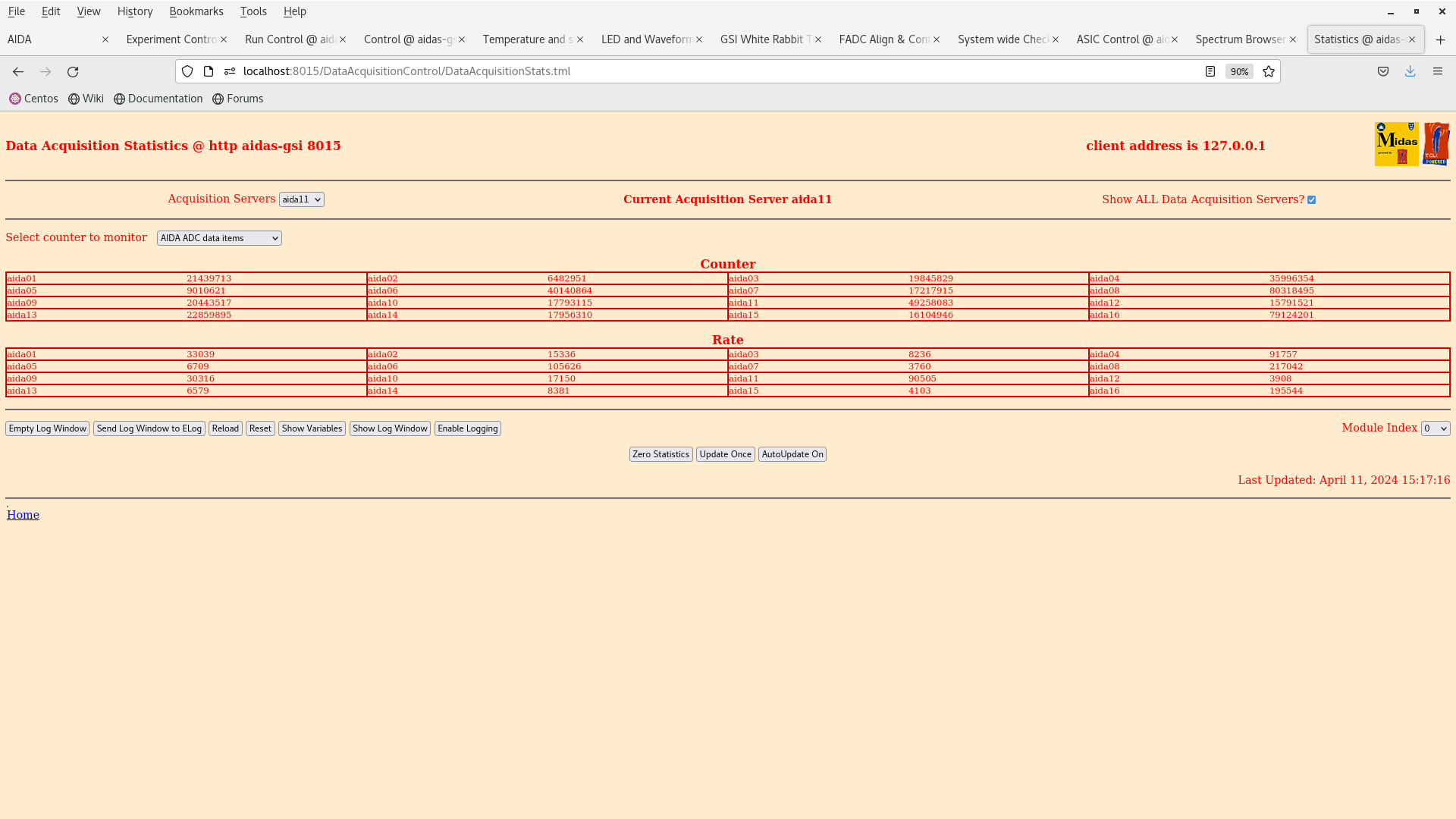

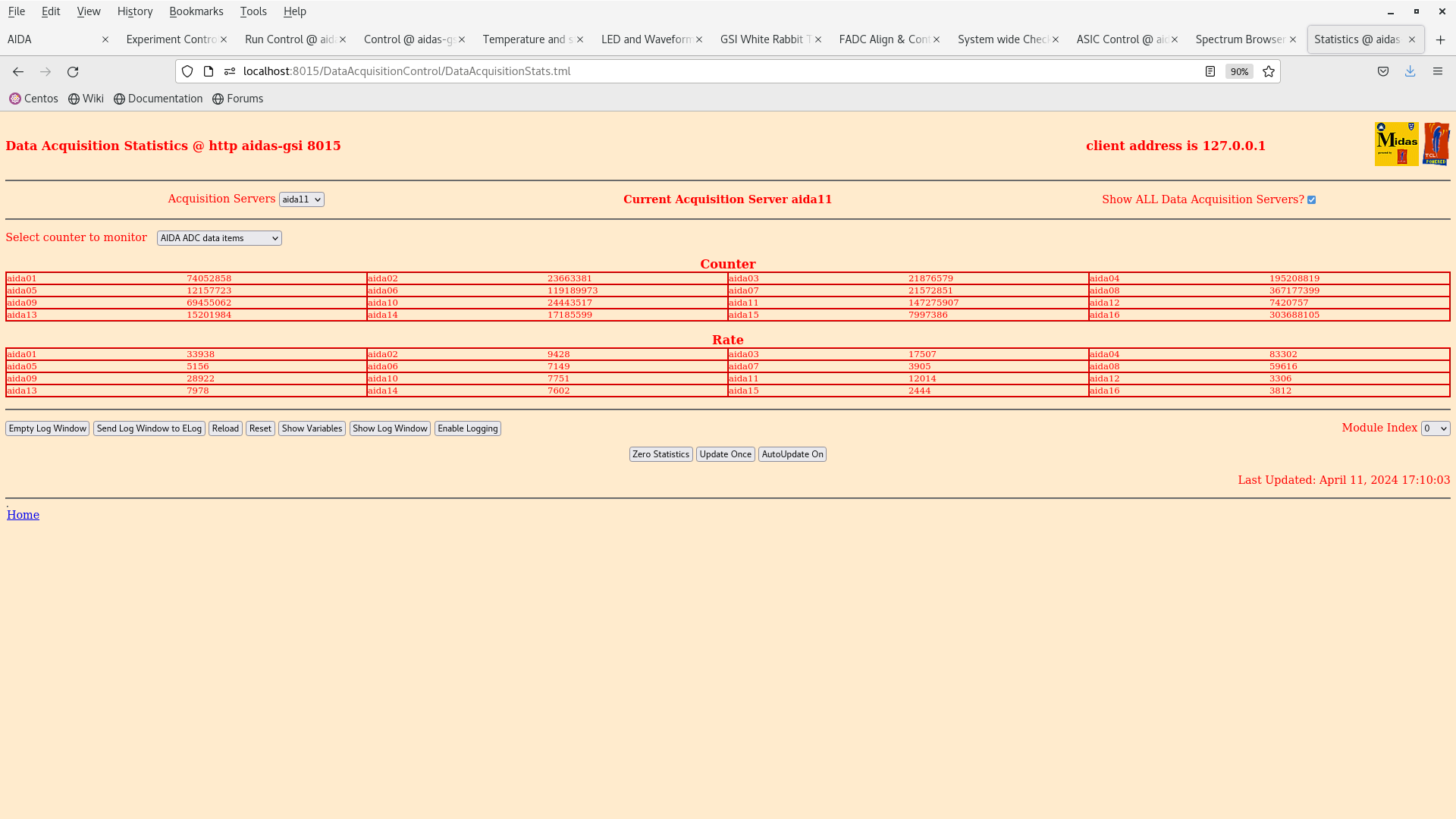

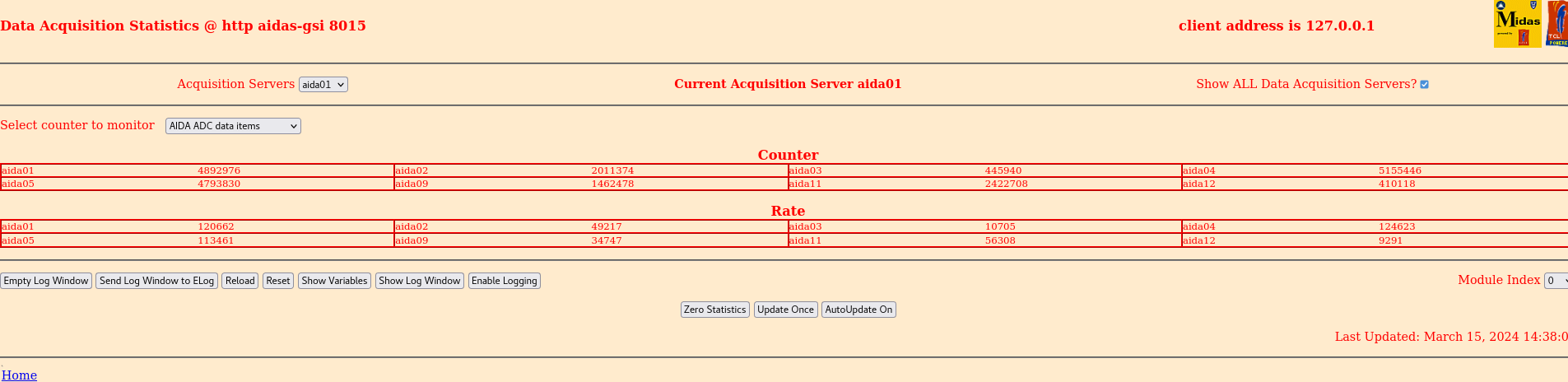

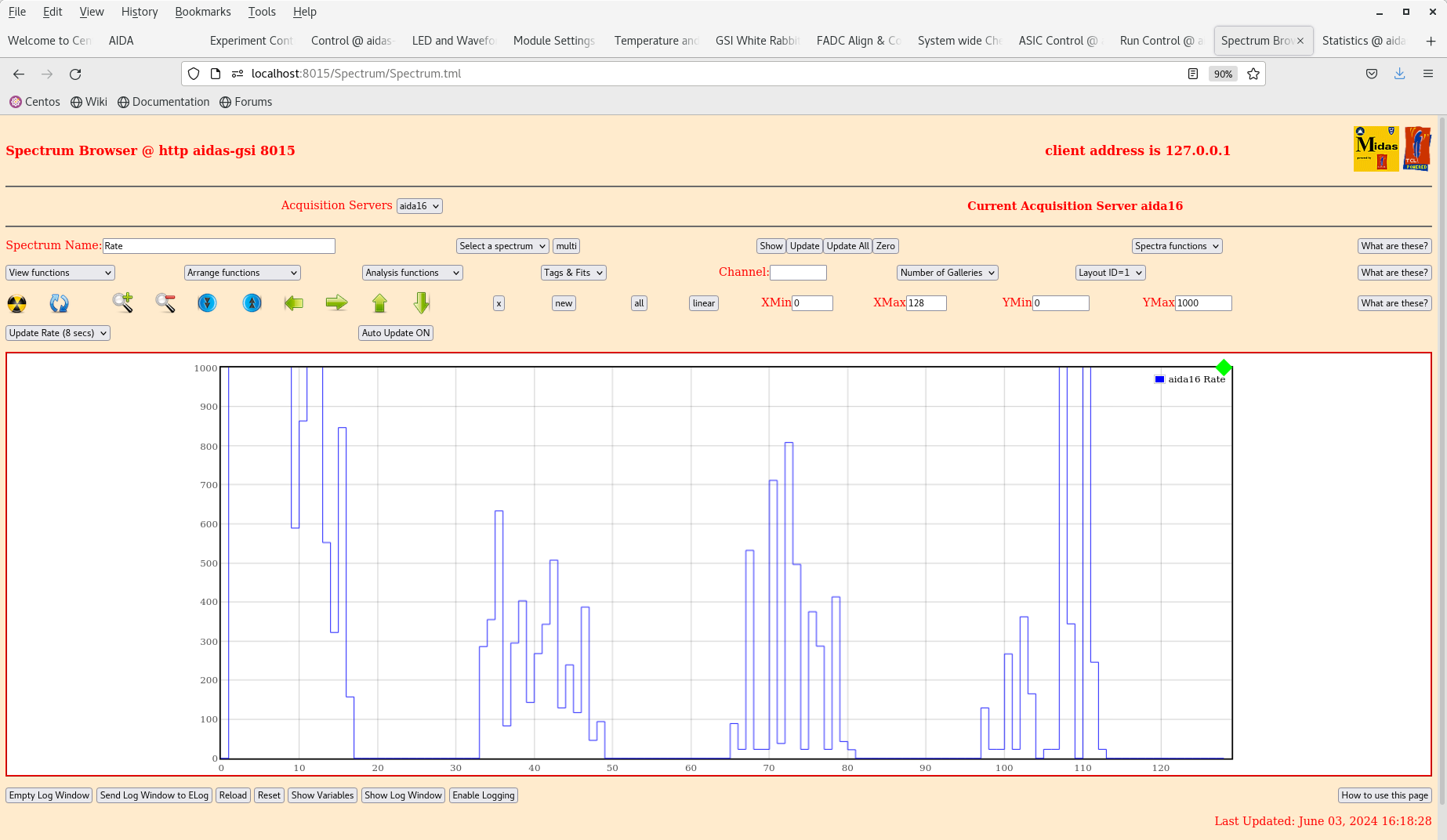

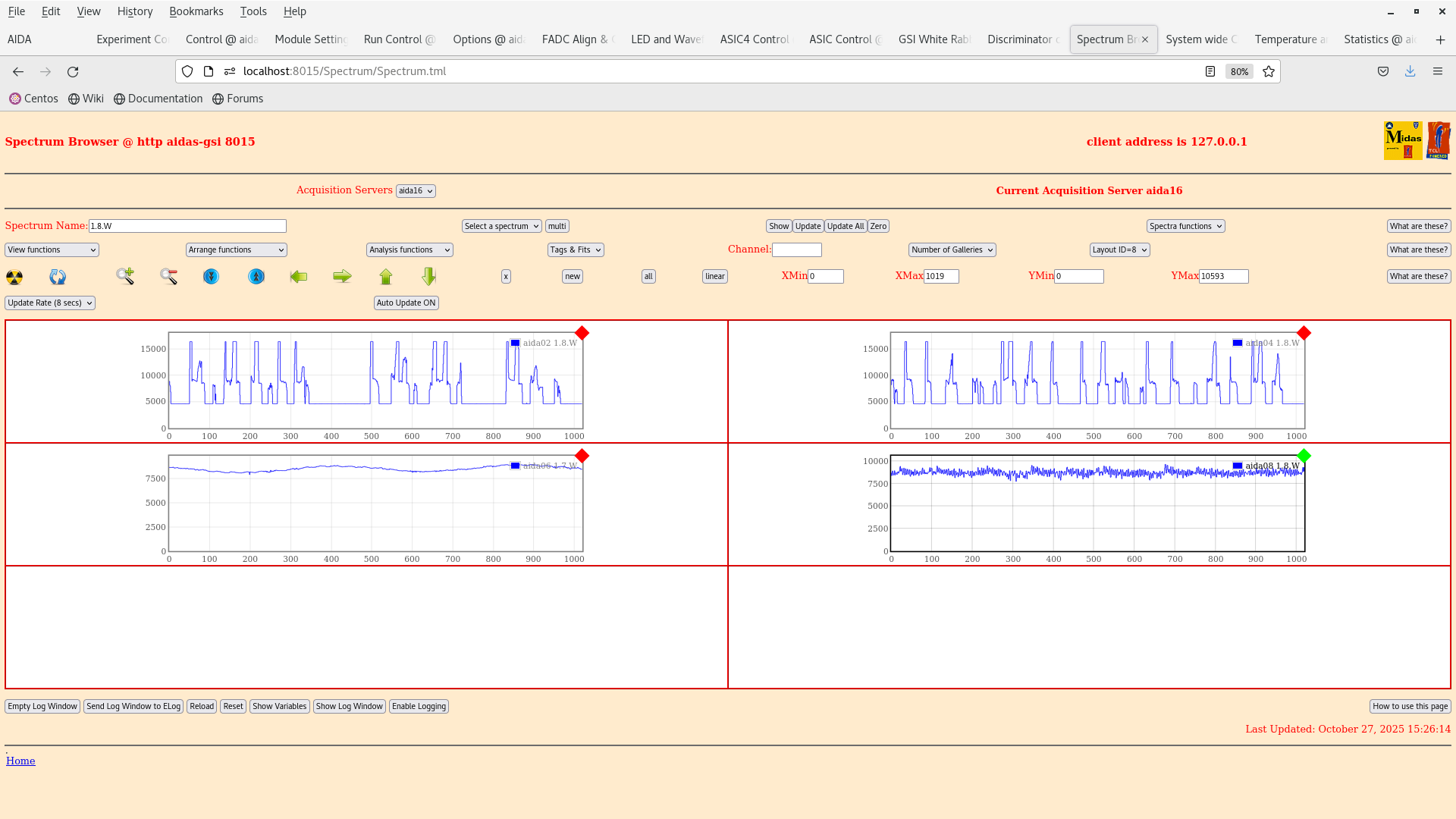

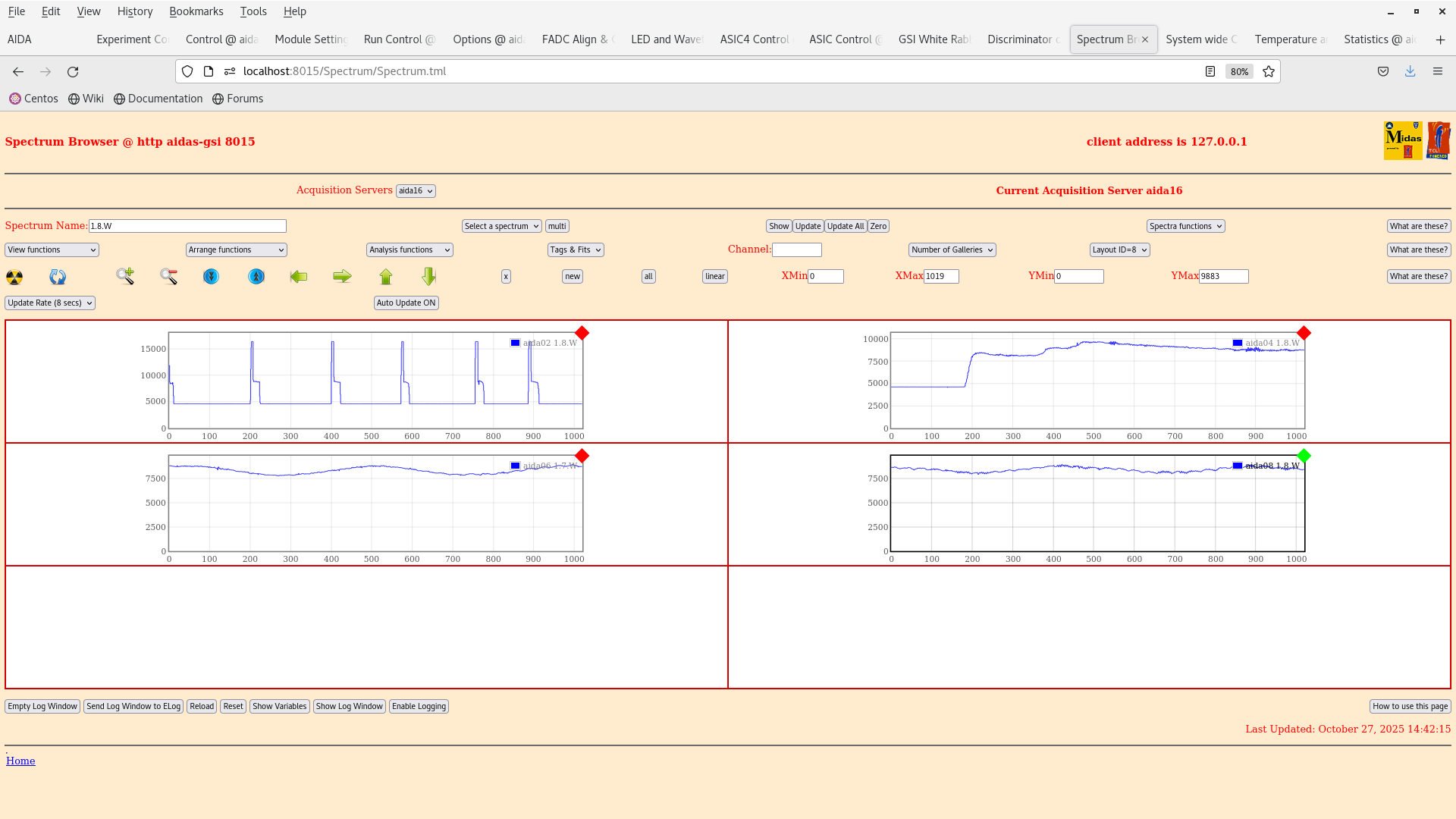

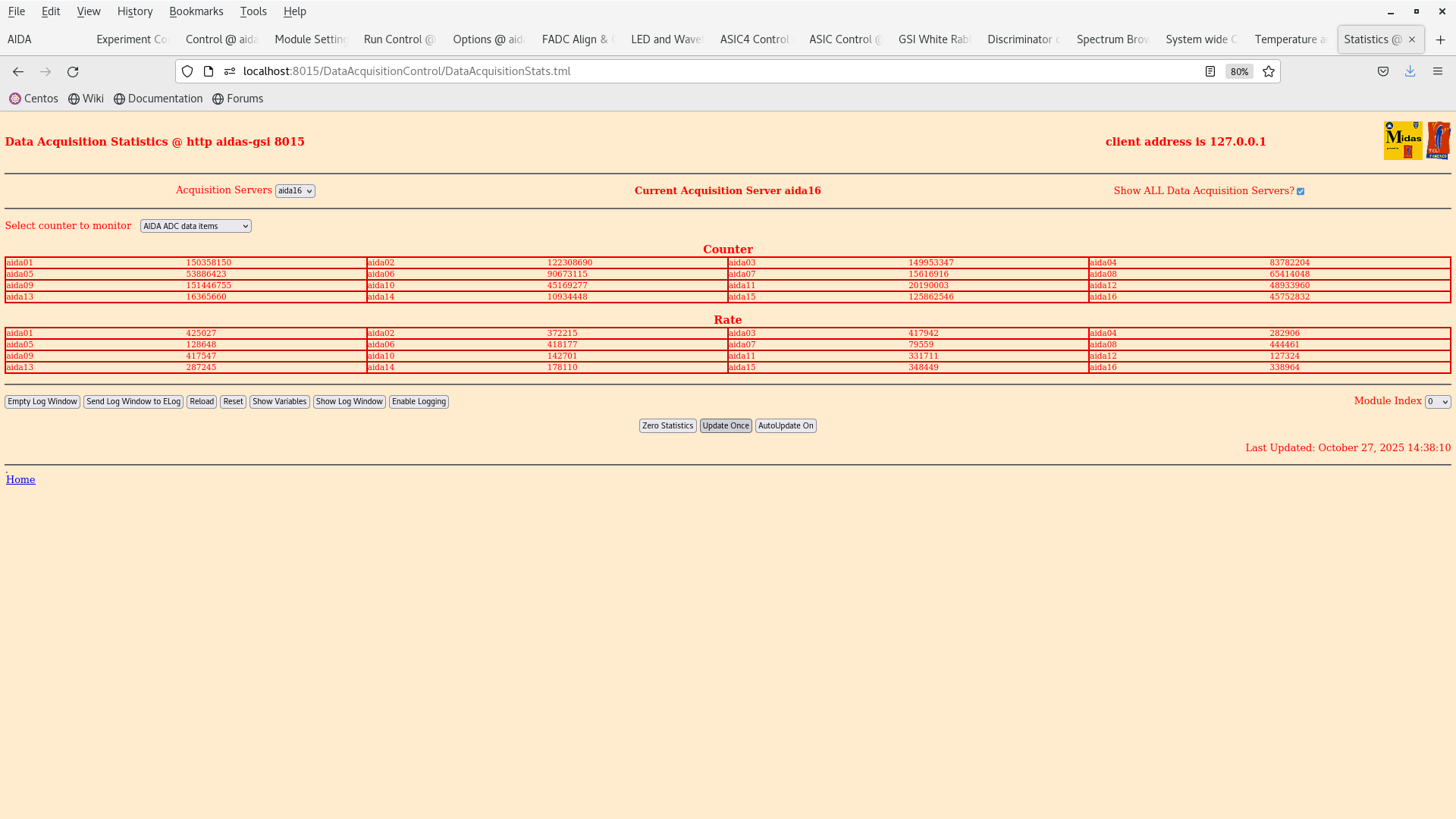

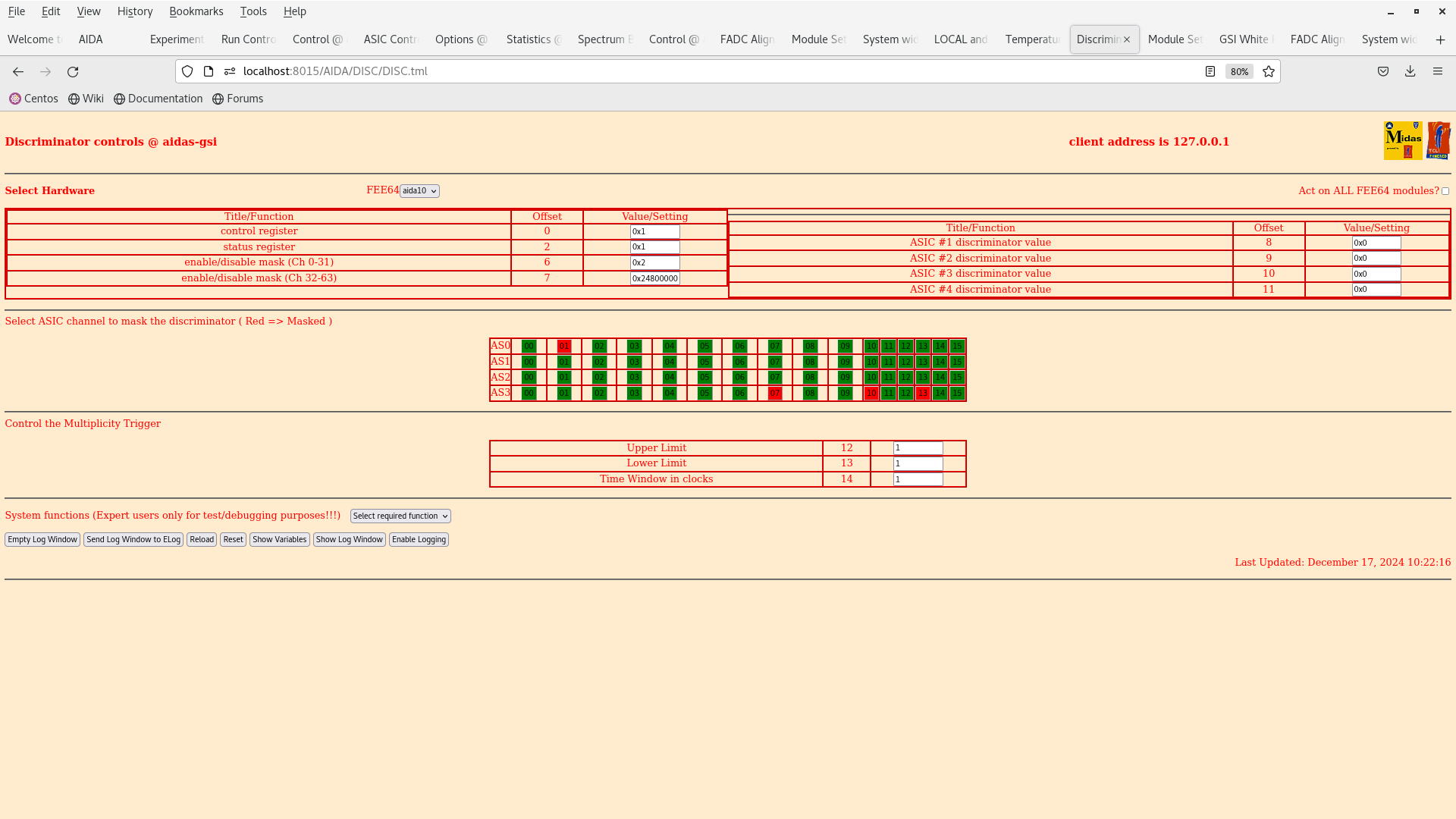

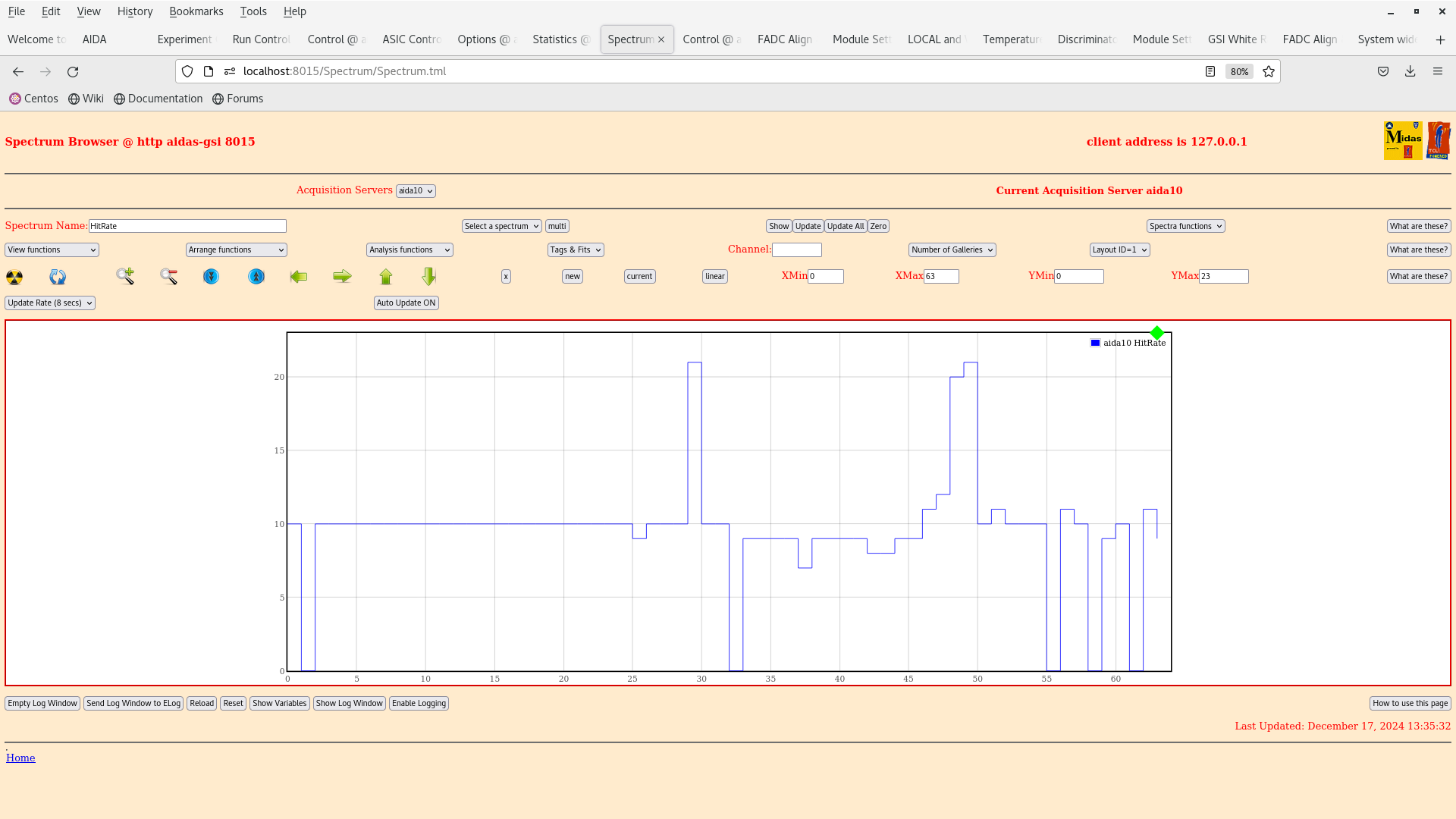

Stats Rates 0, Counter aida01 zeroed but others normal. elog:254/5

Called Tom. Tried resetting in midas, no luck. Full reboot of DAQ and midas required.

According to log at 22:07 aida01 reset

Data taking stopped at 22:04 file R45_193

22:50

After a full power cycle all appear to be up and running well. Starting full checks.

23:00

Clock status test result: Passed 12, Failed 0

Calibration test result: Passed 12, Failed 0

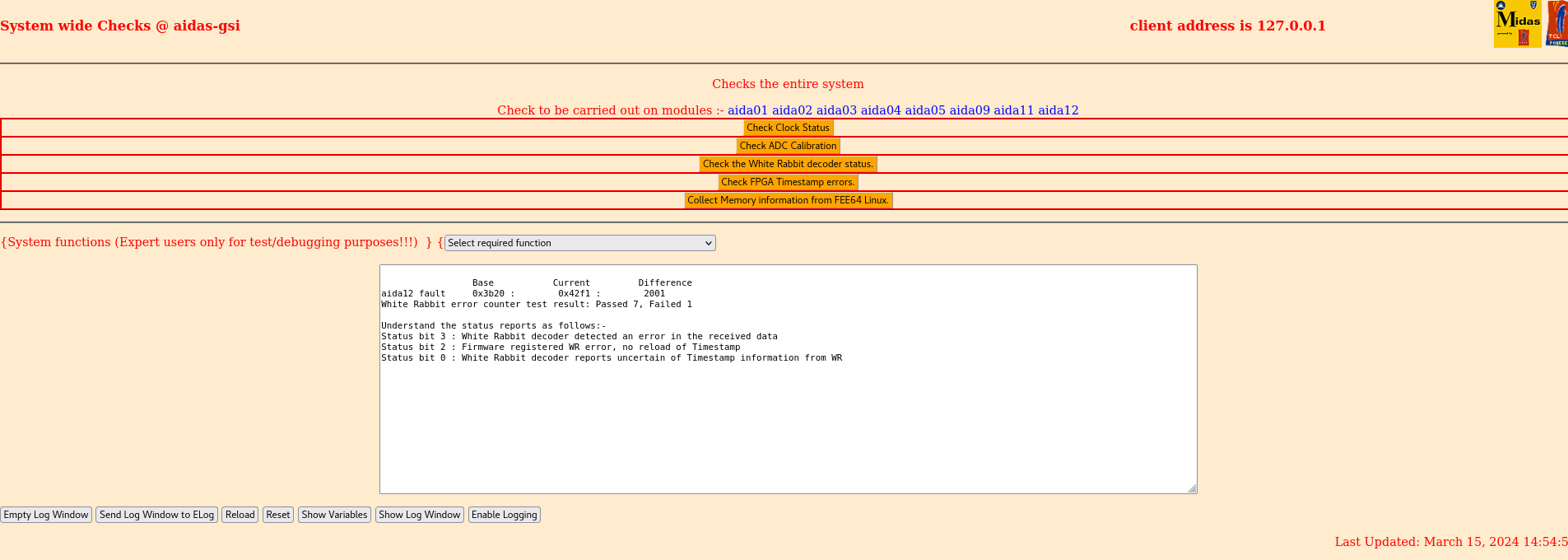

White Rabbit error counter test result: Passed 12, Failed 0

Check FPGA is having a page error

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k

4k

aida01 : 4 8 2 2 1 3 1 4 2 3 7 :

39792

aida02 : 13 9 2 4 2 3 2 3 2 3 7 :

39708

aida03 : 19 5 4 3 1 3 1 4 2 3 7 :

39892

aida04 : 14 5 2 2 0 5 2 3 2 3 7 :

39744

aida05 : 16 11 3 2 2 4 3 2 1 4 7 :

40584

aida06 : 15 9 5 2 2 2 1 4 2 3 7 :

39828

aida07 : 15 9 3 3 2 2 1 4 2 3 7 :

39828

aida08 : 21 4 3 4 2 2 1 4 2 3 7 :

39844

aida09 : 11 6 1 2 3 4 2 3 2 3 7 :

39788

aida10 : 0 6 4 2 0 3 2 3 2 3 7 :

39472

aida11 : 16 7 2 0 1 3 2 3 2 3 7 :

39512

aida12 : 3 7 4 1 3 2 2 3 2 3 7 :

39524

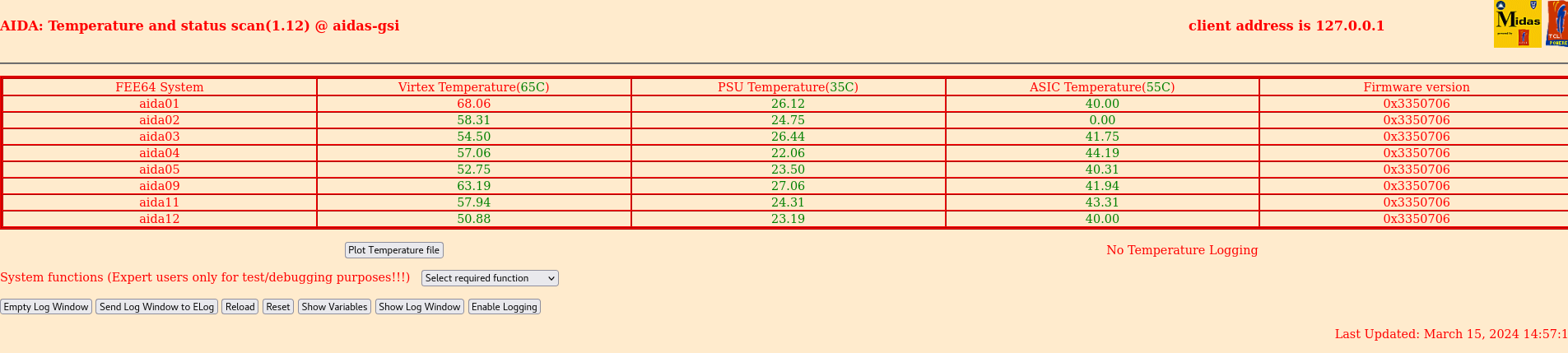

DB No faults.

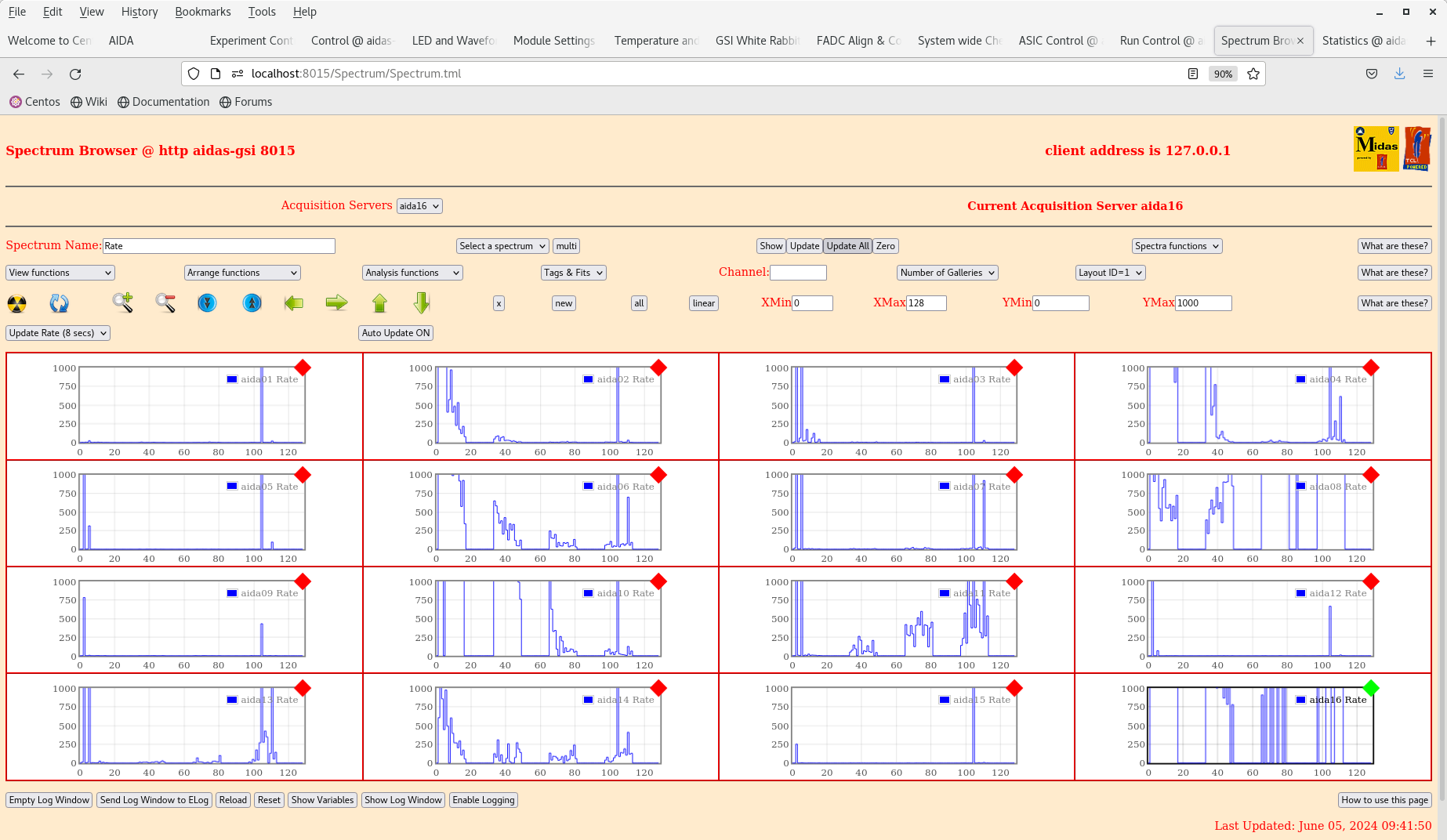

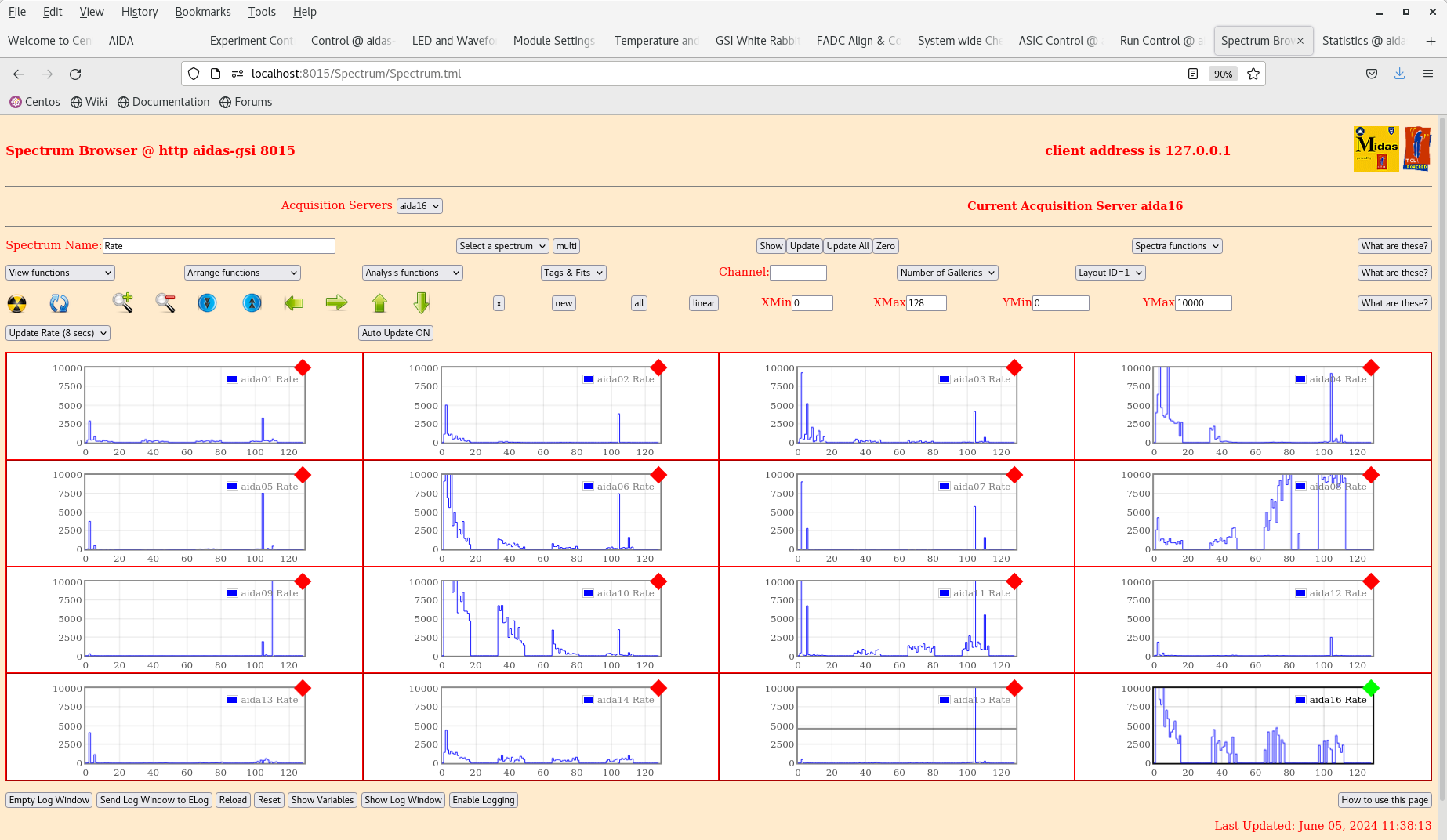

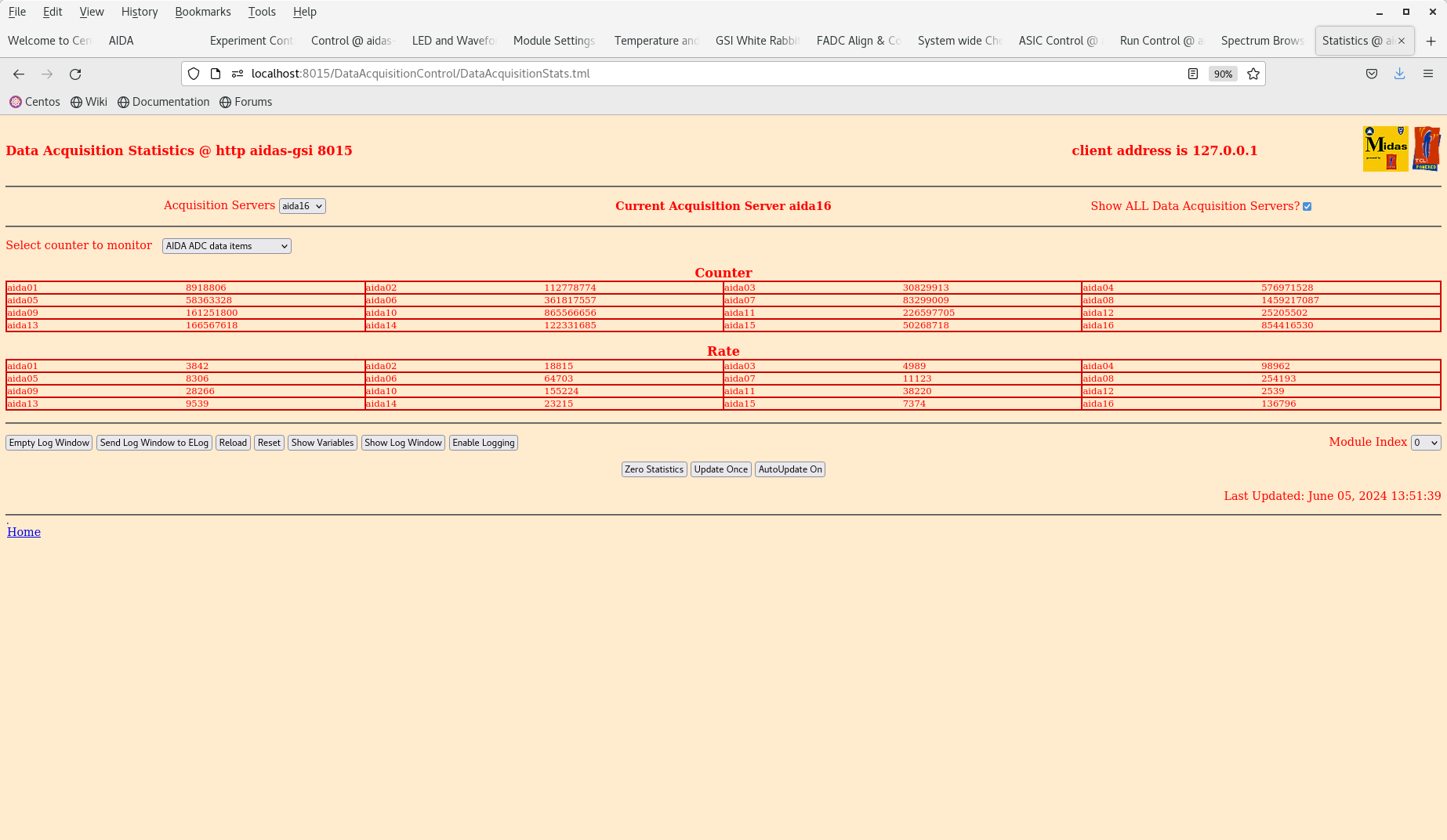

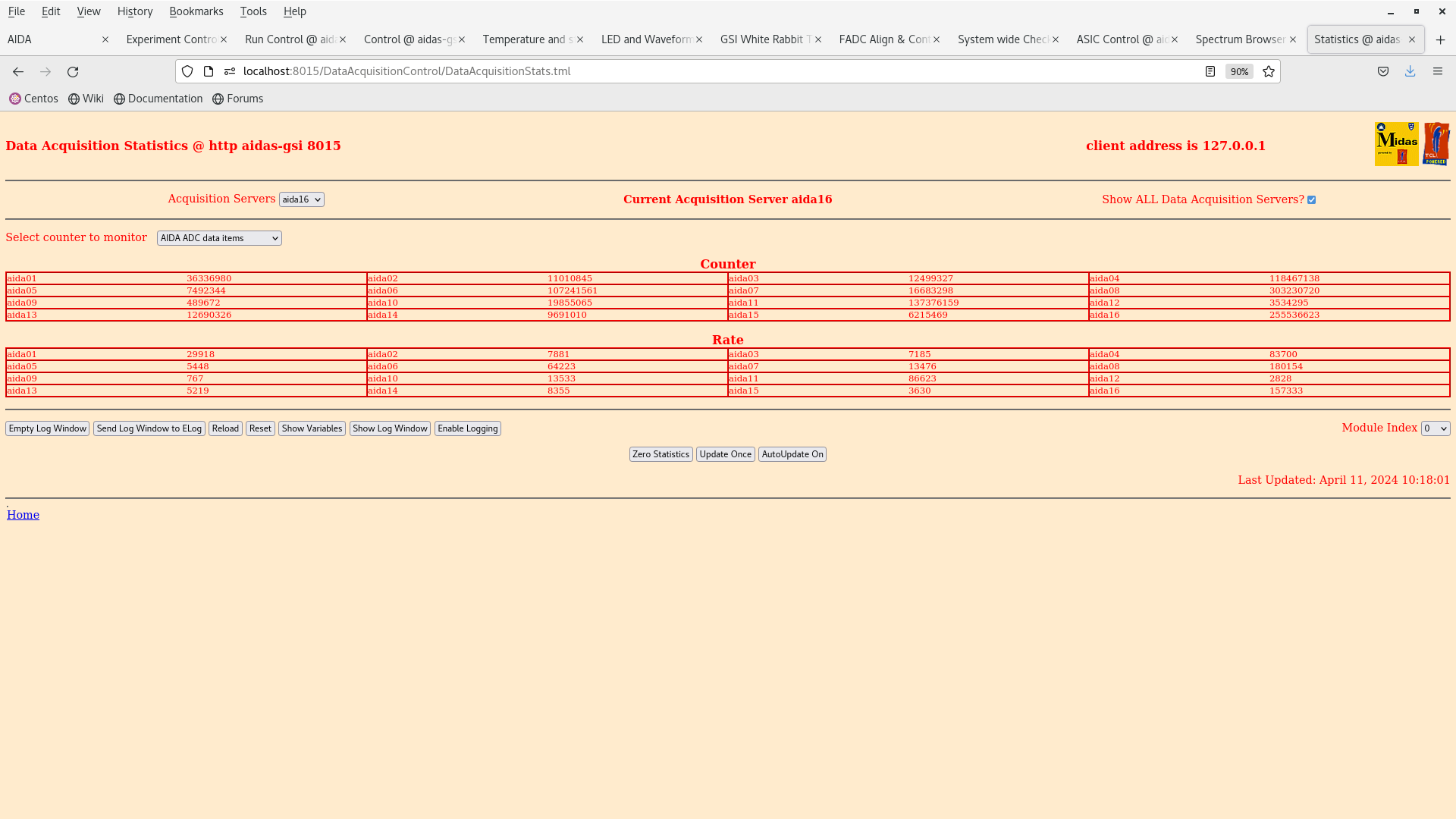

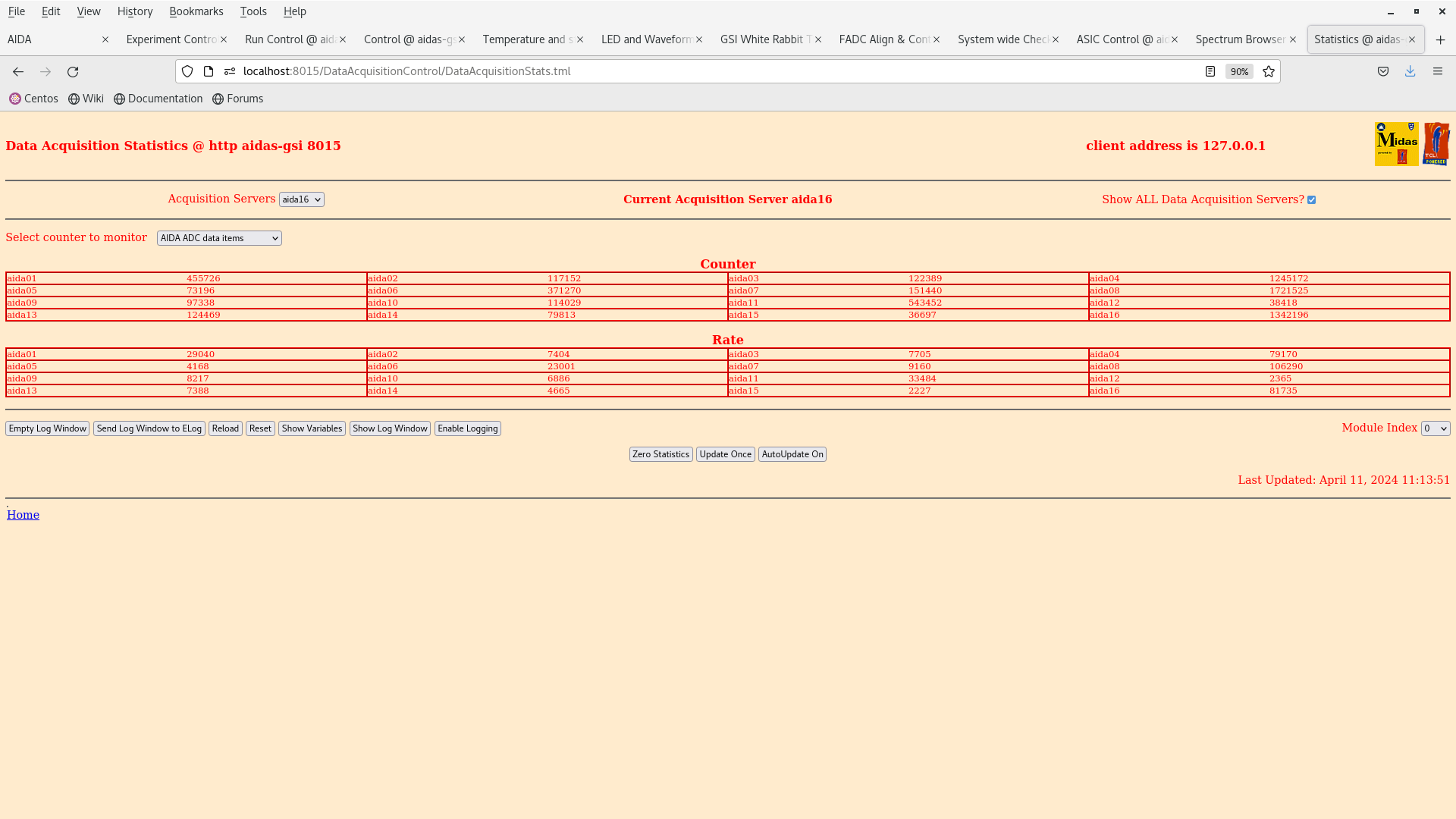

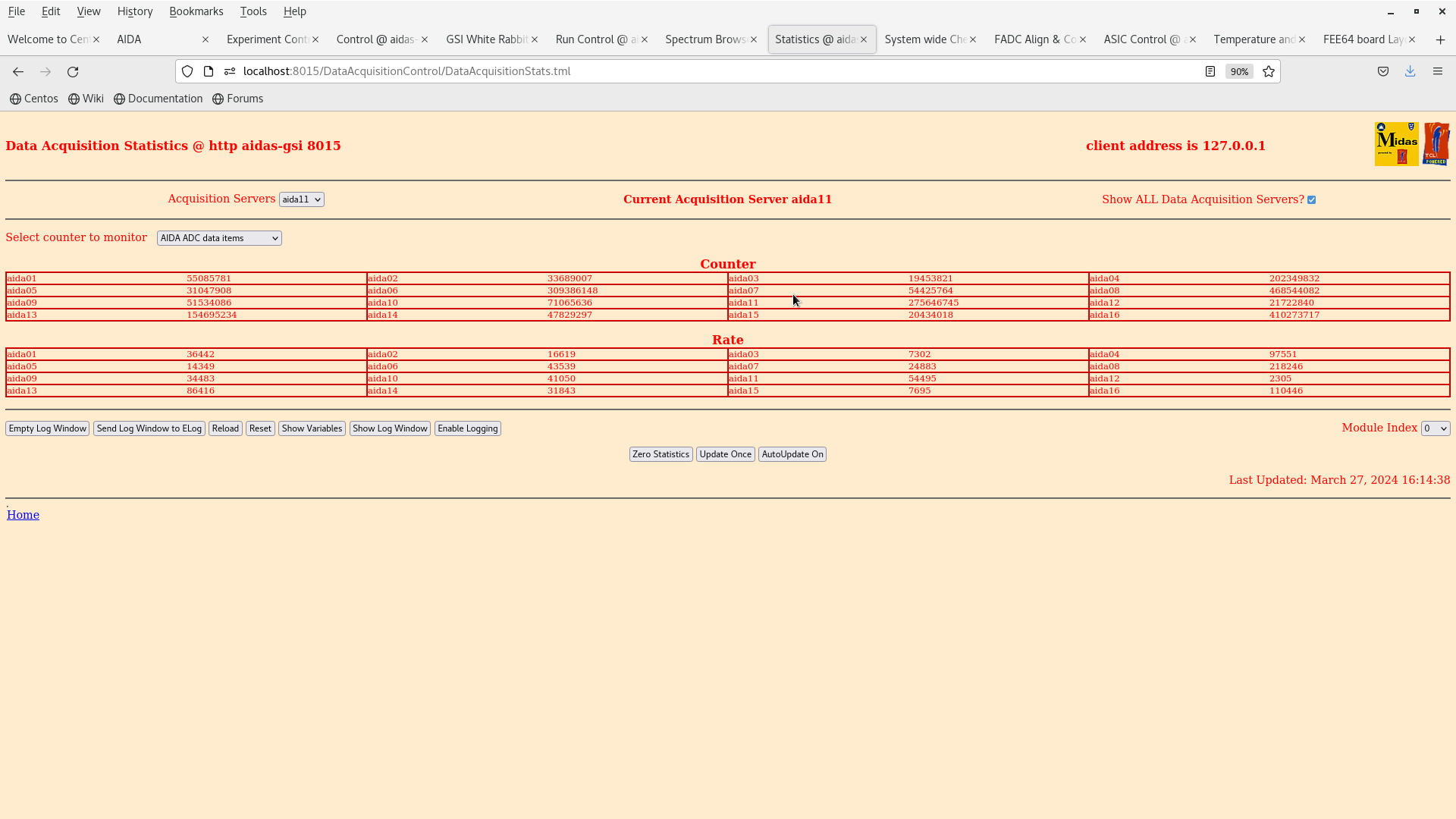

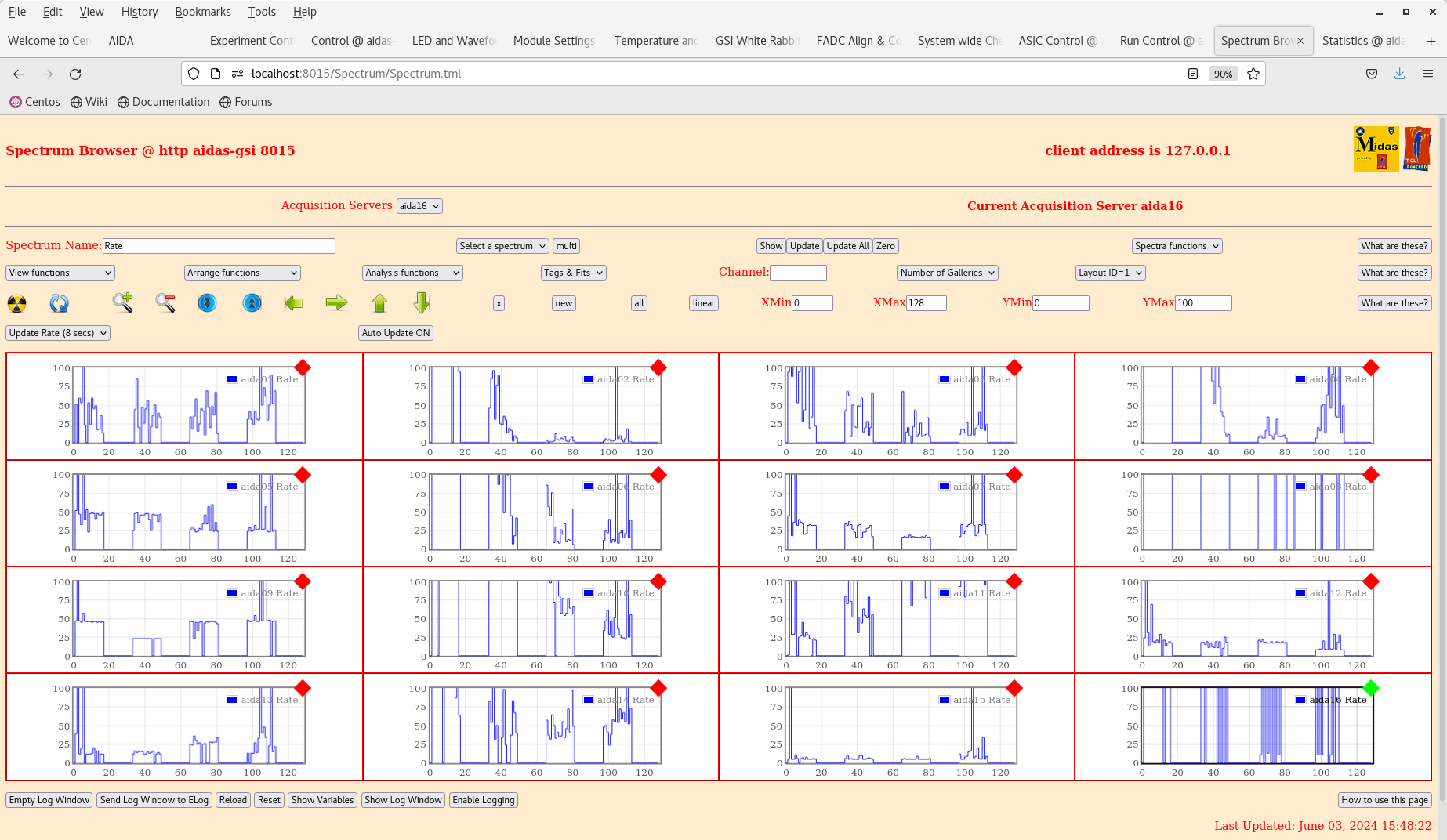

Stats good elog:254/6

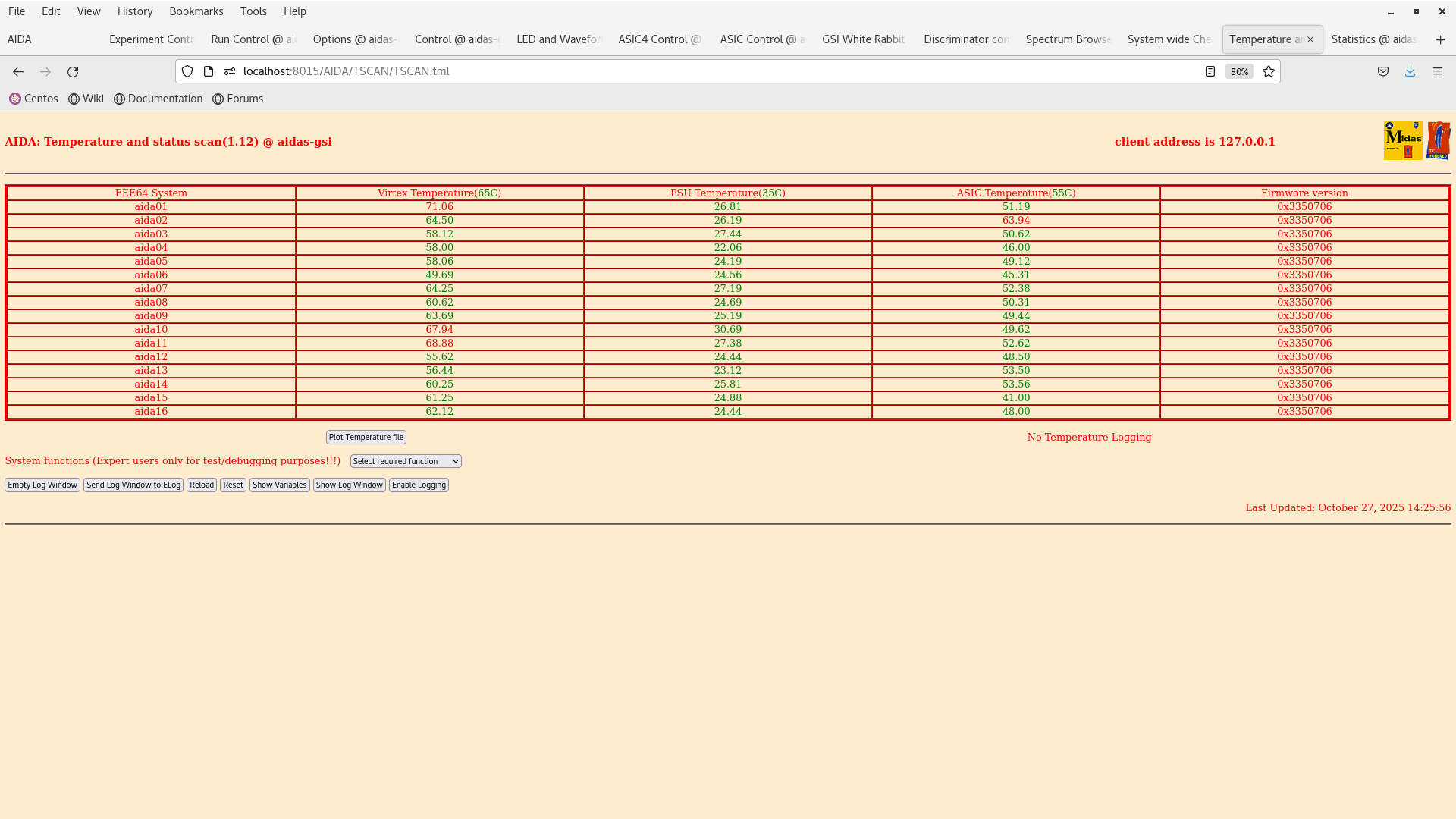

Temps good elog:254/7 aida01 had been high during reboot issue, >70, but now is back down

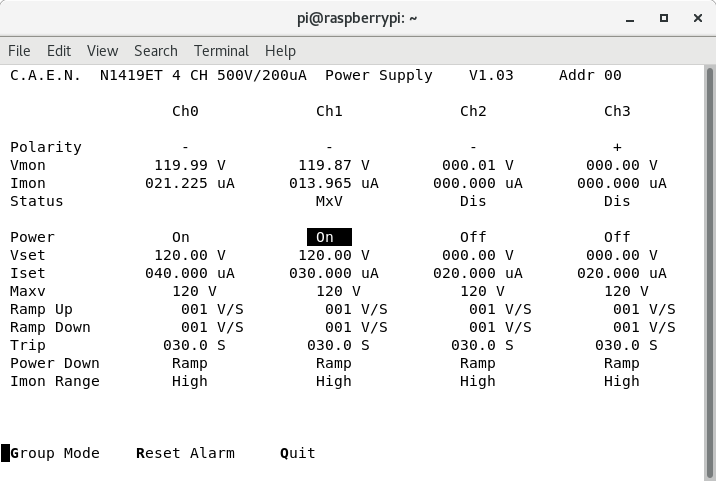

Current ok elog:254/8

ucesb ok

23:25

DB No faults.

Stats good

Temps good

ucesb ok

23:42 No Beam

23:48 Beam Back

23:57

DB No faults.

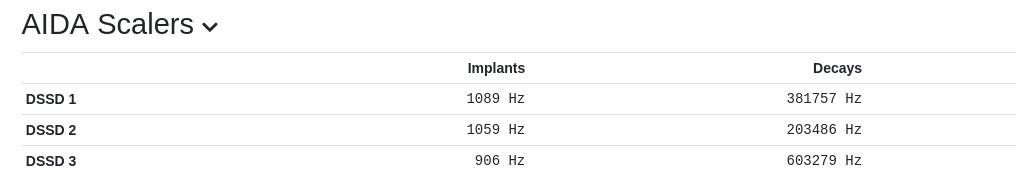

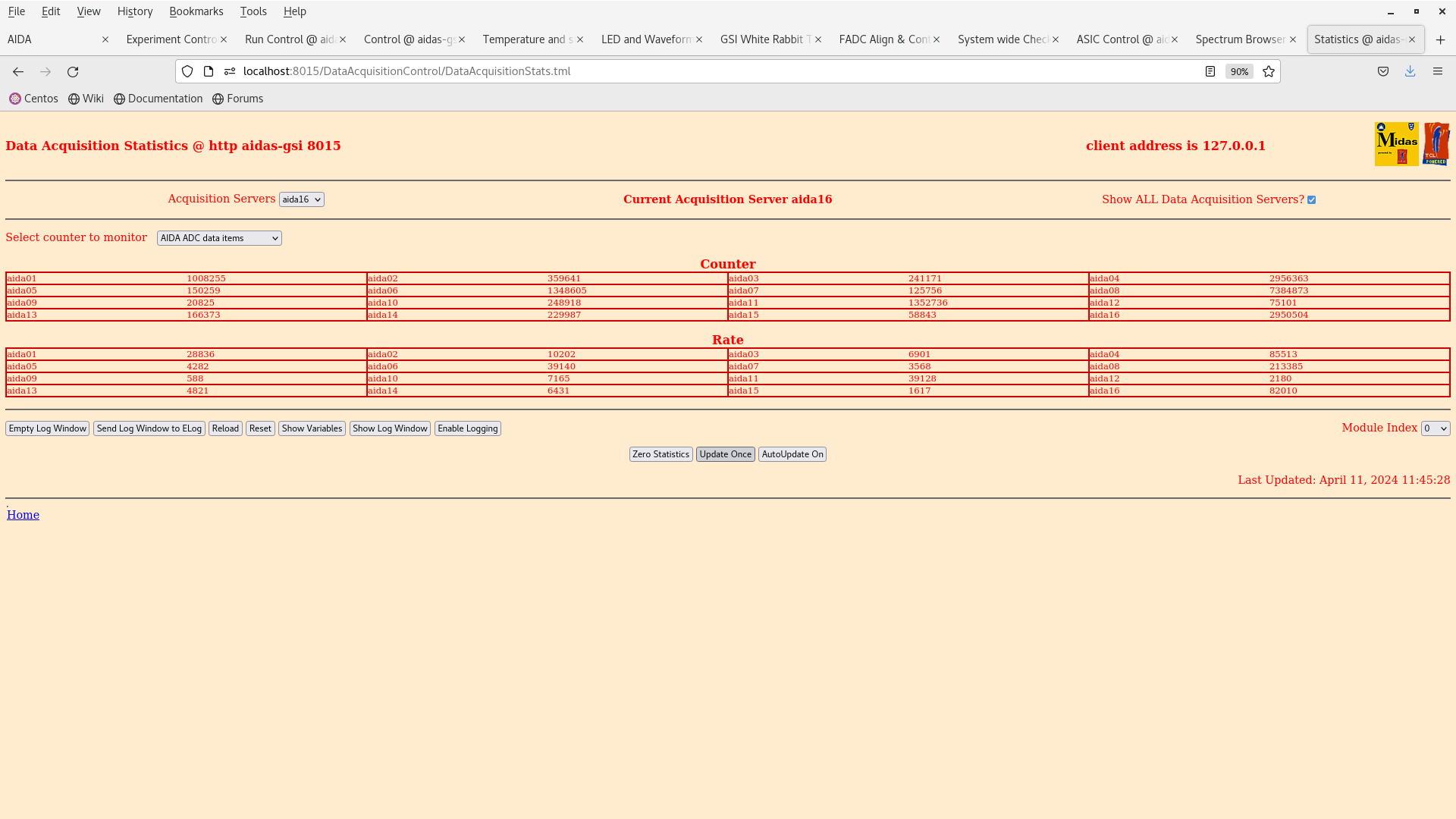

Stats good elog:254/11

Temps good elog:254/12

ucesb ok elog:254/9

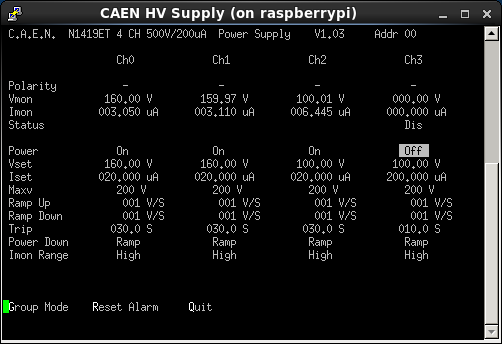

Current ok elog:254/10

Clock status test result: Passed 12, Failed 0

Calibration test result: Passed 12, Failed 0

White Rabbit error counter test result: Passed 12, Failed 0

*FPGA check page error*

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 27 9 5 2 1 2 1 4 2 3 7 : 39812

aida02 : 13 9 5 2 2 2 1 4 2 3 7 : 39820

aida03 : 21 8 3 2 2 2 1 4 2 3 7 : 39812

aida04 : 13 4 3 1 1 5 2 3 2 3 7 : 39780

aida05 : 24 5 3 2 2 4 2 3 2 3 7 : 39800

aida06 : 16 5 5 2 2 2 1 4 2 3 7 : 39800

aida07 : 22 6 2 2 1 3 1 4 2 3 7 : 39848

aida08 : 21 8 2 3 2 2 1 4 2 3 7 : 39828

aida09 : 18 7 1 1 3 4 2 3 2 3 7 : 39792

aida10 : 19 3 3 1 0 3 2 3 2 3 7 : 39476

aida11 : 17 4 4 0 1 3 2 3 2 3 7 : 39524

aida12 : 13 4 3 2 3 1 2 3 2 3 7 : 39428

00:04 Handing over to Corrigan |

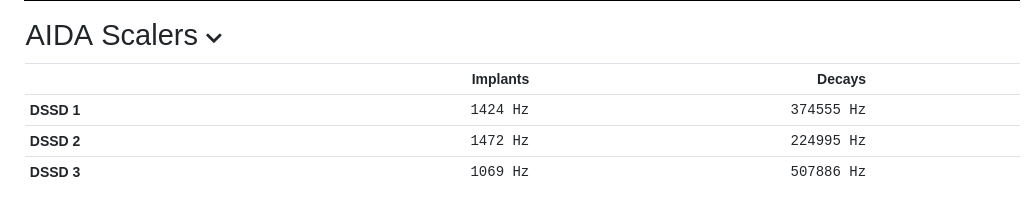

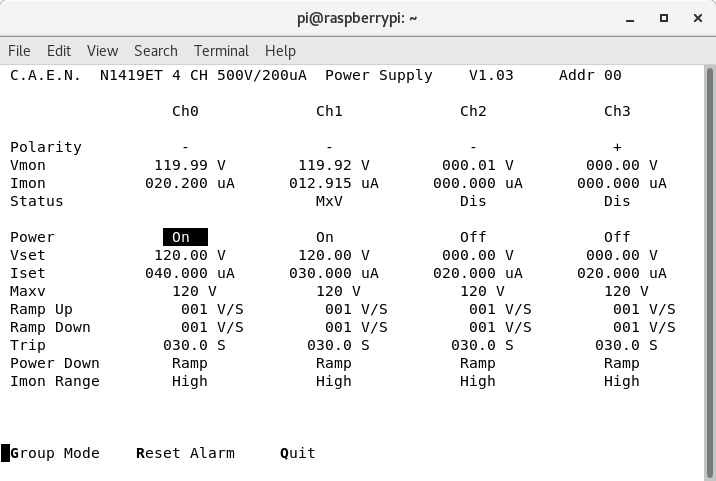

| Attachment 1: 40.png

|

|

| Attachment 2: 41.png

|

|

| Attachment 3: Screenshot_2021-04-20_Statistics_aidas-gsi(3).png

|

.png.png)

|

| Attachment 4: Screenshot_2021-04-20_Temperature_and_status_scan_aidas-gsi(3).png

|

.png.png)

|

| Attachment 5: Screenshot_2021-04-20_Statistics_aidas-gsi(4).png

|

.png.png)

|

| Attachment 6: Screenshot_2021-04-20_Statistics_aidas-gsi(5).png

|

.png.png)

|

| Attachment 7: Screenshot_2021-04-20_Temperature_and_status_scan_aidas-gsi(4).png

|

.png.png)

|

| Attachment 8: 42.png

|

|

| Attachment 9: 44.png

|

|

| Attachment 10: 45.png

|

|

| Attachment 11: Screenshot_2021-04-20_Statistics_aidas-gsi(6).png

|

.png.png)

|

| Attachment 12: Screenshot_2021-04-20_Temperature_and_status_scan_aidas-gsi(5).png

|

.png.png)

|

|

261

|

Thu Apr 22 11:03:57 2021 |

JS | Thursday 22nd April: 12:00-16:00 |

12:00 Taking over from Liam, all is well.

12:10 Beam dropped out for a minute, implantation rate is down a bit, peaking around 300 Hz

12:19 Beam stopped (from GSI log "Run stopped because of a call from HKR stating they have a problematic device which they

need to check and will need apprx. 15 min.")

12:30

ucesb ok (no beam)

DB No faults

Stats ok.

12:34 In order to fix some ongoing FRS problem no beam expected for at least an hour.

13:00

We are taking intermittent beam while they work on the FRS

DB No faults

ucesb ok elog:261/1

Current ok elog:261/2

Stats ok elog:261/3

Temps ok elog:261/4

Clock status test result: Passed 12, Failed 0

Calibration test result: Passed 12, Failed 0

White Rabbit error counter test result: Passed 12, Failed 0

Base Current Difference

aida12 fault 0x0 : 0x46 : 70

FPGA Timestamp error counter test result: Passed 11, Failed 1

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 15 6 5 3 2 2 2 3 2 3 7 : 39580

aida02 : 21 7 4 2 2 3 2 3 2 3 7 : 39692

aida03 : 20 10 3 3 0 3 2 3 2 3 7 : 39600

aida04 : 8 7 4 5 2 4 3 2 2 3 7 : 39608

aida05 : 17 14 1 2 3 3 4 2 2 3 7 : 39748

aida06 : 17 10 2 3 2 2 4 2 2 3 7 : 39572

aida07 : 27 10 8 7 2 3 3 2 2 3 7 : 39708

aida08 : 9 6 2 3 2 1 3 3 2 3 7 : 39636

aida09 : 1 2 1 4 0 3 3 2 2 3 7 : 39204

aida10 : 5 8 4 4 2 2 1 3 2 3 7 : 39316

aida11 : 6 4 5 3 2 3 2 2 2 3 7 : 39144

aida12 : 15 5 8 1 0 4 1 3 2 3 7 : 39428

13:32

ucesb ok

DB No faults

Stats ok

14:01

ucesb ok

DB No faults

Stats ok

14.30 analysis of file /TapeData/S460/R50_528 - attachment 5

cat /var/log/messages | grep /MIDAS - attachments 6 & 7

Grafana DSSSD bias & leakage currents for last 7 days - attachment 8

14:55

DB No faults

ucesb ok

Current ok elog:261/9

Stats ok elog:261/10

Temps ok elog:261/11

FPGA Timestamp Check Error:

Base Current Difference

aida12 fault 0x0 : 0x4d : 77

FPGA Timestamp error counter test result: Passed 11, Failed 1

15:30

ucesb ok

DB No faults

Stats ok

15:59

ucesb ok elog:261/12

DB No faults

Stats ok |

| Attachment 1: 51.png

|

|

| Attachment 2: 52.png

|

|

| Attachment 3: Screenshot_2021-04-22_Statistics_aidas-gsi(2).png

|

.png.png)

|

| Attachment 4: Screenshot_2021-04-22_Temperature_and_status_scan_aidas-gsi(2).png

|

.png.png)

|

| Attachment 5: R50_528

|

*** TDR format 3.3.0 analyser - TD - January 2019

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 256073749 ( 1415213.2 Hz)

Other data format: 5846251 ( 32309.8 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 32674 ( 180.6 Hz)

WR48-63: 32674 ( 180.6 Hz)

FEE64 disc: 1081787 ( 5978.6 Hz)

MBS info: 4699116 ( 25970.1 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 342915 ( 1895.1 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 180.944 s

FEE elapsed dead time(s) elapsed idle time(s)

1 0.000 53.074

2 0.000 66.167

3 0.000 47.044

4 0.000 162.945

5 0.000 122.260

6 0.000 104.653

7 0.000 108.241

8 0.000 75.998

9 0.000 7.078

10 0.000 27.522

11 0.000 39.393

12 0.000 0.000

13 0.000 0.000

14 0.000 0.000

15 0.000 0.000

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 18754736 101009 0 0 0 0 2455 2455 95016 1083 0 35321

1 22221860 61355 0 0 0 0 2741 2741 55873 0 0 20378

2 16643754 1970924 0 0 0 0 2367 2367 197444 1768746 0 33880

3 21495935 1857330 0 0 0 0 2886 2886 82623 1768935 0 33490

4 3525133 403992 0 0 0 0 456 456 99315 303765 0 35967

5 10189380 355501 0 0 0 0 1262 1262 56604 296373 0 20229

6 12085720 387518 0 0 0 0 1592 1592 108226 276108 0 33721

7 11376753 370078 0 0 0 0 1497 1497 82978 284106 0 32056

8 43639711 66166 0 0 0 0 5406 5406 55354 0 0 18854

9 42033424 67528 0 0 0 0 5337 5337 56854 0 0 18886

10 29147293 115191 0 0 0 0 3615 3615 107961 0 0 31625

11 24960050 89659 0 0 0 0 3060 3060 83539 0 0 28508

12 0 0 0 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time:52321.719s ( 0.612 blocks/s, 0.038 Mb/s)

|

| Attachment 6: log2

|

Apr 13 17:43:23 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:43:31 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:43:32 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:43:34 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:43:38 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:43:39 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:43:40 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:43:42 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:44:56 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:44:56 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:44:58 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 13 17:45:01 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 16 00:58:32 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 16 00:58:32 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 16 00:58:34 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 16 00:58:34 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 16 00:58:34 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 16 00:58:35 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 16 00:58:42 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 16 00:58:50 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:10:30 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:10:31 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:10:35 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:10:38 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:10:38 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:10:39 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:10:39 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:10:43 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:11:08 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:11:09 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:11:10 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:11:12 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 17 06:33:31 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:857 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

|

| Attachment 7: log1

|

Apr 19 08:33:03 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:13:33 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:13:36 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:13:37 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:13:38 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:13:40 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:13:42 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:13:46 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:13:56 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:14:48 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:14:48 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:14:50 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:14:51 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:29:49 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:29:49 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:29:51 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:29:52 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:29:53 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:29:53 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:30:00 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:31:16 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:31:17 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:31:17 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:31:17 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 09:33:24 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:857 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:27:23 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:27:24 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:27:24 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:27:26 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:27:27 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:27:30 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:27:30 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:27:32 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:28:43 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:28:45 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:28:45 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 19 10:28:46 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:01:09 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:01:09 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:01:10 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:01:10 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:01:10 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:01:11 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:01:30 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:02:39 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:02:39 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:02:41 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:02:42 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:04:32 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:05:44 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:05:49 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:05:49 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:05:49 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:05:50 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:05:52 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:05:55 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 00:05:57 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:10:52 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:18:01 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:18:05 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:18:06 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:18:10 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:18:13 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:18:19 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:18:19 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:18:23 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:18:25 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:18:26 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:21:20 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 08:21:23 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:23 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:28 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:31 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:34 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:35 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:39 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:39 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:39 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:39 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:41 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:47:44 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 10:50:35 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:08:07 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:857 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:31 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:33 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:33 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:41 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:41 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:42 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:42 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:46 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:49 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:49 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:30:55 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 11:33:56 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:857 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:07:57 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:34:17 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:34:23 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:34:23 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:34:23 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:34:24 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:34:25 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:34:31 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:34:31 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:35:30 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:35:32 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:35:33 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 20 22:35:35 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:20 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.5:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:20 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.3:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:21 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.4:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:22 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.8:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:23 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.1:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:28 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.6:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:47 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.7:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:49 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.9:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:50 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.12:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:50 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.10:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:36:52 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.11:862 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

Apr 21 01:40:07 aidas-gsi rpc.mountd[4497]: authenticated mount request from 192.168.11.2:857 for /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119 (/home/npg/MIDAS_Releases/23Jan19/MIDAS_200119)

|

| Attachment 8: Screenshot_2021-04-22_AIDA_Alerting_-_Grafana.png

|

|

| Attachment 9: 53.png

|

|

| Attachment 10: Screenshot_2021-04-22_Statistics_aidas-gsi(3).png

|

.png.png)

|

| Attachment 11: Screenshot_2021-04-22_Temperature_and_status_scan_aidas-gsi(3).png

|

.png.png)

|

| Attachment 12: 54.png

|

|

|

309

|

Wed May 12 18:53:38 2021 |

JS | Wed 12 20:00-00:00 |

19:51 Shift change

Stats ok

ucesb ok, Max implants ~1500 Hz

20:30

Stats ok

ucesb ok, Max implants ~1000 Hz

current ok (maybe leveling out)

20:51

The online people are starting a new sort and are going to change some things with degraders I think. We are on R1_340.

20:59

Check

Clock status test result: Passed 16, Failed 0

Calibration test result: Passed 16, Failed 0

WR:

Base Current Difference

aida05 fault 0x36ca : 0x36ce : 4

White Rabbit error counter test result: Passed 15, Failed 1

FPGA time:

Base Current Difference

aida13 fault 0xa : 0xb6 : 172

FPGA Timestamp error counter test result: Passed 15, Failed 1

--- both errors above same module as earlier shift

Returned 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 1 3 2 0 1 3 3 2 3 3 6 : 36092

aida02 : 6 4 4 2 2 3 1 3 3 3 6 : 36280

aida03 : 6 3 2 0 0 3 3 2 3 3 6 : 36048

aida04 : 10 3 1 1 3 3 1 3 3 3 6 : 36272

aida05 : 19 8 2 0 2 3 1 3 3 3 6 : 36268

aida06 : 2 2 0 2 3 4 2 2 3 3 6 : 36120

aida07 : 6 7 3 0 3 4 3 2 3 3 6 : 36416

aida08 : 7 5 4 0 3 2 2 3 3 3 6 : 36420

aida09 : 21 6 3 2 2 4 2 3 2 3 6 : 35700

aida10 : 13 3 1 1 3 3 1 4 2 3 6 : 35772

aida11 : 25 6 4 2 1 4 2 4 2 3 6 : 36180

aida12 : 0 4 0 3 2 3 3 3 2 3 6 : 35712

aida13 : 18 5 2 3 2 3 2 4 2 3 6 : 36080

aida14 : 2 1 1 1 2 3 2 4 2 3 6 : 35904

aida15 : 0 1 1 3 0 4 2 2 3 3 6 : 35960

aida16 : 4 5 3 2 3 4 1 3 2 3 6 : 35432

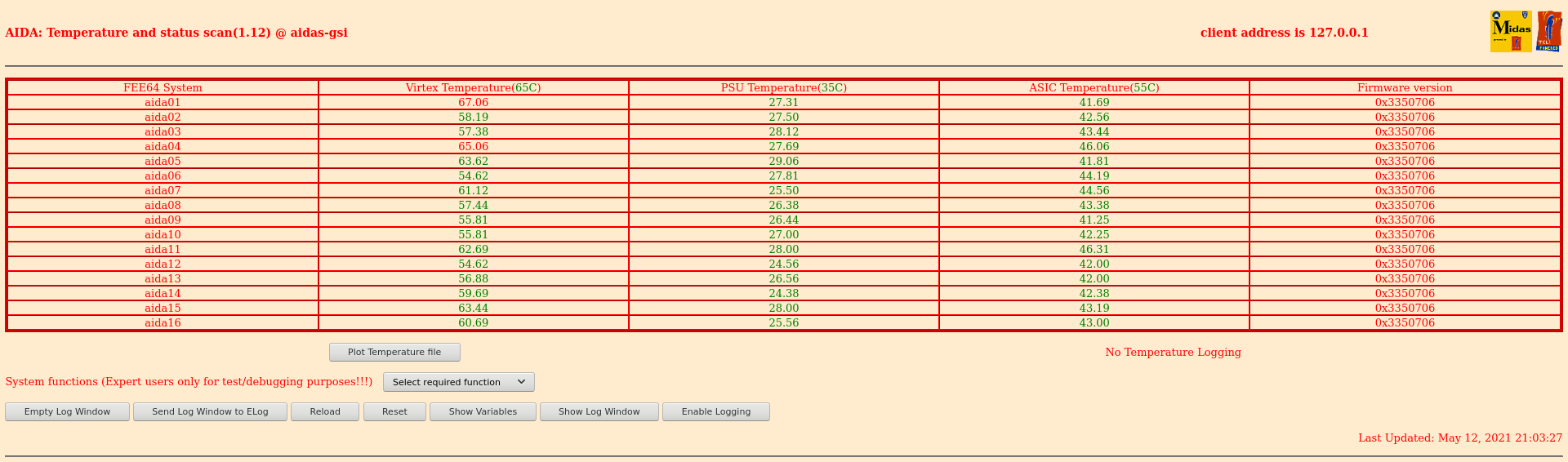

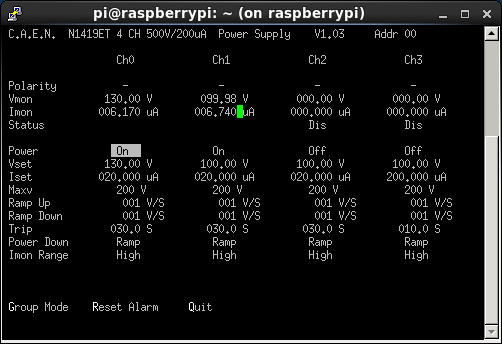

ucesb ok elog:309/1

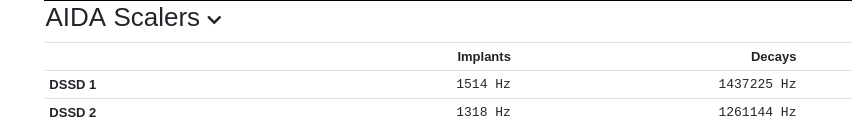

current ok elog:309/2

Stats ok elog:309/3

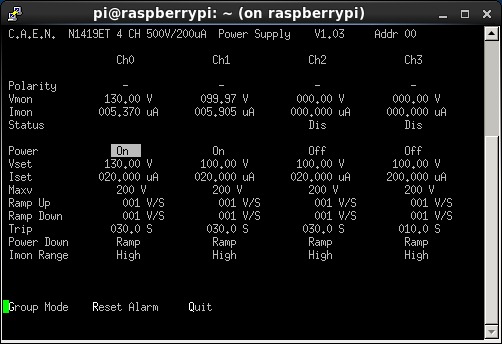

temps ok elog:309/4

21:36

ucesb ok

Stats ok

22:01

ucesb ok 1500 Hz peak implant

Stats ok

temps ok

bias ok - earlier rise seems to have stopped, 0.2uA fluctuations on values.

22:20 Nic noted that they were seeing fewer y-strips events (x agreed with FRS rate).

Dead time was suggested as a problem. Oscar investigating, good event rate in midas doesn't show significant dead time.

Looking at the difference in FEEs3 & 4, which should have the same scaler rate but don't, suggestion data lost in the pause and resume.

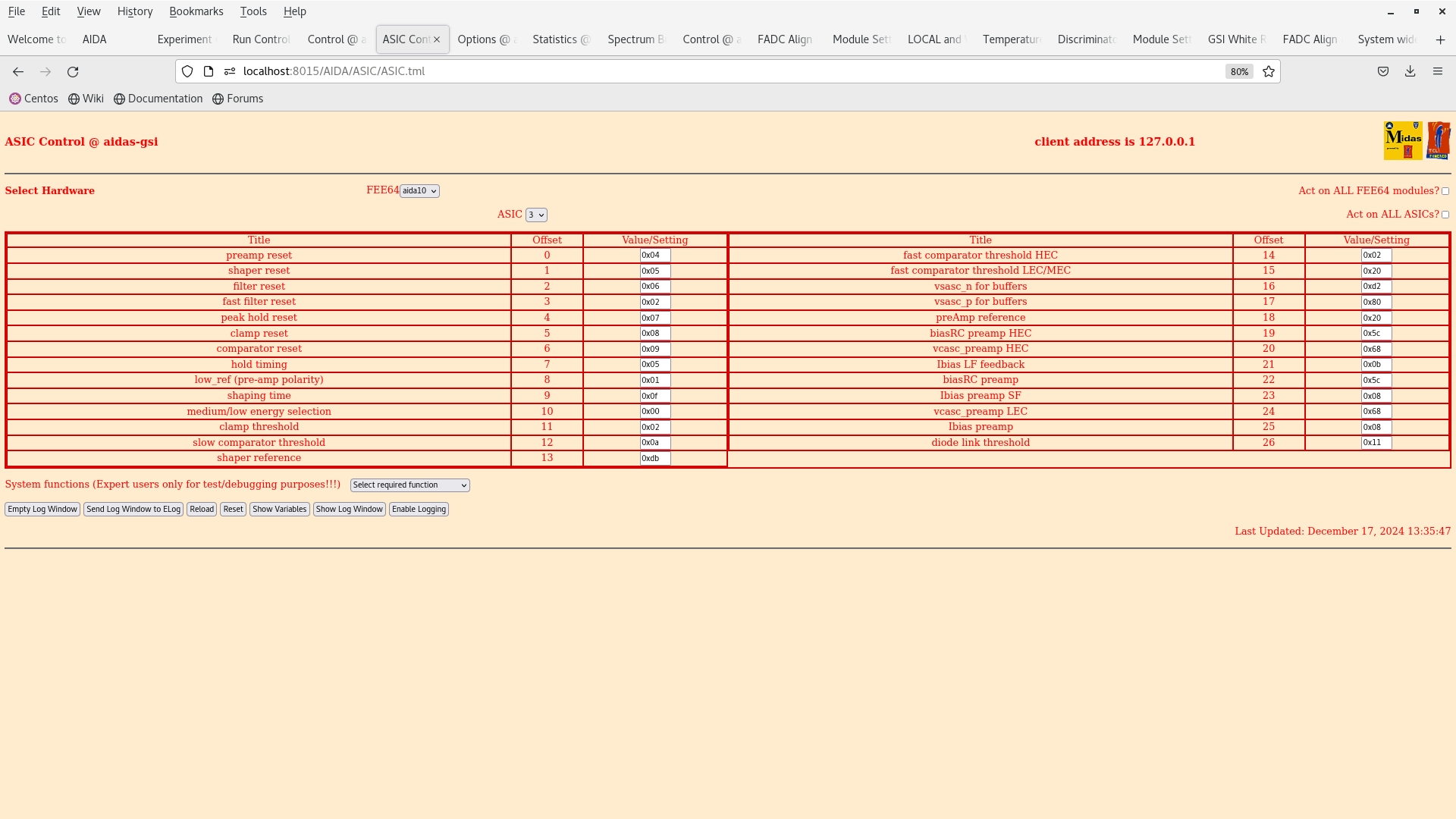

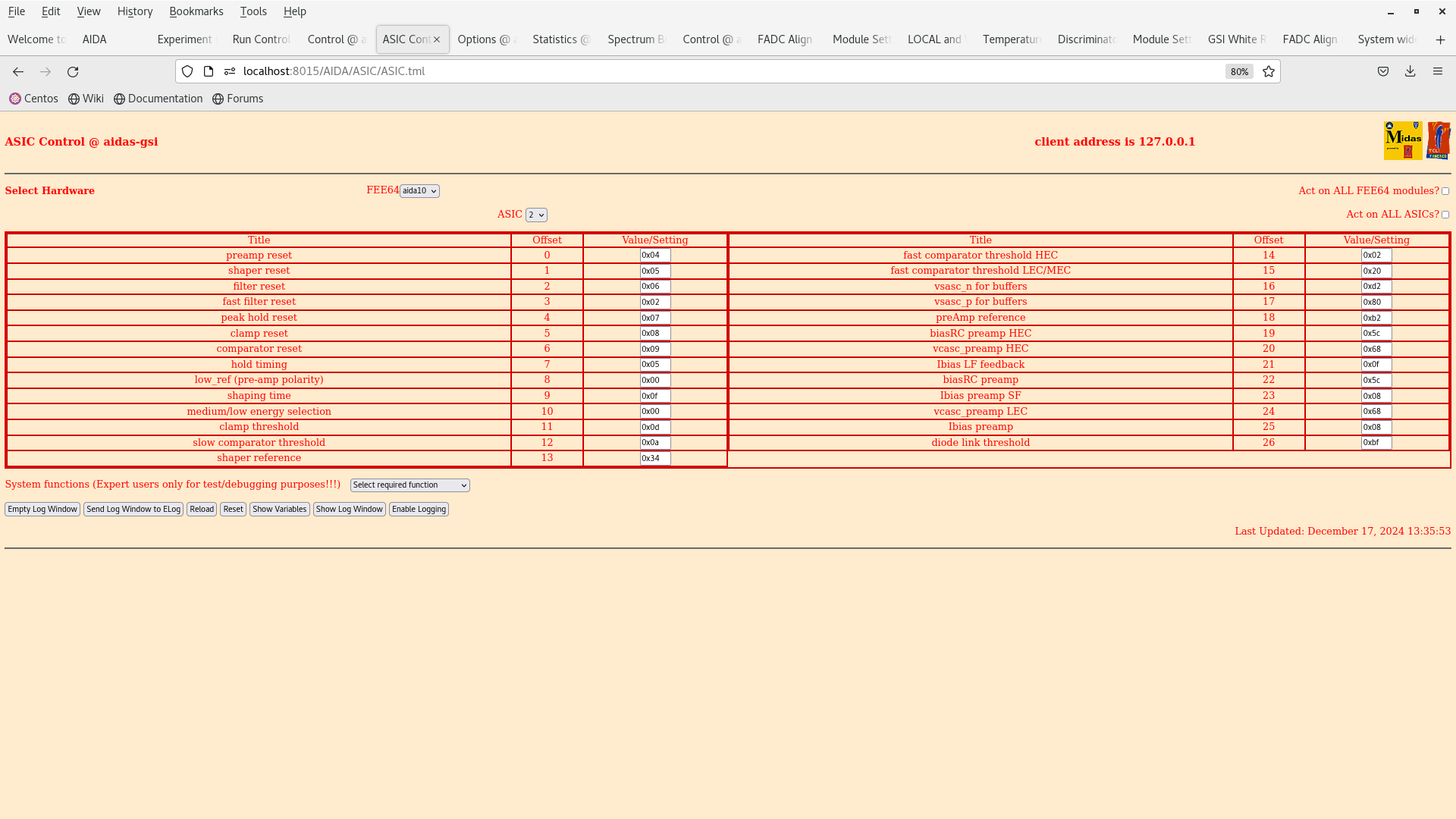

Oscar is going to raise the threshold on one of the y FEEs as a test

Increased aida4 slow comparator threshold changed

There is some confusion as it seems to be dead time but apart rates shown look low enough, dead time is possibly masking true rate?

Results of test, need thresholds 100keV on p+n and 320keV n+n to get a roughly 1:1 between FEE3 and FEE4 scaler

23:40 FRS magnet issue, possibly power, no beam

00:03 bias ok elog:309/5 has come down because no beam

handing over to muneerah |

| Attachment 1: ucesb.png

|

|

| Attachment 2: bias1.png

|

|

| Attachment 3: Screenshot_2021-05-12_Statistics_aidas-gsi.png

|

|

| Attachment 4: Screenshot_2021-05-12_Temperature_and_status_scan_aidas-gsi.png

|

|

| Attachment 5: bias2.png

|

|

|

319

|

Fri May 14 19:01:09 2021 |

JS | Friday 14th May 20:00-00:00 |

20:00 Taking over from CB

20:33 Doing full checks.

Temps ok elog:319/8

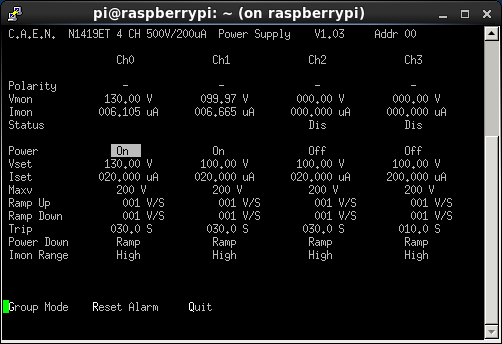

Bias ok elog:319/1

Clock check - ok

ADC Calc check - ok

White Rabbit -

Base Current Difference

aida01 fault 0xf932 : 0xf934 : 2

aida02 fault 0x62ec : 0x62ee : 2

aida03 fault 0x8679 : 0x867b : 2

aida04 fault 0xf0e4 : 0xf0e6 : 2

aida05 fault 0x9db8 : 0x9dc5 : 13

aida06 fault 0x7f18 : 0x7f1a : 2

aida07 fault 0xdd2c : 0xdd2e : 2

aida08 fault 0x1557 : 0x1559 : 2

White Rabbit error counter test result: Passed 8, Failed 8

FPGA Timestamp errors -

Base Current Difference

aida05 fault 0x0 : 0x3 : 3

FPGA Timestamp error counter test result: Passed 15, Failed 1

Memory Info-

Returned 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 35 34 30 8 1 4 1 2 2 3 6 : 35772

aida02 : 37 30 28 5 3 1 2 4 2 3 6 : 36644

aida03 : 41 29 30 16 4 3 1 5 1 3 6 : 36588

aida04 : 13 6 23 12 4 4 4 4 2 2 6 : 35412

aida05 : 20 32 23 10 2 2 2 2 1 4 6 : 36736

aida06 : 14 5 10 5 1 3 2 3 2 3 6 : 35680

aida07 : 44 23 22 9 4 3 1 3 2 3 6 : 36200

aida08 : 39 30 28 9 0 3 2 3 3 2 6 : 35308

aida09 : 41 31 28 10 2 5 1 3 1 3 6 : 35484

aida10 : 43 23 27 7 3 1 1 3 3 3 6 : 36916

aida11 : 39 35 17 10 3 3 2 2 2 3 6 : 35908

aida12 : 37 36 15 10 2 2 2 4 3 2 6 : 35684

aida13 : 47 32 17 7 4 2 3 4 3 2 6 : 36012

aida14 : 23 33 14 10 3 4 3 4 3 2 6 : 36164

aida15 : 44 28 24 12 3 2 4 3 3 2 6 : 35920

aida16 : 22 17 24 17 3 4 2 3 1 3 6 : 35648

Stats

Aida Correlation Info #8 - elog:319/2 same as elog:317/27

Resume info #3 - elog:319/3 same as elog:317/26

Pause info #2 - elog:319/4 same as elog:317/32

AIDA disk info #6 - elog:319/5 same as elog:317/31

AIDA ADC data items - elog:319/6 same as elog:317/30

Good Events - elog:319/7 same as elog:317/29

[I had some artifacts in AnyDesk when looking at the stats pages with many zeros, but could see

clearly once uploaded the screenshots]

Analysis R5_108 elog:319/9

Pause 149 Resume 150

Highest deadtime FEE10 3%

21:01

ucesb ok - Max 1700 Hz Implant - 1MHz Decay

21:35

Temps ok

Bias ok

Clock check - ok

ADC Calc check - ok

White Rabbit -

Base Current Difference

aida01 fault 0xf932 : 0xf934 : 2

aida02 fault 0x62ec : 0x62ee : 2

aida03 fault 0x8679 : 0x867b : 2

aida04 fault 0xf0e4 : 0xf0e6 : 2

aida05 fault 0x9db8 : 0x9dc5 : 13

aida06 fault 0x7f18 : 0x7f1a : 2

aida07 fault 0xdd2c : 0xdd2e : 2

aida08 fault 0x1557 : 0x1559 : 2

White Rabbit error counter test result: Passed 8, Failed 8

Base Current Difference

aida05 fault 0x0 : 0x3 : 3

FPGA Timestamp error counter test result: Passed 15, Failed 1

Returned 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 39 34 29 8 1 4 1 2 2 3 6 : 35772

aida02 : 46 29 28 5 3 2 2 3 2 3 6 : 36288

aida03 : 39 25 29 16 4 2 2 5 1 3 6 : 36660

aida04 : 14 6 19 12 4 4 3 4 2 2 6 : 35096

aida05 : 20 30 24 10 2 2 2 2 1 4 6 : 36736

aida06 : 26 4 11 5 2 4 3 2 2 3 6 : 35672

aida07 : 46 22 22 9 4 3 1 3 2 3 6 : 36200

aida08 : 28 32 28 9 0 2 2 4 3 2 6 : 35664

aida09 : 32 30 29 10 3 5 2 3 1 3 6 : 35776

aida10 : 39 23 25 7 3 1 1 3 3 3 6 : 36868

aida11 : 40 31 21 10 3 3 1 4 1 3 6 : 35688

aida12 : 17 31 12 10 2 2 3 4 3 2 6 : 35772

aida13 : 35 28 22 7 4 2 3 4 3 2 6 : 36012

aida14 : 30 33 14 10 3 4 3 4 3 2 6 : 36192

aida15 : 34 26 24 12 3 2 4 3 3 2 6 : 35864

aida16 : 38 24 27 17 3 4 2 3 1 3 6 : 35816

Stats

Good Events - elog:319/10

AIDA ADC data items - elog:319/11

AIDA disk info #6 - elog:319/12

Pause info #2 - elog:319/13

Resume info #3 - elog:319/14

Aida Correlation Info #8 - elog:319/15 - rates showed zero, checked again and normal elog:319/17

Analysis R5_128 elog:319/16

Pause 167 Resume 166

Highest deadtime FEE10 5%

22:00

Temps ok

Stats ok

ucesb ok

22:35

Temps ok

Stats ok

ucesb- DSSD 2 is reading consistently 30% lower, not sure if this is dead time issue cropping up

again elog:319/17

22:54 They are closing the file, we are on R5_155

23:00 |

| Attachment 1: bias1.png

|

|

| Attachment 2: Screenshot_2021-05-14_Statistics_aidas-gsi(10).png

|

.png.png)

|

| Attachment 3: Screenshot_2021-05-14_Statistics_aidas-gsi(9).png

|

.png.png)

|

| Attachment 4: Screenshot_2021-05-14_Statistics_aidas-gsi(8).png

|

.png.png)

|

| Attachment 5: Screenshot_2021-05-14_Statistics_aidas-gsi(7).png

|

.png.png)

|

| Attachment 6: Screenshot_2021-05-14_Statistics_aidas-gsi(6).png

|

.png.png)

|

| Attachment 7: Screenshot_2021-05-14_Statistics_aidas-gsi(5).png

|

.png.png)

|

| Attachment 8: Screenshot_2021-05-14_Temperature_and_status_scan_aidas-gsi(1).png

|

.png.png)

|

| Attachment 9: R5_108_analysis.txt

|

*** TDR format 3.3.0 analyser - TD - January 2019

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 256861958 ( 1503007.9 Hz)

Other data format: 5058042 ( 29596.7 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 149 ( 0.9 Hz)

RESUME: 150 ( 0.9 Hz)

SYNC100: 32636 ( 191.0 Hz)

WR48-63: 32636 ( 191.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 4992471 ( 29213.1 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 207149 ( 1212.1 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 170.899 s

FEE elapsed dead time(s) elapsed idle time(s)

1 4.459 72.353

2 1.217 86.117

3 3.357 28.177

4 0.000 160.970

5 0.495 76.386

6 0.216 93.617

7 1.418 40.259

8 3.253 44.571

9 0.000 168.837

10 5.250 9.058

11 1.956 49.014

12 0.182 82.483

13 0.000 160.585

14 0.143 88.740

15 3.053 35.456

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 8464368 3303 0 0 2 2 1138 1138 0 1023 0 11424

1 16399642 4233 0 0 17 18 2099 2099 0 0 0 22505

2 13045073 1576129 0 0 6 6 1793 1793 0 1572531 0 18179

3 26563169 1558422 0 0 14 14 3487 3487 0 1551420 0 26353

4 2213090 510296 0 0 0 0 328 328 0 509640 0 5100

5 15498485 314714 0 0 4 4 1986 1986 0 310734 0 15610

6 12553775 609520 0 0 7 7 1573 1573 0 606360 0 10360

7 23384876 446841 0 0 10 10 3029 3029 0 440763 0 18175

8 21832531 5542 0 0 15 15 2756 2756 0 0 0 22662

9 1045474 278 0 0 0 0 139 139 0 0 0 1866

10 42357744 10552 0 0 43 43 5233 5233 0 0 0 12639

11 20606319 4998 0 0 11 11 2488 2488 0 0 0 4351

12 14311836 3576 0 0 6 6 1782 1782 0 0 0 20348

13 3016503 780 0 0 0 0 390 390 0 0 0 1508

14 13047482 3248 0 0 4 4 1620 1620 0 0 0 12826

15 22521591 5610 0 0 10 10 2795 2795 0 0 0 3243

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time:74697.445s ( 0.428 blocks/s, 0.027 Mb/s)

|

| Attachment 10: Screenshot_2021-05-14_Statistics_aidas-gsi(16).png

|

.png.png)

|

| Attachment 11: Screenshot_2021-05-14_Statistics_aidas-gsi(15).png

|

.png.png)

|

| Attachment 12: Screenshot_2021-05-14_Statistics_aidas-gsi(14).png

|

.png.png)

|

| Attachment 13: Screenshot_2021-05-14_Statistics_aidas-gsi(13).png

|

.png.png)

|

| Attachment 14: Screenshot_2021-05-14_Statistics_aidas-gsi(12).png

|

.png.png)

|

| Attachment 15: Screenshot_2021-05-14_Statistics_aidas-gsi(11).png

|

.png.png)

|

| Attachment 16: R5_128_analysis.txt

|

*** TDR format 3.3.0 analyser - TD - January 2019

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 256841478 ( 1482693.9 Hz)

Other data format: 5078522 ( 29317.3 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 167 ( 1.0 Hz)

RESUME: 166 ( 1.0 Hz)

SYNC100: 32644 ( 188.4 Hz)

WR48-63: 32644 ( 188.4 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 5012901 ( 28938.5 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 205165 ( 1184.4 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 173.226 s

FEE elapsed dead time(s) elapsed idle time(s)

1 2.621 76.080

2 1.556 81.876

3 3.719 27.628

4 0.000 162.954

5 0.710 80.266

6 0.170 93.769

7 2.714 44.740

8 3.483 45.565

9 0.000 167.005

10 8.522 10.948

11 2.181 50.562

12 0.202 85.035

13 0.000 161.510

14 0.146 88.959

15 1.812 38.597

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 8468806 3273 0 0 7 7 1112 1112 0 1035 0 11260

1 16364560 4360 0 0 13 13 2167 2167 0 0 0 23505

2 13265609 1594590 0 0 6 6 1881 1881 0 1590816 0 18254

3 26054686 1576337 0 0 14 14 3422 3422 0 1569465 0 26152

4 2223261 507850 0 0 0 0 362 362 0 507126 0 4952

5 15152054 312213 0 0 8 7 1938 1938 0 308322 0 15336

6 12659379 606961 0 0 4 4 1612 1612 0 603729 0 10099

7 22669666 438118 0 0 14 14 2841 2841 0 432408 0 17594

8 22337729 5564 0 0 15 15 2767 2767 0 0 0 22524

9 1020352 240 0 0 0 0 120 120 0 0 0 1807

10 42596491 10676 0 0 59 59 5279 5279 0 0 0 12076

11 20672887 5060 0 0 13 13 2517 2517 0 0 0 4379

12 14335521 3608 0 0 5 5 1799 1799 0 0 0 20105

13 2812573 690 0 0 0 0 345 345 0 0 0 1405

14 13325633 3260 0 0 4 4 1626 1626 0 0 0 12554

15 22882271 5722 0 0 5 5 2856 2856 0 0 0 3163

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time:78055.344s ( 0.410 blocks/s, 0.026 Mb/s)

|

| Attachment 17: Screenshot_2021-05-14_Statistics_aidas-gsi(17).png

|

.png.png)

|

| Attachment 18: ucesb.png

|

|

| Attachment 19: _~.png

|

|

| Attachment 20: Screenshot_2021-05-14_Temperature_and_status_scan_aidas-gsi(2).png

|

.png.png)

|

| Attachment 21: Screenshot_2021-05-14_Statistics_aidas-gsi(23).png

|

.png.png)

|

| Attachment 22: Screenshot_2021-05-14_Statistics_aidas-gsi(22).png

|

.png.png)

|

| Attachment 23: Screenshot_2021-05-14_Statistics_aidas-gsi(21).png

|

.png.png)

|

| Attachment 24: Screenshot_2021-05-14_Statistics_aidas-gsi(20).png

|

.png.png)

|

| Attachment 25: Screenshot_2021-05-14_Statistics_aidas-gsi(19).png

|

.png.png)

|

| Attachment 26: Screenshot_2021-05-14_Statistics_aidas-gsi(18).png

|

.png.png)

|

| Attachment 27: R5_157_analysis.txt

|

*** TDR format 3.3.0 analyser - TD - January 2019

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 256650793 ( 1485751.4 Hz)

Other data format: 5269207 ( 30503.4 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 130 ( 0.8 Hz)

RESUME: 129 ( 0.7 Hz)

SYNC100: 32643 ( 189.0 Hz)

WR48-63: 32643 ( 189.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 5203662 ( 30124.0 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 223116 ( 1291.6 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 172.741 s

FEE elapsed dead time(s) elapsed idle time(s)

1 2.094 74.418

2 0.927 76.576

3 3.655 26.911

4 0.000 161.752

5 0.023 80.653

6 0.215 91.583

7 1.871 44.002

8 1.038 39.676

9 0.000 166.718

10 8.591 10.747

11 3.917 45.280

12 0.214 88.240

13 0.000 163.408

14 0.280 88.718

15 1.416 44.122

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 8604841 3308 0 0 0 0 1138 1138 0 1032 0 12424

1 16359820 4228 0 0 13 13 2101 2101 0 0 0 24974

2 13547296 1610585 0 0 6 6 1930 1930 0 1606713 0 19730

3 25981004 1589167 0 0 14 13 3491 3491 0 1582158 0 28914

4 2316430 549243 0 0 0 0 351 351 0 548541 0 5271

5 15208801 341870 0 0 1 1 1974 1974 0 337920 0 16457

6 12807457 657341 0 0 5 5 1667 1667 0 653997 0 10925

7 22697274 479019 0 0 10 10 2849 2849 0 473301 0 19398

8 22587880 5594 0 0 5 5 2792 2792 0 0 0 24704

9 1078064 266 0 0 0 0 133 133 0 0 0 1963

10 42543713 10740 0 0 43 43 5327 5327 0 0 0 13313

11 20362862 5182 0 0 14 14 2577 2577 0 0 0 4606

12 13994455 3436 0 0 7 7 1711 1711 0 0 0 21818

13 2731986 666 0 0 0 0 333 333 0 0 0 1621

14 13145005 3222 0 0 8 8 1603 1603 0 0 0 13539

15 22683905 5340 0 0 4 4 2666 2666 0 0 0 3459

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time:83137.008s ( 0.385 blocks/s, 0.024 Mb/s)

|

|

719

|

Mon Oct 13 15:04:53 2025 |

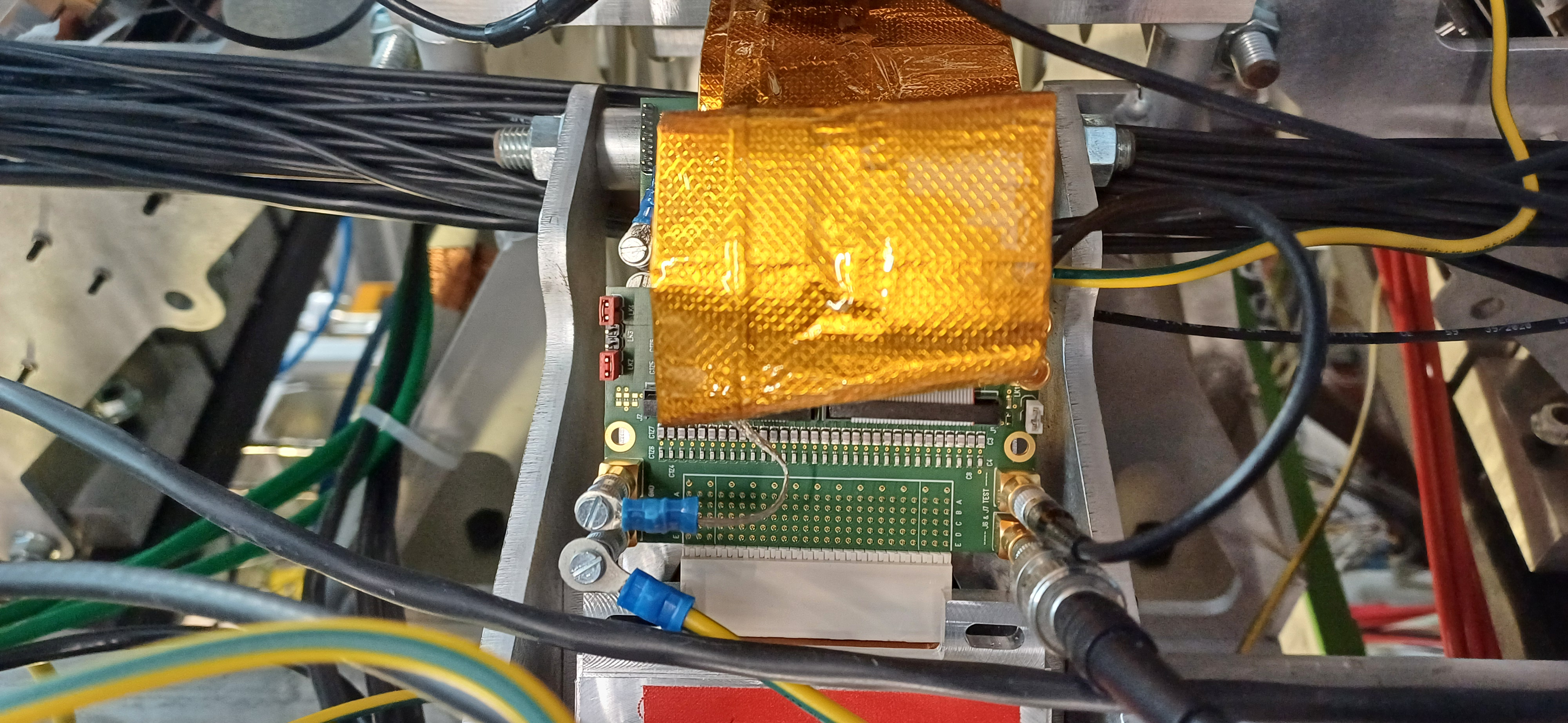

JPB, NH, GB, MP | Dismount AIDA and realign the cables |

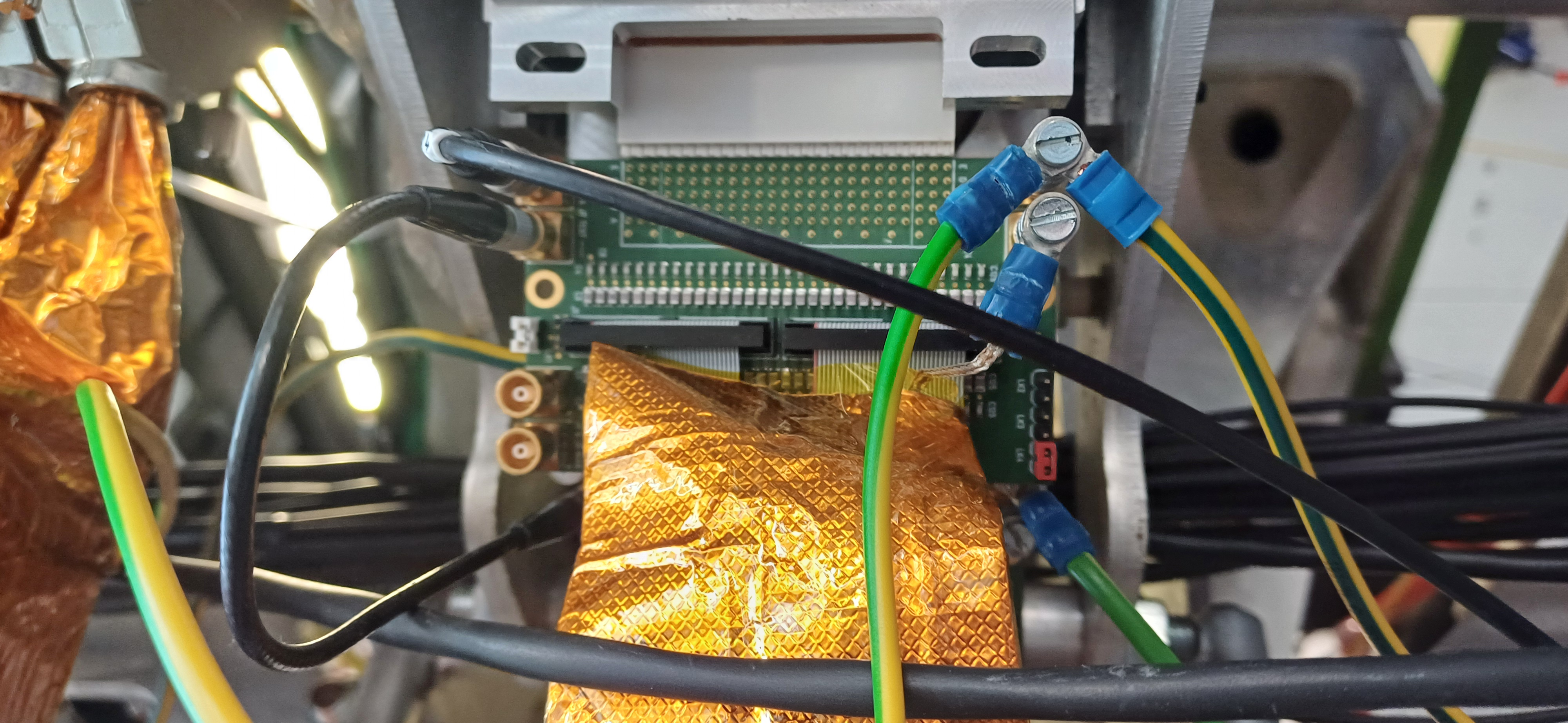

We have dismounted the AIDA stack and bPlast and realigned the cables so that they can fit into the adaptors.

The plan for the next couple days is the following:

- Alignment -- done

- Remount cable -- ongoing

- Fix position w/o bPlast mounted --

- Remount bracket for the last stage --

- Remount AIDA 1 & 2 and the 207Bi source with the source holder --

- Mount the snout and take data --

The tests we want to perform are the following:

- Energy distribution in x and y for ADC items and cluster

- The cluster size from conversion electrons

- ADC offsets with the 207Bi source after performing a pulser walkthrough

- Threshold test /w a 207Bi source - varying the threshold as while the source is in place and seeing when the 207Bi peaks are cut off.

- Background run without the 207Bi source (after the above tests)

- Possible test with a 152Eu source as well to measure conversion electrons from Eu could also be an option but we would need to discuss how to do this since all the 152Eu source are closed. We could possibly measure the compton edge from this

data. |

| Attachment 1: IMG_5778.jpeg

|

|

| Attachment 2: IMG_5779.jpeg

|

|

|

745

|

Wed Nov 19 10:28:24 2025 |

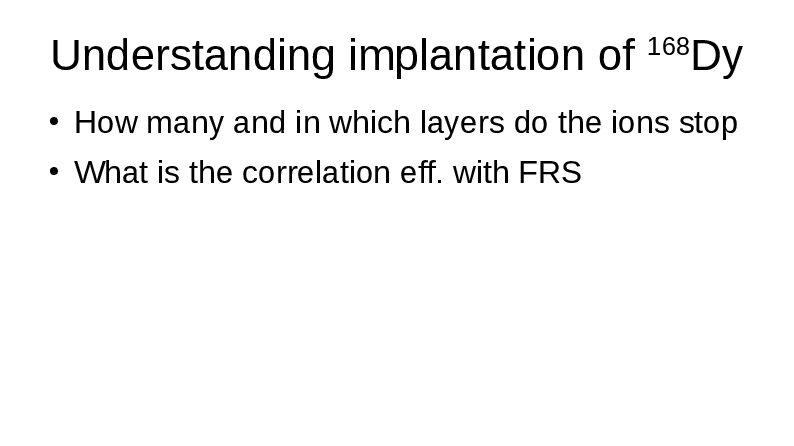

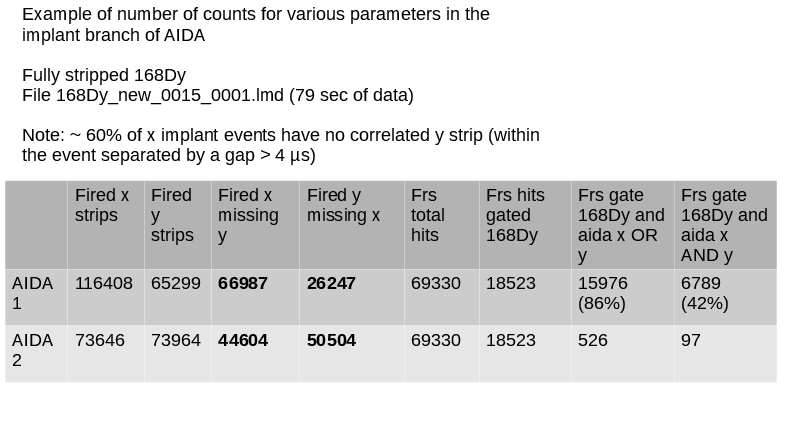

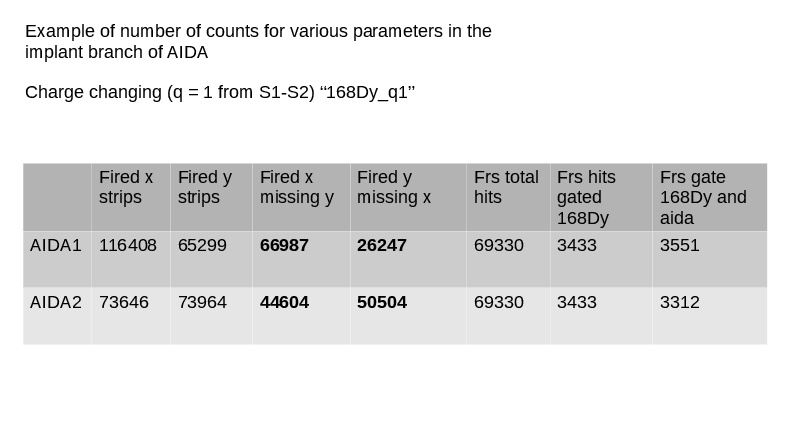

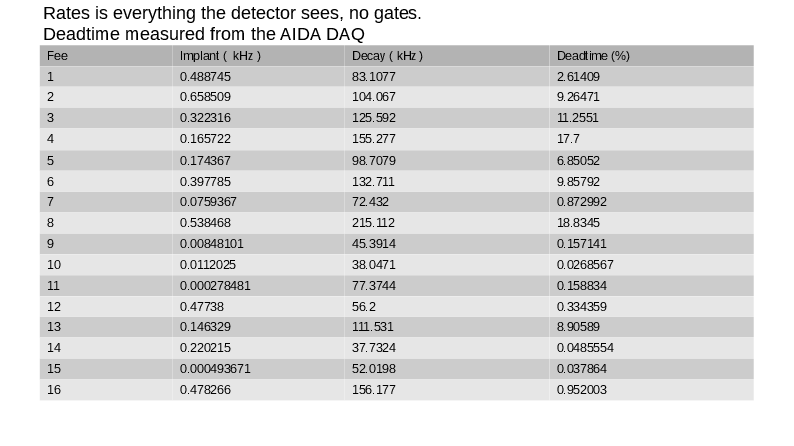

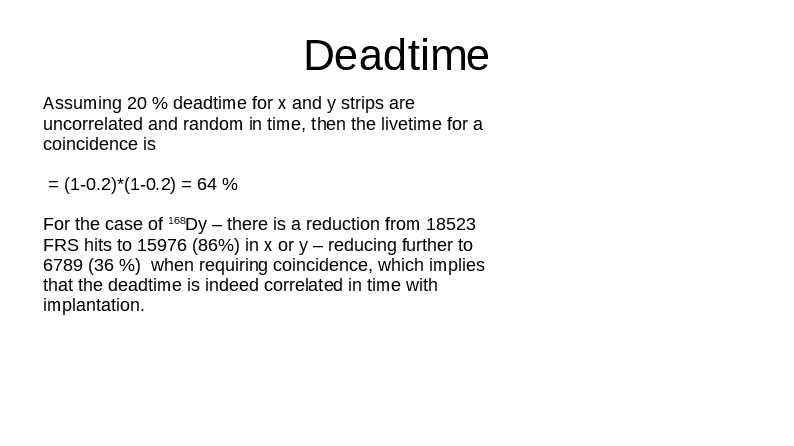

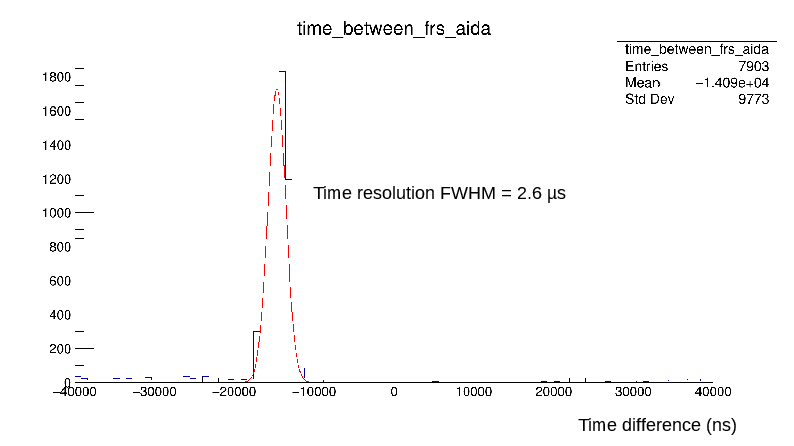

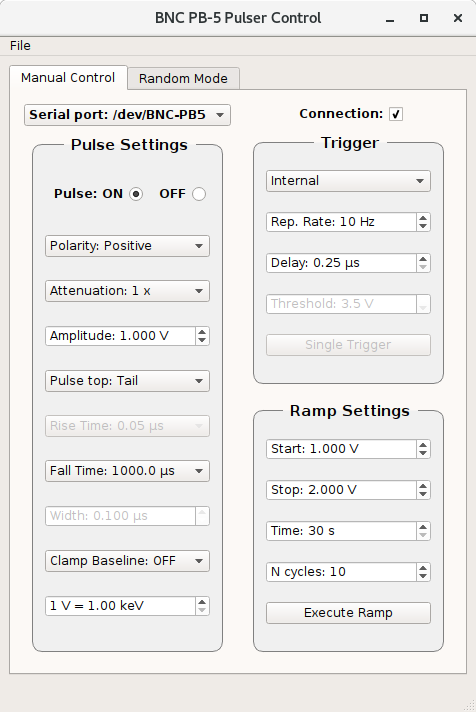

JEL, JB | Analysis of AIDA from S100 experiment by JEL |

Analysis done by JEL of the AIDA daq with his own time-stitcher -- not the standard one used by DESPEC.

- Analysis of 168Dy:

-- Correlation efficiency and stopping layer of ion 168Dy in fully-stripped and hydrogen-like charge-state.

|

| Attachment 1: aidastop.pdf

|

|

|

639

|

Wed Jun 5 08:34:47 2024 |

JB. AM, MP, MY | Detector bias tests |

We are trying to bias each system on its own and in sequence biasing each other detector system to see the interdependence.

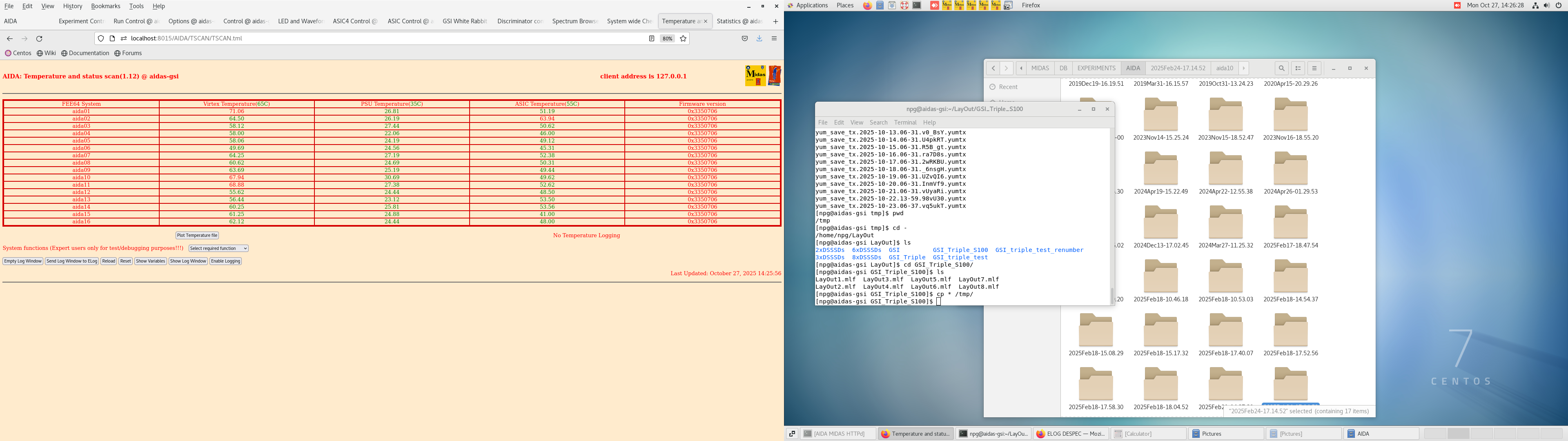

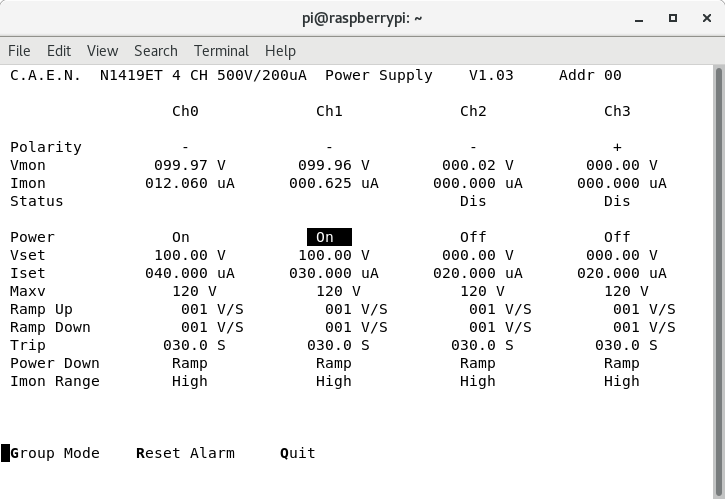

HV OK. TEMP OK. Attachment 1 &2.

9.43 bPlast unbiased, BB7 unbiased. Attachments 3-6 is the noise situation with only AIDA biased (bPlast was biased but turned off after AIDA was biased.)

10/16 FEEs < 20k noise. Max noise is 250k. Downstream AIDA appears to be seeing additional noise since S100.

11:21 Returning after an hour the noise has increased significantly in many channels. Scale changed to 10000 in histograms, it appears that the problem is from a couple hot channels.

11:41 'Power' cycled AIDA turned off. bPlast turned on, on its own, then BB7. bPlast doesn't seem to notice anything.

12:21 bPlast and BB7 on. AIDA ON. Rates and histograms given by attachment 7-8. More FEEs noisy, but same level as 11:21. There appears to be the same noisy channel in all of the FEEs (?) Some grounding not properly accounted for, or a wire touching somewhere (?)

13:55h: AIDA & BB7 on. Rates and histograms given in attachments 9-10. Same level as bplast & AIDA on. Same noisy channels in FEEs. According to Nic, these correspond to the end of the ribbon cables & is normal.

13:59 AIDA, bPlast & BB7 on before lunch. Same levels of noise as in previous combinations (attachments 11-12).

So it seems we can run with the three sub-systems biased simultaneously.

|

| Attachment 1: Screenshot_from_2024-06-05_09-36-25.png

|

|

| Attachment 2: Screenshot_from_2024-06-05_09-39-42.png

|

|

| Attachment 3: Screenshot_from_2024-06-05_09-41-44.png

|

|

| Attachment 4: Screenshot_from_2024-06-05_09-41-52.png

|

|

| Attachment 5: Screenshot_from_2024-06-05_09-42-35.png

|

|

| Attachment 6: Screenshot_from_2024-06-05_09-43-43.png

|

|

| Attachment 7: Screenshot_from_2024-06-05_11-40-33.png

|

|

| Attachment 8: Screenshot_from_2024-06-05_11-40-39.png

|

|

| Attachment 9: Screenshot_from_2024-06-05_12-19-14.png

|

|

| Attachment 10: Screenshot_from_2024-06-05_12-20-42.png

|

|

| Attachment 11: Screenshot_from_2024-06-05_13-58-21.png

|

|

| Attachment 12: Screenshot_from_2024-06-05_13-55-08.png

|

|

| Attachment 13: Screenshot_from_2024-06-05_12-20-42.png

|

|

| Attachment 14: Screenshot_from_2024-06-05_12-19-14.png

|

|

|

571

|

Thu Apr 11 08:27:21 2024 |

JB, TD | 11 April noise tests |

TO-DO for 11.04.2024

- Try bringing bPlast drain wire ground back to the PSU ground for PN 300 and R&SRMP4040.

- Recheck the downstream detector bias and ground scheme.

-

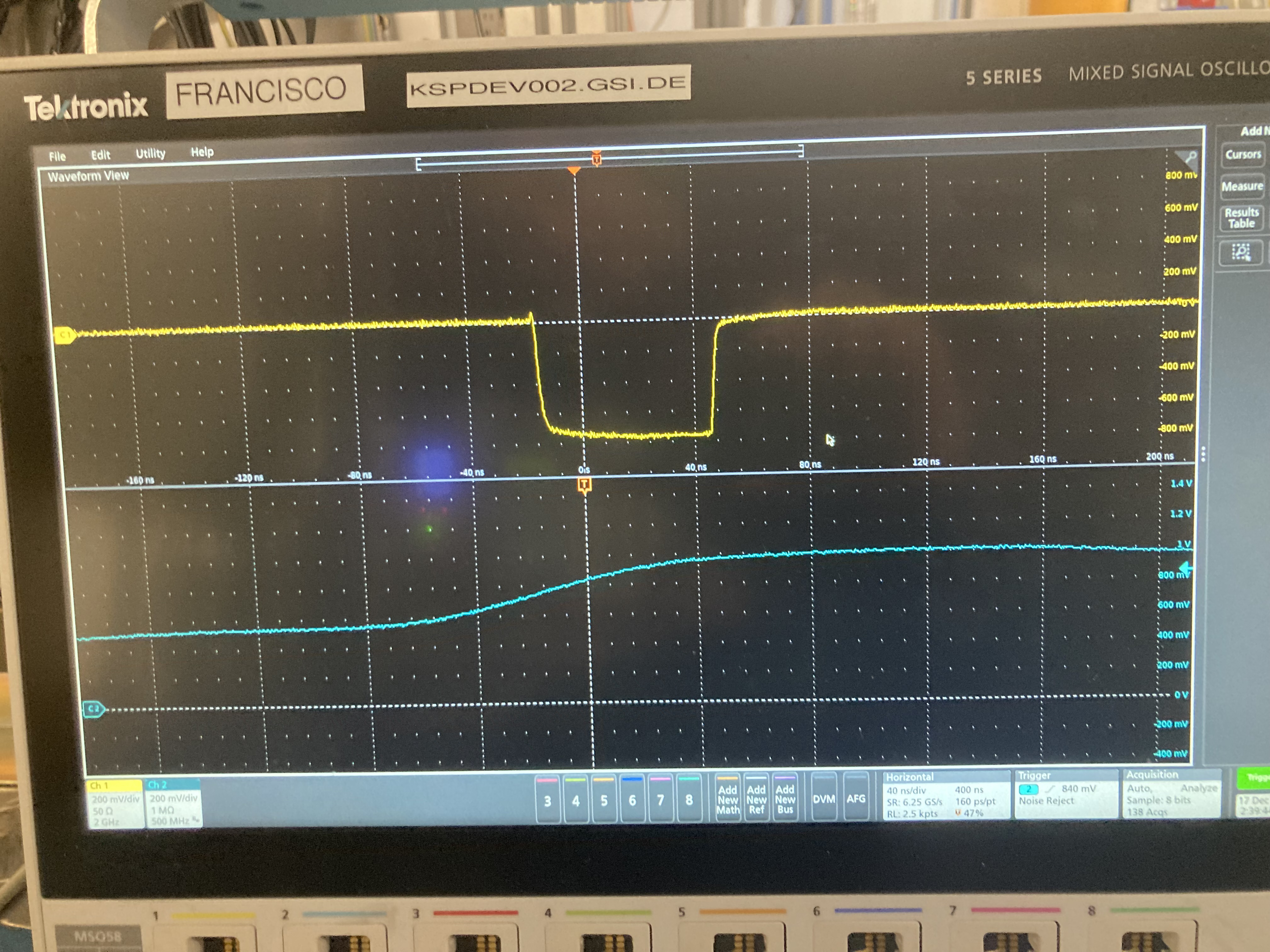

9:27 Restarted AIDA and hit go at 9:54. Situation the same as it was in the evening of 10.04.2024. 10 out of 16 FEE64s in good condition. Waveforms of aida16,

TEMP OK - HV OK. See attachments 1-6.

10:20 We grounded the output of the R&SRMP4040 to to the drain wire ground of the bPlast ribbon cables and the output of the PN 300 PSU that is powering the booster boards. Results given by attachments 7 -11. We only saw a marginal improvement in the overall noise condition.

10:32 We connected the ground of the frame to the drain wire ground, that is also mutually connected to the ground of the R&SRMP4040 output ground and PN 300 output ground. Results given by attachments ???. We did not see any improvement in the overal noise condition.

11.00 DSSSD HV OFF

FEE64 power OFF

Check seating of all adaptor PCBs and drain/ground wires secured - generally OK

Restart

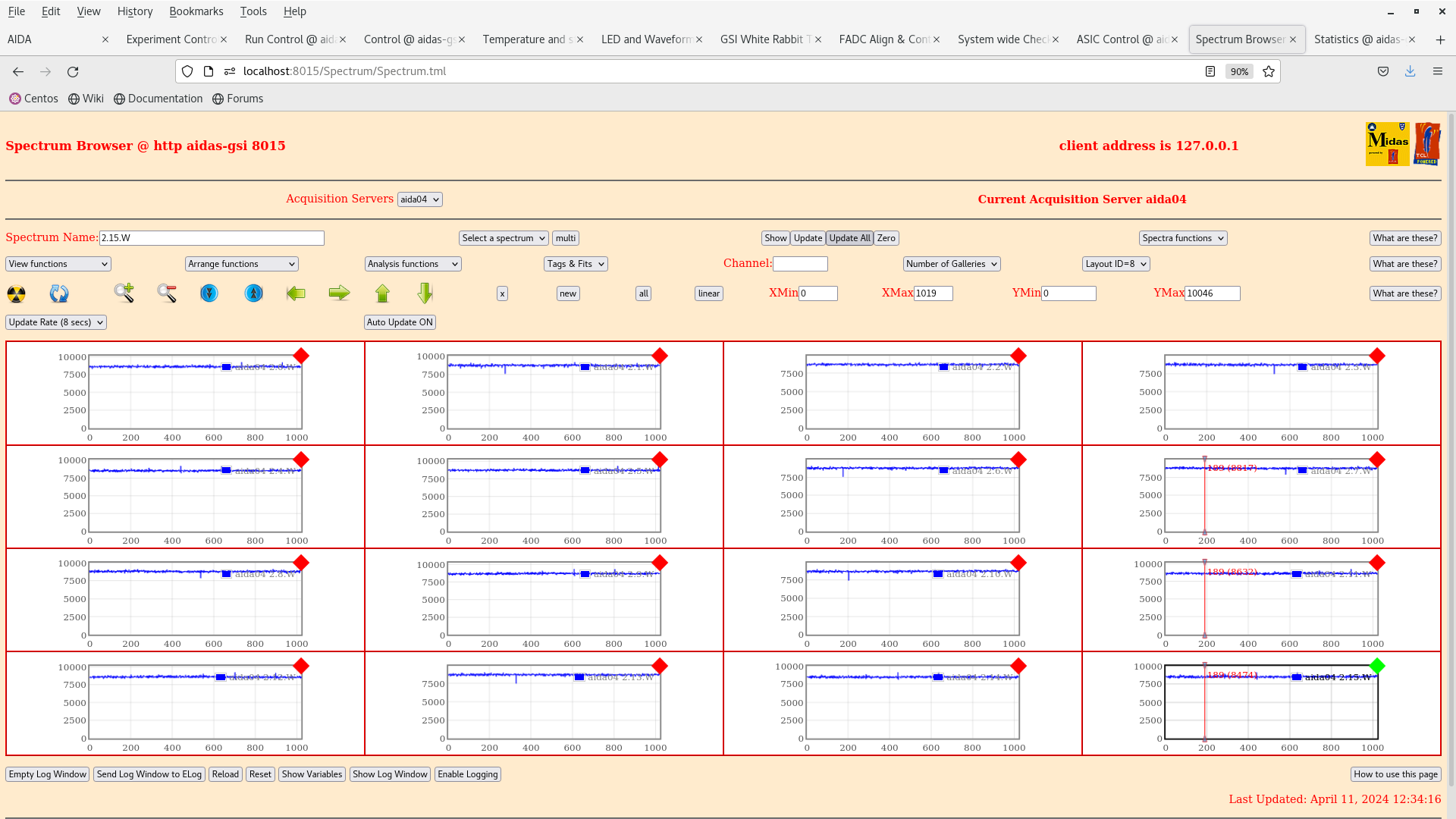

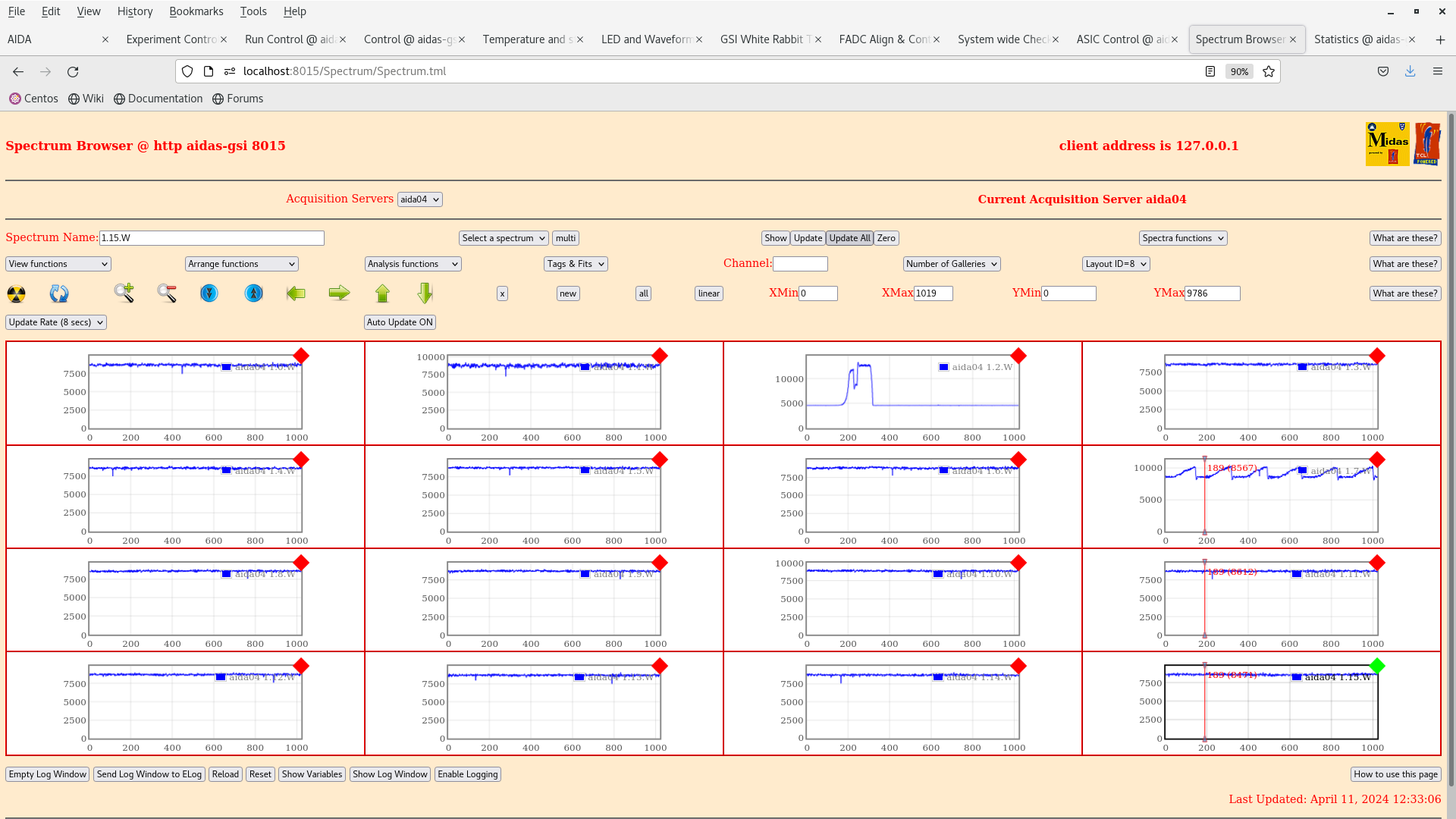

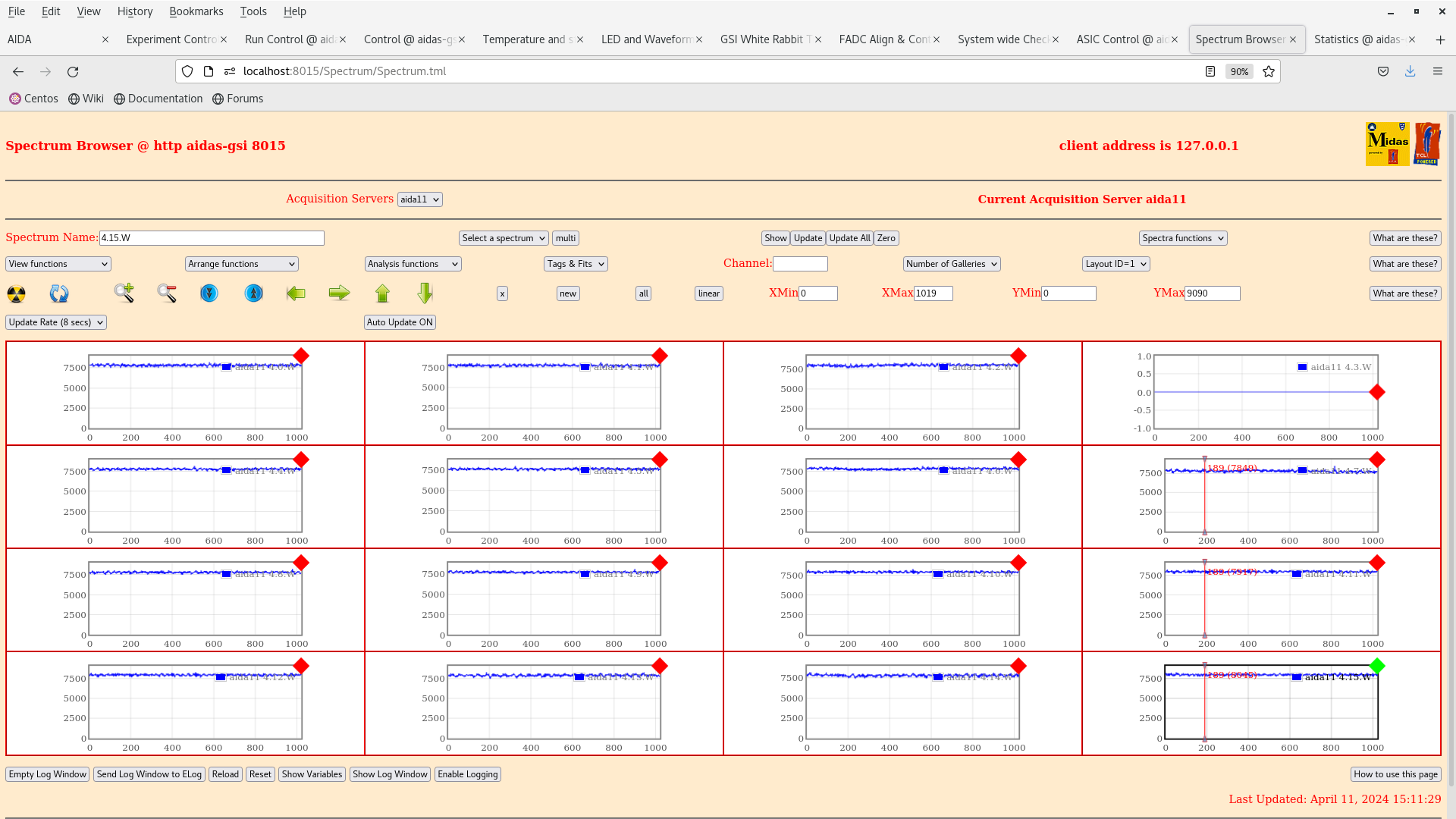

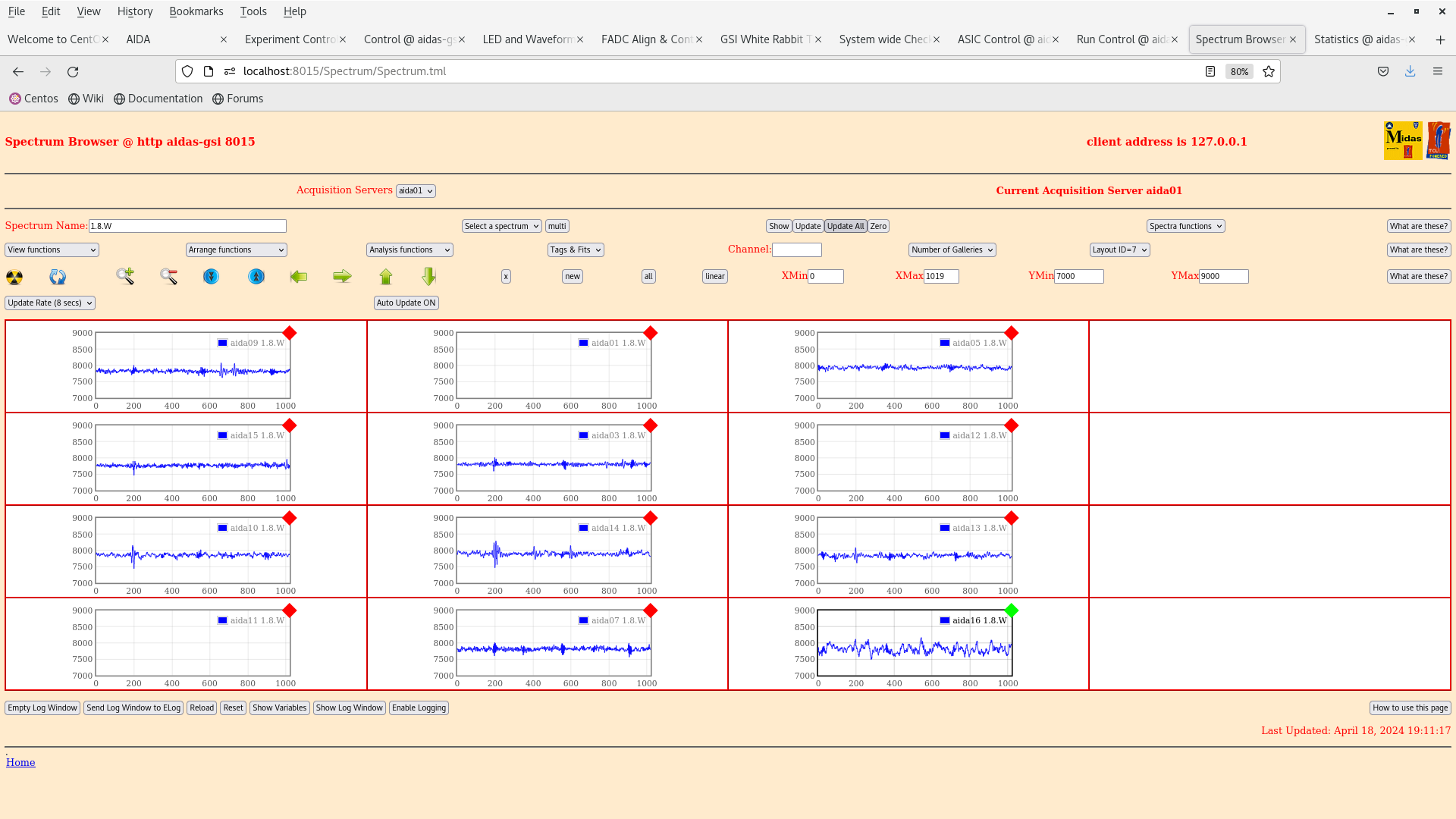

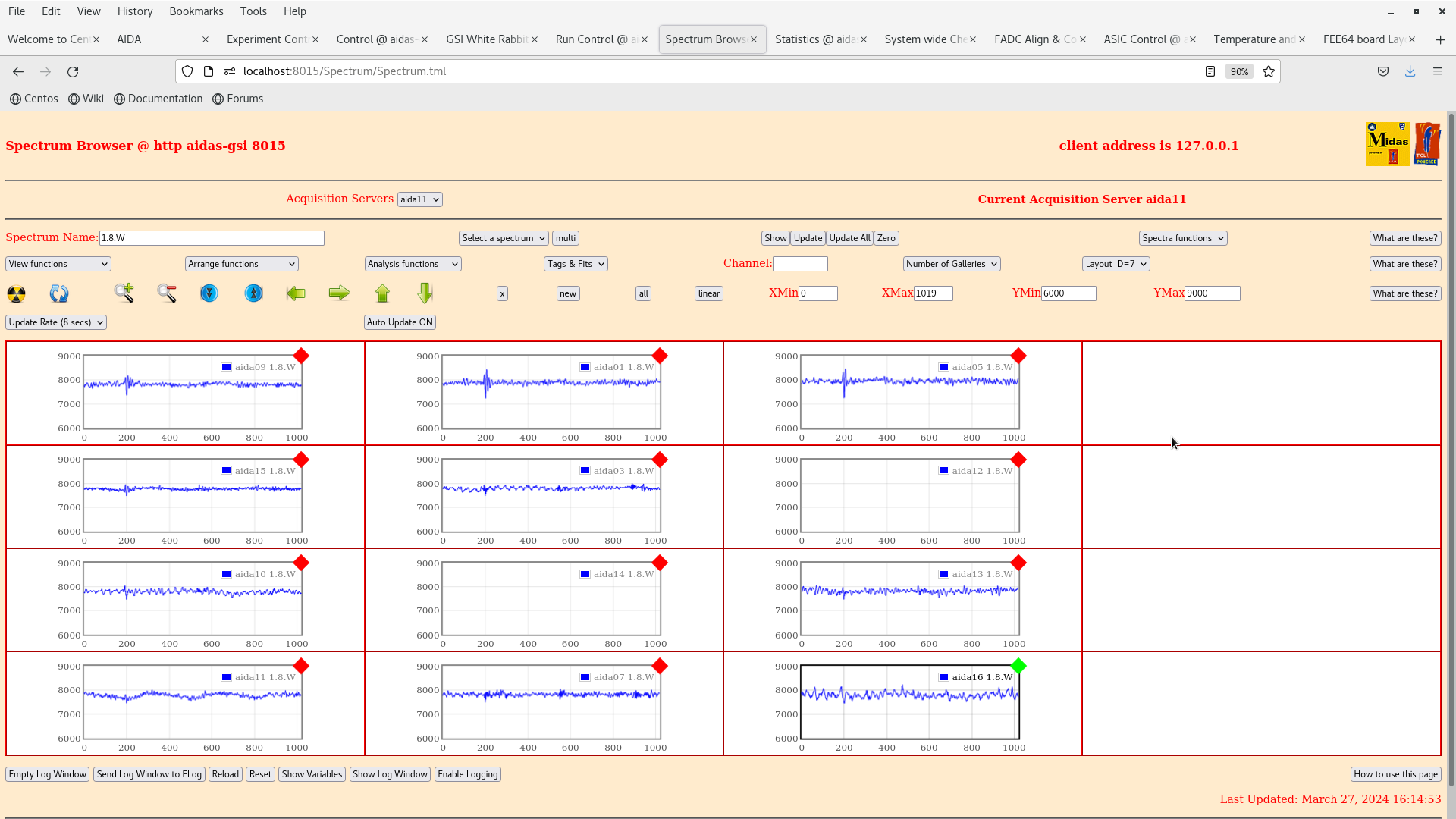

1.8.W spectra - 20us FSR - attachments 15-16

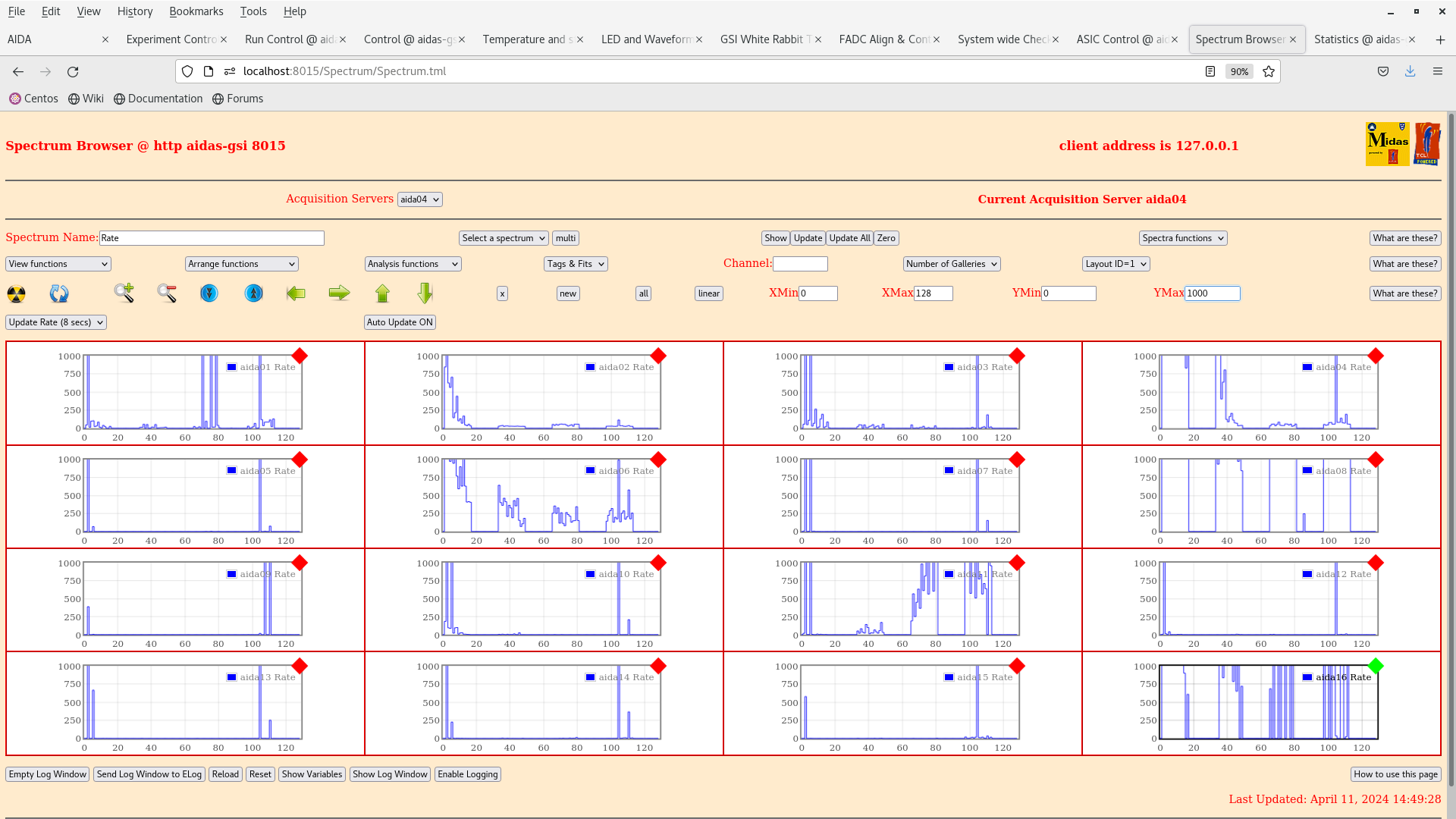

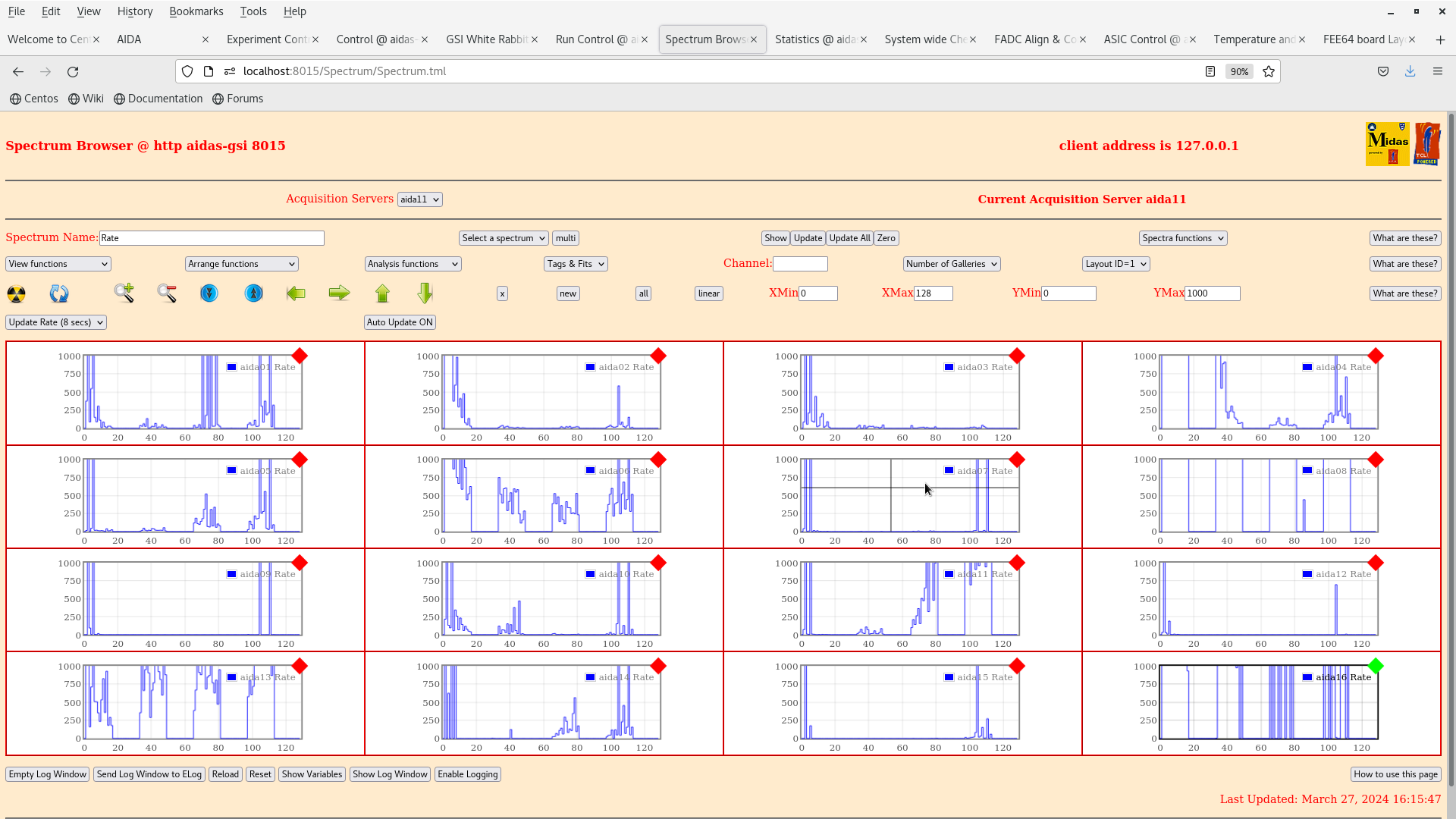

per FEE64 Rate spectra - attachment 17

10/16 < 20k, max 110k

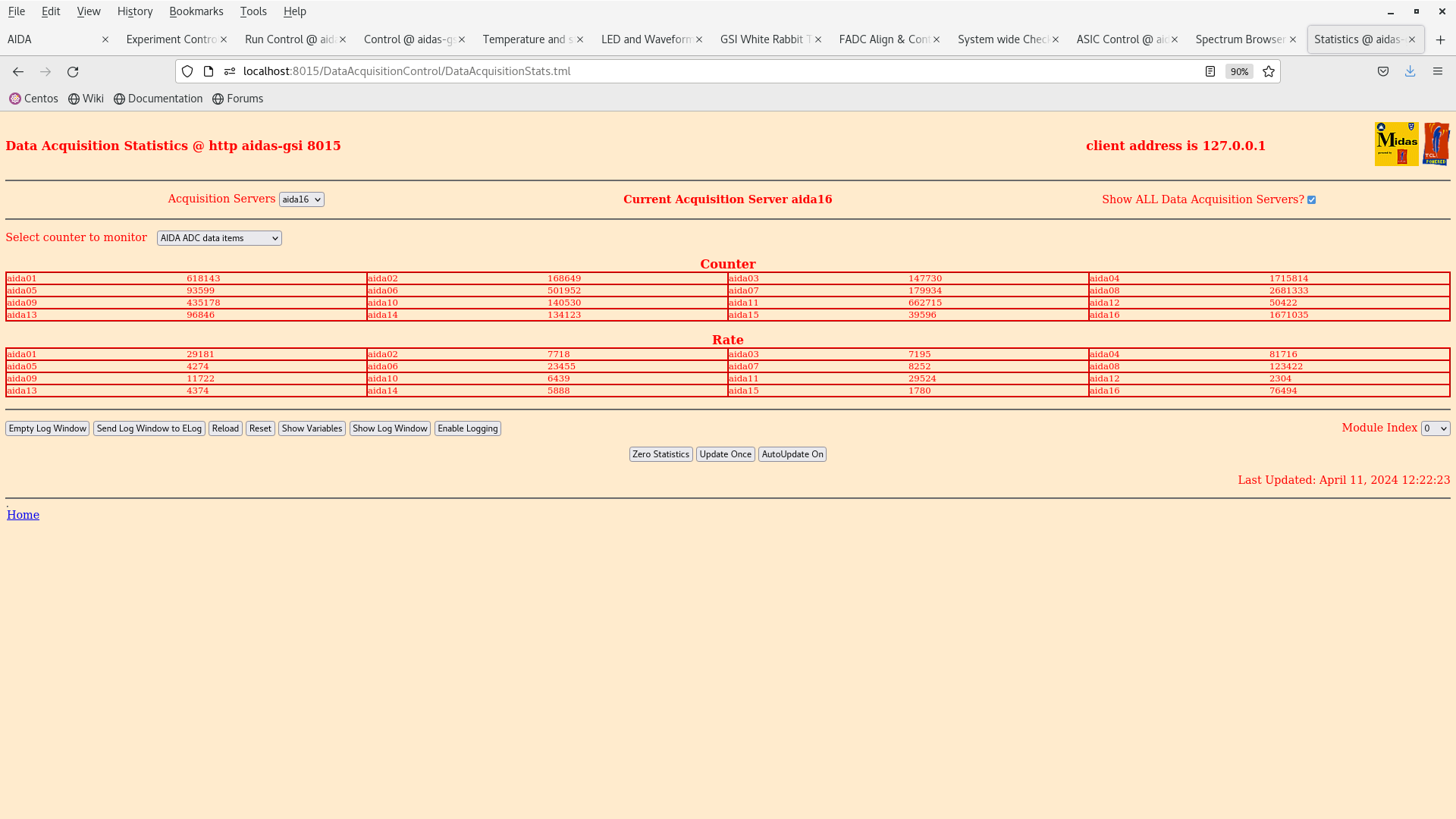

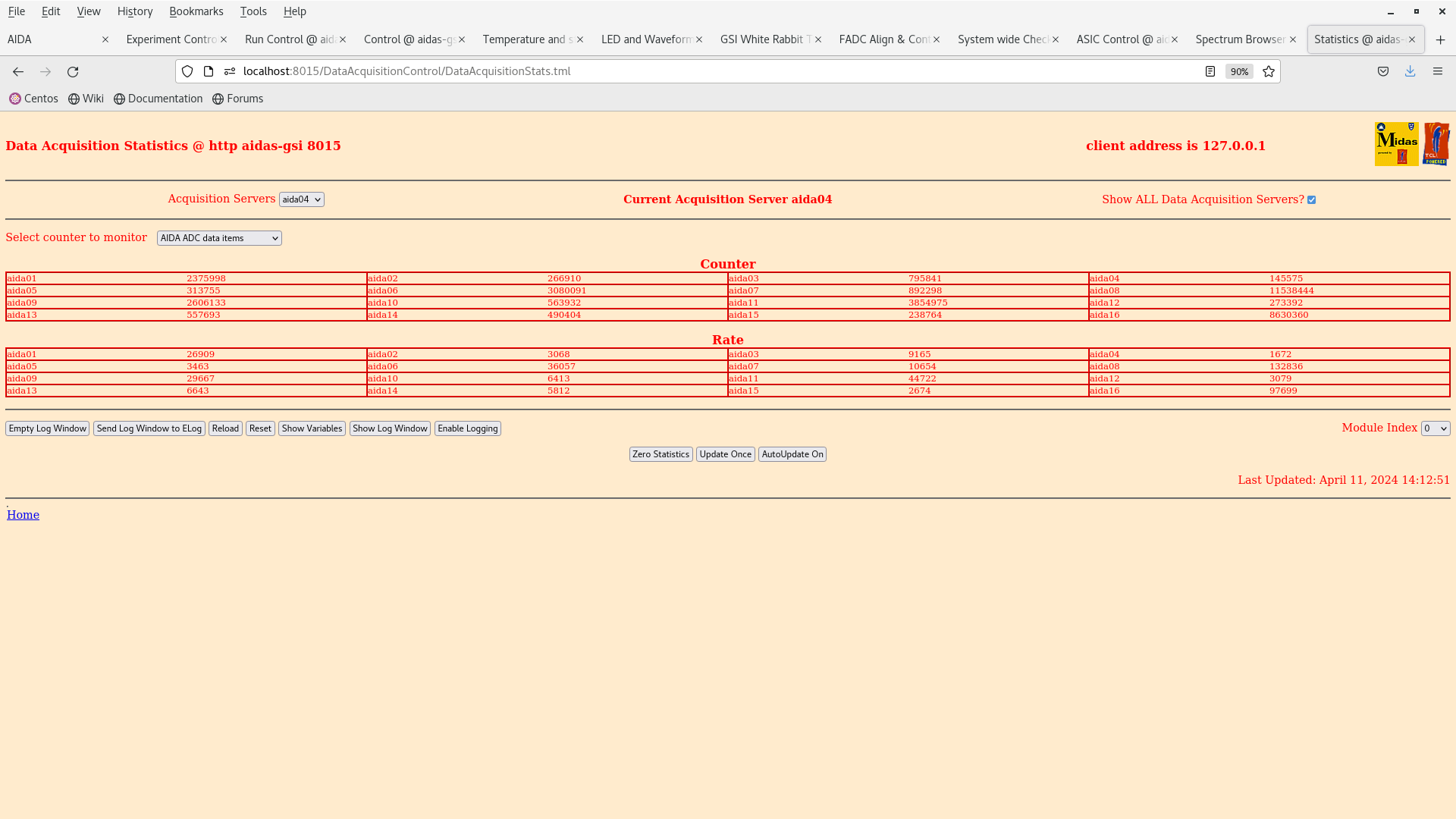

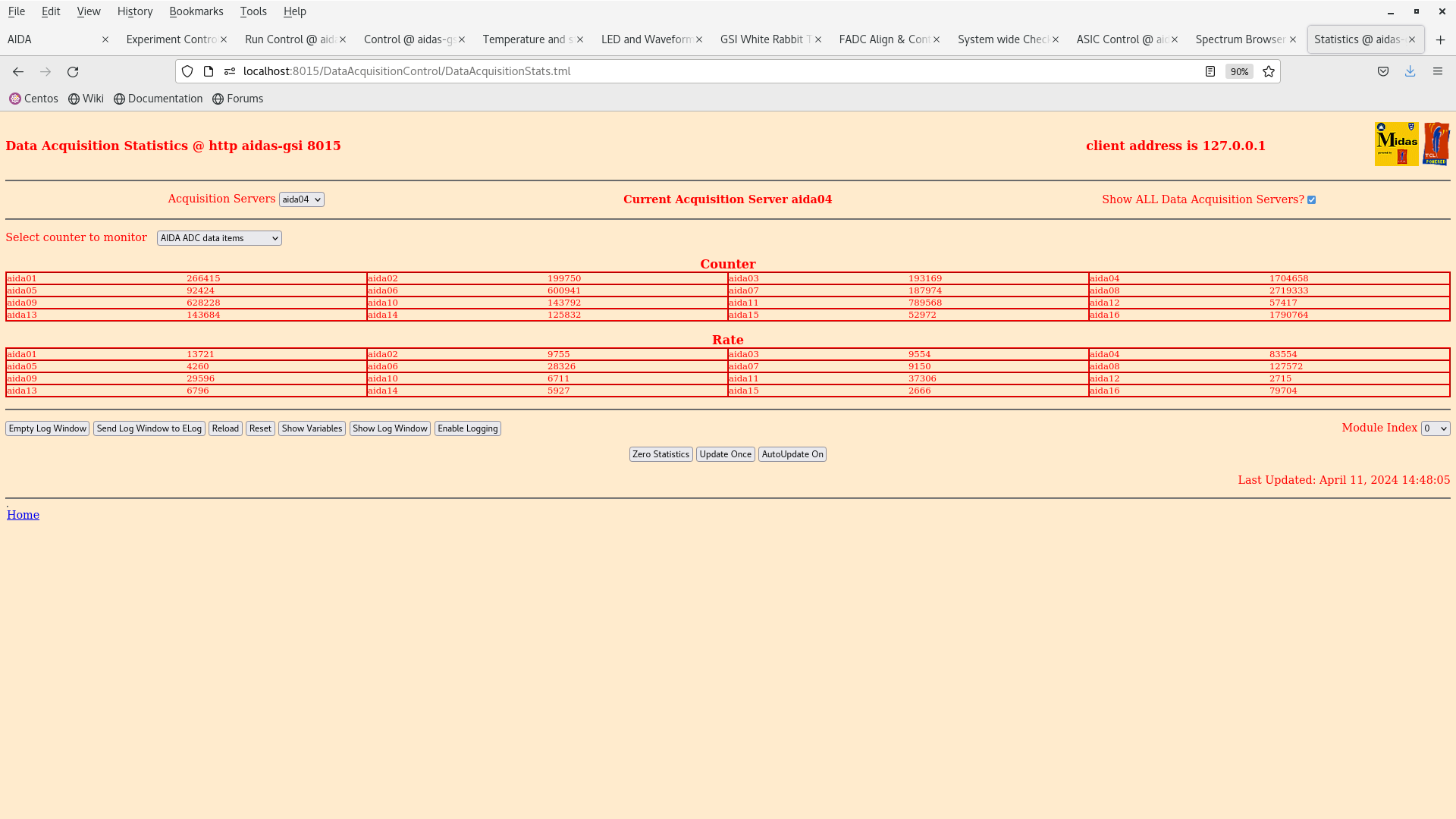

ADC data item stats - attachment 18

Incremental improvement.

11.45 DSSSD HV OFF

FEE64 power OFF

test - daisy chain removed

Restart

1.8.W spectra - 20us FSR - attachments 20-21

per FEE64 Rate spectra - attachment 19

10/16 < 20k, max 210k

ADC data item stats - attachment 22

overall somewhat worse

12.20 DSSSD HV OFF

FEE64 power OFF

Re-install test - daisy chain, Tighten aida04 DSSSD ribbon cable drain wire.

Restart

1.8.W spectra - 20us FSR - attachments 23-24

per FEE64 Rate spectra - attachment 25

ADC data item stats - attachment 26

10/16 < 20k, max 110k

Status quo ante

aida04 & aida08 1*W & 2*W spectra - 200us FSR - attachments 27-31

large transients observed for aida04 1*W - cable or ASIC fault?

aida16 **W spectra - 200us FSR - attachments 32-35

all channels apopear to be working but mix of high/low noise channels for asics #3-4, asics #1-2 all appear high noise

14.00 DSSSD HV OFF

FEE64 power OFF

Disconnect ribbon cables from aida04 adaptor PCB

Restart

n+n FEE64 1.8.W spectra - 20us FSR - attachments 37

per FEE64 Rate spectra - attachment 36

ADC data item stats - attachment 38

Implies origin of large transients observed in aida04 asic#1 is downstream of the FEE64 adaptor PCB, i.e. ribbon cable or DSSSD.

14.40 DSSSD HV OFF

FEE64 power OFF

re-connect ribbon cables from aida04 adaptor PCB

1x pin J2 slightly bent - straightended with screwdriver - FFSD connector insertion OK

Restart

n+n FEE64 1.8.W spectra - 20us FSR - attachments 40-41

per FEE64 Rate spectra - attachment 42-43

ADC data item stats - attachment 39

10x < 20k, max 120k

aida11 asic#4 1.8.W spectra - 200us FSR - attachment

no large transients observed

DSSSD #1 & #2 bias from -120V to -100V

ADC data item stats - attachment 40

9x < 20k, max 220k (aida08)

per FEE64 Rate spectra - attachment 41

17.15 bPlas ON -

Current bPlast ground configuration:

bPlas current ground configuration - drainwires of all ribbon cables excluding short side (cont. with snout) are grounded back to the bPlast R&SRMP4040 PSU, on the 29 V output. 4 V PSU to booster boards are floating, output of PN 300 is grounded to the PSU. The mesytec PSU, that also powers bPlast SiPMs at

29V is not grounded to anything but the frame. Snout is currently light tight, I suspect internal radiation from FATIMA.

It is noted that bPlast current draw fluctuated significantly (+/- 300 mV) as a result of thresholds set to the detector. I tried to set the thresholds HIGH to stabilise the bPlast detector as the power draw is fluctuating greatly.

AIDA noise very good

ADC data item stats - attachment 42

12x < 20k, max 83k (aida04)

per FEE64 Rate spectra - attachment 43

To Do list

- separate 29V (low current) and 4V (high current) return paths/ground refs

- The mesytec PSU that powers the bPlast detector is running to frame, it might be an idea to ground ribbon c

|

| Attachment 1: Screenshot_from_2024-04-11_09-56-51.png

|

|

| Attachment 2: Screenshot_from_2024-04-11_09-55-50.png

|

|

| Attachment 3: Screenshot_from_2024-04-11_09-55-21.png

|

|

| Attachment 4: Screenshot_from_2024-04-11_09-55-10.png

|

|

| Attachment 5: Screenshot_from_2024-04-11_09-54-19.png

|

|

| Attachment 6: Screenshot_from_2024-04-11_09-53-48.png

|

|

| Attachment 7: Screenshot_from_2024-04-11_10-21-37.png

|

|

| Attachment 8: Screenshot_from_2024-04-11_10-21-08.png

|

|

| Attachment 9: Screenshot_from_2024-04-11_10-18-40.png

|

|

| Attachment 10: Screenshot_from_2024-04-11_10-18-38.png

|

|

| Attachment 11: Screenshot_from_2024-04-11_10-38-51.png

|

|

| Attachment 12: Screenshot_from_2024-04-11_10-37-16.png

|

|

| Attachment 13: Screenshot_from_2024-04-11_10-36-23.png

|

|

| Attachment 14: Screenshot_from_2024-04-11_10-36-13.png

|

|

| Attachment 15: Screenshot_from_2024-04-11_11-18-05.png

|

|

| Attachment 16: Screenshot_from_2024-04-11_11-17-16.png

|

|

| Attachment 17: Screenshot_from_2024-04-11_11-14-20.png

|

|

| Attachment 18: Screenshot_from_2024-04-11_11-14-08.png

|

|

| Attachment 19: Screenshot_from_2024-04-11_11-47-55.png

|

|

| Attachment 20: Screenshot_from_2024-04-11_11-46-52.png

|

|

| Attachment 21: Screenshot_from_2024-04-11_11-46-01.png

|

|

| Attachment 22: Screenshot_from_2024-04-11_11-45-32.png

|

|

| Attachment 23: Screenshot_from_2024-04-11_12-24-14.png

|

|

| Attachment 24: Screenshot_from_2024-04-11_12-23-39.png

|

|

| Attachment 25: Screenshot_from_2024-04-11_12-23-08.png

|

|

| Attachment 26: Screenshot_from_2024-04-11_12-22-27.png

|

|

| Attachment 27: Screenshot_from_2024-04-11_12-35-36.png

|

|

| Attachment 28: Screenshot_from_2024-04-11_12-35-07.png

|

|

| Attachment 29: Screenshot_from_2024-04-11_12-34-18.png

|

|

| Attachment 30: Screenshot_from_2024-04-11_12-33-13.png

|

|

| Attachment 31: Screenshot_from_2024-04-11_12-37-22.png

|

|

| Attachment 32: Screenshot_from_2024-04-11_12-44-59.png

|

|

| Attachment 33: Screenshot_from_2024-04-11_12-43-07.png

|

|

| Attachment 34: Screenshot_from_2024-04-11_12-42-19.png

|

|

| Attachment 35: Screenshot_from_2024-04-11_12-40-03.png

|

|

| Attachment 36: Screenshot_from_2024-04-11_14-04-59.png

|

|

| Attachment 37: Screenshot_from_2024-04-11_14-05-23.png

|

|

| Attachment 38: Screenshot_from_2024-04-11_14-19-10.png

|

|

| Attachment 39: Screenshot_from_2024-04-11_14-48-09.png

|

|

| Attachment 40: Screenshot_from_2024-04-11_14-48-29.png

|

|

| Attachment 41: Screenshot_from_2024-04-11_14-48-57.png

|

|

| Attachment 42: Screenshot_from_2024-04-11_14-49-37.png

|

|

| Attachment 43: Screenshot_from_2024-04-11_14-49-26.png

|

|

| Attachment 44: Screenshot_from_2024-04-11_15-11-42.png

|

|

| Attachment 45: Screenshot_from_2024-04-11_15-17-34.png

|

|

| Attachment 46: Screenshot_from_2024-04-11_15-17-10.png

|

|

| Attachment 47: Screenshot_from_2024-04-11_17-13-36.png

|

|

| Attachment 48: Screenshot_from_2024-04-11_17-13-40.png

|

|

|

577

|

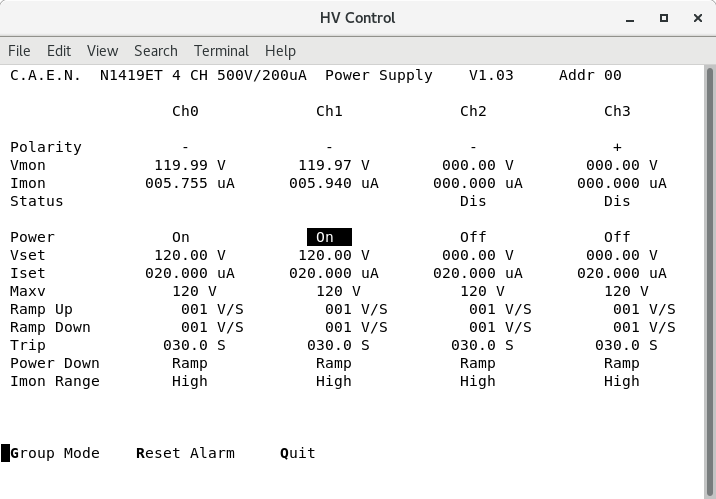

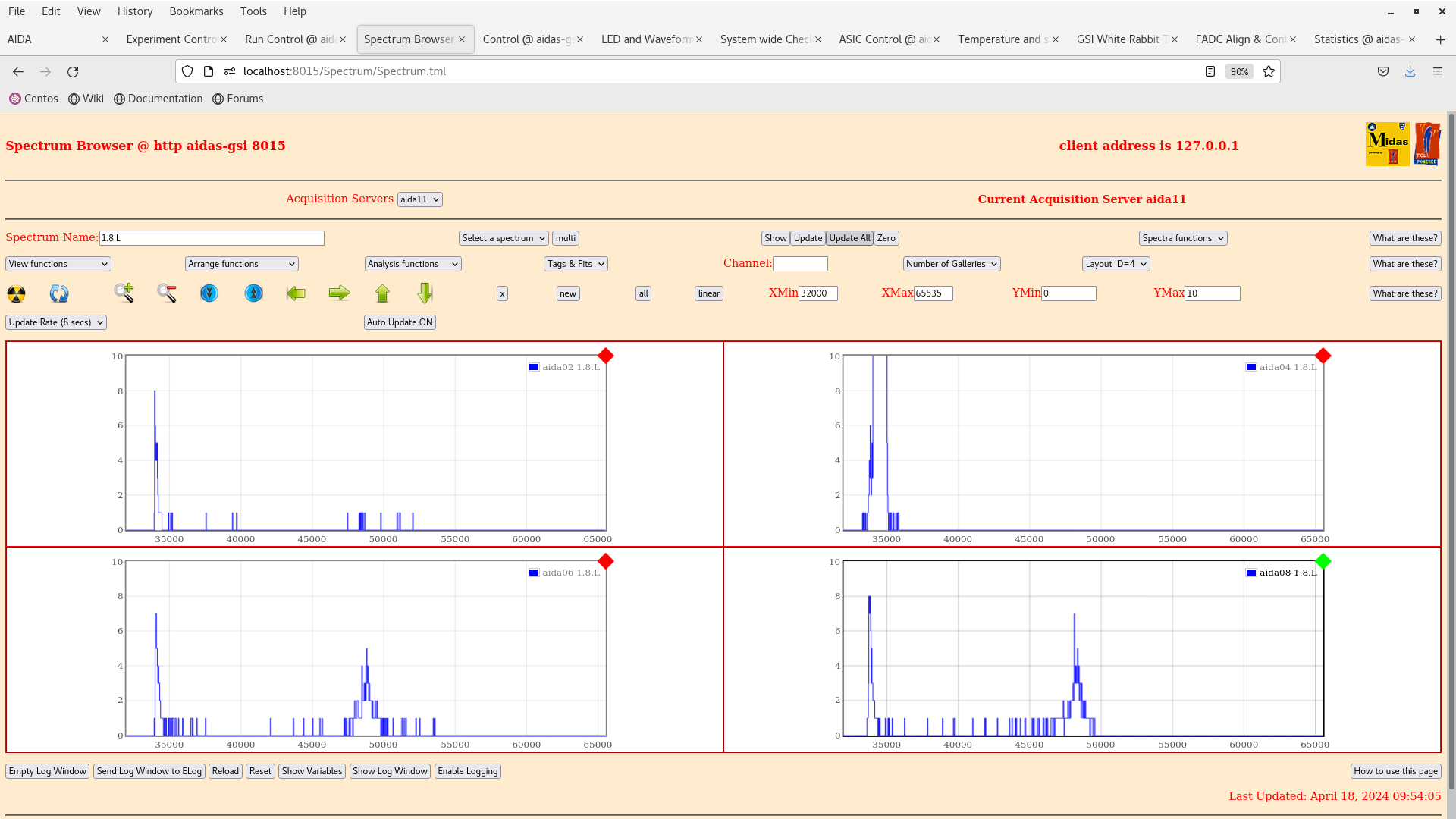

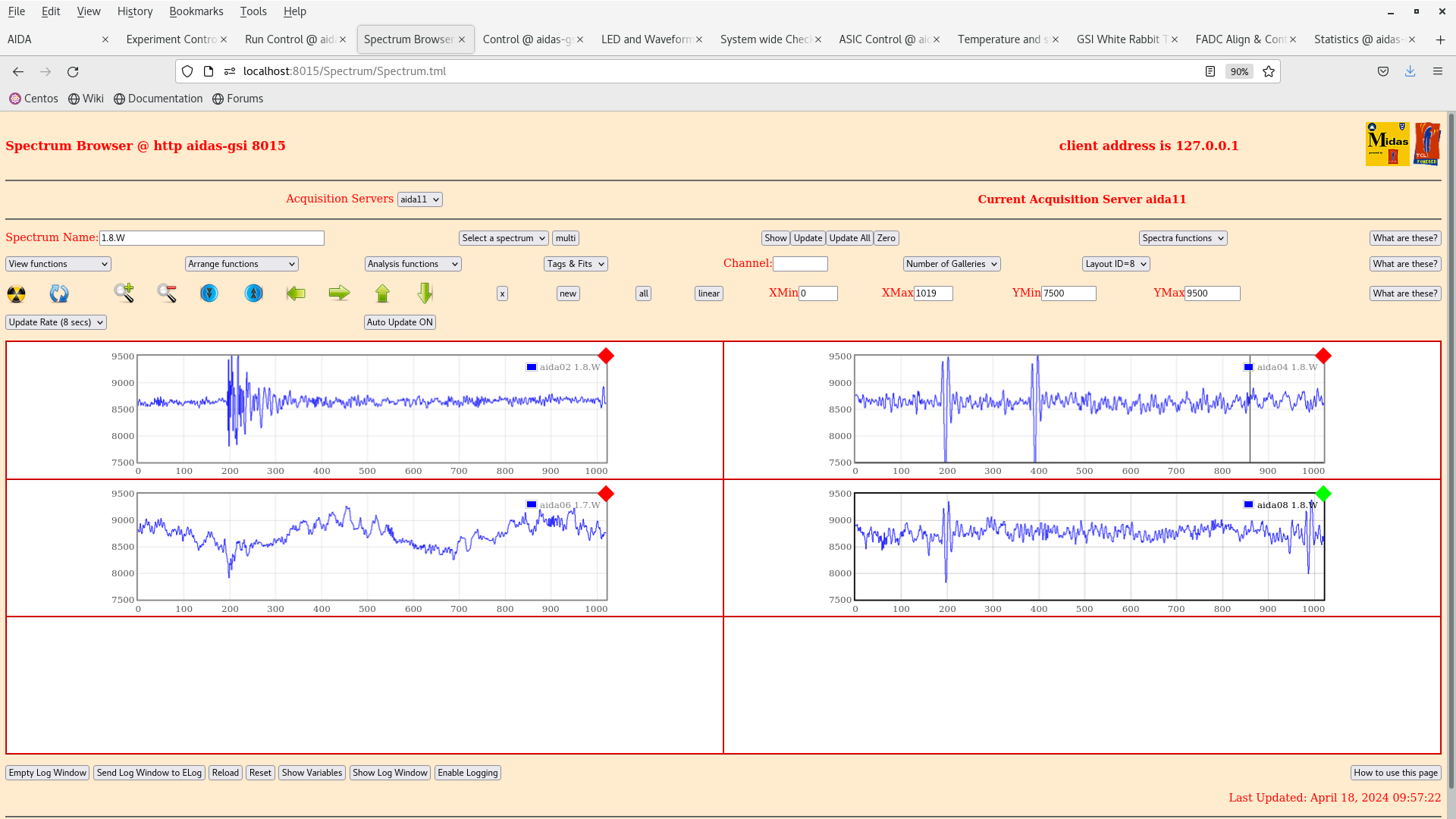

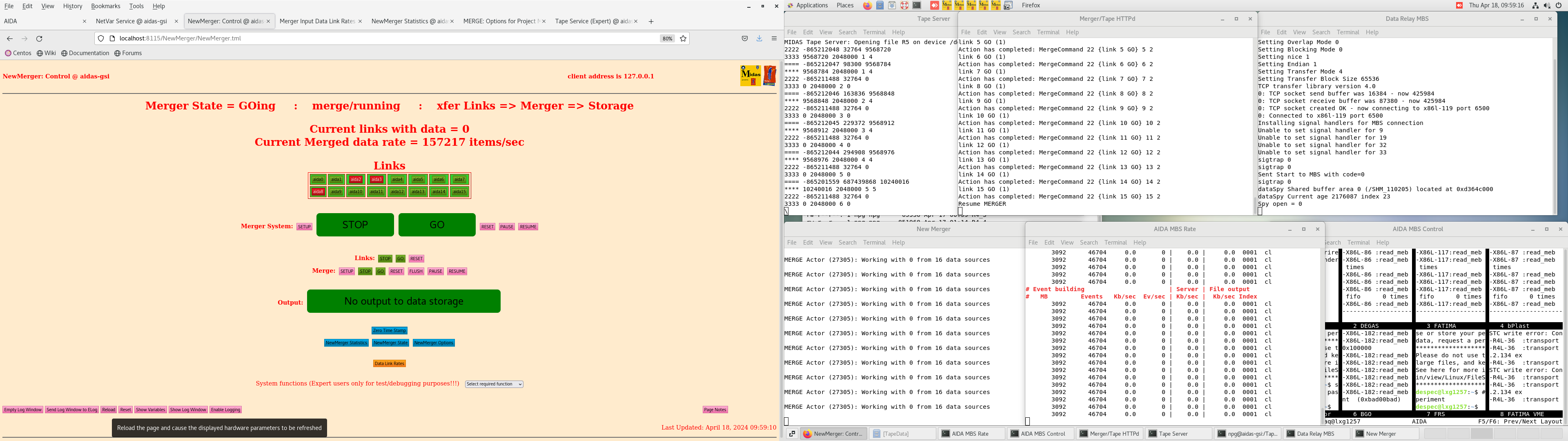

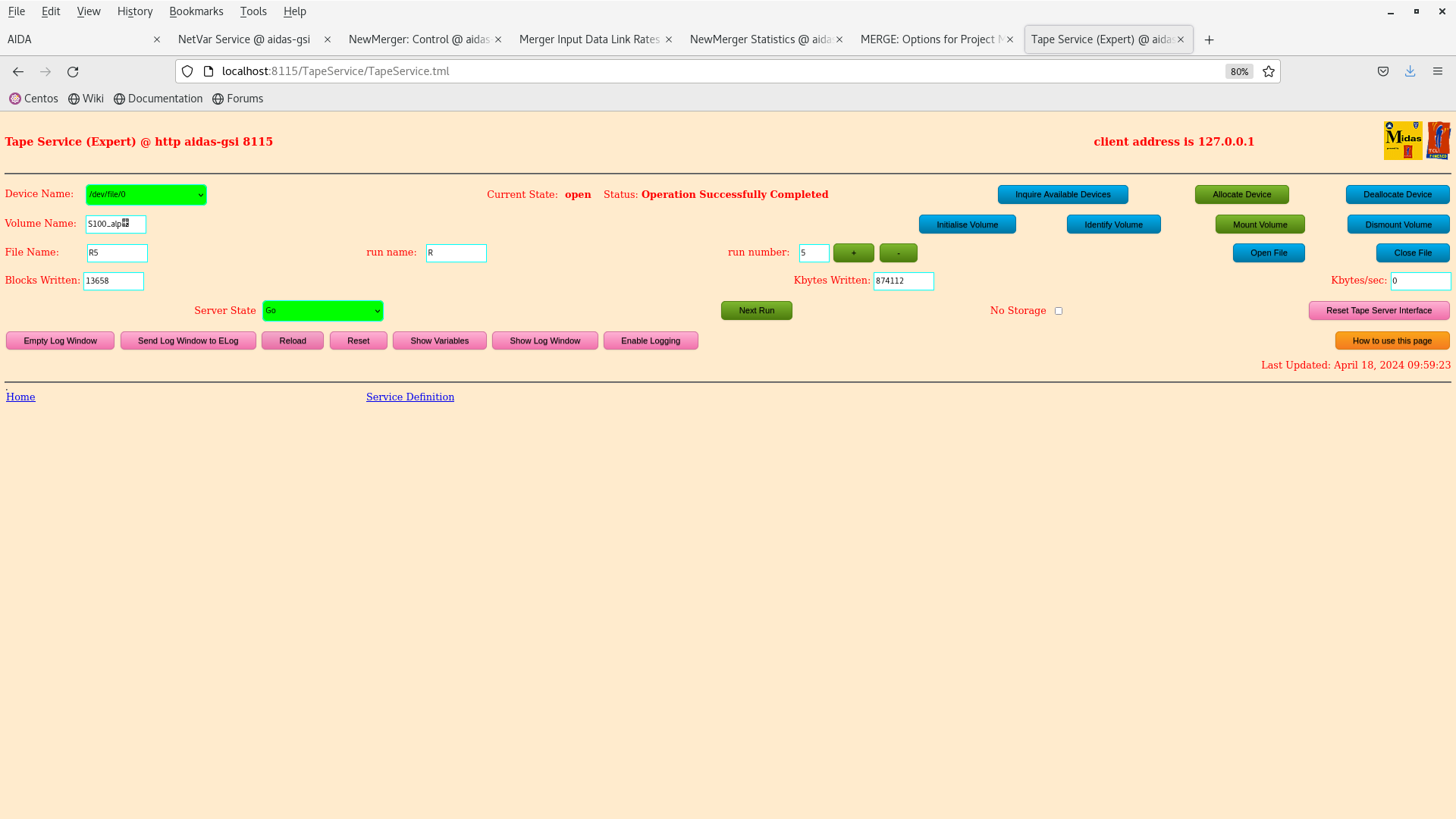

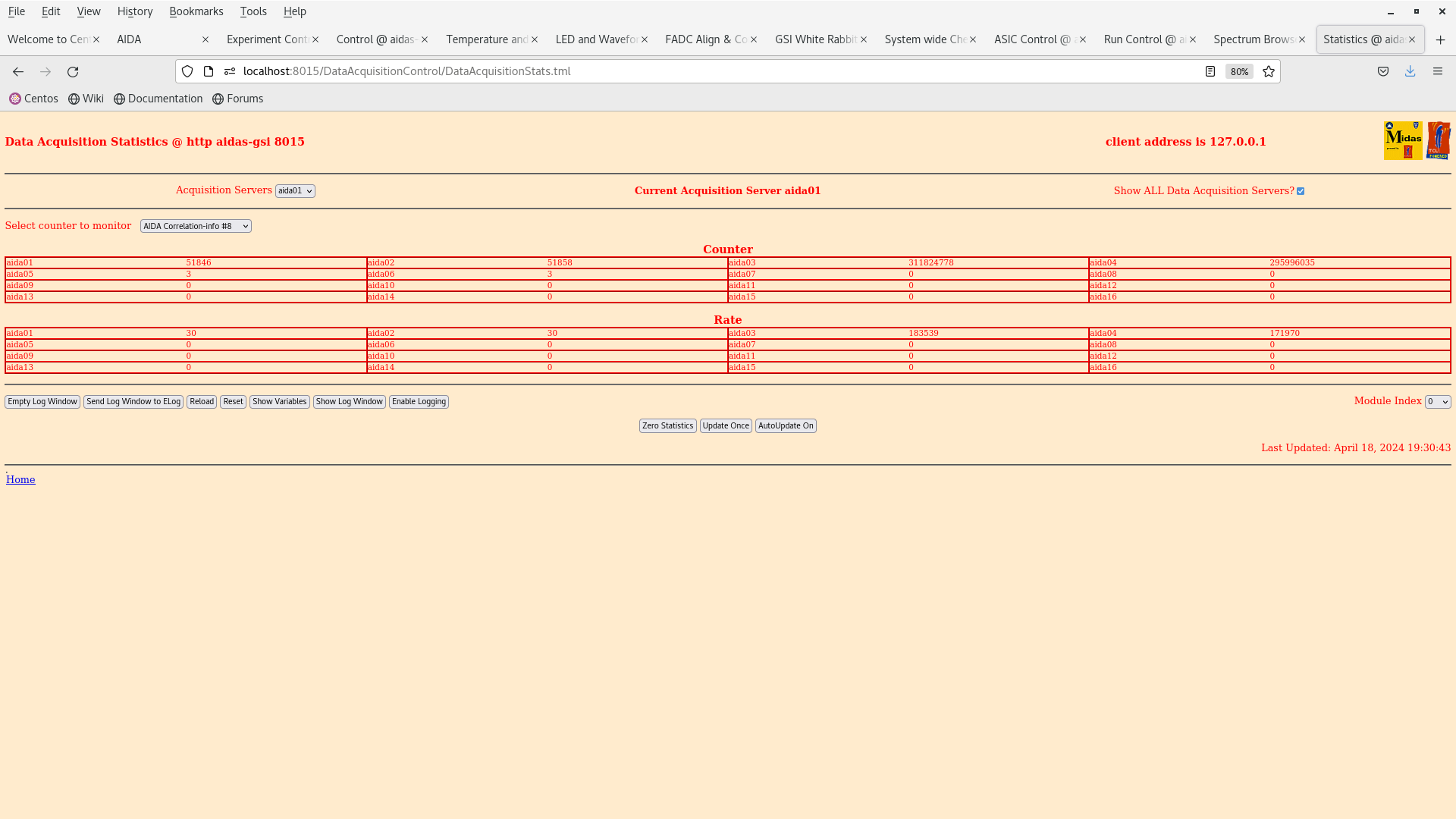

Thu Apr 18 08:57:48 2024 |

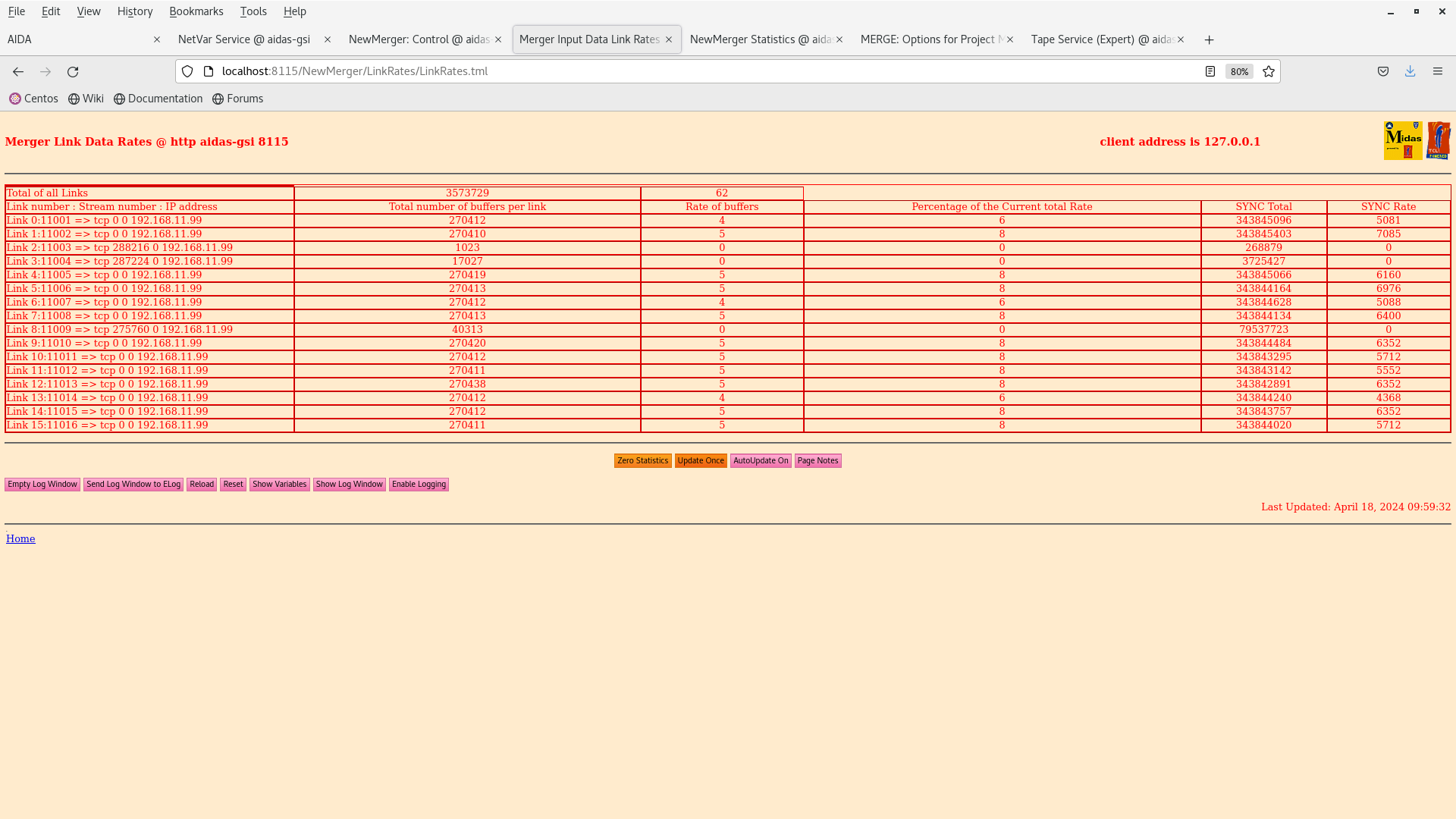

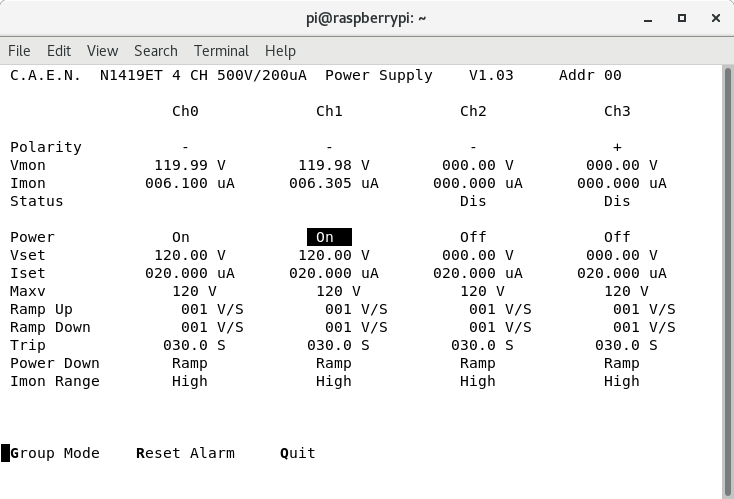

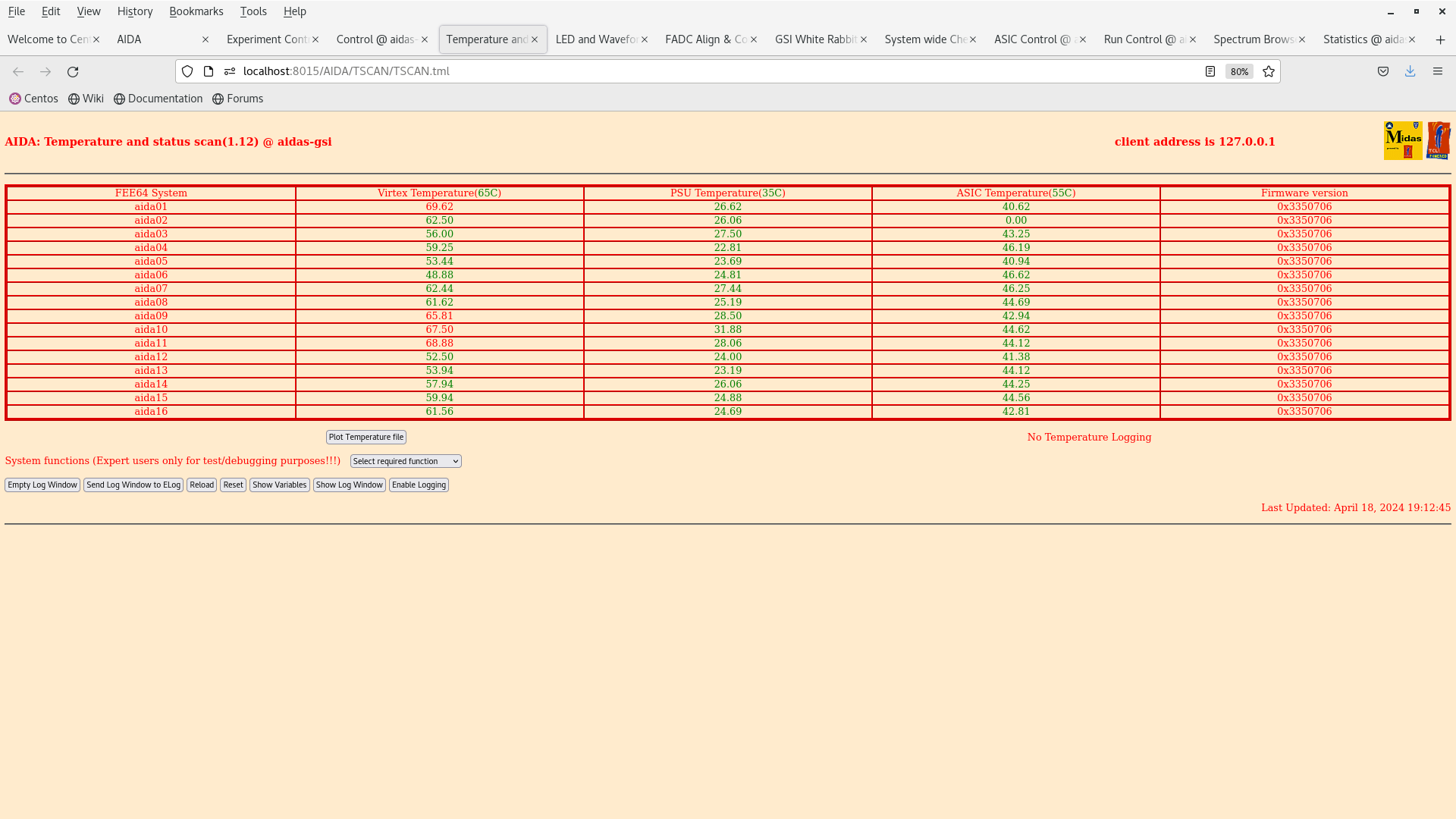

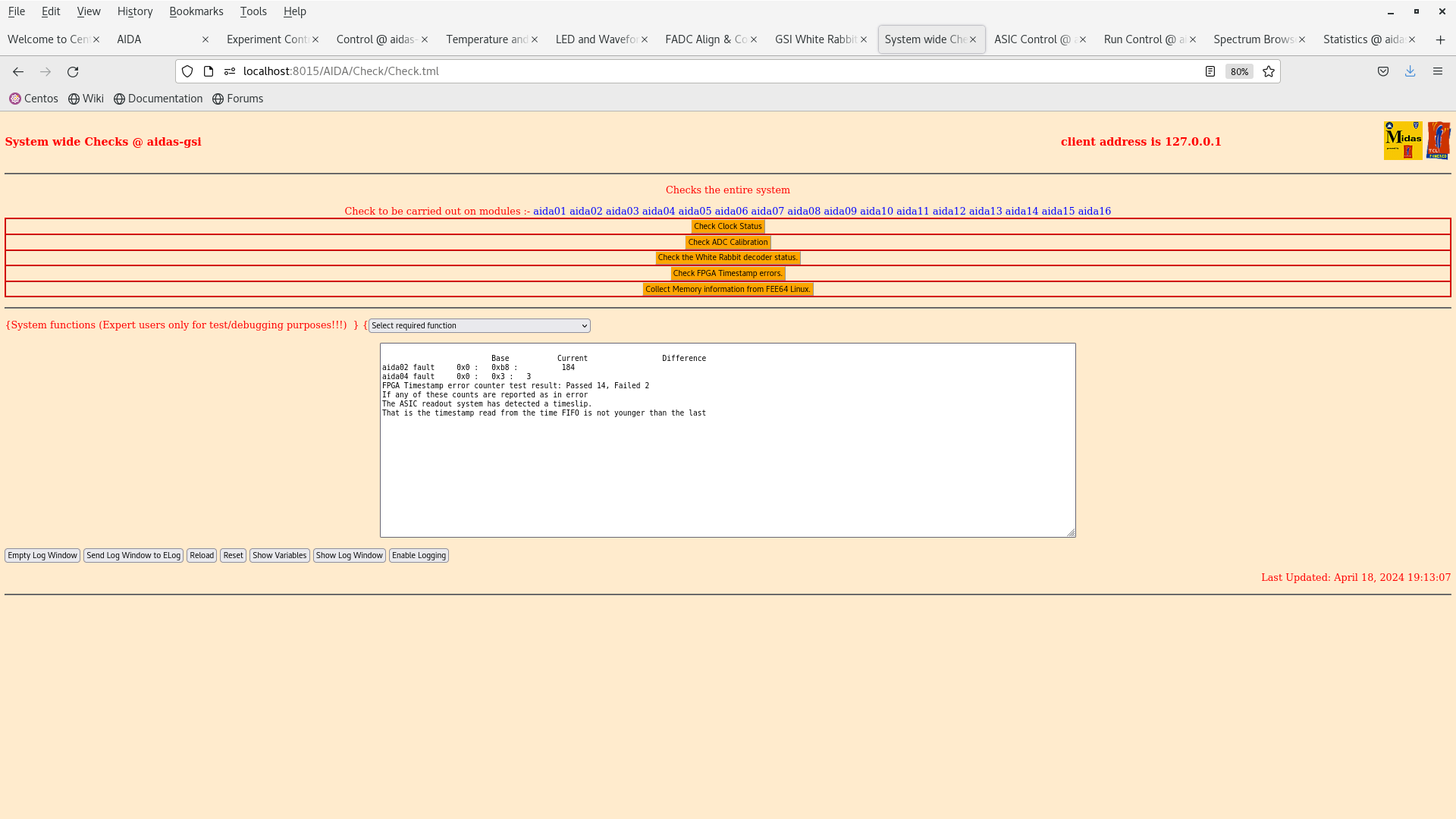

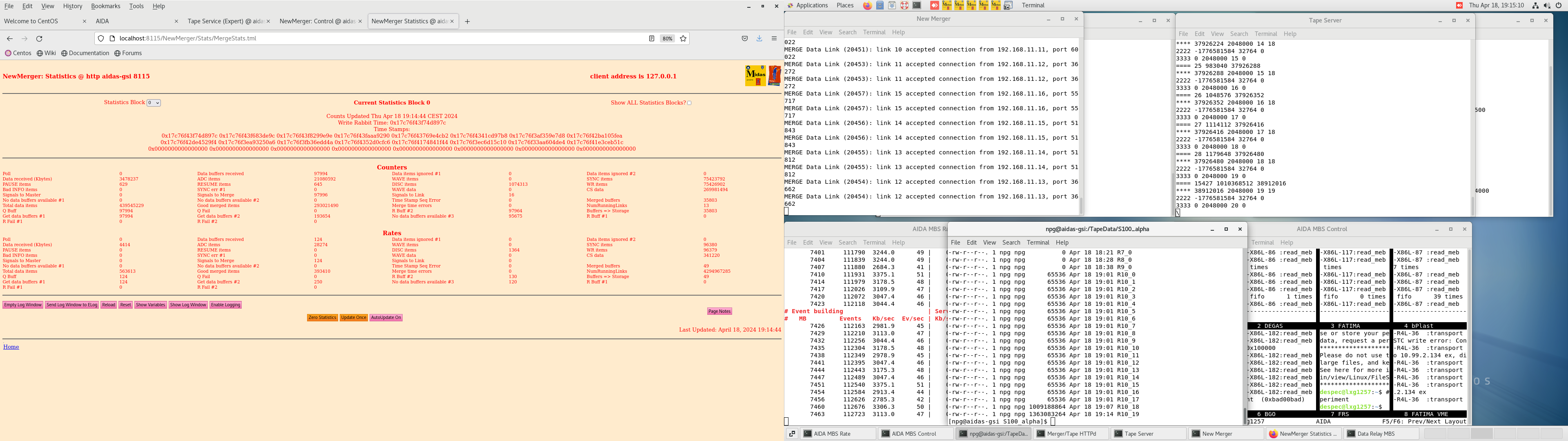

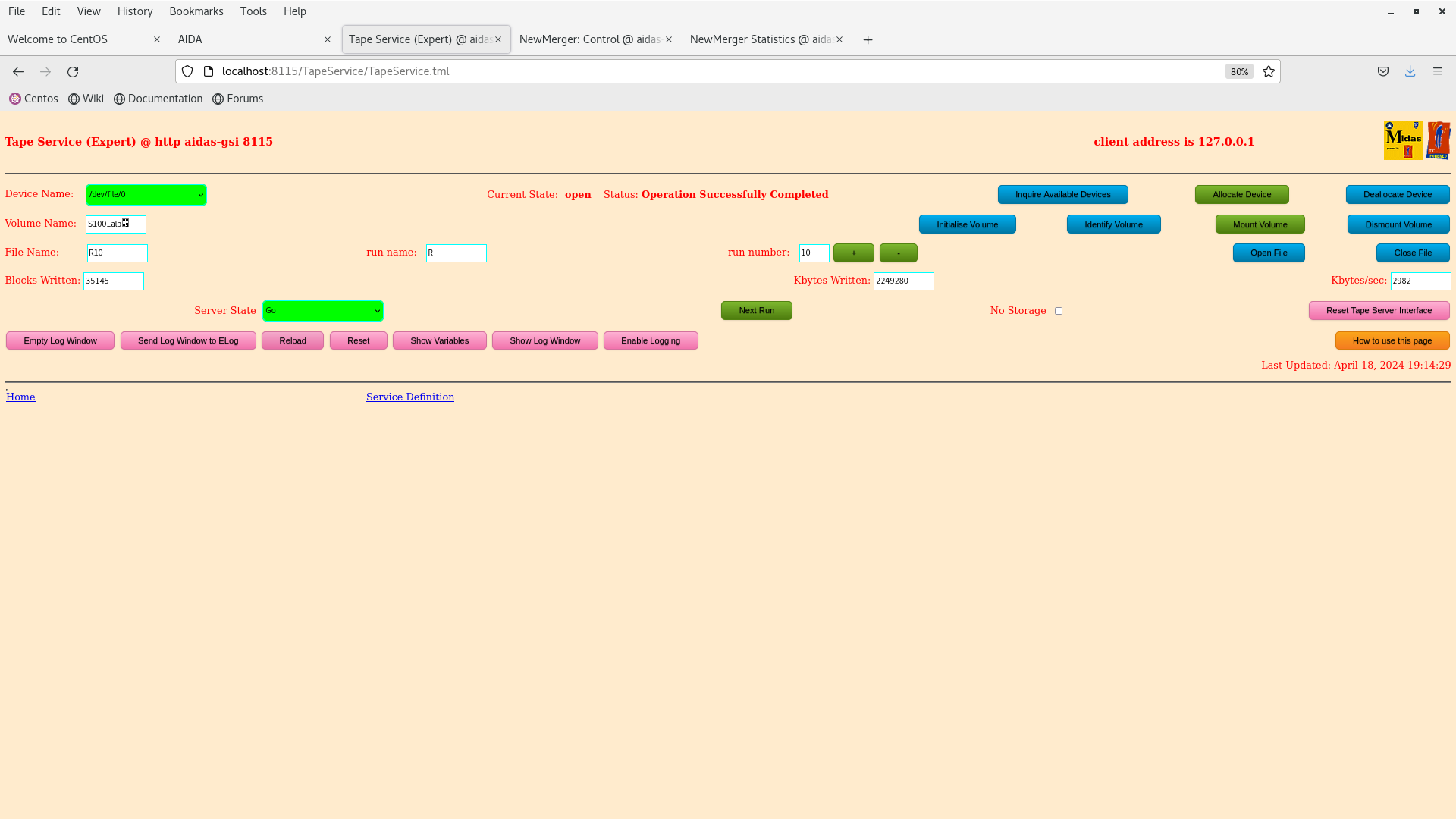

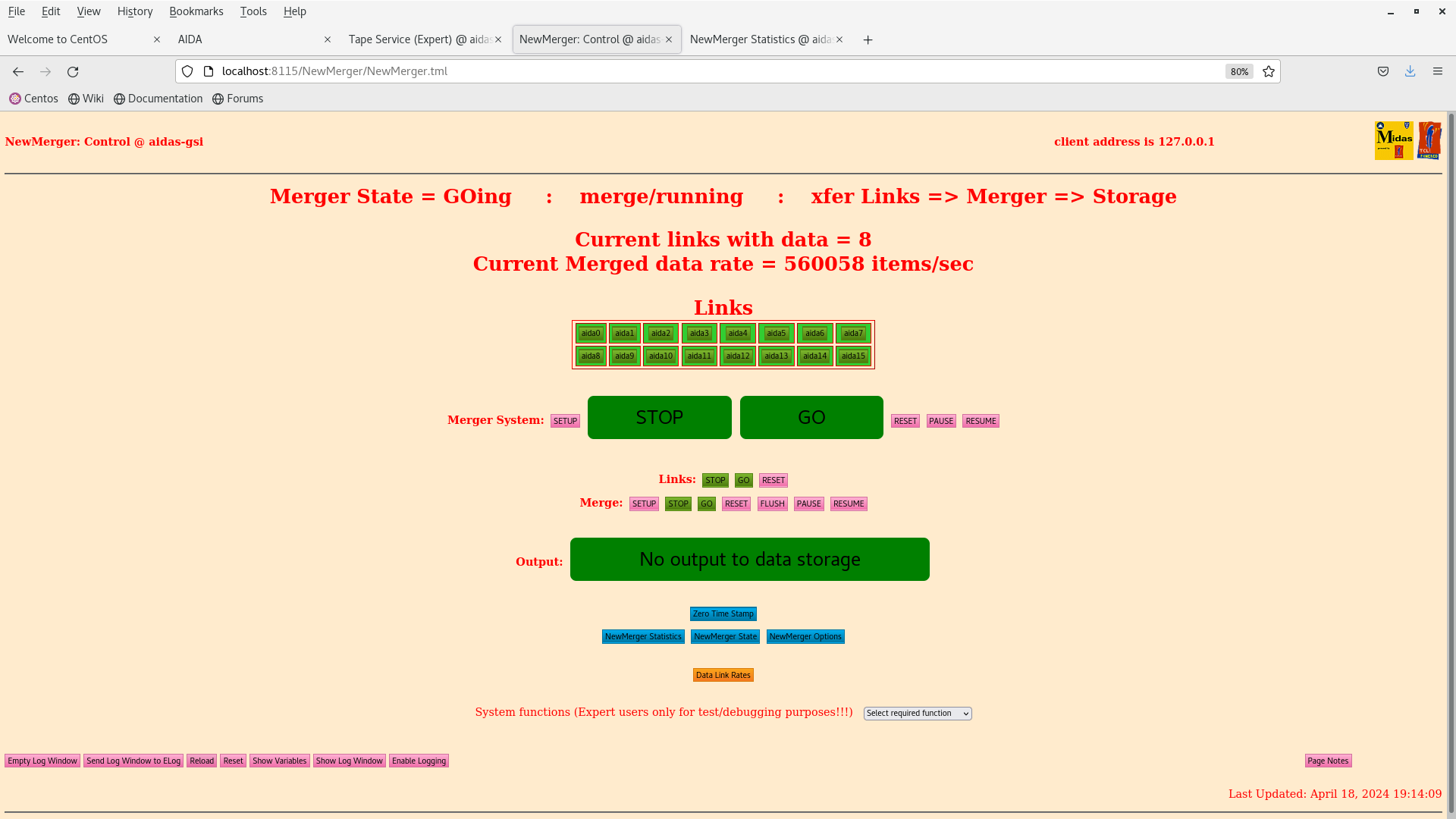

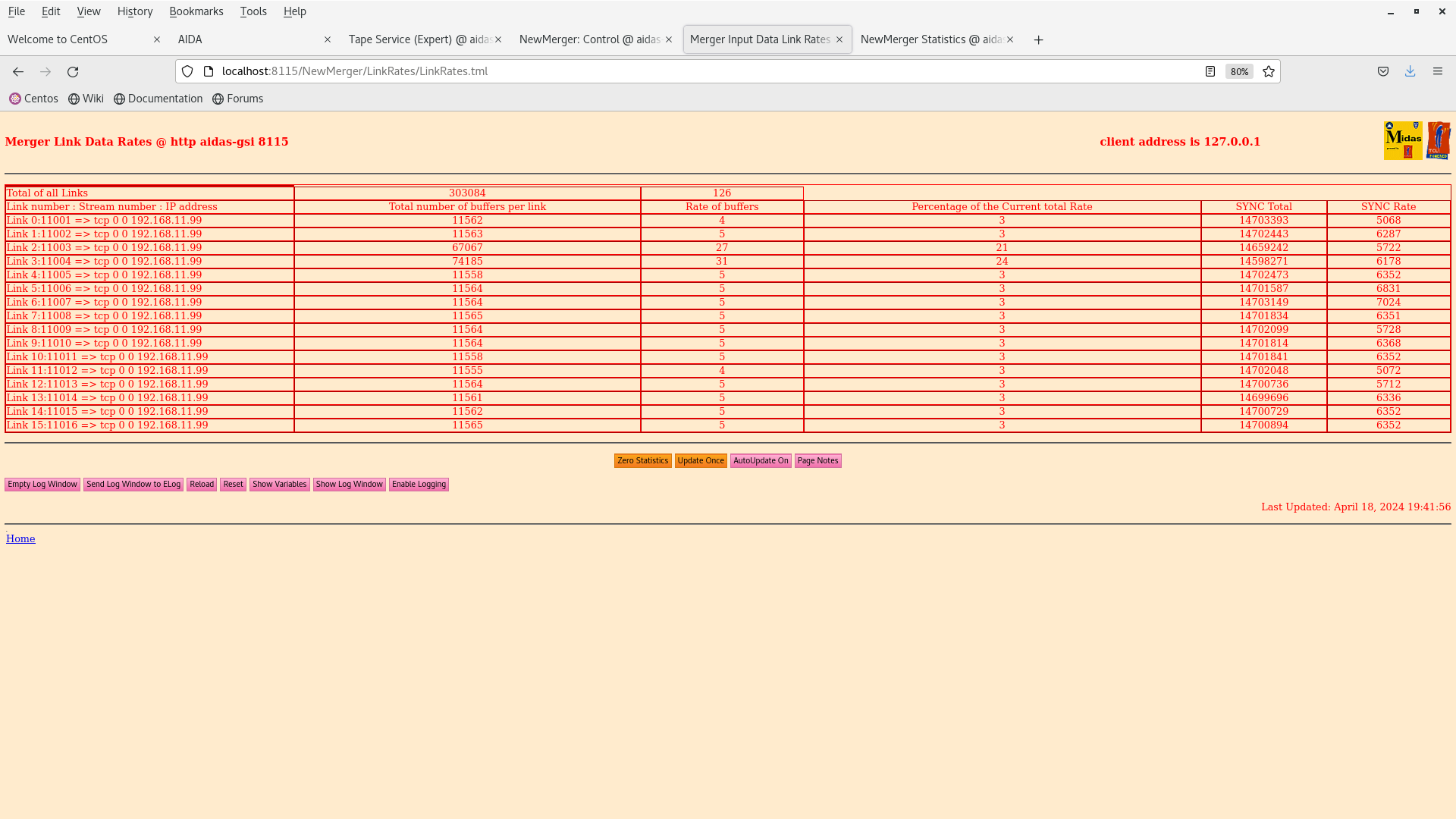

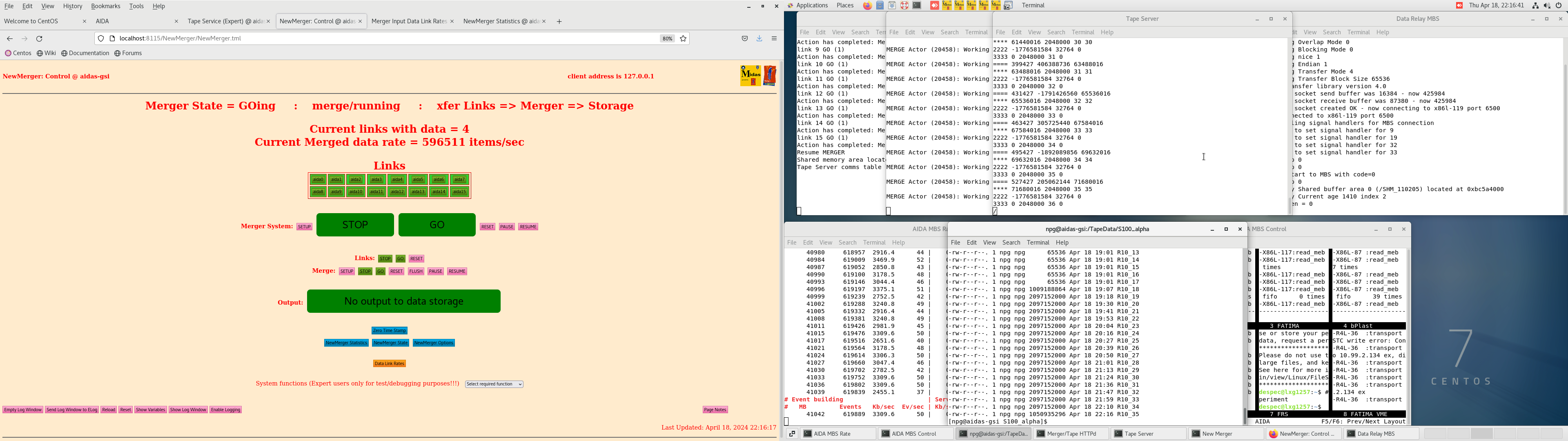

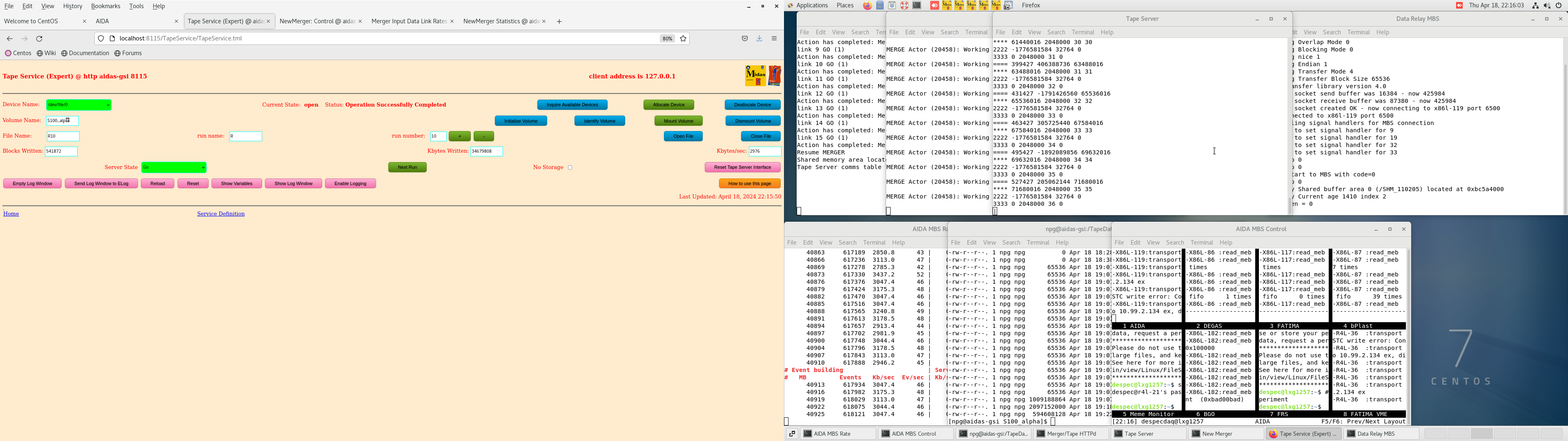

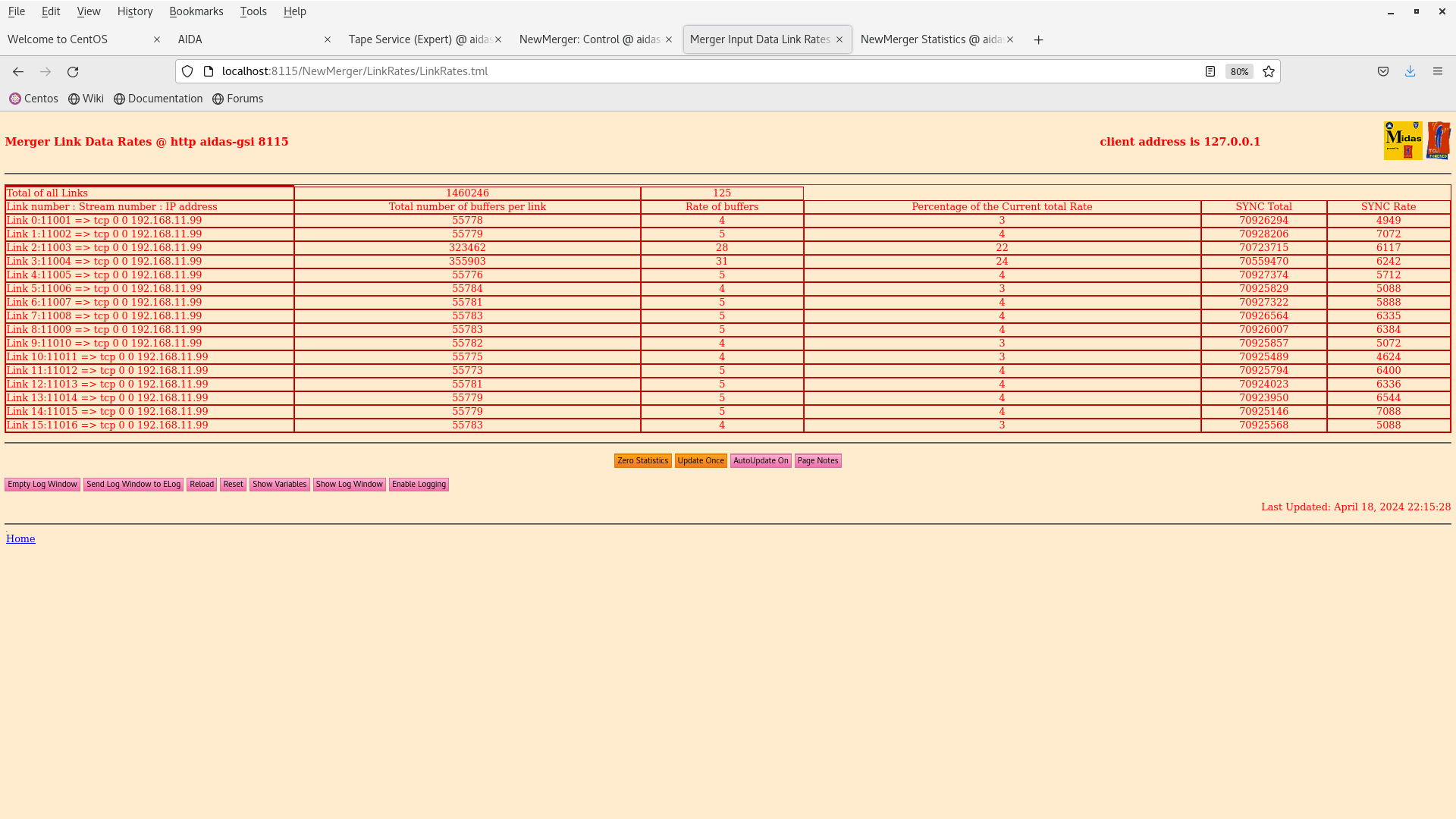

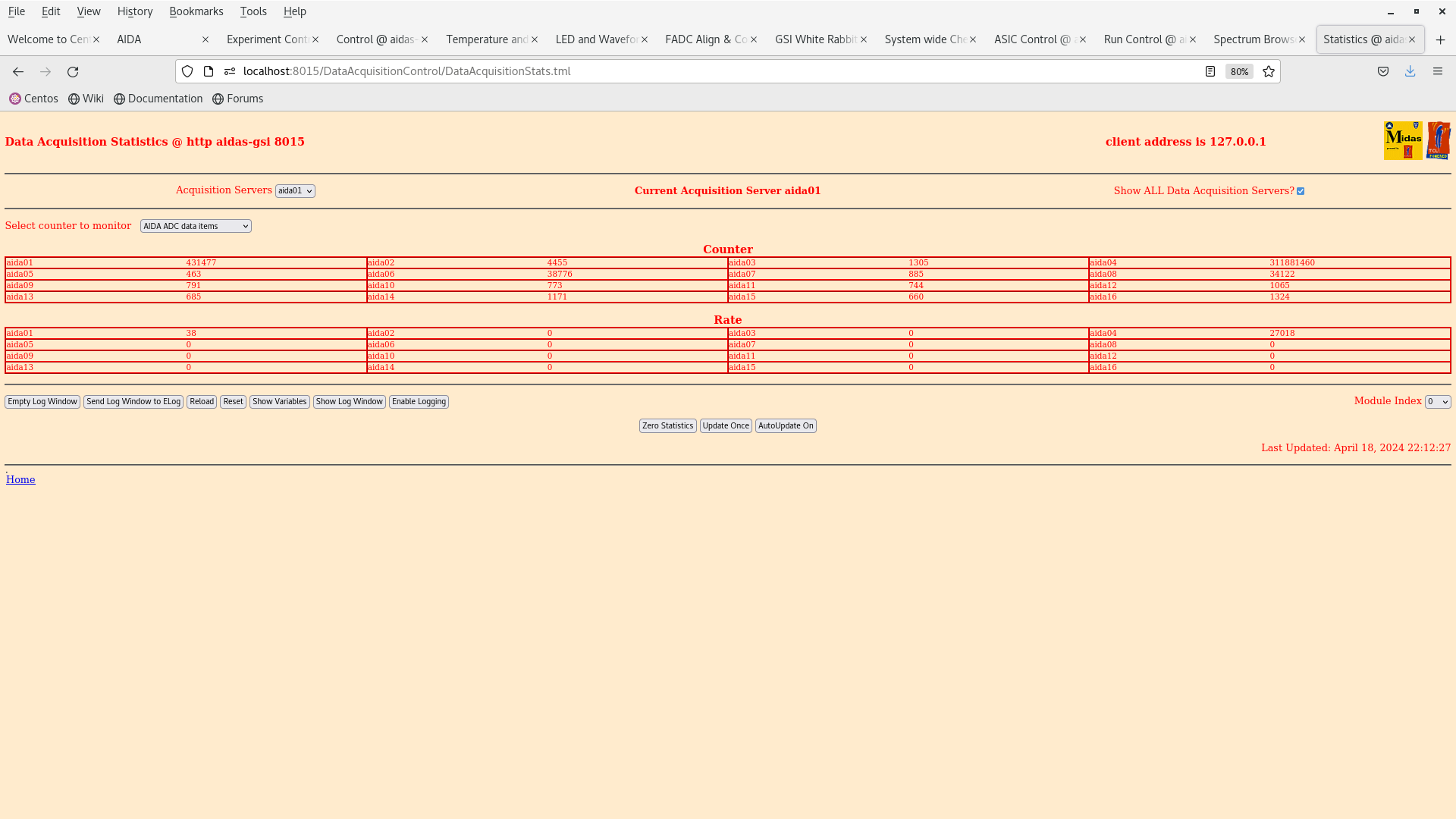

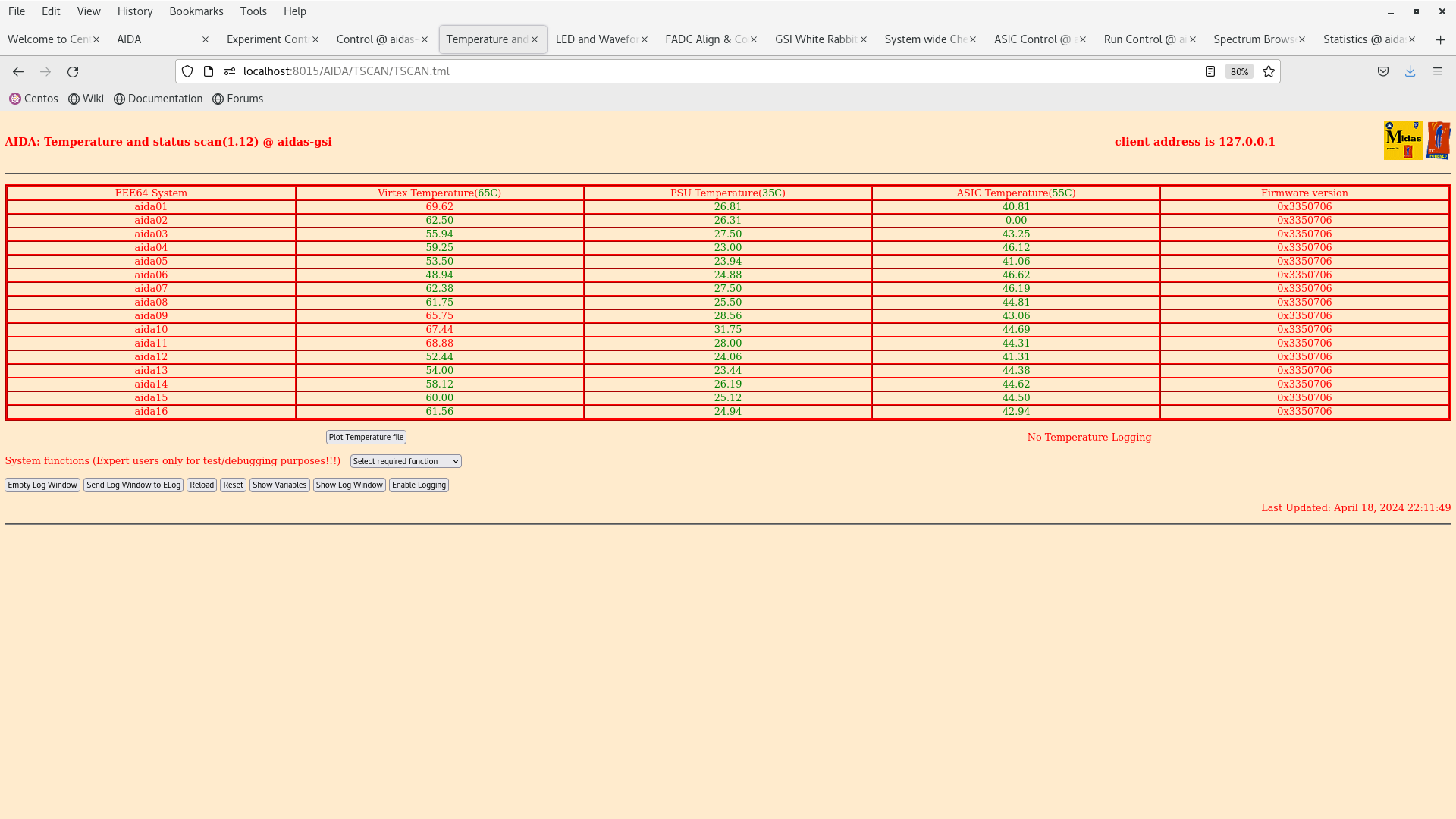

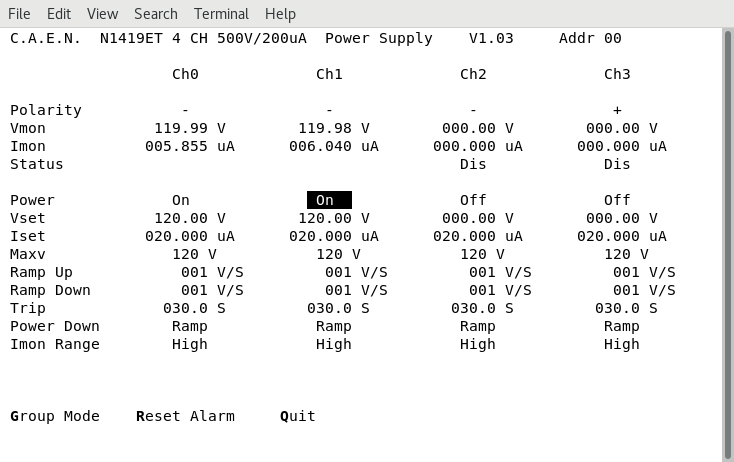

JB, TD | Thursday 18 April |

09.52 DAQ continues file S100_alpha/R5

note merger not functioning correctly due to aida03, aida04 & aida09 out of WR sequence

DSSSD bias & leakage current OK - attachment 1

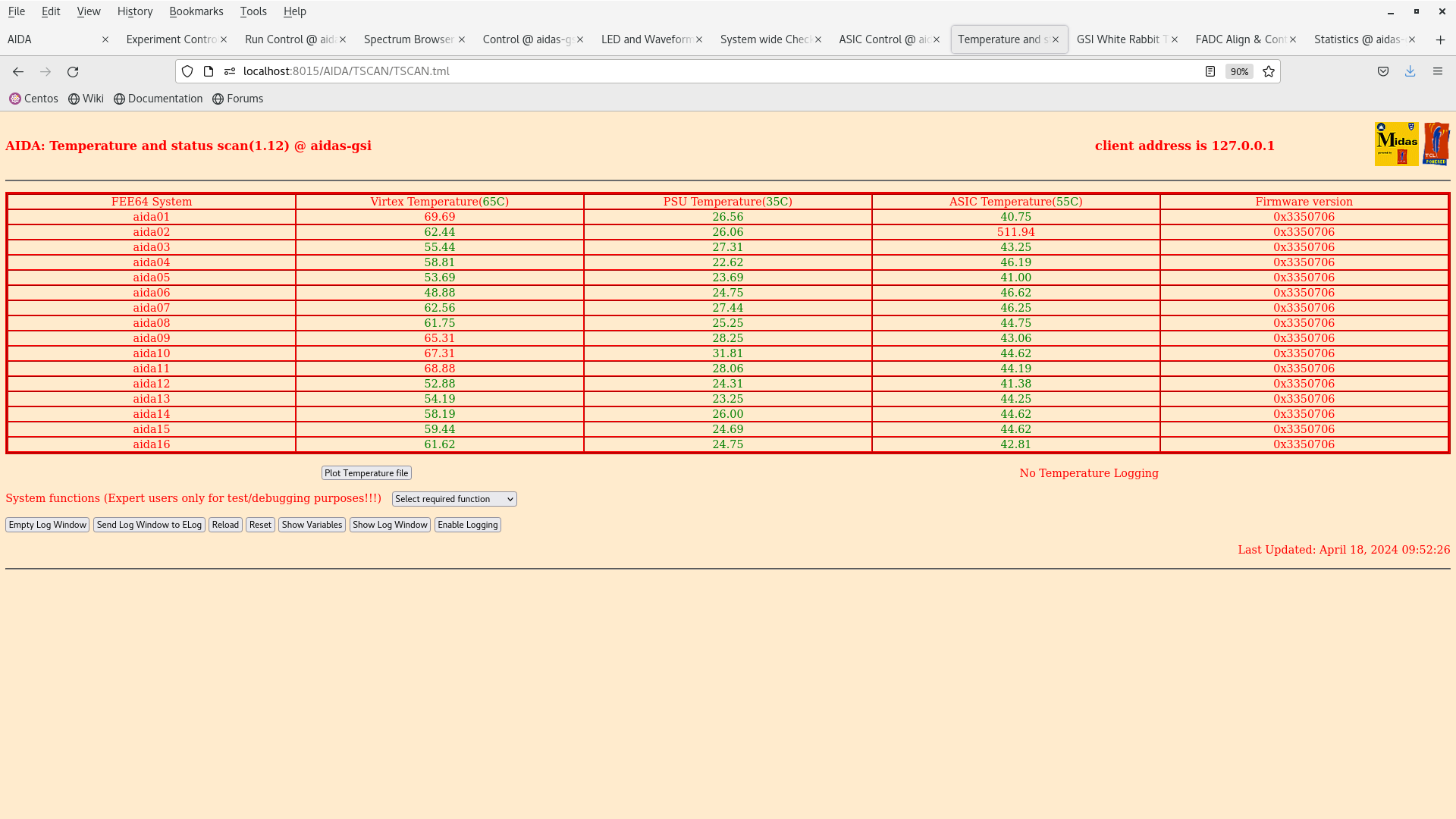

FEE64 temps OK - attachment 2

*except* aida02 ASIC temp which is known to be u/s

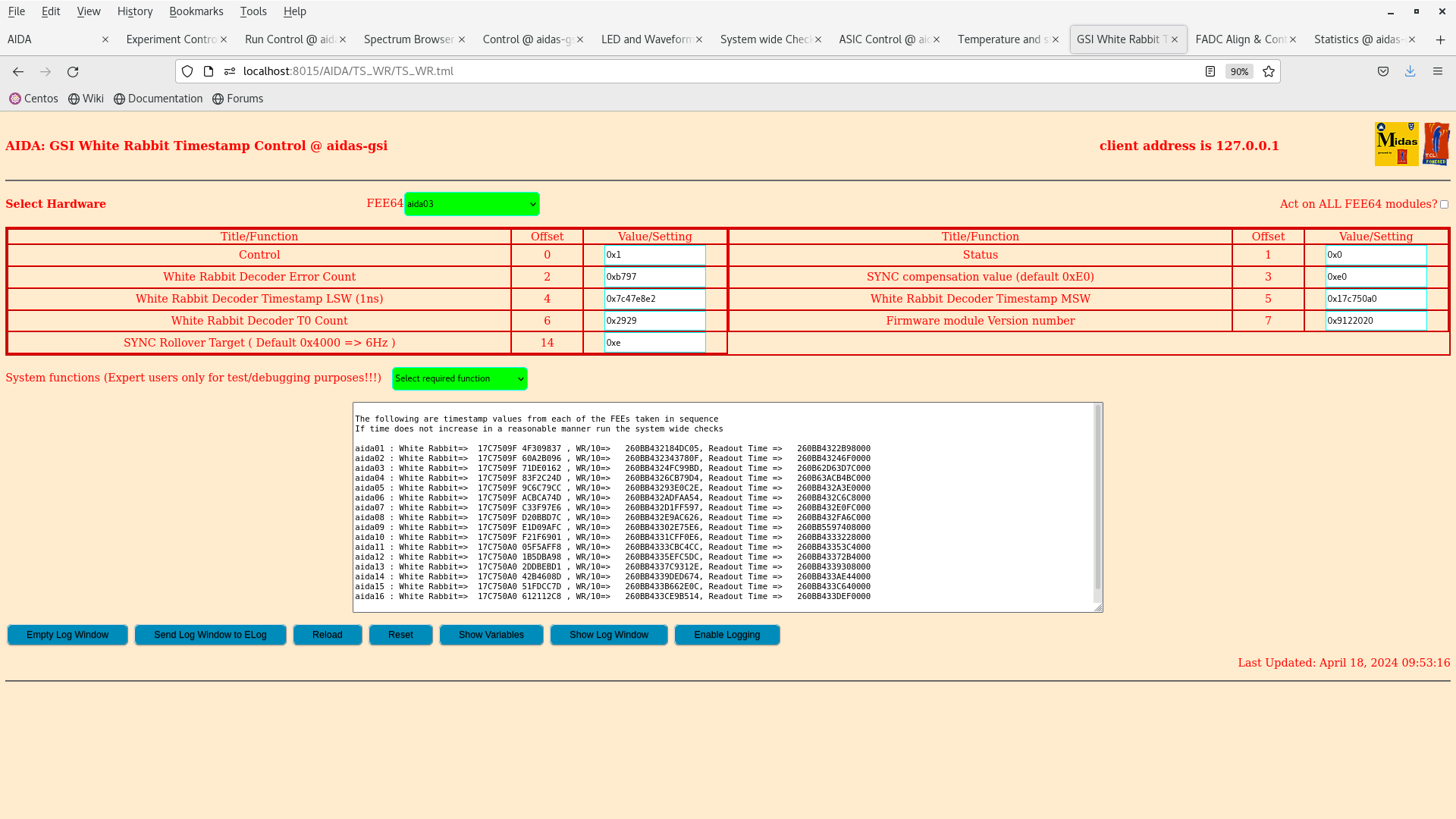

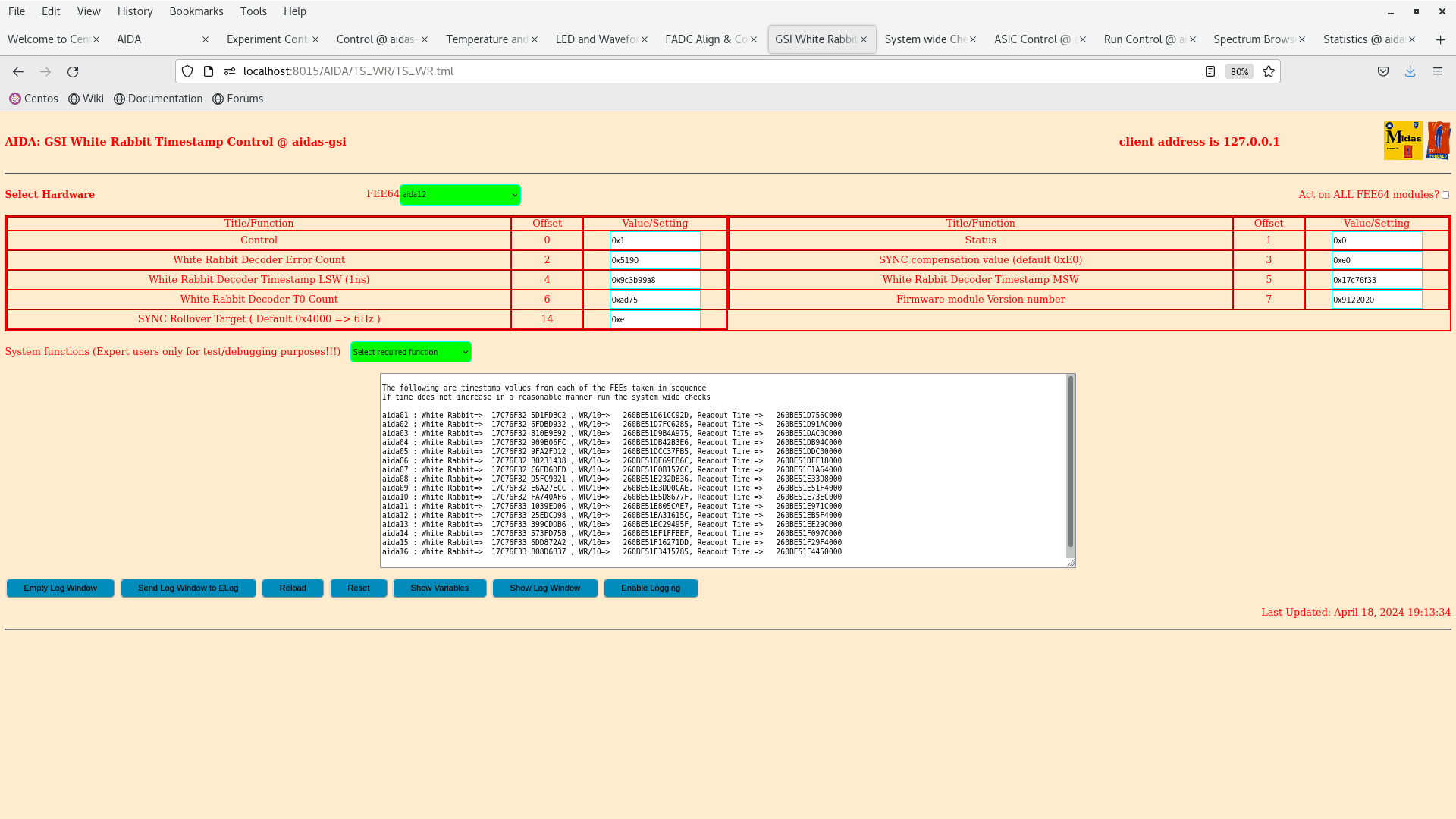

WR timestamps - attachment 3

aida03, aida04 & aida09 out of sequence

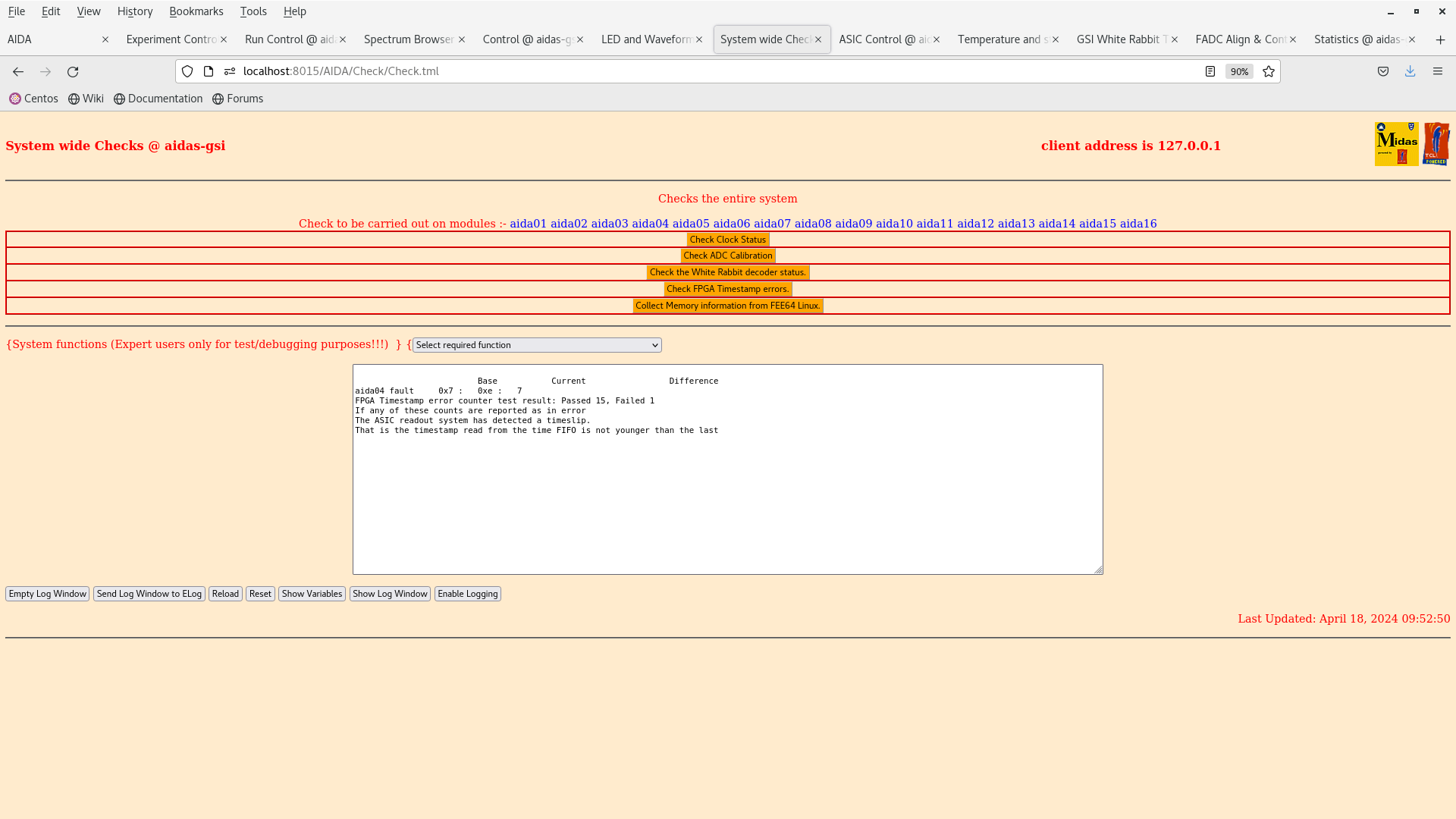

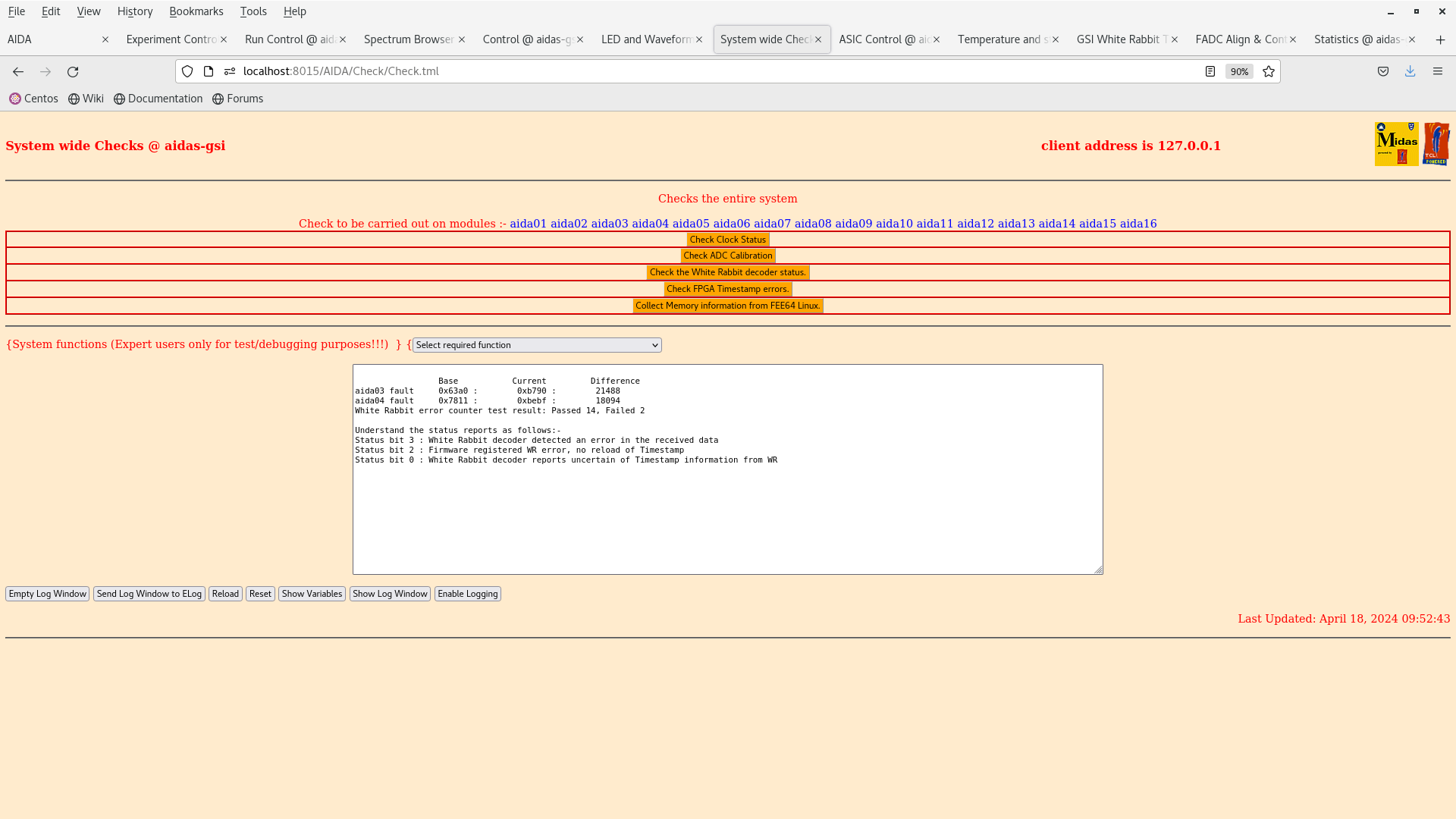

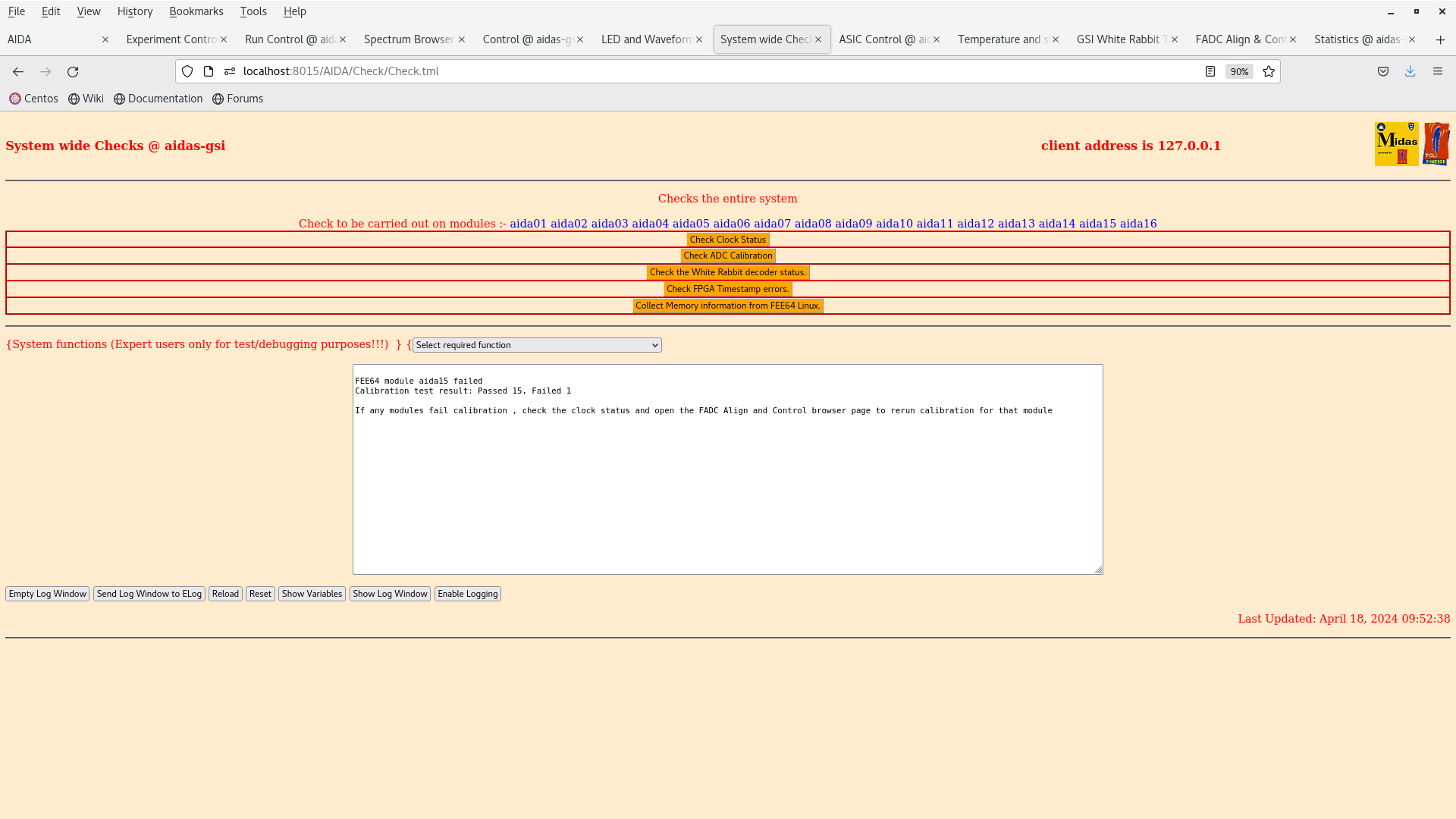

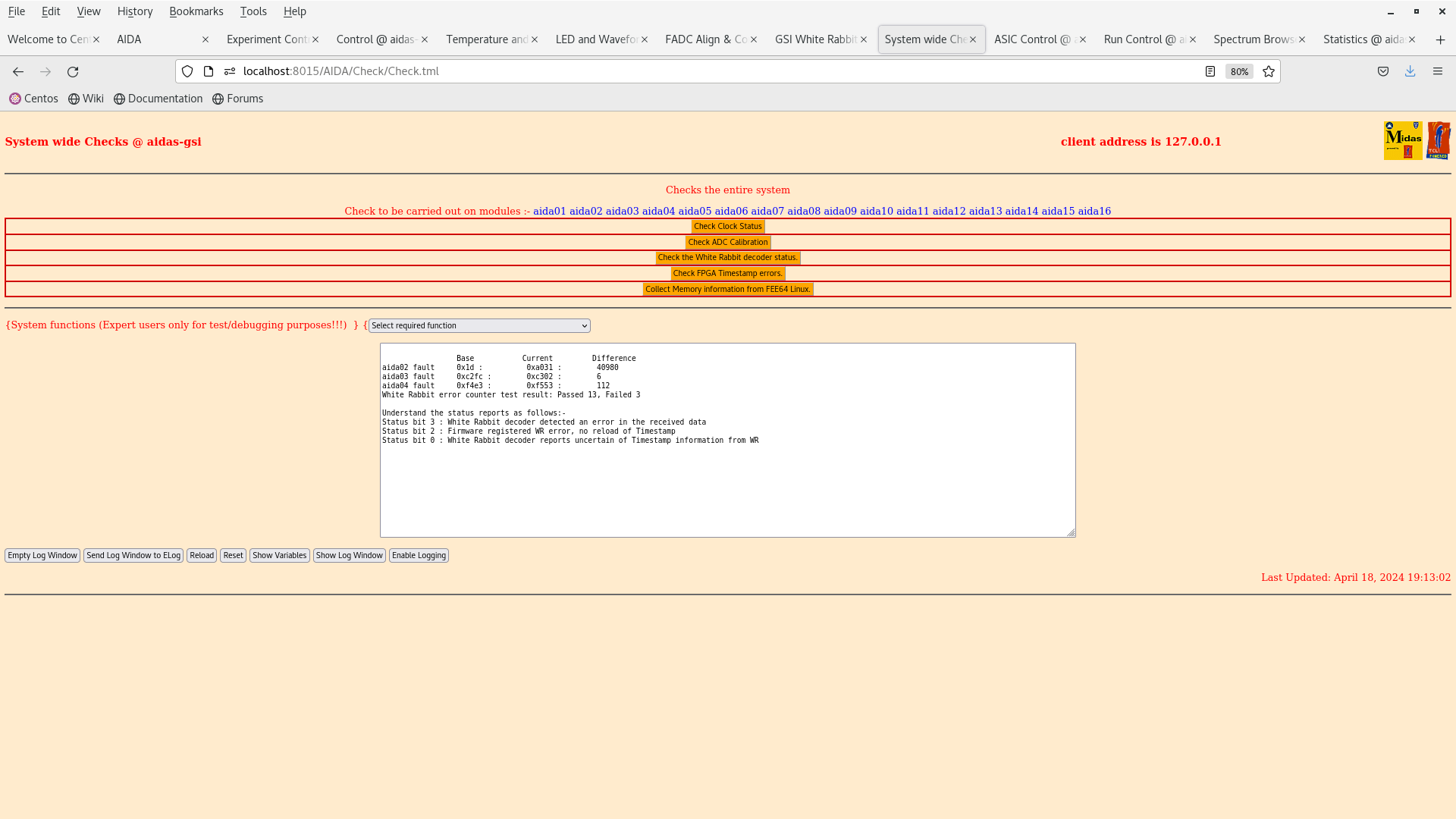

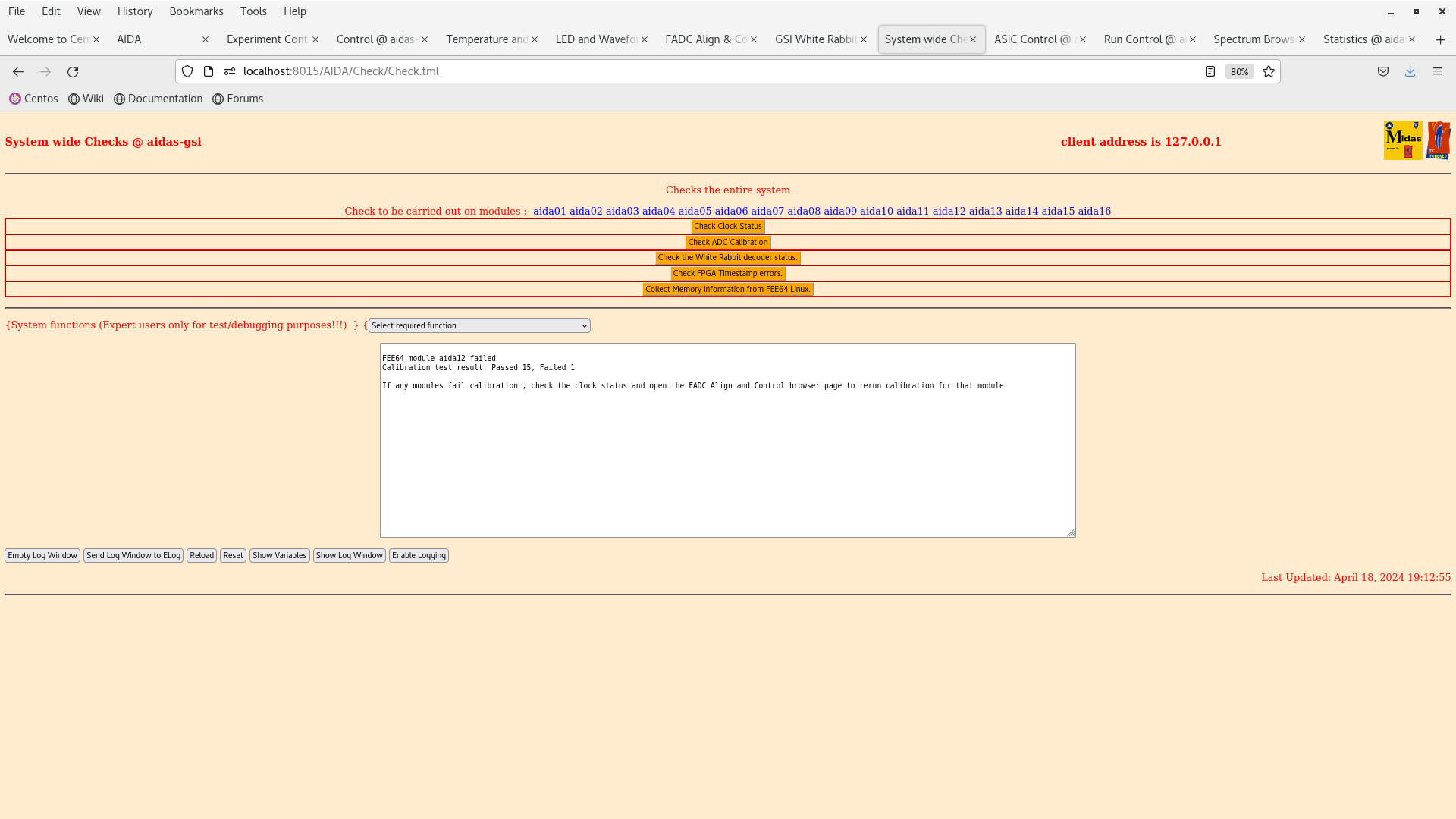

All system wide checks OK *except* ADC calibratio/FPGA/WR decoder status - attachments 4-6

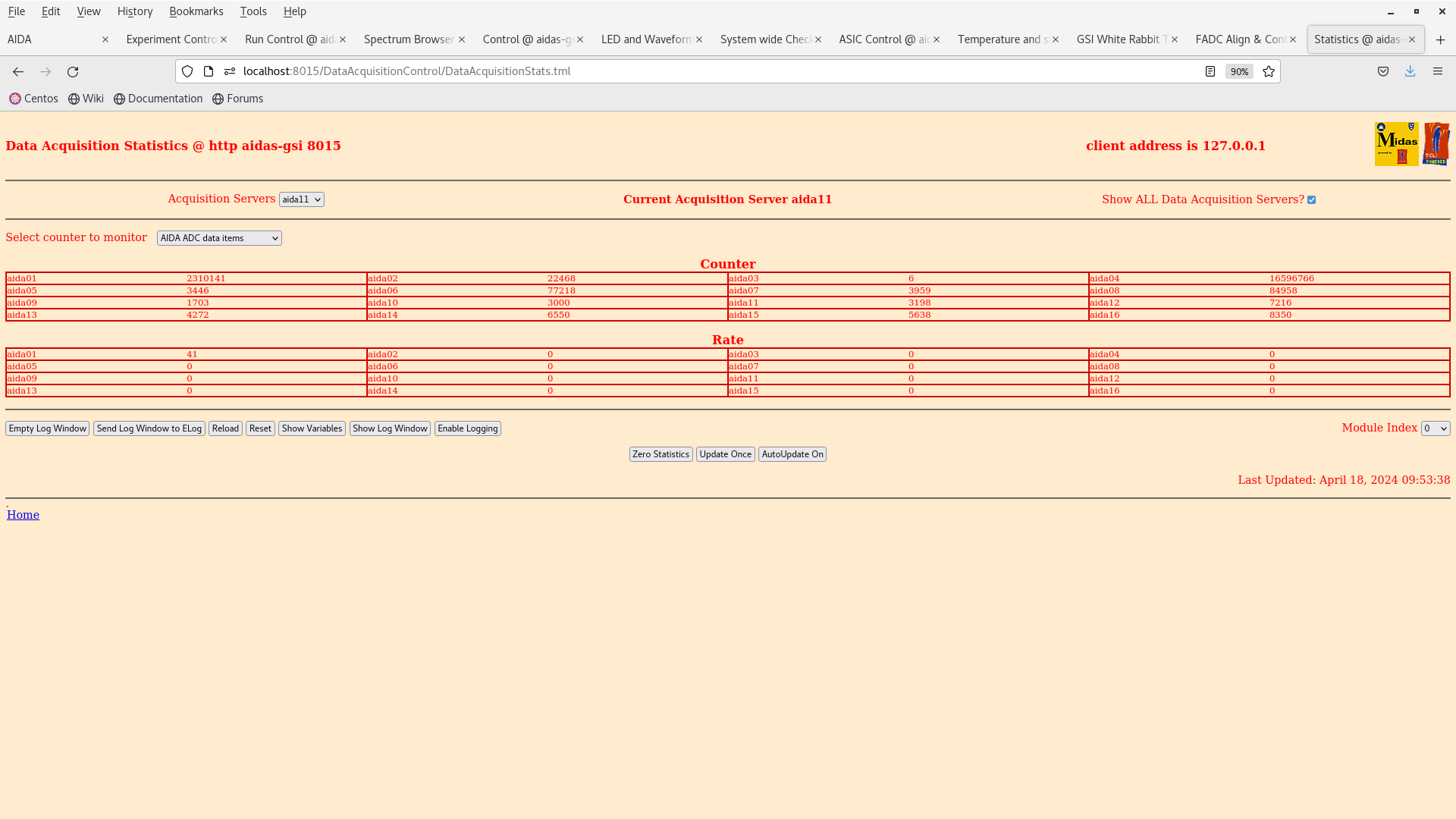

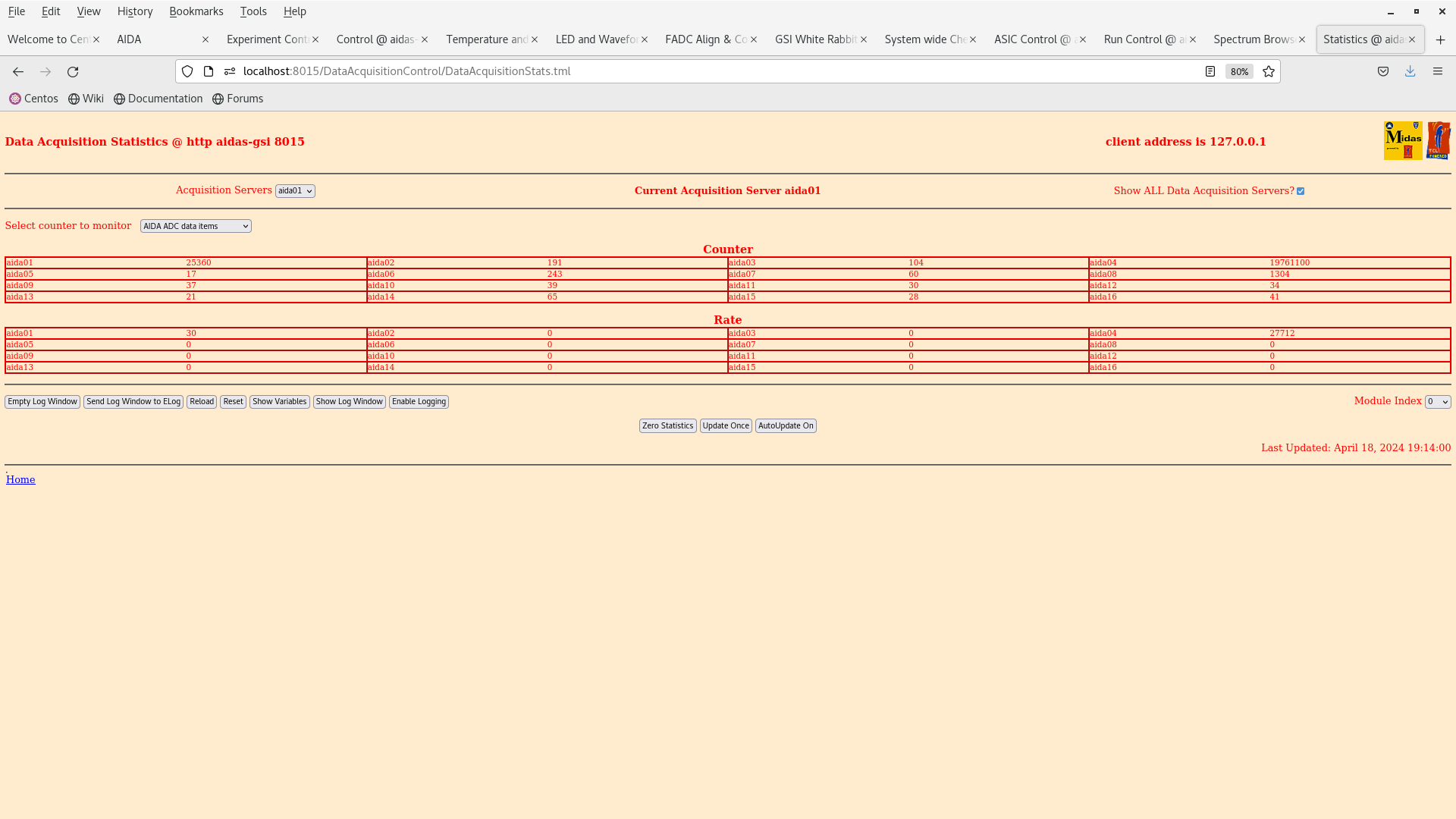

ADC data item stats - attachment 7

per FEE64 Stat spectra - attachment 8

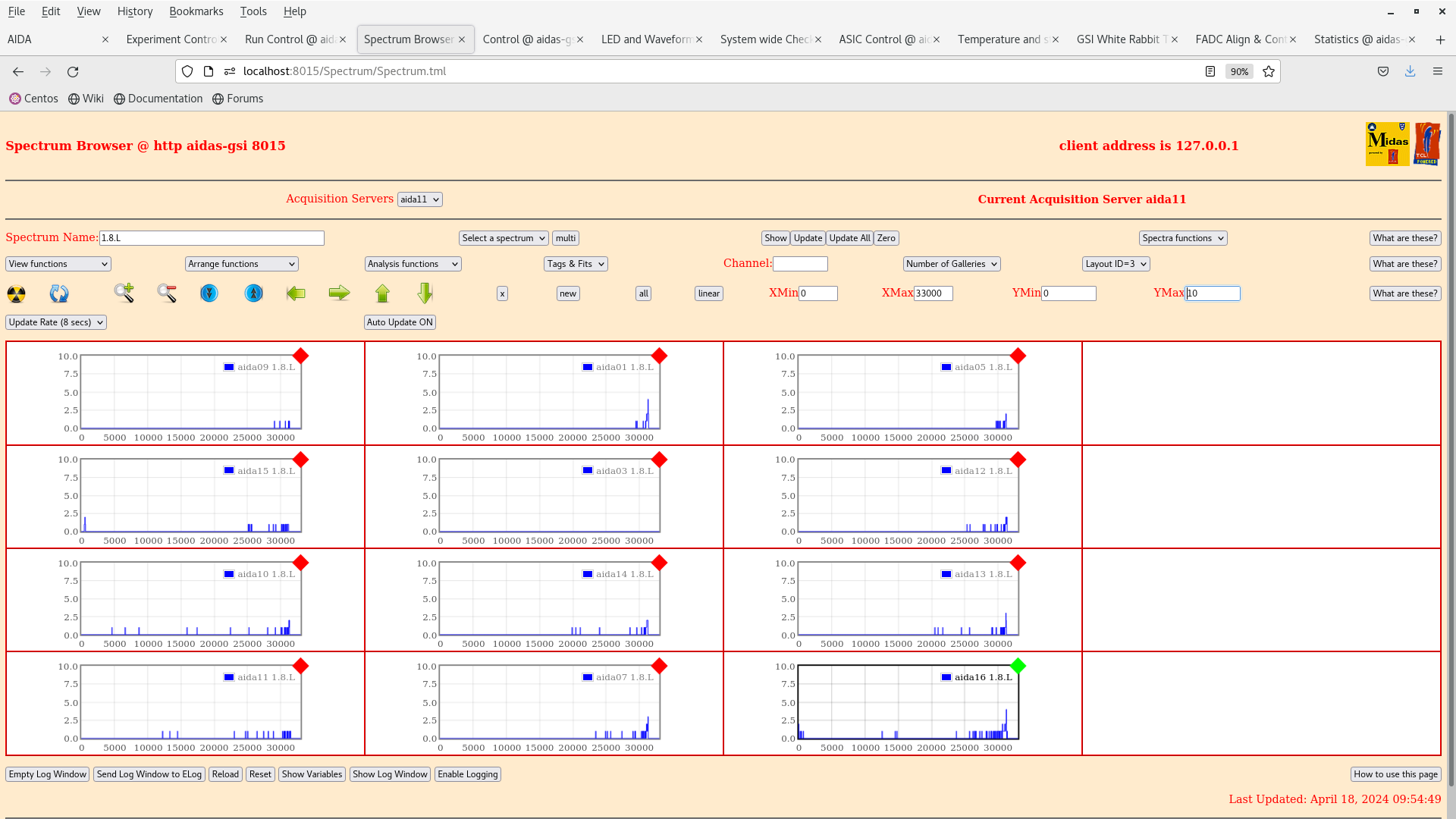

per FEE64 1.8.L spectra - attachments 9-10

per FEE64 1.8.W spectra - 20us FSR - attachments 11-12

Merger, TapeServer & Link Data Rates - attachments 13-15

Grafana - attachment 16

DSSSD bias/leakage current trends OK

19.15 alpha background file S100_alpha/R10

DSSSD bias & leakage current OK - attachment 17

FEE64 temps OK - attachment 18

*except* aida02 ASIC temp which is known to be u/s

All system wide checks OK *except* ADC calibratio/FPGA/WR decoder status - attachments 19-21

WR timestamps OK - attachment 22

ADC data item stats - attachment 23

Merger, TapeServer & Meger stats - attachments 24-26

data rate c. 2.8Mb/s