| ID |

Date |

Author |

Subject |

|

635

|

Sun Jun 2 01:45:05 2024 |

TD | Sunday 2 June |

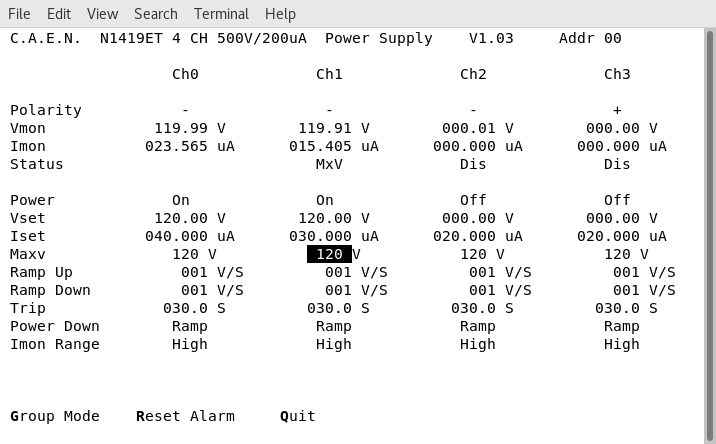

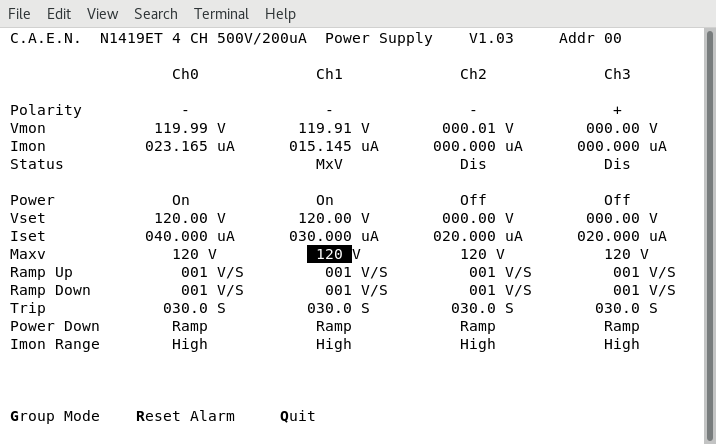

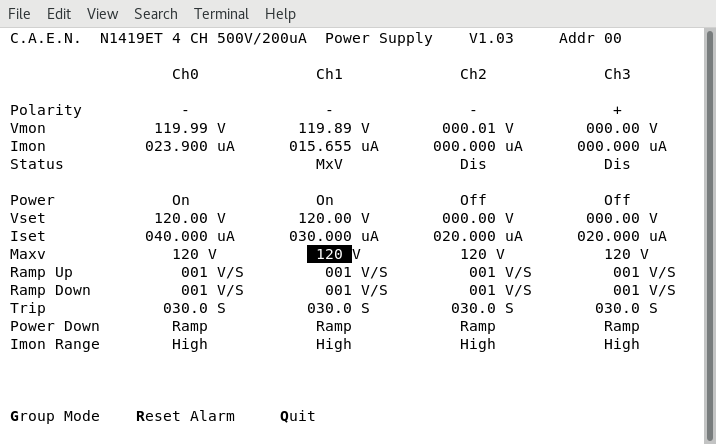

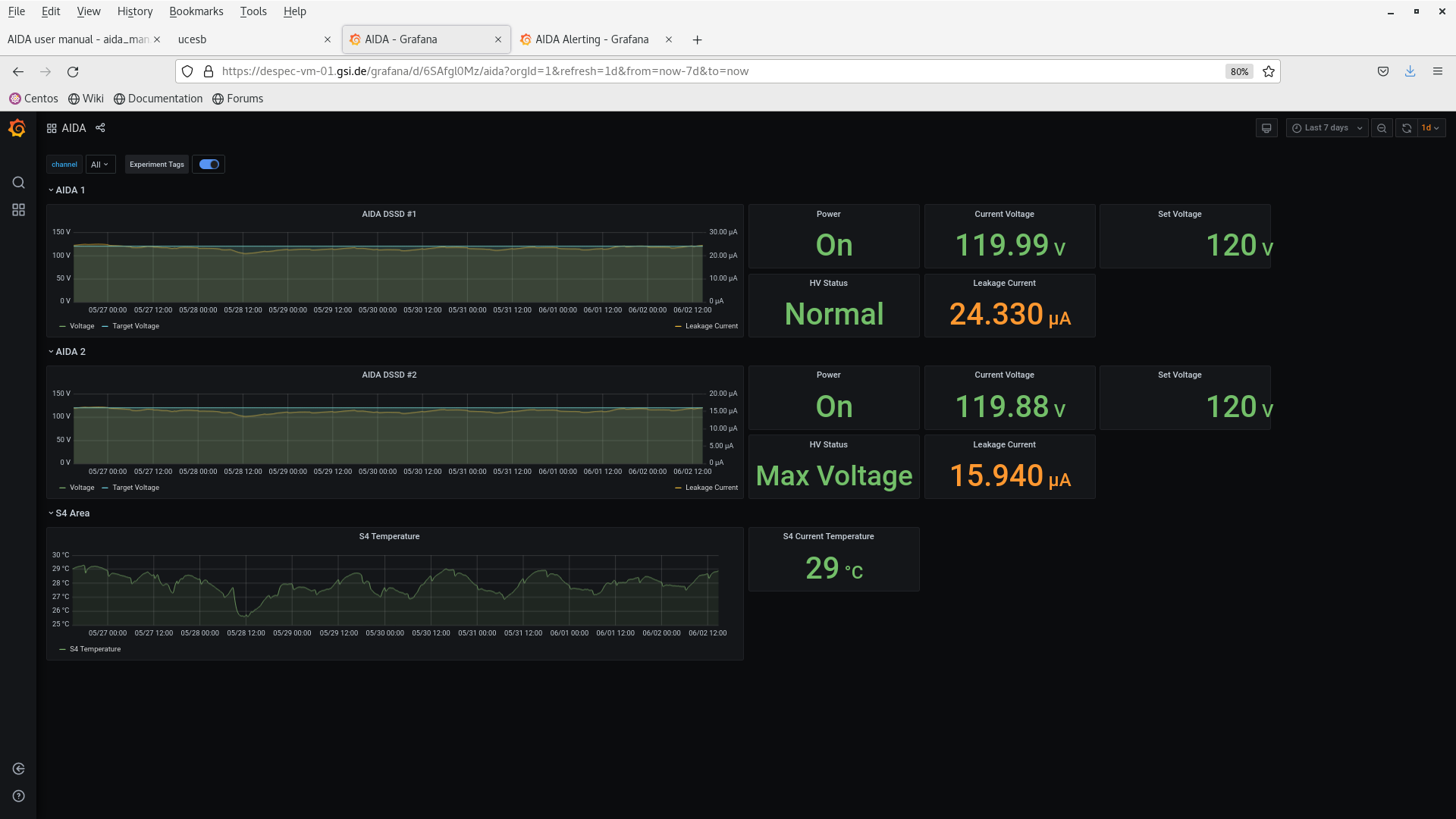

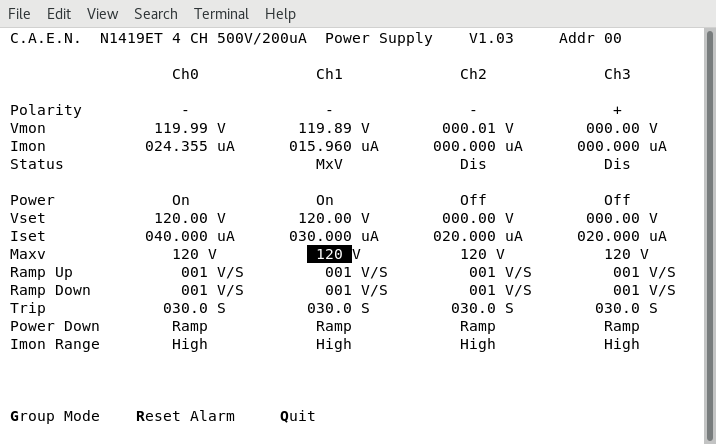

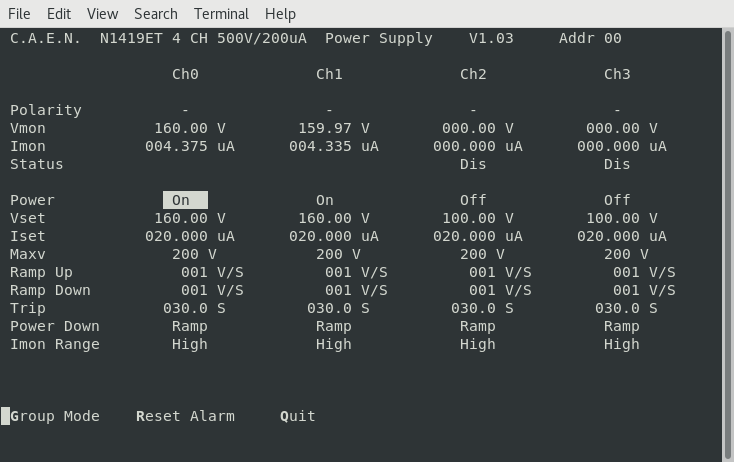

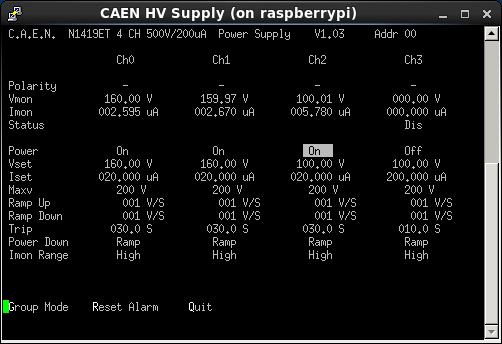

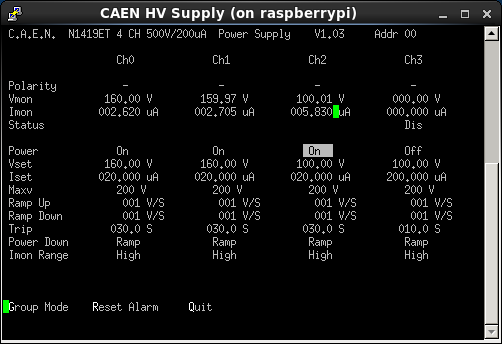

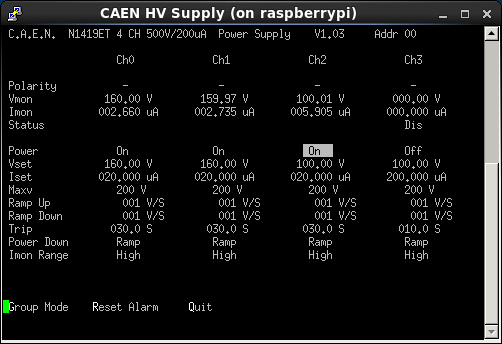

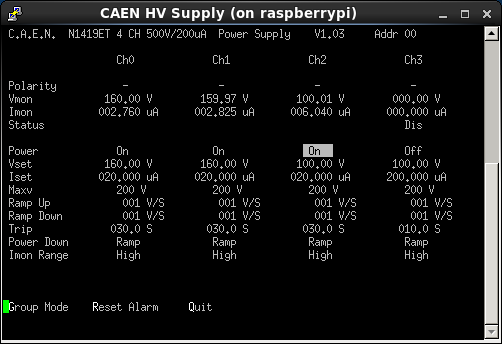

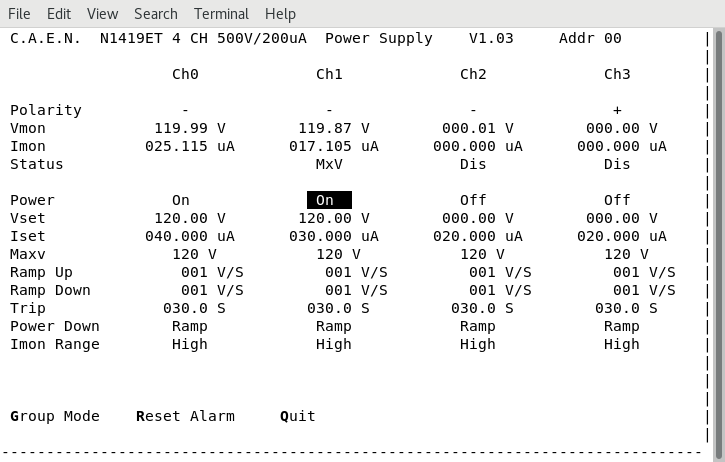

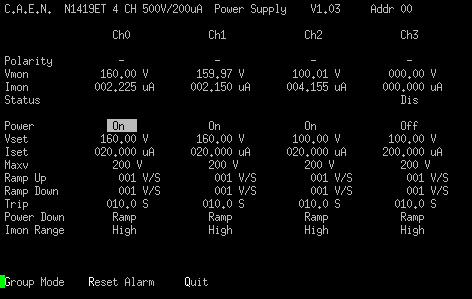

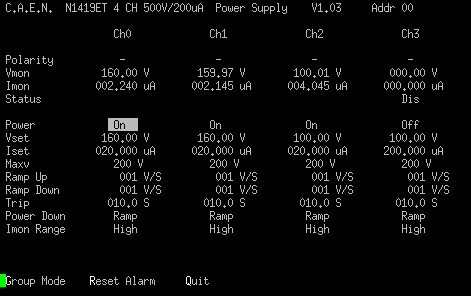

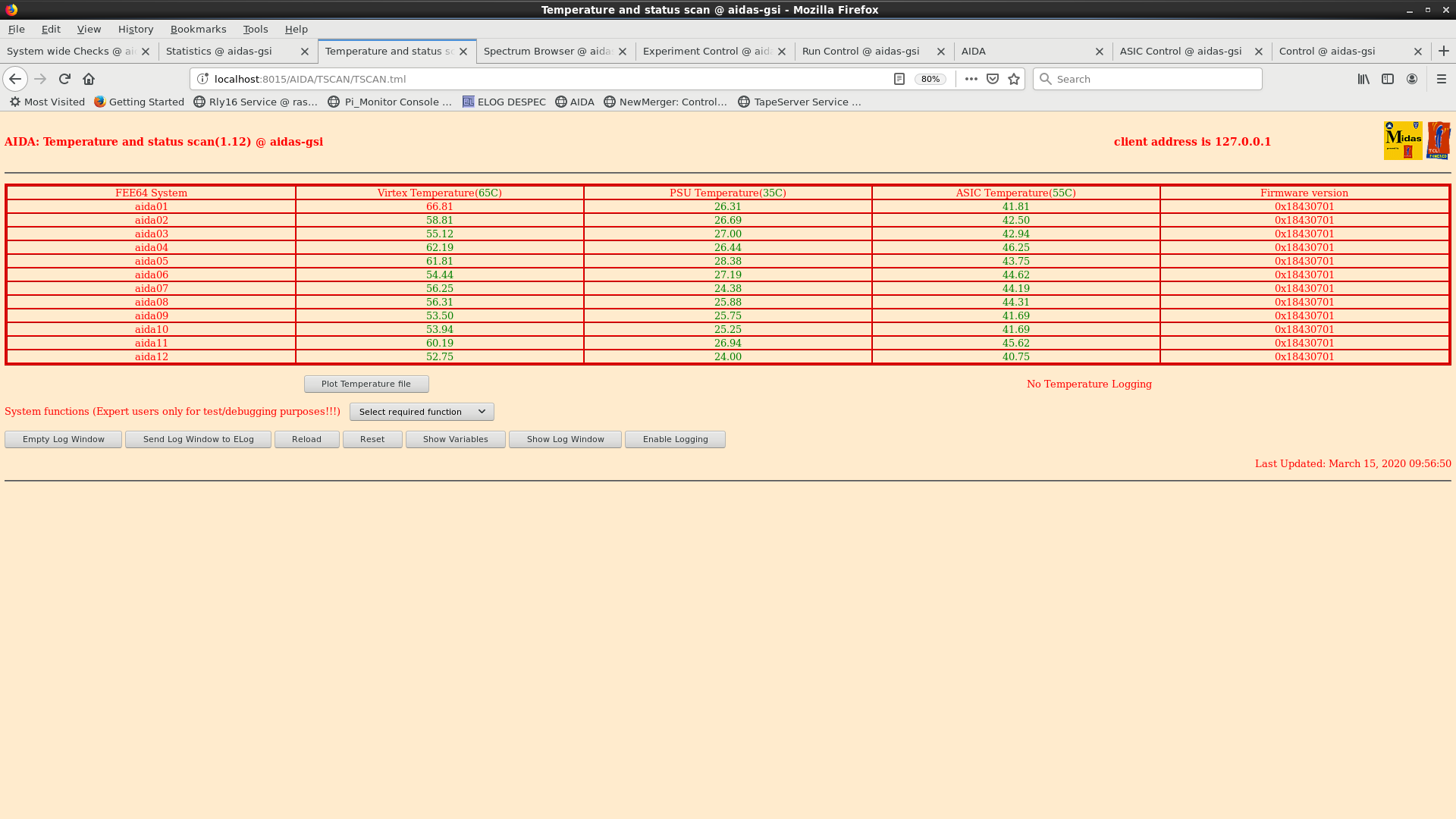

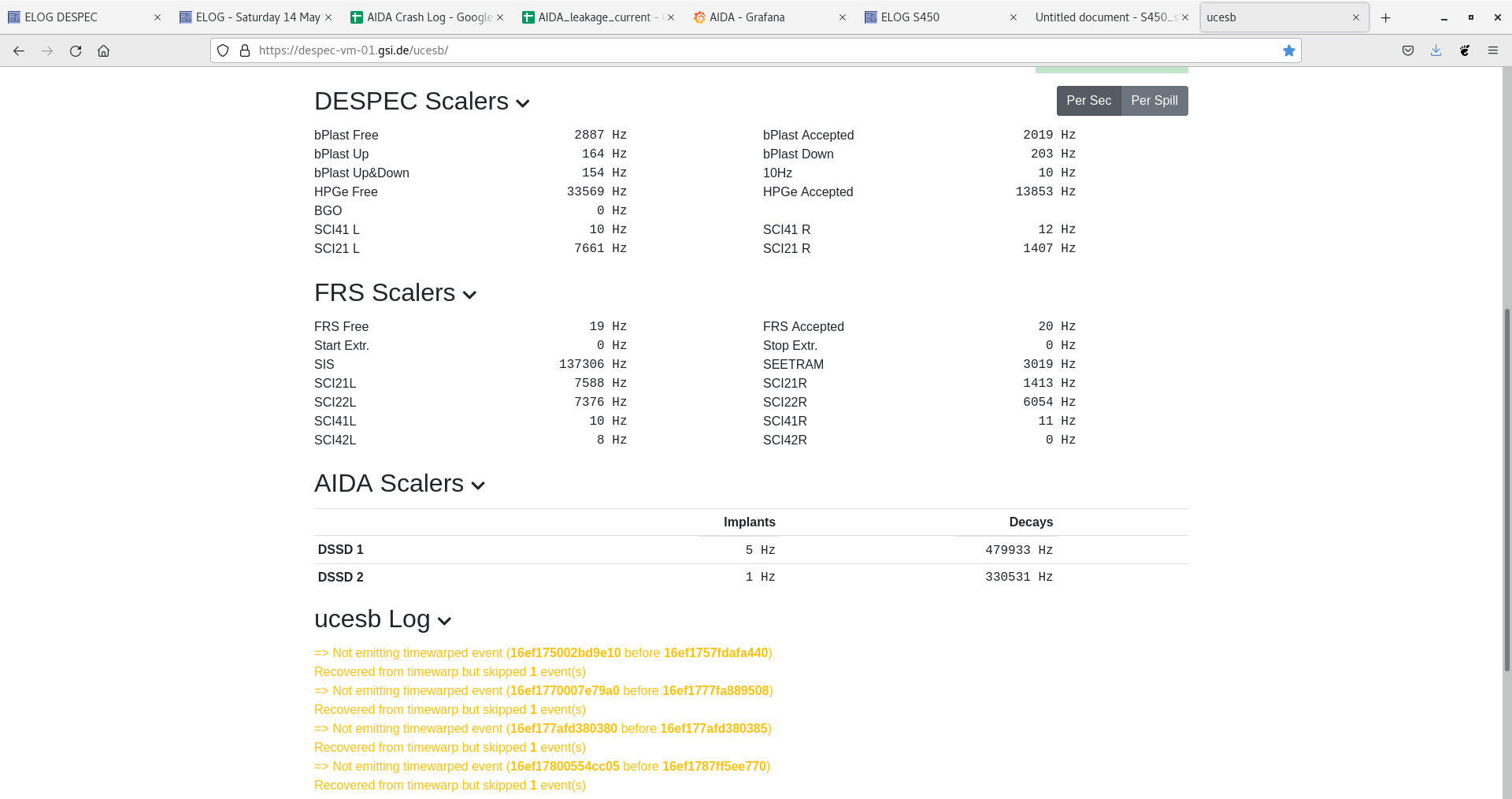

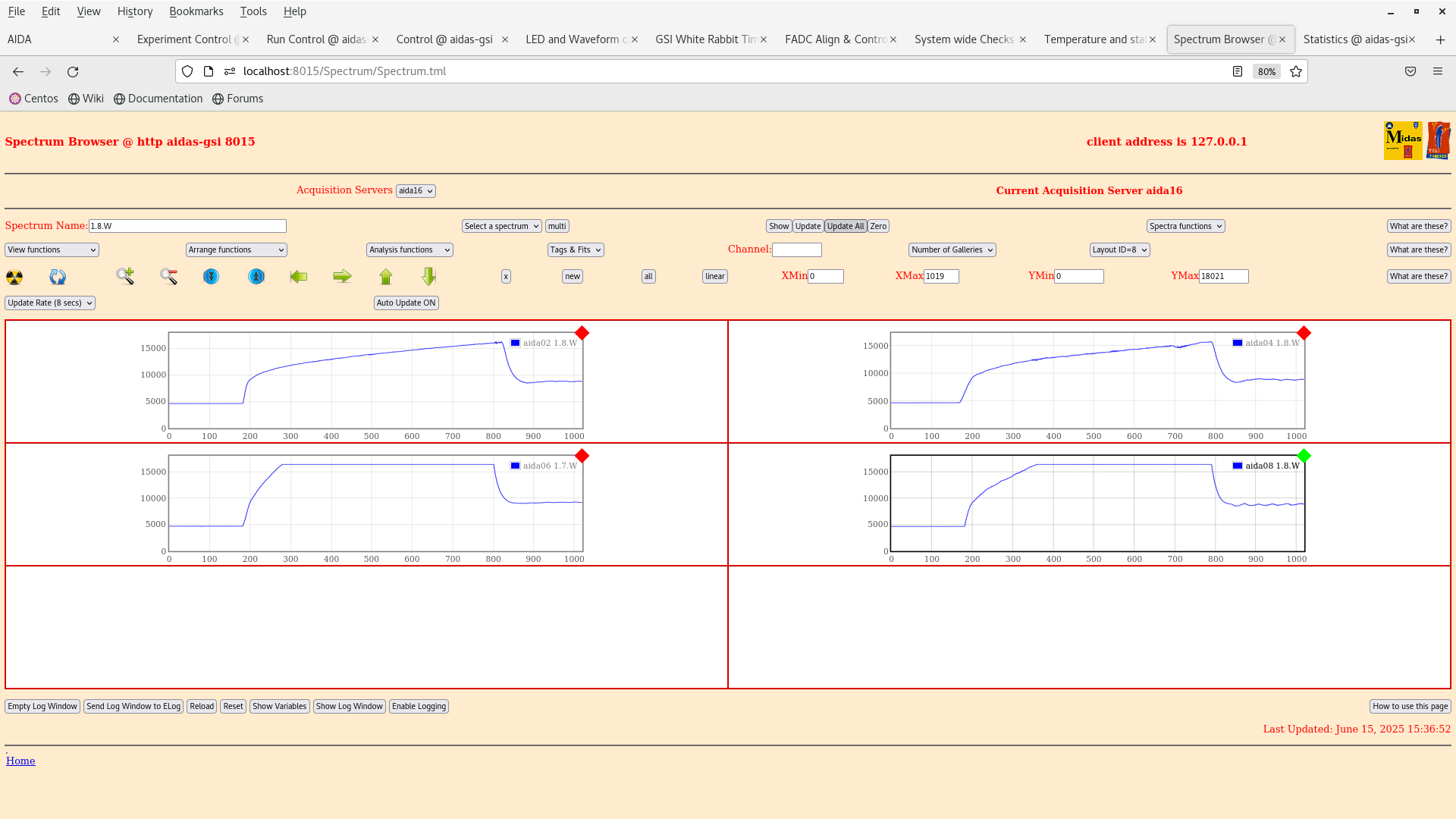

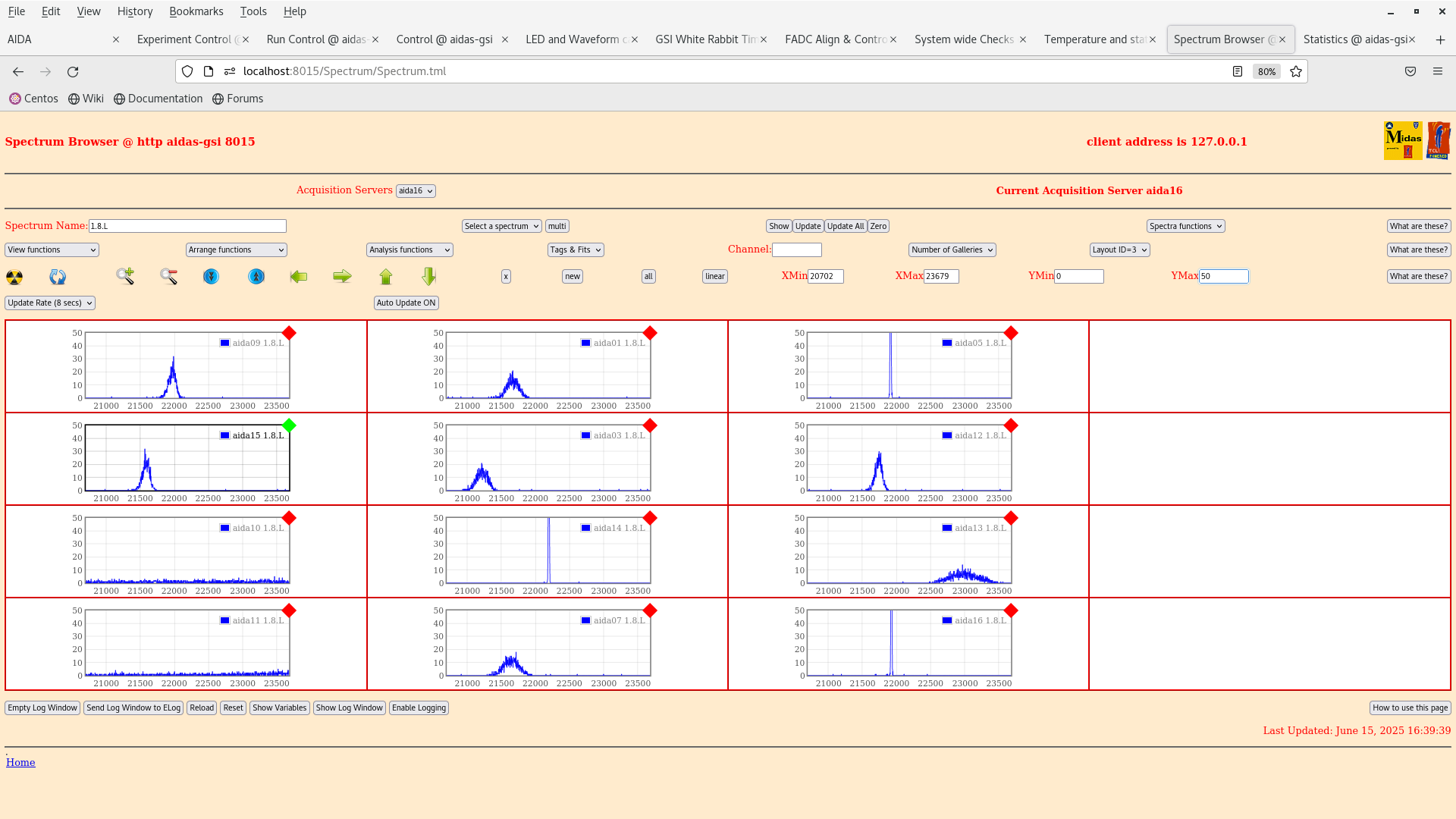

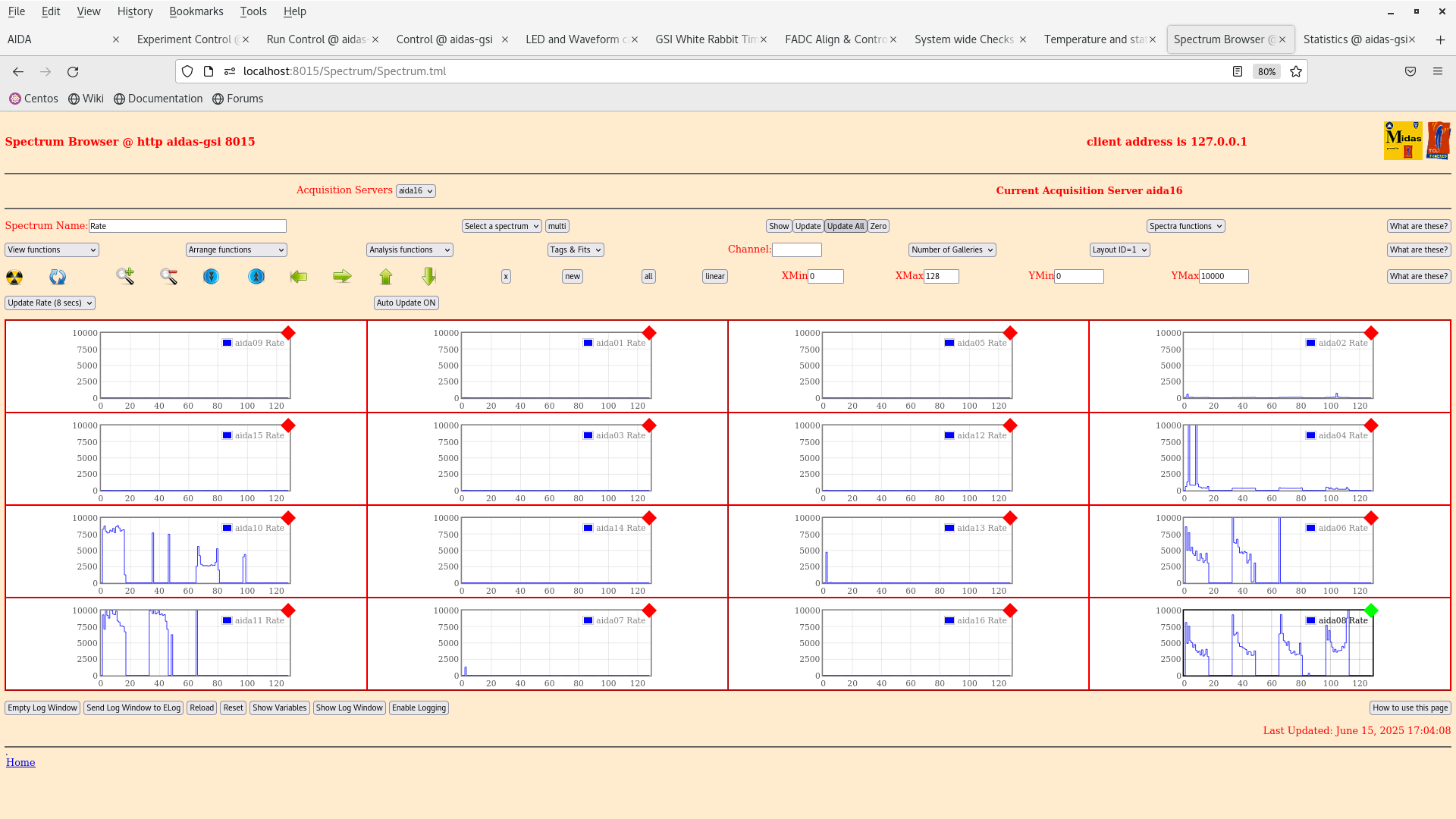

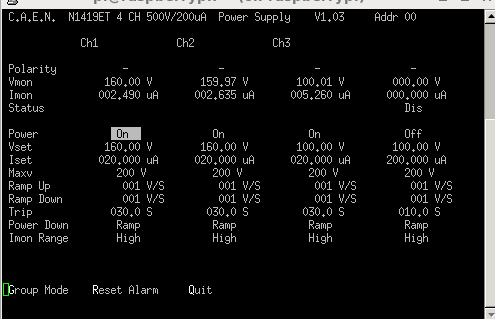

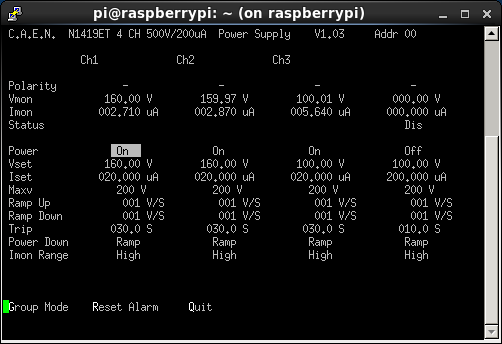

02.41 DSSSD bias & leakage current - attachment 1

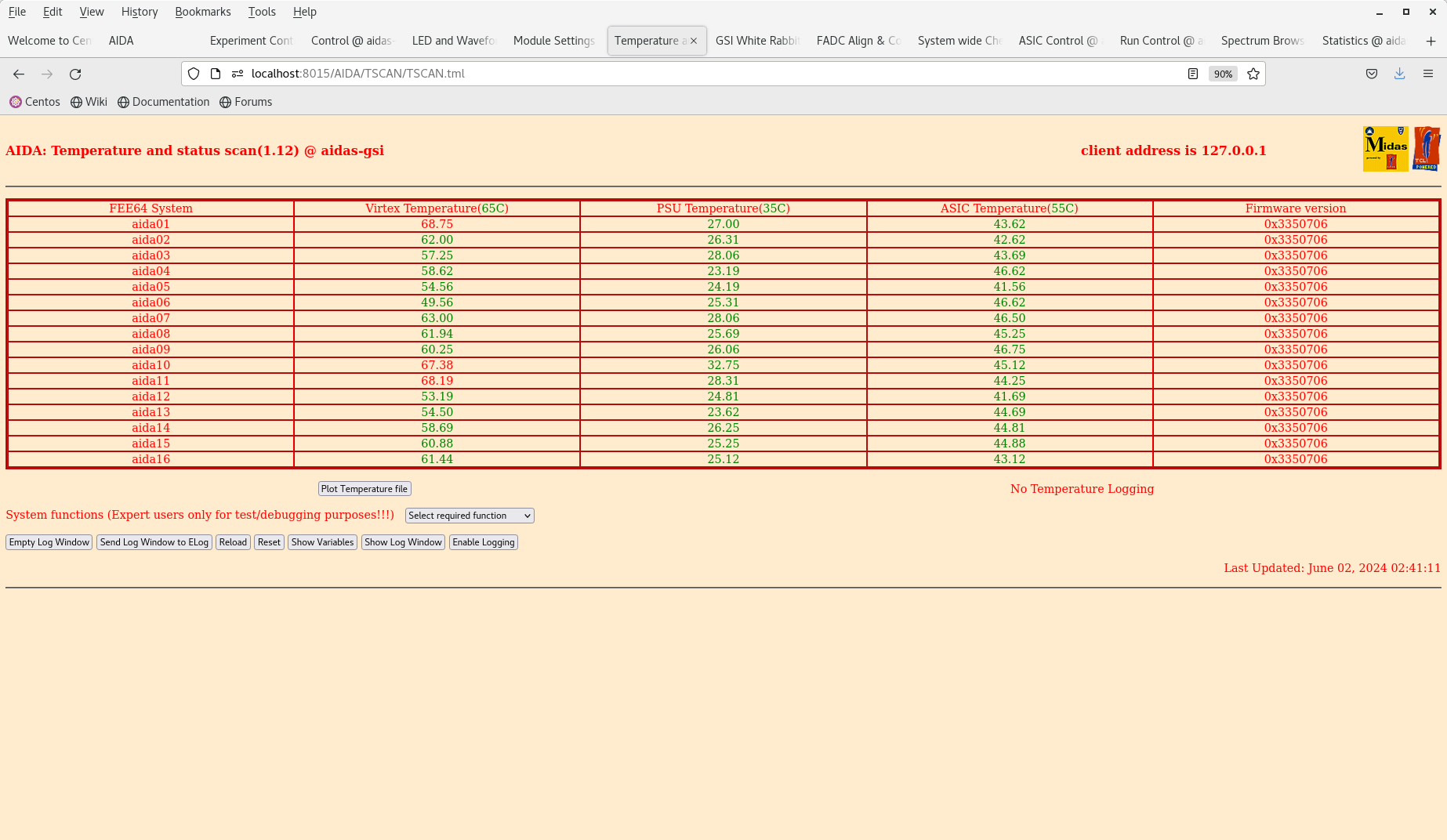

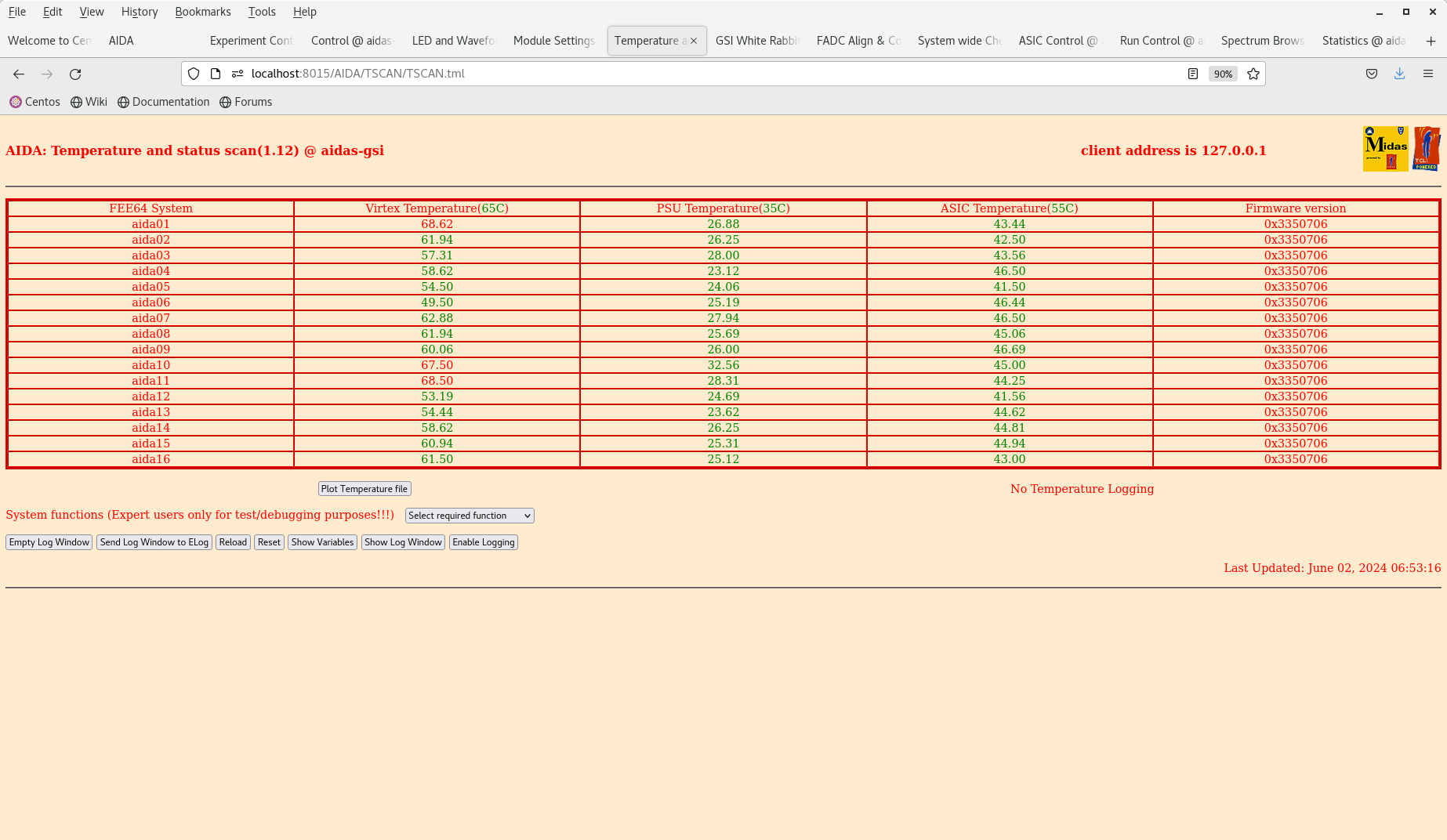

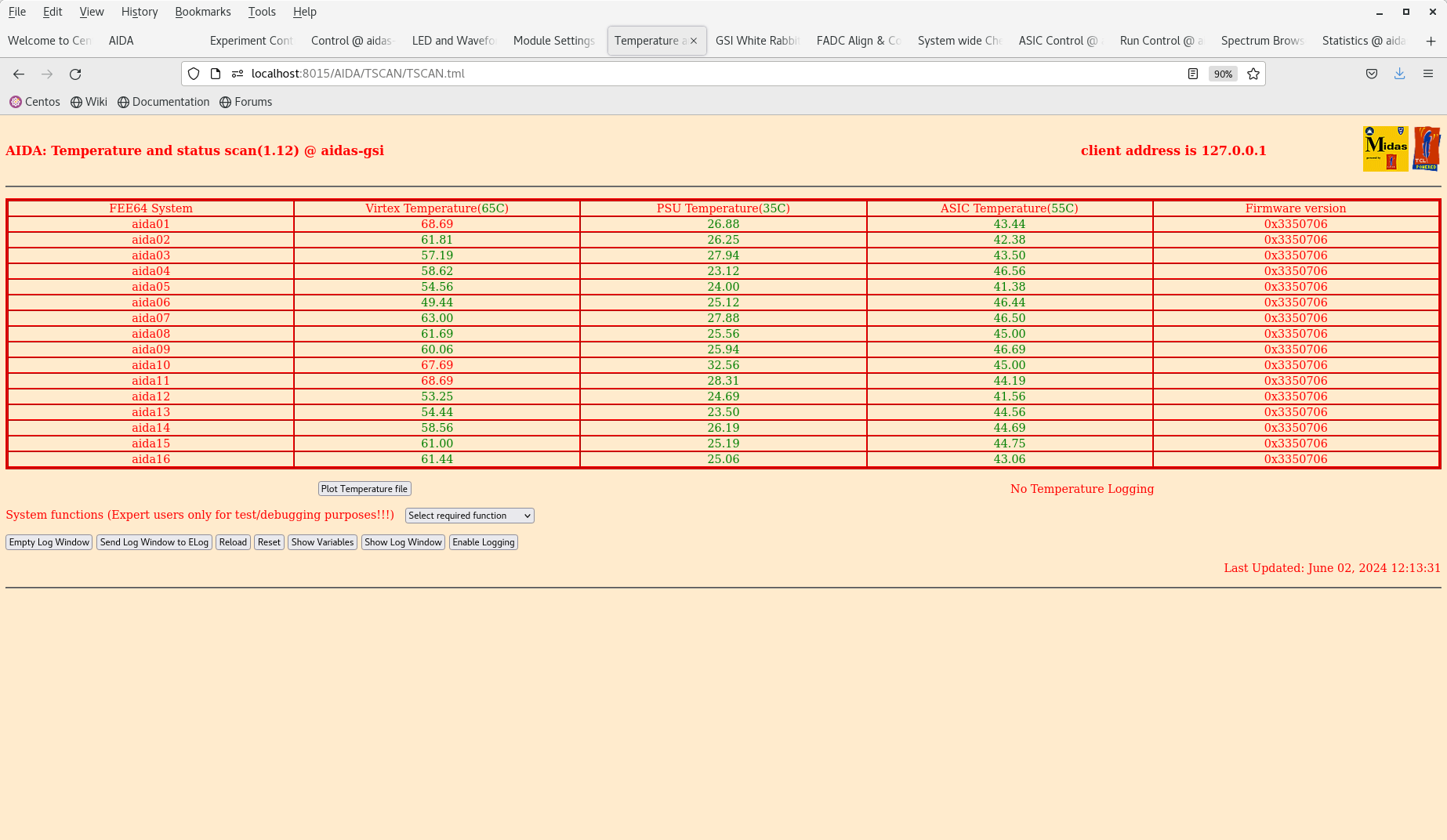

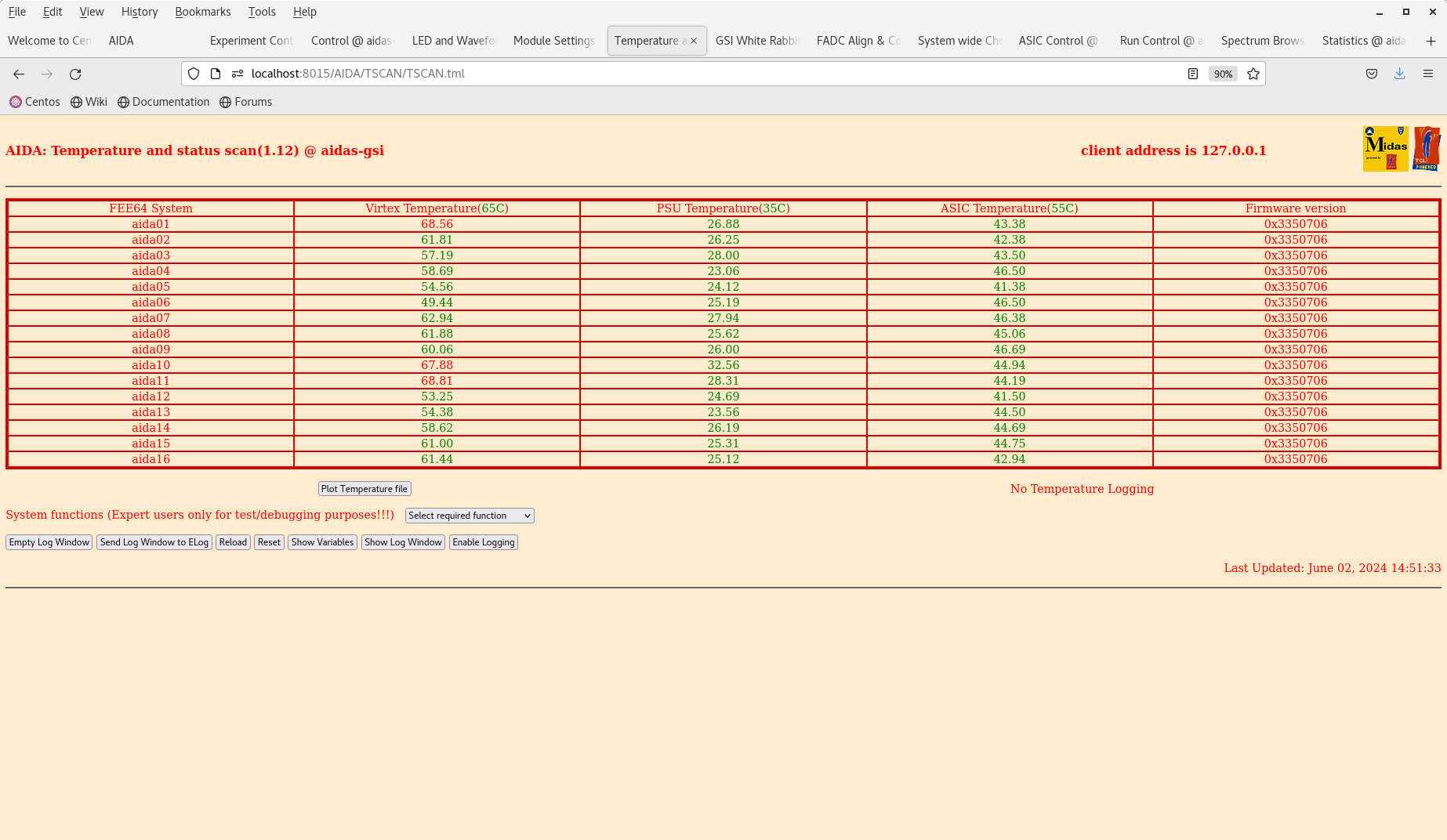

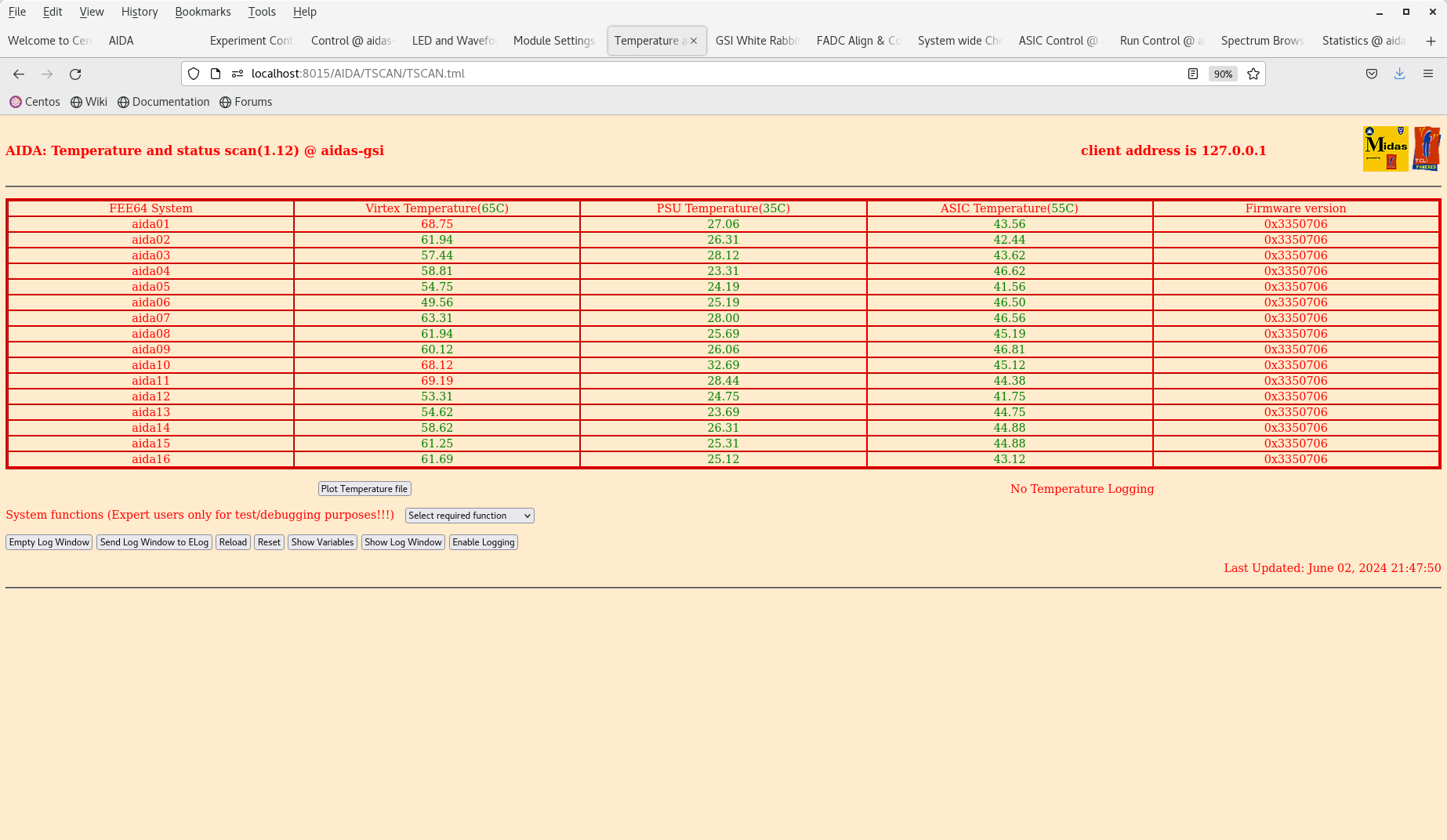

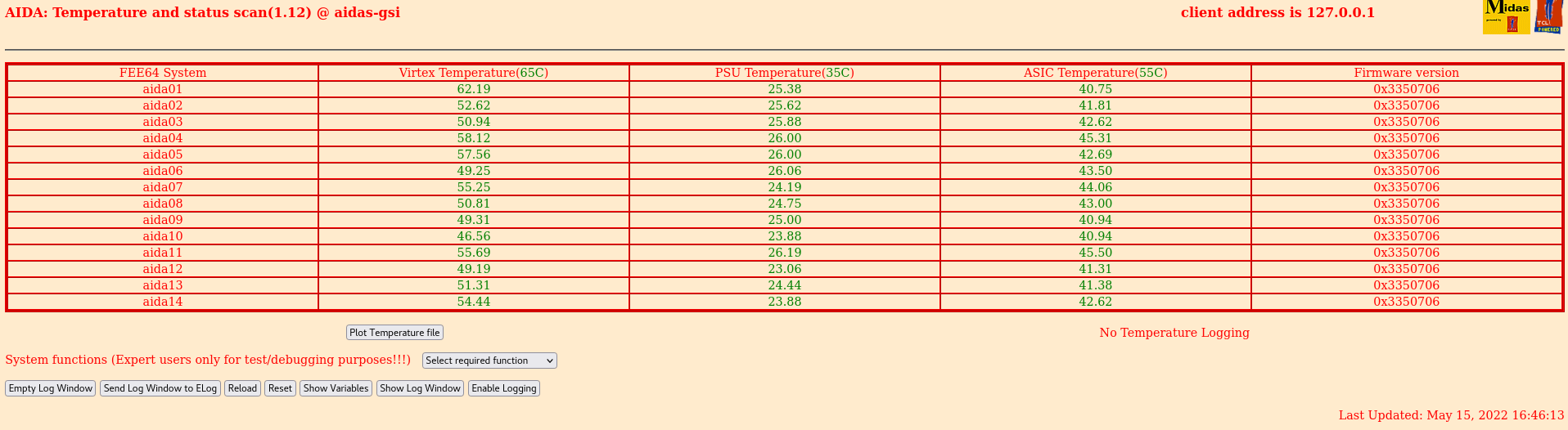

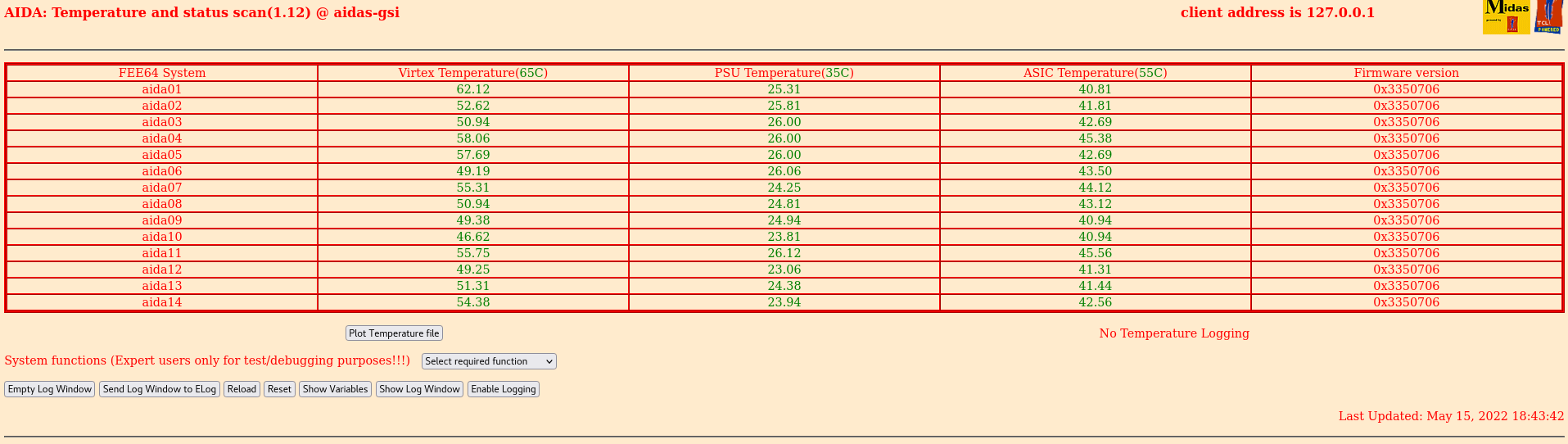

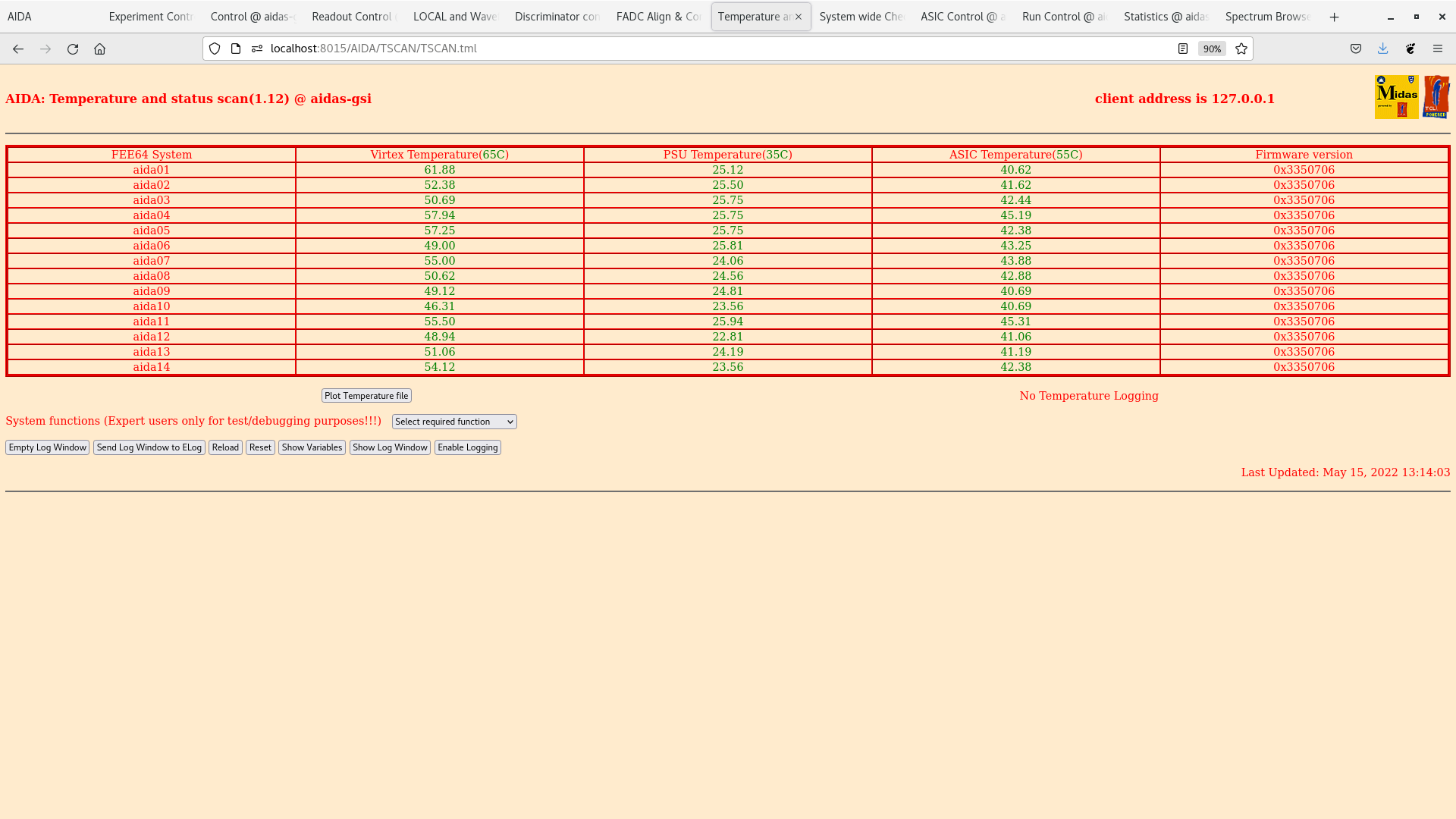

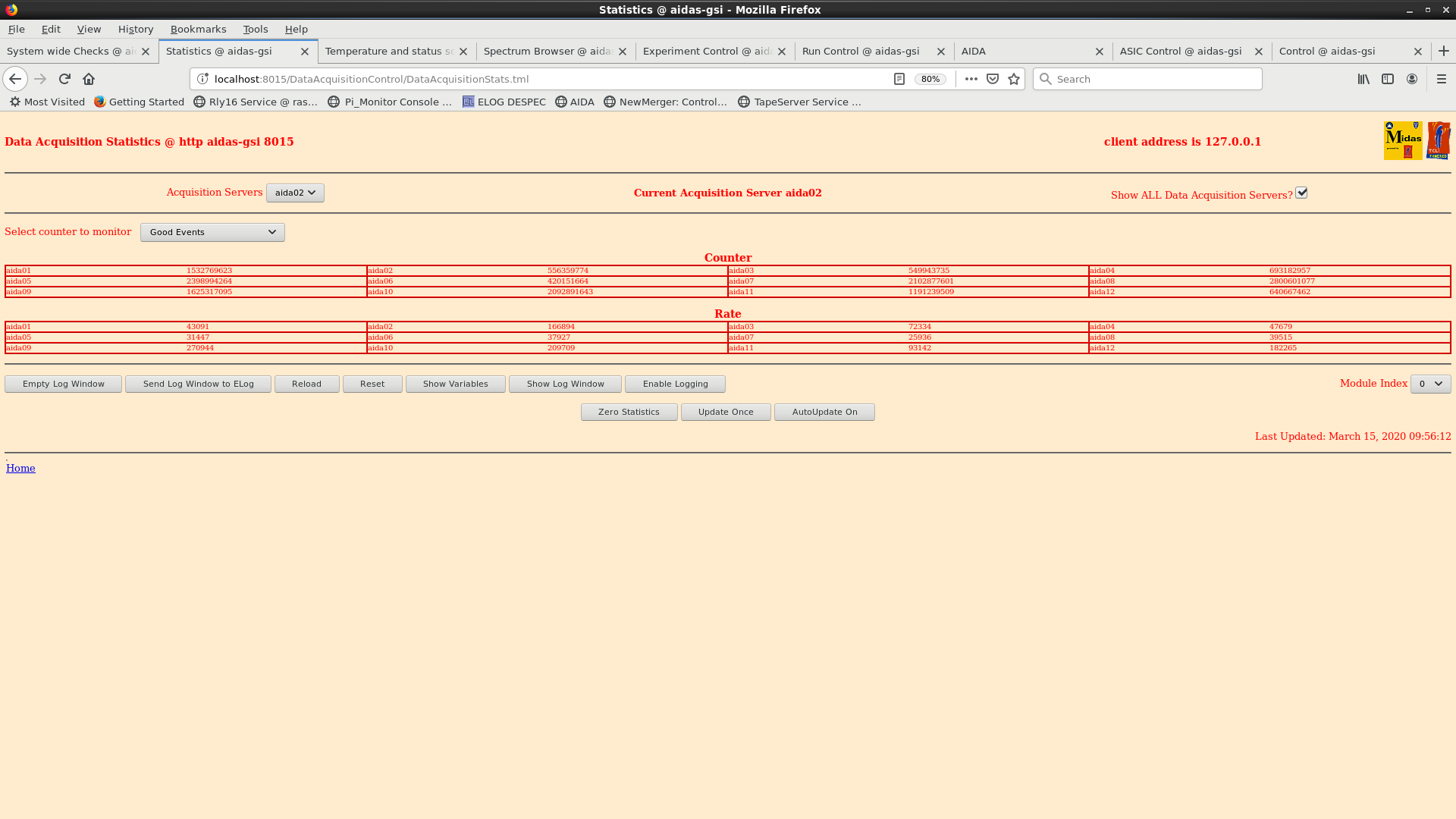

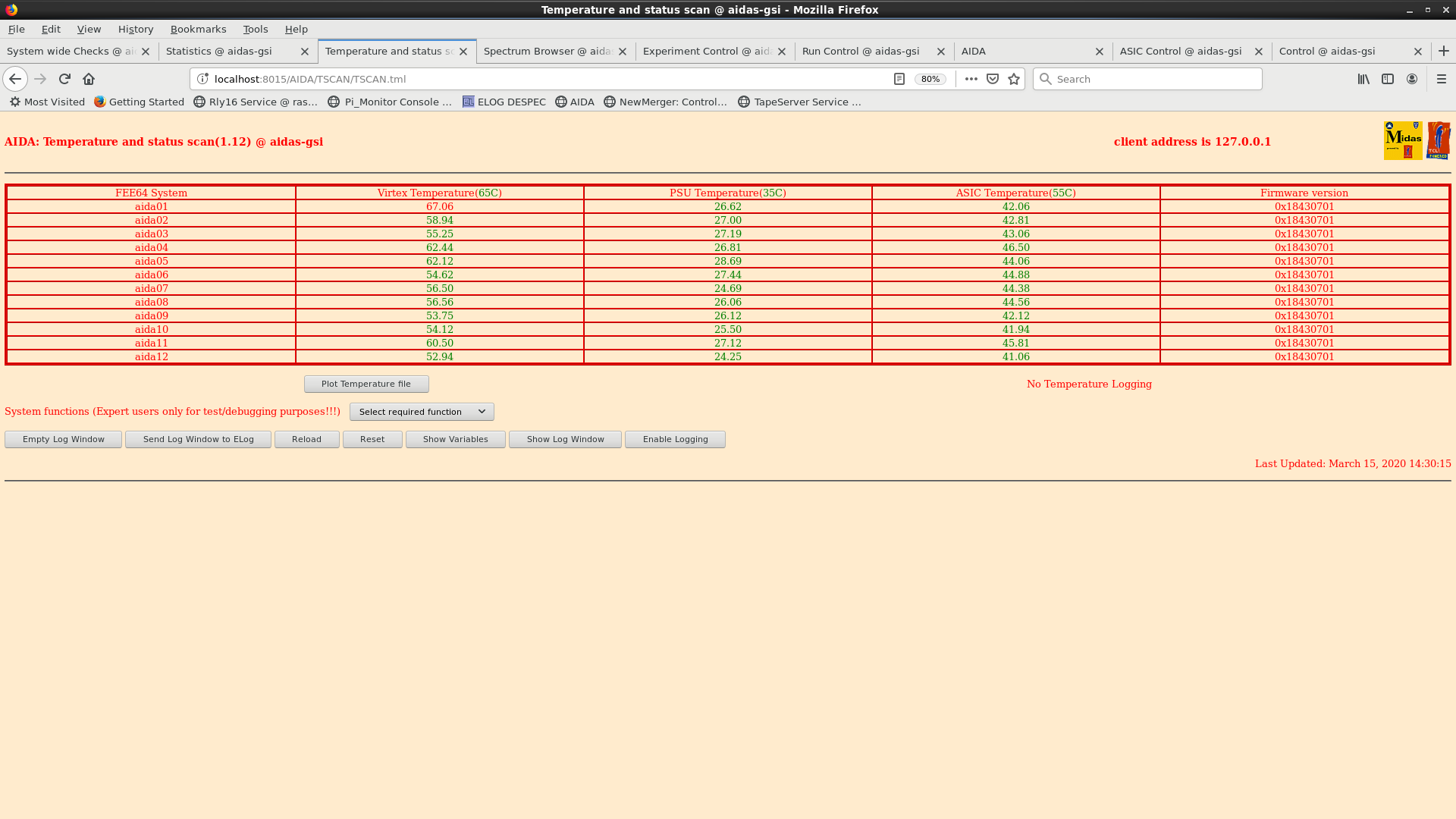

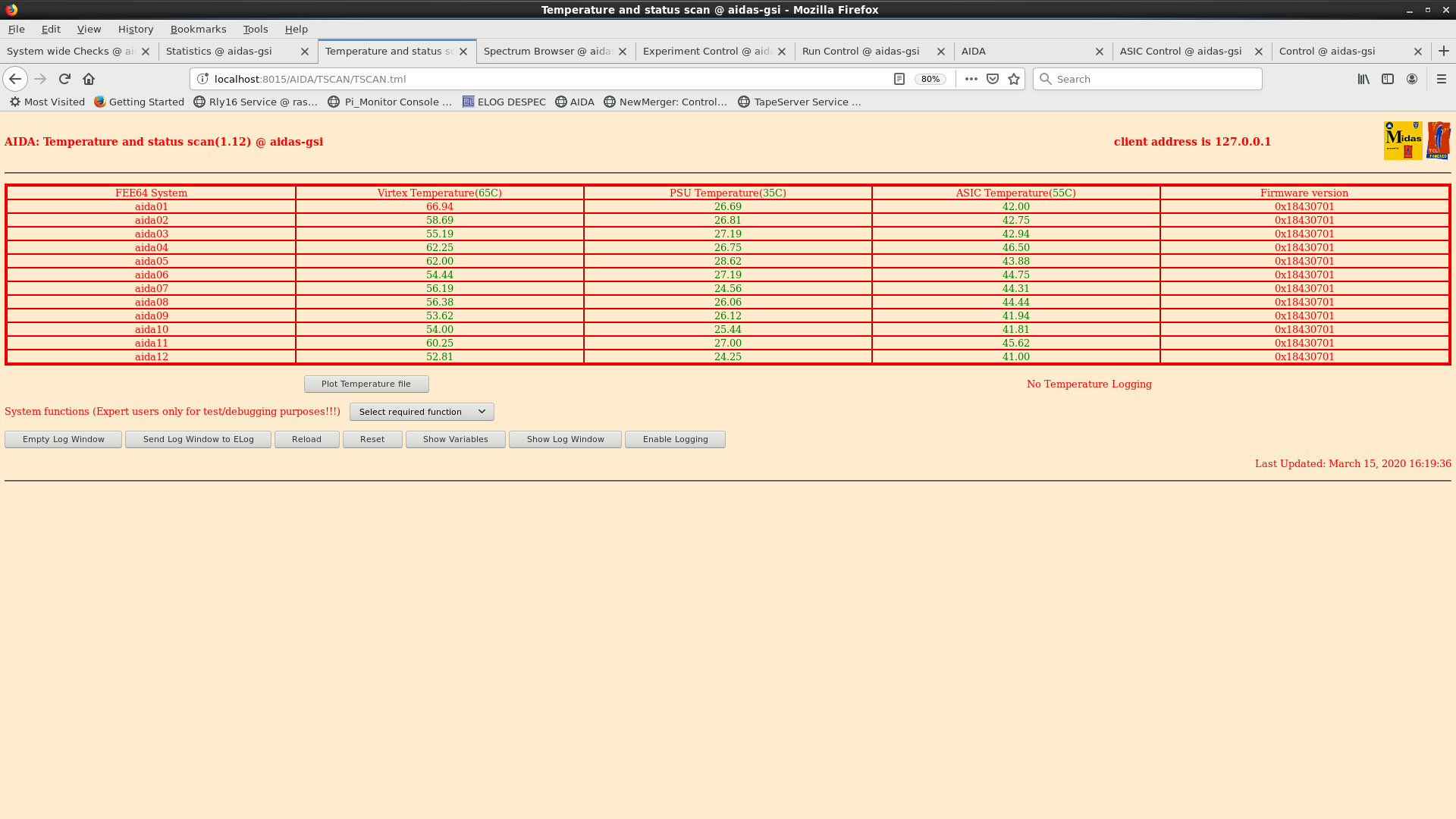

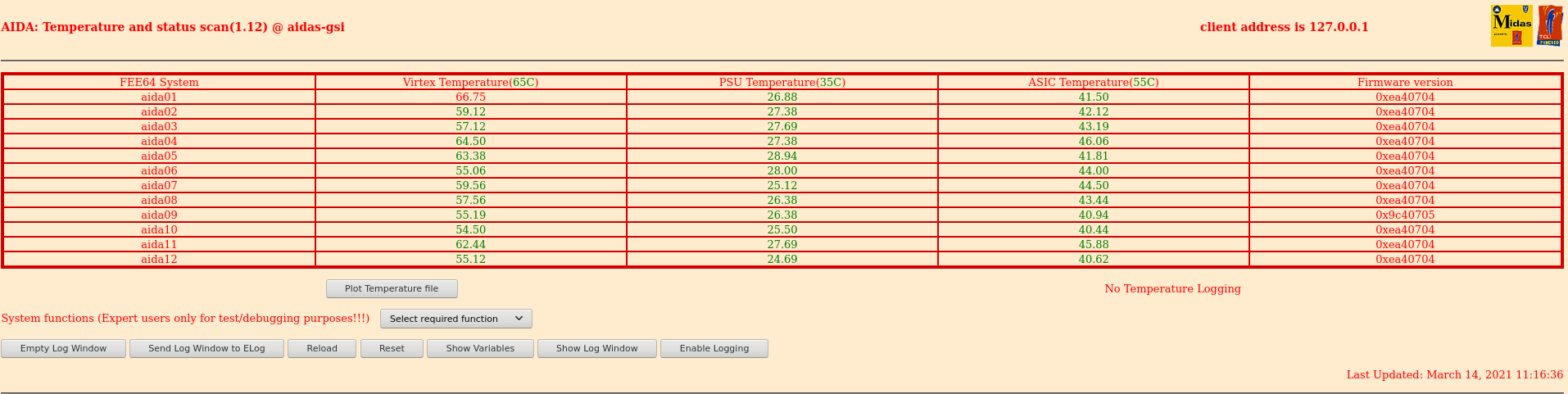

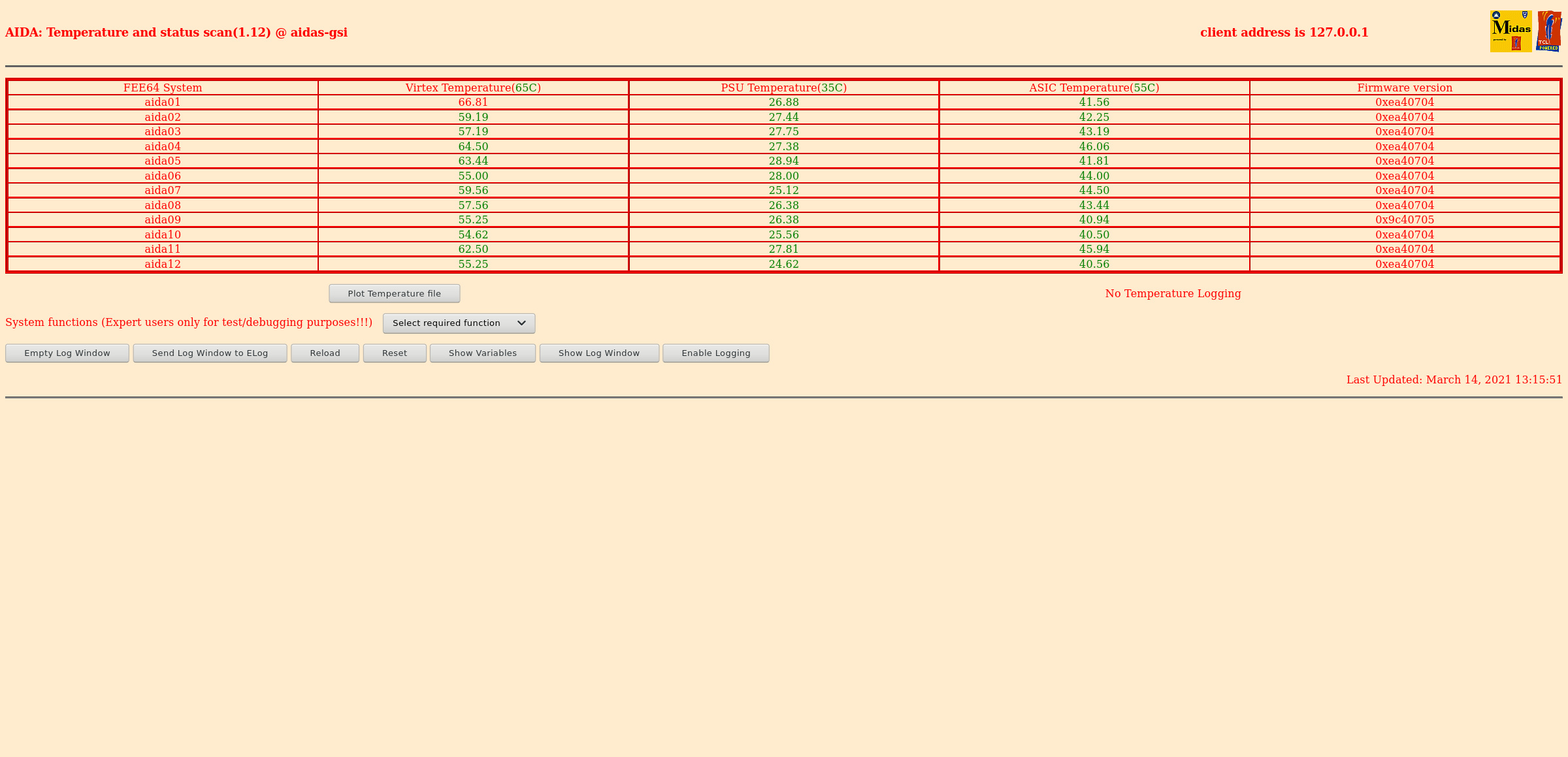

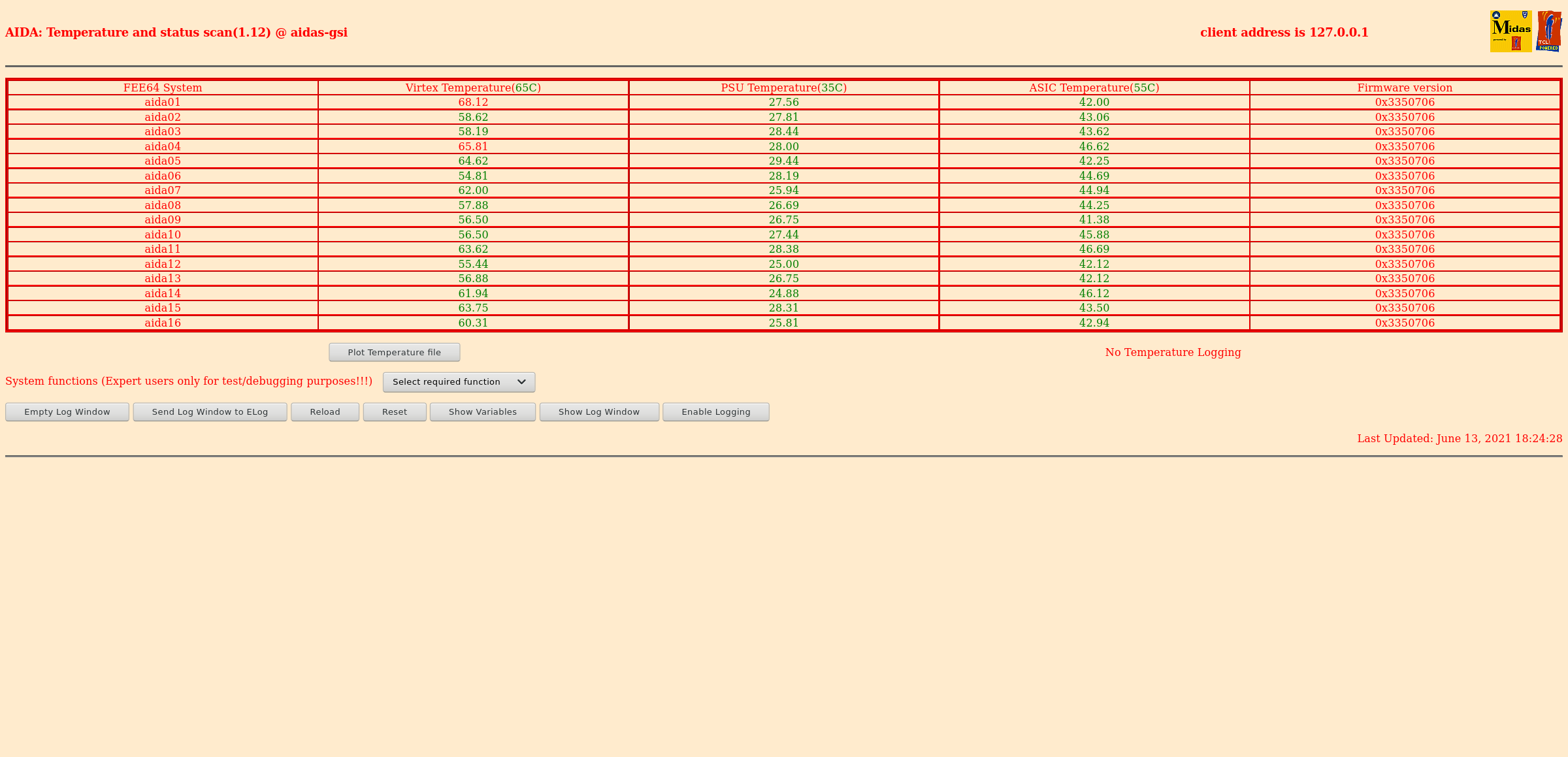

FEE64 temps OK - attachment 2

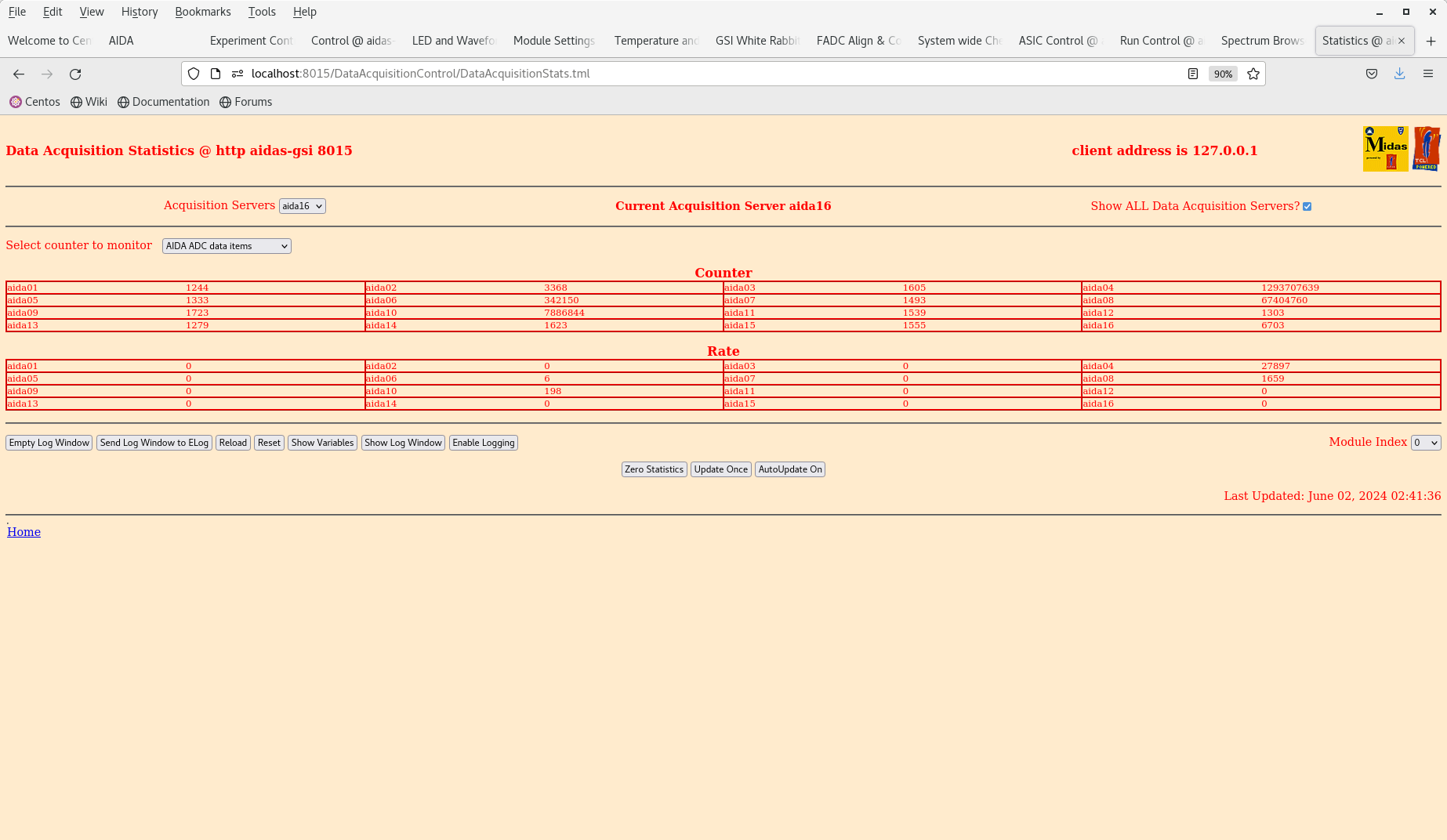

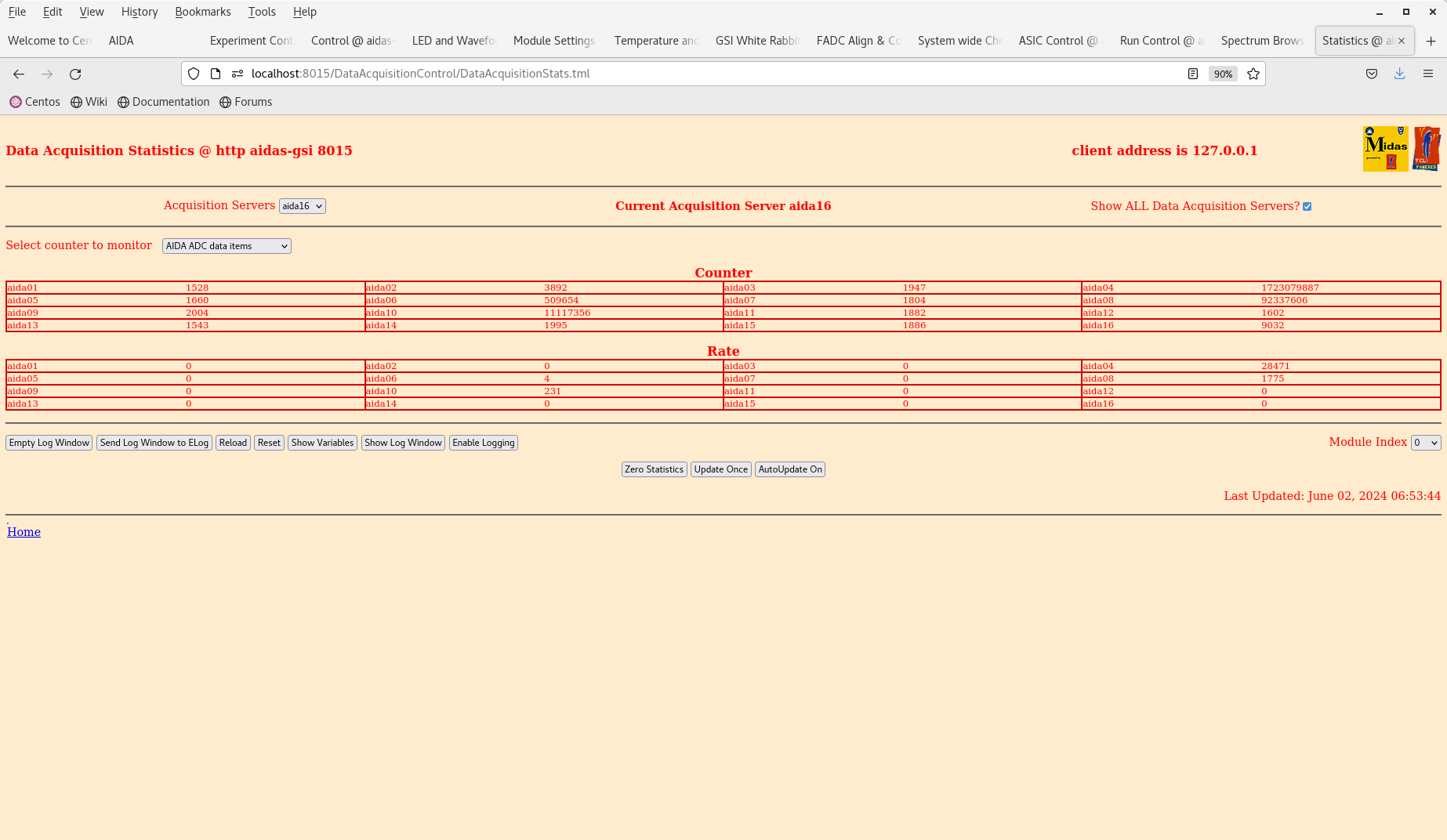

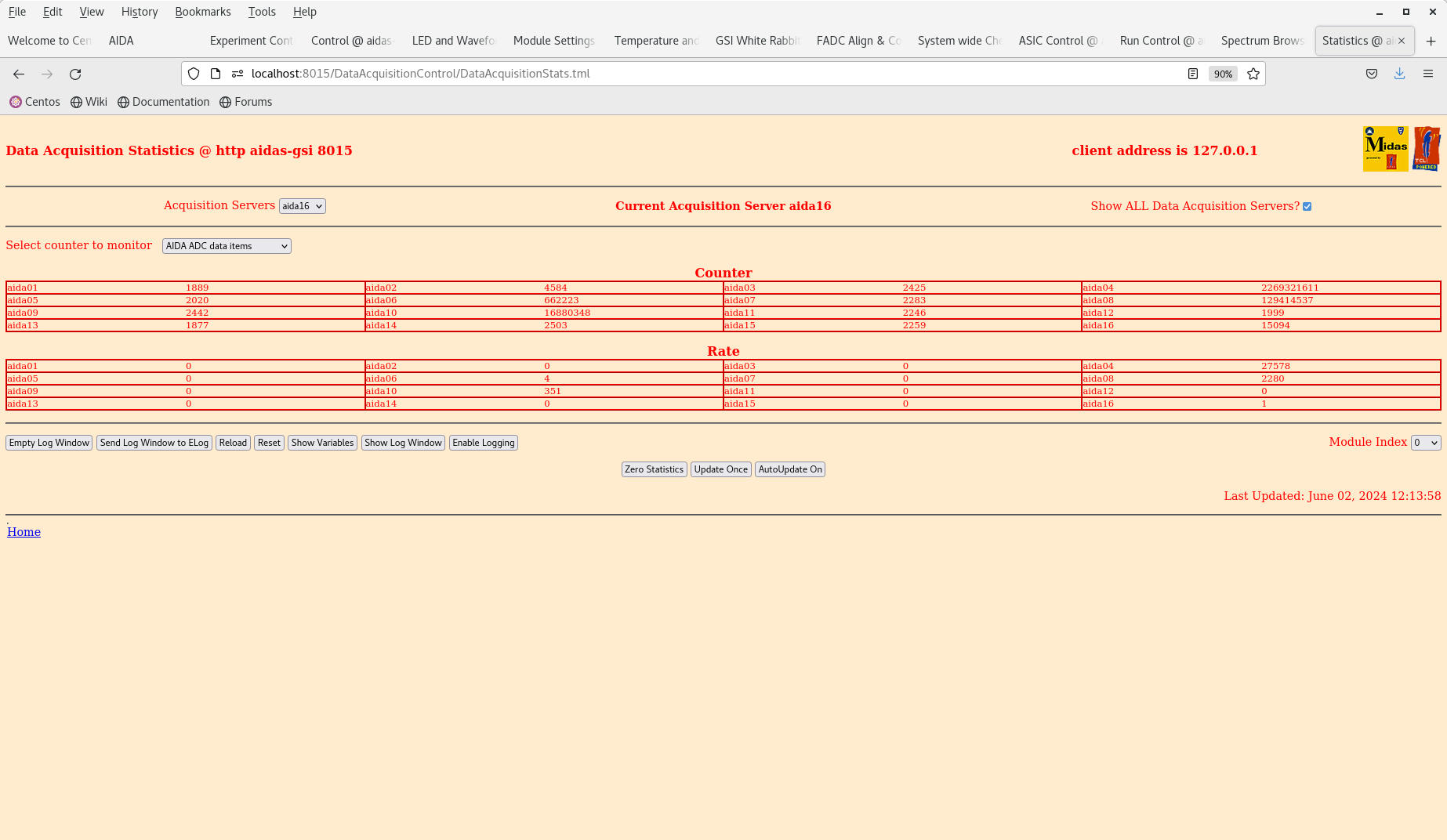

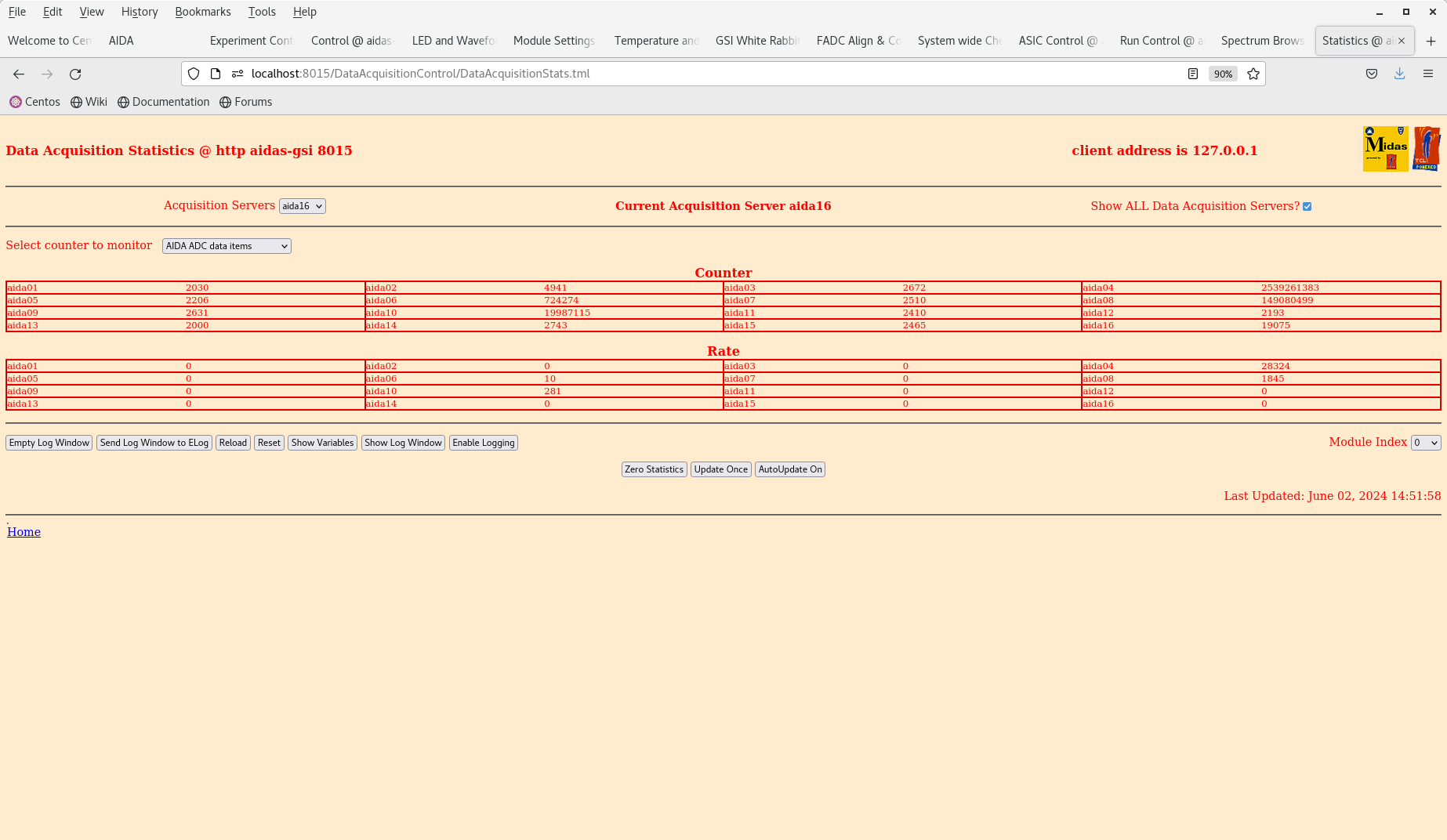

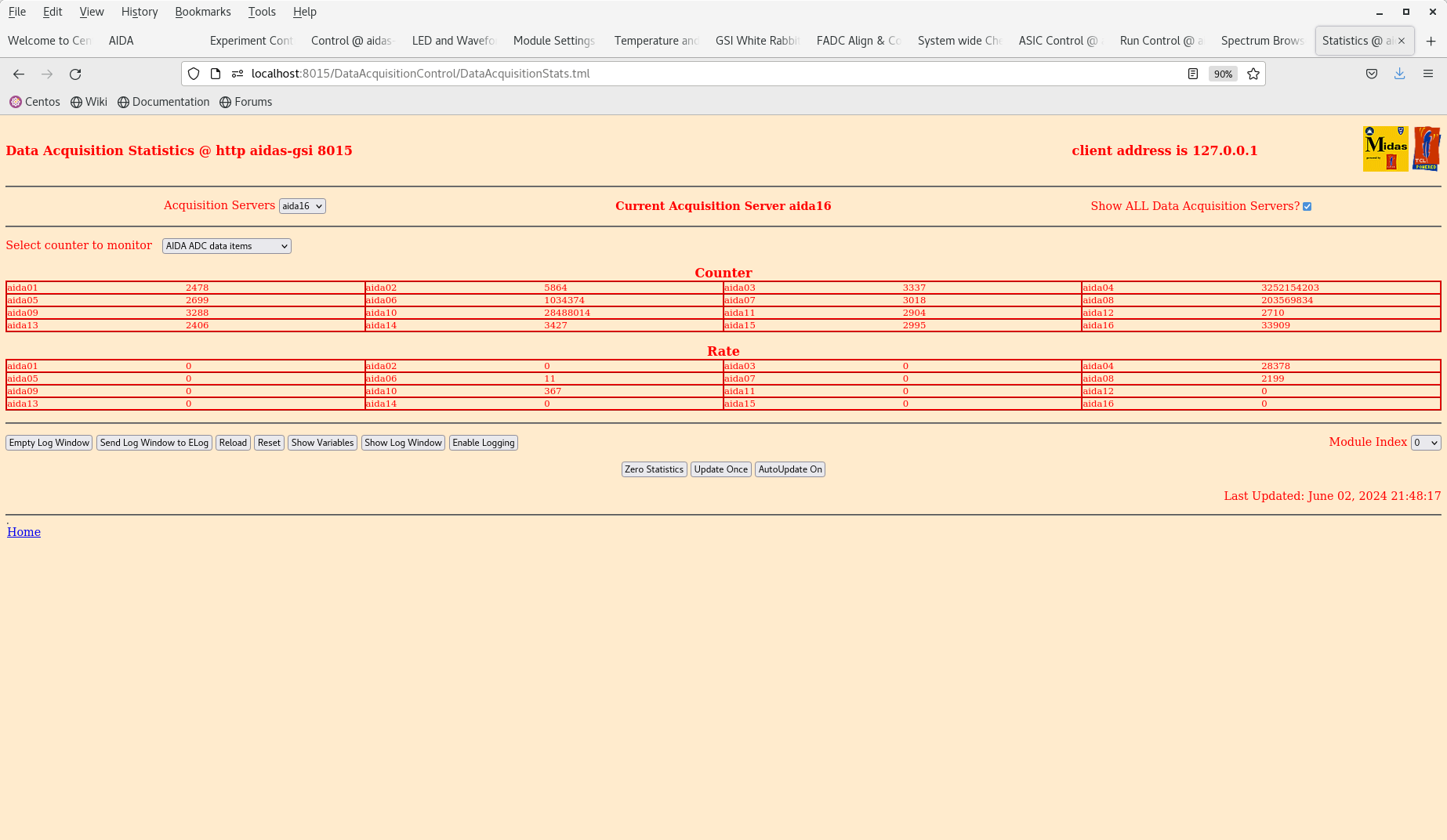

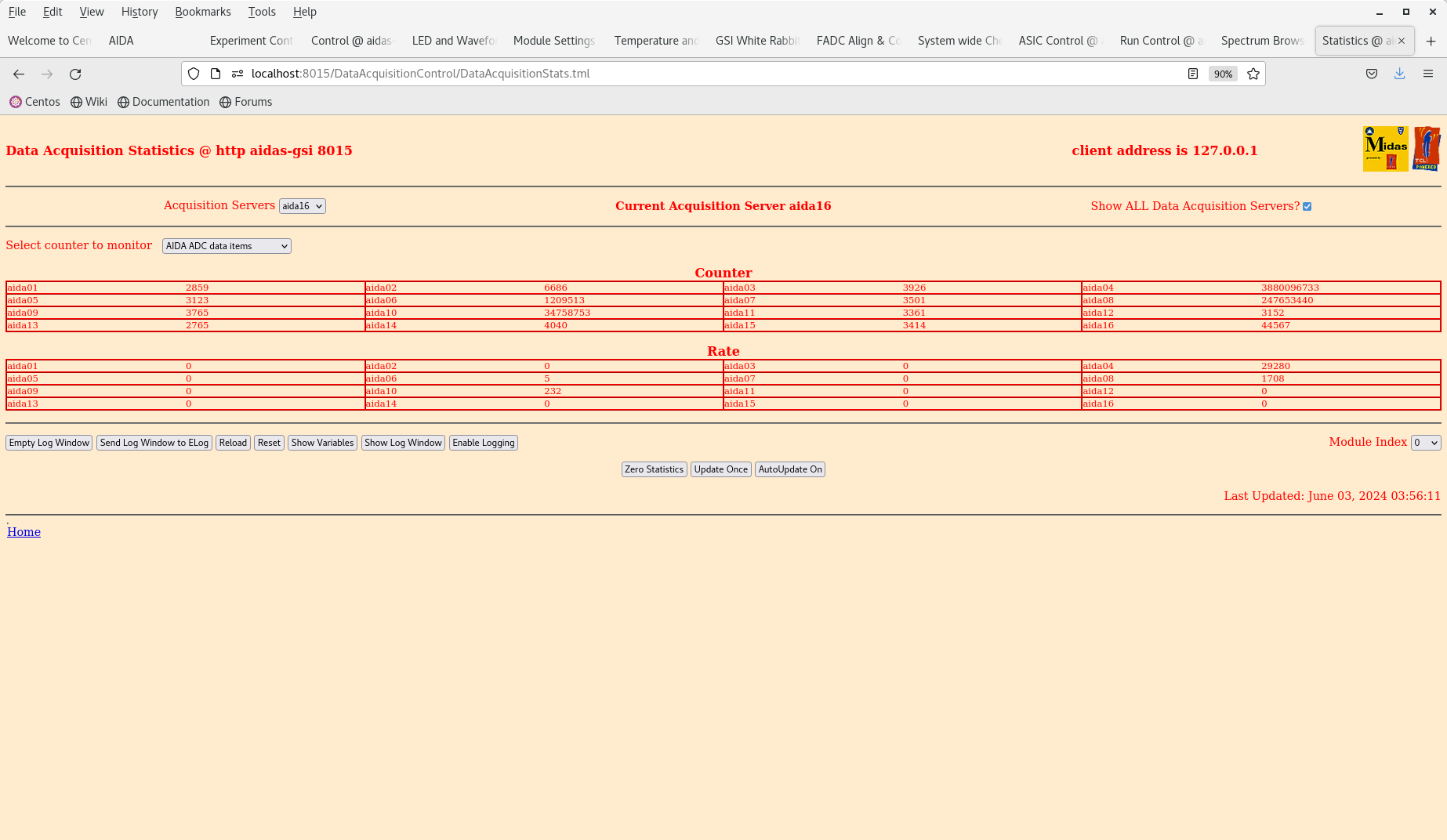

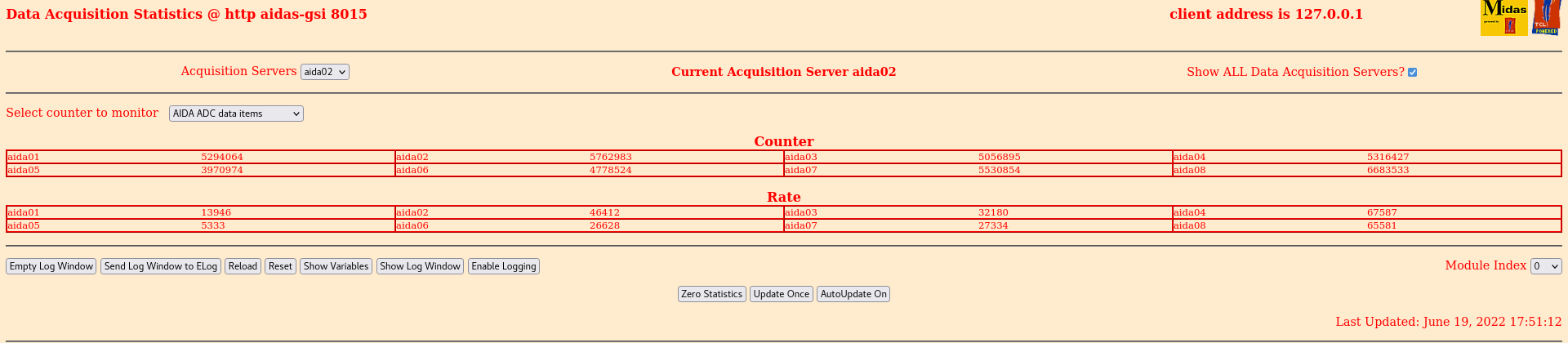

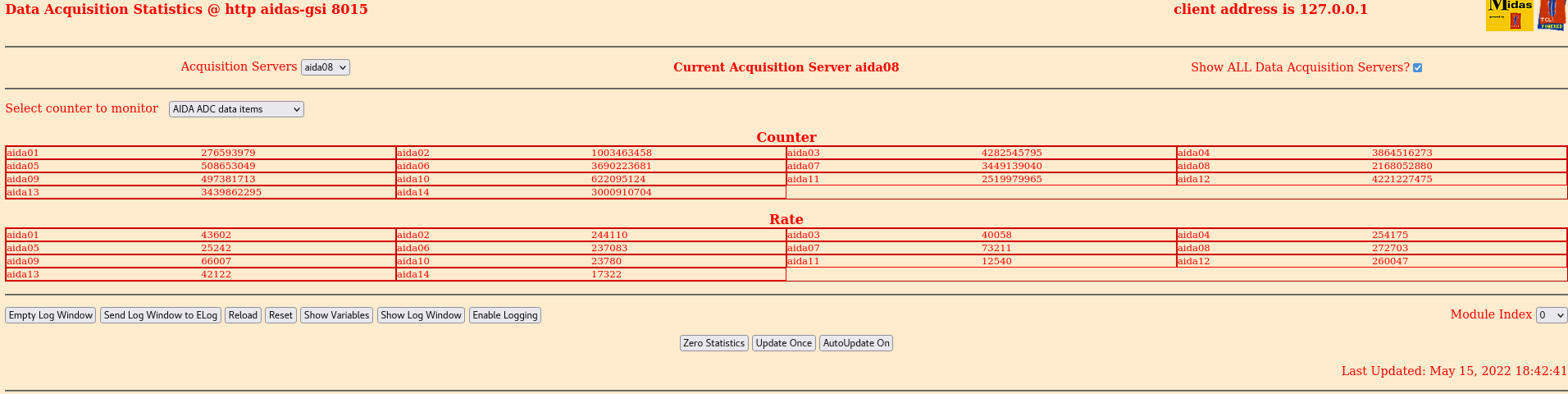

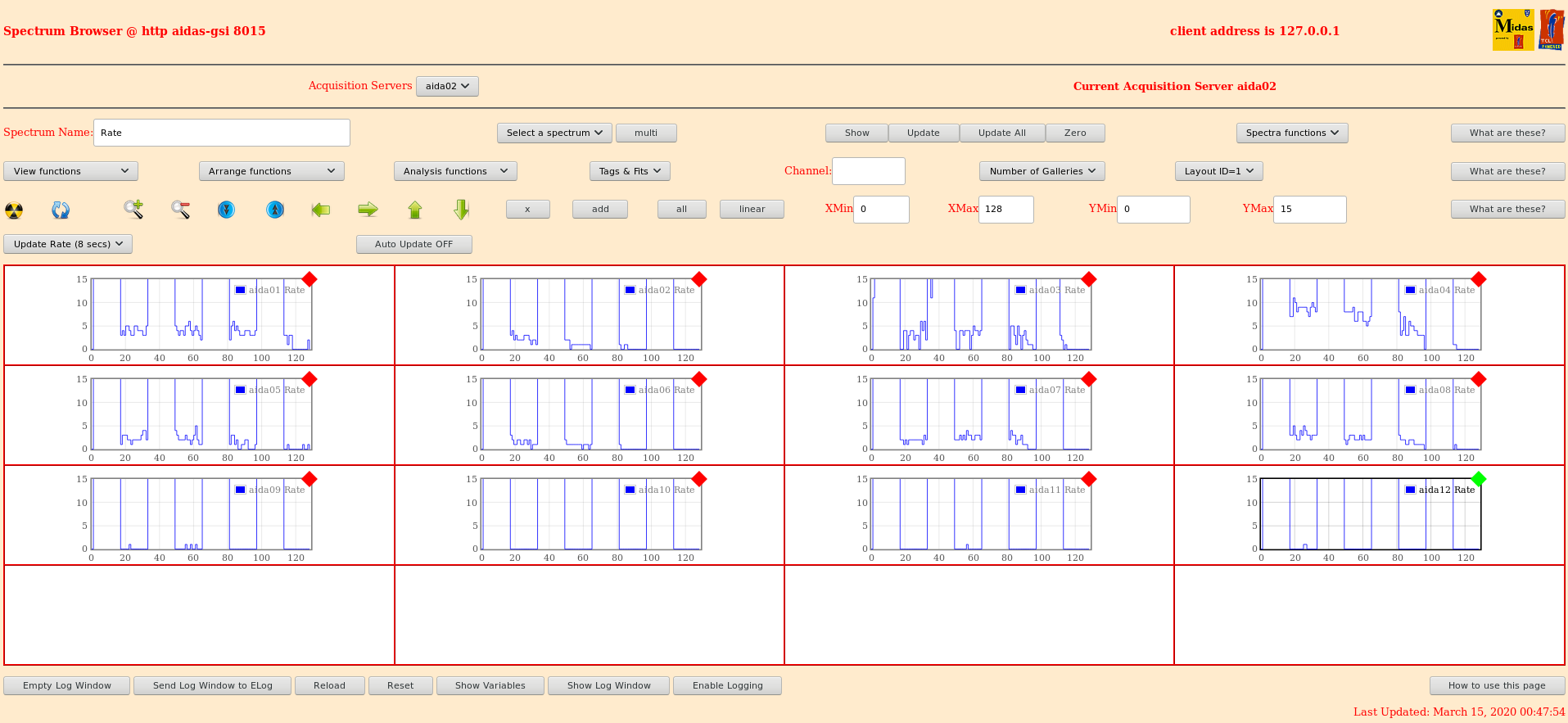

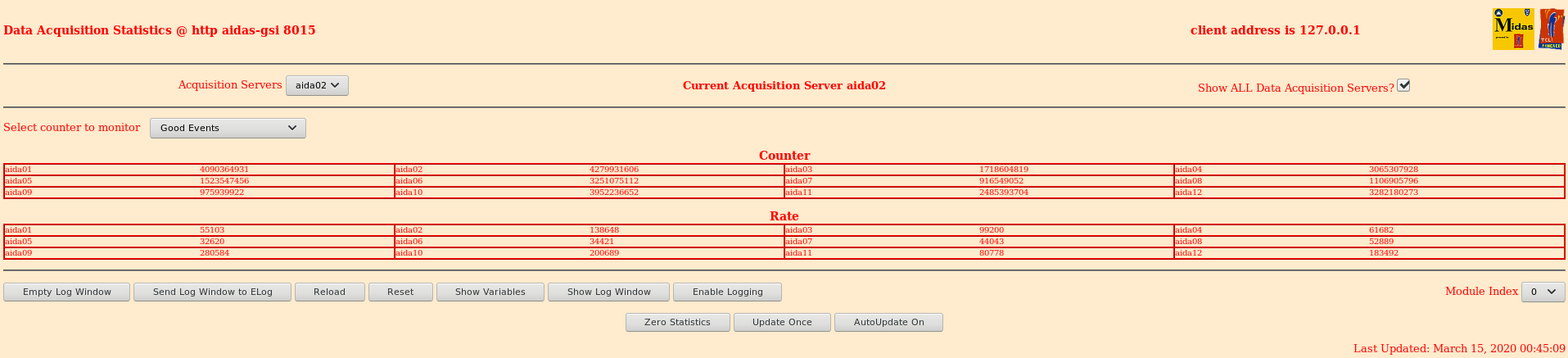

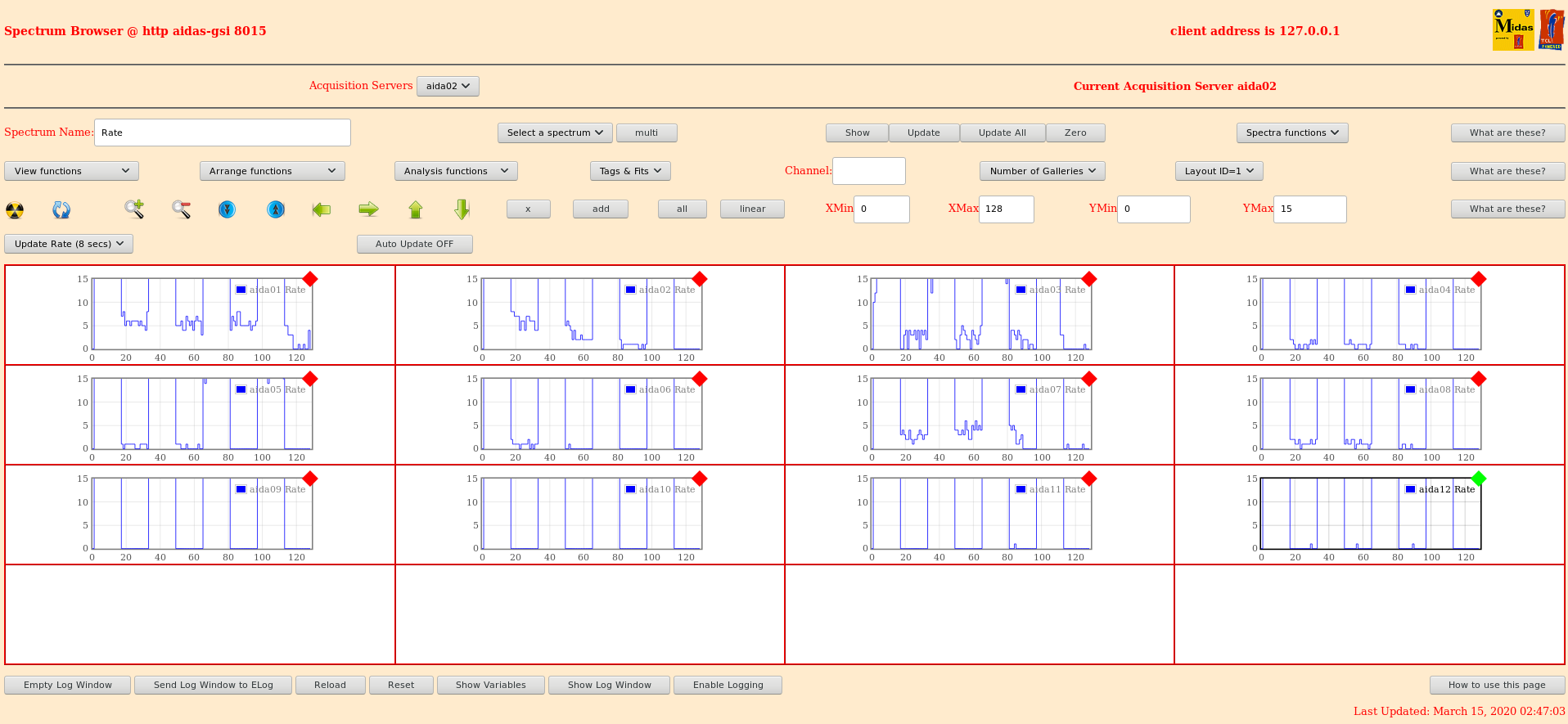

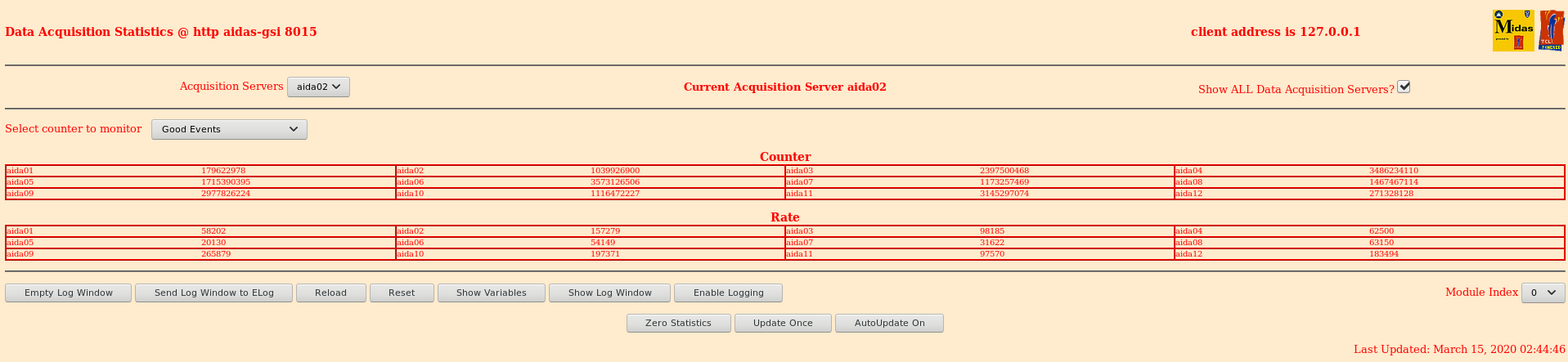

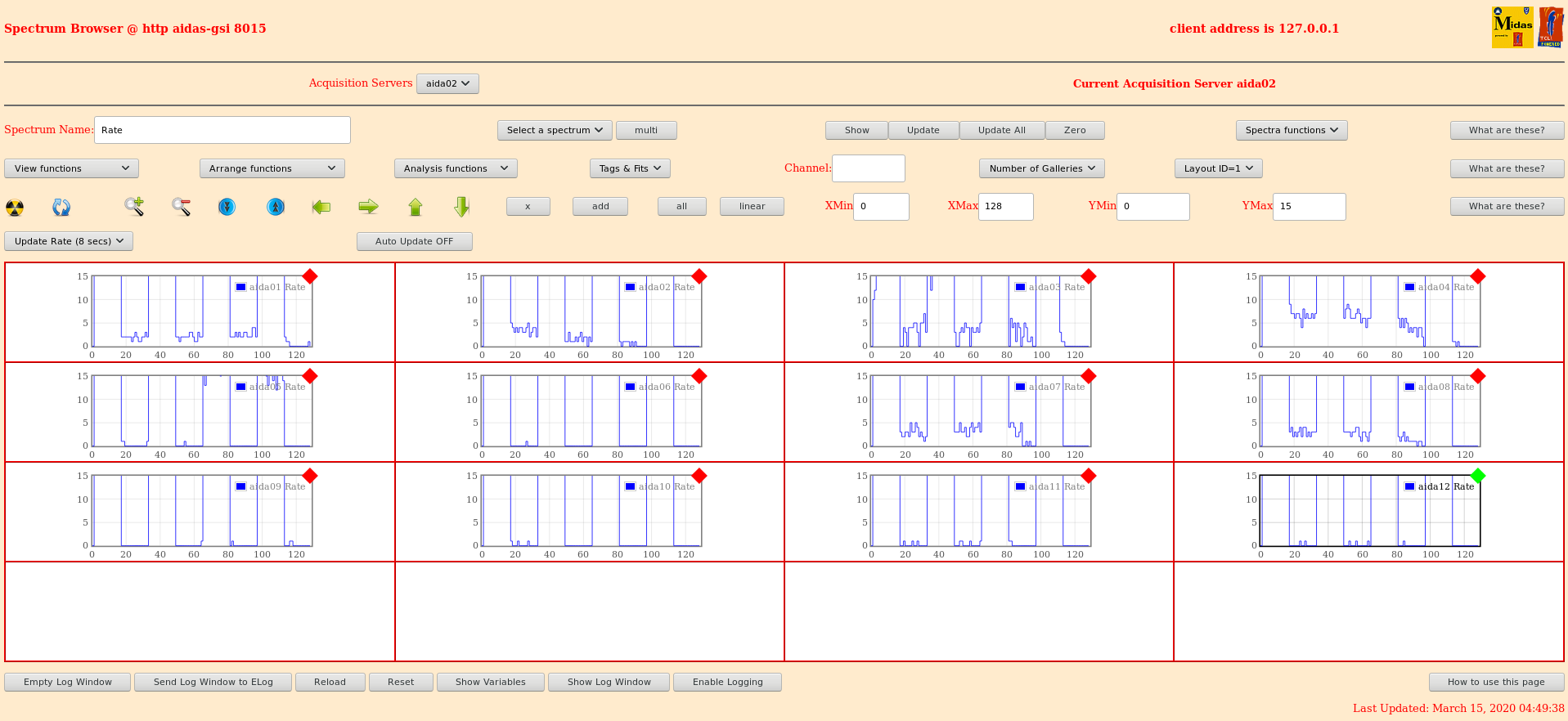

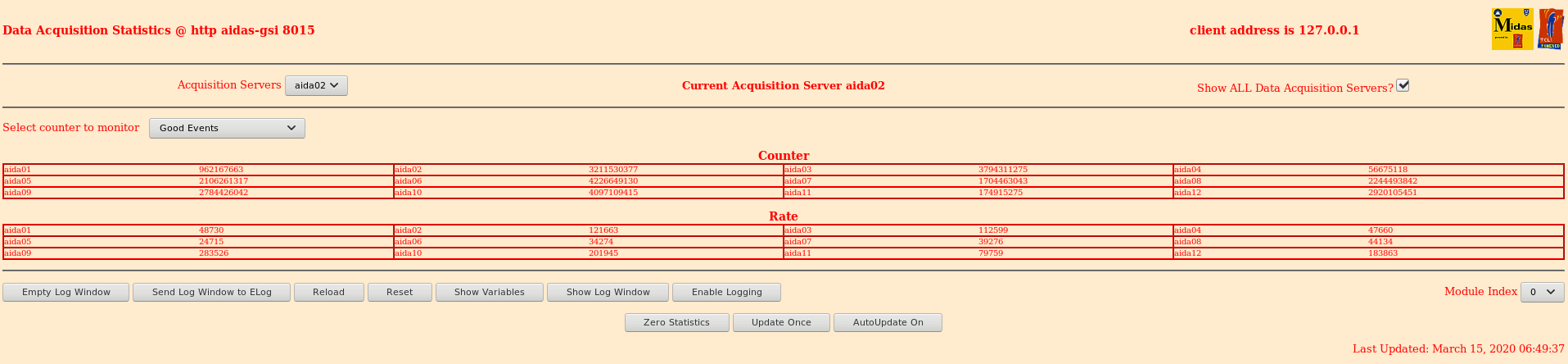

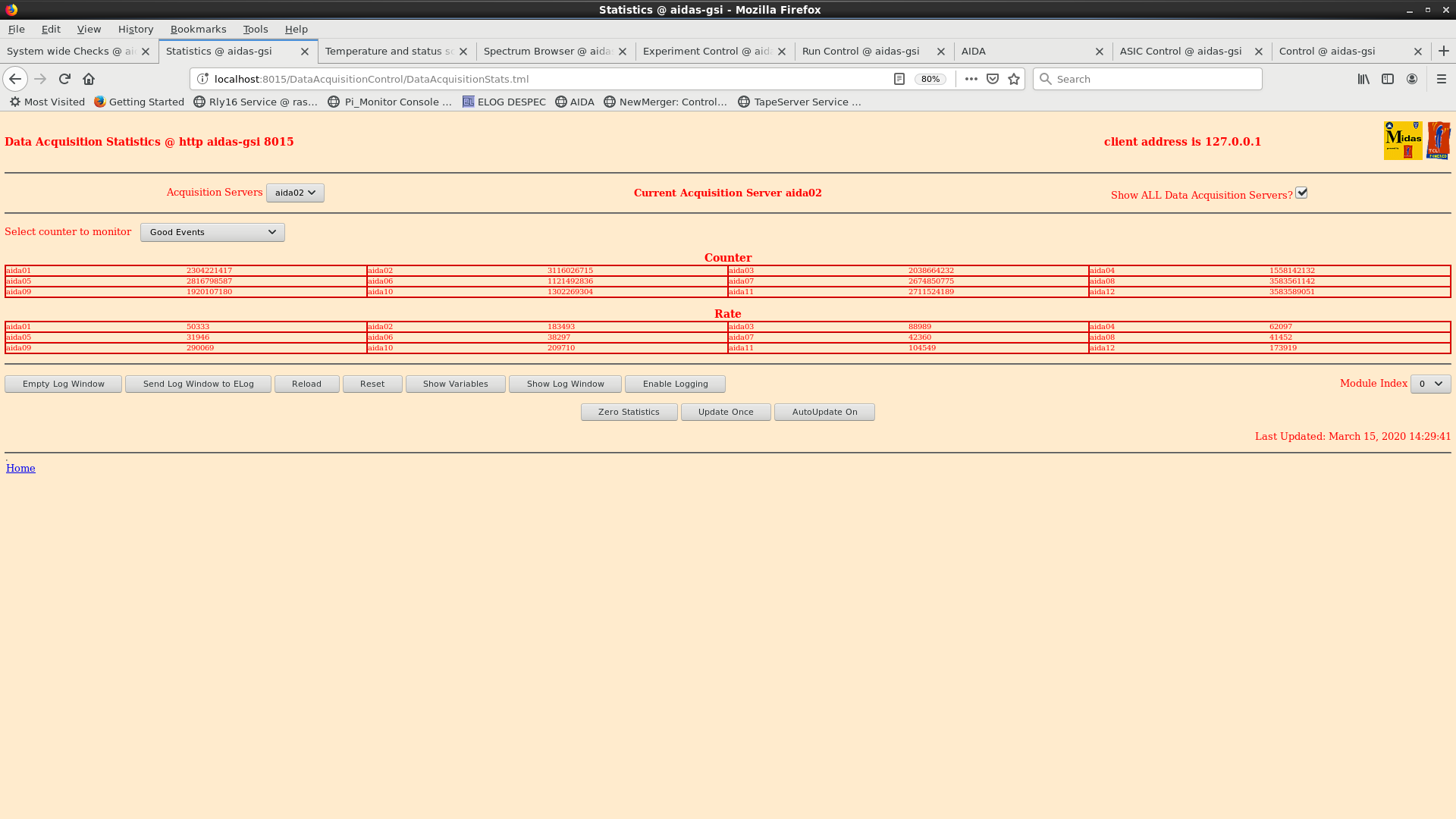

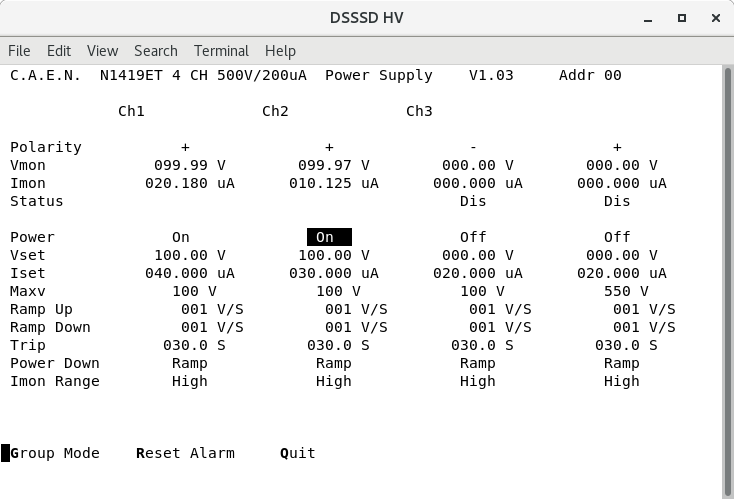

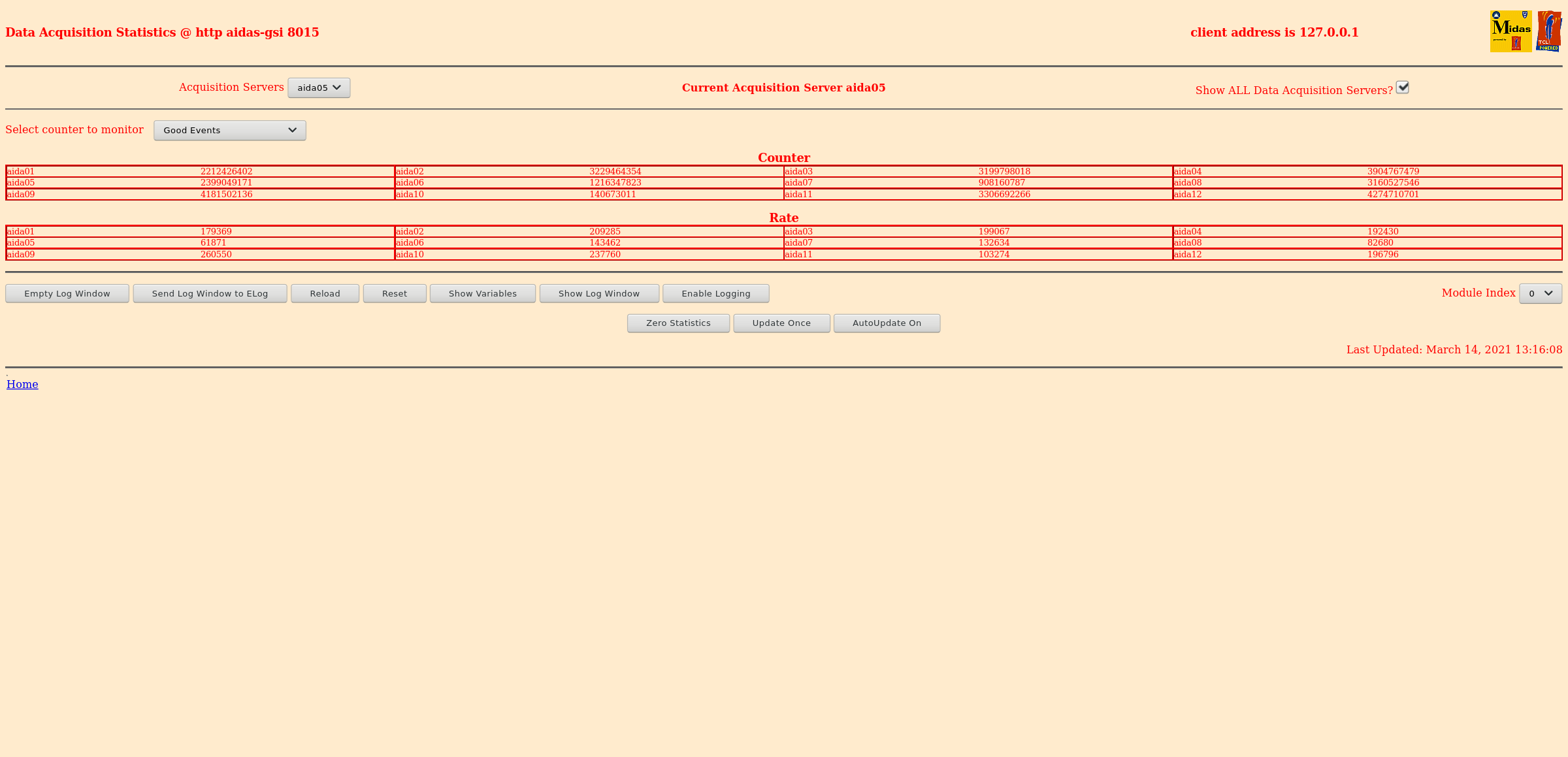

ADC data item stats - attachment 3

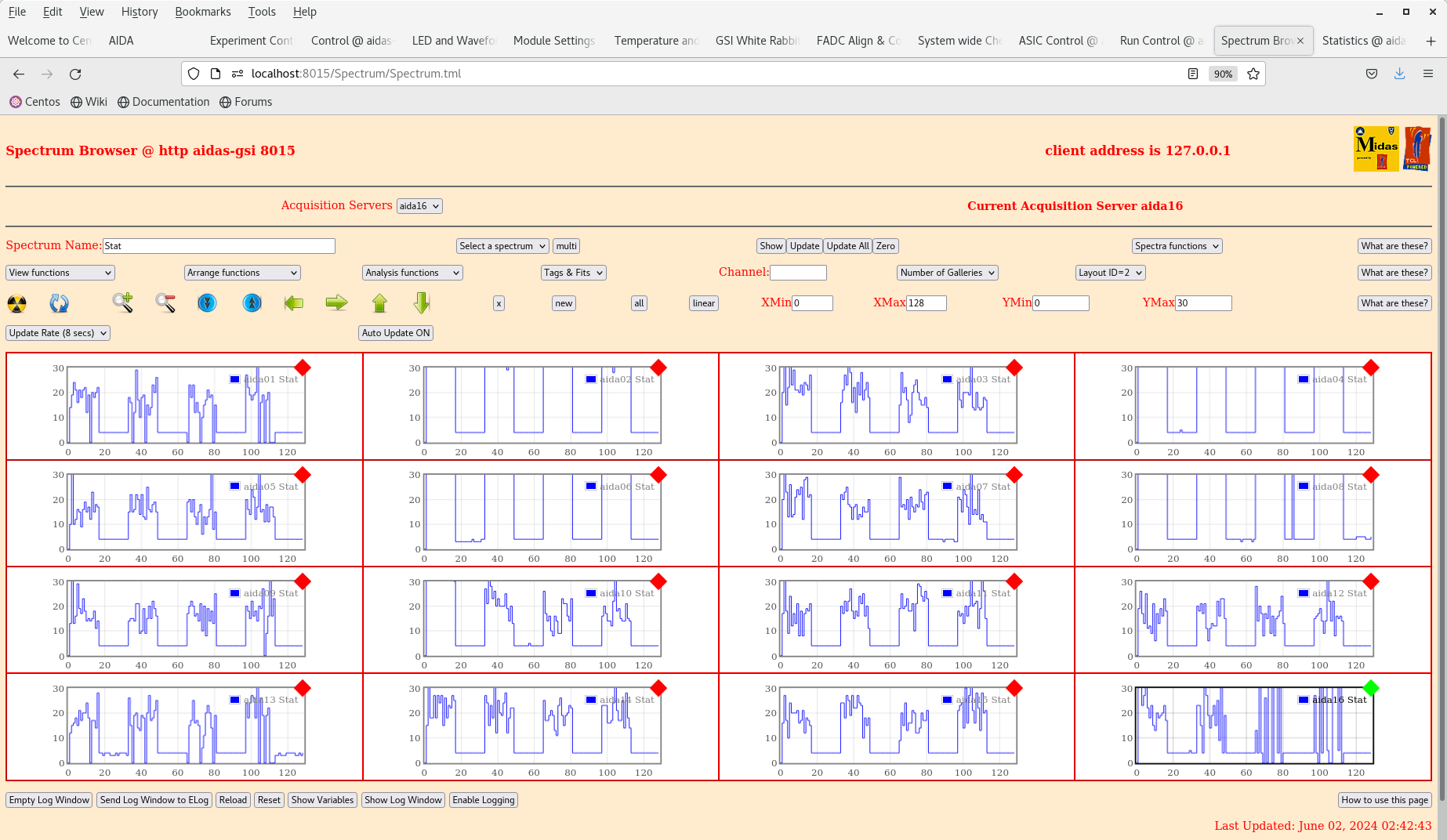

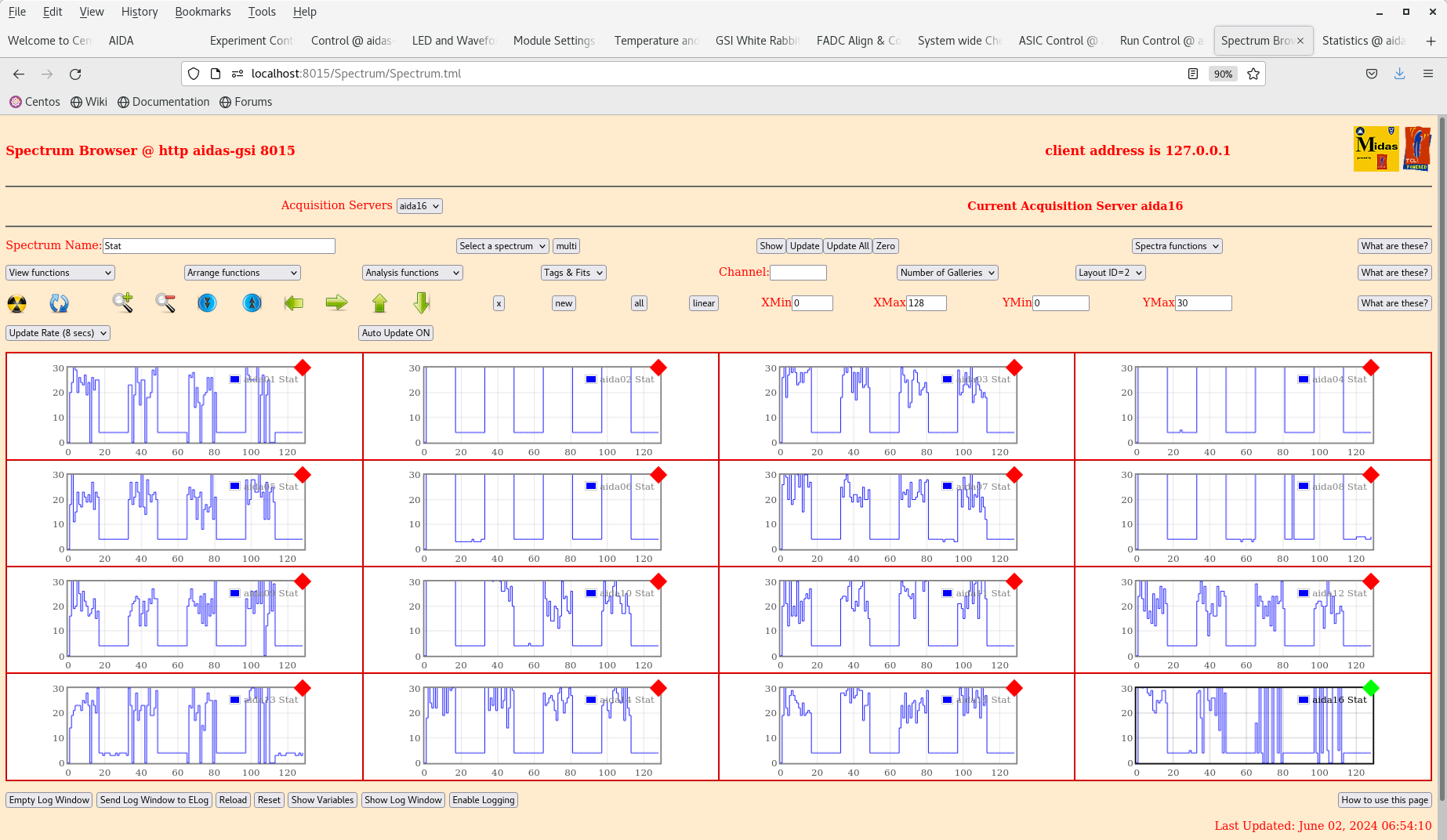

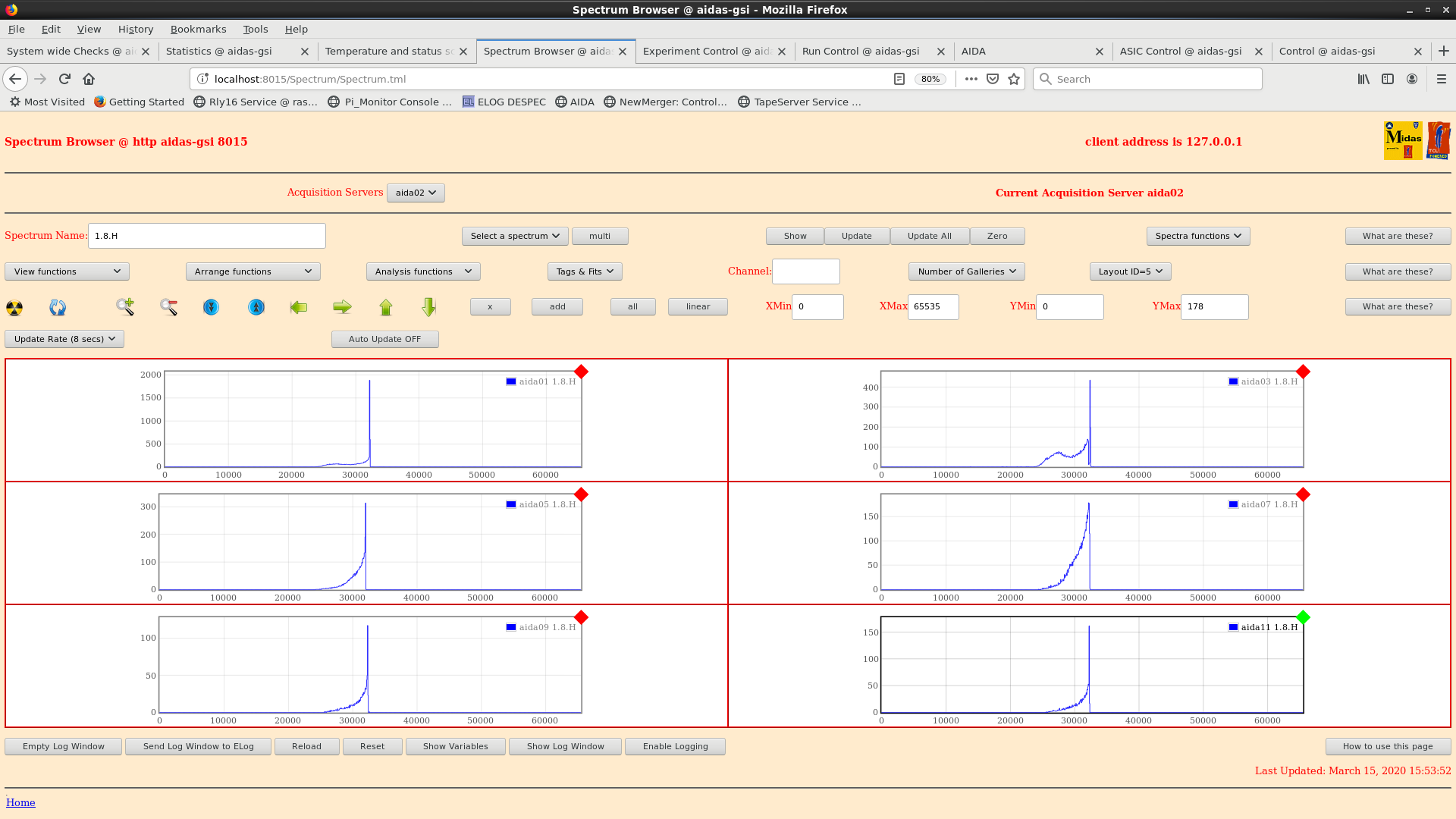

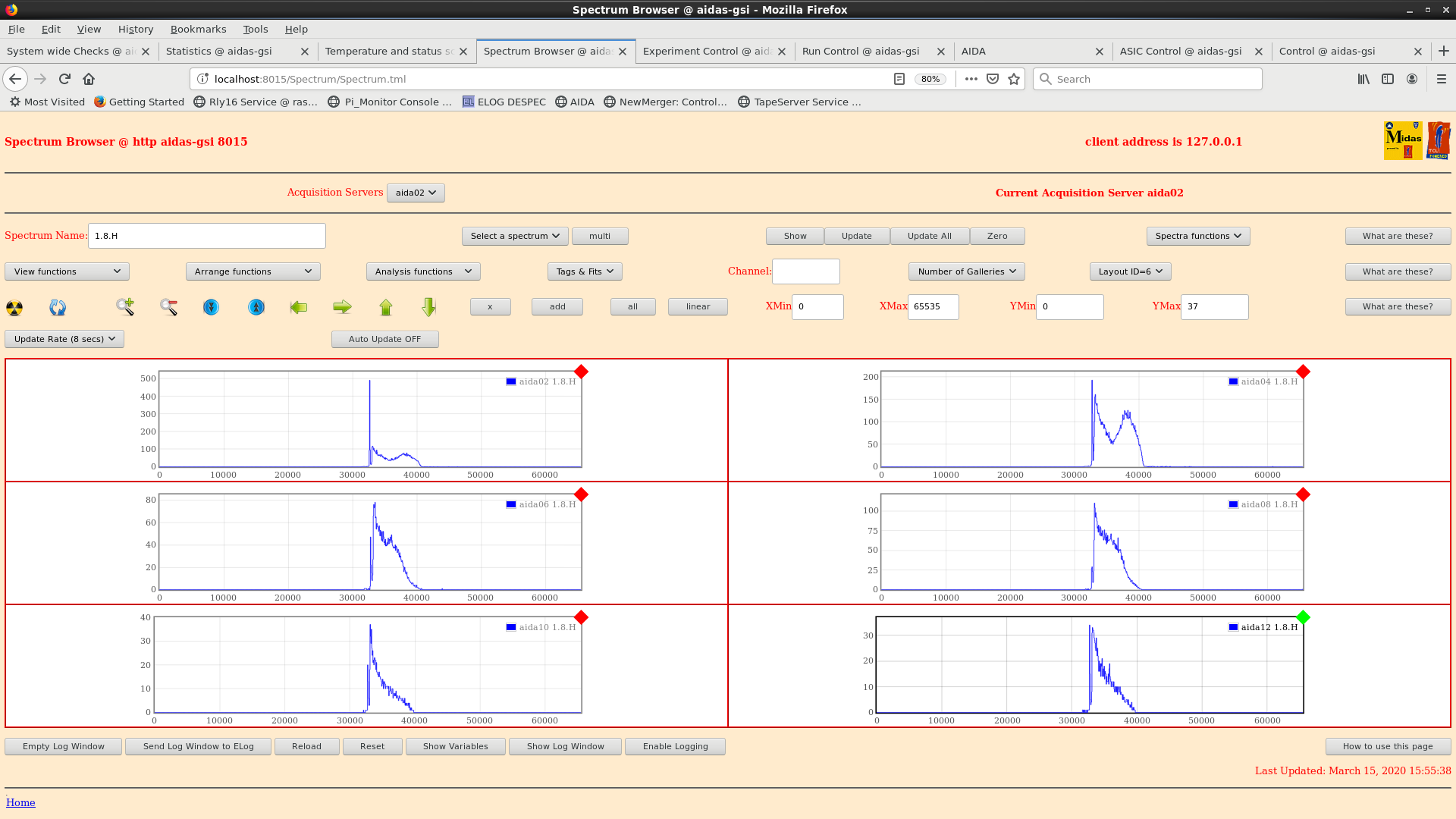

per FEE64 Stat spectra - attachment 4

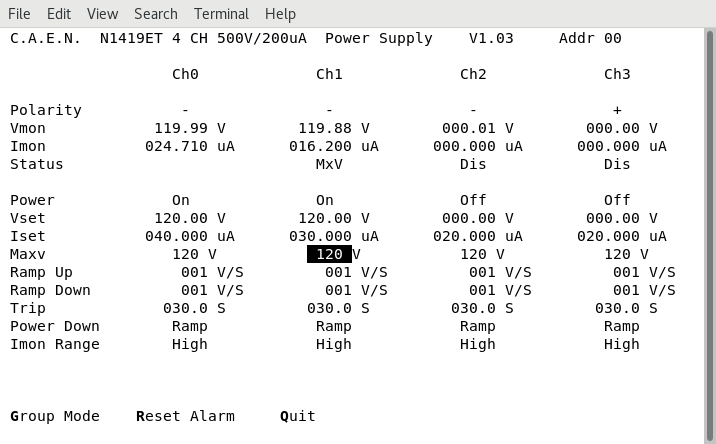

06.52 DSSSD bias & leakage current - attachment 5

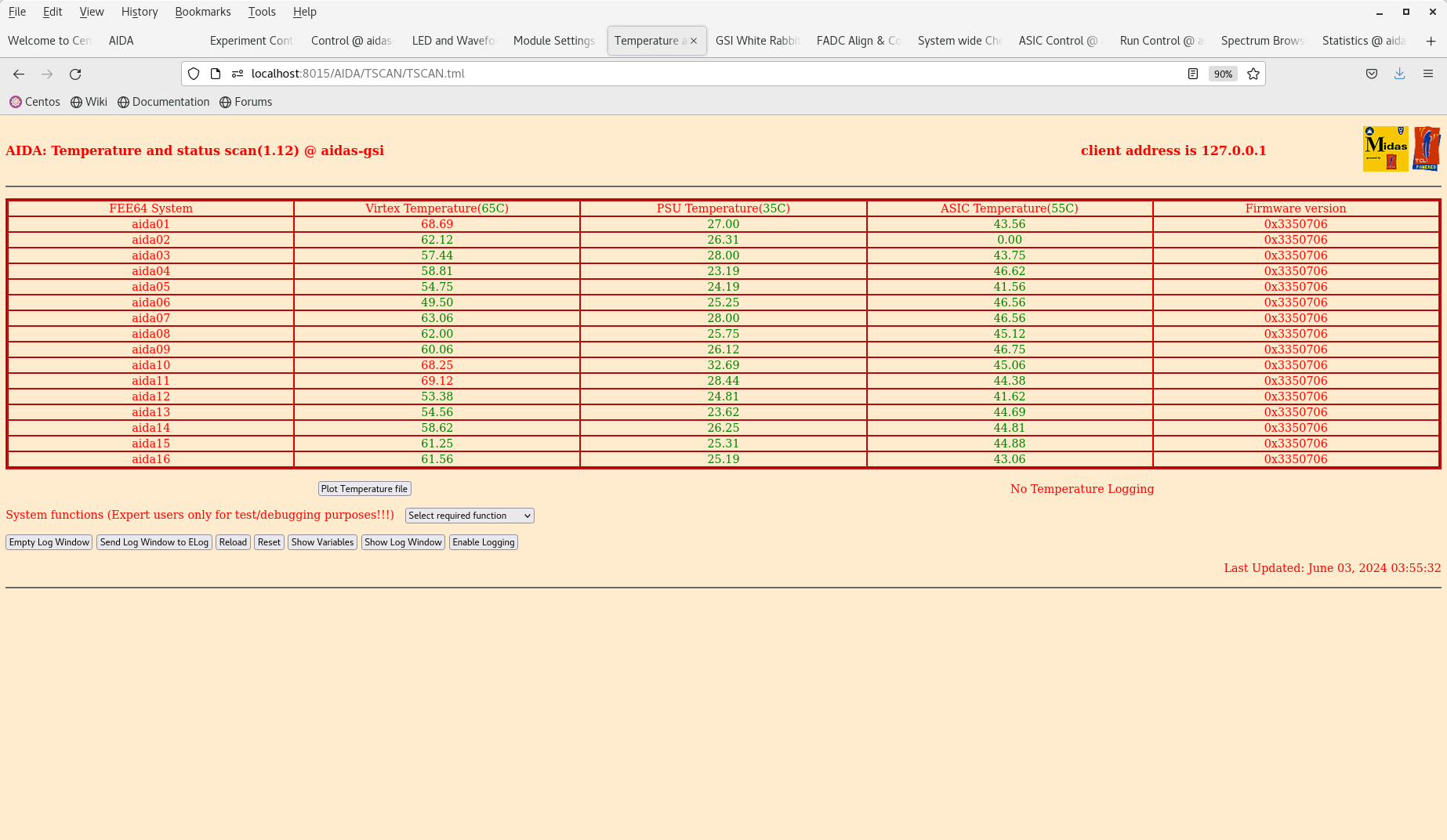

FEE64 temps OK - attachment 6

ADC data item stats - attachment 7

per FEE64 Stat spectra - attachment 8

12.13 DSSSD bias & leakage current - attachment 9

FEE64 temps OK - attachment 10

ADC data item stats - attachment 11

per FEE64 Stat spectra - attachment 12

14.51 DSSSD bias & leakage current - attachments 13-14

FEE64 temps OK - attachment 15

ADC data item stats - attachment 16

per FEE64 Stat spectra - attachment 17

21.49 DSSSD bias & leakage current - attachment 18

FEE64 temps OK - attachment 19

ADC data item stats - attachment 20

per FEE64 Stat spectra - attachment 21

03.55 DSSSD bias & leakage current - attachment 22

FEE64 temps OK - attachment 23

ADC data item stats - attachment 24

per FEE64 Stat spectra - attachment 25 |

| Attachment 1: Screenshot_from_2024-06-02_02-40-53.png

|

|

| Attachment 2: Screenshot_from_2024-06-02_02-41-25.png

|

|

| Attachment 3: Screenshot_from_2024-06-02_02-41-49.png

|

|

| Attachment 4: Screenshot_from_2024-06-02_02-42-57.png

|

|

| Attachment 5: Screenshot_from_2024-06-02_06-52-56.png

|

|

| Attachment 6: Screenshot_from_2024-06-02_06-53-29.png

|

|

| Attachment 7: Screenshot_from_2024-06-02_06-53-57.png

|

|

| Attachment 8: Screenshot_from_2024-06-02_06-54-52.png

|

|

| Attachment 9: Screenshot_from_2024-06-02_12-13-13.png

|

|

| Attachment 10: Screenshot_from_2024-06-02_12-13-46.png

|

|

| Attachment 11: Screenshot_from_2024-06-02_12-14-07.png

|

|

| Attachment 12: Screenshot_from_2024-06-02_12-15-07.png

|

|

| Attachment 13: Screenshot_from_2024-06-02_14-47-23.png

|

|

| Attachment 14: Screenshot_from_2024-06-02_14-51-12.png

|

|

| Attachment 15: Screenshot_from_2024-06-02_14-51-45.png

|

|

| Attachment 16: Screenshot_from_2024-06-02_14-52-12.png

|

|

| Attachment 17: Screenshot_from_2024-06-02_14-52-46.png

|

|

| Attachment 18: Screenshot_from_2024-06-02_21-47-35.png

|

|

| Attachment 19: Screenshot_from_2024-06-02_21-48-05.png

|

|

| Attachment 20: Screenshot_from_2024-06-02_21-48-30.png

|

|

| Attachment 21: Screenshot_from_2024-06-02_21-49-08.png

|

|

| Attachment 22: Screenshot_from_2024-06-03_03-55-12.png

|

|

| Attachment 23: Screenshot_from_2024-06-03_03-55-56.png

|

|

| Attachment 24: Screenshot_from_2024-06-03_03-56-23.png

|

|

| Attachment 25: Screenshot_from_2024-06-03_03-58-23.png

|

|

|

484

|

Sun Jun 19 12:36:10 2022 |

OH | Sunday 19th June |

Yesterday the sum/inverter was found to be a considerable source of noise in the system.

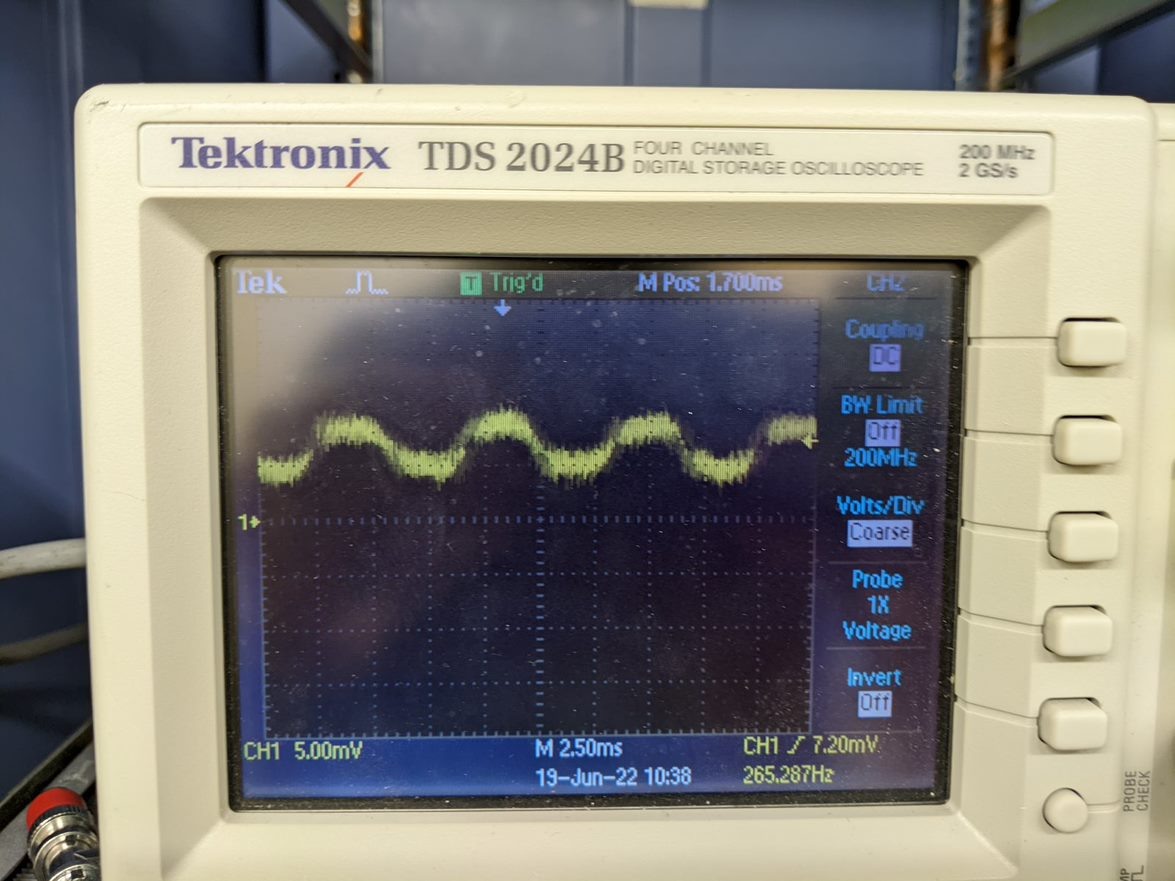

Plugging it into an oscilloscope this morning it was clear there was a Vpp 17mv 60kHz sin wave in its signal - attachment 1 yellow trace

Moved the inverter to a crate in the messheute and did not see same behaviour. This time see Vpp 5mV and a ~265Hz wave that looks much less clean. - attachment 2 yellow

Put inverter back in CAEN crate in S4 and confirm similar behavior.

Move CAEN crate to new mains port, same behaviour

Move CAEN crate to AC voltage stabiliser, same behaviour

Remove module one by one from CAEN crate.

Removing BIAS supply - No change

Remove Pulser - No change

Remove right most MACB - No change

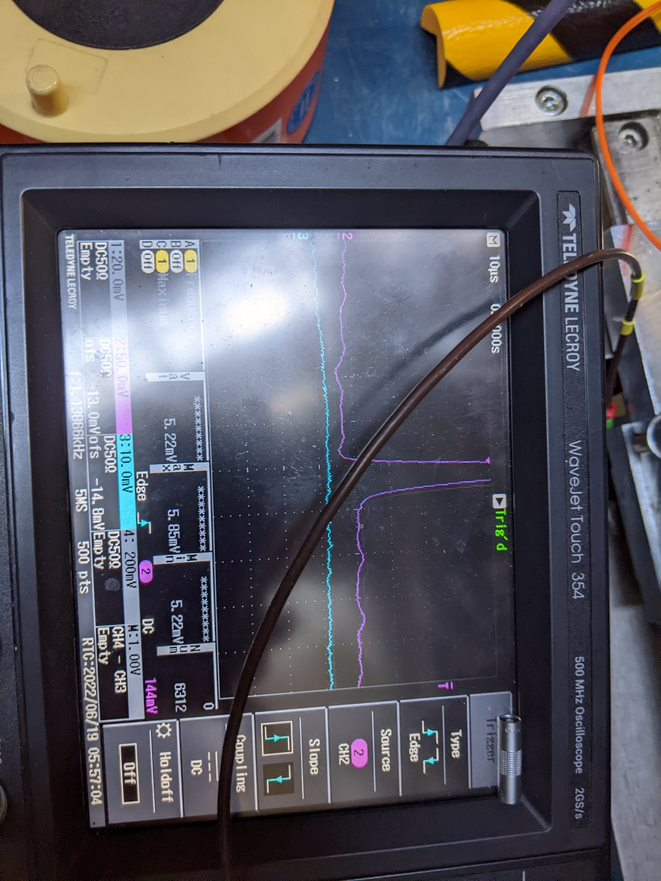

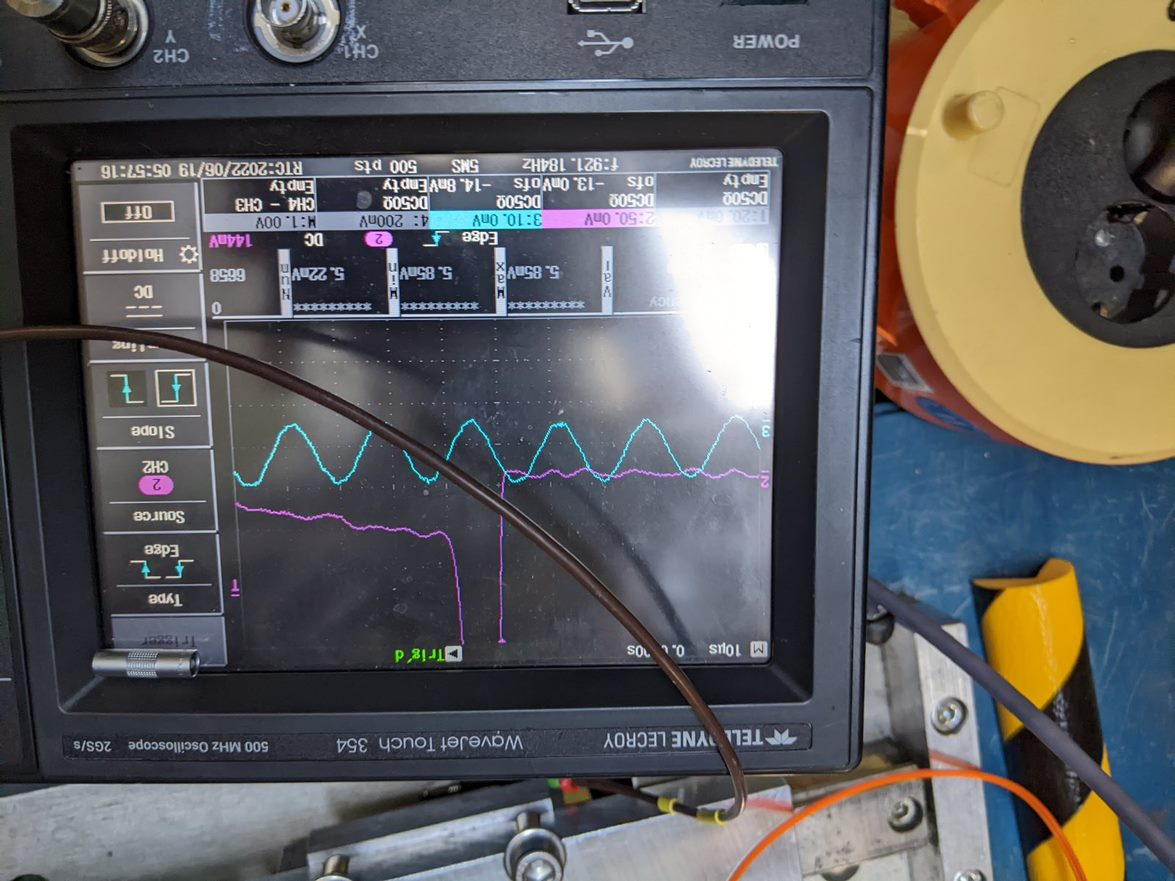

Remove second right most MACB - Signal disappears - attachment 3 blue trace

Remove second right most MACB from the rack entirely

Put right most MACB back - Signal comes back - attachment 4 blue trace

Test MACB with and without HDMI connectors connected signal remains

Remove rightmost MACB from the rack - Signal disappears

Put pulser and bias back - Signal does not return

Signal also doesn't return when ramping up bias or running the pulser

Power DAQ up - No change in performance from yesterday with inverter removed.

MACB and Inverter don't share any voltages on NIM:

MACB +-6V and Gnd

Inverter +-24V and Gnd

CAEN Crate does not have any easily accessible monitoring points. Anyone have any ideas?

MACBs and inverter checked on another crate - no signal

Inverter put back in CAEN crate and no noise observed on scope.

With waveforms disabled am able to get <100kHz on all FEEs with the pulser connected

Tested adding bias filters - No change

15:30 Nic realised that one of the mains boxes is labelled measurement network so we connect the AIDA PSU to this via the ac stabiliser

We get ok stats even with waveforms on at 0xa- attachment 5

Waveforms still have the 100kHz oscillation in them though attachments 6 and 7

Without waveforms we get similar performance to before the switch to the new mains - attachment 8

15:56 Move CAEN NIM crate across to this mains network

300+kHz on all FEEs with waveforms on. Can recover waveform off performance though

16:01 Place CAEN NIM crate back onto platform mains but don't recover the ealier rates with waveform. Everything still around 300kHz.

17:43 Current best settings are waveforms off and we can run at 0xa on all FEEs - attachment 9 |

| Attachment 1: 1.jpg

|

|

| Attachment 2: 2.jpg

|

|

| Attachment 3: 3.jpg

|

|

| Attachment 4: 4.jpg

|

|

| Attachment 5: 220618_1753_stats_no_waveform.png

|

|

|

483

|

Sun Jun 19 00:22:24 2022 |

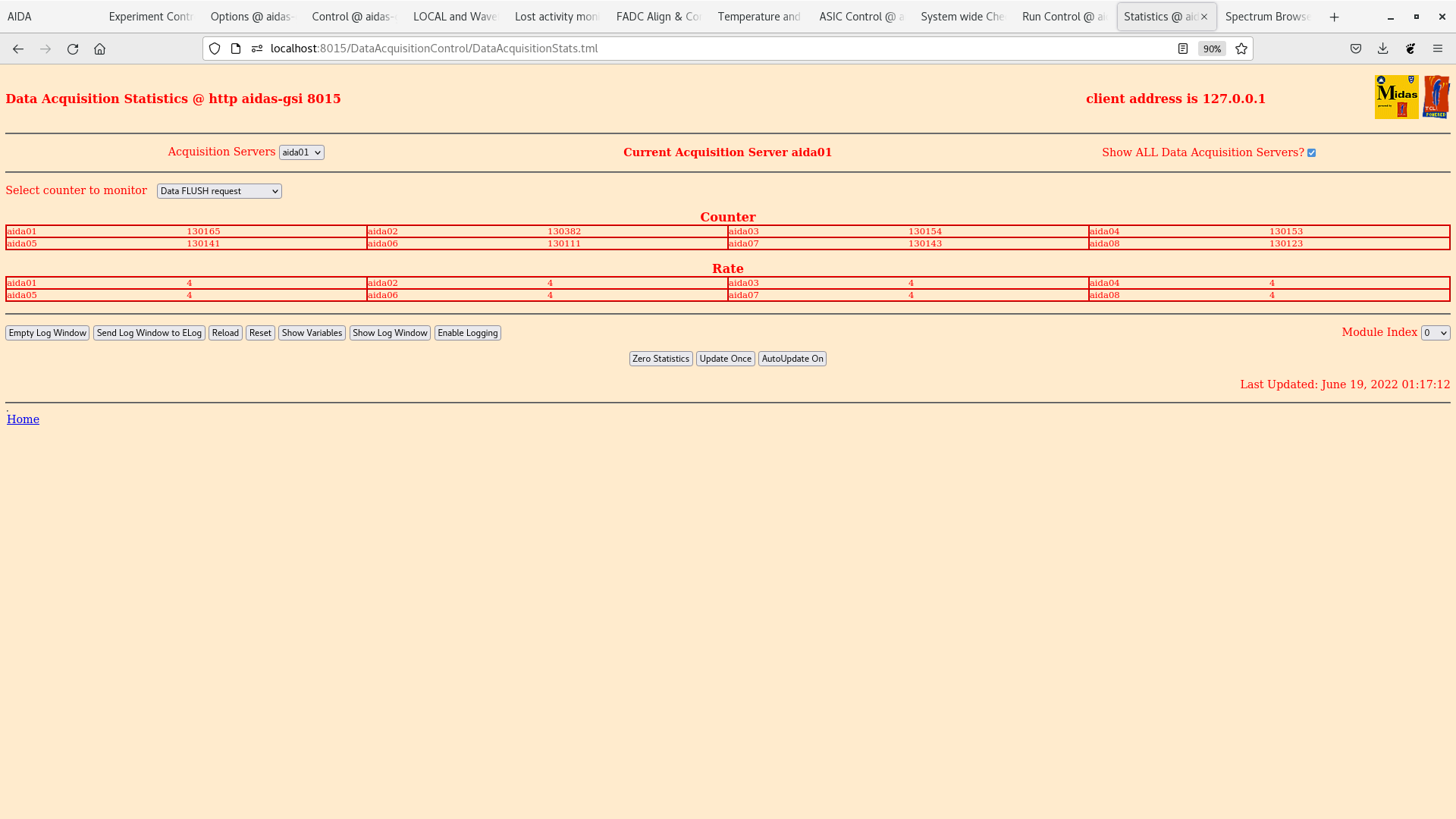

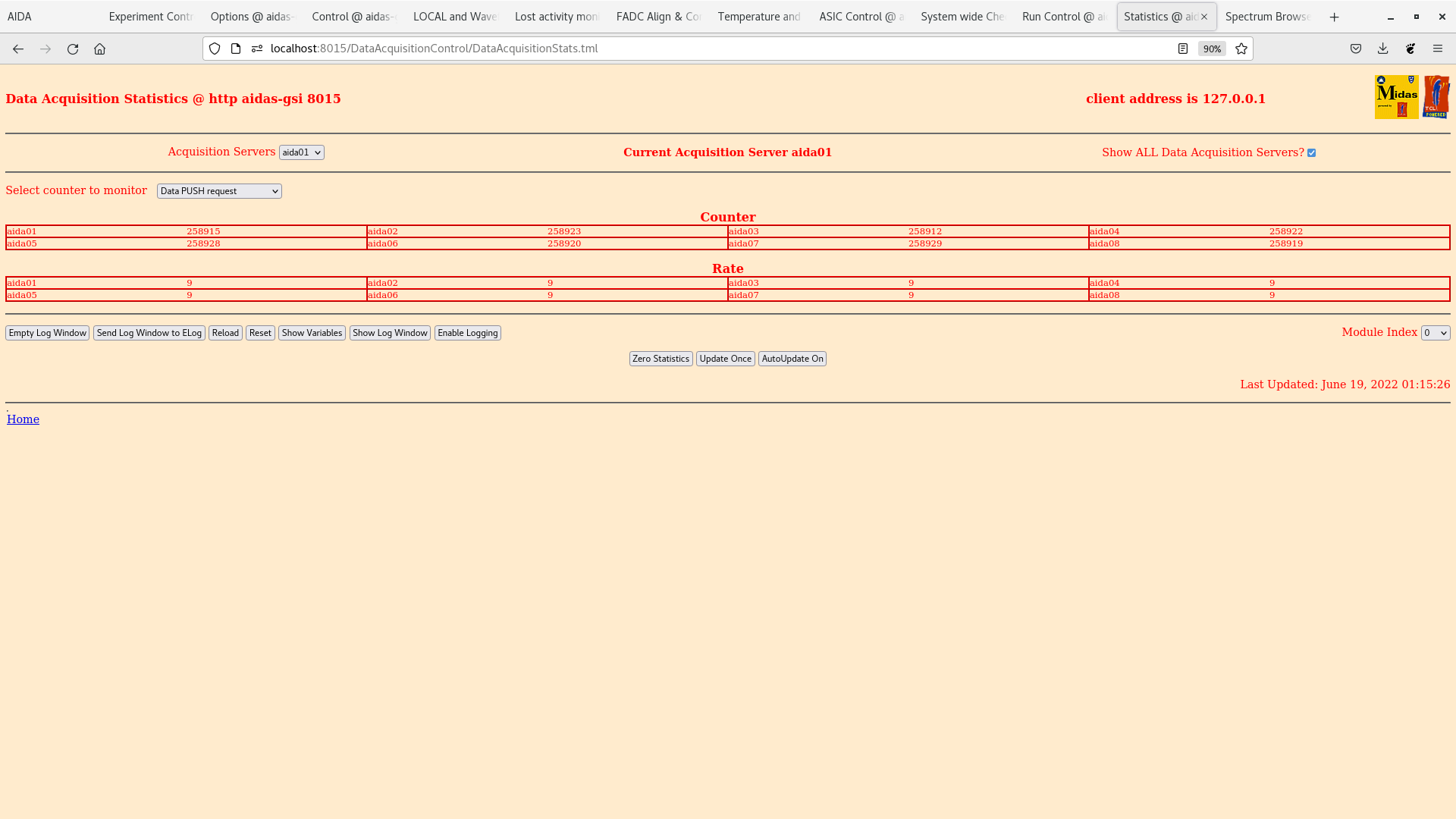

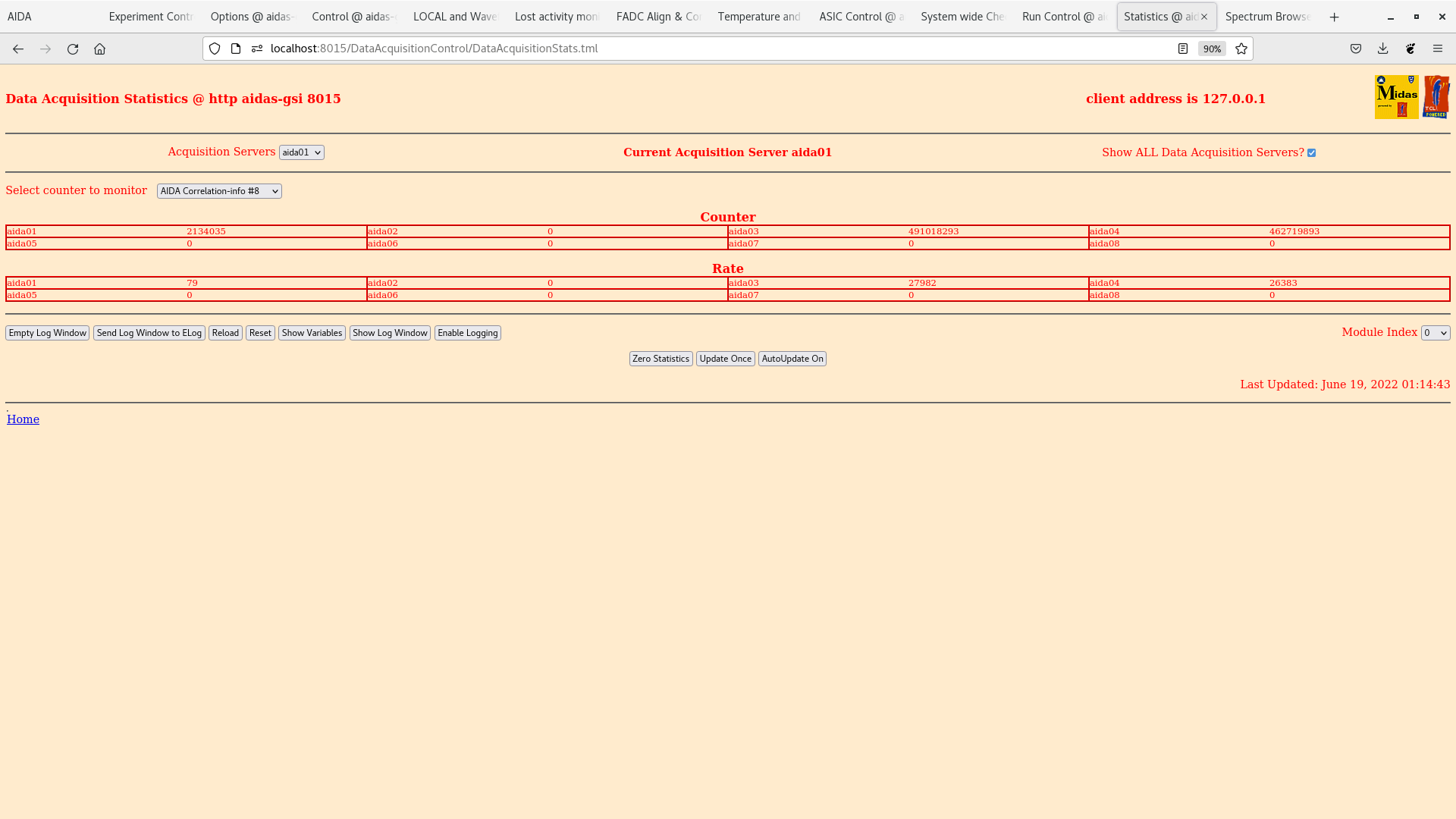

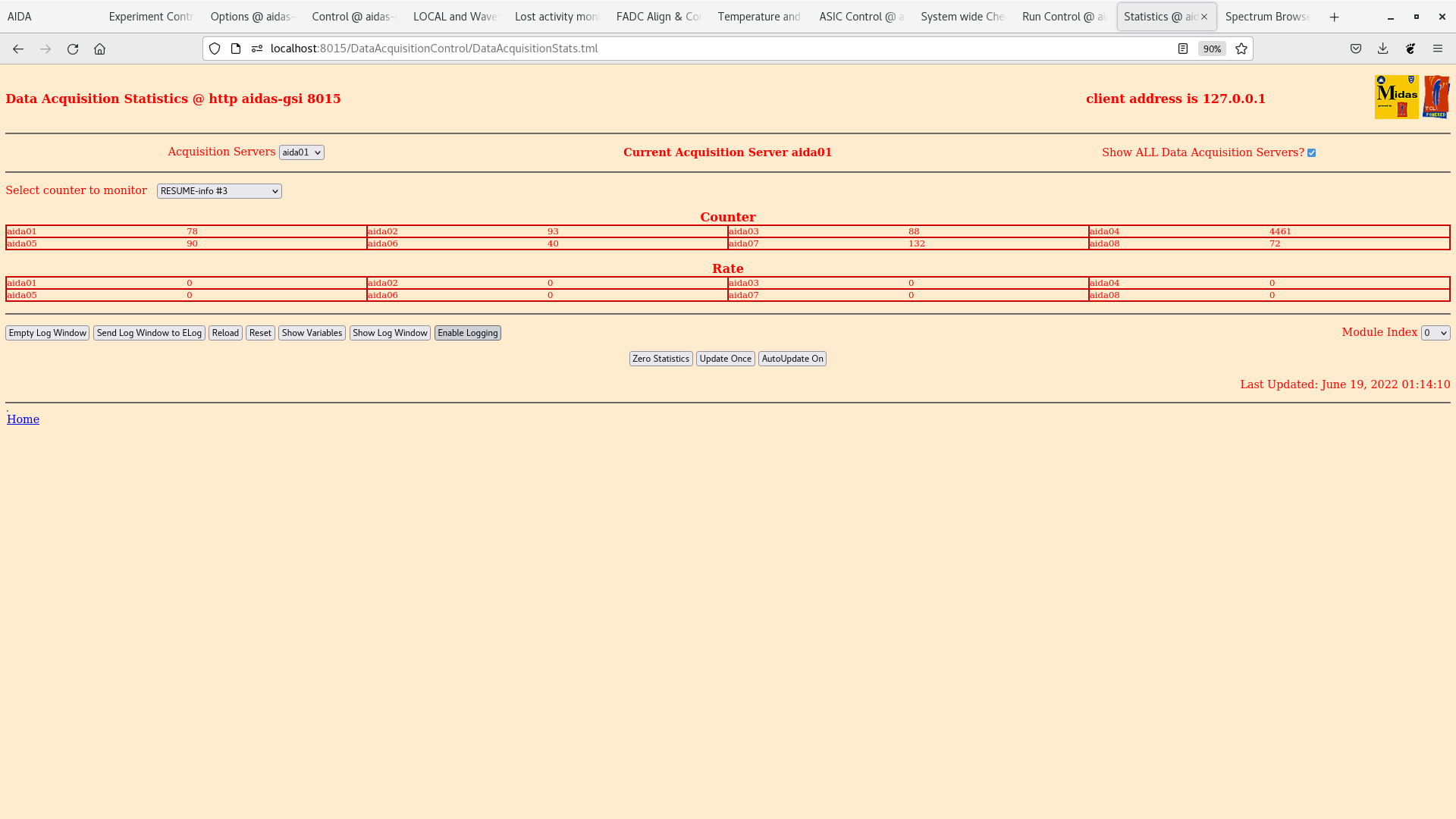

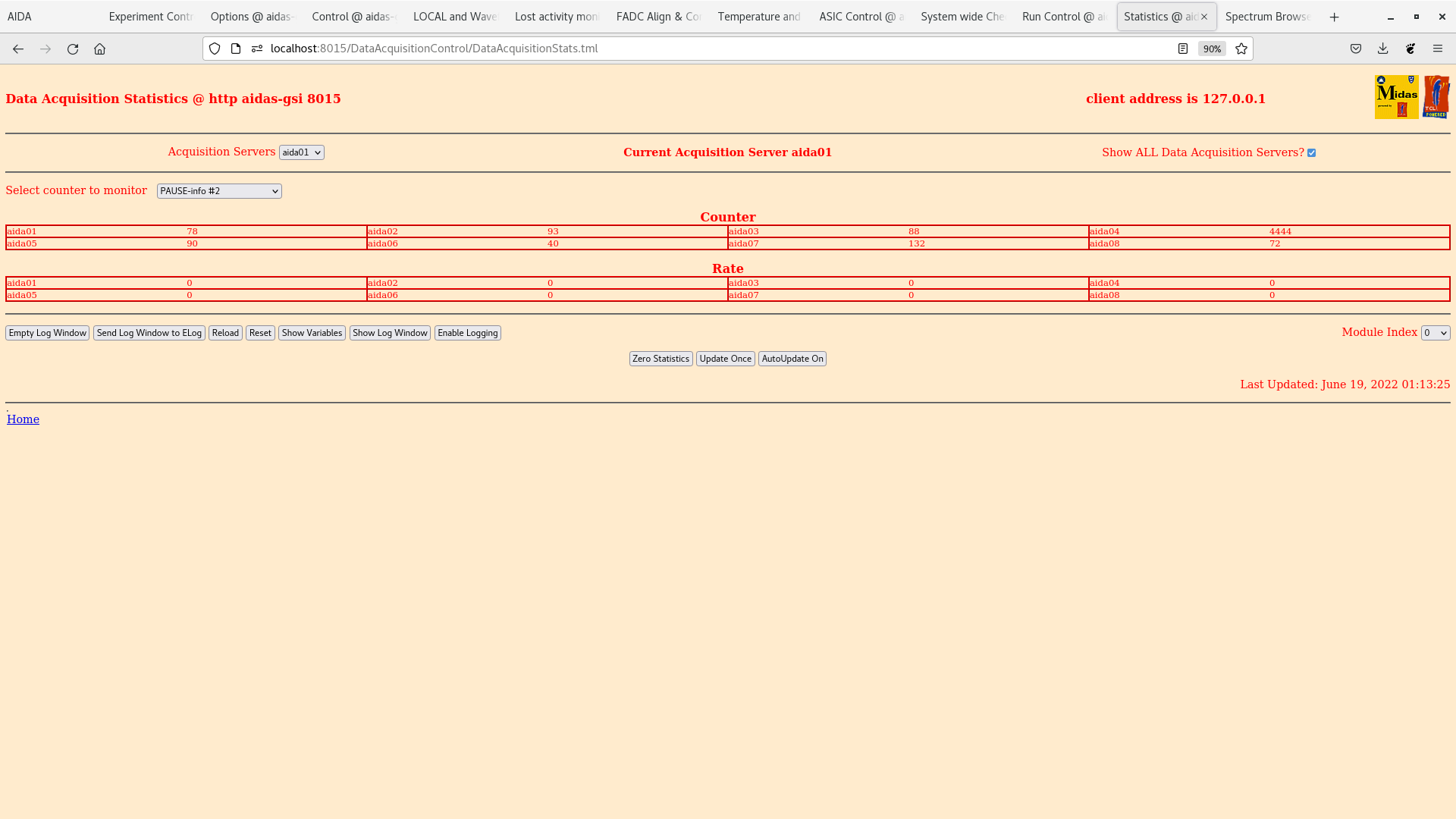

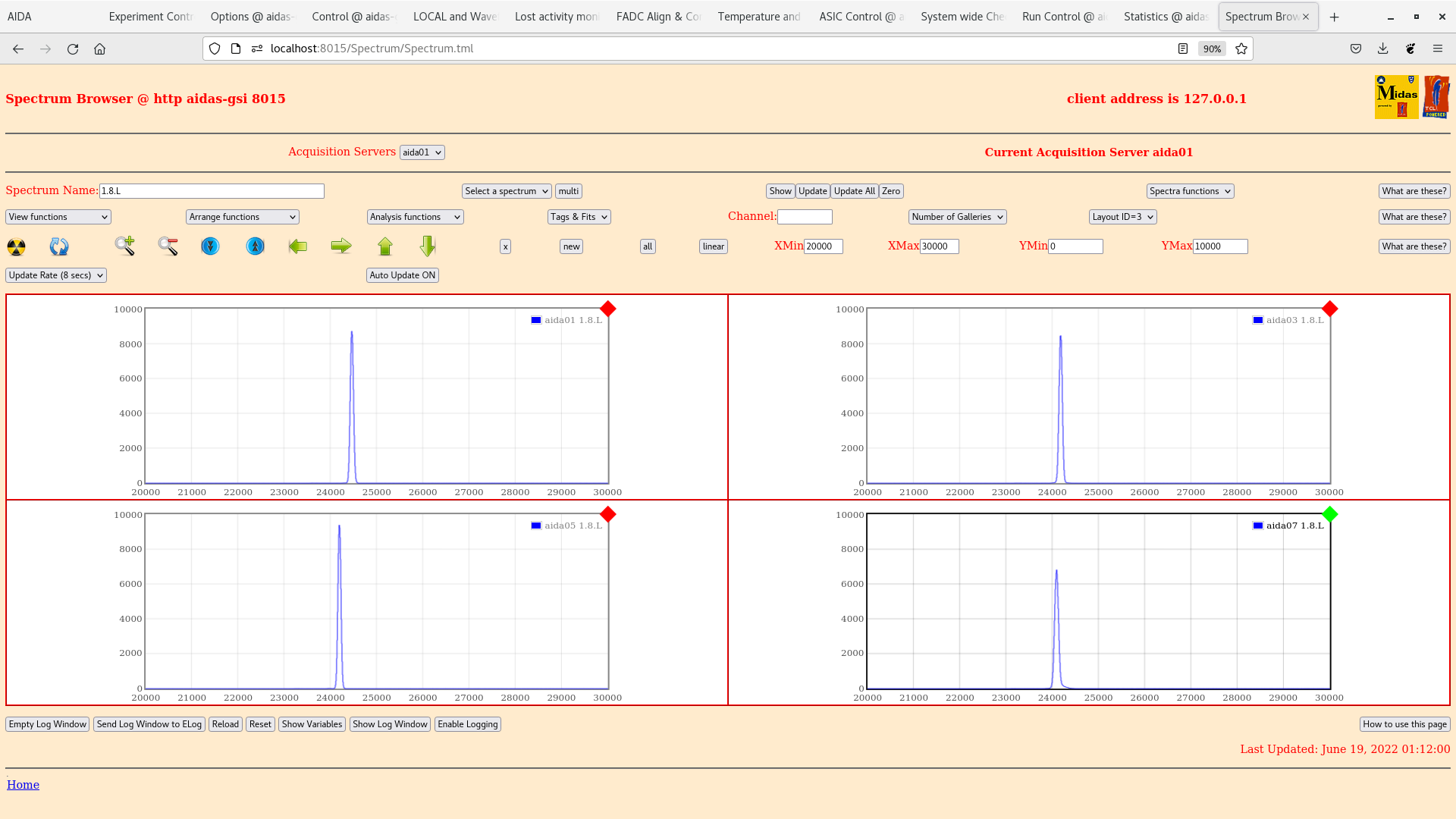

TD | Sunday 19 June |

01.20

ASIC settings 2021Apr29-13-16-00

*except* slow comparator 0x64 -> 0xa

All waveform ADCs disabled

BNC PB-5 pulser

to p+n FEE64s only

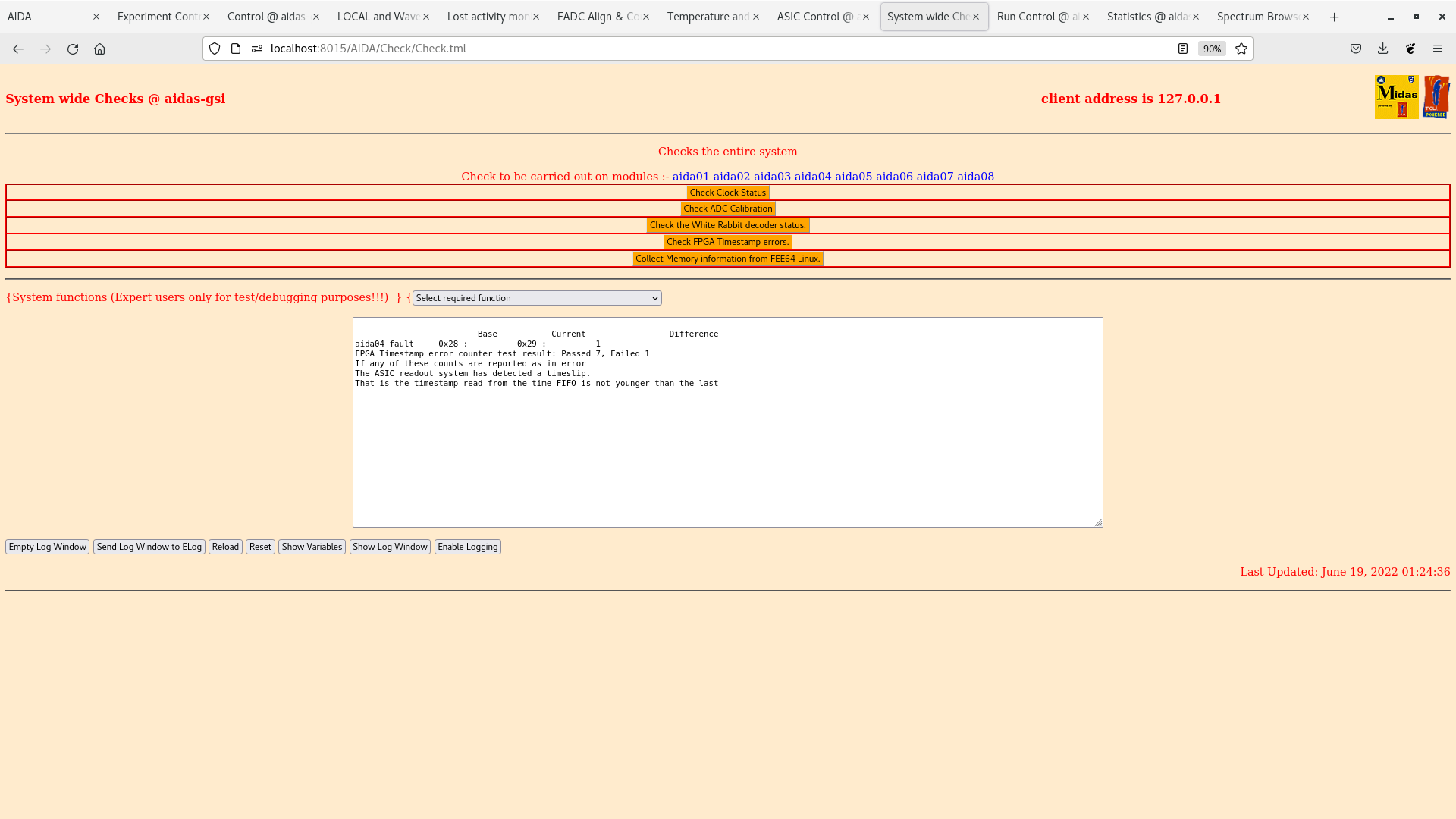

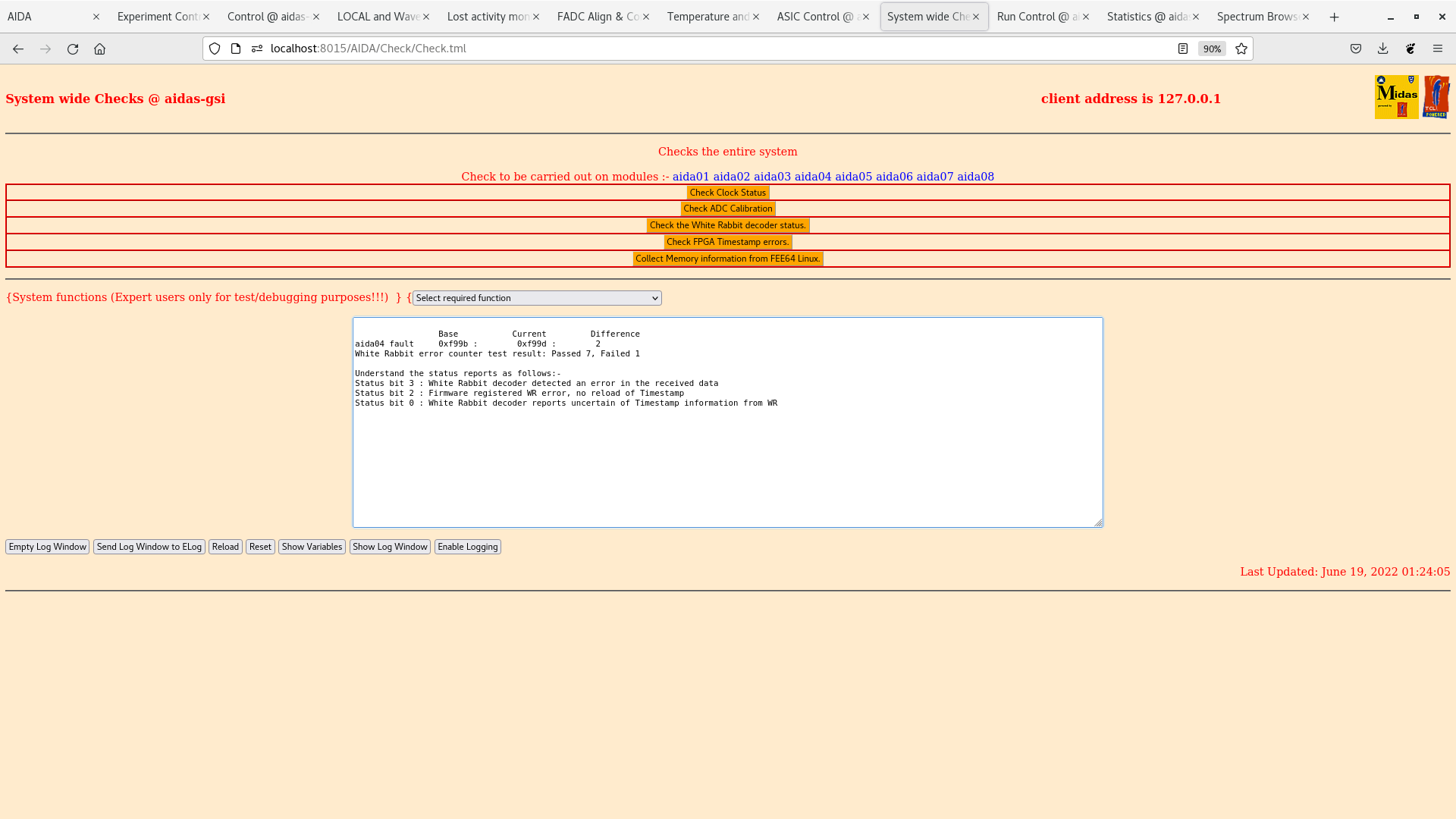

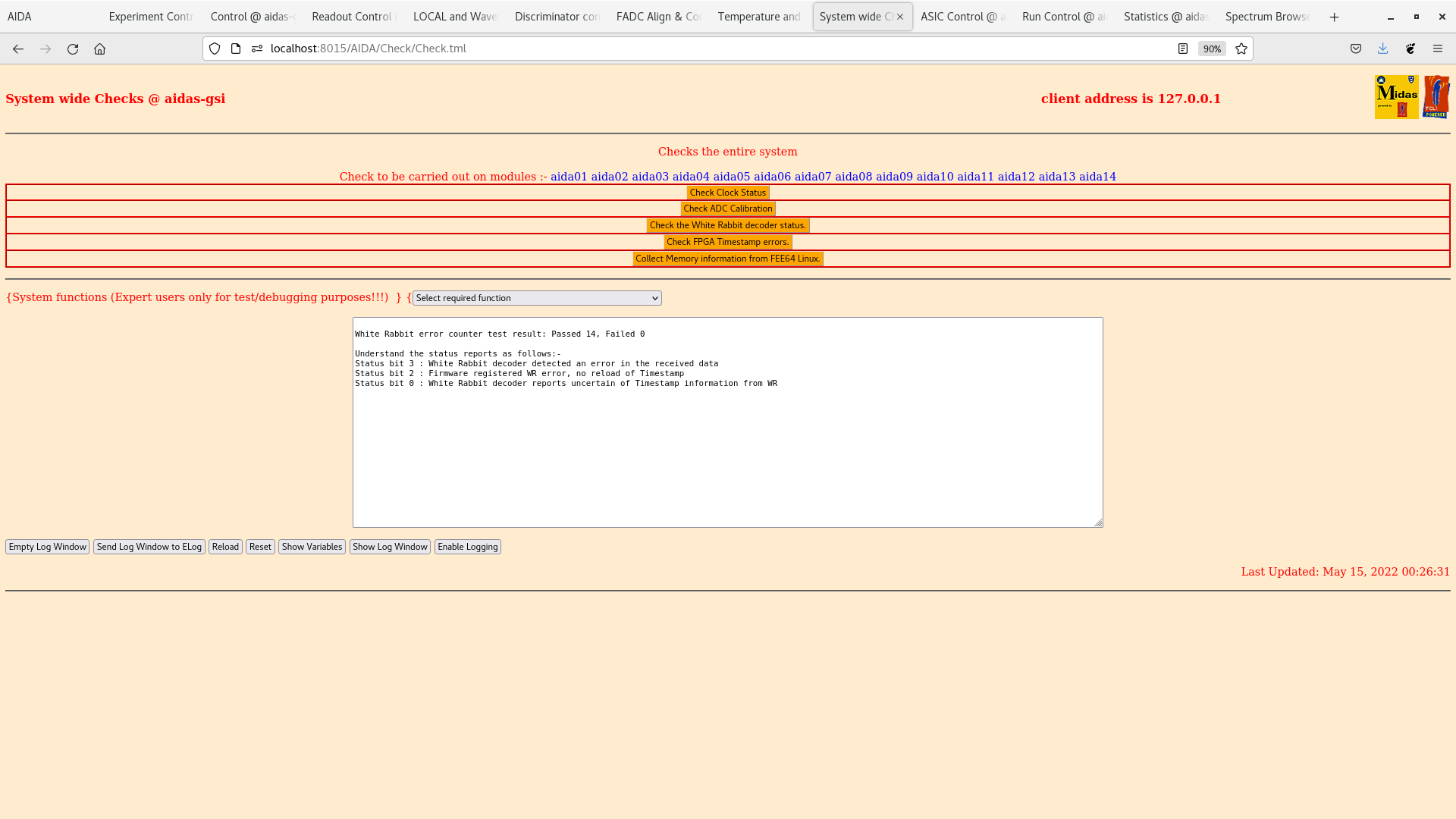

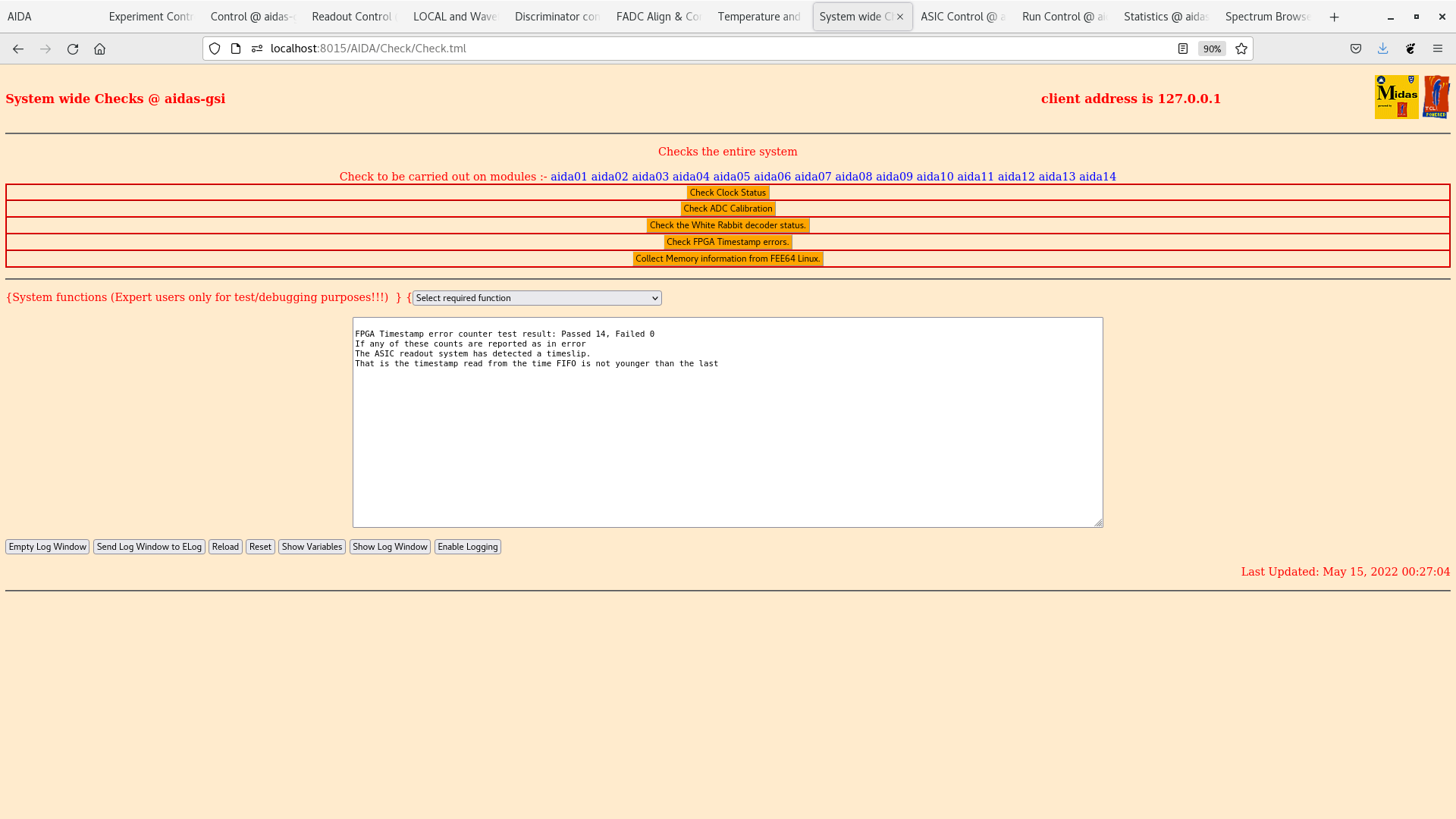

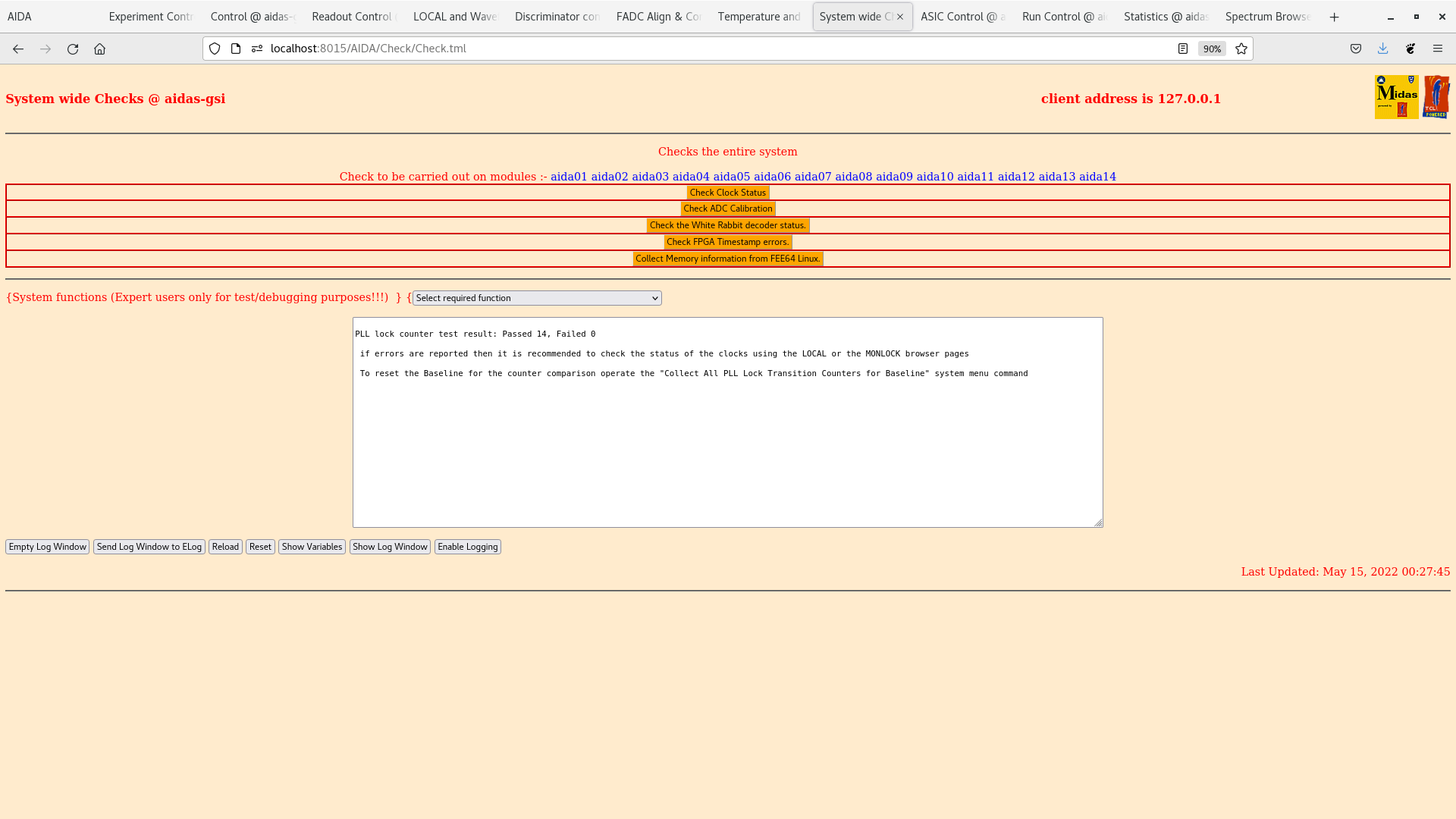

all system wide checks OK *except* ADC calibration, WR decoder & FPGA timestamp errors - see attachments 1 & 2

DSSSD bias & leakage current OK - see attachments 3 & 4

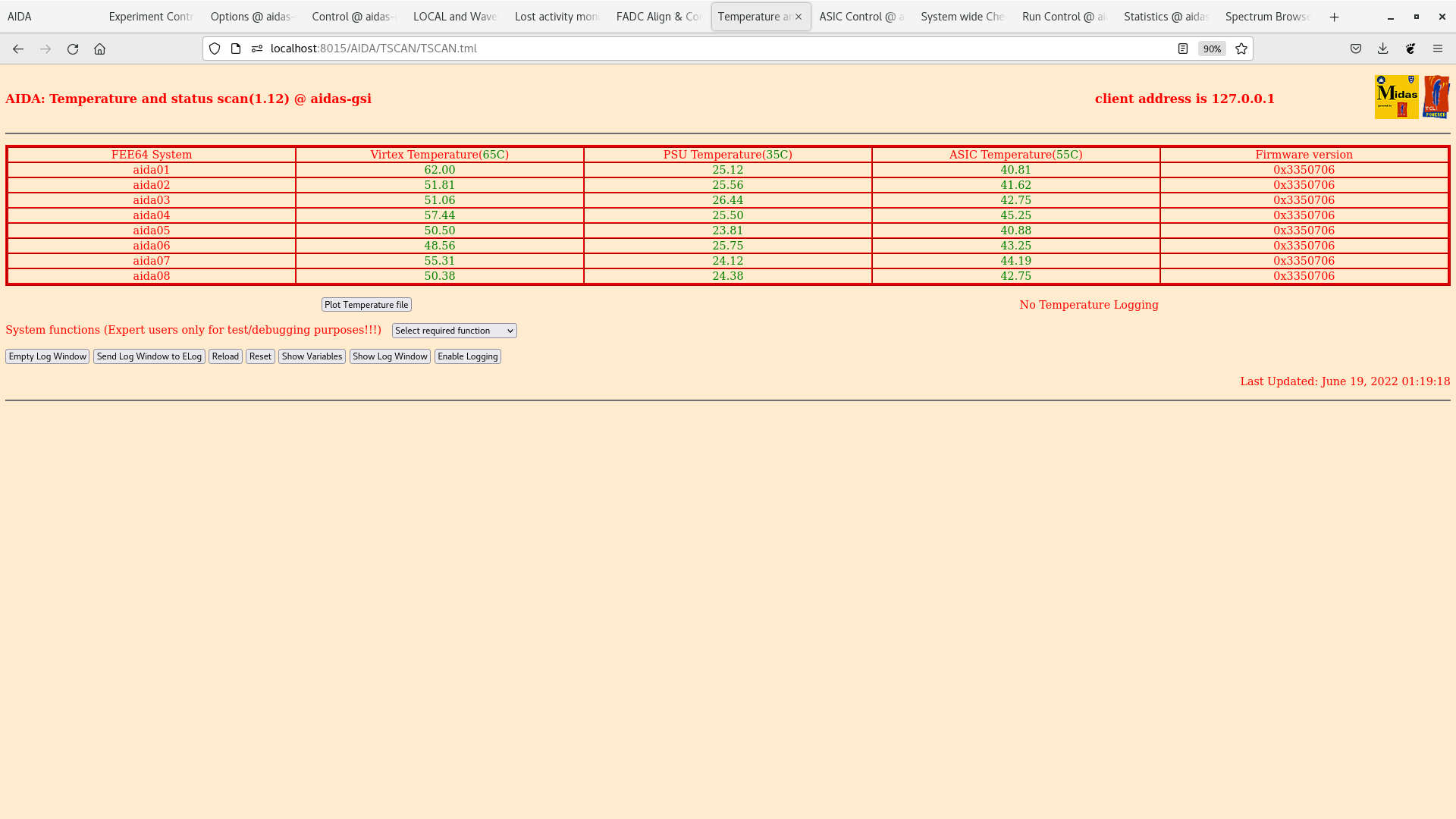

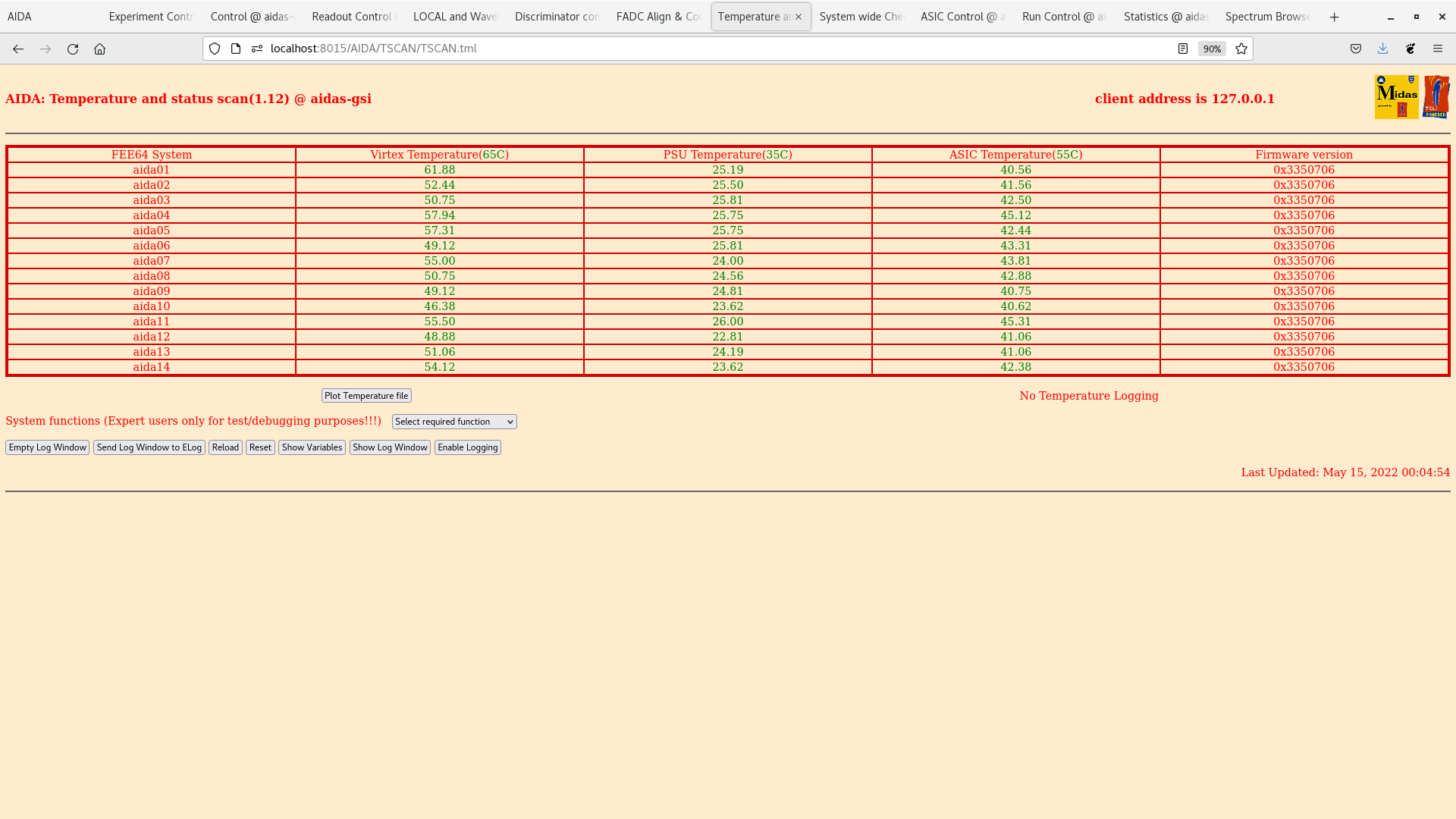

FEE64 temps OK - see attachment 5

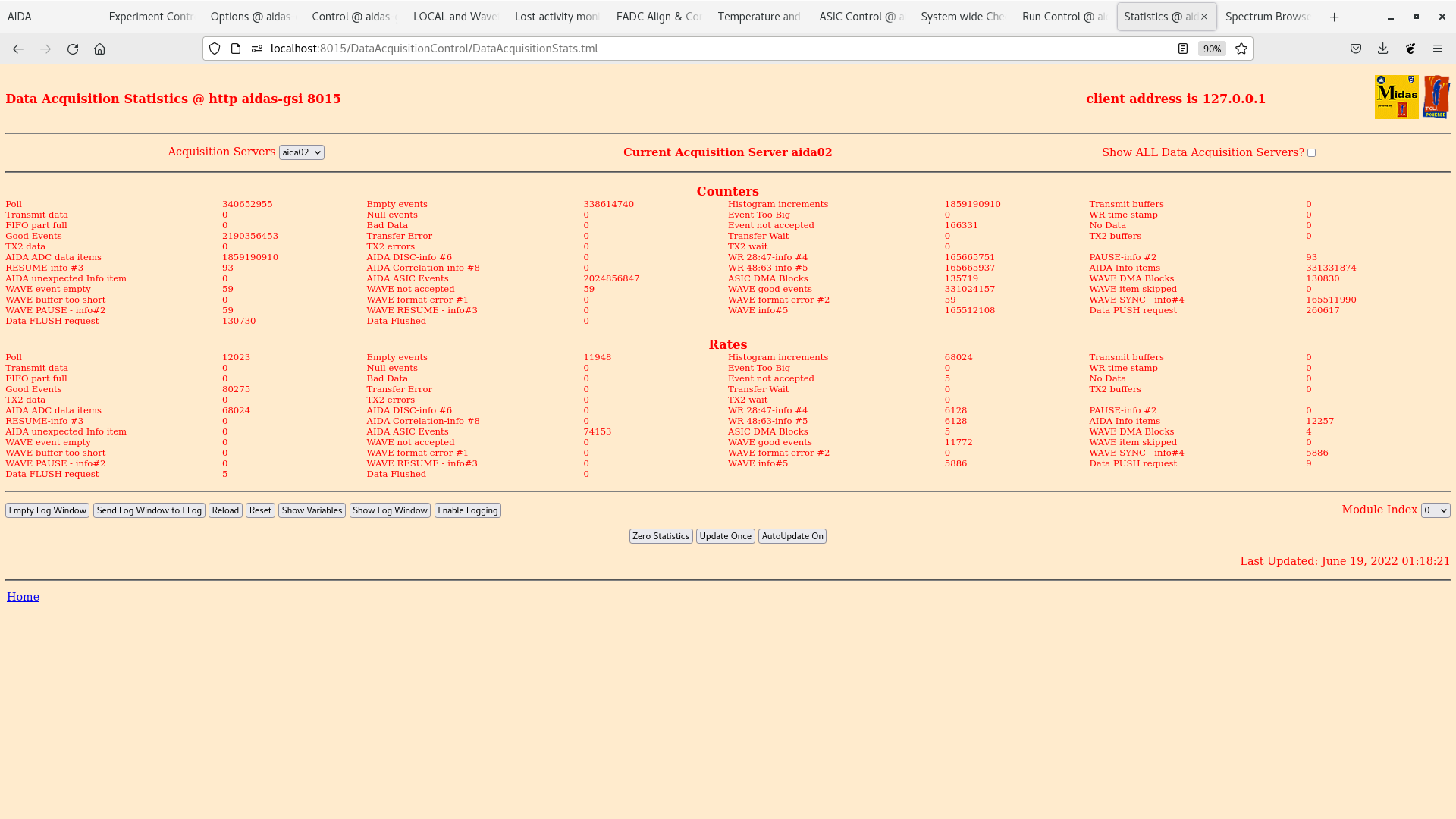

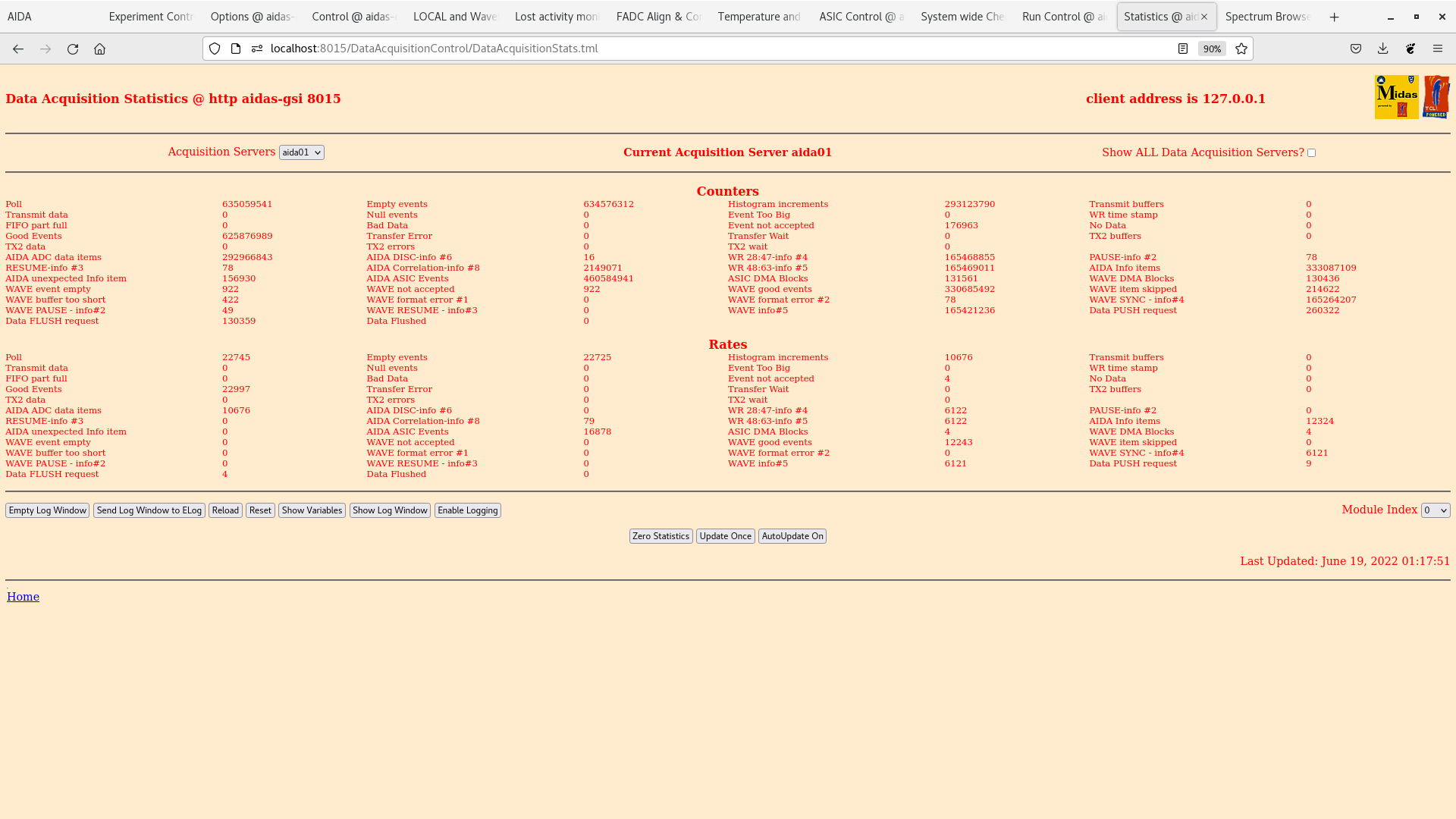

statistics OK - ADC data, pause, resume & correlation scaler data items

data push, data flush, aida01, aida02 - see attachments 6-13

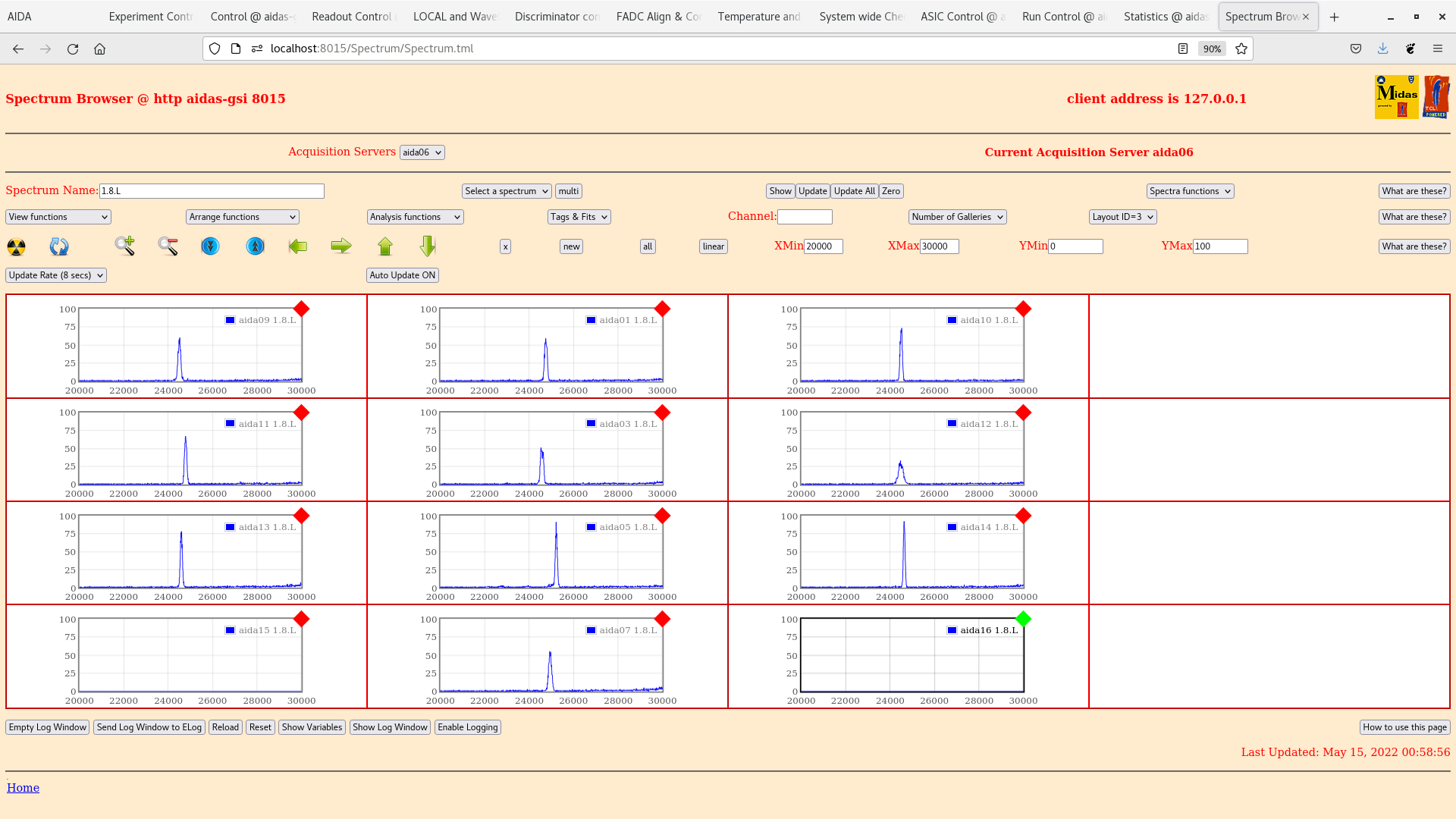

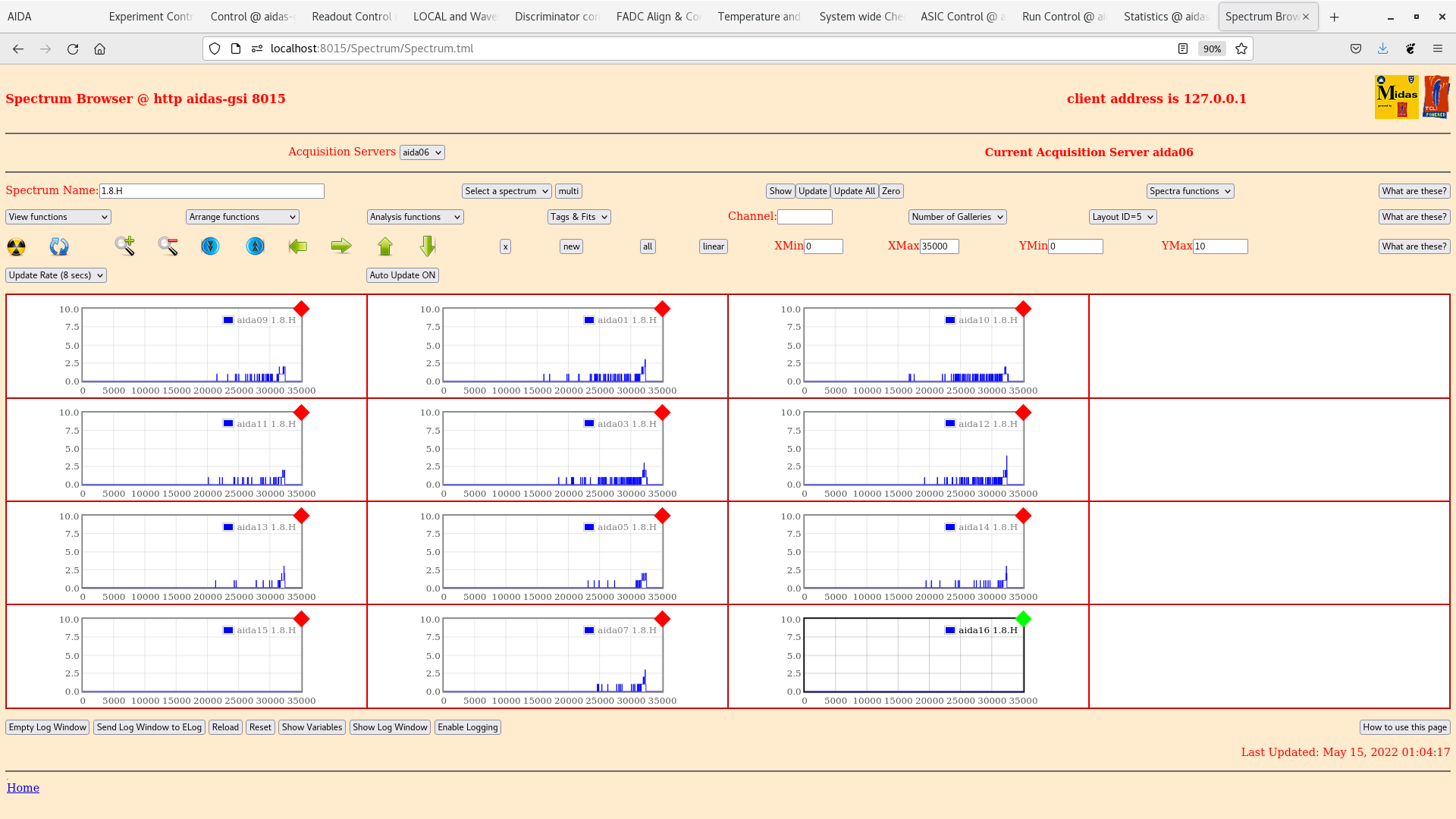

per FEE64 1.8.L spectra - see attachment 14

aida01 pulser peak width 73 ch FWHM |

| Attachment 1: Screenshot_from_2022-06-19_01-24-50.png

|

|

| Attachment 2: Screenshot_from_2022-06-19_01-24-24.png

|

|

| Attachment 3: Screenshot_from_2022-06-19_01-20-50.png

|

|

| Attachment 4: Screenshot_from_2022-06-19_01-20-09.png

|

|

| Attachment 5: Screenshot_from_2022-06-19_01-19-37.png

|

|

| Attachment 6: Screenshot_from_2022-06-19_01-18-35.png

|

|

| Attachment 7: Screenshot_from_2022-06-19_01-18-05.png

|

|

| Attachment 8: Screenshot_from_2022-06-19_01-17-28.png

|

|

| Attachment 9: Screenshot_from_2022-06-19_01-15-44.png

|

|

| Attachment 10: Screenshot_from_2022-06-19_01-14-59.png

|

|

| Attachment 11: Screenshot_from_2022-06-19_01-14-24.png

|

|

| Attachment 12: Screenshot_from_2022-06-19_01-13-43.png

|

|

| Attachment 13: Screenshot_from_2022-06-19_01-13-03.png

|

|

| Attachment 14: Screenshot_from_2022-06-19_01-12-16.png

|

|

|

238

|

Sun Apr 18 07:30:20 2021 |

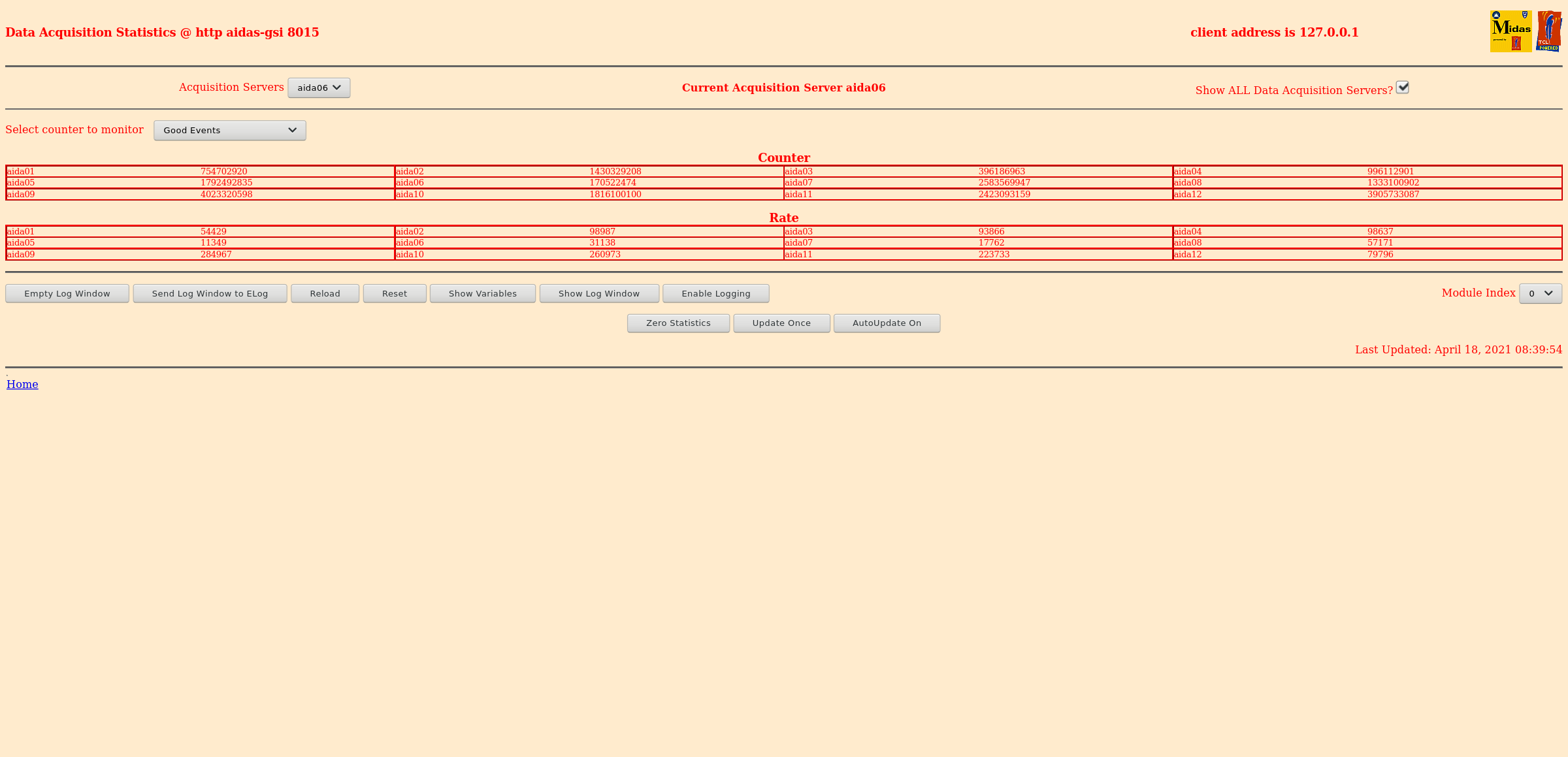

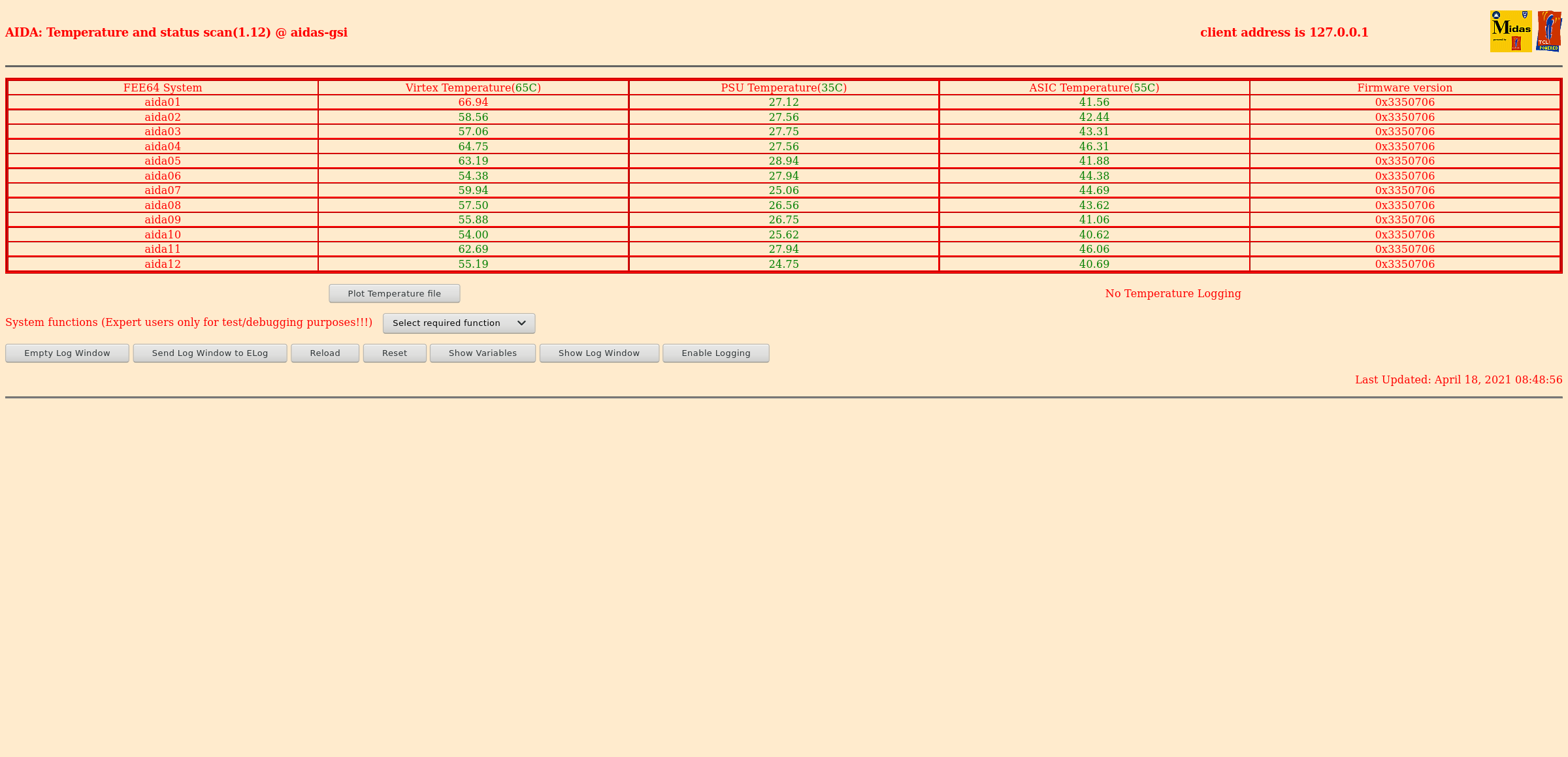

DJ, TD | Sunday 18th April 08:00-12:00 |

---- 09-26

FEE64 module aida06 failed

FEE64 module aida07 failed

FEE64 module aida10 failed

Calibration test result: Passed 9, Failed 3

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

---

Base Current Difference

aida01 fault 0x7685 : 0x7686 : 1

aida02 fault 0x941c : 0x941d : 1

aida03 fault 0x7cd6 : 0x7cd7 : 1

aida04 fault 0xb86c : 0xb86d : 1

aida05 fault 0x1a52 : 0x1a59 : 7

aida06 fault 0x4f3e : 0x4f45 : 7

aida07 fault 0x3bcd : 0x3bfc : 47

aida08 fault 0xc7c7 : 0xc7ce : 7

aida09 fault 0xb33a : 0xb33b : 1

White Rabbit error counter test result: Passed 3, Failed 9

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

--

Base Current Difference

aida01 fault 0x7685 : 0x7686 : 1

aida02 fault 0x941c : 0x941d : 1

aida03 fault 0x7cd6 : 0x7cd7 : 1

aida04 fault 0xb86c : 0xb86d : 1

aida05 fault 0x1a52 : 0x1a59 : 7

aida06 fault 0x4f3e : 0x4f45 : 7

aida07 fault 0x3bcd : 0x3bfc : 47

aida08 fault 0xc7c7 : 0xc7ce : 7

aida09 fault 0xb33a : 0xb33b : 1

White Rabbit error counter test result: Passed 3, Failed 9

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

-

Base Current Difference

aida01 fault 0x7685 : 0x7686 : 1

aida02 fault 0x941c : 0x941d : 1

aida03 fault 0x7cd6 : 0x7cd7 : 1

aida04 fault 0xb86c : 0xb86d : 1

aida05 fault 0x1a52 : 0x1a59 : 7

aida06 fault 0x4f3e : 0x4f45 : 7

aida07 fault 0x3bcd : 0x3bfc : 47

aida08 fault 0xc7c7 : 0xc7ce : 7

aida09 fault 0xb33a : 0xb33b : 1

White Rabbit error counter test result: Passed 3, Failed 9

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

08.45 TD resets baseline for WR and FPGA errors

|

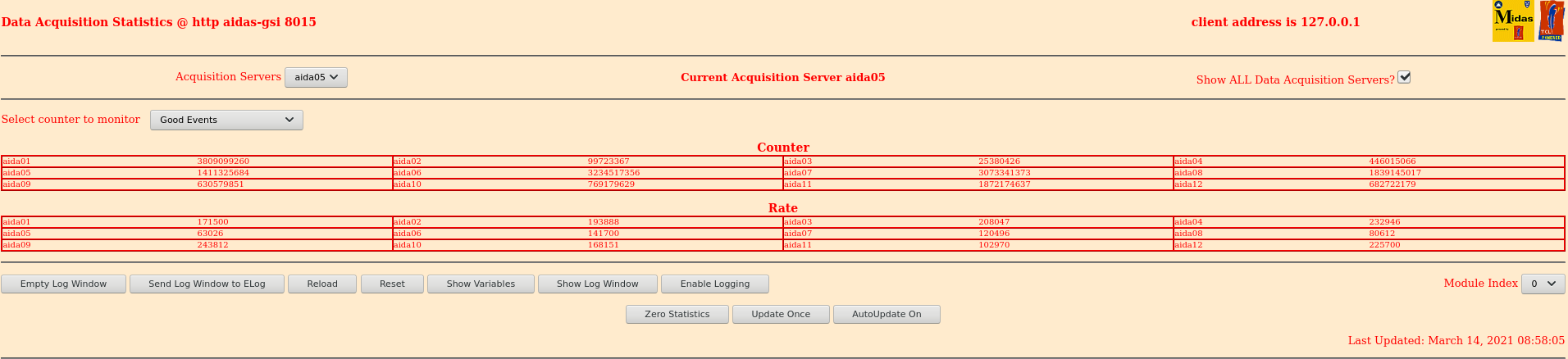

| Attachment 1: Screenshot_2021-04-18_Statistics_aidas-gsi.png

|

|

| Attachment 2: Screenshot_2021-04-18_Temperature_and_status_scan_aidas-gsi.png

|

|

| Attachment 3: 52.png

|

|

| Attachment 4: 53.png

|

|

| Attachment 5: Screenshot_2021-04-18_Temperature_and_status_scan_aidas-gsi(1).png

|

.png.png)

|

| Attachment 6: 54.png

|

|

| Attachment 7: Screenshot_2021-04-18_Statistics_aidas-gsi(1).png

|

.png.png)

|

|

239

|

Sun Apr 18 11:18:21 2021 |

TD | Sunday 18 April 12.00-16.00 |

12.18 DAQ continues file NULL/R30_490

ASIC settings 2019Dec19-16.19.51

slow comparator 0x64 -> 0xa

BNC PB-5

amplitude 2V

attenuation 1x

decay time 1ms

frequency 2Hz

12.22 all histograms zero'd

c. 12.30 219Rn setting

12.35 analysis of R30_490 - see attachment 1

13.15 system wide checks

Clock status test result: Passed 12, Failed 0

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

FEE64 module aida06 failed

FEE64 module aida07 failed

FEE64 module aida10 failed

Calibration test result: Passed 9, Failed 3

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

Base Current Difference

aida01 fault 0x7686 : 0x768a : 4

aida02 fault 0x941d : 0x9421 : 4

aida03 fault 0x7cd7 : 0x7cdb : 4

aida04 fault 0xb86d : 0xb871 : 4

aida05 fault 0x1a59 : 0x1a5f : 6

aida06 fault 0x4f45 : 0x4f4b : 6

aida07 fault 0x3bfc : 0x3c04 : 8

aida08 fault 0xc7ce : 0xc7d4 : 6

aida09 fault 0xb33b : 0xb33c : 1

White Rabbit error counter test result: Passed 3, Failed 9

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

Base Current Difference

aida12 fault 0xa : 0xb : 1

FPGA Timestamp error counter test result: Passed 11, Failed 1

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 23 10 3 1 1 2 1 3 3 3 6 : 36156

aida02 : 2 11 7 4 2 2 2 4 2 3 6 : 36048

aida03 : 21 8 6 4 5 4 3 3 2 3 6 : 36276

aida04 : 19 11 14 3 2 3 2 4 2 3 6 : 36324

aida05 : 25 4 5 4 4 2 1 3 2 4 6 : 37460

aida06 : 13 9 15 1 3 5 1 3 3 3 6 : 36812

aida07 : 19 10 6 1 3 3 2 2 4 3 6 : 37212

aida08 : 23 6 4 2 1 1 3 4 2 3 6 : 36044

aida09 : 11 5 5 1 2 4 3 3 2 3 6 : 35908

aida10 : 14 5 6 5 3 1 3 3 2 3 6 : 35744

aida11 : 16 5 3 0 3 3 1 4 2 3 6 : 35800

aida12 : 12 10 0 2 4 4 1 3 3 3 6 : 36544

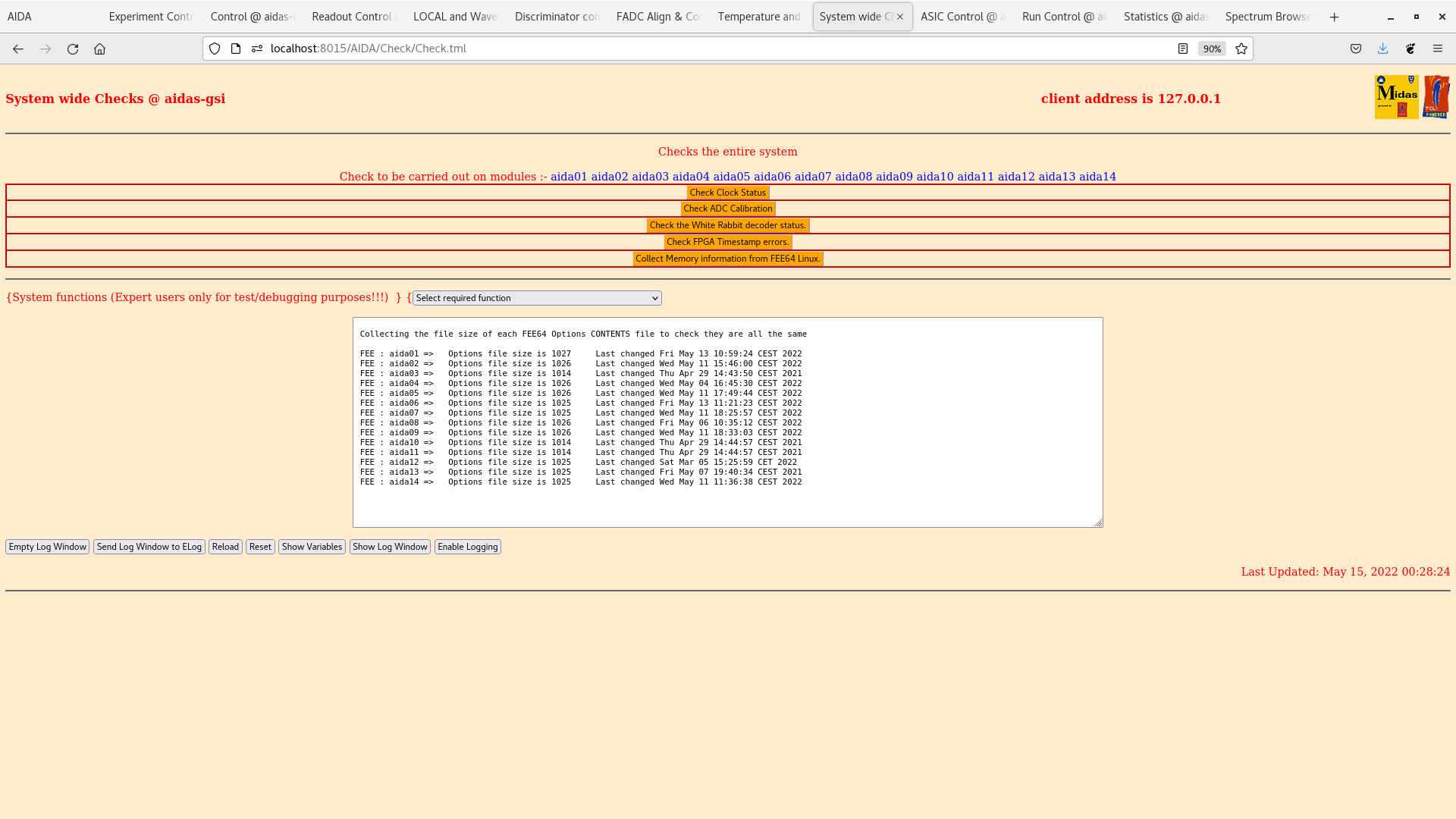

Collecting the file size of each FEE64 Options CONTENTS file to check they are all the same

FEE : aida01 => Options file size is 1025 Last changed Sat Apr 17 06:14:30 CEST 2021

FEE : aida02 => Options file size is 1014 Last changed Fri Apr 16 00:56:20 CEST 2021

FEE : aida03 => Options file size is 1014 Last changed Wed Apr 14 21:52:04 CEST 2021

FEE : aida04 => Options file size is 1025 Last changed Sat Apr 17 06:07:36 CEST 2021

FEE : aida05 => Options file size is 1025 Last changed Fri Apr 16 00:53:25 CEST 2021

FEE : aida06 => Options file size is 1014 Last changed Wed Apr 14 21:52:04 CEST 2021

FEE : aida07 => Options file size is 1014 Last changed Wed Apr 14 21:52:04 CEST 2021

FEE : aida08 => Options file size is 1014 Last changed Wed Apr 14 21:52:04 CEST 2021

FEE : aida09 => Options file size is 1014 Last changed Wed Apr 14 21:52:05 CEST 2021

FEE : aida10 => Options file size is 1014 Last changed Wed Apr 14 21:52:06 CEST 2021

FEE : aida11 => Options file size is 1014 Last changed Wed Apr 14 21:52:05 CEST 2021

FEE : aida12 => Options file size is 1025 Last changed Wed Apr 14 21:58:54 CEST 2021

*no faults detected by ~/oh/OptionsCheck.py

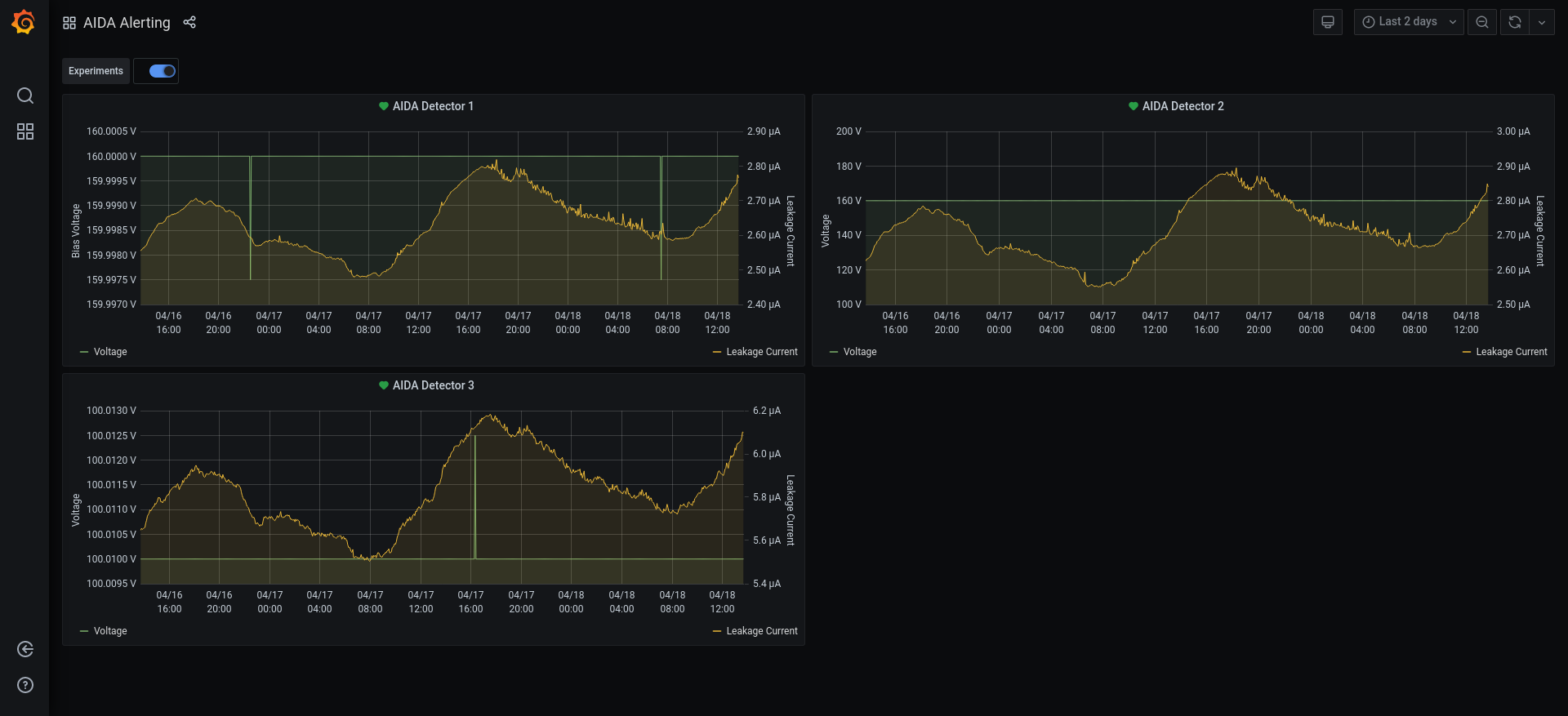

13.10 Detector biases & leakage currents OK - see attachment 2

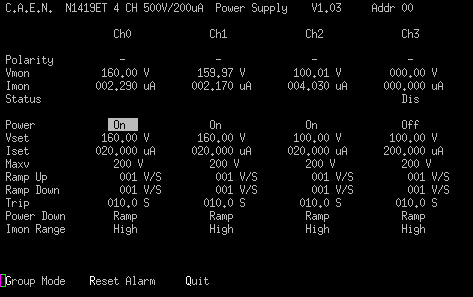

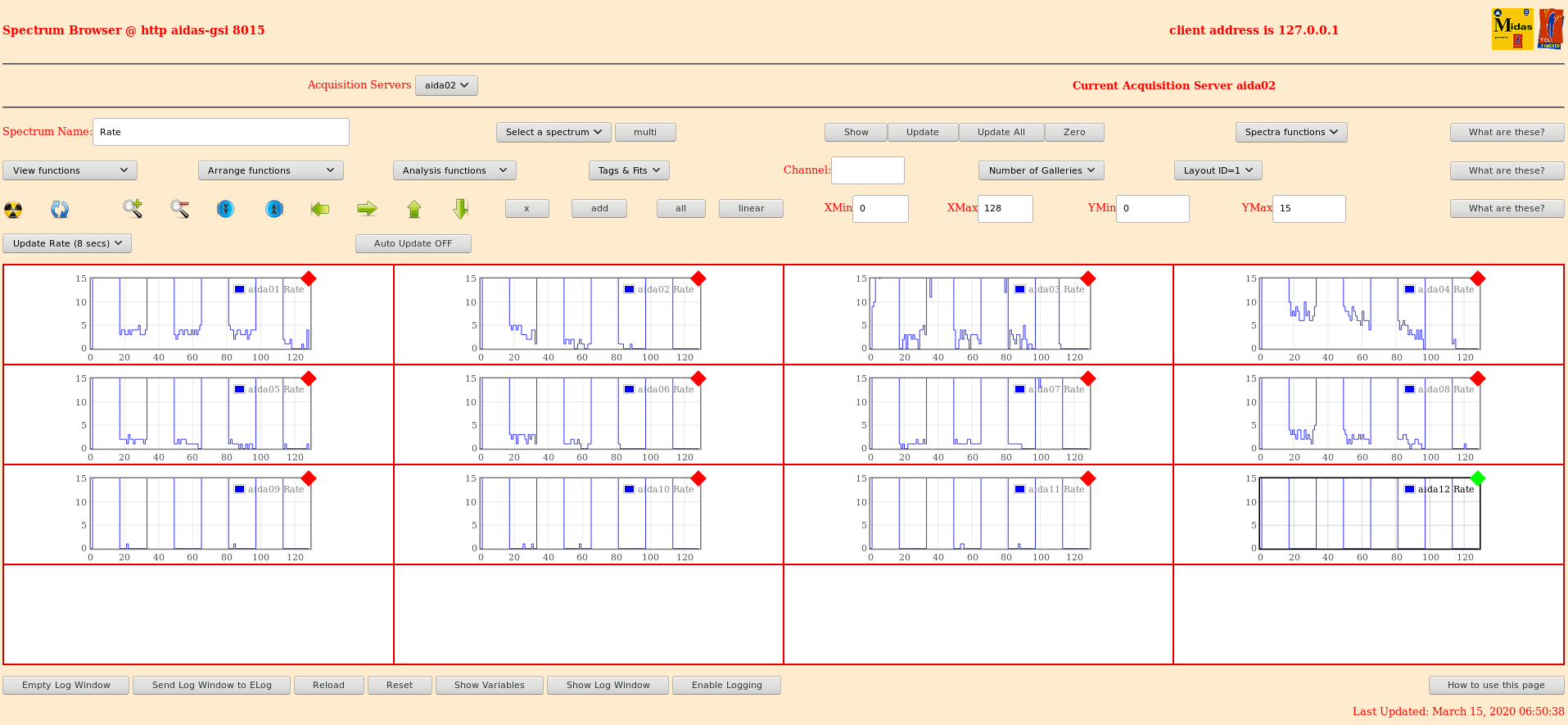

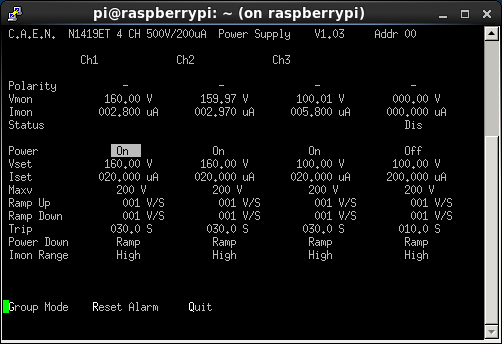

Statistics - good events, adc data, disc data, info code 4 & 5, pause, resume, correlation info - attachments 3-12

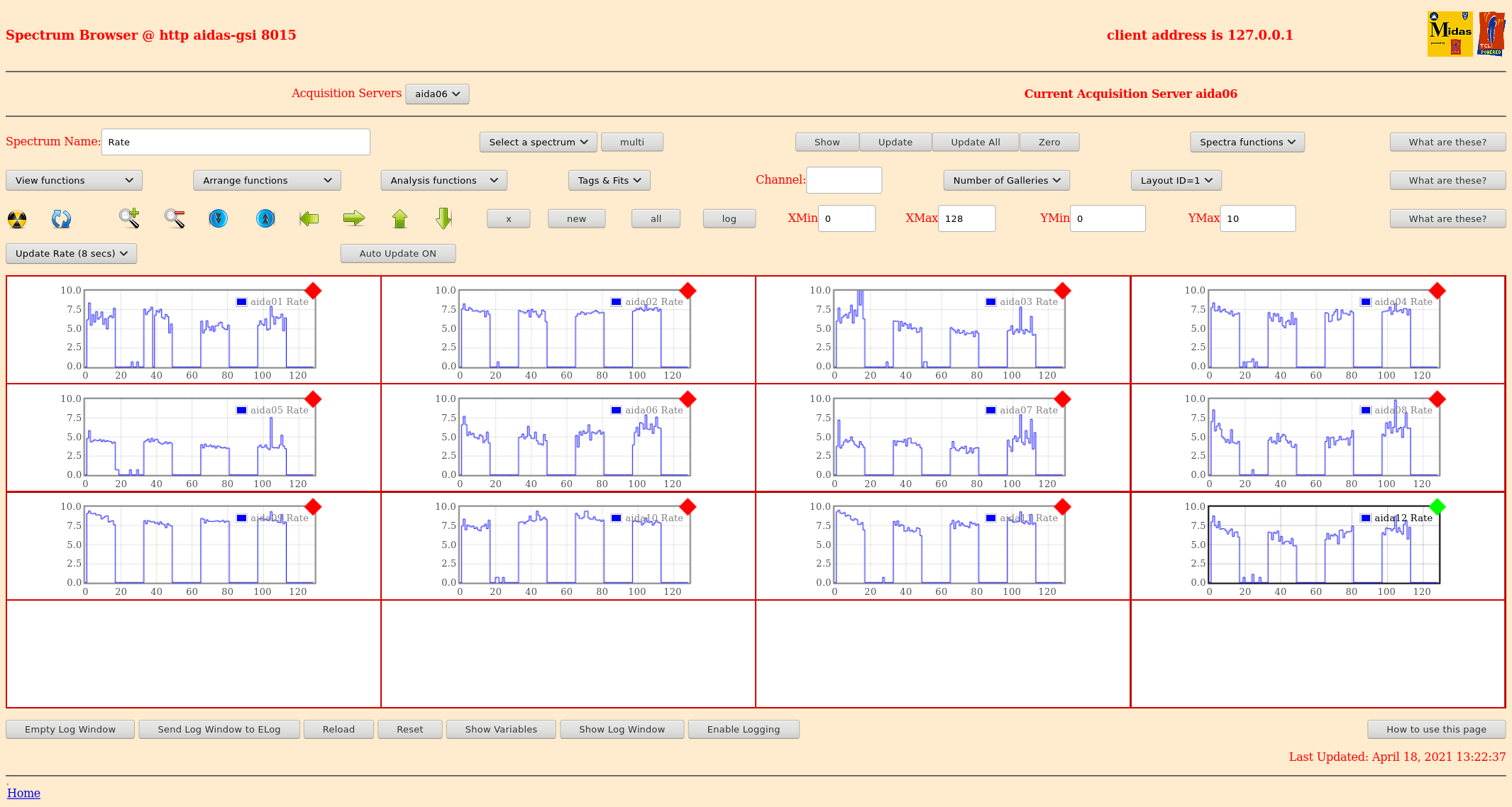

per FEE64 rate spectra - attachments 13-14

1.8.L spectra - attachments 15-18

pulser peak widths

1 80

2 113

3 308

4 105

5 50

6 91

7 61

8 90

9 200

10 133

11 187

12 107

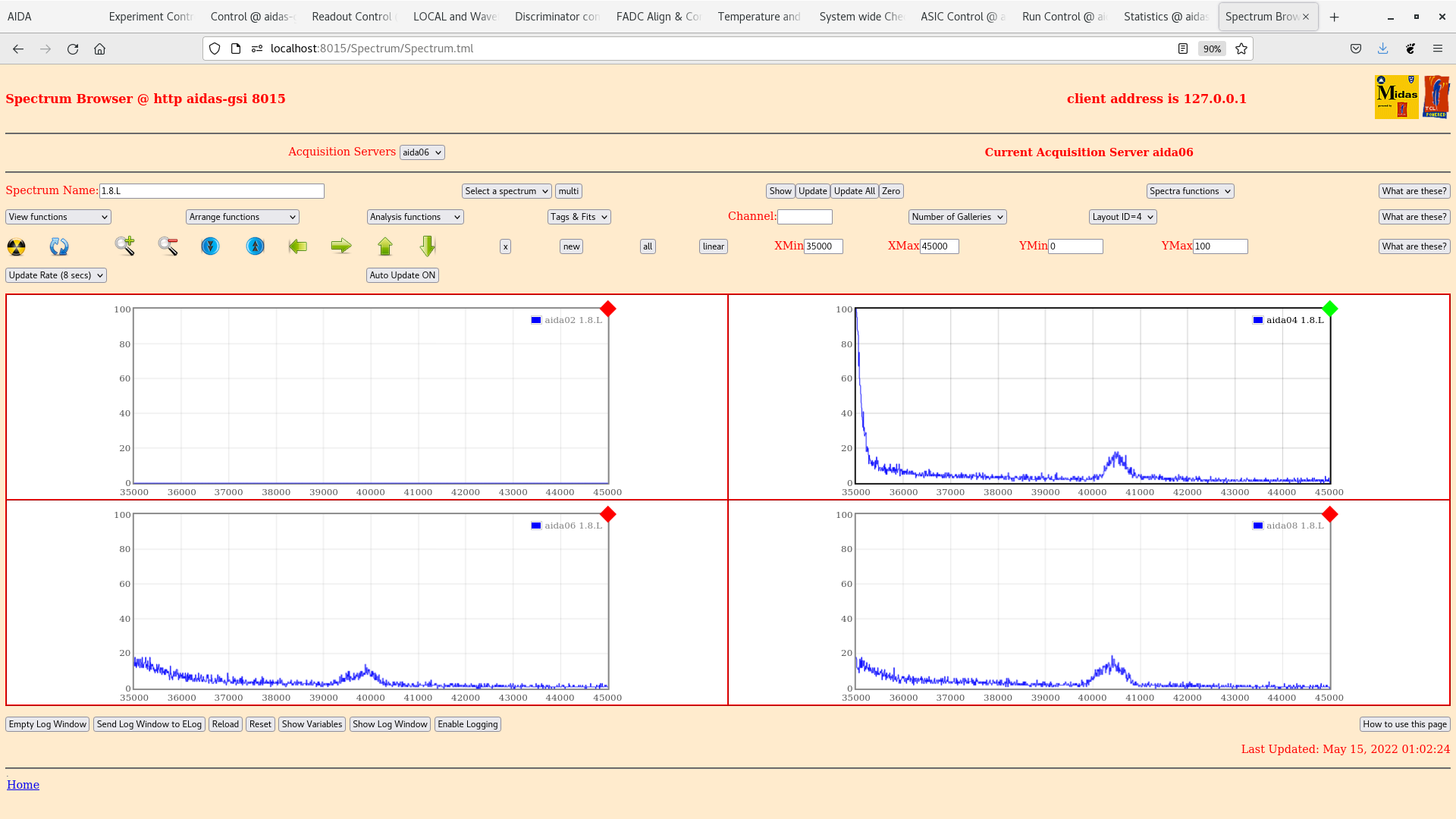

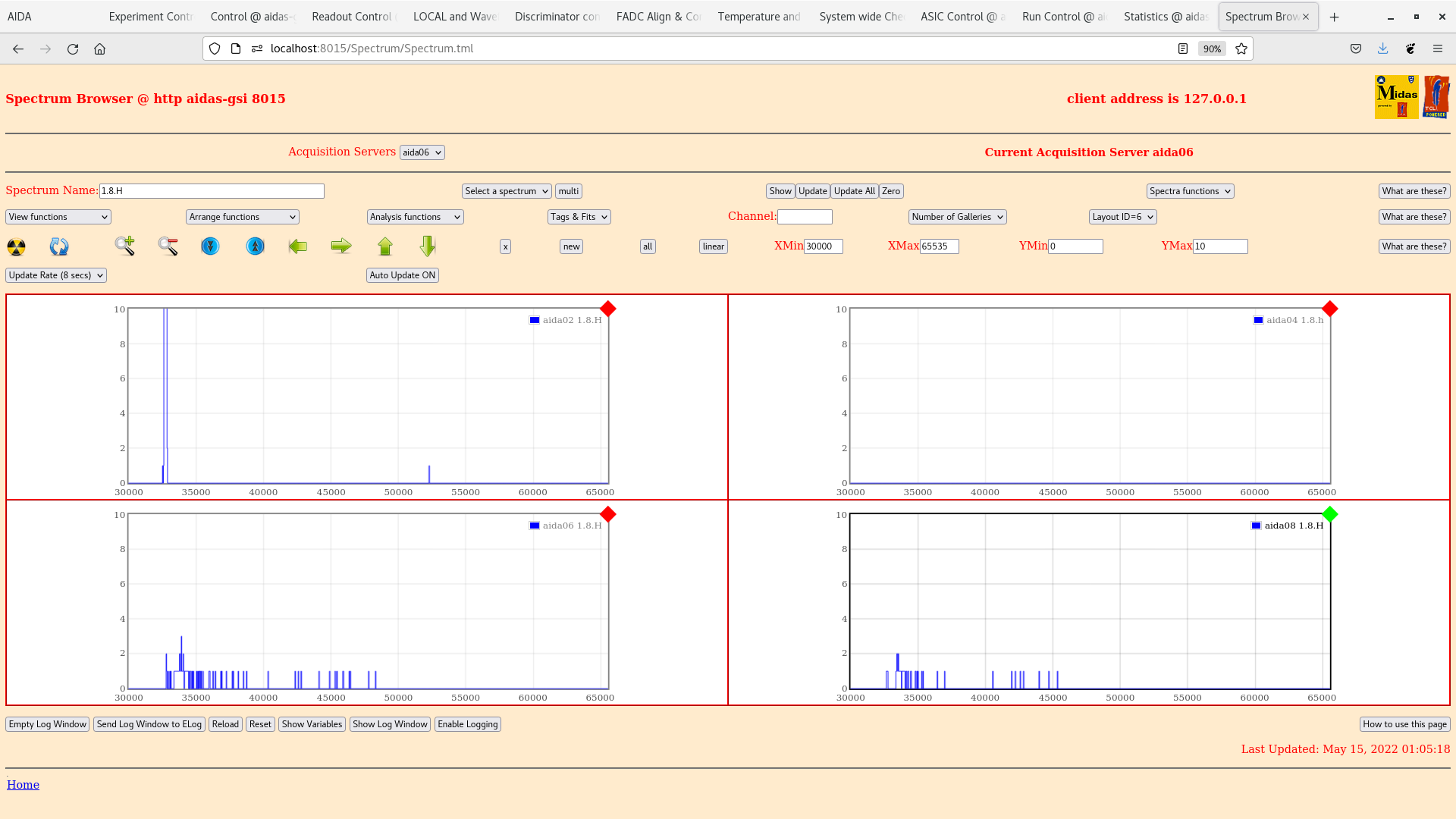

1.8.H spectra - attachments 19-20

1.8.W spectra - attachments 21-22

ucesb - attachment 23

implant rates DSSSD#1-3 to c. 1kHz

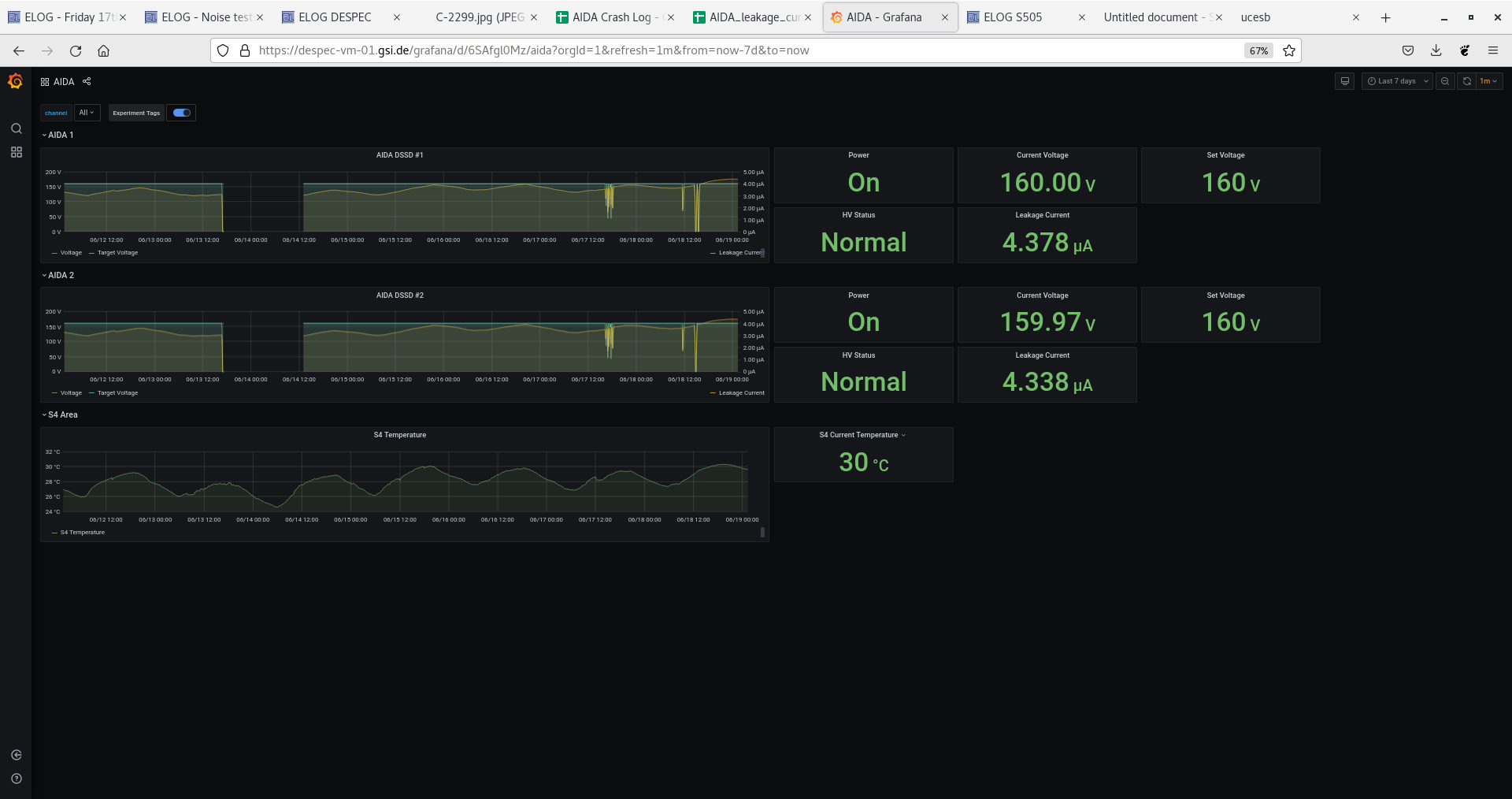

grafana - AIDA DSSSD leakage currents for previous 2 days - attachment 24

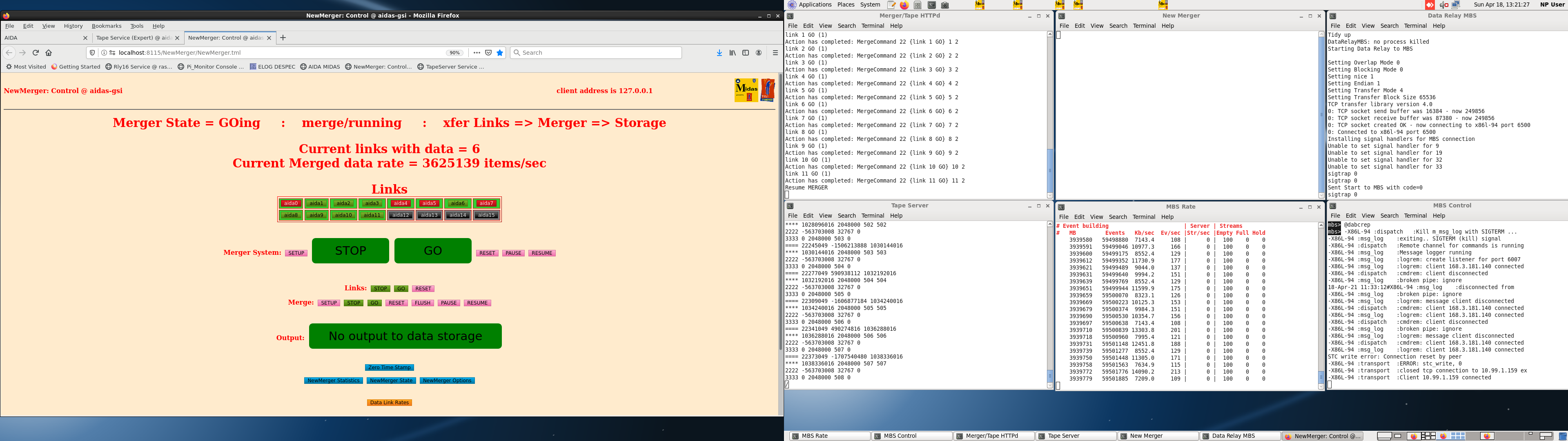

merger & merger/tape server/mbs data tranfser - attachment 25

no recent merger warning/error messages

13.30 225At setting |

| Attachment 1: R30_490

|

*** TDR format 3.3.0 analyser - TD - January 2019

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 256516272 ( 1223332.2 Hz)

Other data format: 5403728 ( 25770.5 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 32781 ( 156.3 Hz)

WR48-63: 32781 ( 156.3 Hz)

FEE64 disc: 828389 ( 3950.6 Hz)

MBS info: 4509777 ( 21507.2 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 263493 ( 1256.6 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 209.687 s

FEE elapsed dead time(s) elapsed idle time(s)

1 0.000 76.433

2 0.000 87.604

3 0.000 78.795

4 0.000 195.707

5 0.000 158.854

6 0.000 193.755

7 0.000 152.656

8 0.000 23.126

9 0.000 23.243

10 0.000 11.178

11 0.000 108.457

12 0.000 0.000

13 0.000 0.000

14 0.000 0.000

15 0.000 0.000

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 9851554 72944 0 0 0 0 1261 1261 69168 1254 0 26448

1 21158309 48956 0 0 0 0 2701 2701 43554 0 0 16374

2 17027137 1992411 0 0 0 0 2376 2376 156273 1831386 0 25239

3 18790255 1894647 0 0 0 0 2567 2567 58490 1831023 0 23746

4 2269151 296174 0 0 0 0 339 339 74660 220836 0 26646

5 8373135 260125 0 0 0 0 1152 1152 43783 214038 0 16230

6 4256540 286725 0 0 0 0 532 532 81589 204072 0 25586

7 9526319 267328 0 0 0 0 1246 1246 57668 207168 0 22643

8 54059298 76554 0 0 0 0 6619 6619 63316 0 0 22746

9 49446691 53505 0 0 0 0 6256 6256 40993 0 0 14045

10 45199495 92635 0 0 0 0 5711 5711 81213 0 0 23246

11 16558388 61724 0 0 0 0 2021 2021 57682 0 0 20544

12 0 0 0 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time:44645.059s ( 0.717 blocks/s, 0.045 Mb/s)

|

| Attachment 2: 50.png

|

|

| Attachment 3: Screenshot_2021-04-18_Statistics_aidas-gsi(1).png

|

.png.png)

|

| Attachment 4: Screenshot_2021-04-18_Temperature_and_status_scan_aidas-gsi(2).png

|

.png.png)

|

| Attachment 5: Screenshot_2021-04-18_Statistics_aidas-gsi(2).png

|

.png.png)

|

| Attachment 6: Screenshot_2021-04-18_Statistics_aidas-gsi(3).png

|

.png.png)

|

| Attachment 7: Screenshot_2021-04-18_Statistics_aidas-gsi(4).png

|

.png.png)

|

| Attachment 8: Screenshot_2021-04-18_Statistics_aidas-gsi(5).png

|

.png.png)

|

| Attachment 9: Screenshot_2021-04-18_Statistics_aidas-gsi(6).png

|

.png.png)

|

| Attachment 10: Screenshot_2021-04-18_Statistics_aidas-gsi(7).png

|

.png.png)

|

| Attachment 11: Screenshot_2021-04-18_Statistics_aidas-gsi(8).png

|

.png.png)

|

| Attachment 12: Screenshot_2021-04-18_Statistics_aidas-gsi(9).png

|

.png.png)

|

| Attachment 13: Screenshot_2021-04-18_Spectrum_Browser_aidas-gsi.png

|

|

| Attachment 14: Screenshot_2021-04-18_Spectrum_Browser_aidas-gsi(1).png

|

.png.png)

|

| Attachment 15: Screenshot_2021-04-18_Spectrum_Browser_aidas-gsi(2).png

|

.png.png)

|

| Attachment 16: Screenshot_2021-04-18_Spectrum_Browser_aidas-gsi(3).png

|

.png.png)

|

| Attachment 17: Screenshot_2021-04-18_Spectrum_Browser_aidas-gsi(4).png

|

.png.png)

|

| Attachment 18: Screenshot_2021-04-18_Spectrum_Browser_aidas-gsi(5).png

|

.png.png)

|

| Attachment 19: Screenshot_2021-04-18_Spectrum_Browser_aidas-gsi(6).png

|

.png.png)

|

| Attachment 20: Screenshot_2021-04-18_Spectrum_Browser_aidas-gsi(7).png

|

.png.png)

|

| Attachment 21: Screenshot_2021-04-18_Spectrum_Browser_aidas-gsi(8).png

|

.png.png)

|

| Attachment 22: Screenshot_2021-04-18_Spectrum_Browser_aidas-gsi(9).png

|

.png.png)

|

| Attachment 23: Screenshot_2021-04-18_ucesb.png

|

|

| Attachment 24: Screenshot_2021-04-18_AIDA_Alerting_-_Grafana.png

|

|

| Attachment 25: 51.png

|

|

|

665

|

Sun Jun 16 03:11:27 2024 |

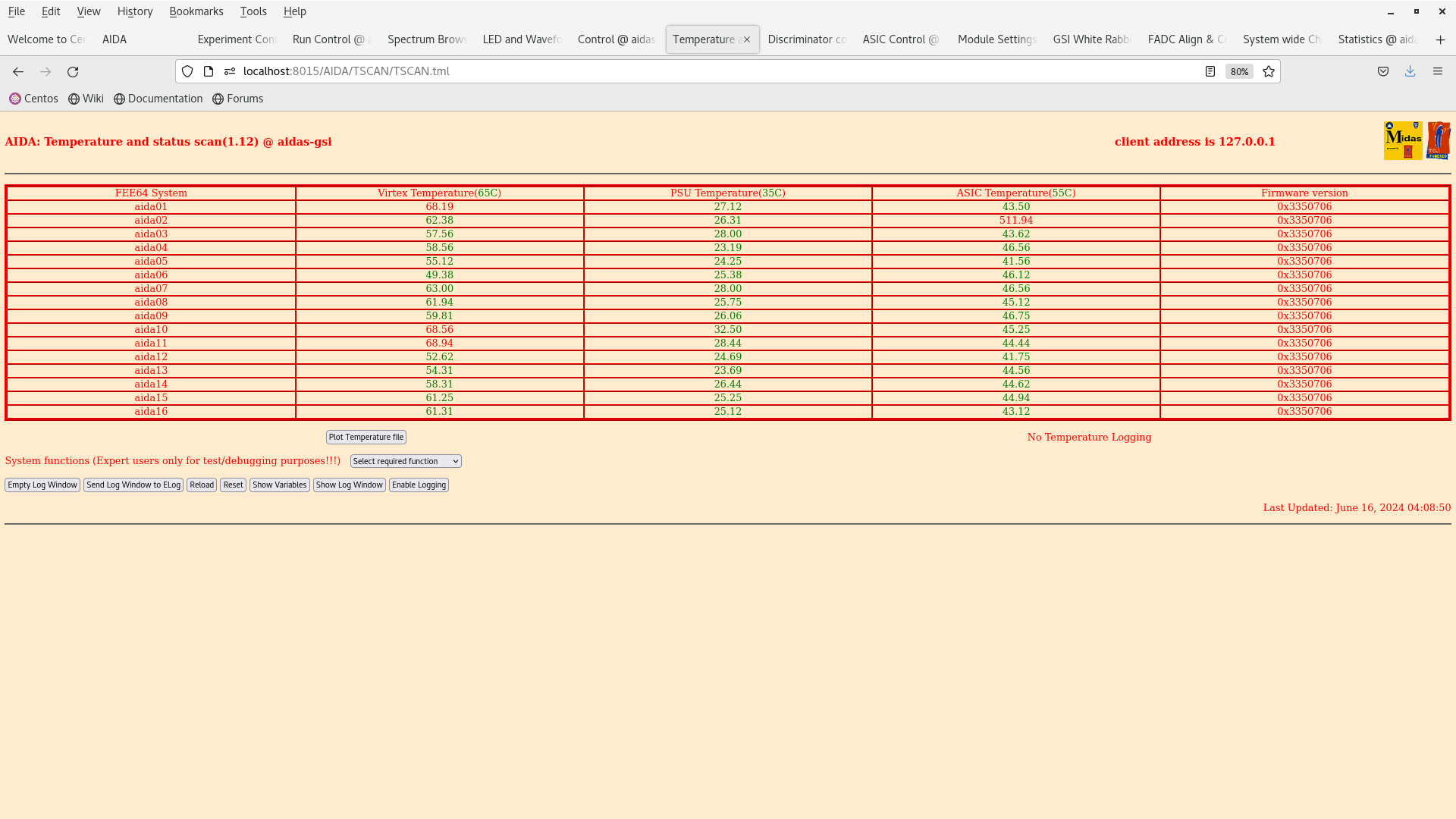

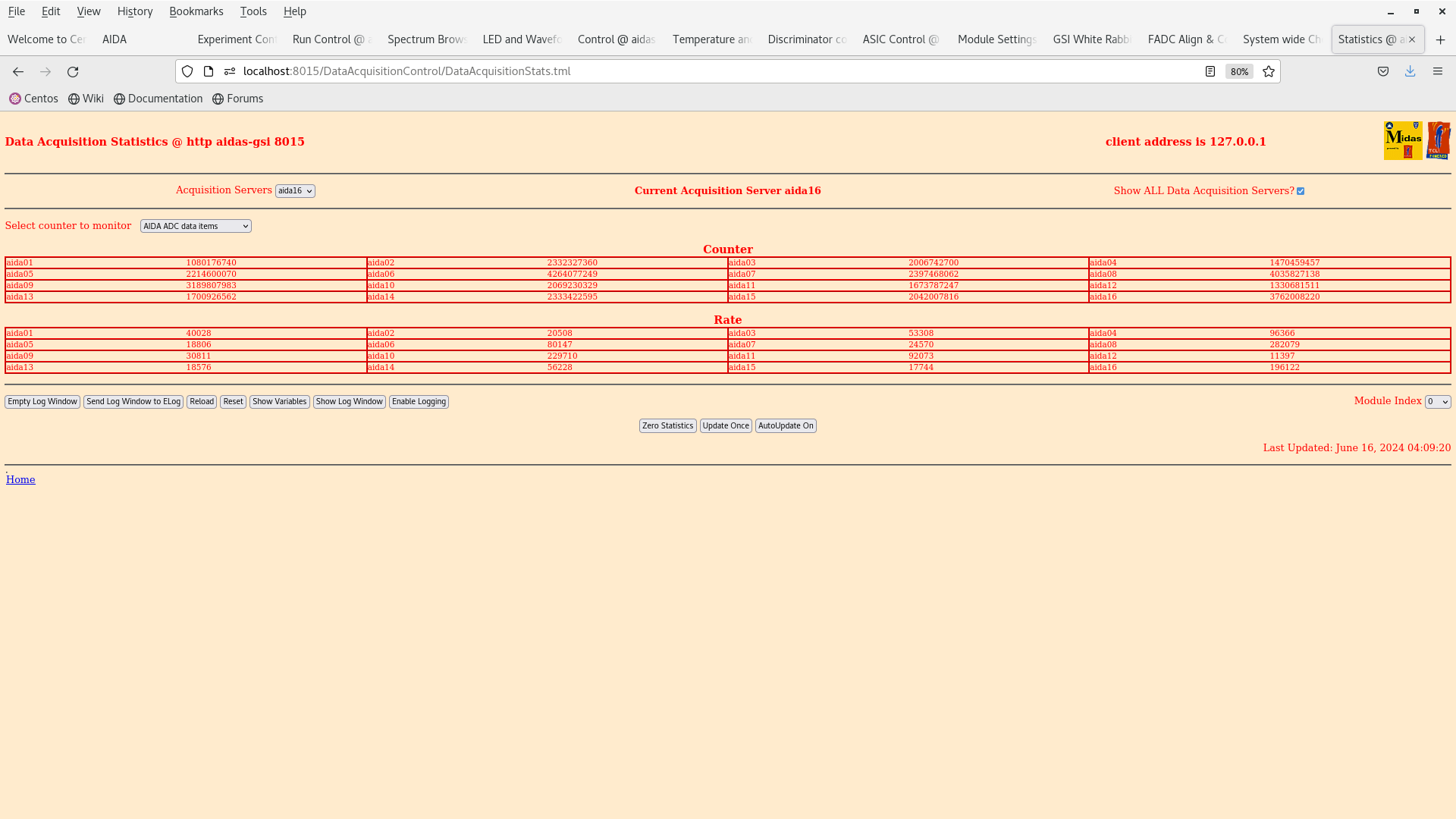

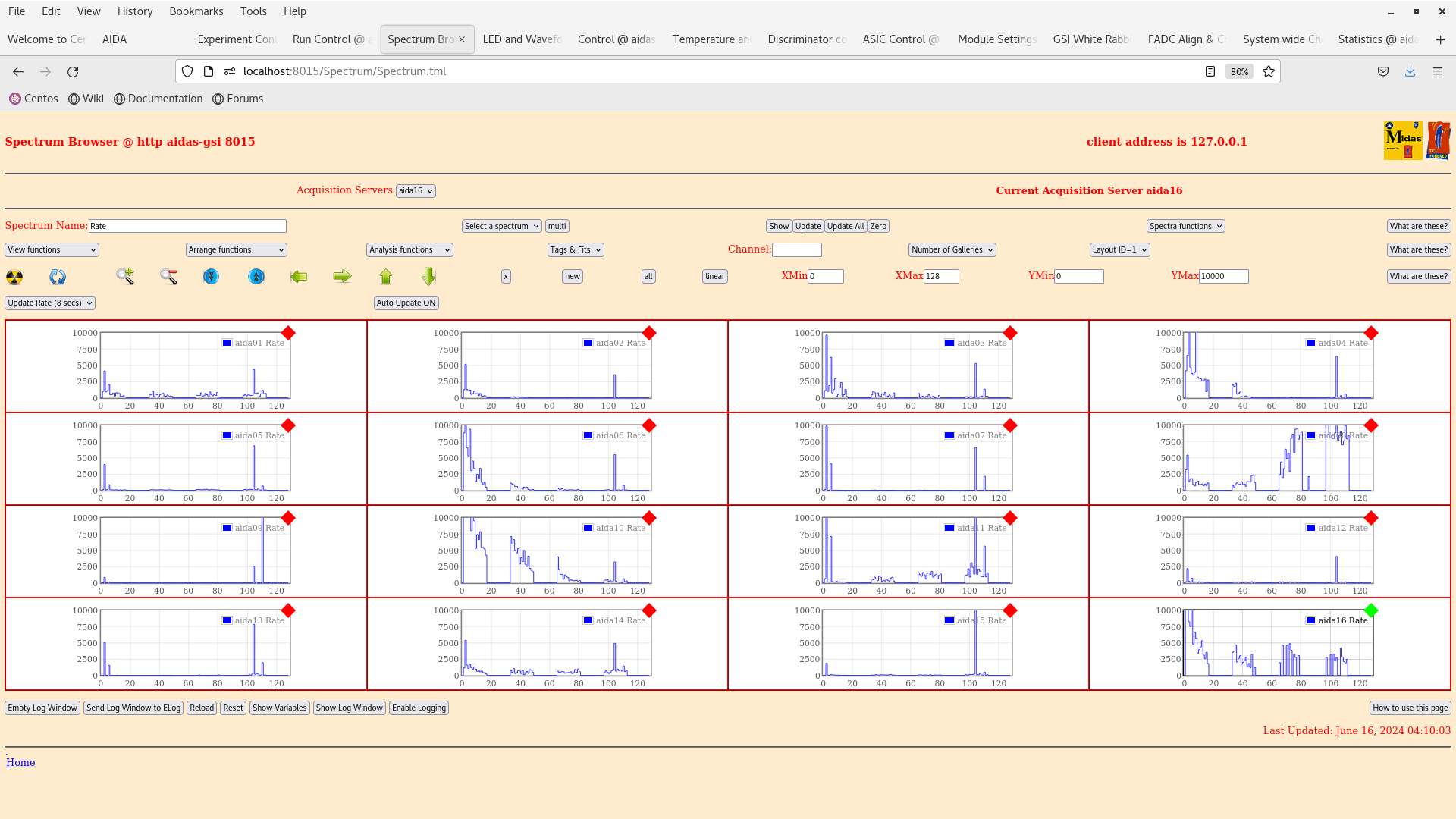

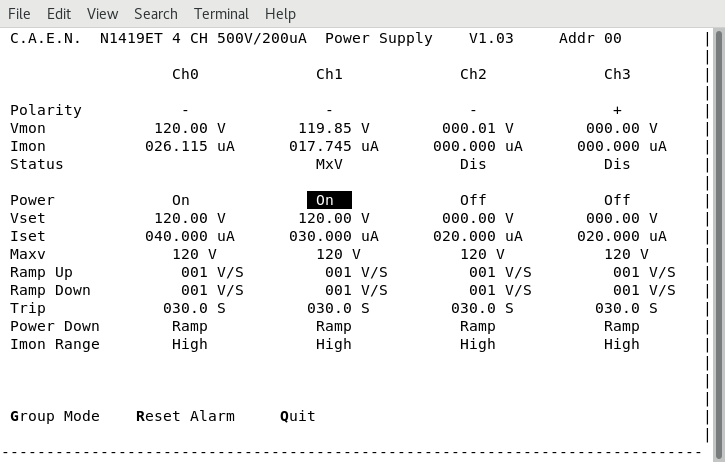

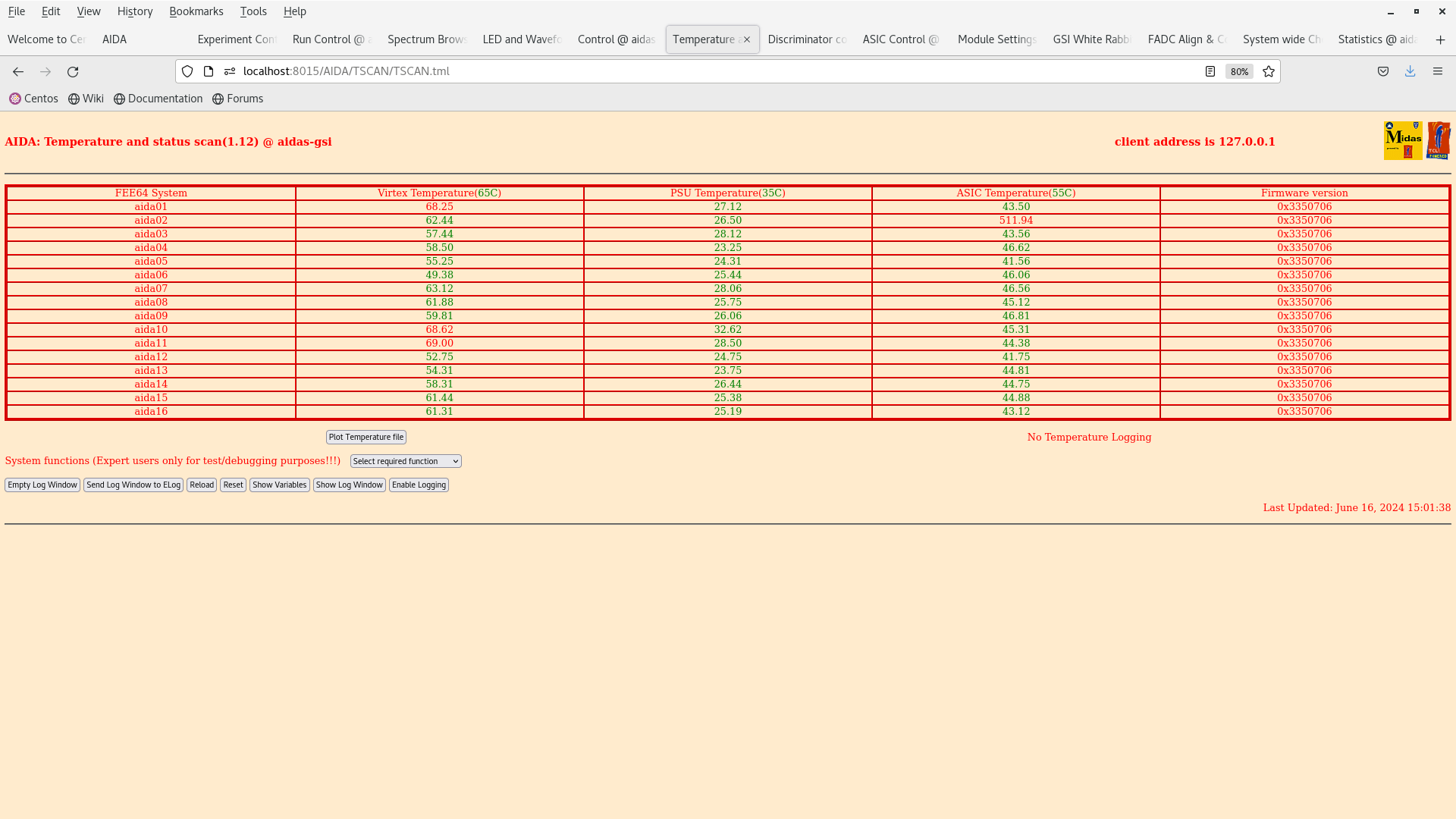

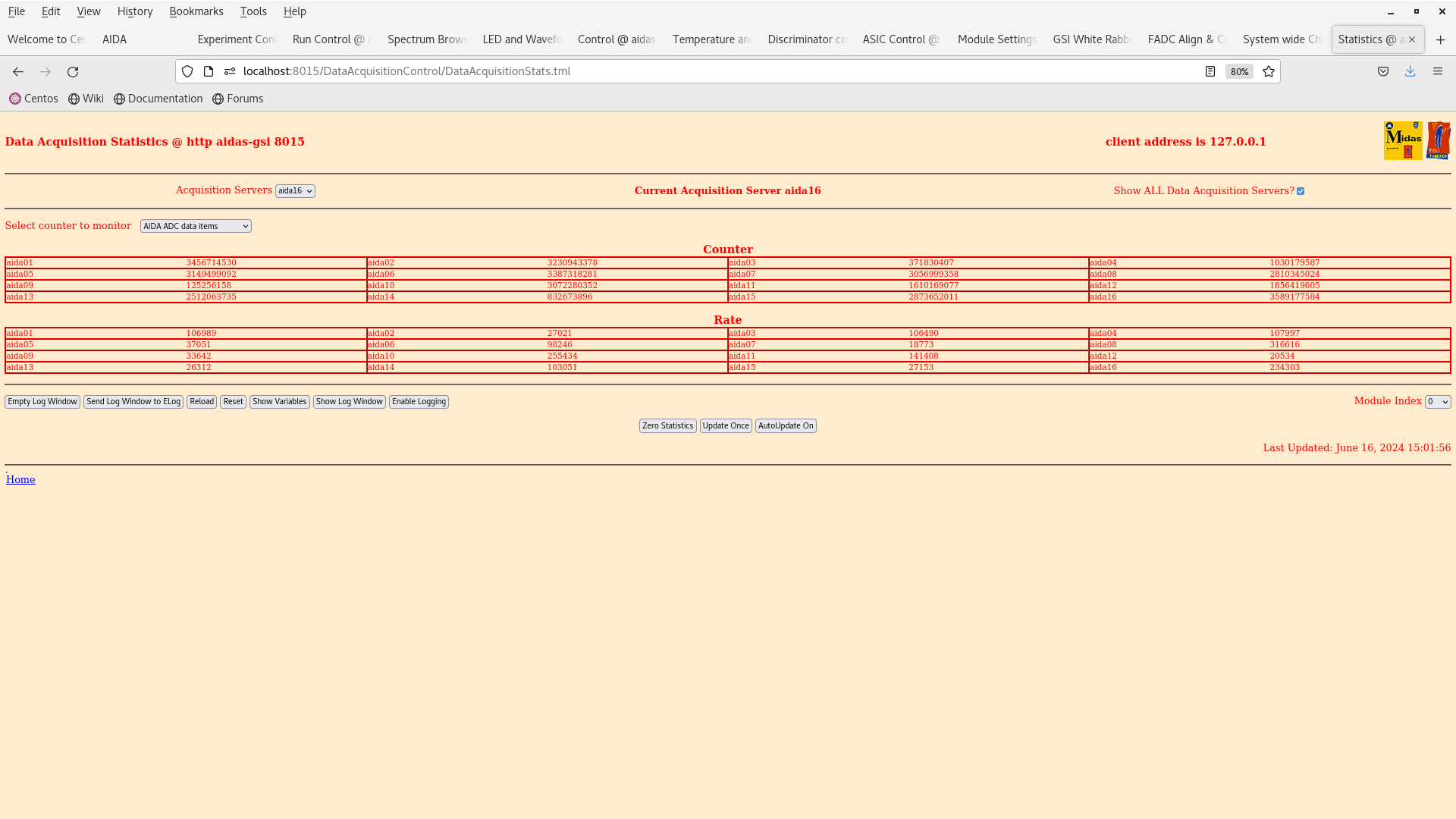

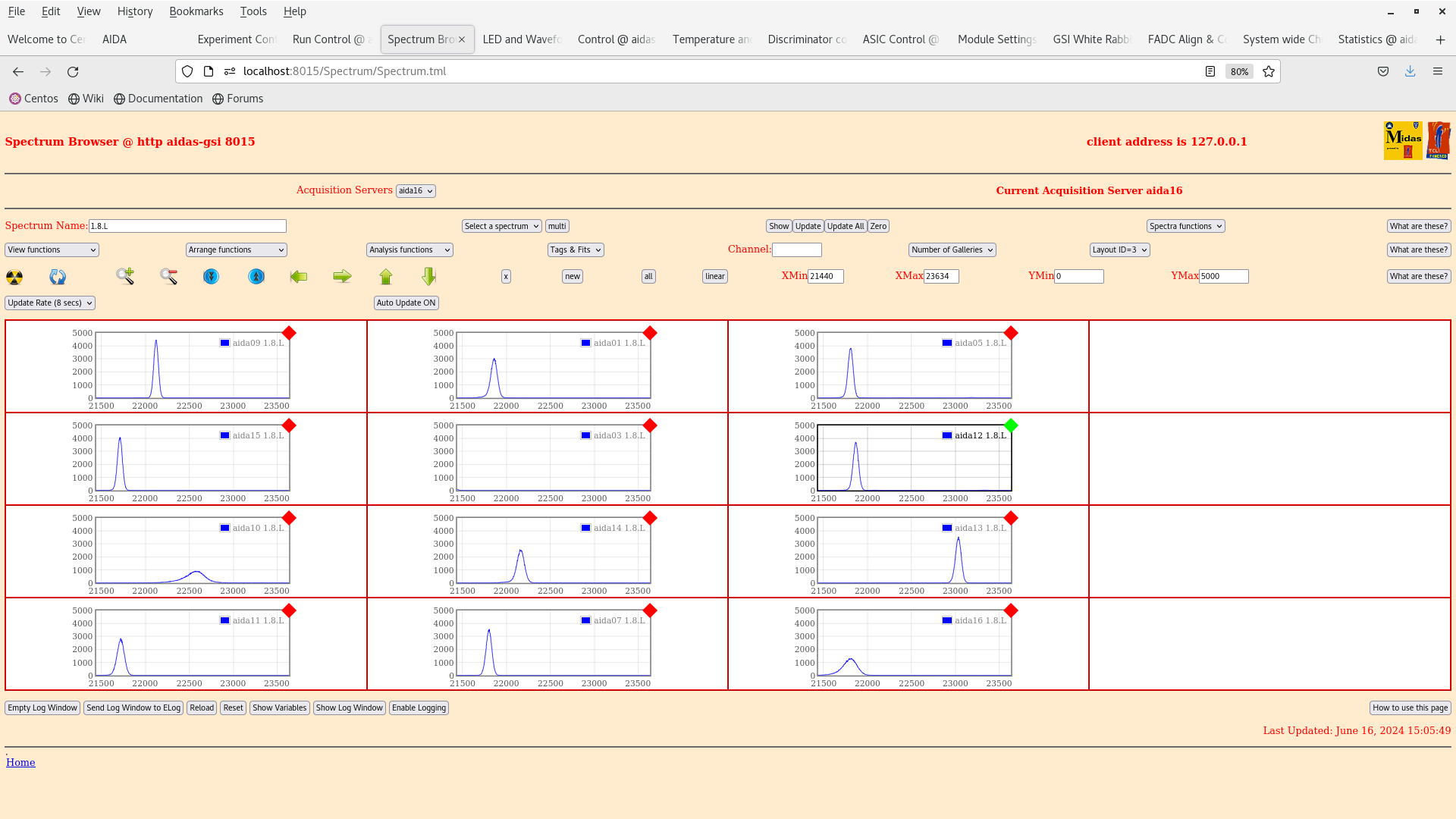

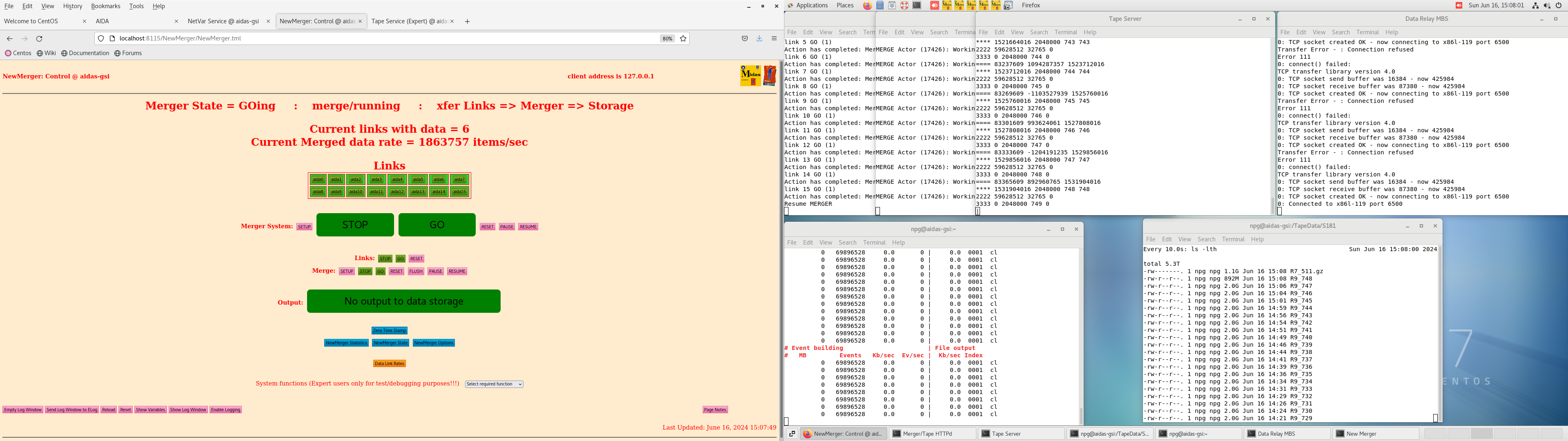

TD | Sunday 16 June |

04.08 DSSSD bias & leakage current OK - attachment 1

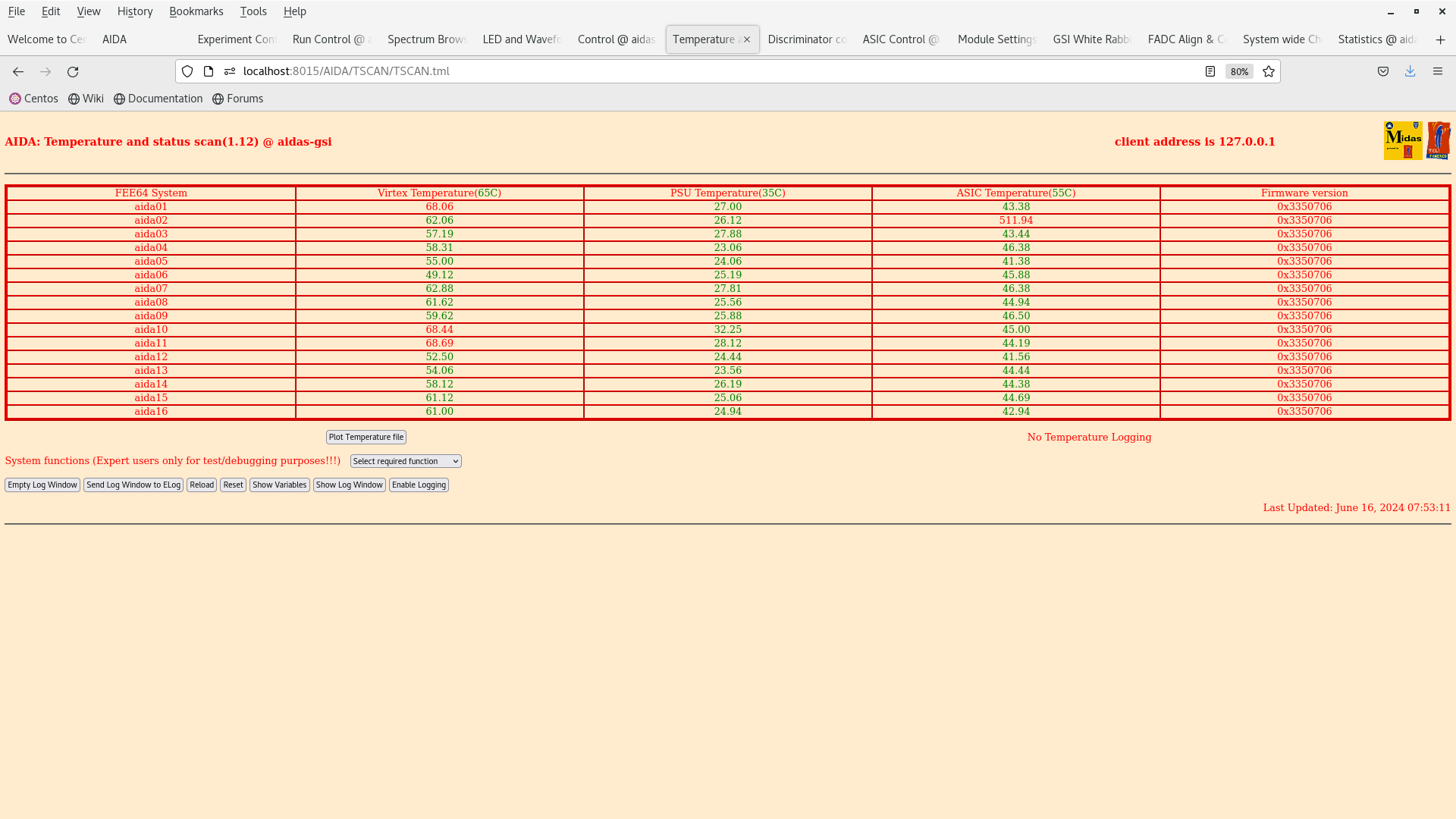

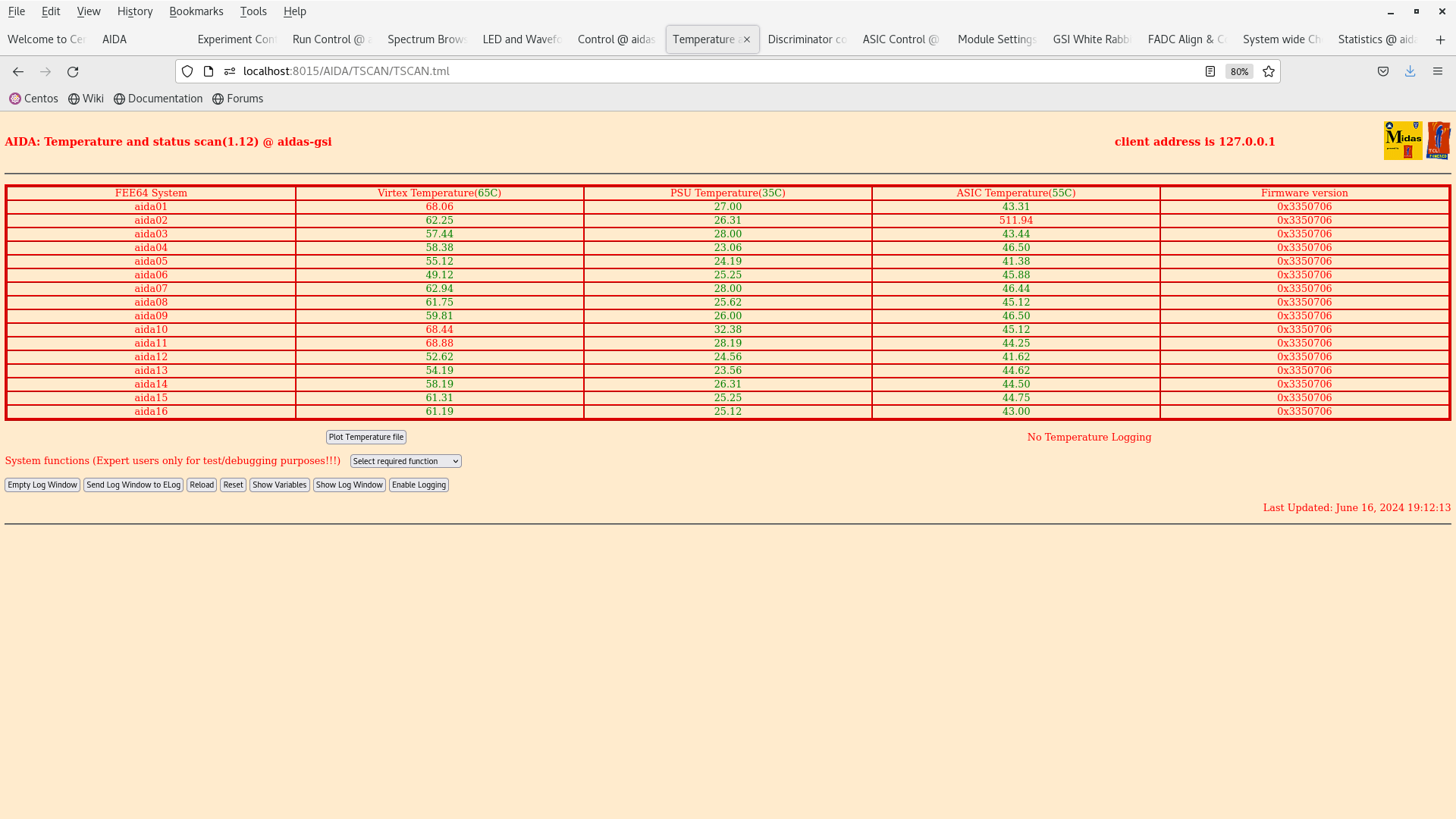

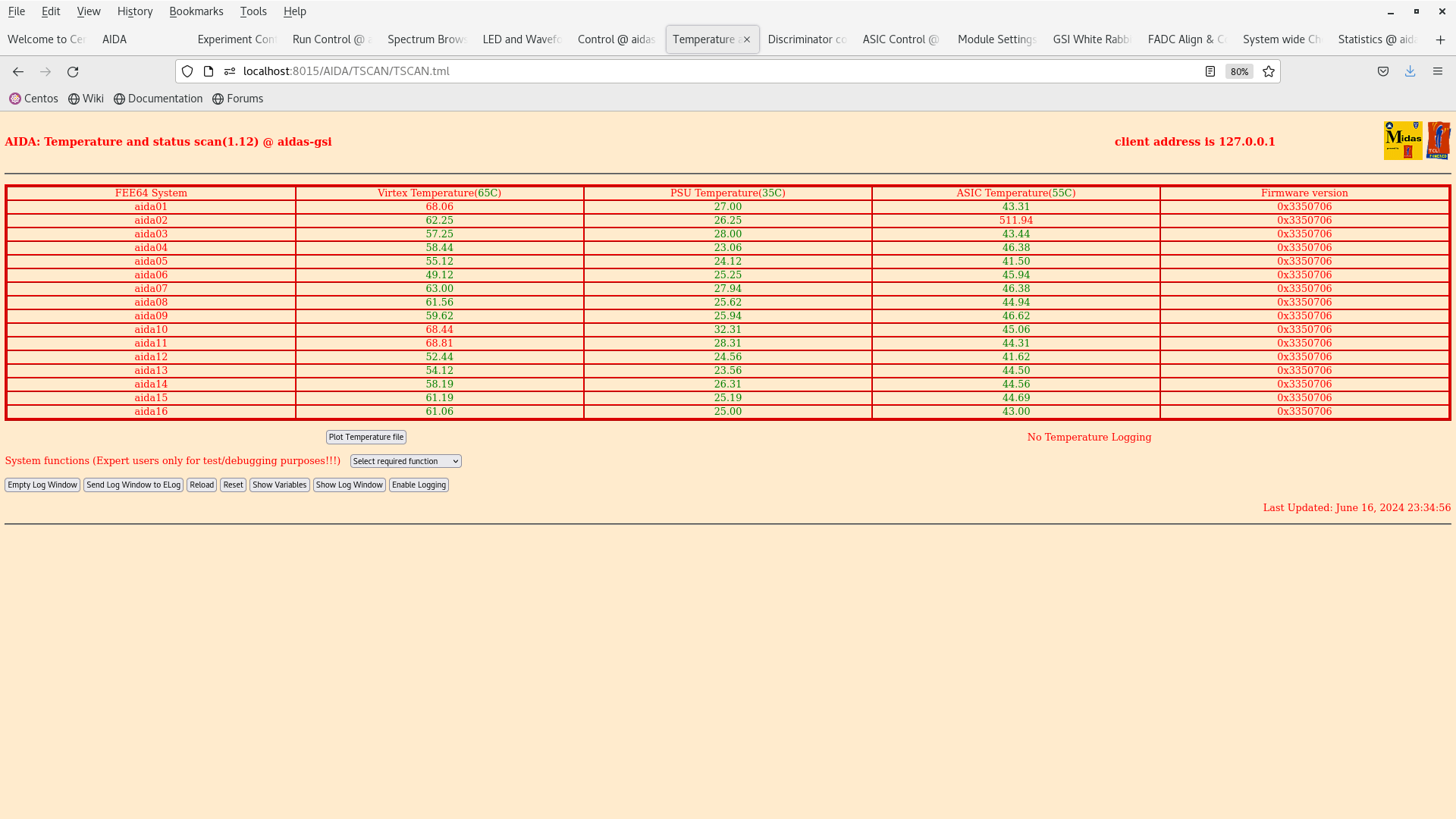

FEE64 temperatures OK - attachment 2

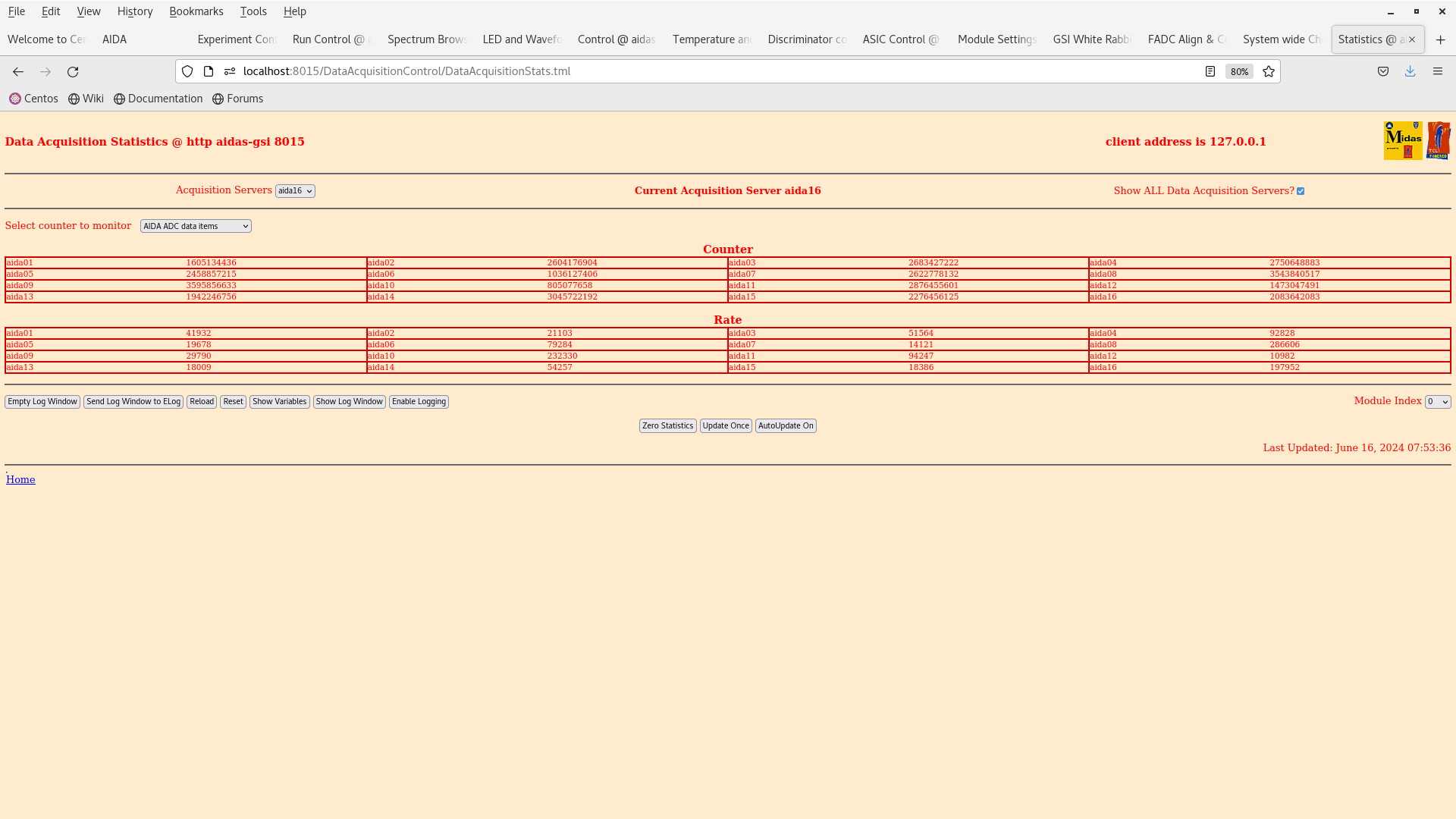

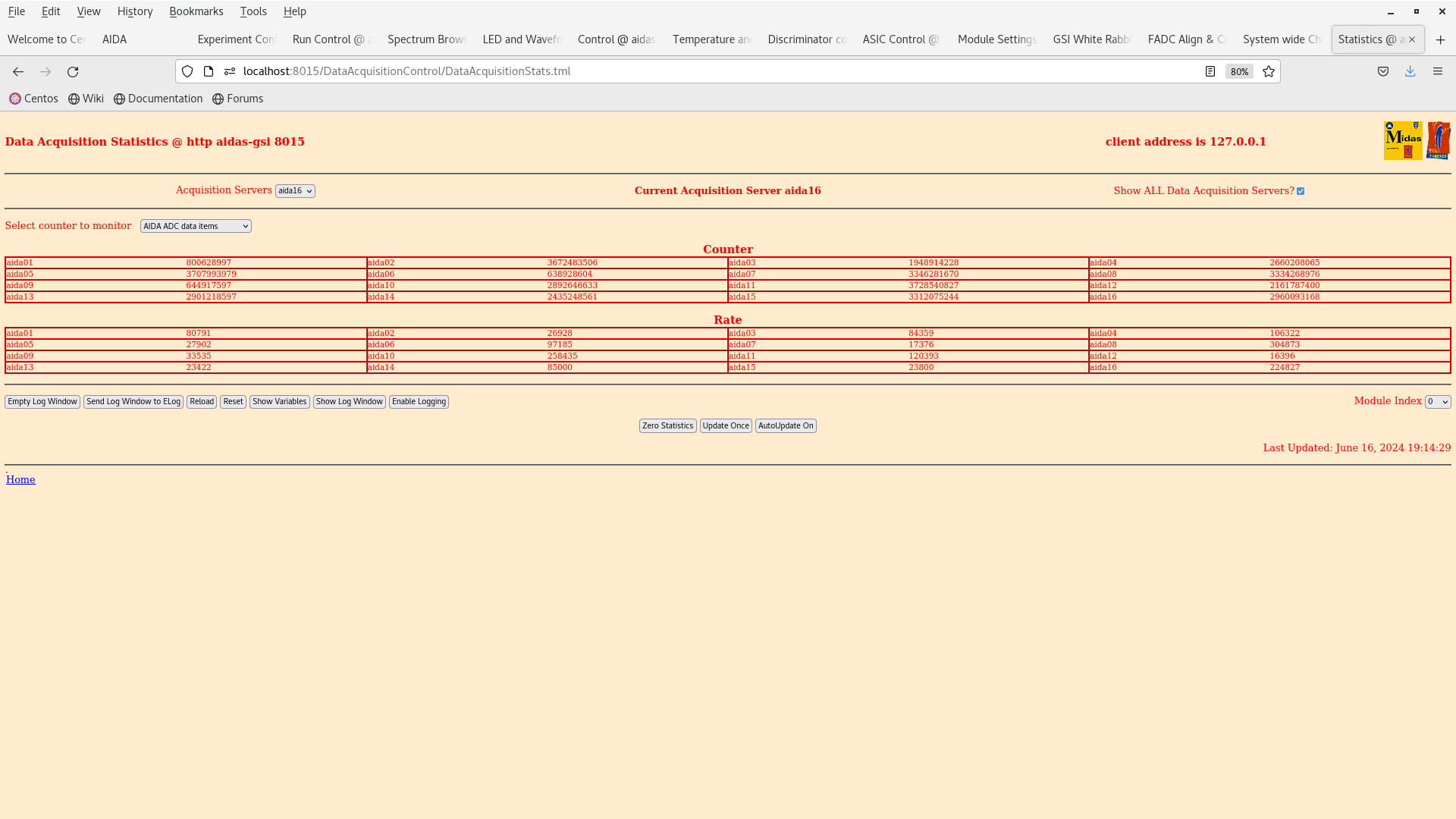

ADC data item stats OK - attachment 3

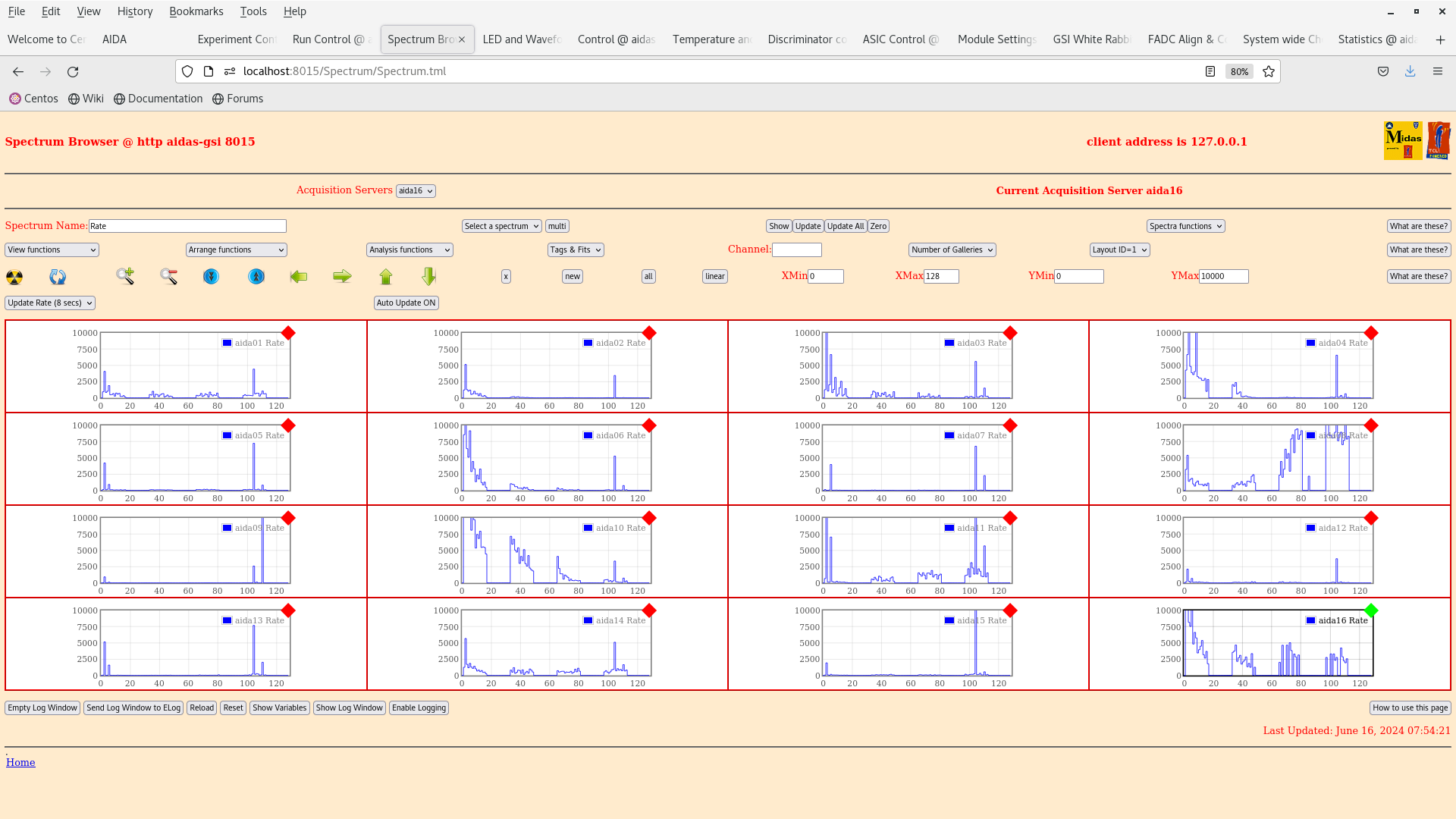

per FEE64 Rate spectra - attachment 4

07.52 DSSSD bias & leakage current OK - attachment 5

FEE64 temperatures OK - attachment 6

ADC data item stats OK - attachment 7

per FEE64 Rate spectra - attachment 8

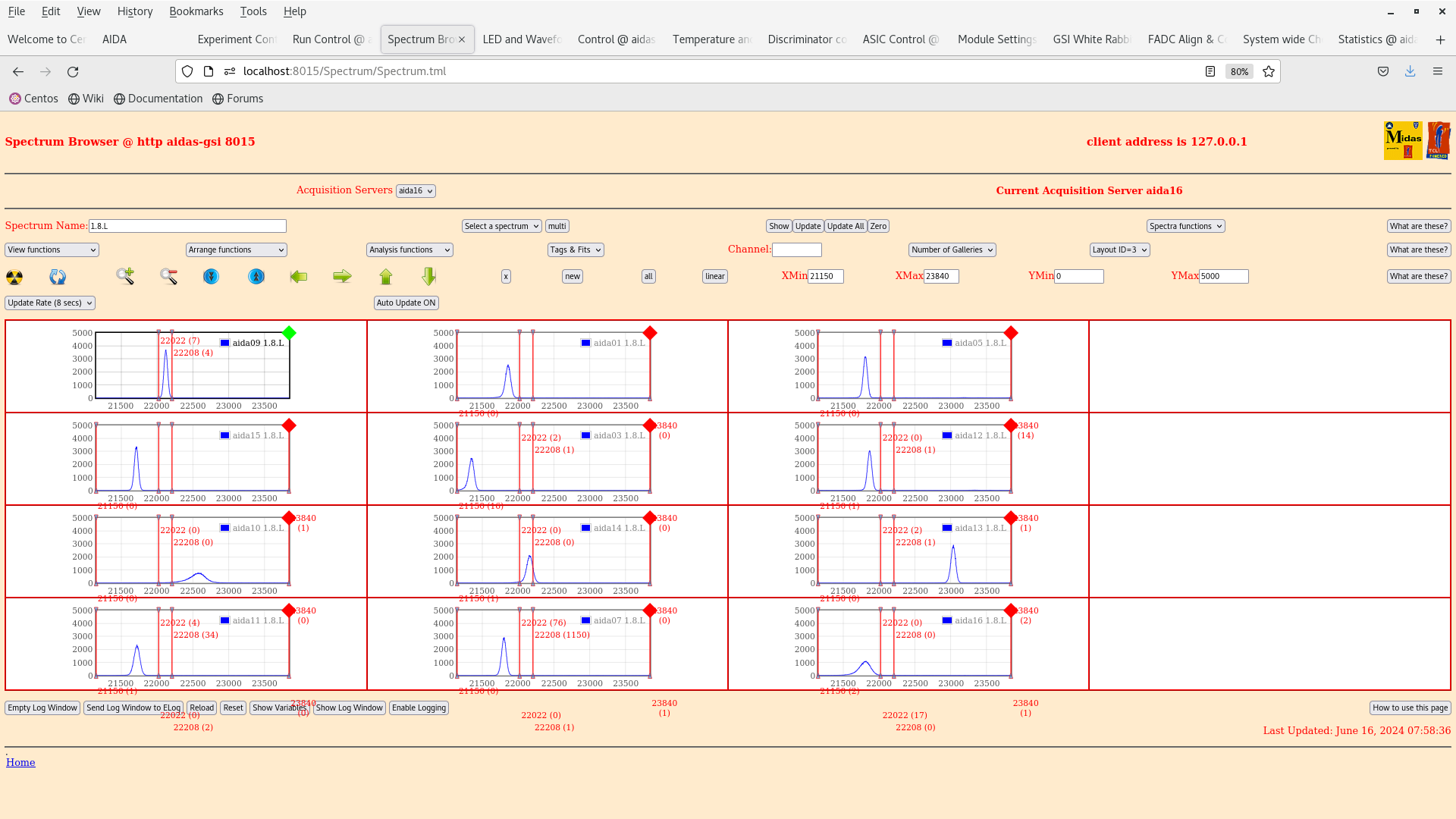

per p+n FEE64 1.8.L spectra - attachments 9-10

aida09 pulser peak width 59 ch FWHM

15.01 DSSSD bias & leakage current OK - attachment 11

FEE64 temperatures OK - attachment 12

ADC data item stats OK - attachment 13

per p+n FEE64 1.8.L spectra - attachments 14-15

aida09 pulser peak width 59 ch FWHM

aida05 pulser peak width 68 ch FWHM

aida12 pulser peak width 71 ch FWHM

per FEE64 Rate spectra - attachment 16

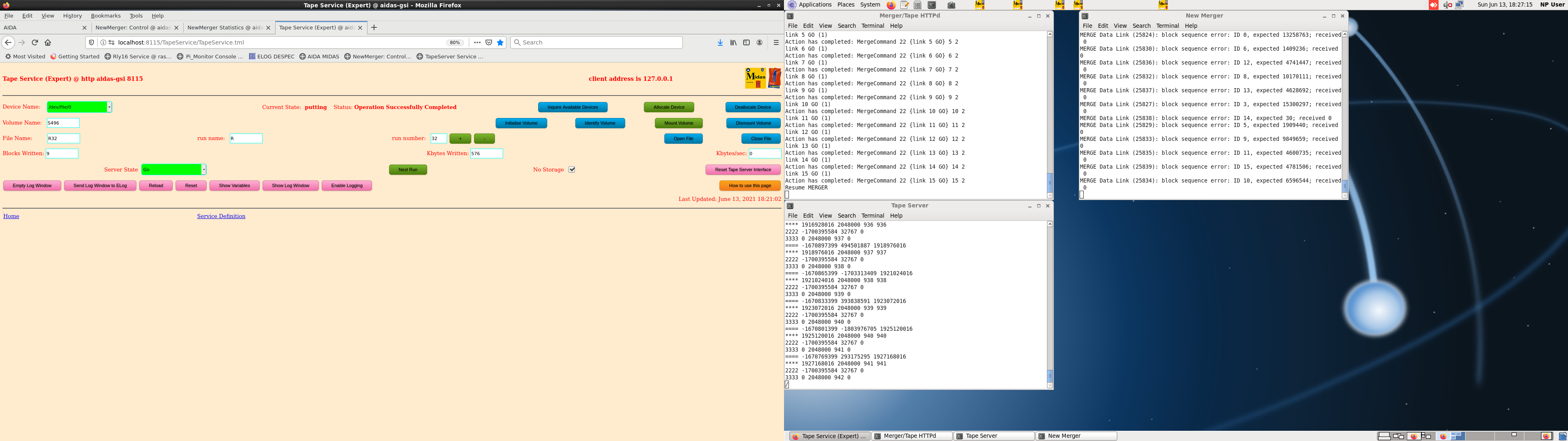

Merger, TapeSever etc - attachment 17

no data transfer to MBS - MBS down?

15.06 analysis data file R9_747 - attachment 18

max dead time 4.3% aida08, all other FEE64s < 2%

ADC data rate 1.667M, HEC data rate 2.3k

19.12 DSSSD bias & leakage current OK - attachment 19

FEE64 temperatures OK - attachment 20

ADC data item stats OK - attachment 21

per FEE64 Rate spectra - attachment 22

23.34 DSSSD bias & leakage current OK - attachment 23

FEE64 temperatures OK - attachment 24

ADC data item stats OK - attachment 25

per FEE64 Rate spectra - attachment 26 |

| Attachment 1: Screenshot_from_2024-06-16_04-10-35.png

|

|

| Attachment 2: Screenshot_from_2024-06-16_04-09-07.png

|

|

| Attachment 3: Screenshot_from_2024-06-16_04-09-41.png

|

|

| Attachment 4: Screenshot_from_2024-06-16_04-10-21.png

|

|

| Attachment 5: Screenshot_from_2024-06-16_07-52-49.png

|

|

| Attachment 6: Screenshot_from_2024-06-16_07-53-20.png

|

|

| Attachment 7: Screenshot_from_2024-06-16_07-53-47.png

|

|

| Attachment 8: Screenshot_from_2024-06-16_07-54-42.png

|

|

| Attachment 9: Screenshot_from_2024-06-16_07-59-28.png

|

|

| Attachment 10: Screenshot_from_2024-06-16_08-01-35.png

|

|

| Attachment 11: Screenshot_from_2024-06-16_15-01-23.png

|

|

| Attachment 12: Screenshot_from_2024-06-16_15-01-46.png

|

|

| Attachment 13: Screenshot_from_2024-06-16_15-02-12.png

|

|

| Attachment 14: Screenshot_from_2024-06-16_15-03-05.png

|

|

| Attachment 15: Screenshot_from_2024-06-16_15-06-14.png

|

|

| Attachment 16: Screenshot_from_2024-06-16_15-07-06.png

|

|

| Attachment 17: Screenshot_from_2024-06-16_15-08-02.png

|

|

| Attachment 18: R9_747

|

*** TDR format 3.3.0 analyser - TD - May 2021

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 261839349 ( 1667447.6 Hz)

Other data format: 80651 ( 513.6 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 683 ( 4.3 Hz)

RESUME: 683 ( 4.3 Hz)

SYNC100: 32585 ( 207.5 Hz)

WR48-63: 32585 ( 207.5 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 14115 ( 89.9 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 357749 ( 2278.2 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 157.030 s

FEE elapsed dead time(s) elapsed idle time(s)

0 0.474 0.000

1 0.000 0.000

2 0.114 0.000

3 0.086 0.000

4 0.007 0.000

5 0.165 0.000

6 0.000 0.000

7 6.815 0.000

8 0.000 0.000

9 3.068 0.000

10 0.526 0.000

11 0.000 0.000

12 0.000 0.000

13 0.247 0.000

14 0.002 0.000

15 1.373 0.000

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 17385482 9389 0 0 56 56 2291 2291 0 4695 0 0

1 4359471 1110 0 0 0 0 555 555 0 0 0 0

2 16890768 4312 0 0 14 14 2142 2142 0 0 0 0

3 16799432 4226 0 0 17 17 2096 2096 0 0 0 0

4 5895210 1414 0 0 2 2 705 705 0 0 0 0

5 15605735 4074 0 0 27 27 2010 2010 0 0 0 0

6 2976504 10096 0 0 0 0 338 338 0 9420 0 0

7 48753528 12540 0 0 223 223 6047 6047 0 0 0 357748

8 5419325 1414 0 0 0 0 707 707 0 0 0 0

9 41464320 10520 0 0 151 151 5109 5109 0 0 0 0

10 21531781 5458 0 0 66 66 2663 2663 0 0 0 1

11 3242993 744 0 0 0 0 372 372 0 0 0 0

12 3988909 970 0 0 0 0 485 485 0 0 0 0

13 16192913 4074 0 0 38 38 1999 1999 0 0 0 0

14 4620379 1122 0 0 1 1 560 560 0 0 0 0

15 36712599 9188 0 0 88 88 4506 4506 0 0 0 0

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time: 63.340s ( 505.211 blocks/s, 31.576 Mb/s)

|

| Attachment 19: Screenshot_from_2024-06-16_19-11-54.png

|

|

| Attachment 20: Screenshot_from_2024-06-16_19-12-22.png

|

|

| Attachment 21: Screenshot_from_2024-06-16_19-14-40.png

|

|

| Attachment 22: Screenshot_from_2024-06-16_19-15-10.png

|

|

| Attachment 23: Screenshot_from_2024-06-16_23-34-39.png

|

|

| Attachment 24: Screenshot_from_2024-06-16_23-35-06.png

|

|

| Attachment 25: Screenshot_from_2024-06-16_23-35-37.png

|

|

| Attachment 26: Screenshot_from_2024-06-16_23-36-04.png

|

|

|

457

|

Sun May 15 15:51:49 2022 |

ML | Sunday 15th May 16:00-0:00 |

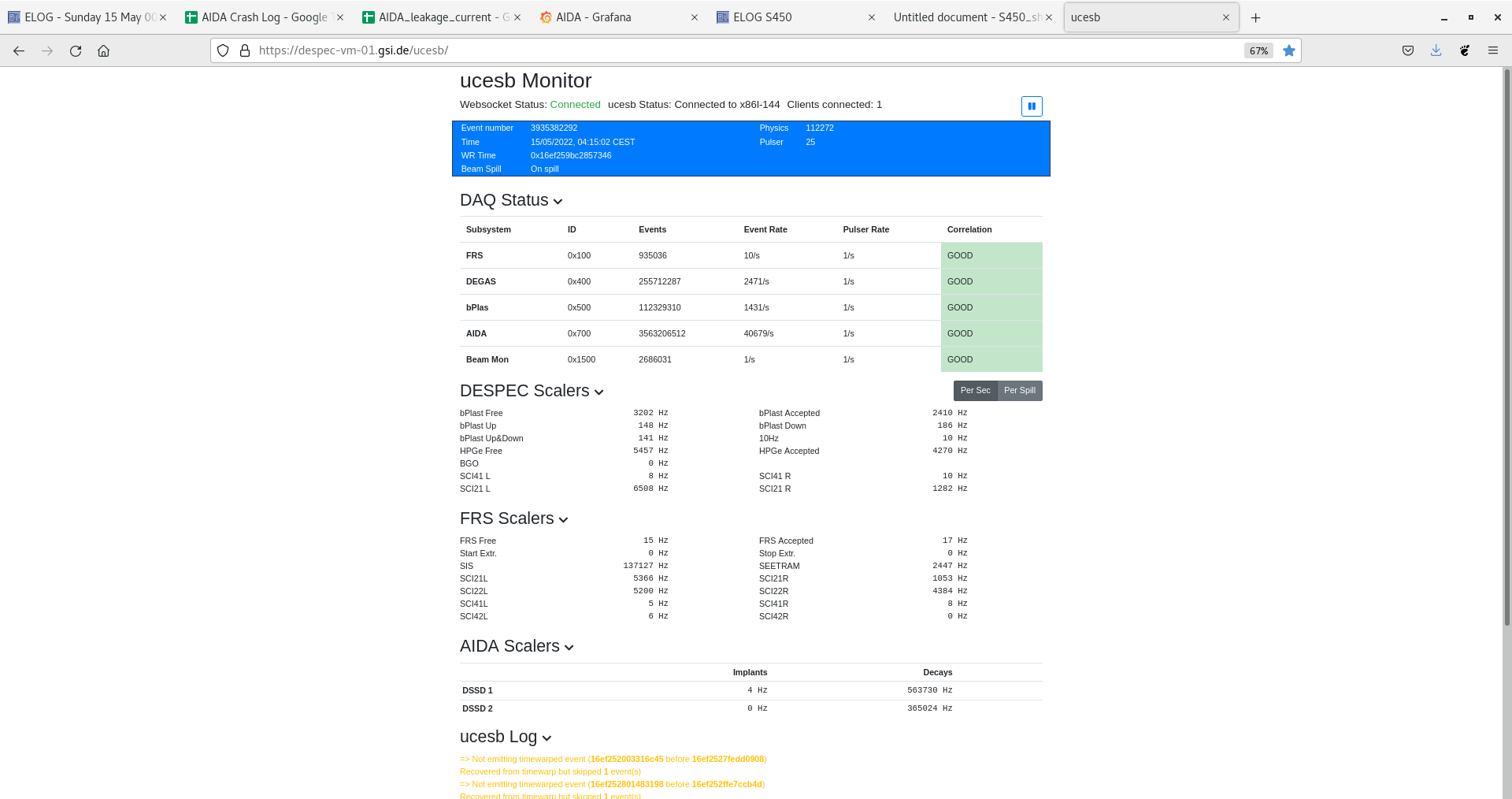

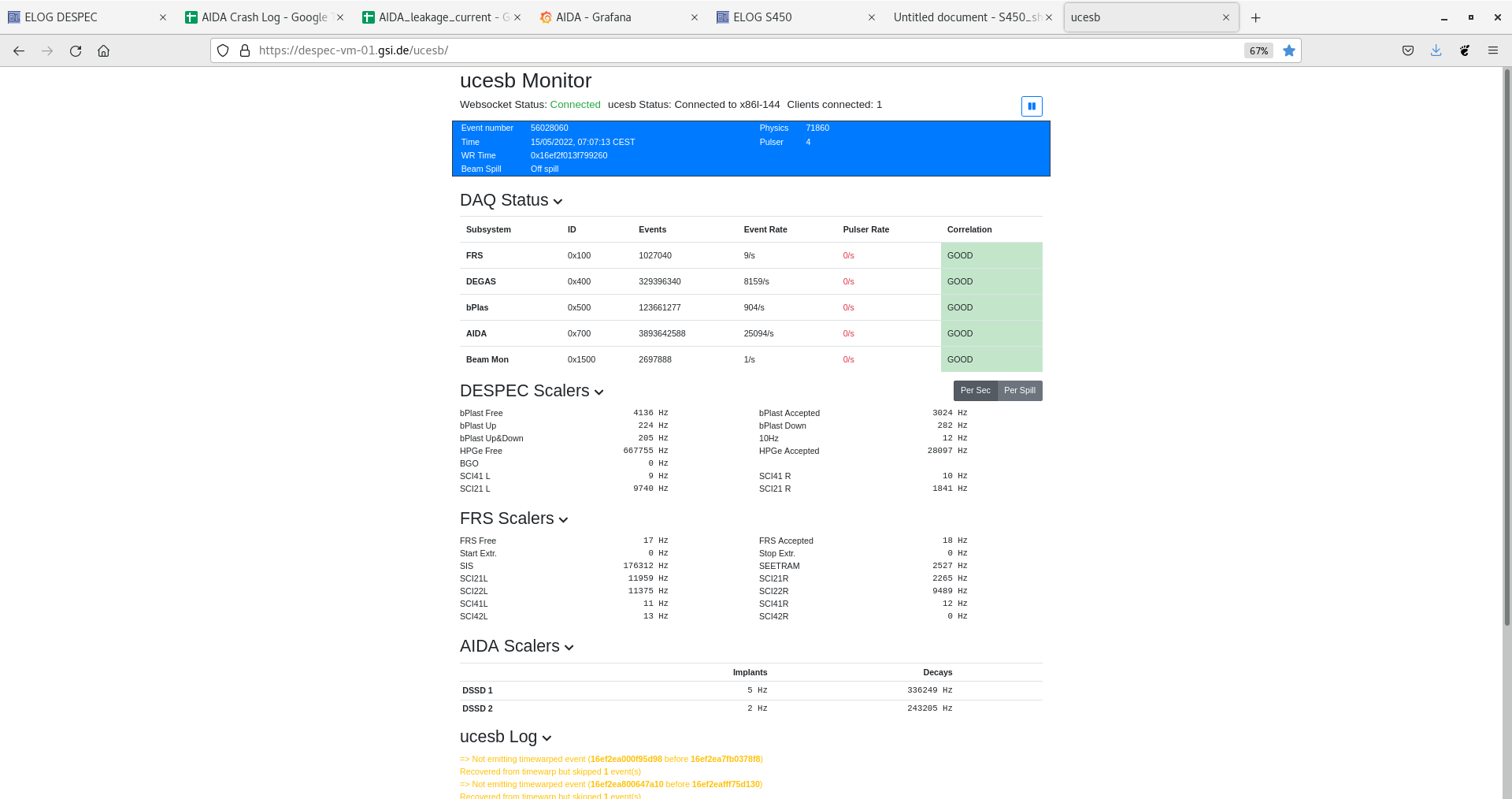

Status at 16:45 (CET)

The expreiment continues to run smoothly.

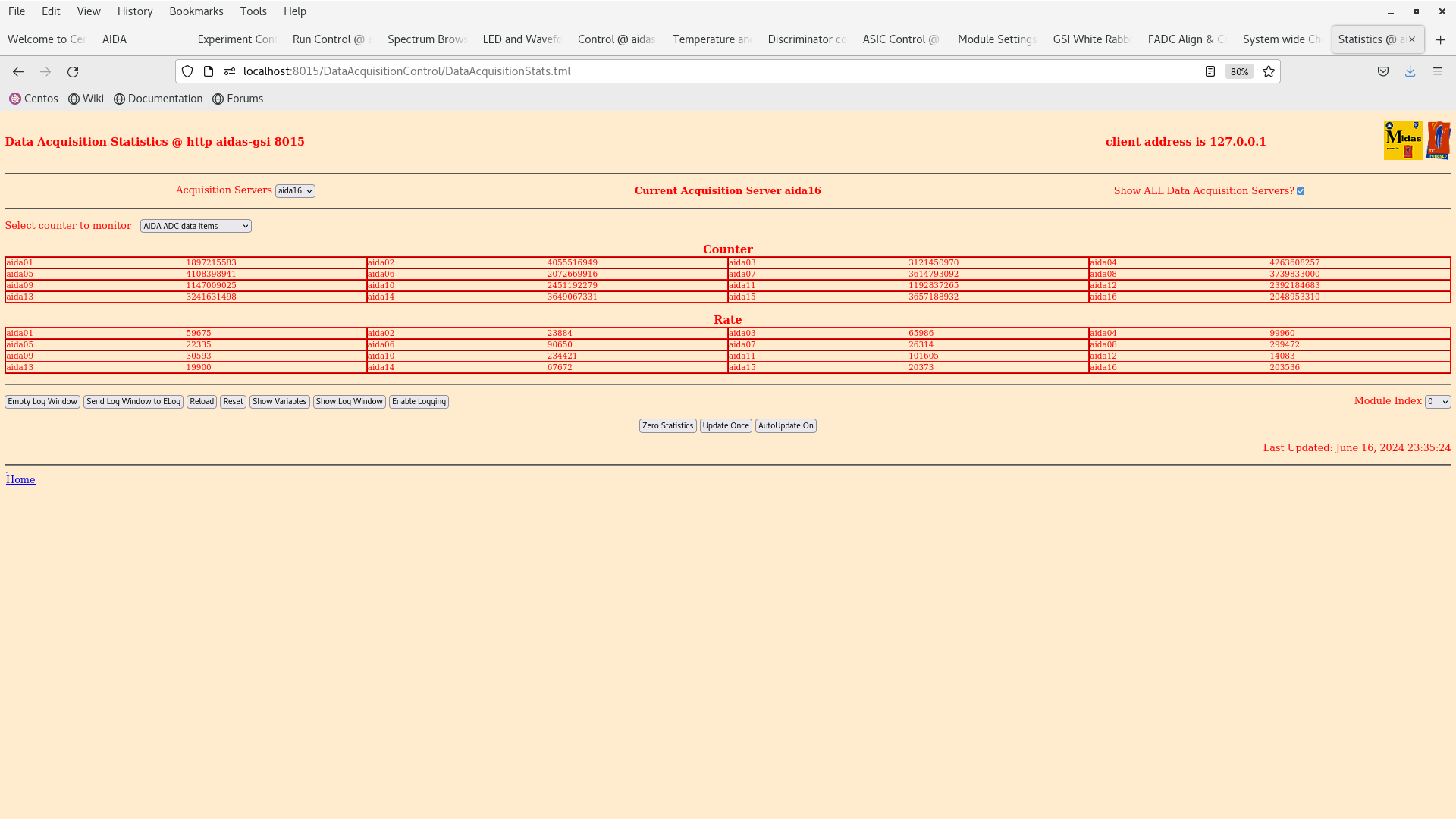

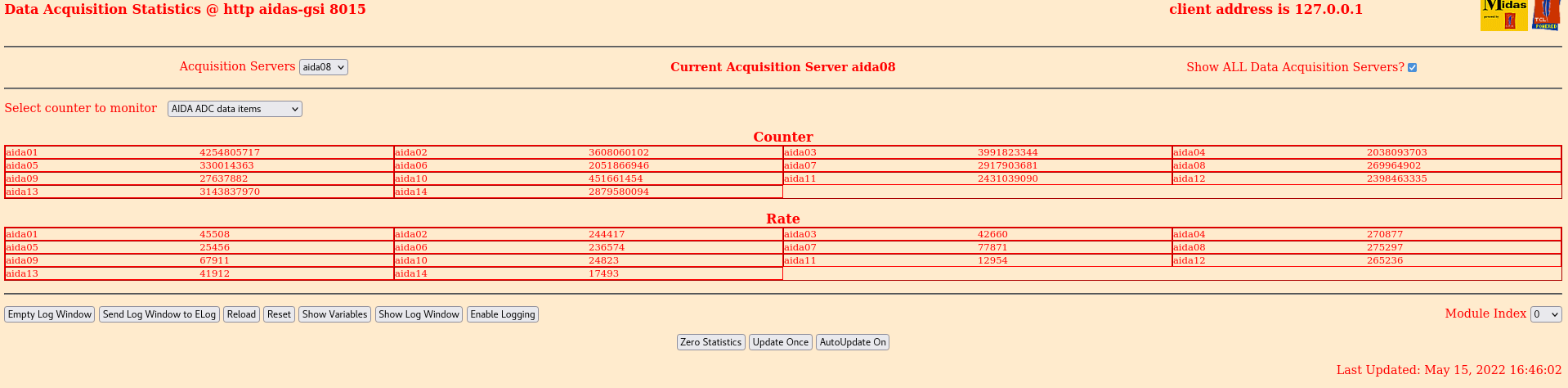

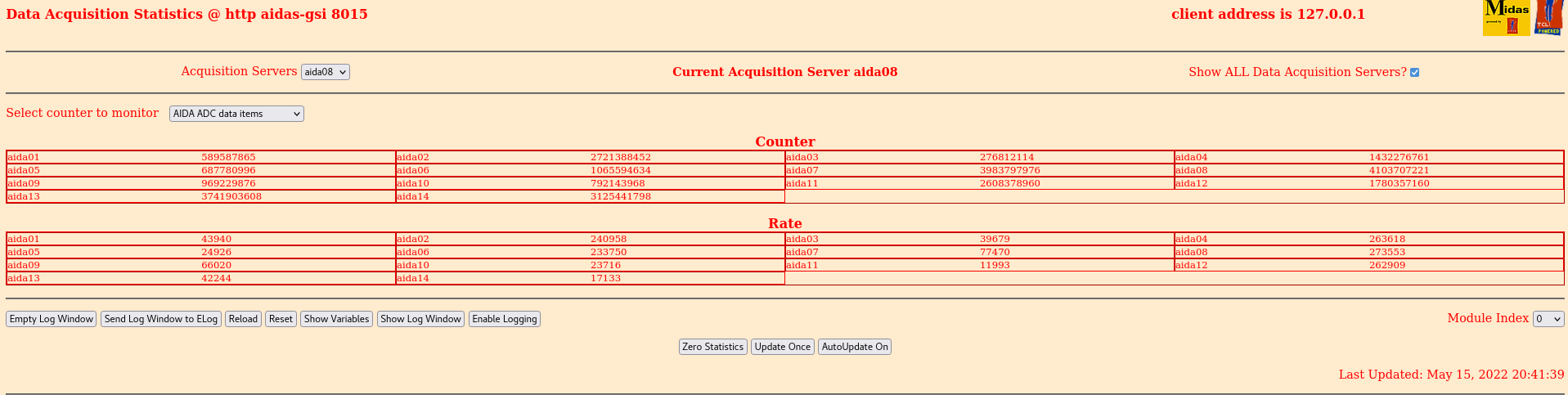

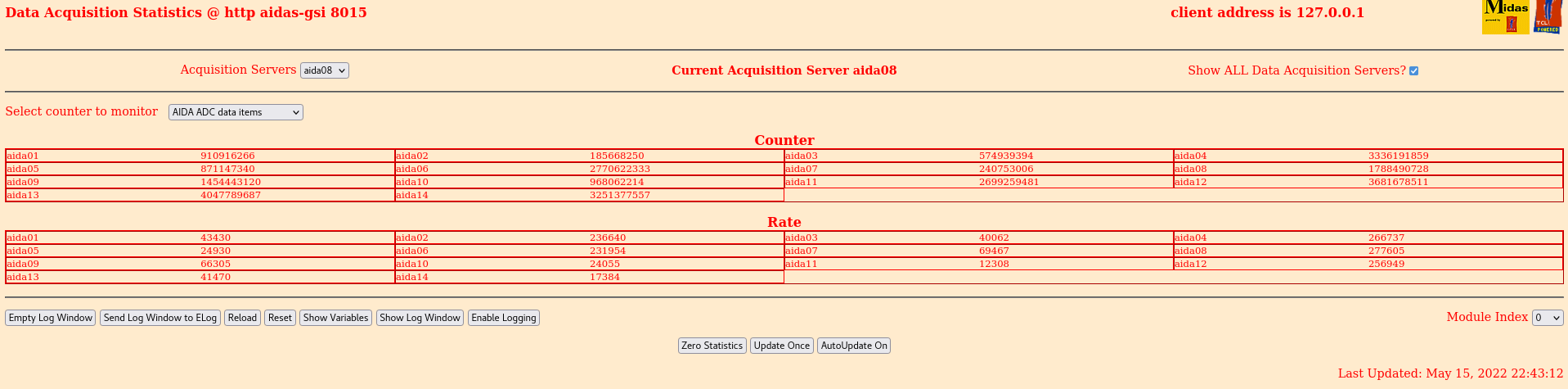

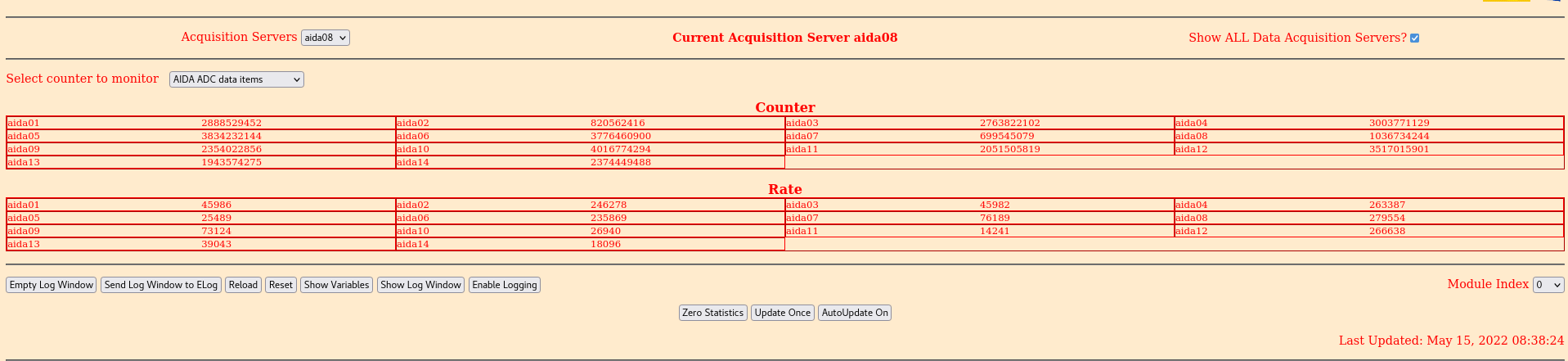

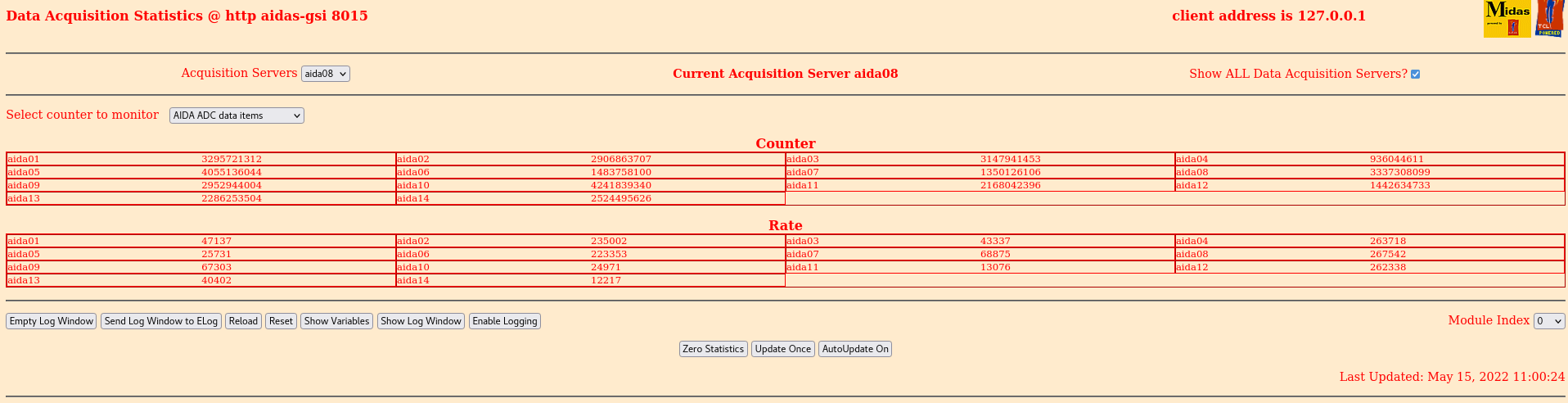

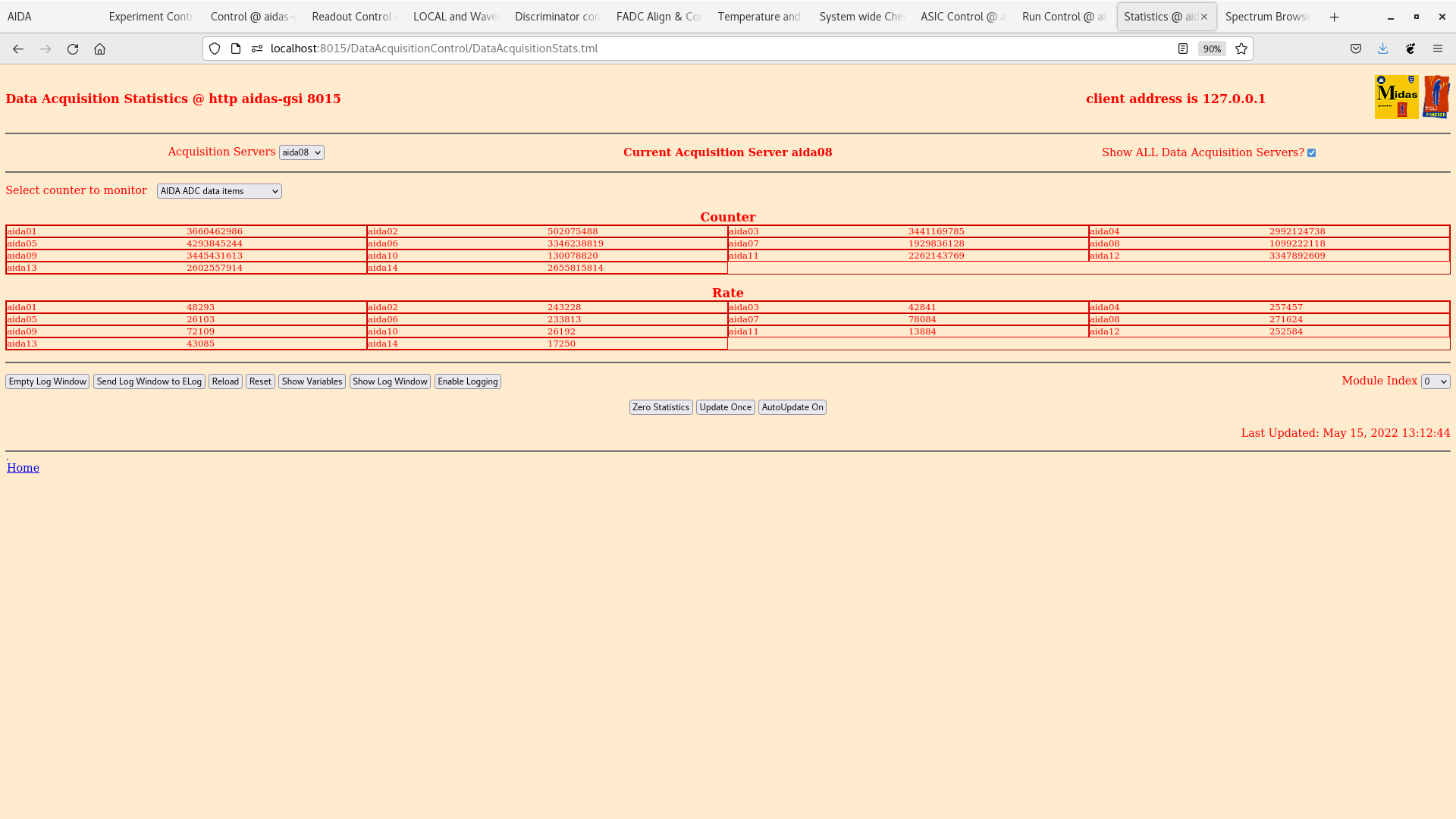

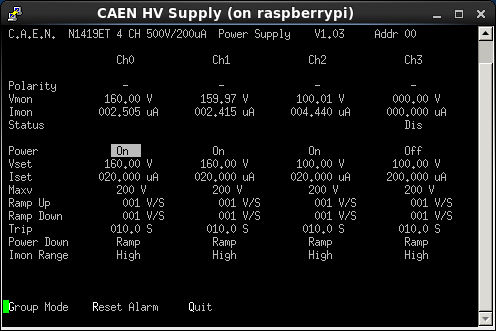

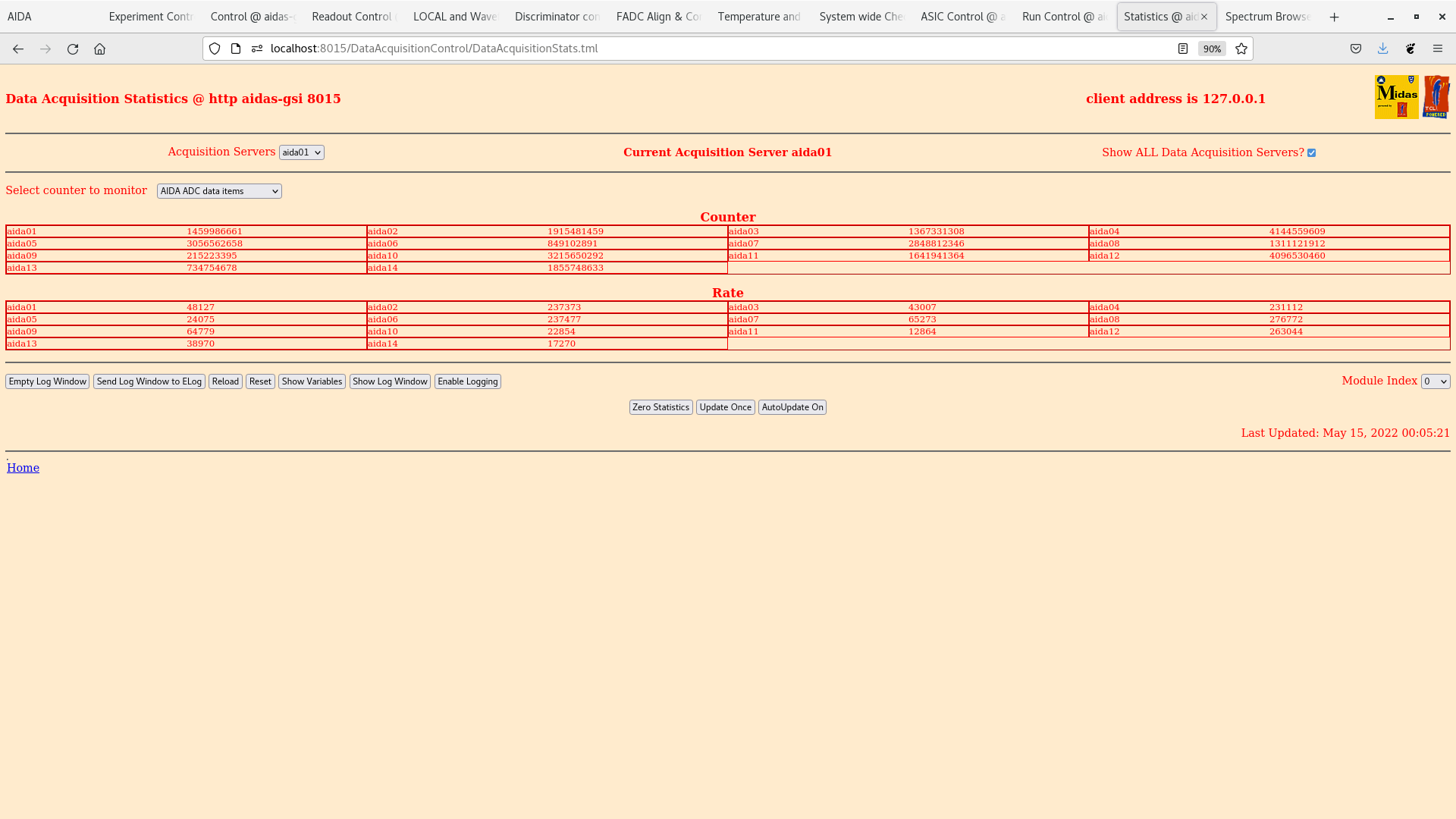

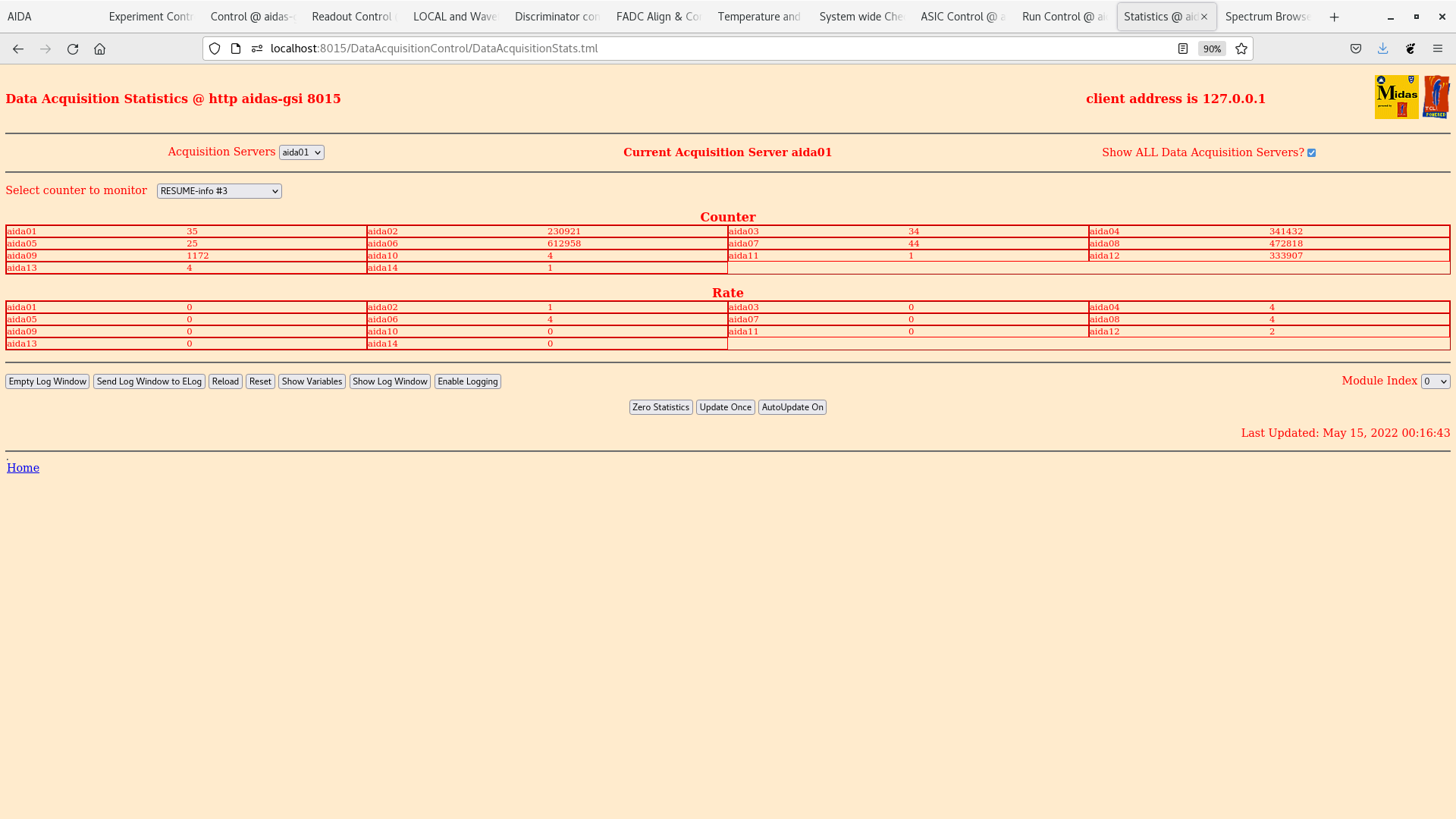

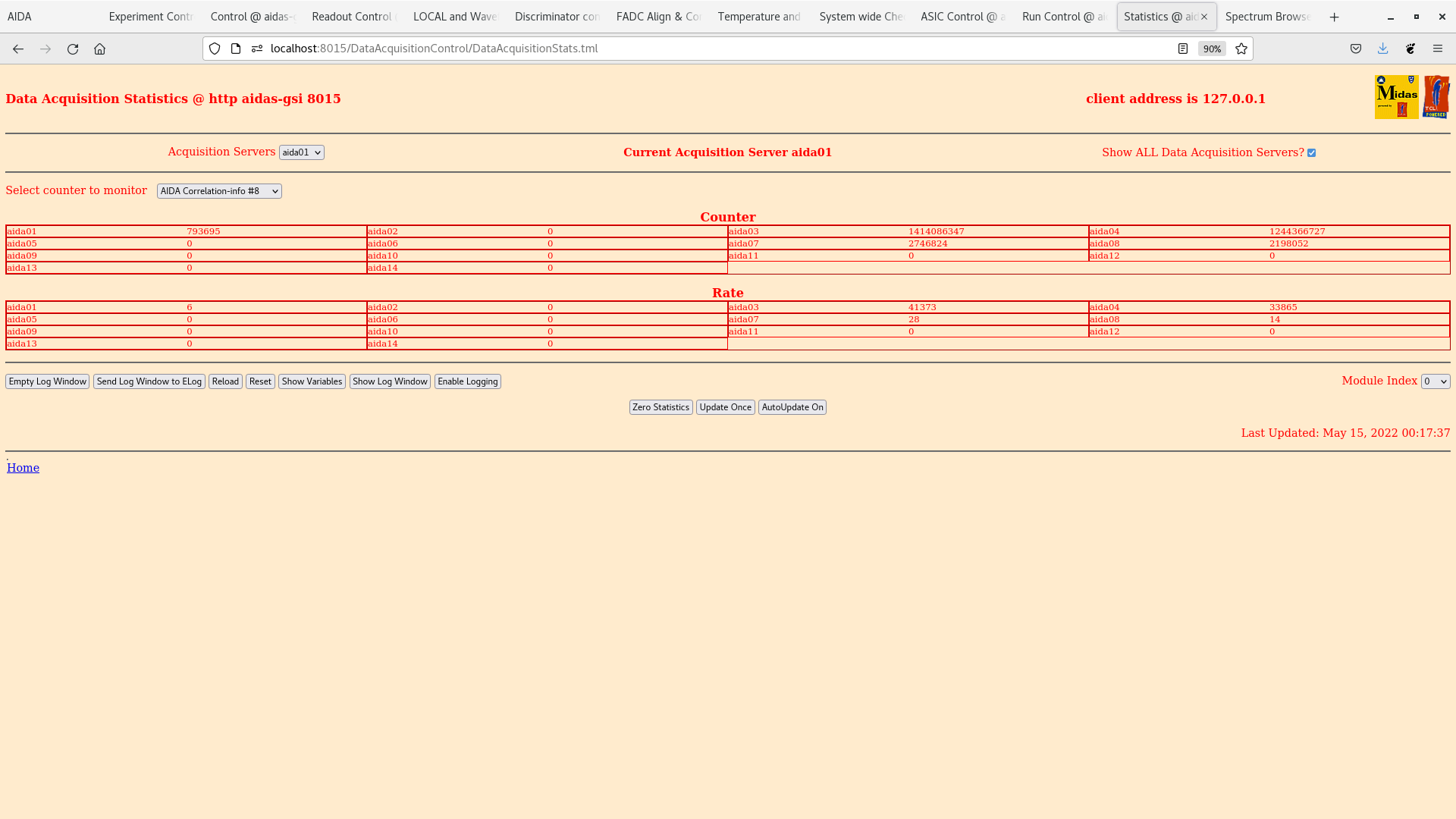

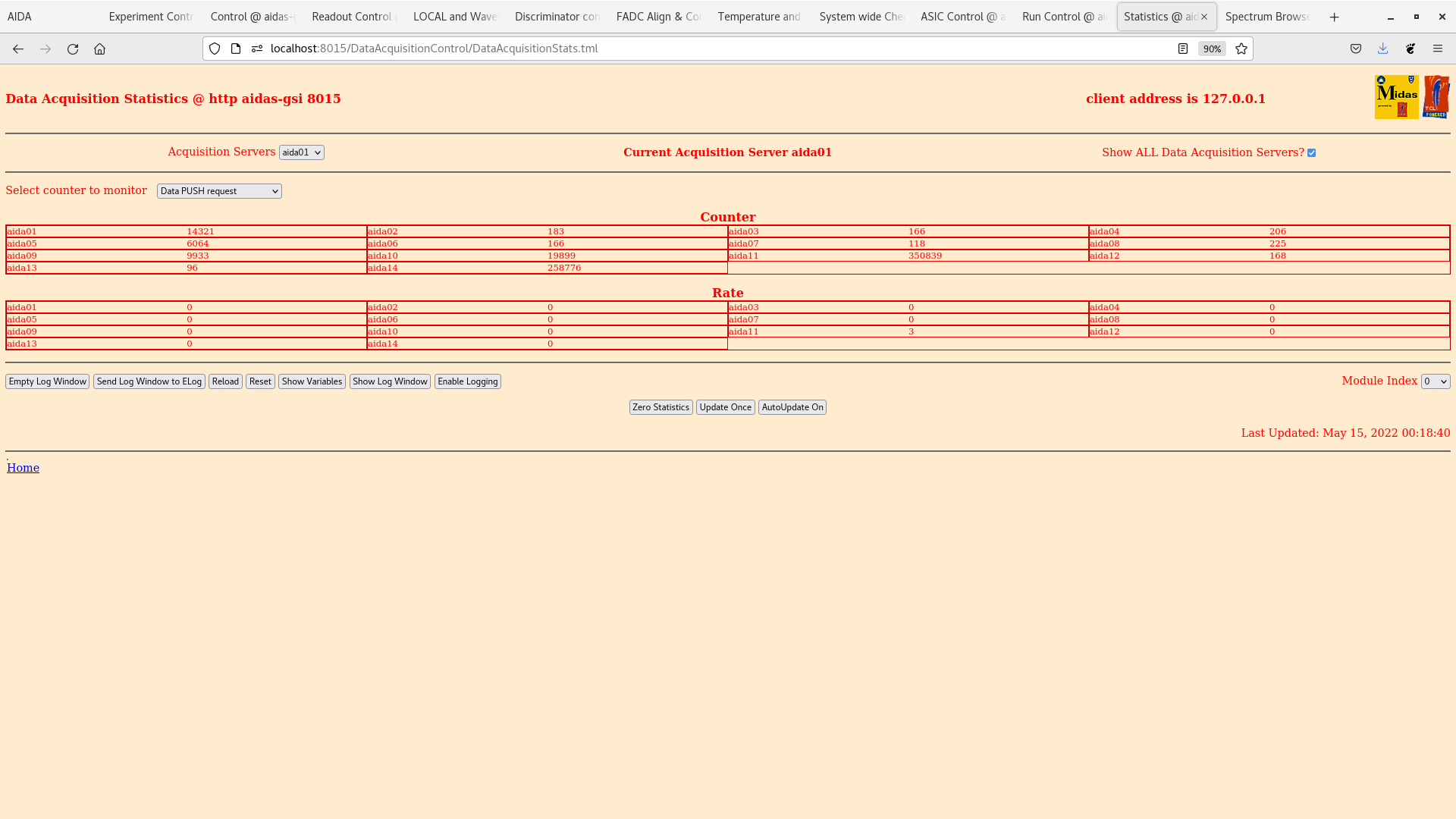

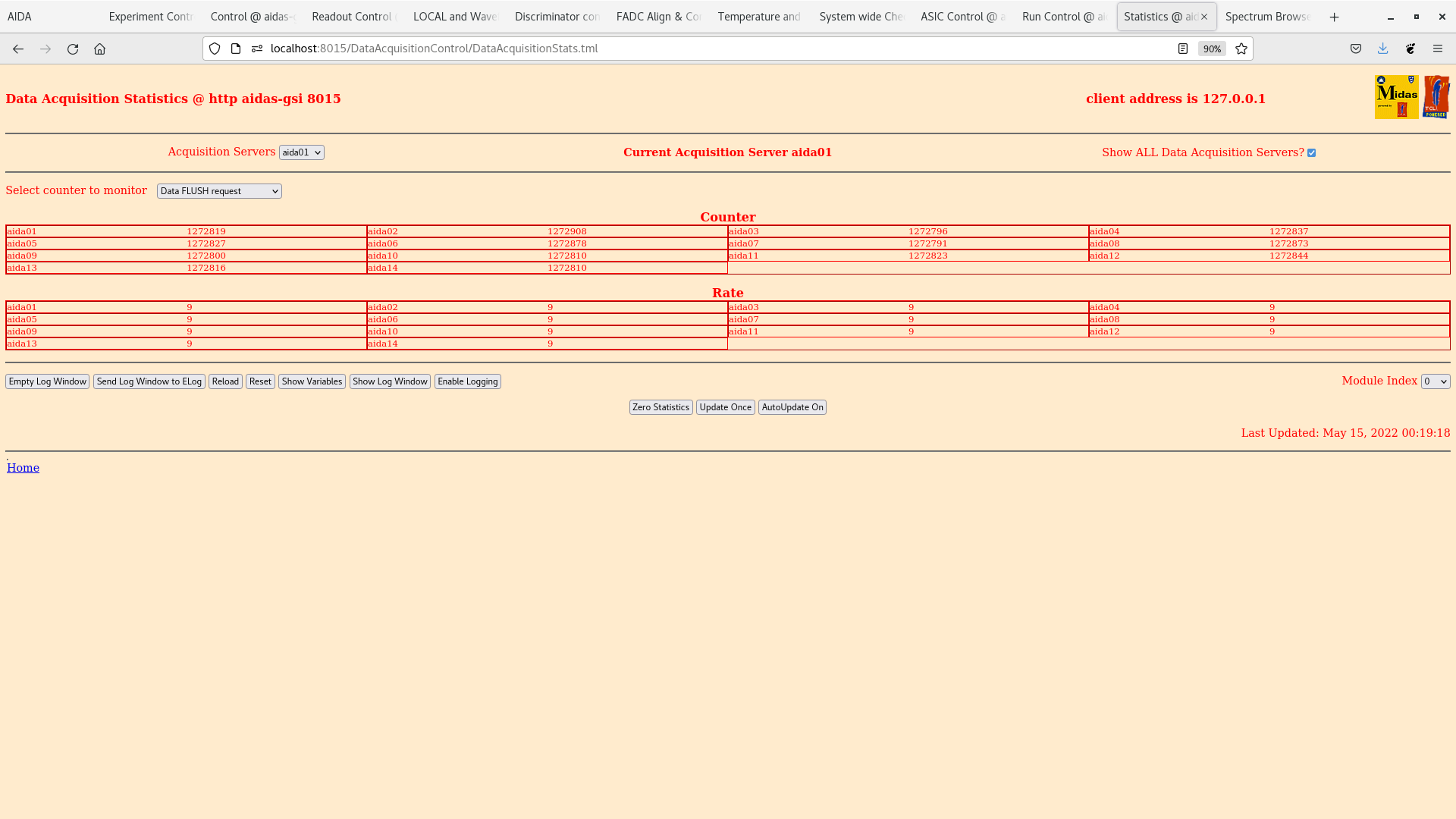

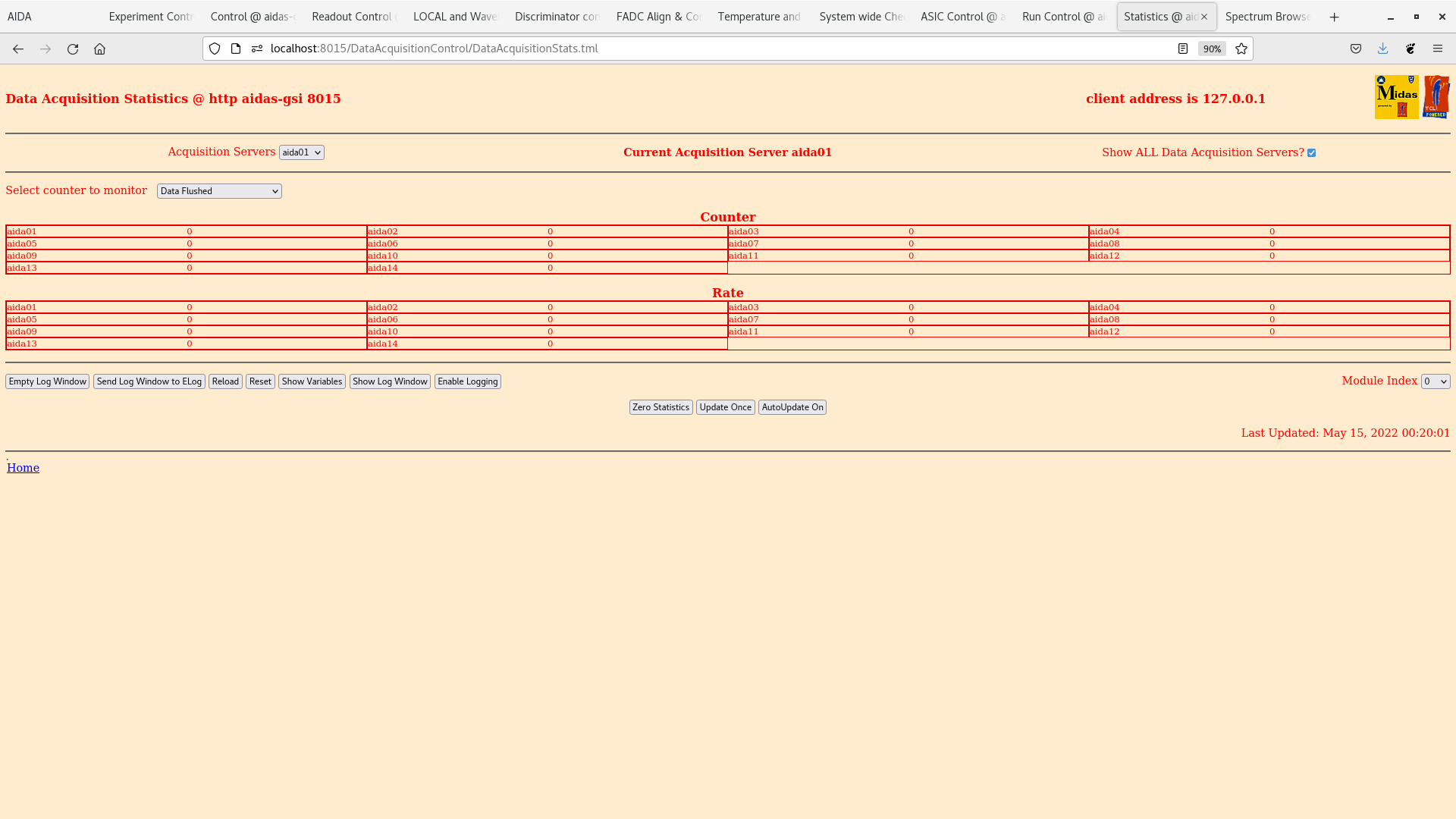

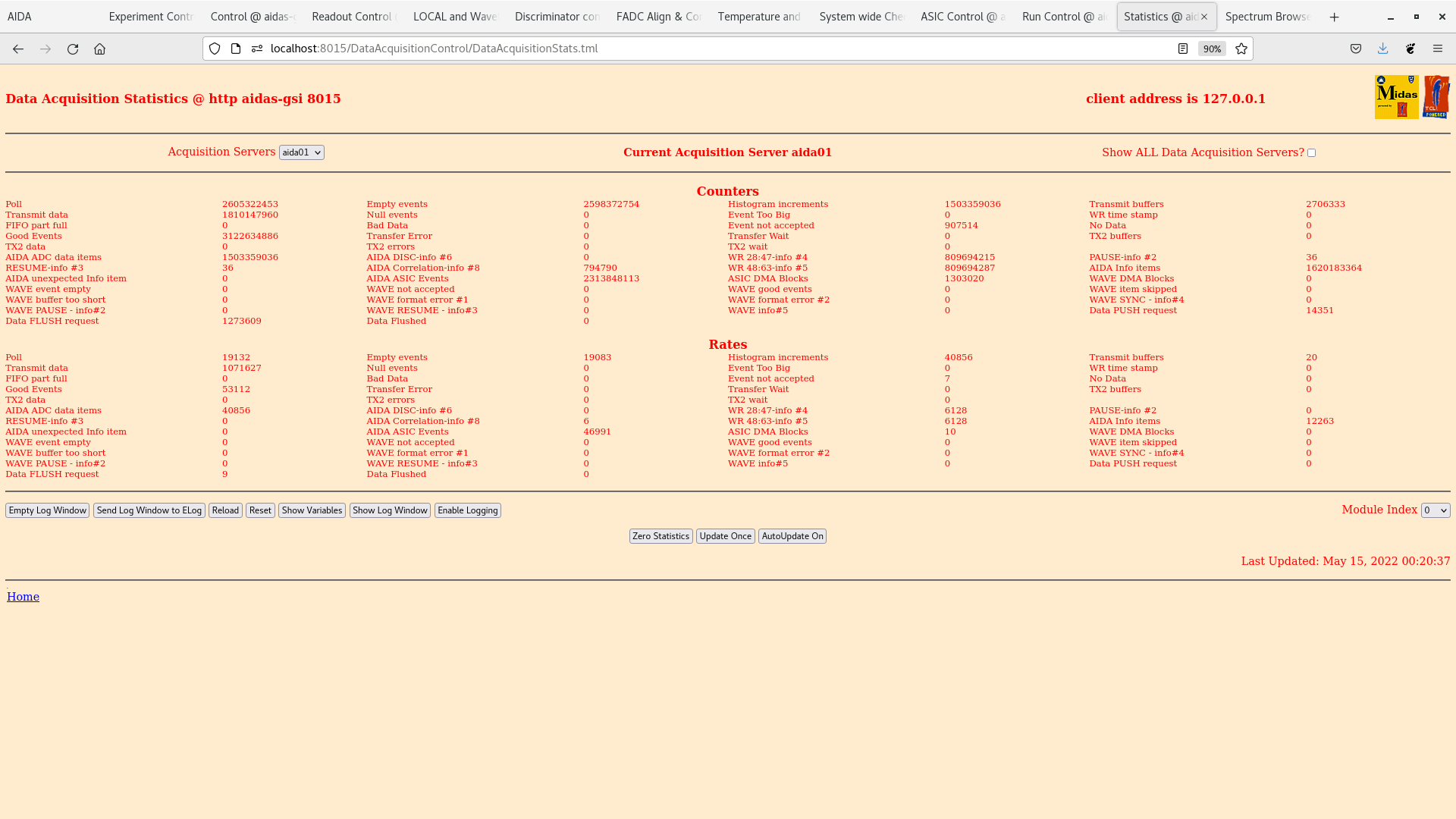

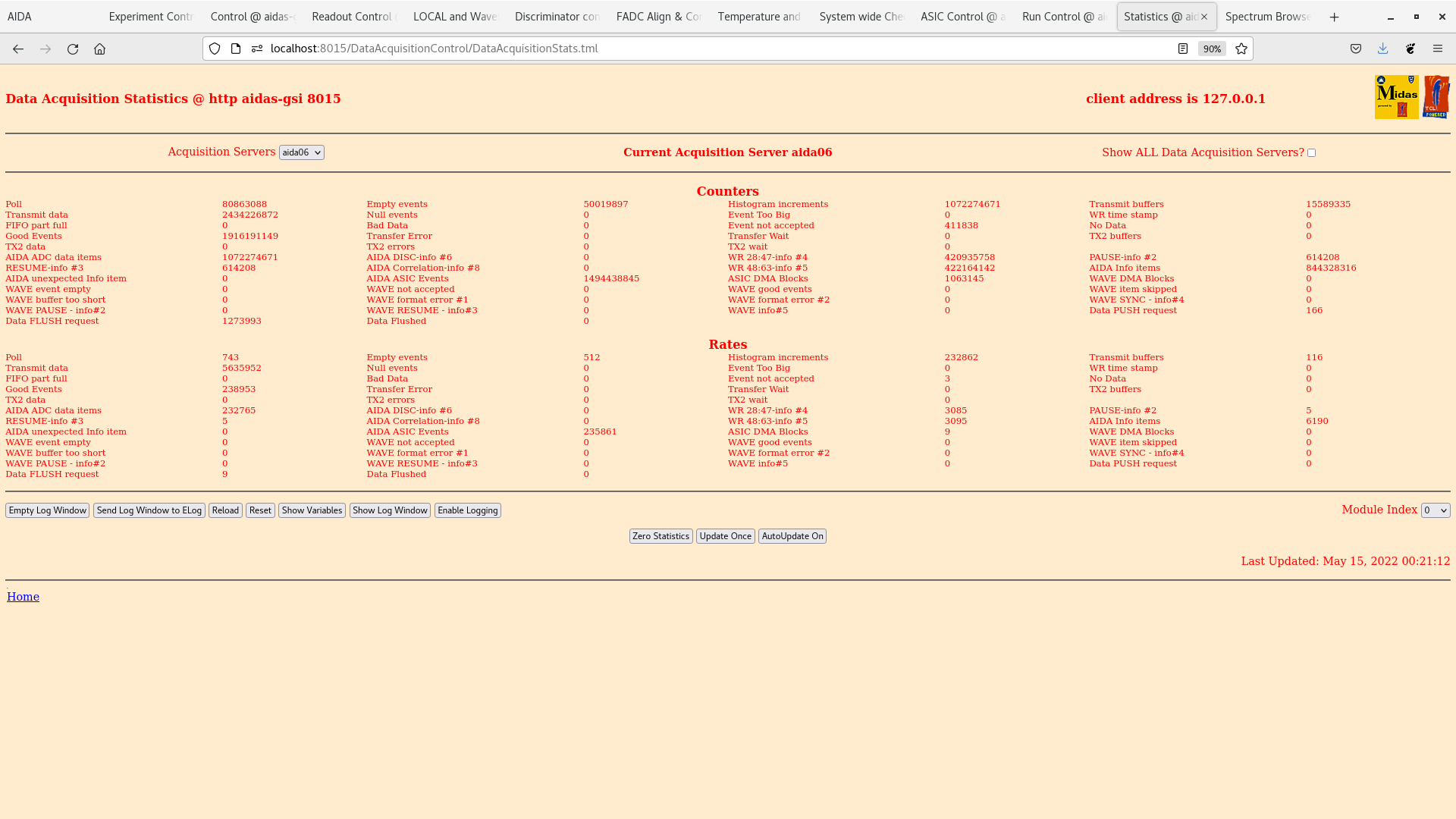

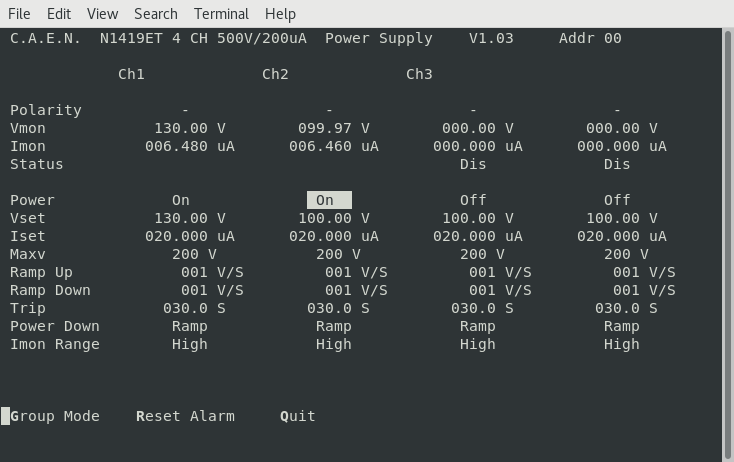

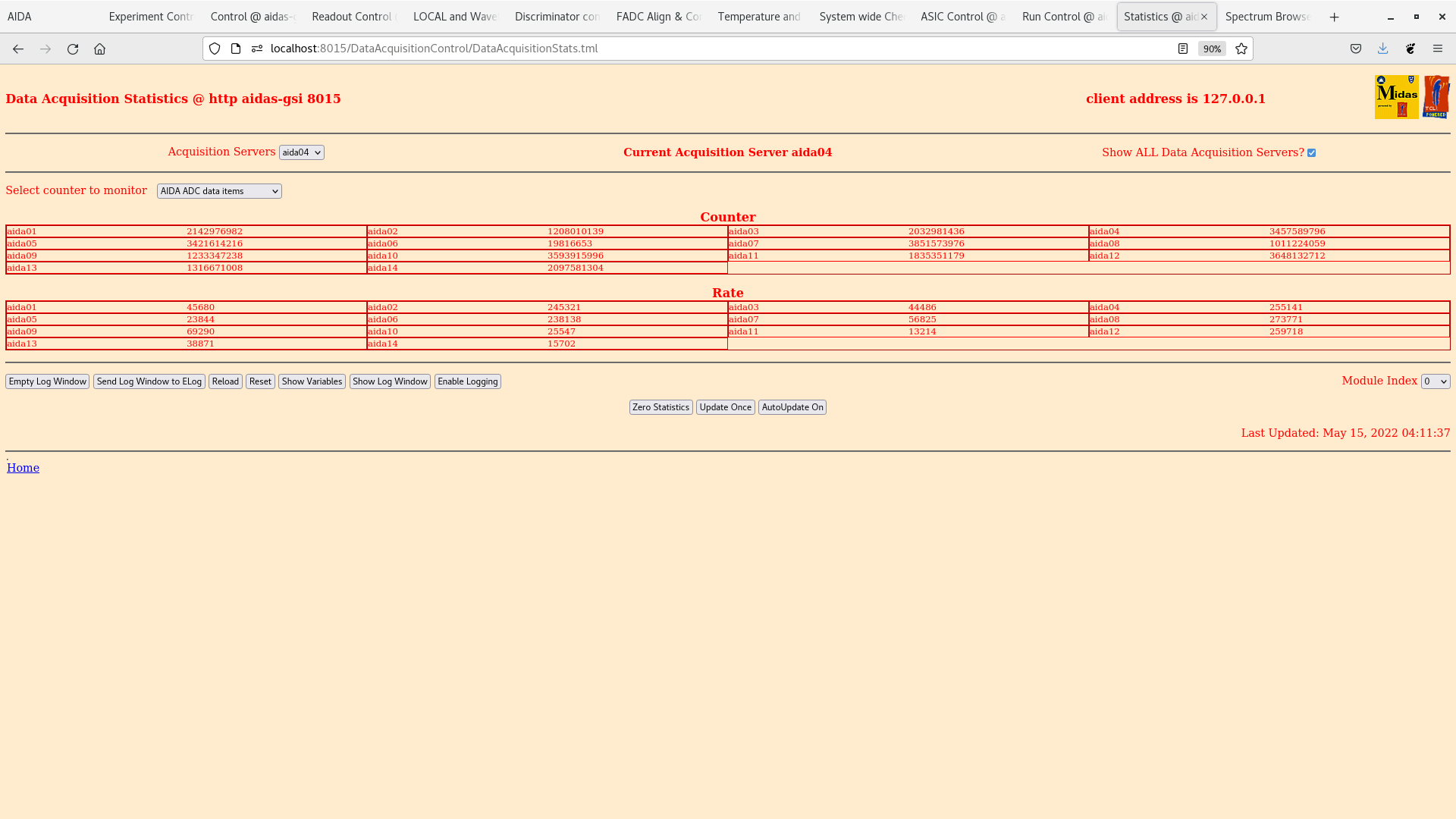

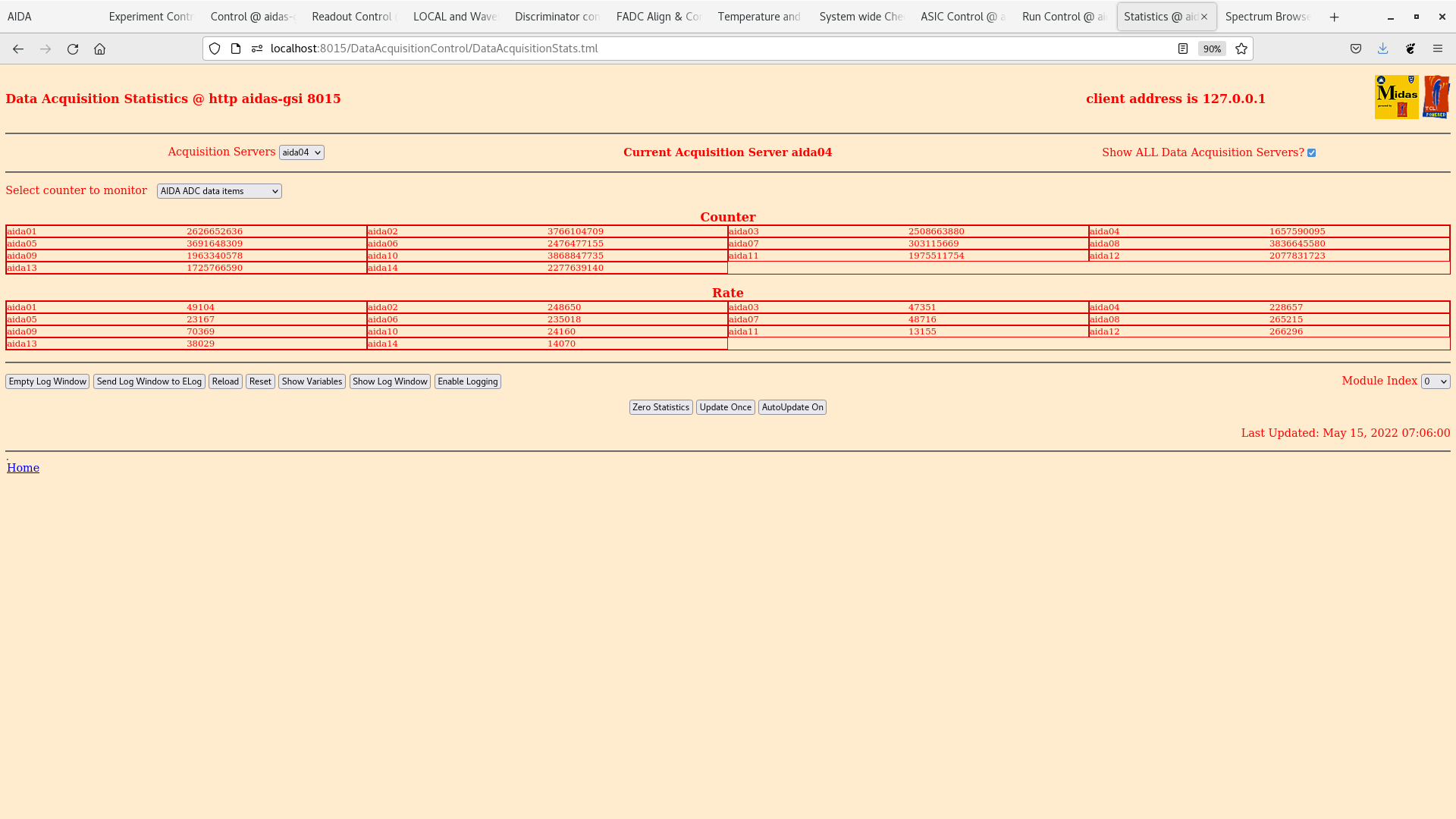

AIDA Stats look ok - Attachment 1

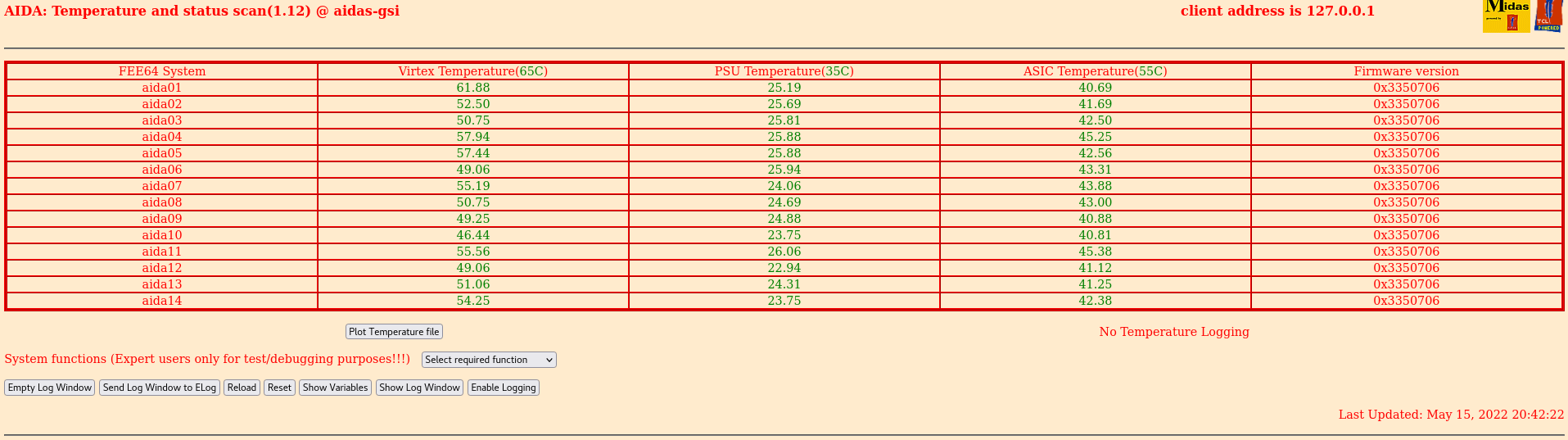

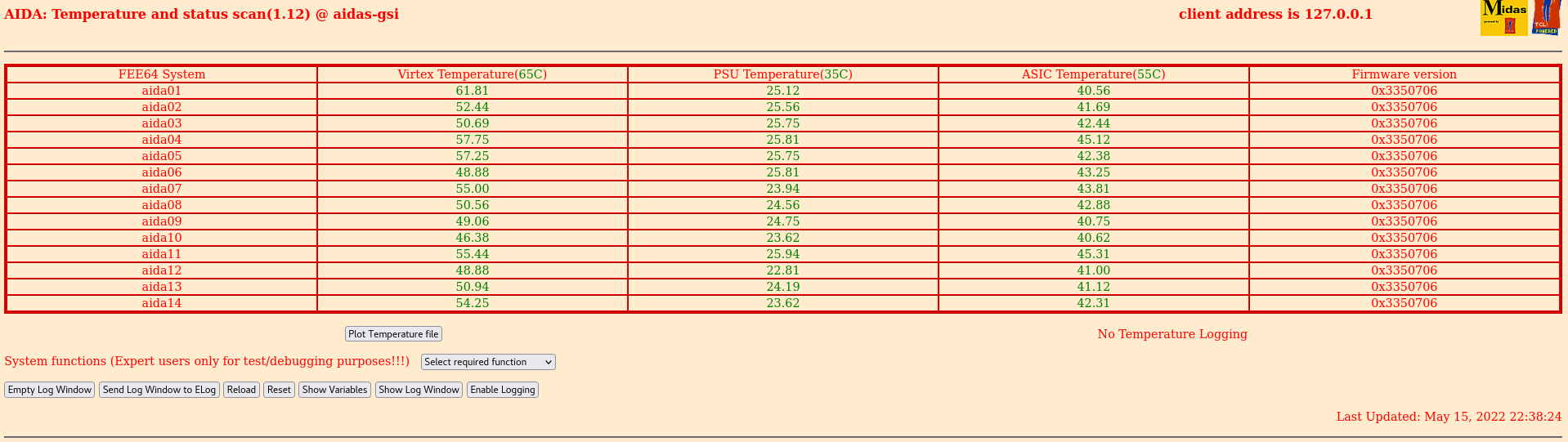

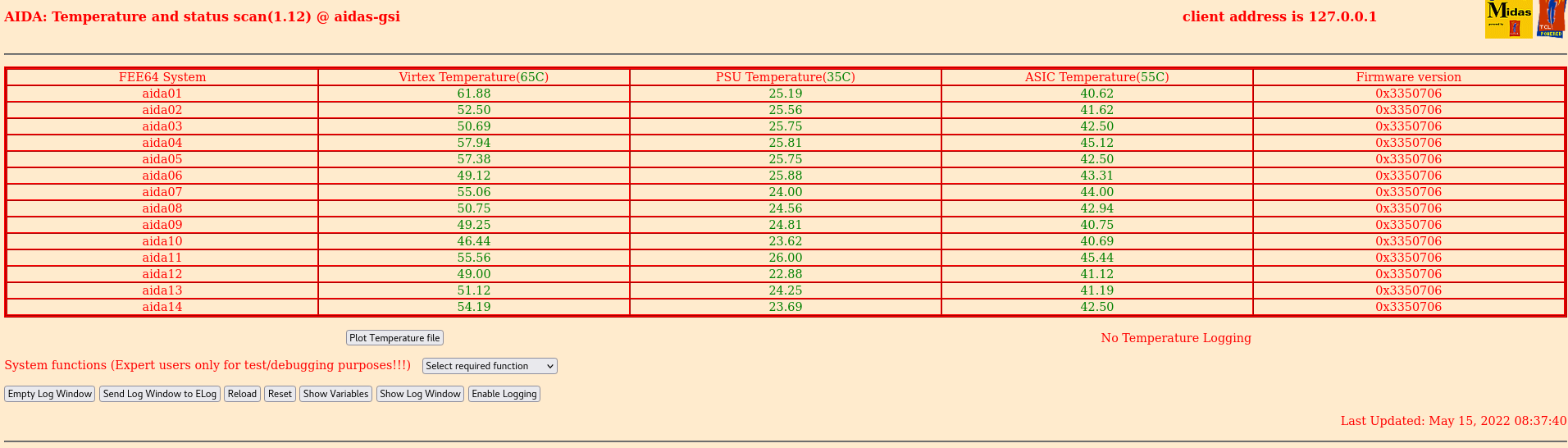

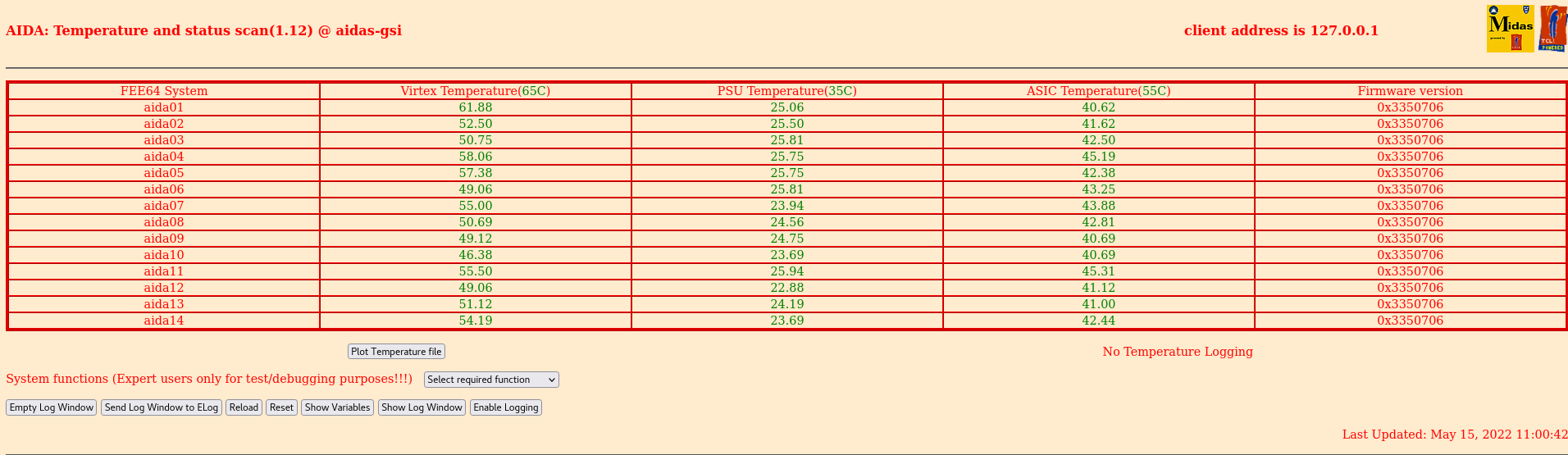

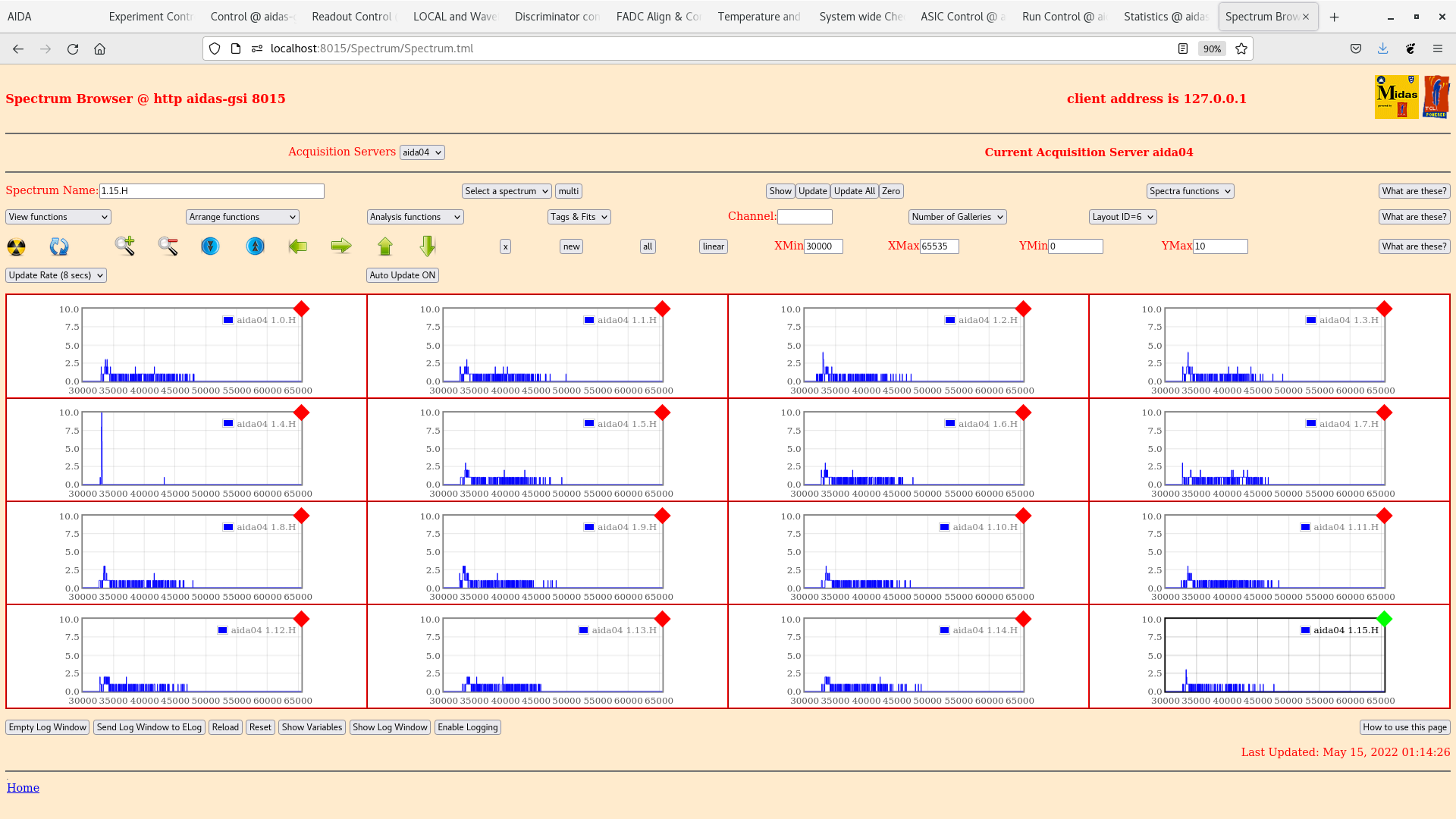

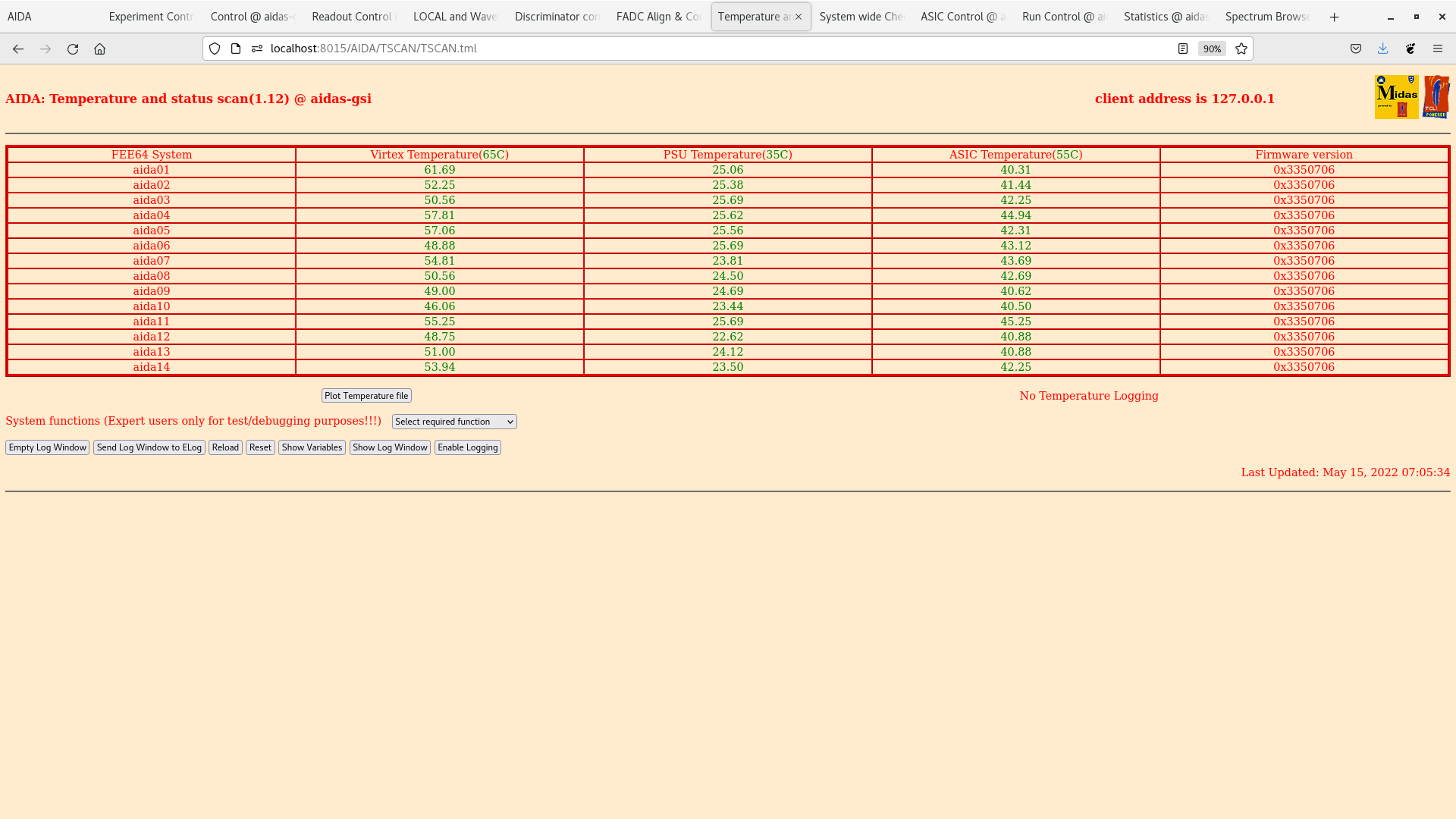

AIDA Temperature ok - Attachment 2

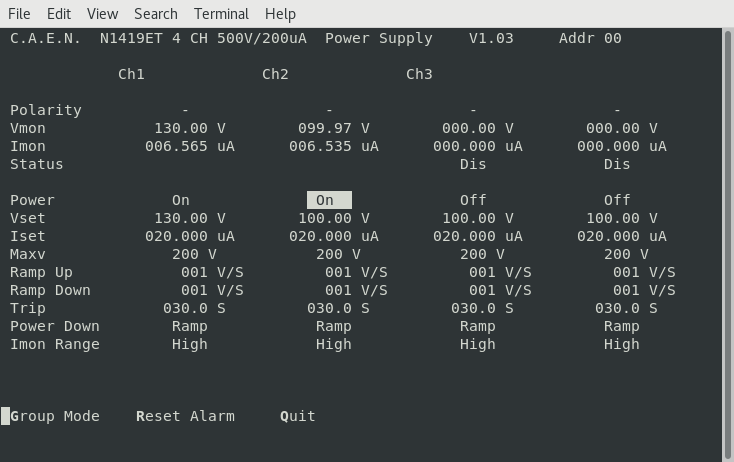

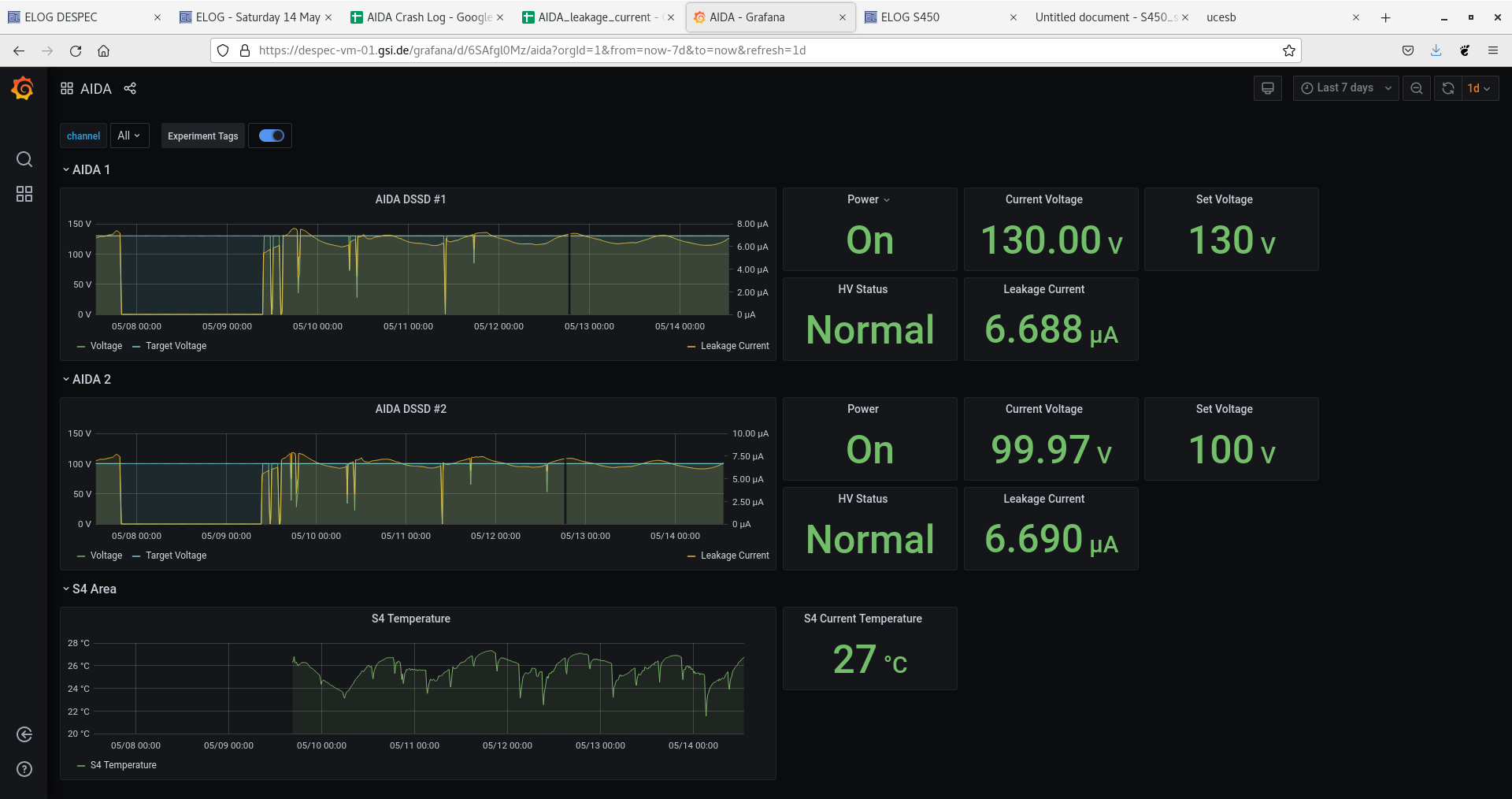

AIDA Leakage current: ok - Attachment 3

System wide check:

Clock: 13 passed, 1 failed (aida09)

ADC Calibration: 9 passed, 5 fialed (aida2,6,9,10,13)

White rabbit decoder: 14 passed, 0 failed.

FPGA timestamp: 14 passed, 0 failed.

Status at 18:45 (CET):

All rates ok on ucesb.

AIDA Stats ok - Attachment 4

AIDA Temperature ok - Attachment 5

AIDA Leakage current: increase slightly - Attachment 6

System wide check: No changes, same as above

Status at 20:45 (CET):

All rates ok on ucesb.

AIDA Stats ok - Attachment 7

AIDA Temperature ok - Attachment 8

AIDA Leakage current: increase slightly - Attachment 9

System wide check: No changes, same as above

Status at 22:45 (CET):

All rates ok on ucesb.

AIDA Stats ok - Attachment 10

AIDA Temperature ok - Attachment 11

AIDA Leakage current: increase slightly - Attachment 12

System wide check: No changes, same as above |

| Attachment 1: Stats_Screenshot_from_2022-05-15_16-49-06.png

|

|

| Attachment 2: Temp_Screenshot_from_2022-05-15_16-48-31.png

|

|

| Attachment 3: HV_LC_Screenshot_from_2022-05-15_16-47-44.png

|

|

| Attachment 4: Stats_Screenshot_from_2022-05-15_18-43-16.png

|

|

| Attachment 5: Temp_Screenshot_from_2022-05-15_18-44-06.png

|

|

| Attachment 6: HV_LC_Screenshot_from_2022-05-15_18-42-23.png

|

|

| Attachment 7: Stats_Screenshot_from_2022-05-15_20-42-03.png

|

|

| Attachment 8: Temp_Screenshot_from_2022-05-15_20-42-42.png

|

|

| Attachment 9: HV_LC_Screenshot_from_2022-05-15_20-36-28.png

|

|

| Attachment 10: Stats_Screenshot_from_2022-05-15_22-43-37.png

|

|

| Attachment 11: Temp_Screenshot_from_2022-05-15_22-44-20.png

|

|

| Attachment 12: HV_LC_Screenshot_from_2022-05-15_22-42-36.png

|

|

|

456

|

Sun May 15 07:40:52 2022 |

OH | Sunday 15th May 08:00-16:00 |

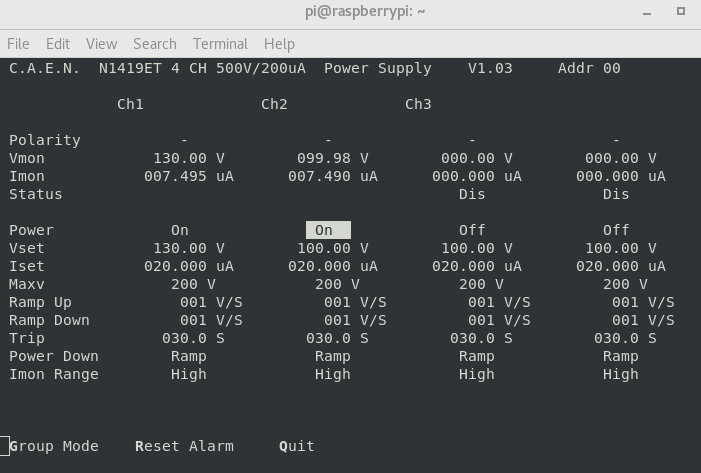

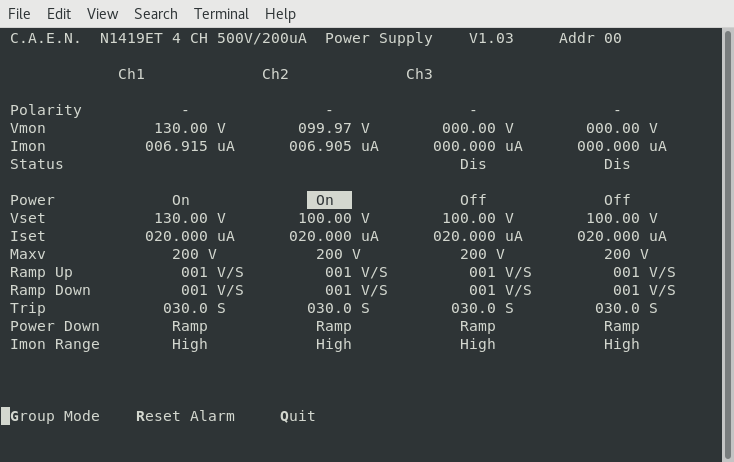

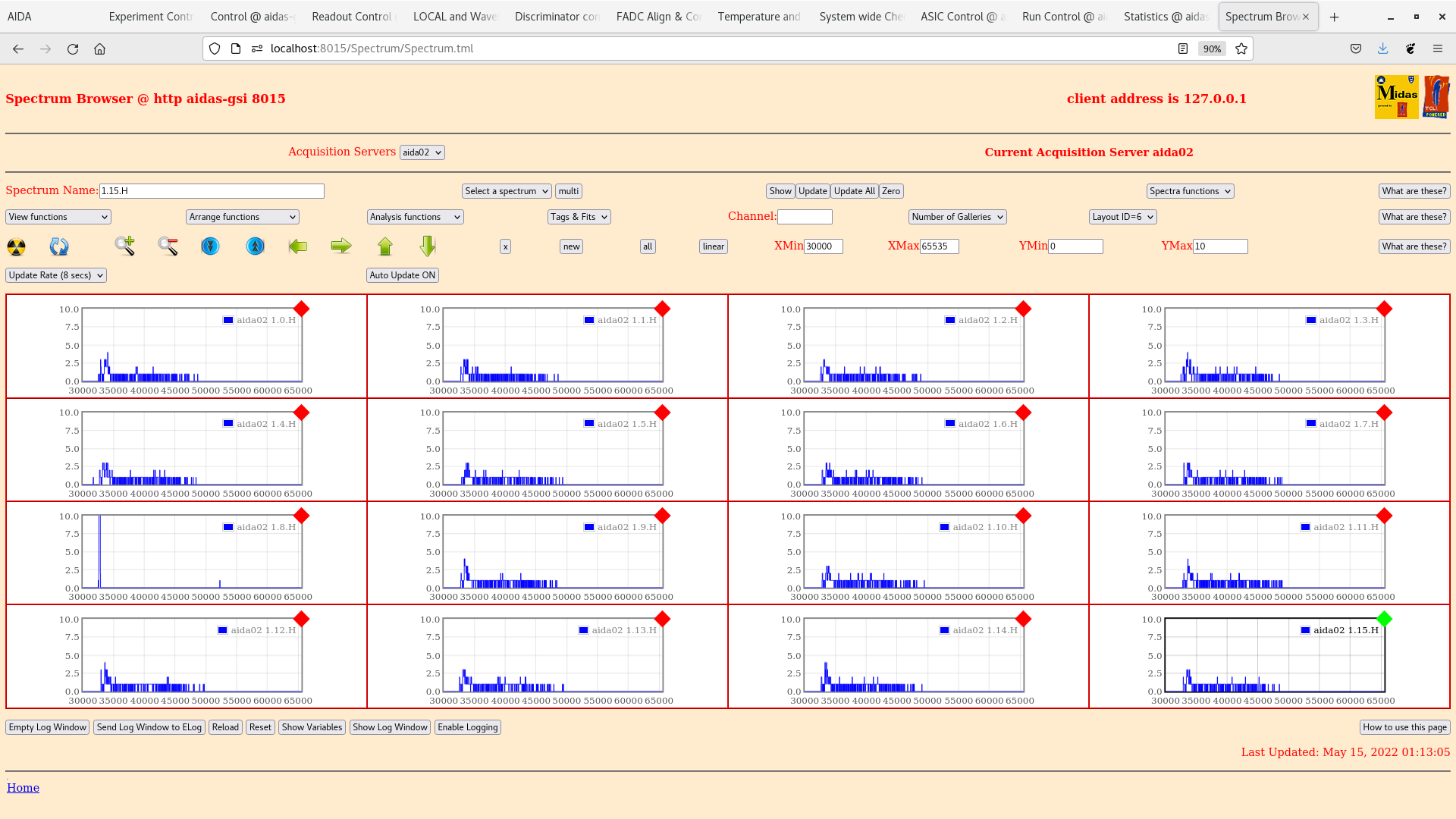

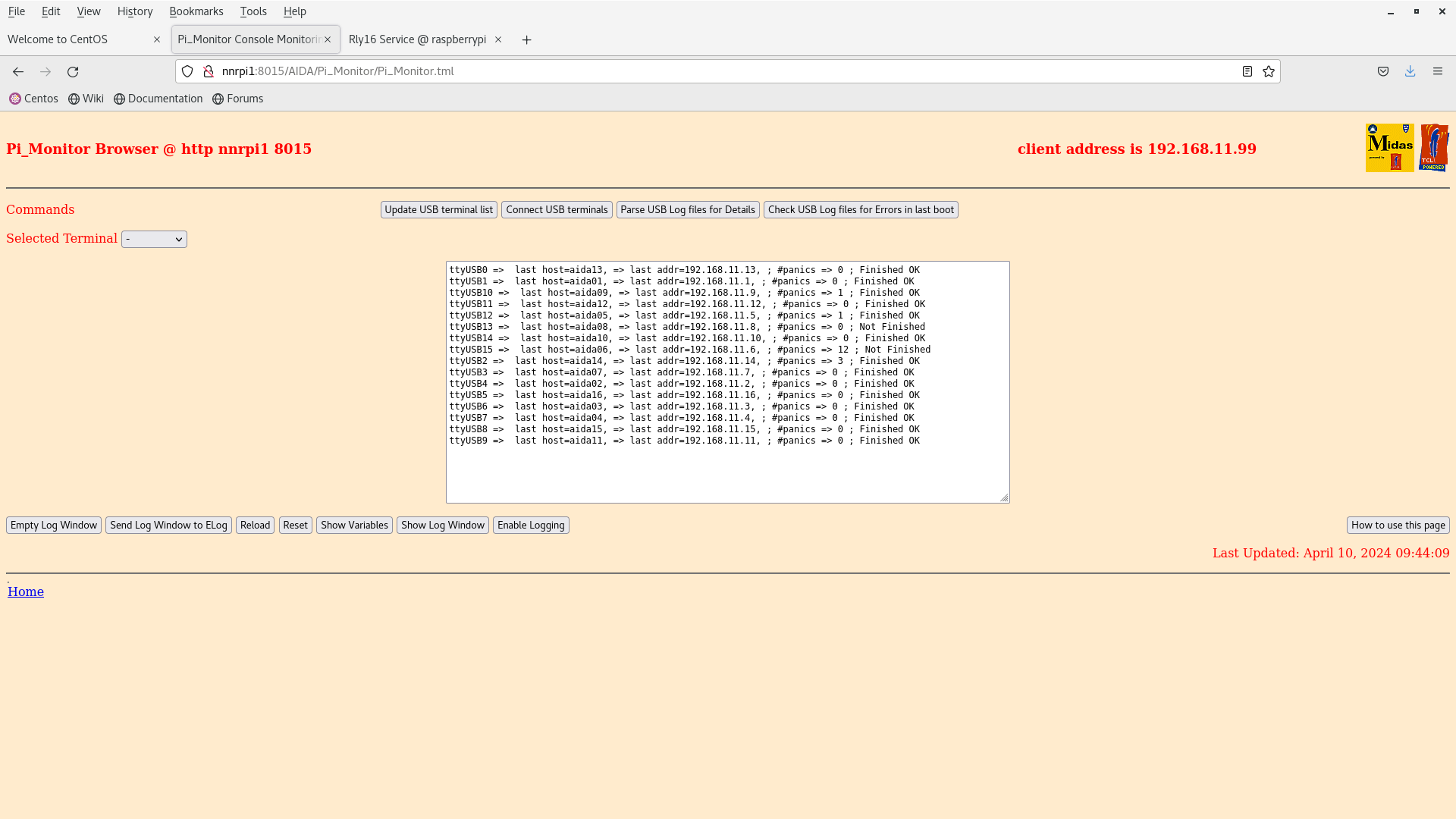

08:40 FEE Temperatures ok - attachment 1

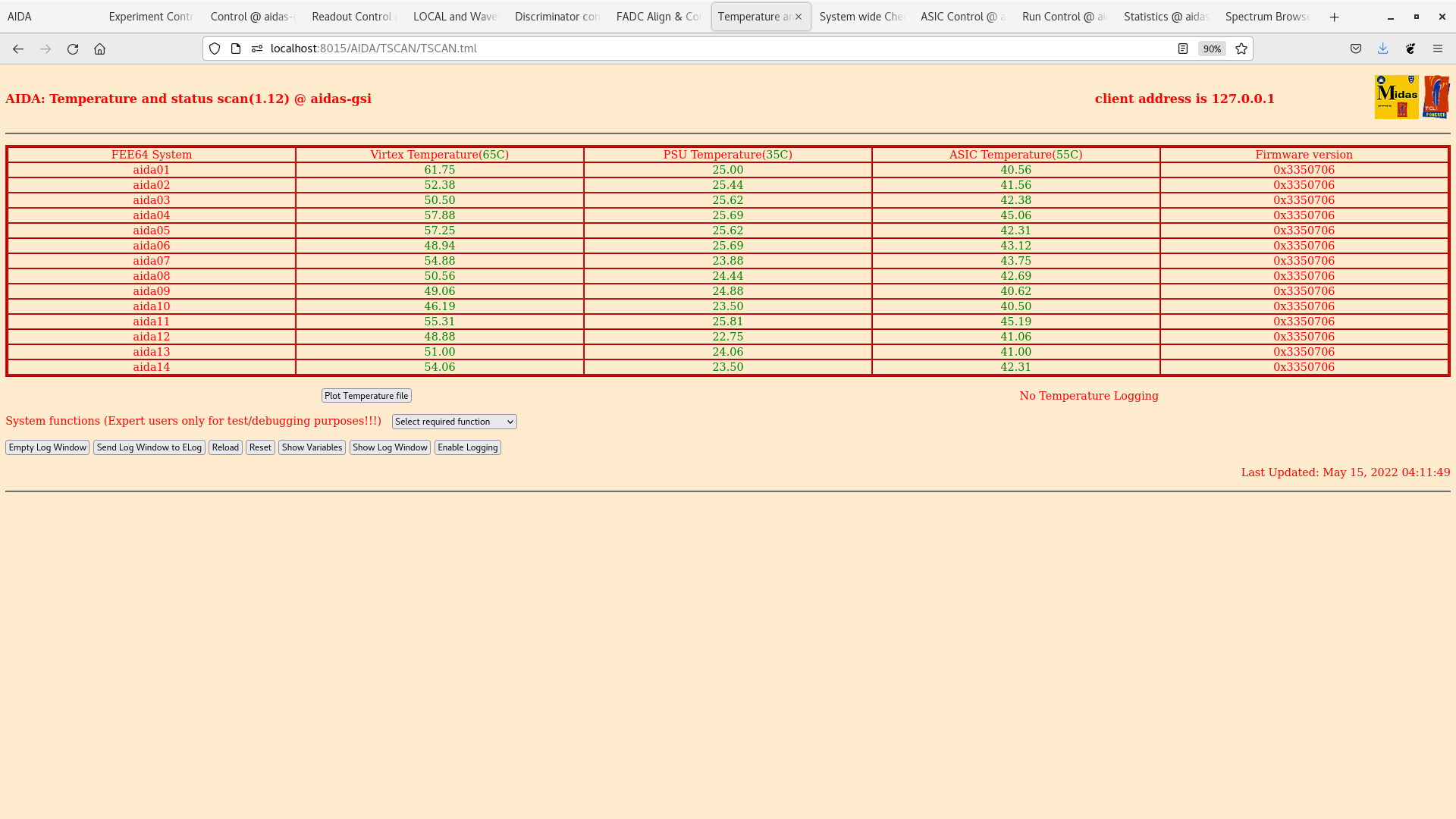

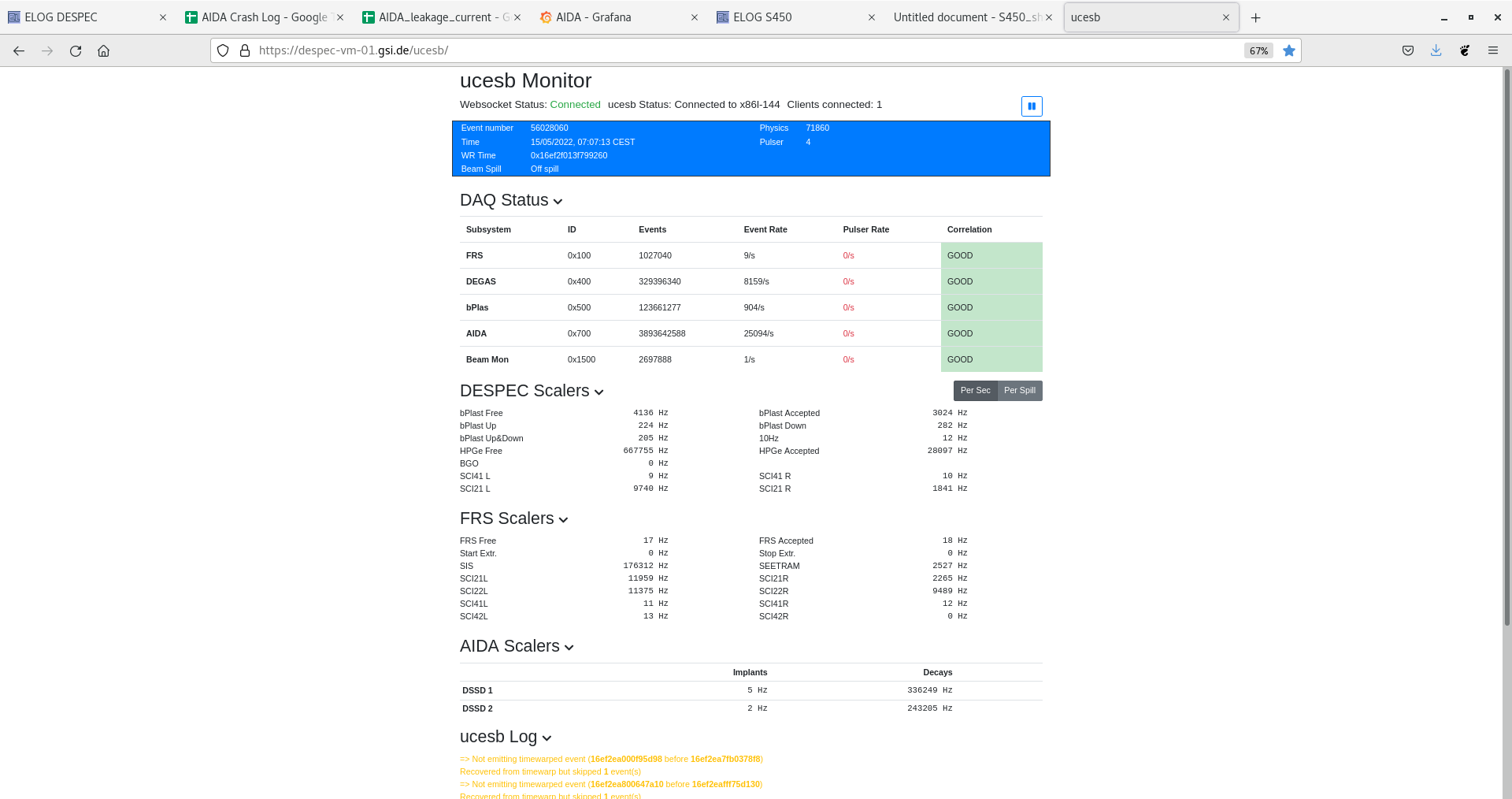

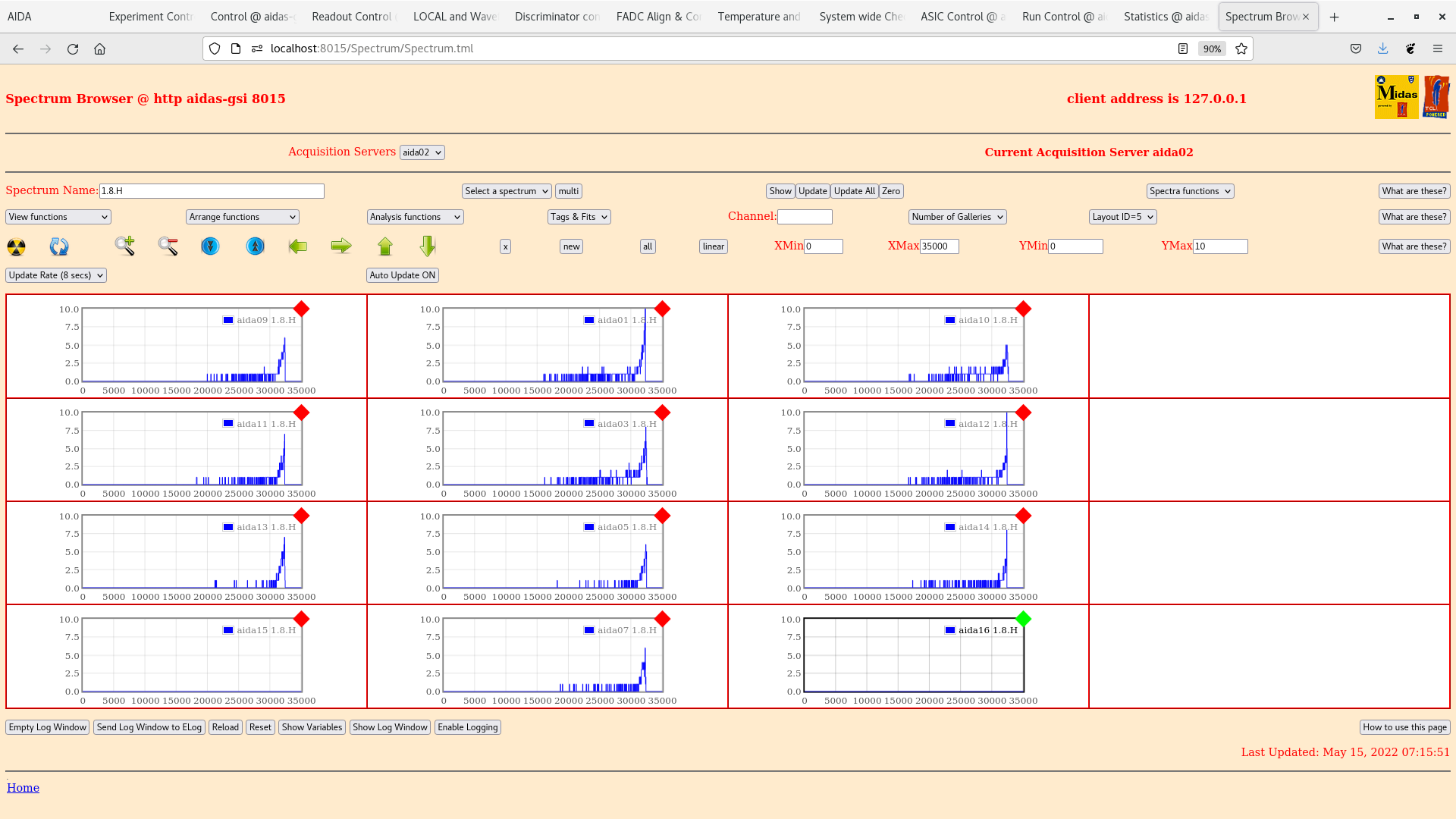

FEE statistics - Attachment 2

Bias and leakage currents ok - attachment 3

ASIC check ok

All system wide checks ok - Except aida09 fails clock check with bit 6

11:00 FEE statistics - attachment 4

FEE temperatures all ok - attachment 5

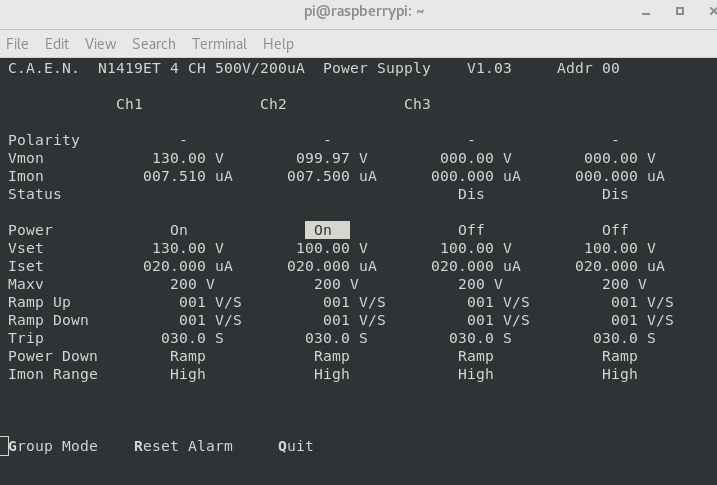

BIAS and leakage currents - attachment 6

ASIC check ok

All system wide checks as before

Currently on file R4_1030

13.1 MB/s to disk

4.8 million items per second

13:13 FEE statistics - attachment 7

FEE Temperatures all ok - attahcment 8

Bias and leakage currents ok - attachment 9

ASIC check ok

All system wide checks as before

Currently on file R4_1078

13.1 MB/s to disk

4.8 million items per second

15:35 Analysis of R4_1128 - attachment 10 |

| Attachment 1: Screenshot_from_2022-05-15_08-38-04.png

|

|

| Attachment 2: Screenshot_from_2022-05-15_08-38-34.png

|

|

| Attachment 3: Screenshot_from_2022-05-15_08-39-12.png

|

|

| Attachment 4: Screenshot_from_2022-05-15_11-00-32.png

|

|

| Attachment 5: Screenshot_from_2022-05-15_11-00-50.png

|

|

| Attachment 6: Screenshot_from_2022-05-15_11-01-02.png

|

|

| Attachment 7: Screenshot_from_2022-05-15_13-13-50.png

|

|

| Attachment 8: Screenshot_from_2022-05-15_13-14-12.png

|

|

| Attachment 9: Screenshot_from_2022-05-15_13-14-31.png

|

|

| Attachment 10: R4_1128

|

*** TDR format 3.3.0 analyser - TD - May 2021

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 259195371 ( 1637875.8 Hz)

Other data format: 2724629 ( 17217.1 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 2455 ( 15.5 Hz)

RESUME: 2456 ( 15.5 Hz)

SYNC100: 32590 ( 205.9 Hz)

WR48-63: 32590 ( 205.9 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 2654538 ( 16774.2 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 38026 ( 240.3 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 158.251 s

FEE elapsed dead time(s) elapsed idle time(s)

0 0.000 0.000

1 4.735 0.000

2 0.000 0.000

3 16.674 0.000

4 0.000 0.000

5 77.034 0.000

6 0.000 0.000

7 33.677 0.000

8 0.000 0.000

9 0.000 0.000

10 0.000 12.872

11 17.247 0.000

12 0.000 0.000

13 0.000 8.200

14 0.000 0.000

15 0.000 0.000

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 7464928 2802 0 0 0 0 927 927 0 948 0 661

1 38695355 10162 0 0 254 254 4827 4827 0 0 0 32843

2 6890959 1397581 0 0 0 0 1028 1028 0 1395525 0 633

3 41303989 1261446 0 0 398 398 5227 5227 0 1250196 0 331

4 4066993 1070 0 0 0 0 535 535 0 0 0 242

5 37291979 10883 0 0 737 738 4704 4704 0 0 0 222

6 12390385 7719 0 0 0 0 1626 1626 0 4467 0 394

7 42901955 15088 0 0 626 626 5217 5217 0 3402 0 167

8 10872099 2752 0 0 0 0 1376 1376 0 0 0 592

9 4061050 1014 0 0 0 0 507 507 0 0 0 432

10 2113468 548 0 0 0 0 274 274 0 0 0 291

11 41561869 11172 0 0 440 440 5146 5146 0 0 0 468

12 6798748 1722 0 0 0 0 861 861 0 0 0 436

13 2781594 670 0 0 0 0 335 335 0 0 0 314

14 0 0 0 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time: 33.348s ( 959.588 blocks/s, 59.974 Mb/s)

|

|

152

|

Sat Mar 14 23:09:28 2020 |

MB, SJ, MR | Sunday 15th March 0:00-8:00 |

AIDA ELog filled out by DESPEC night shift members Matthew Brunet (MB), Shaheen Jazrawi (SJ), and Matthias Rudiger (MR).

0:05-0:08 Beam operators altering settings, beam off/sporadic during this period.

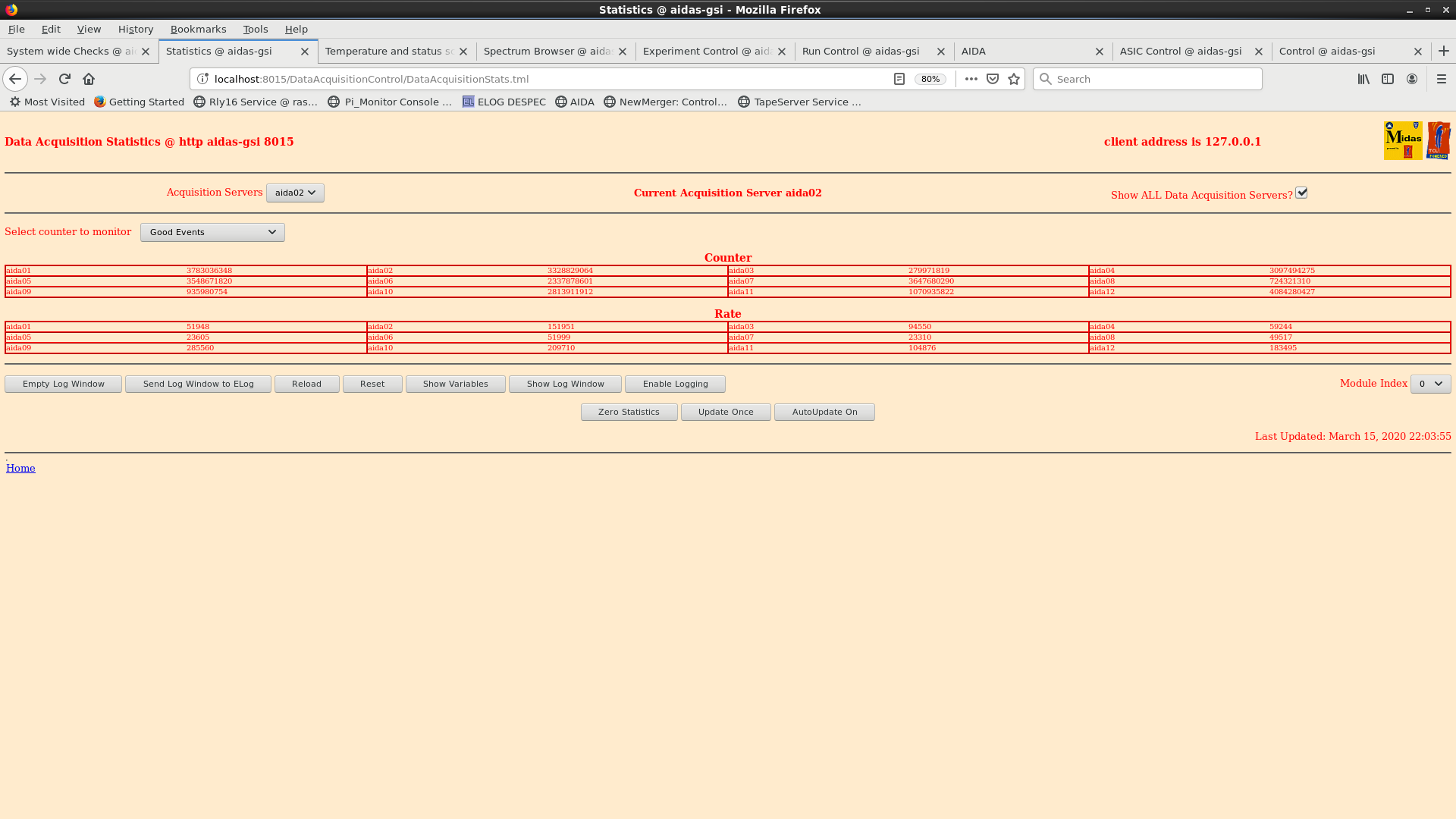

0:46

All system wide checks passed

Leak currents lower than previous measurement - attachment #1

Implants look as previously - attachment #2

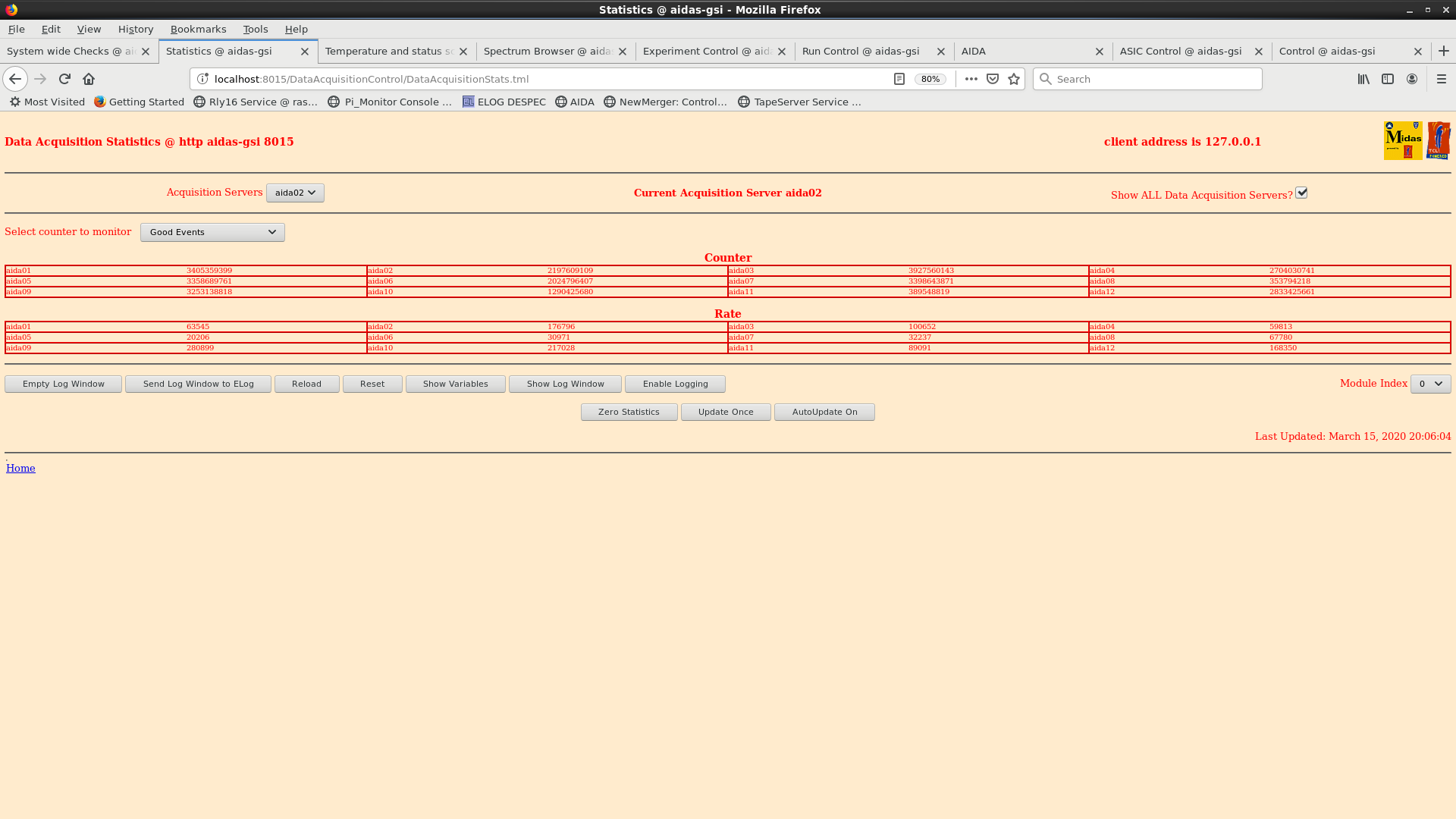

Stats about where they have been - attachment #3

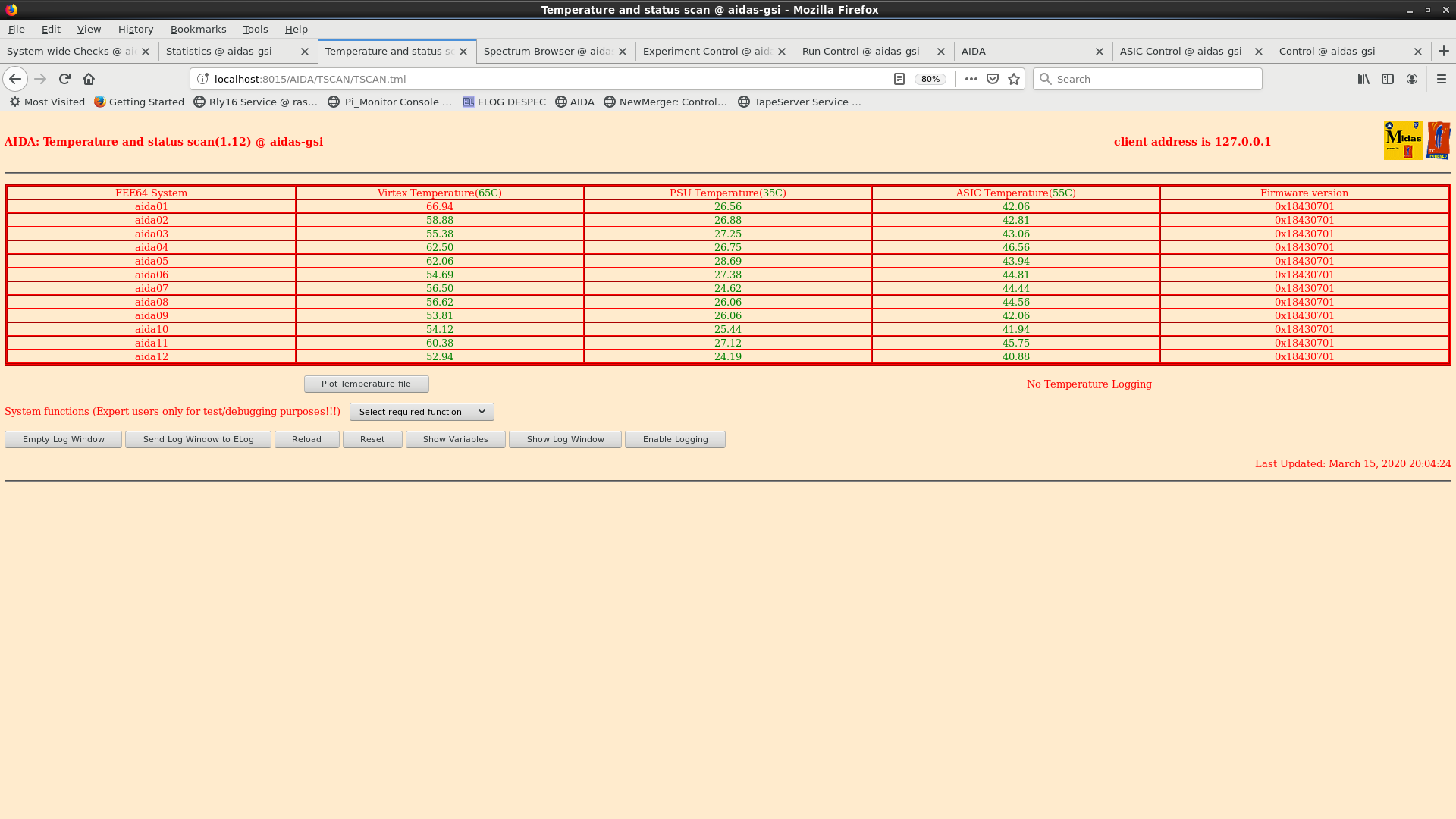

FEE temperatures fine - attachment #4

Merger fine, 3 Mega items / sec

TapeServer writing about 25 MB/s

2:46

All system wide checks passed

Leak currents similar to previous - attachment #5

Implants look as previously - attachment #6

Stats about where they have been - attachment #7

FEE temperatures fine - attachment #8

Merger fine, 3 Mega items / sec

TapeServer writing about 27 MB/s

4:49

All system wide checks passed

Leak currents similar to previous - attachment #9

Implants look as previously - attachment #10

Stats good - attachment #11

FEE temperatures fine - attachment #12

Merger fine, 3 Mega items / sec

TapeServer writing about 27 MB/s

6:49

All system wide checks passed

Leak currents no significant change - attachment #13

Implants look as previously - attachment #14

Stats good - attachment #15

FEE temperatures fine - attachment #16

Merger fine, 3 Mega items / sec

TapeServer writing about 25 MB/s |

| Attachment 1: Matt-15-BiasesA.png

|

|

| Attachment 2: Matt-15-HistosA.png

|

|

| Attachment 3: Matt-15-StatsA.png

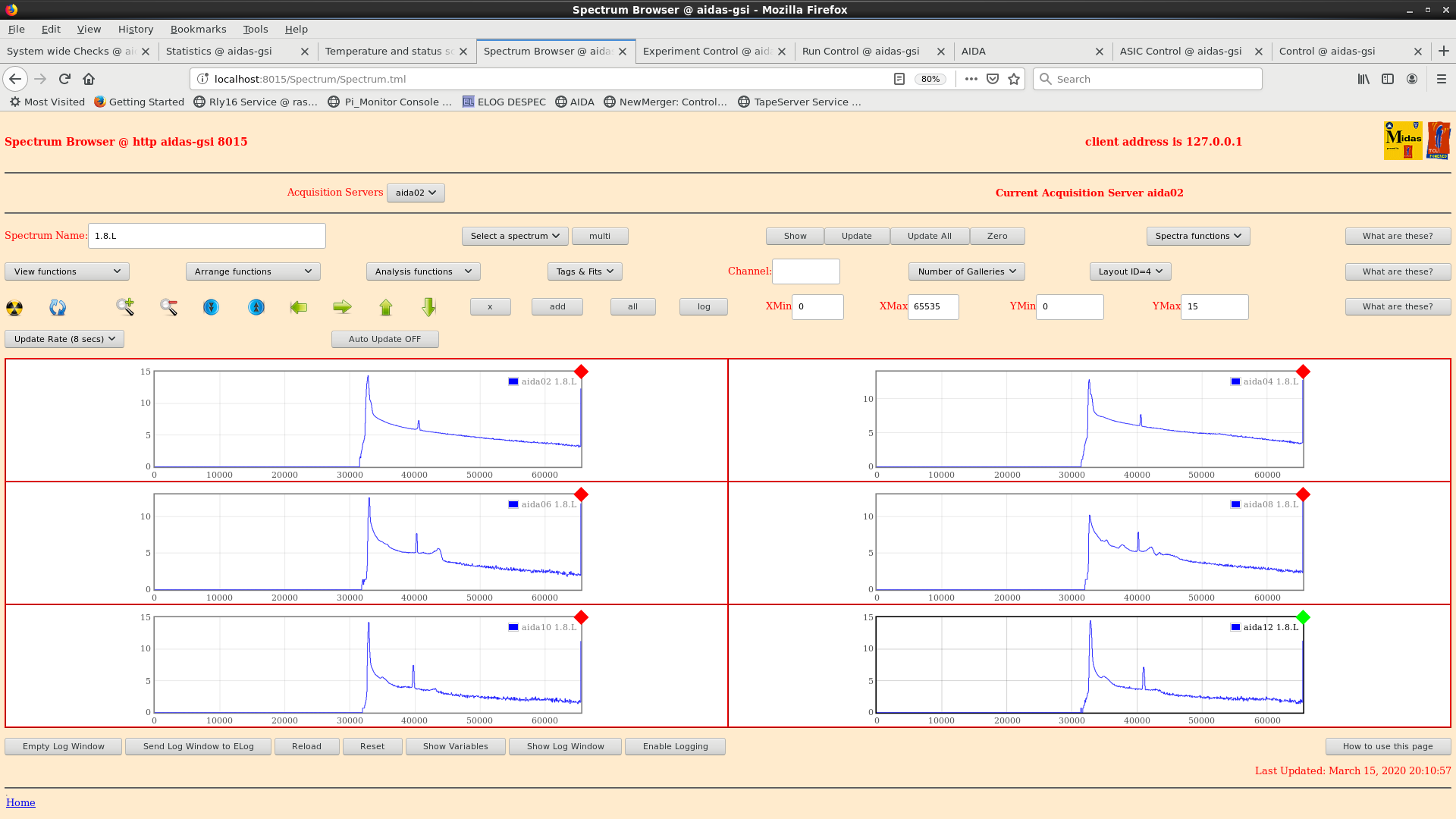

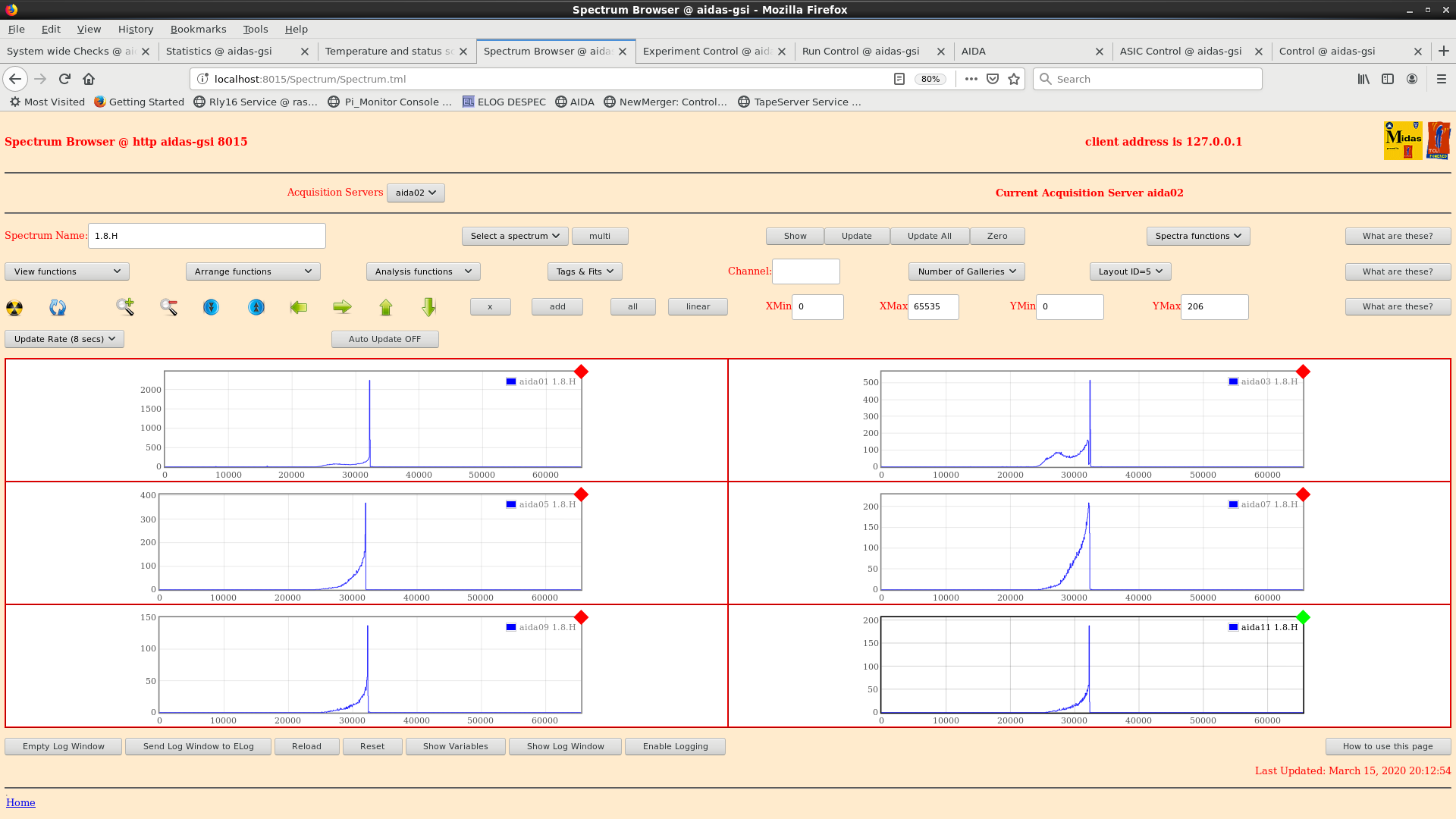

|

|

| Attachment 4: Matt-15-TempsA-.png

|

|

| Attachment 5: Matt-15-BiasesB.png

|

|

| Attachment 6: Matt-15-HistosB.png

|

|

| Attachment 7: Matt-15-StatsB.png

|

|

| Attachment 8: Matt-15-TempsB.png

|

|

| Attachment 9: Matt-15-BiasesC.png

|

|

| Attachment 10: Matt-15-HistosC.png

|

|

| Attachment 11: Matt-15-StatsC.png

|

|

| Attachment 12: Matt-15-TempsC.png

|

|

| Attachment 13: Matt-15-BiasesD.png

|

|

| Attachment 14: Matt-15-HistosD.png

|

|

| Attachment 15: Matt-15-StatsD.png

|

|

| Attachment 16: Matt-15-TempsD.png

|

|

|

153

|

Sun Mar 15 06:45:00 2020 |

CA, LS, CG | Sunday 15th March 08:00 - 24:00 |

ASIC settings 2019Oct31-13.24.23

slow comparator 0xa

BNC PB-5 pulser

amplitude 1.0V , attenuator x1

frequency 2Hz

decay time 1ms

07:46 all system wide checks ok

good event statistics ok - attachment 1

FEE64 temperatures ok - attachment 2

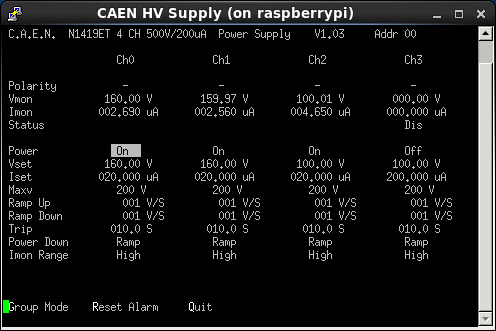

detector bias/leakage currents ok - attachment 3

08:48 merger ok ~ 3 million data items/s

TapeServer ok ~ 27 MB/s

data forwarding to MBS ok

08:50 AIDA writing to file SecondDrive/TapeData/S480/R12_1524

09:56 all system wide checks ok

good event statistics ok - attachment 4

detector bias/leakage currents ok - attachment 5

FEE64 temperatures ok - attachment 6

12:09 all system wide checks ok

12:13 all system wide checks ok

good event statistics ok - attachment 7

FEE64 temperatures ok - attachment 8

detector bias/leakage currents ok, but ramping up - attachment 9

13:32 merger ok ~ 3 million data items/s

TapeServer ok ~ 23 MB/s

data forwarding to MBS ok

Beam seems to be off

13:33 AIDA writing to file R12_1743

*update* checked DESPEC S480 Elog, issues with UNILAC, beam lost at 13:29

13:55 beam back

13:57 AIDA writing to file R12_1759

14:35 all system wide checks ok

FEE64 temperatures ok - attachment 10

good event statistics ok - attachment 11

detector bias/leakage currents ok, but ramping up - attachment 12

15:18 merger ok ~ 2.7 million data items/s

TapeServer ok ~ 27 MB/s

data forwarding to MBS ok

AIDA writing to file R12_1283

16:00 1.8.H high energy spectra - attachments 13 & 14

hit-rate spectra - attachment 15

16.22 all system wide checks okay

FEE temperatures okay (attachment 16)

leakage currents okay and recorded to spreadsheet (attachment 17)

good event stats okay (attachment 18)

merger running at 3M items/sec

tape service running at 26MB/sec

18.00 began compressing R7 files with command: nice -n 10 gzip -v R7_* &

all system wide checks okay

FEE temperatures okay (attachment 19)

leakage currents okay and recorded to spreadsheet (attachment 20)

good event stats okay (attachment 21)

merger running at 3M items/sec

tape service running at 27MB/sec

20.10 all system wide checks okay

FEE temperatures okay (attachment 22)

leakage currents okay and recorded to spreadsheet, detectors 1 and 2 still rising (attachment 23)

good event stats okay (attachment 24)

merger running at 3M items/sec

tape service running at 25MB/sec

rates histogram (attachment 25)

low energy histograms (attachment 26 and 27)

high energy histograms (attachments 28 and 29)

22.07 all system wide checks okay

FEE temperatures okay (attachment 30)

leakage currents okay and recorded to spreadsheet (attachment 31)

good event stats okay (attachment 32)

merger running at 3M items/sec

tape service running at 25MB/sec

currently on R12_2097

23.56 all system wide checks okay

FEE temperatures okay (attachment 33)

leakage currents okay and recorded to spreadsheet (attachment 34)

good event stats okay (attachment 35)

merger running at 3M items/sec

tape service running at 26MB/sec

finishing up now. night shift group have been informed how to check up on AIDA, there is a sheet on the table with relevant information

|

| Attachment 1: 200315_0749_stats.png

|

|

| Attachment 2: 200315_0749_temp.png

|

|

| Attachment 3: 200315_0750_bias.png

|

|

| Attachment 4: 200315_0956_stats.png

|

|

| Attachment 5: 200315_0957_bias.png

|

|

| Attachment 6: 200315_0957_temp.png

|

|

| Attachment 7: 200315_1210_stats.png

|

|

| Attachment 8: 200315_1211_temp.png

|

|

| Attachment 9: 200315_1212_bias.png

|

|

| Attachment 10: corrigan_temperature.png

|

|

| Attachment 11: corrigan_stats.png

|

|

| Attachment 12: corrigan_bias.png

|

|

| Attachment 13: corriganhe1.png

|

|

| Attachment 14: corriganhe2.png

|

|

| Attachment 15: 200315_1553_rates.png

|

|

| Attachment 16: 200315_1619_feetemps.png

|

|

| Attachment 17: 200315_1620_leakagecurrents.png

|

|

| Attachment 18: 200315_1620_goodevents.png

|

|

| Attachment 19: 200315_1758_feetemps.png

|

|

| Attachment 20: 200315_1759_leakagecurrents.png

|

|

| Attachment 21: 200315_1758_goodevents.png

|

|

| Attachment 22: 200315_2004_feetemps.png

|

|

| Attachment 23: 200315_2007_leakagecurrents#.png

|

|

| Attachment 24: 200315_2006_goodevents.png

|

|

| Attachment 25: 200315_2009_rates.png

|

|

| Attachment 26: 200315_2010_lowodd.png

|

|

| Attachment 27: 200315_2011_loweven.png

|

|

| Attachment 28: 200315_2012_highodd.png

|

|

| Attachment 29: 200315_2014_higheven.png

|

|

| Attachment 30: 200315_2202_feetemps.png

|

|

| Attachment 31: 200315_2203_leakagecurrents.png

|

|

| Attachment 32: 200315_2204_goodevents.png

|

|

| Attachment 33: 200315_2358_FEETEMPS.png

|

|

| Attachment 34: 200315_2358LEAKAGECURRENTS.png

|

|

| Attachment 35: 200315_2359_goodevents.png

|

|

|

455

|

Sat May 14 23:02:33 2022 |

TD | Sunday 15 May 00:00-08:00 |

Pb beam c. 1e+9/spill

00.02 zero all histograms

system wide checks - baseline counters

00.08 ASIC check control - all FEE64s, all ASICs

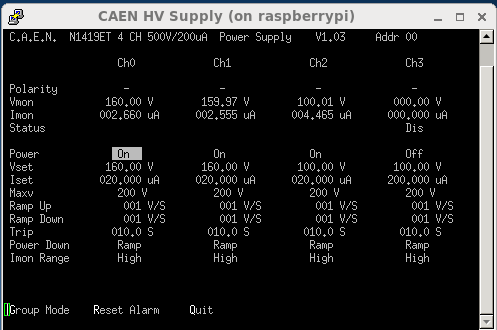

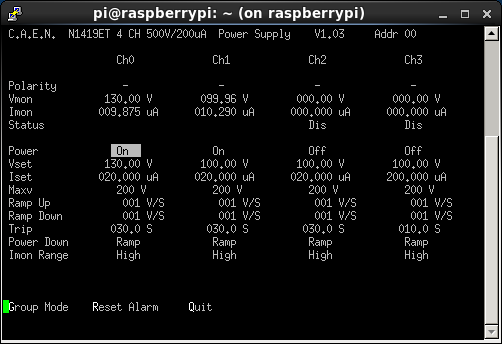

Attachment 1 - grafana DSSSD bias, leakage current & temp - OK

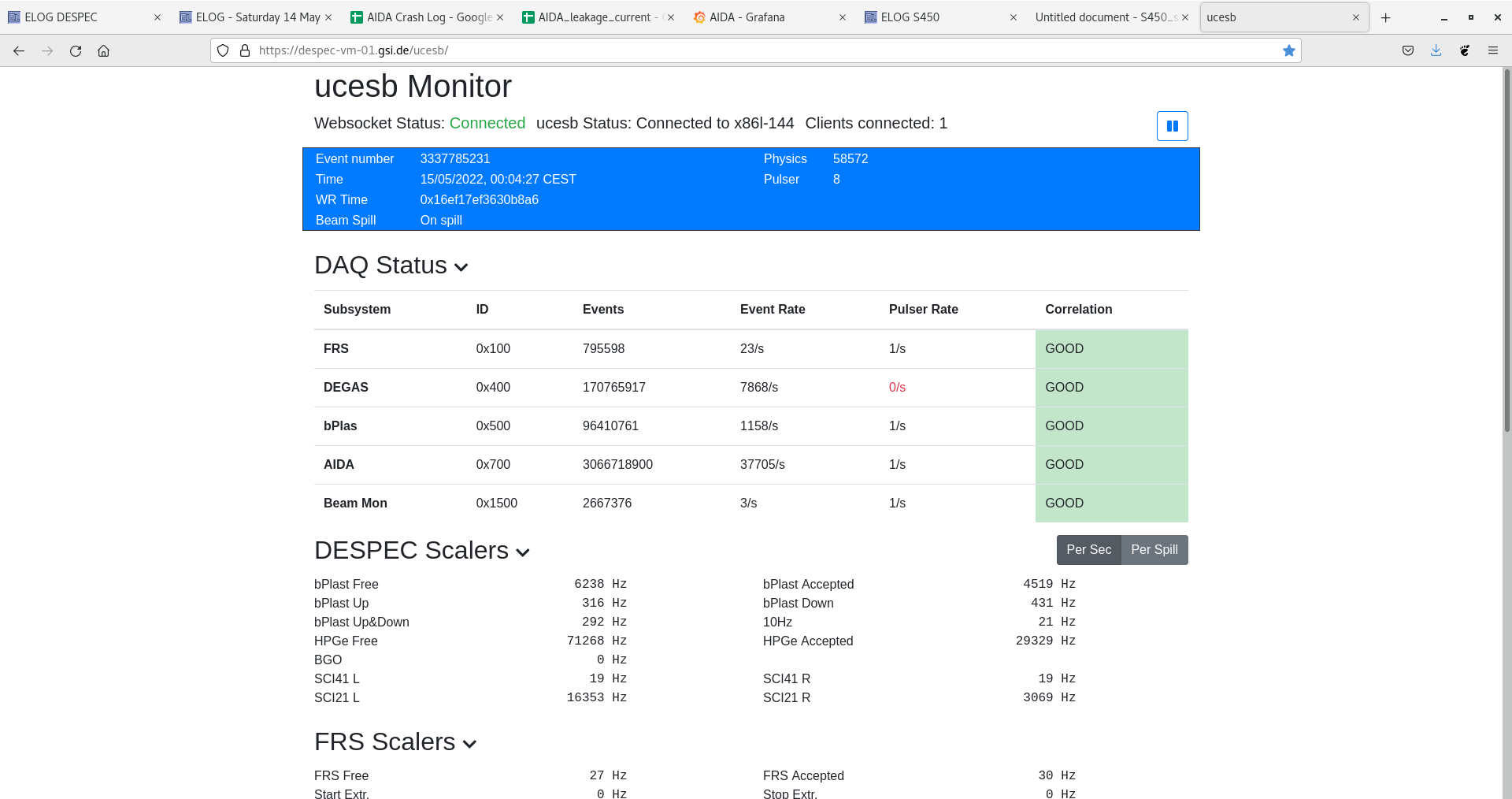

Attachments 2 & 3 - ucesb - AIDA DSSSD #1 c. 10-20Hz peak rate on spill, c. 0Hz off spill

Attachment 4 - DSSSD bias & Leakage current - OK

Attachment 5 - FEE64 temps OK

Attachment 6-13 - adc, pause, resume & correlation scaler data items, push, flush, aida01, aida06

Attachments 14-18 - system wide checks - all OK *except* aida09 clock fail status 6

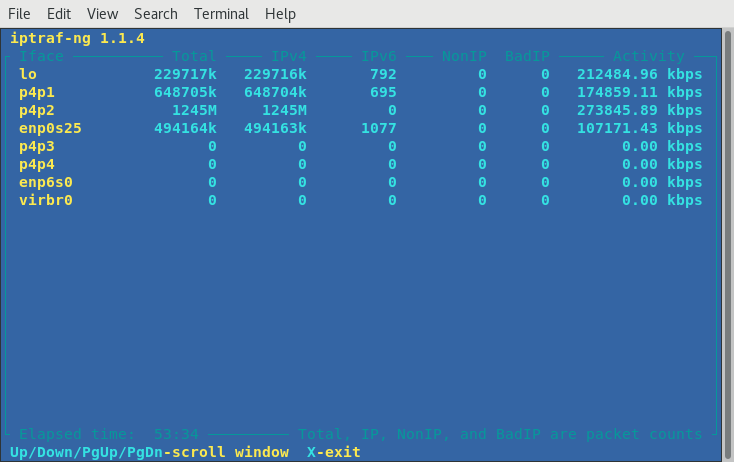

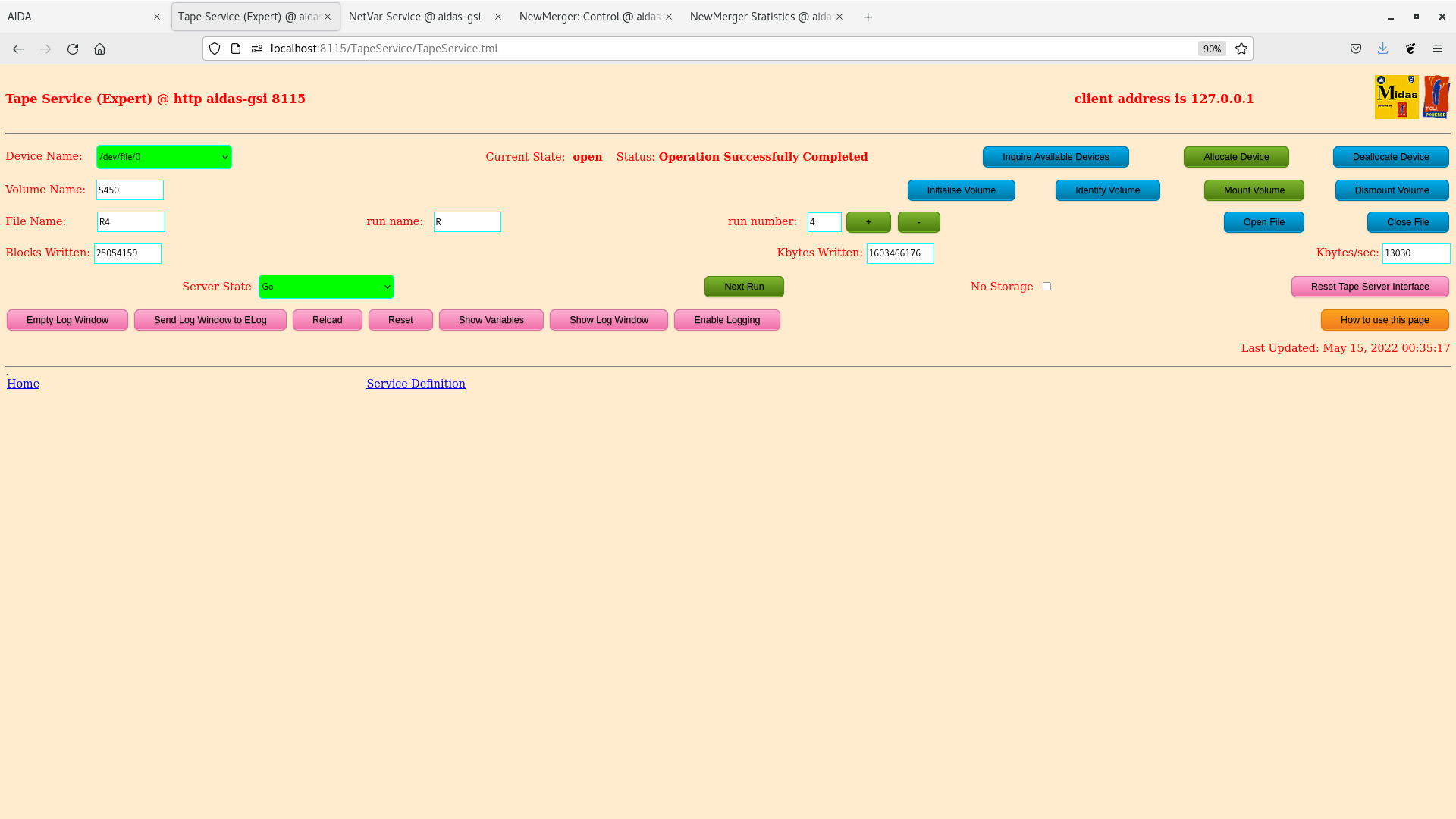

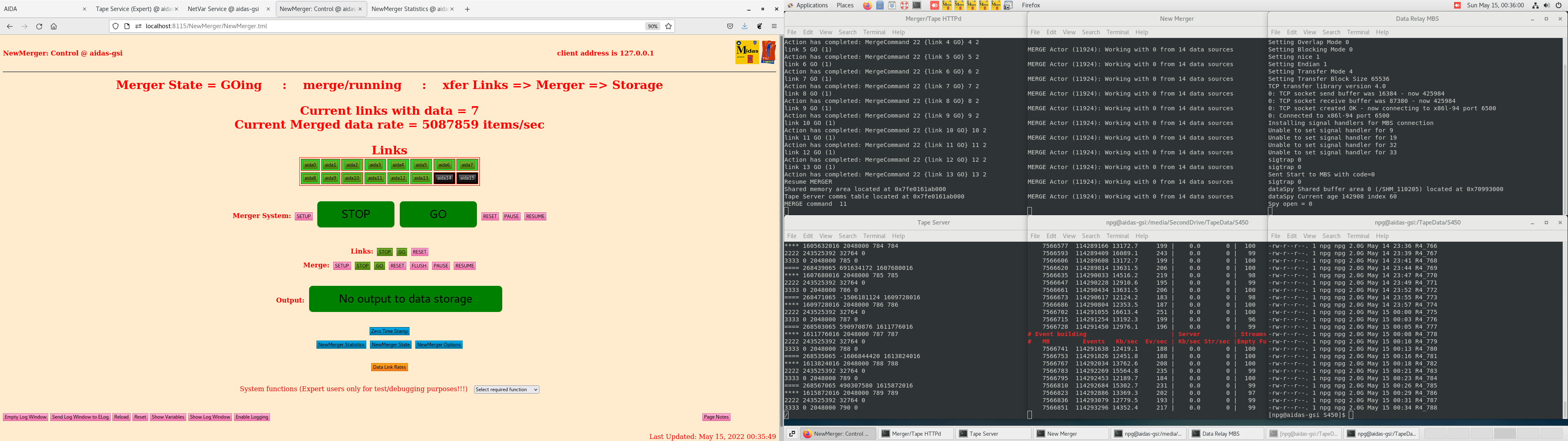

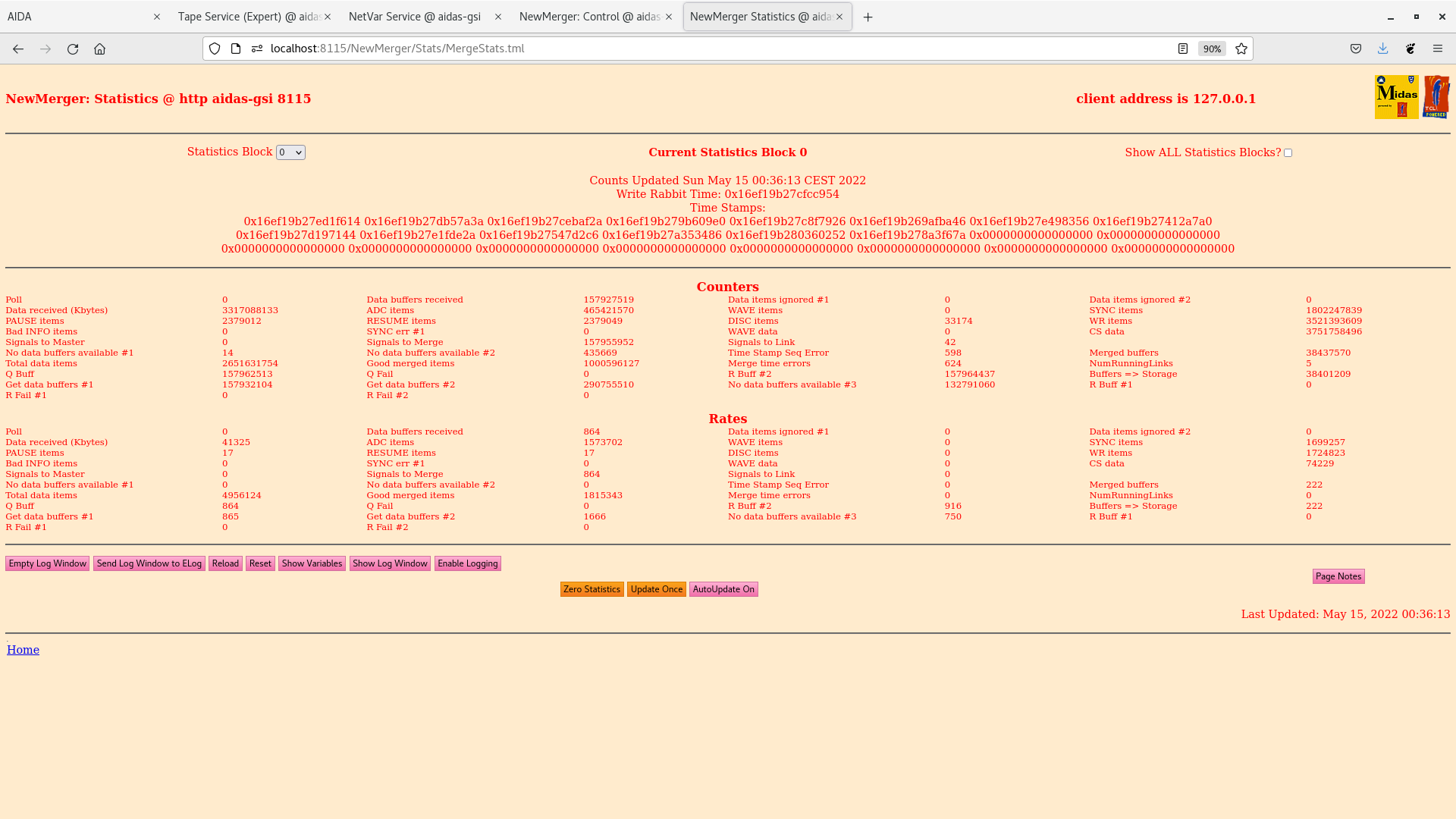

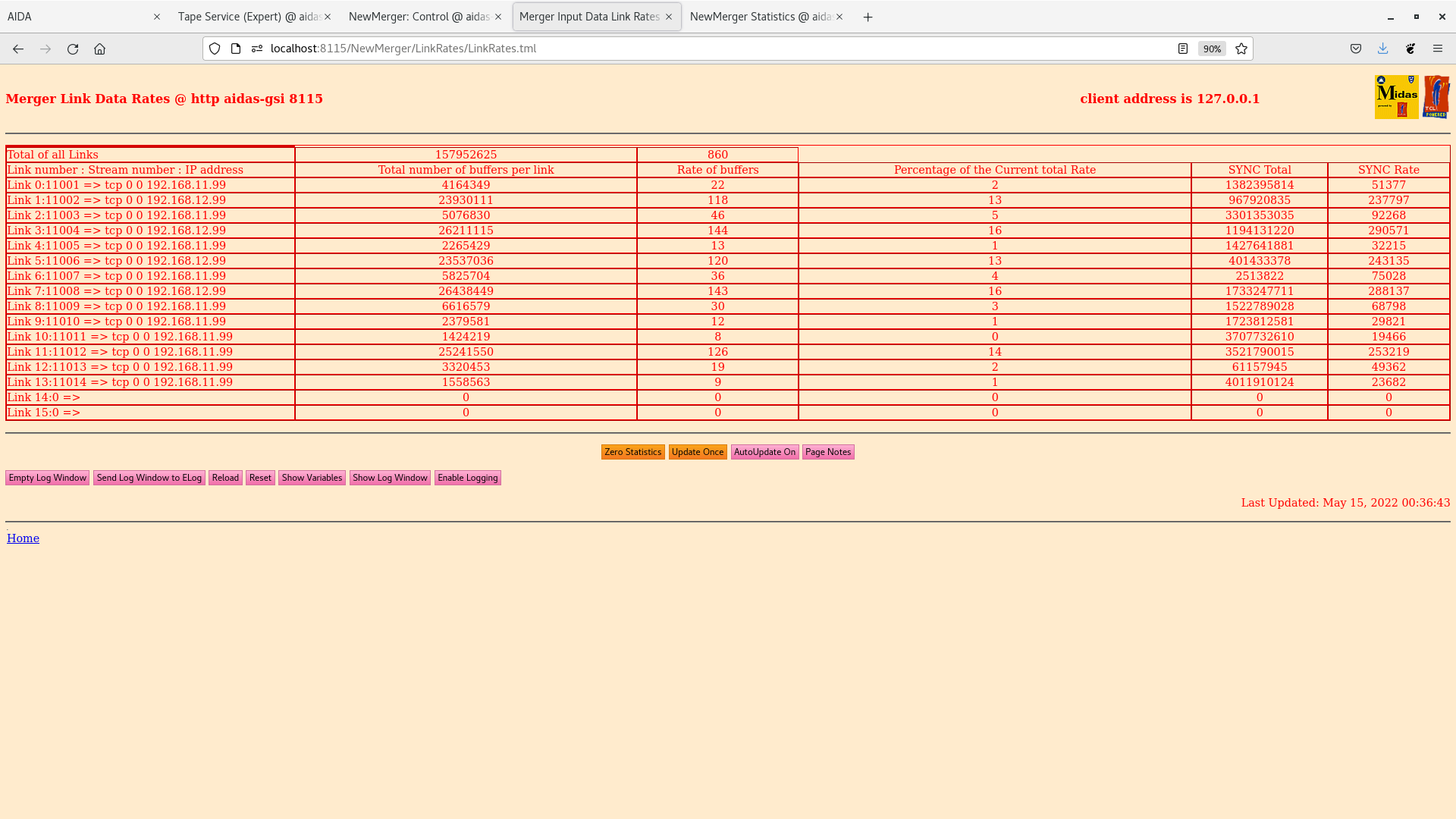

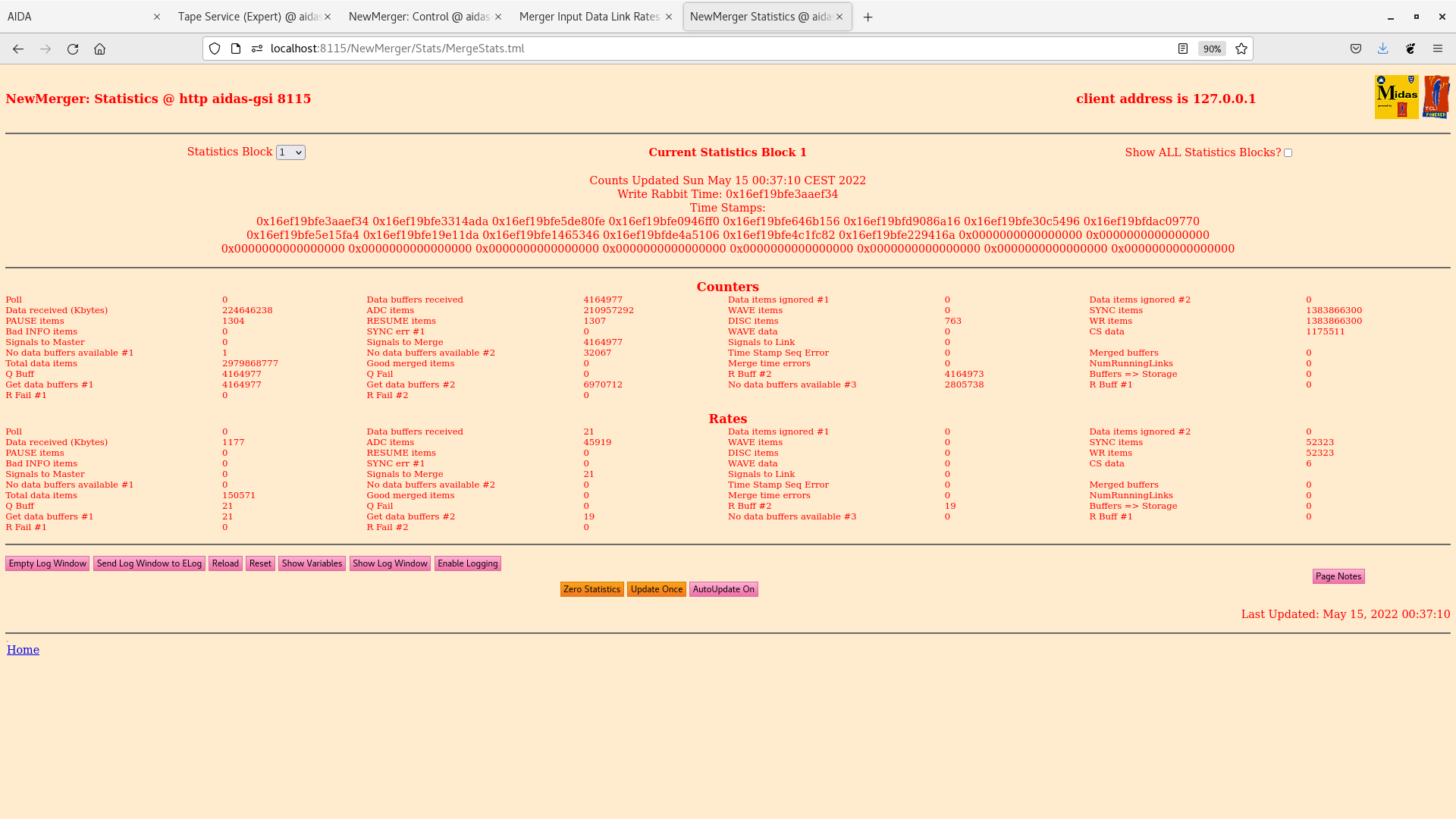

Attachments 19-25 - iptraf, TapeServer, NewMerger, NewMerger stats

00.44 file S450/R4_792

ADC control register 0xff

all disc outputs disabled

ASIC settings 2021Apr29-13-16-00

slow comparator aida02 & aida04 0x16, aida06 & aida08 0x23, aida12 0xd, all others 0xc

BNC PB-5 settings

amplitude 1.000V

attenuation x1

tau_d 1ms

frequency 2Hz

polarity +

00.51 disk space OK - c. 3' per data file

[npg@aidas-gsi S450]$ ls -l /

total 40

lrwxrwxrwx. 1 root root 7 Oct 18 2021 bin -> usr/bin

dr-xr-xr-x. 5 root root 4096 May 12 18:31 boot

drwxr-xr-x. 23 root root 4100 May 12 18:31 dev

drwxr-xr-x. 145 root root 8192 May 12 18:31 etc

drwxr-xr-x. 4 root root 56 Jan 28 14:56 home

lrwxrwxrwx. 1 root root 7 Oct 18 2021 lib -> usr/lib

lrwxrwxrwx. 1 root root 9 Oct 18 2021 lib64 -> usr/lib64

drwxr-xr-x. 5 root root 113 Apr 28 11:58 media

lrwxrwxrwx. 1 root root 45 Oct 18 2021 MIDAS -> /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119

drwxr-xr-x. 2 root root 6 Apr 11 2018 mnt

drwxr-xr-x. 3 root root 16 Oct 18 2021 opt

dr-xr-xr-x. 464 root root 0 May 12 18:30 proc

dr-xr-x---. 10 root root 4096 May 13 11:47 root

drwxr-xr-x. 44 root root 1360 May 14 06:34 run

lrwxrwxrwx. 1 root root 8 Oct 18 2021 sbin -> usr/sbin

drwxr-xr-x. 2 root root 6 Apr 11 2018 srv

dr-xr-xr-x. 13 root root 0 May 12 18:31 sys

lrwxrwxrwx. 1 root root 28 Apr 28 14:19 TapeData -> /media/SecondDrive/TapeData/

drwxrwxrwt. 40 root root 12288 May 15 00:49 tmp

drwxr-xr-x. 13 root root 155 Oct 18 2021 usr

drwxr-xr-x. 21 root root 4096 Oct 18 2021 var

[npg@aidas-gsi S450]$ df -h

Filesystem Size Used Avail Use% Mounted on

devtmpfs 7.8G 0 7.8G 0% /dev

tmpfs 7.8G 373M 7.4G 5% /dev/shm

tmpfs 7.8G 19M 7.7G 1% /run

tmpfs 7.8G 0 7.8G 0% /sys/fs/cgroup

/dev/mapper/centos-root 50G 16G 35G 31% /

/dev/sda2 1014M 226M 789M 23% /boot

/dev/sda1 200M 12M 189M 6% /boot/efi

/dev/sde1 7.2T 3.1T 3.8T 46% /media/SecondDrive

/dev/mapper/centos-home 407G 91G 316G 23% /home

tmpfs 1.6G 52K 1.6G 1% /run/user/1000

/dev/sdd1 7.2T 6.5T 310G 96% /run/media/npg/ThirdDrive

Attachment 26 - analysis data file R4_792

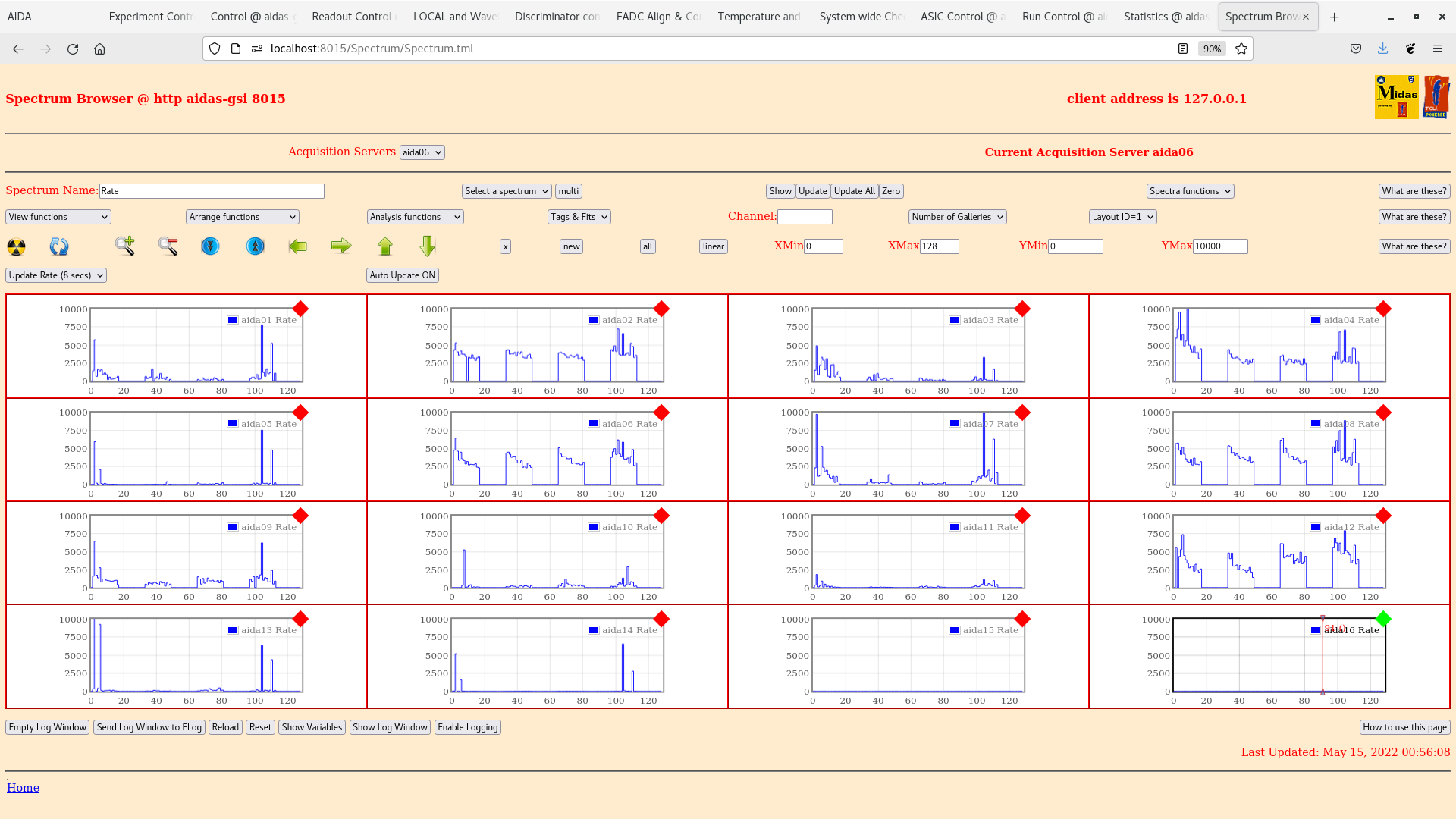

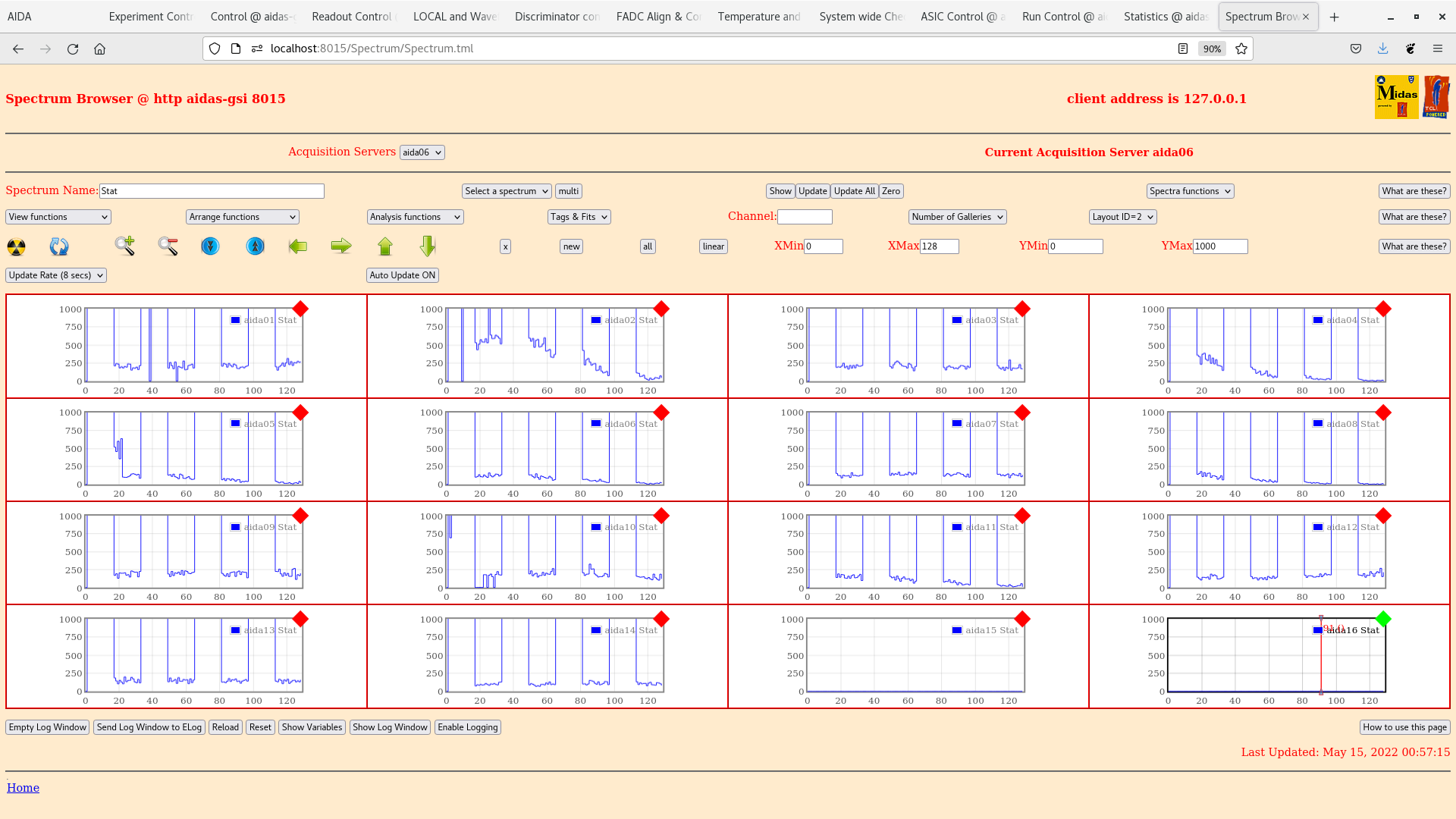

Attachments 27-28 - per FEE64 rate & stat spectra - shows distro HEC events

Attachments 29-30 - per FEE64 1.8.L spectra

pulser peak widths aida01 134 ch FWHM, aida04 393 ch FWHM

Attachments 31-32 - per FEE64 1.8.H spectra

Attachments 33-34 - aida02 & aida04 1.*.H spectra

04.13

Attachment 35 - DSSSD bias & Leakage current - OK

Attachment 36 - FEE64 temps OK

Attachment 37 - adc data item stats

Attachments 38 - ucesb

system wide checks - all OK *except* aida09 clock fail status 6

07.05

Attachment 39 - DSSSD bias & Leakage current - OK

Attachment 40 - FEE64 temps OK

Attachment 41 - adc data item stats

Attachments 42 - ucesb

system wide checks - all OK *except* aida09 clock fail status 6

Attachments 43-48 - aida02 & aida04 & aida06 & aida08 & 1.*.H spectra |

| Attachment 1: Screenshot_from_2022-05-15_00-03-33.png

|

|

| Attachment 2: Screenshot_from_2022-05-15_00-03-58.png

|

|

| Attachment 3: Screenshot_from_2022-05-15_00-04-18.png

|

|

| Attachment 4: Screenshot_from_2022-05-15_00-04-39.png

|

|

| Attachment 5: Screenshot_from_2022-05-15_00-05-10.png

|

|

| Attachment 6: Screenshot_from_2022-05-15_00-07-25.png

|

|

| Attachment 7: Screenshot_from_2022-05-15_00-16-59.png

|

|

| Attachment 8: Screenshot_from_2022-05-15_00-17-52.png

|

|

| Attachment 9: Screenshot_from_2022-05-15_00-18-55.png

|

|

| Attachment 10: Screenshot_from_2022-05-15_00-19-35.png

|

|

| Attachment 11: Screenshot_from_2022-05-15_00-20-14.png

|

|

| Attachment 12: Screenshot_from_2022-05-15_00-20-57.png

|

|

| Attachment 13: Screenshot_from_2022-05-15_00-21-32.png

|

|

| Attachment 14: Screenshot_from_2022-05-15_00-26-13.png

|

|

| Attachment 15: Screenshot_from_2022-05-15_00-26-49.png

|

|

| Attachment 16: Screenshot_from_2022-05-15_00-27-19.png

|

|

| Attachment 17: Screenshot_from_2022-05-15_00-28-00.png

|

|

| Attachment 18: Screenshot_from_2022-05-15_00-28-45.png

|

|

| Attachment 19: Screenshot_from_2022-05-15_00-33-46.png

|

|

| Attachment 20: Screenshot_from_2022-05-15_00-35-33.png

|

|

| Attachment 21: Screenshot_from_2022-05-15_00-36-00.png

|

|

| Attachment 22: Screenshot_from_2022-05-15_00-36-26.png

|

|

| Attachment 23: Screenshot_from_2022-05-15_00-36-58.png

|

|

| Attachment 24: Screenshot_from_2022-05-15_00-37-25.png

|

|

| Attachment 25: Screenshot_from_2022-05-15_00-37-46.png

|

|

| Attachment 26: R4_792

|

*** TDR format 3.3.0 analyser - TD - May 2021

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 250102849 ( 1597022.2 Hz)

Other data format: 11817151 ( 75458.0 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 2692 ( 17.2 Hz)

RESUME: 2692 ( 17.2 Hz)

SYNC100: 32584 ( 208.1 Hz)

WR48-63: 32584 ( 208.1 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 11746599 ( 75007.5 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 48170 ( 307.6 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 156.606 s

FEE elapsed dead time(s) elapsed idle time(s)

0 0.000 0.000

1 6.802 0.000

2 0.000 0.000

3 28.710 0.000

4 0.000 0.000

5 76.548 0.000

6 0.000 0.000

7 36.670 0.000

8 0.002 0.000

9 0.000 0.000

10 0.000 14.137

11 20.418 0.000

12 0.000 0.000

13 0.000 3.327

14 0.000 0.000

15 0.000 0.000

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 7219269 2805 0 0 0 0 933 933 0 939 0 589

1 37816150 10006 0 0 269 269 4734 4734 0 0 0 43094

2 6973157 6465448 0 0 0 0 1676 1676 0 6462096 0 570

3 37723722 5287878 0 0 579 580 5326 5326 0 5276067 0 352

4 3982759 1044 0 0 0 0 522 522 0 0 0 233

5 36626106 10369 0 0 747 746 4438 4438 0 0 0 211

6 11915365 7321 0 0 0 0 1544 1544 0 4233 0 403

7 42135728 15066 0 0 653 653 5248 5248 0 3264 0 174

8 10616770 2532 0 0 2 2 1264 1264 0 0 0 570

9 3975235 966 0 0 0 0 483 483 0 0 0 497

10 2072466 538 0 0 0 0 269 269 0 0 0 289

11 40106886 10836 0 0 442 442 4976 4976 0 0 0 472

12 6251481 1636 0 0 0 0 818 818 0 0 0 413

13 2687755 706 0 0 0 0 353 353 0 0 0 303

14 0 0 0 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time: 36.205s ( 883.854 blocks/s, 55.241 Mb/s)

|

| Attachment 27: Screenshot_from_2022-05-15_00-56-27.png

|

|

| Attachment 28: Screenshot_from_2022-05-15_00-57-44.png

|

|

| Attachment 29: Screenshot_from_2022-05-15_00-59-12.png

|

|

| Attachment 30: Screenshot_from_2022-05-15_01-02-36.png

|

|

| Attachment 31: Screenshot_from_2022-05-15_01-04-44.png

|

|

| Attachment 32: Screenshot_from_2022-05-15_01-05-49.png

|

|

| Attachment 33: Screenshot_from_2022-05-15_01-13-22.png

|

|

| Attachment 34: Screenshot_from_2022-05-15_01-15-01.png

|

|

| Attachment 35: Screenshot_from_2022-05-15_04-13-03.png

|

|

| Attachment 36: Screenshot_from_2022-05-15_04-13-31.png

|

|

| Attachment 37: Screenshot_from_2022-05-15_04-13-52.png

|

|

| Attachment 38: Screenshot_from_2022-05-15_04-14-31.png

|

|

| Attachment 39: Screenshot_from_2022-05-15_07-05-19.png

|

|

| Attachment 40: Screenshot_from_2022-05-15_07-05-50.png

|

|

| Attachment 41: Screenshot_from_2022-05-15_07-06-15.png

|

|

| Attachment 42: Screenshot_from_2022-05-15_07-06-42.png

|

|

| Attachment 43: Screenshot_from_2022-05-15_07-06-42.png

|

|

| Attachment 44: Screenshot_from_2022-05-15_07-12-37.png

|

|

| Attachment 45: Screenshot_from_2022-05-15_07-14-49.png

|

|

| Attachment 46: Screenshot_from_2022-05-15_07-16-18.png

|

|

| Attachment 47: Screenshot_from_2022-05-15_07-20-47.png

|

|

| Attachment 48: Screenshot_from_2022-05-15_07-22-02.png

|

|

|

706

|

Sun Jun 15 10:53:08 2025 |

TD | Sunday 15 June 2025 |

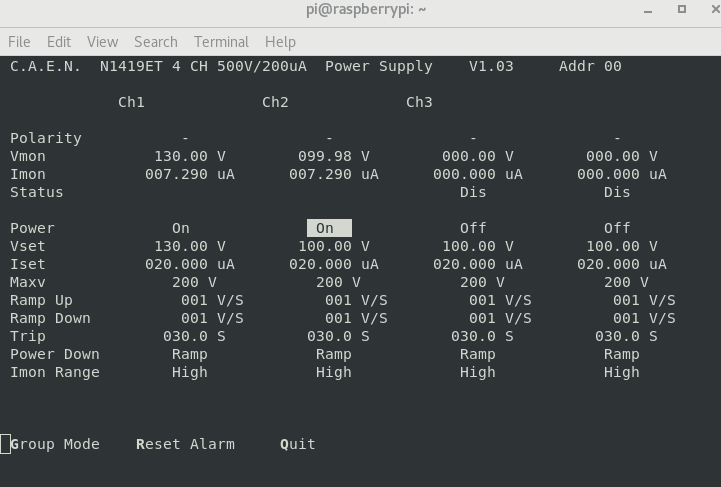

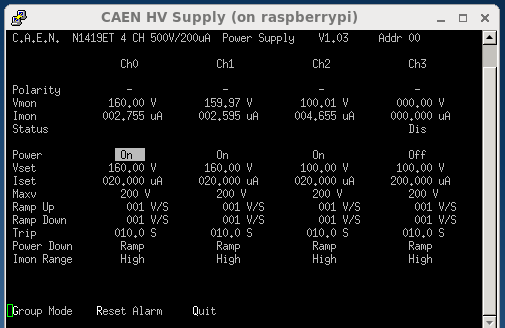

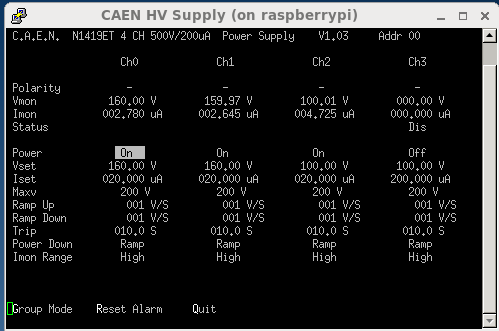

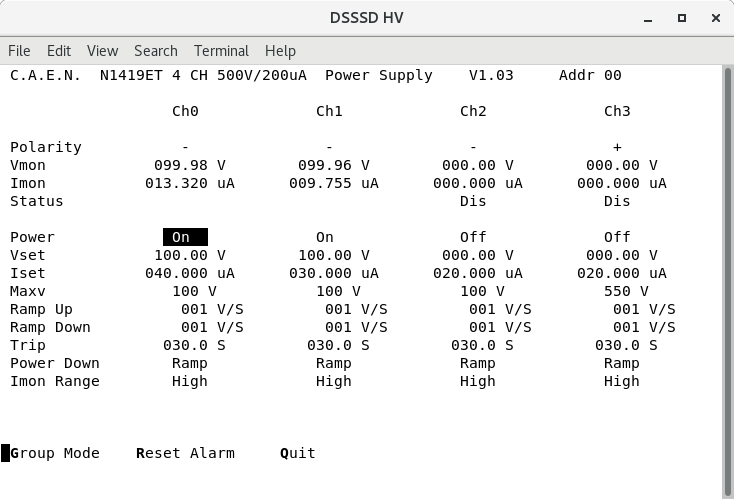

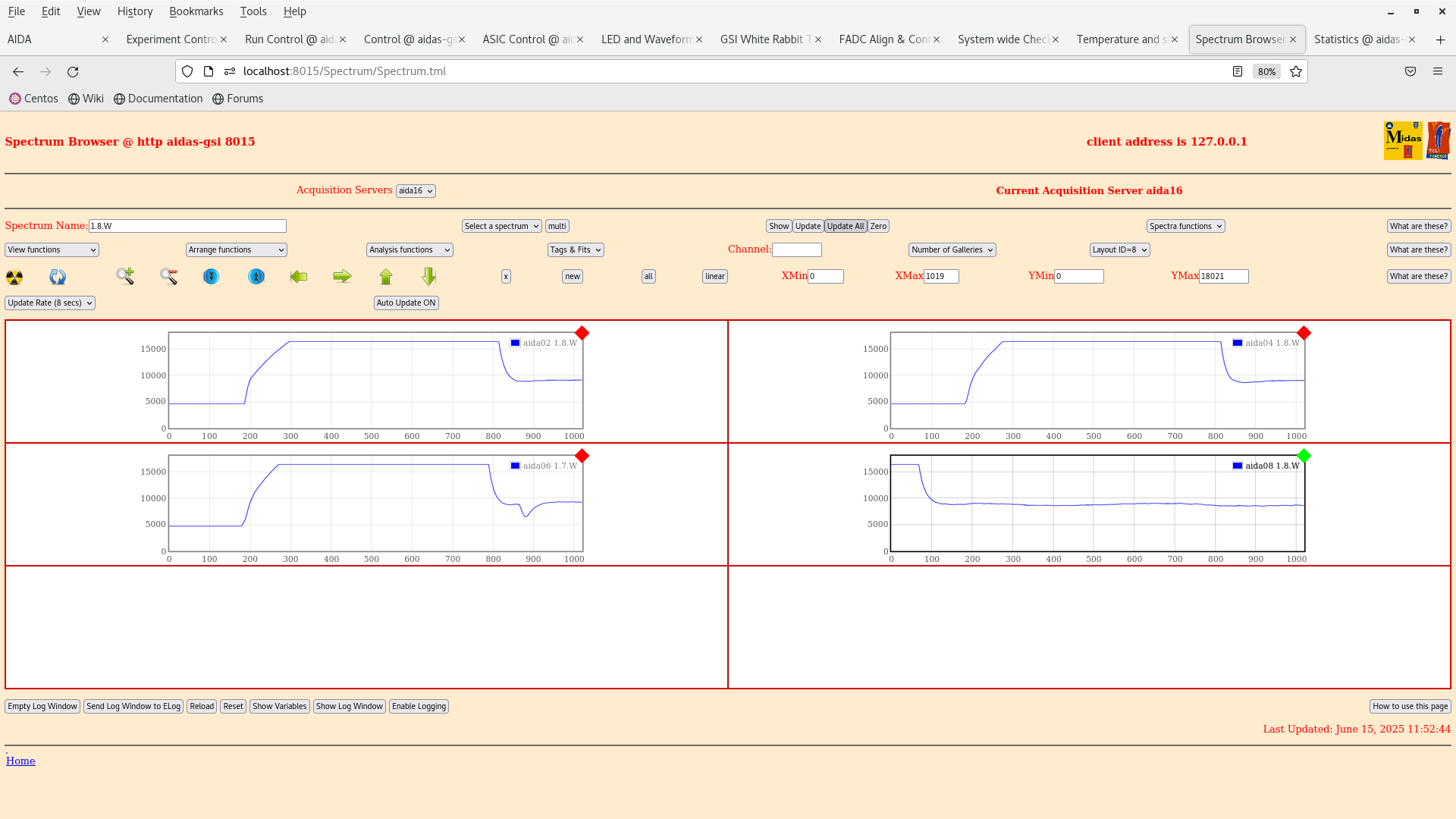

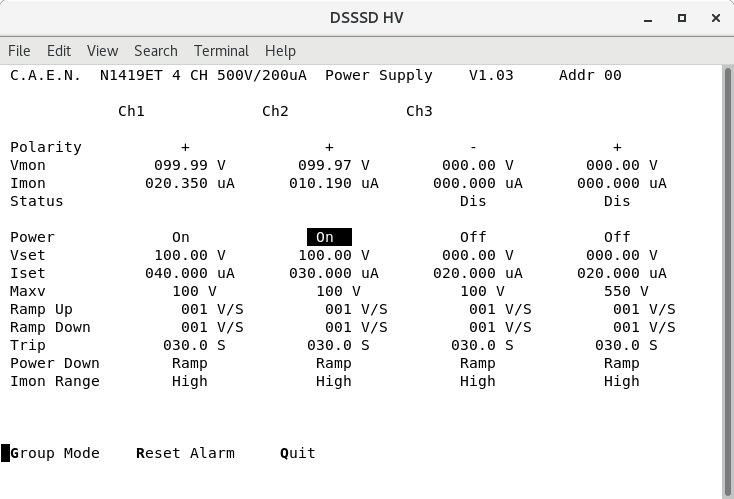

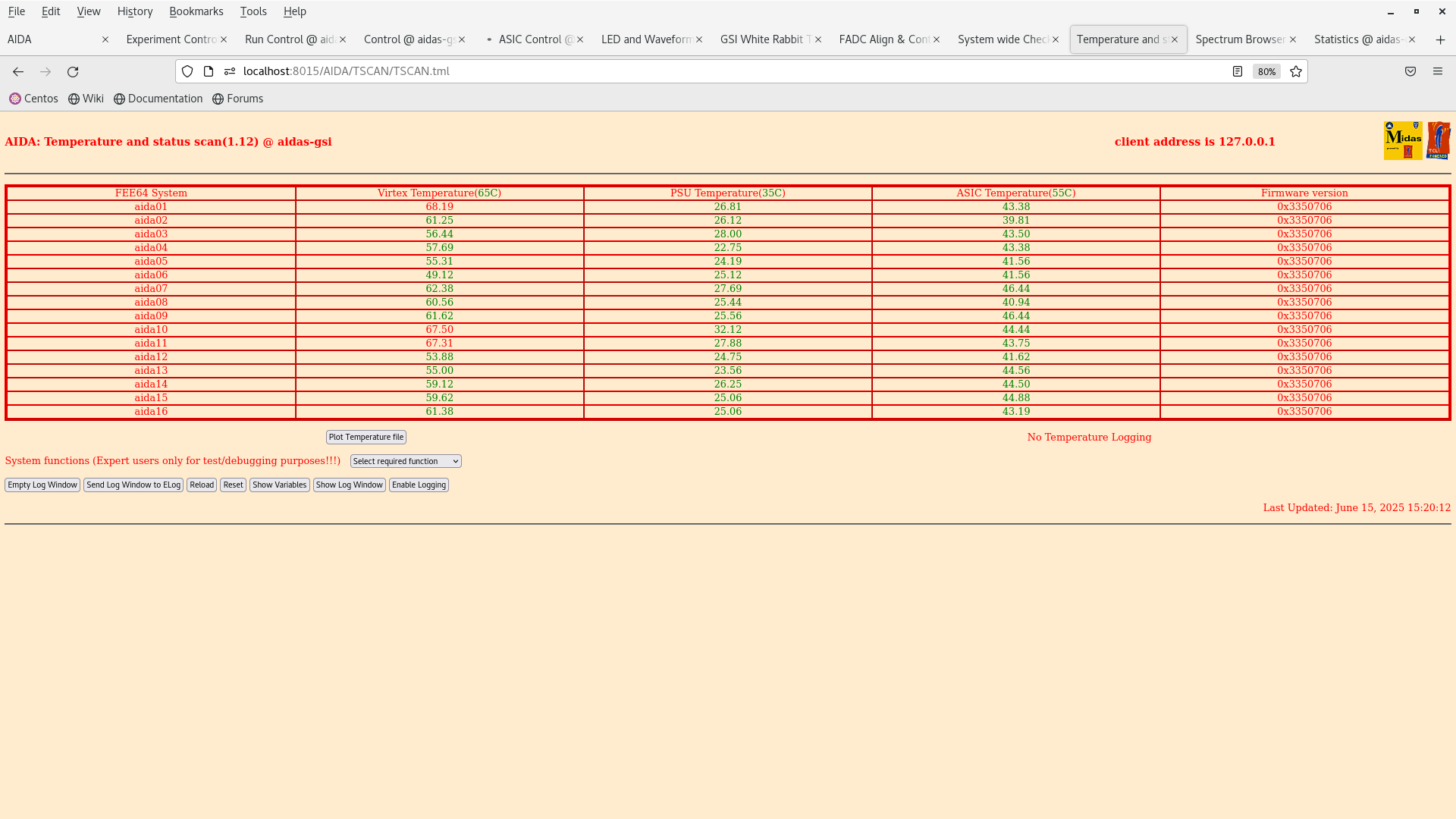

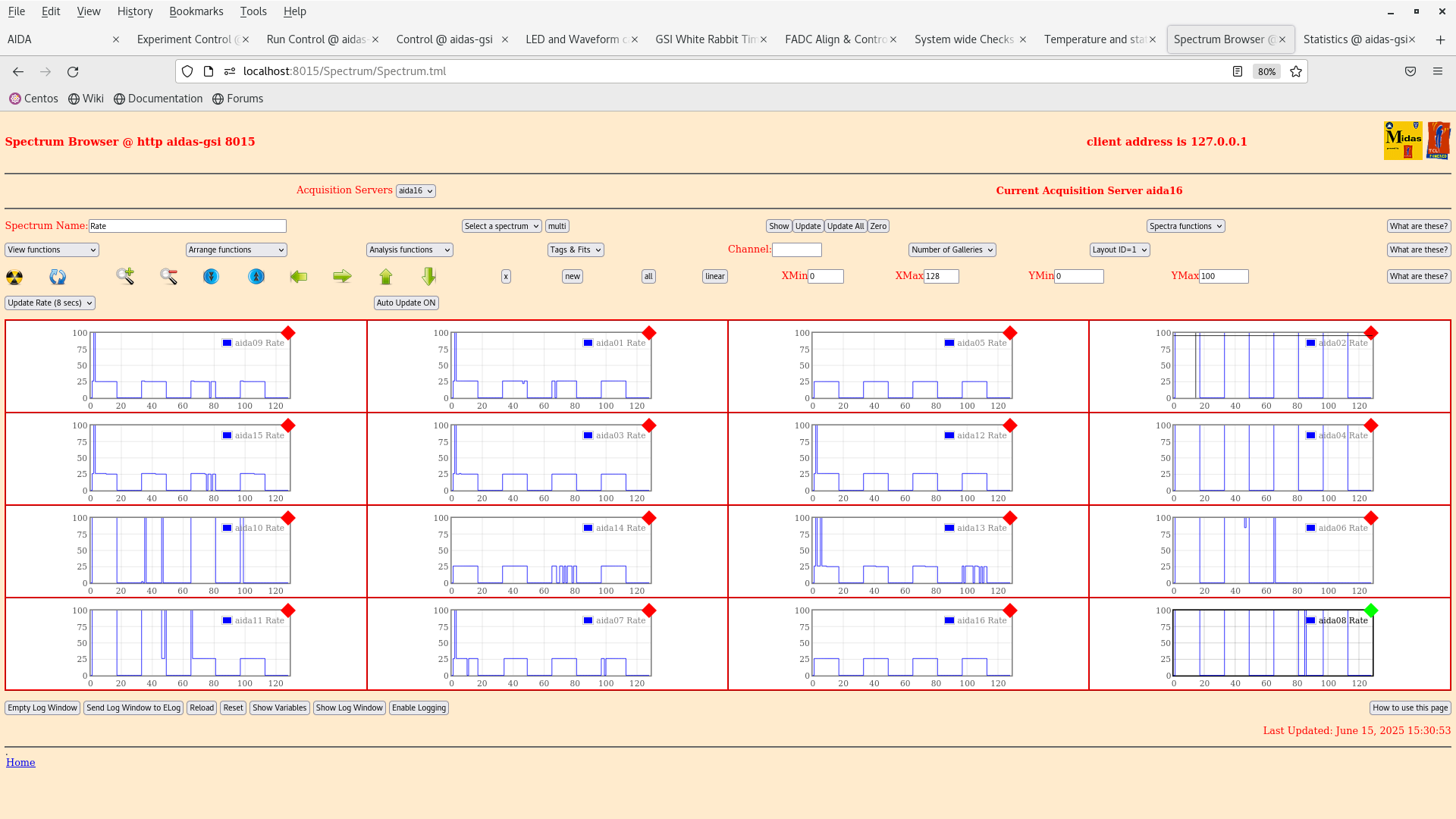

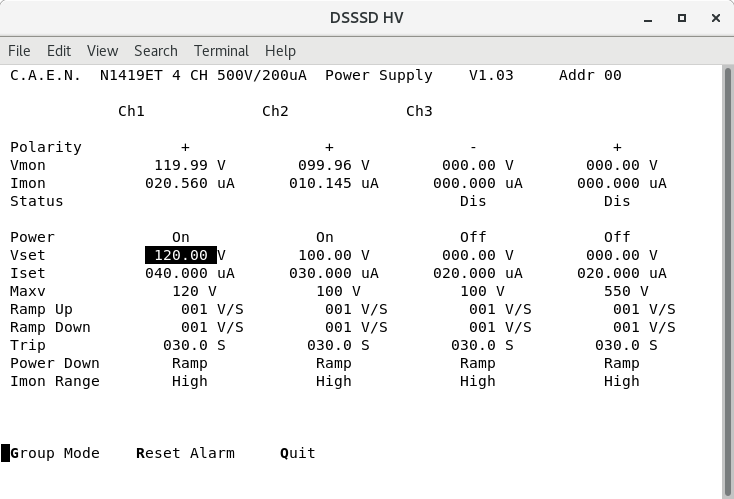

11.45 DSSSD bias & leakage current - attachment 1

FEE64 temps OK - attachment 2

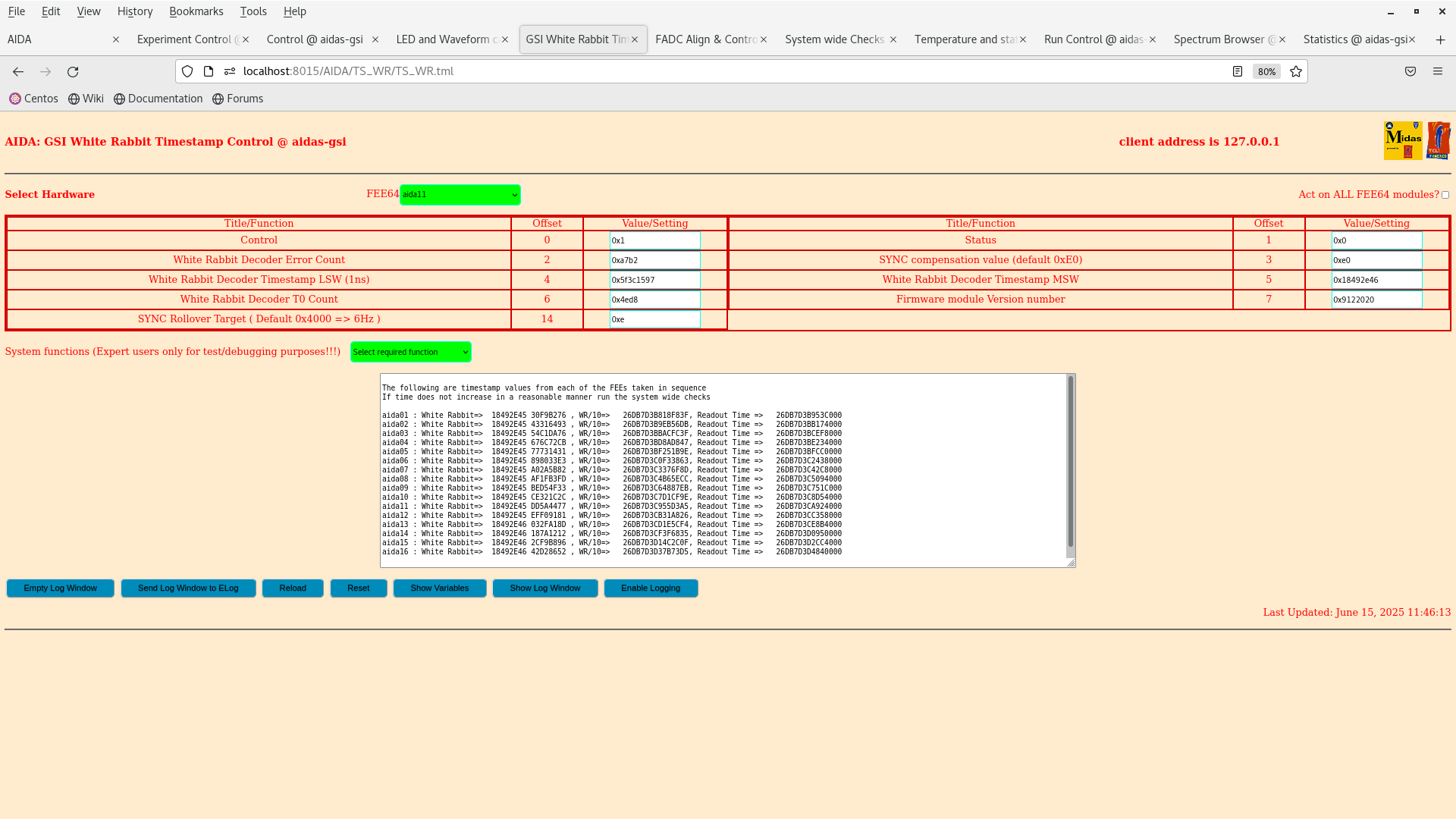

All system wide checks OK *except* WR decoder status aida02 - attachment 3

WR timestamps OK - attachment 4

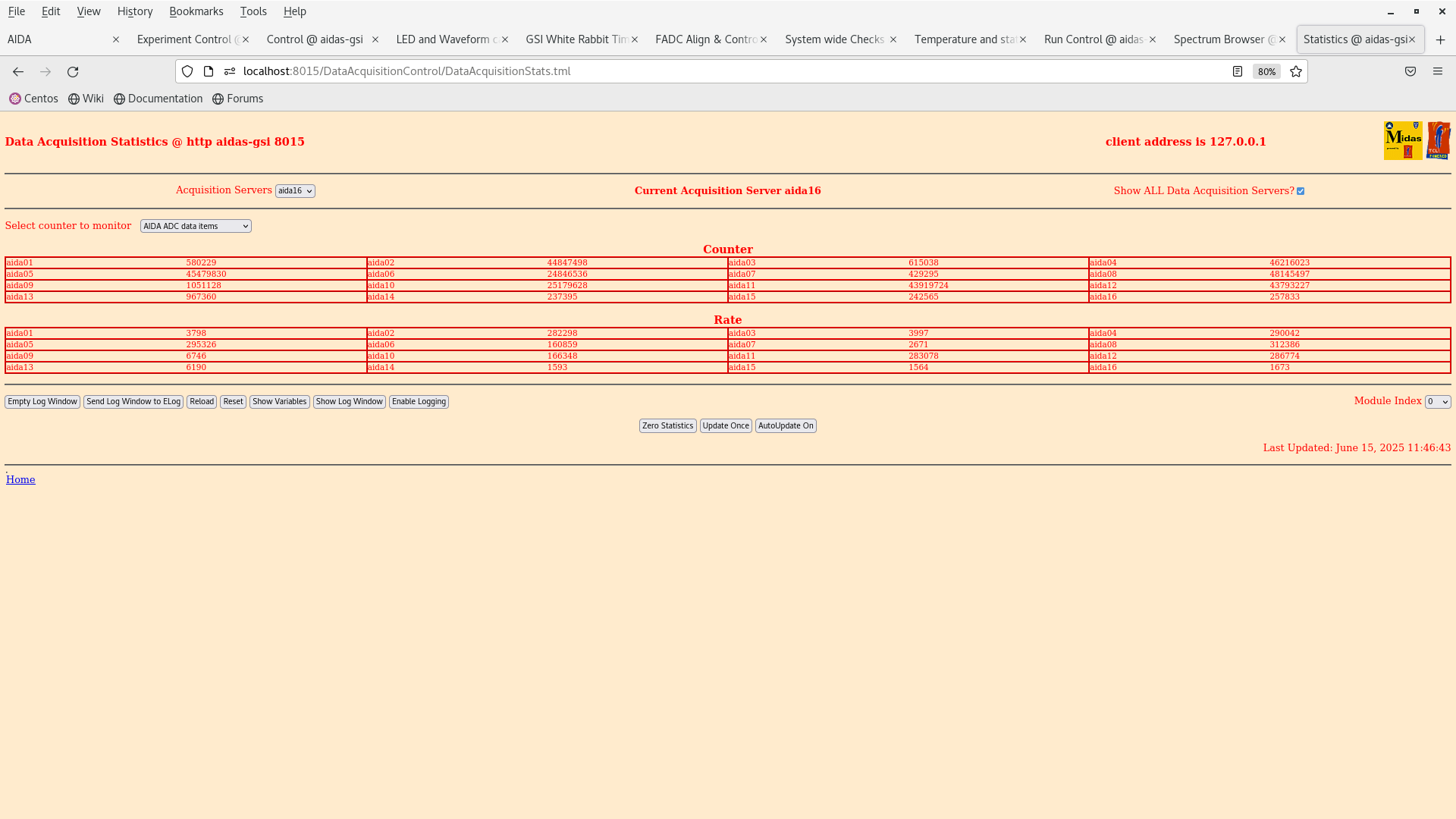

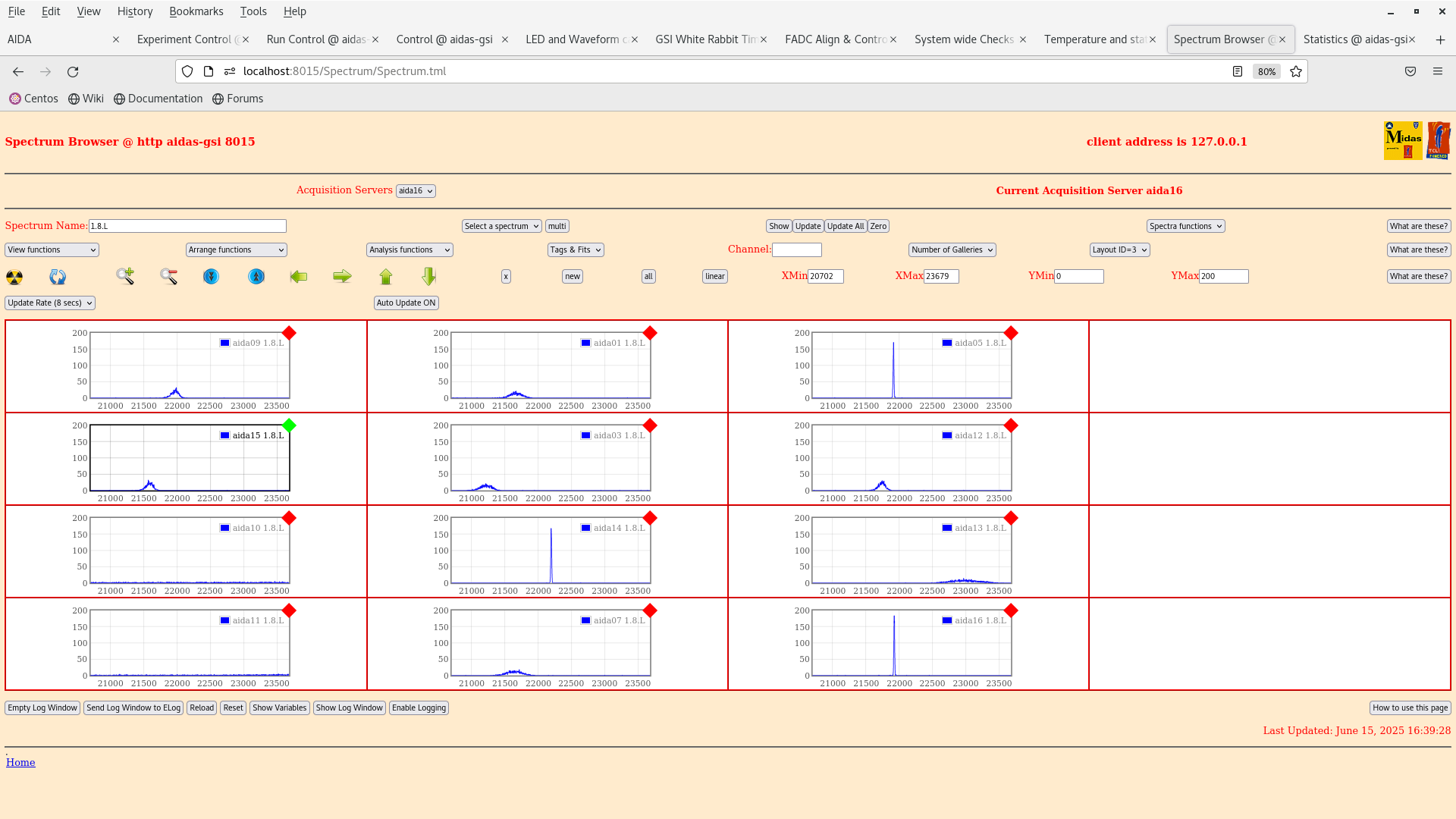

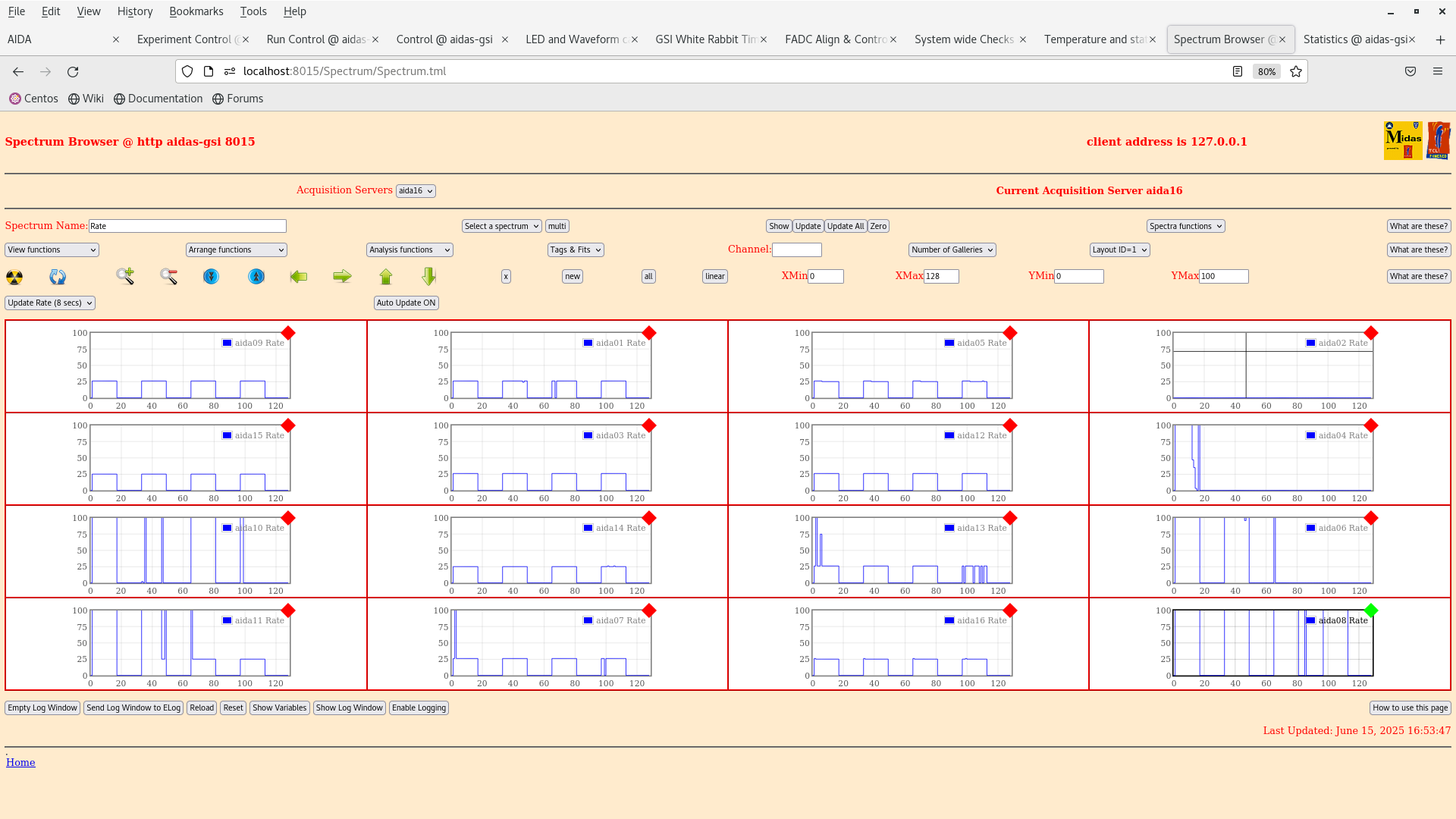

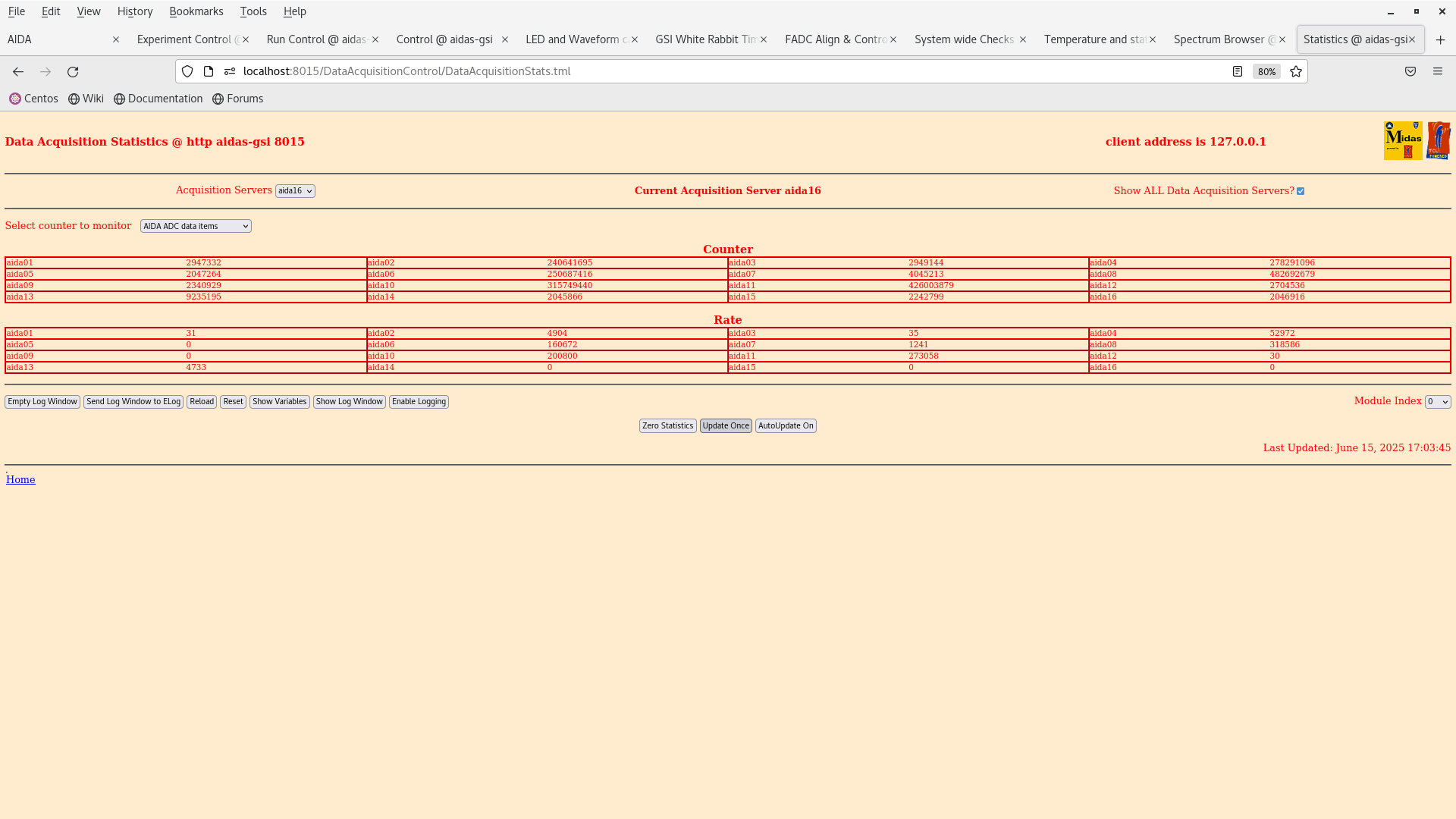

ADC data item stats - attachment 5

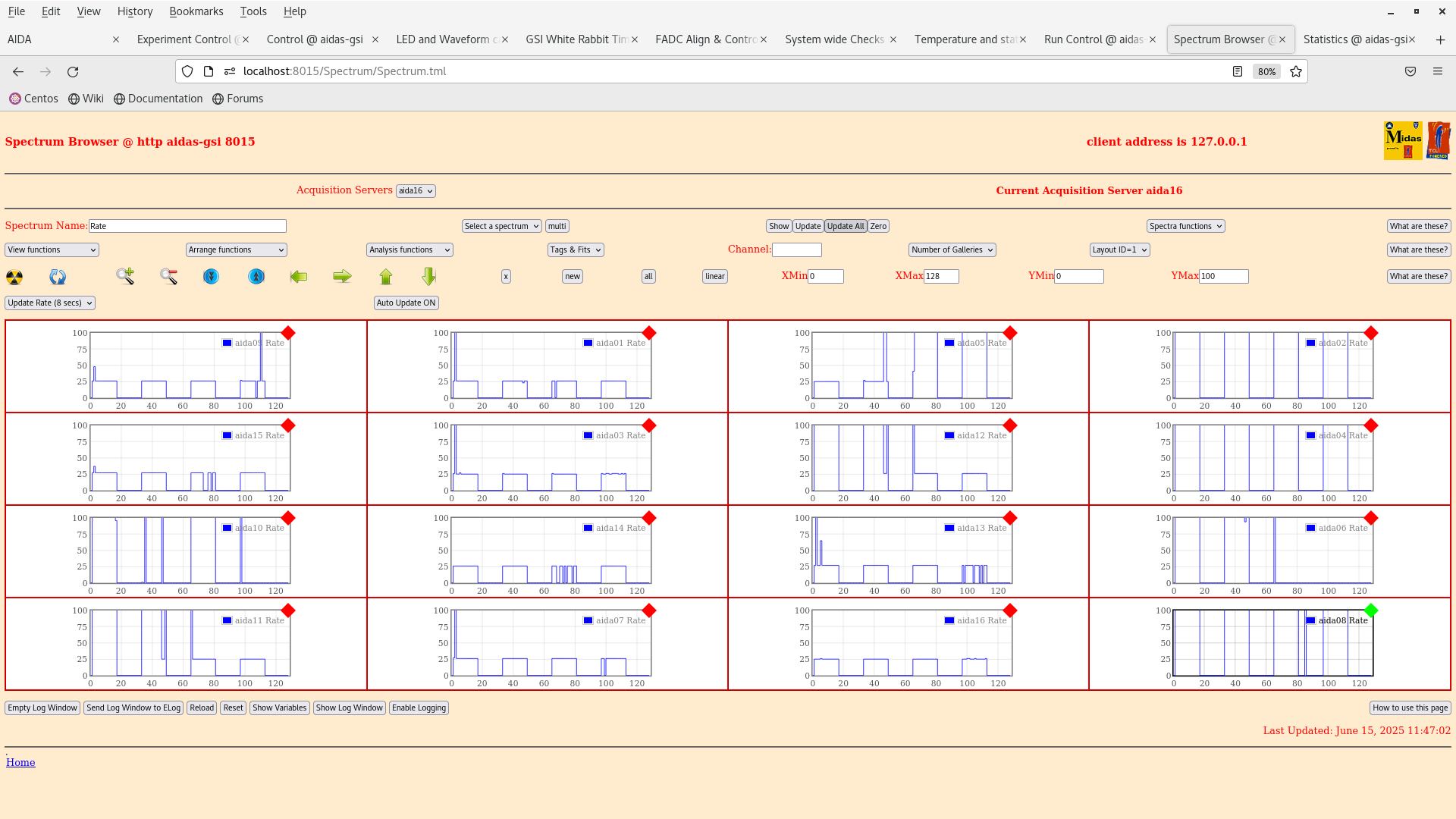

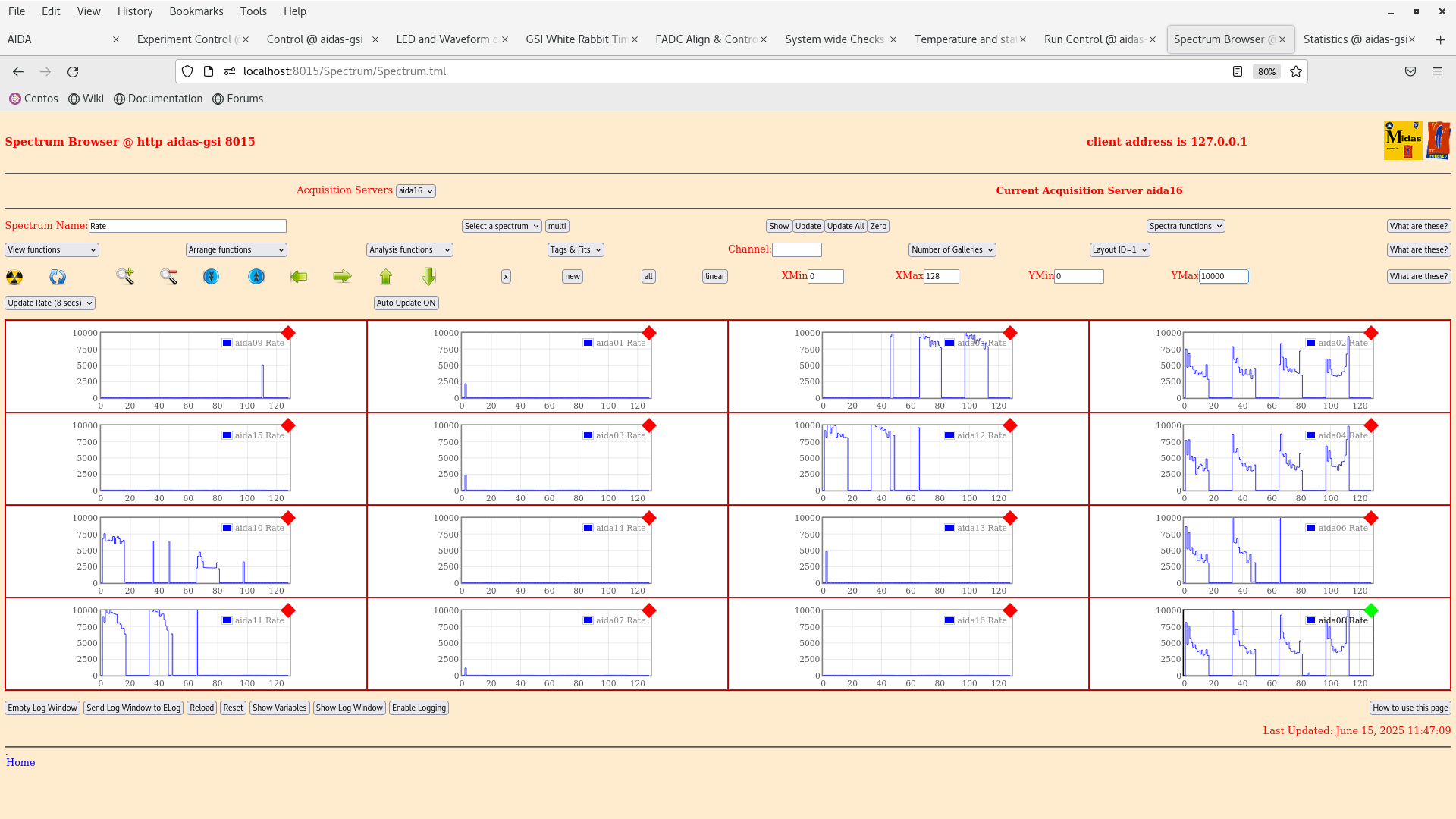

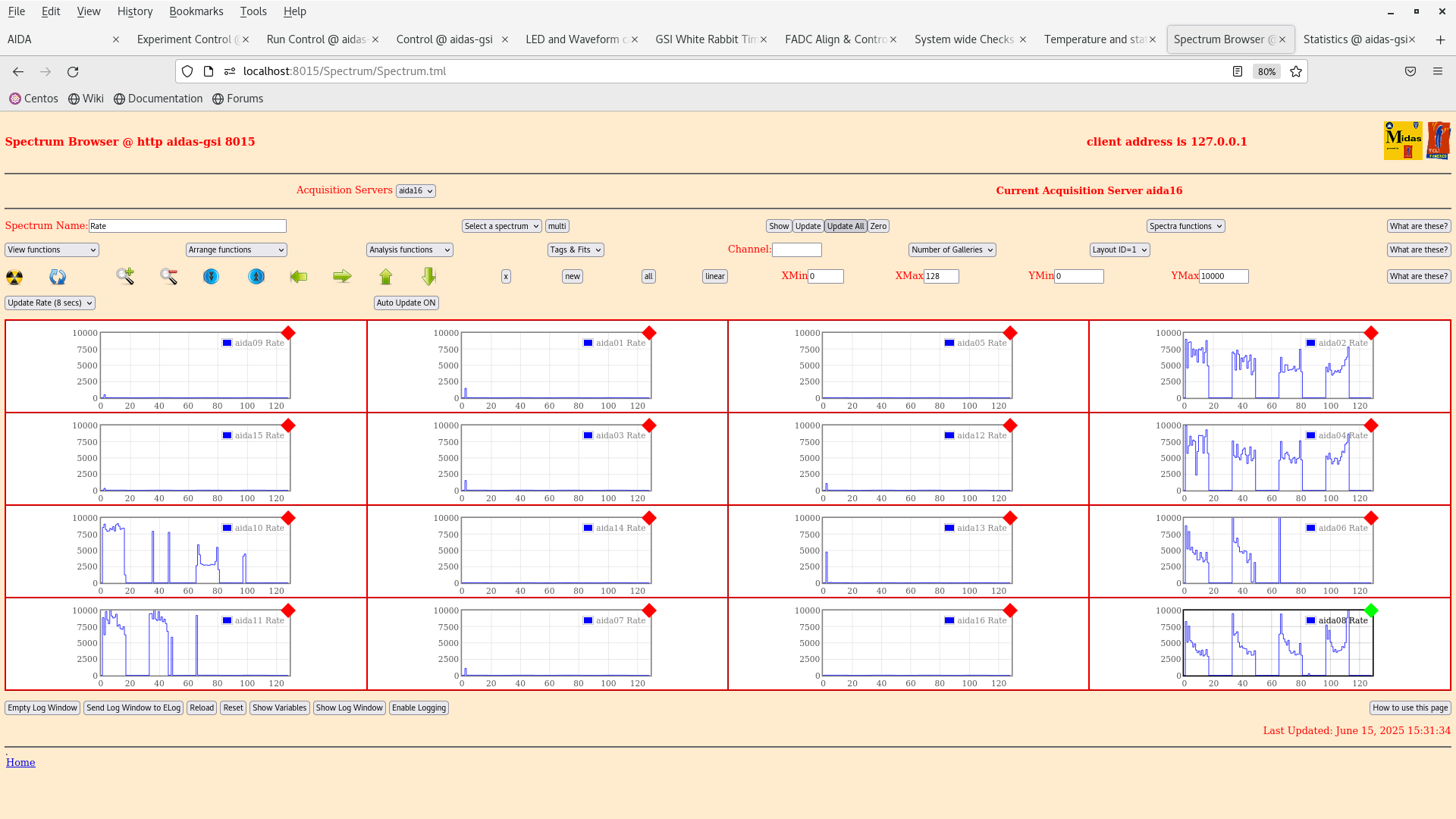

per FEE64 Rate spectra - attachments 6-7

note ASICs with per channel rates of 22Hz (pulser)

note *all* FEE64 slow comparator 0x64

note ignore aida10 - connected to MSL type BB7 - not biased yet

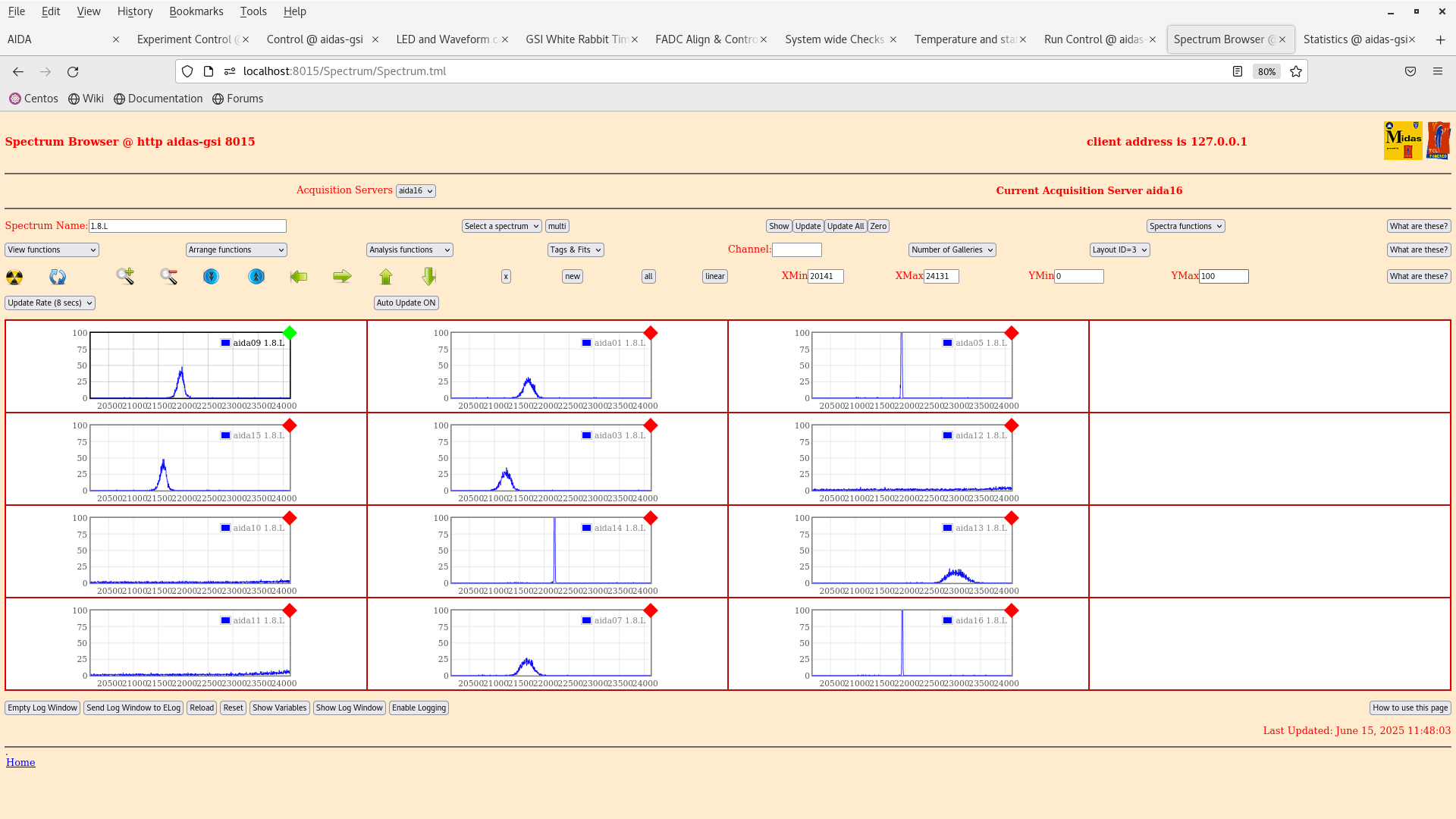

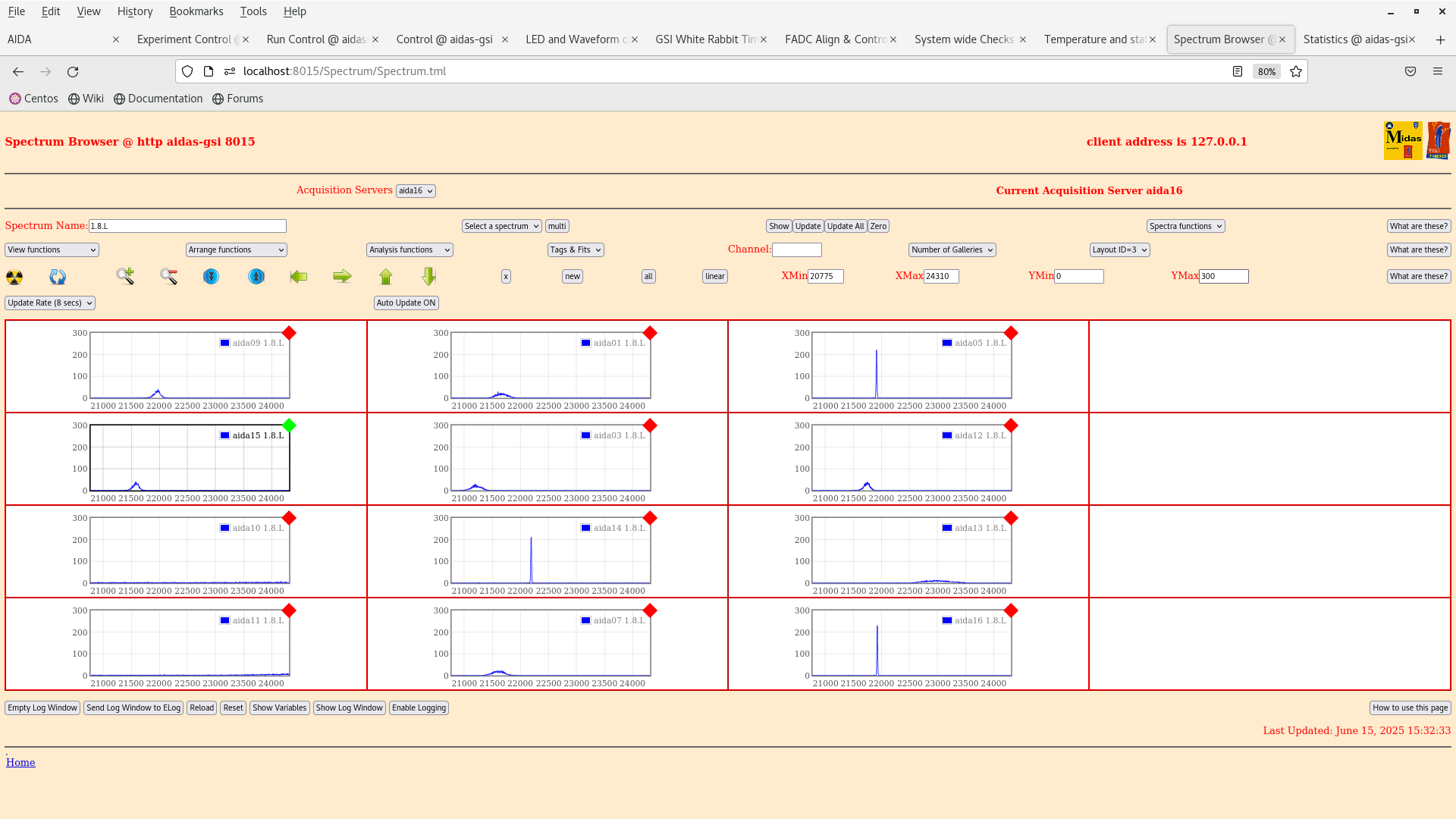

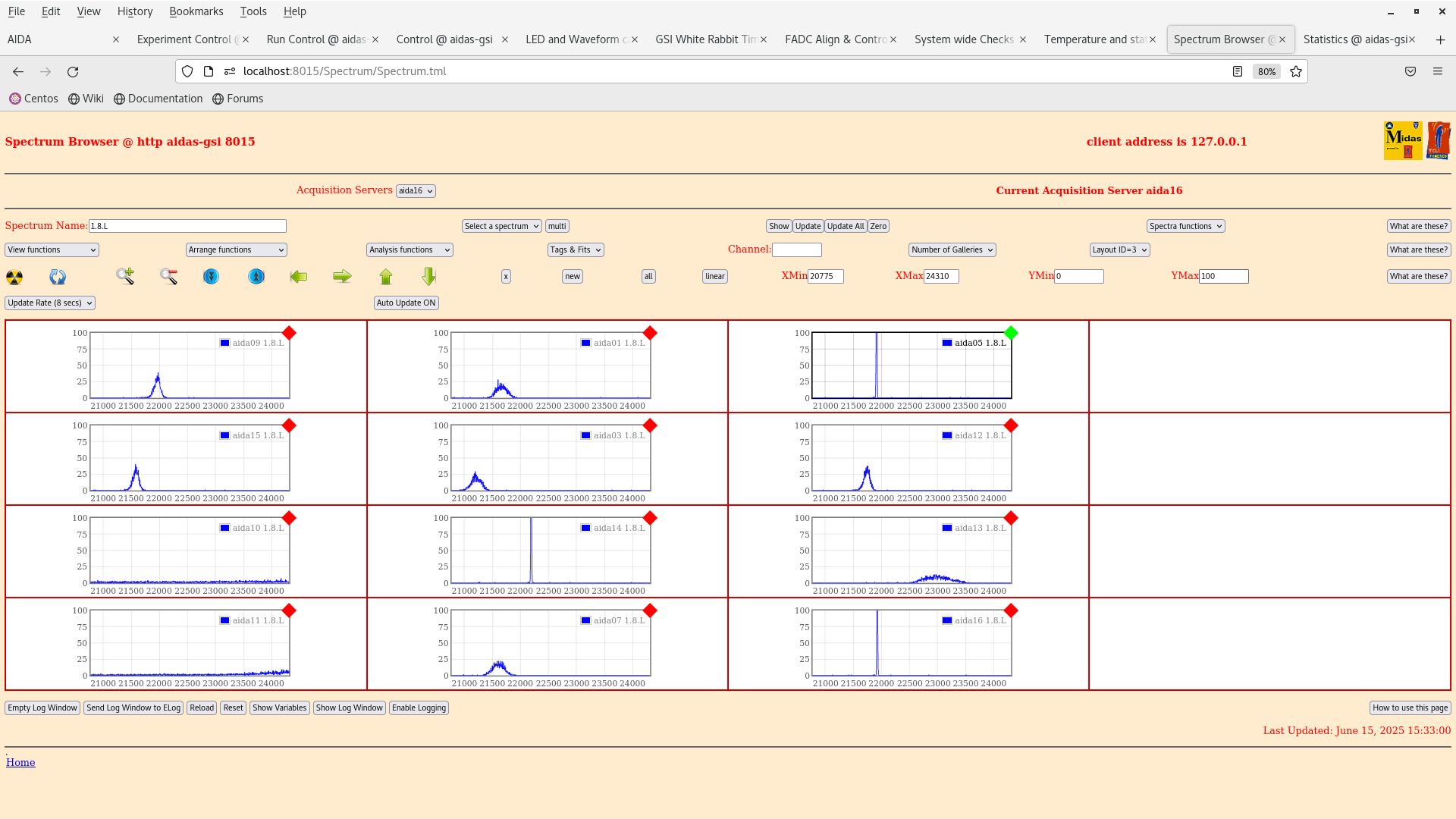

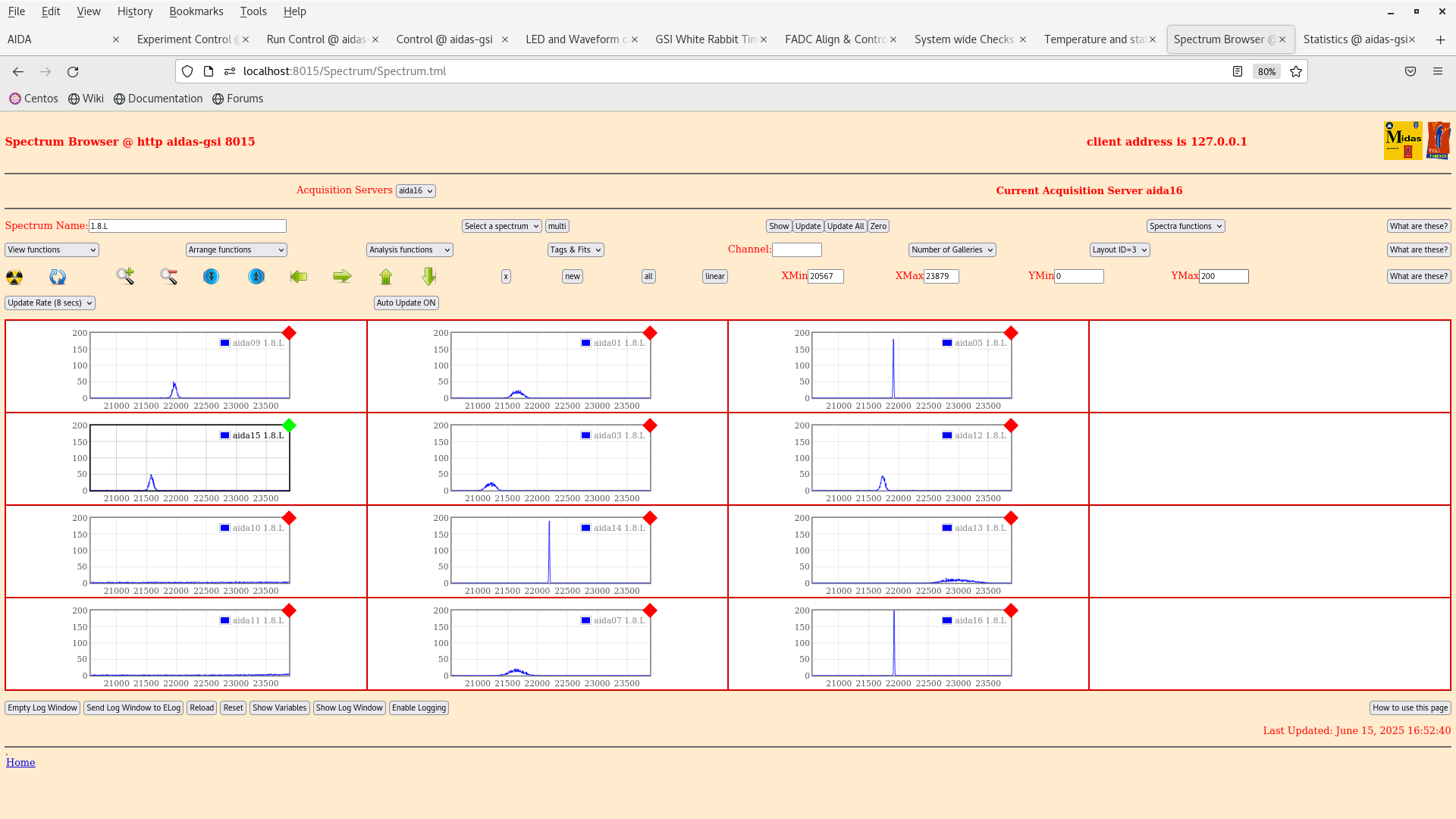

per p+n FEE64 1.8.L spectra - attachment 8-9

pulser peak widths

aida05, aida14, aida16 c. 15-20 ch FWHM ( c. 10-15keV FWHM ) - cable from DSSSD not connected to adaptor PCB

aida15 c. 137 ch FWHM - electronic noise c. 2x worse than configuration used for 2023/4 tests

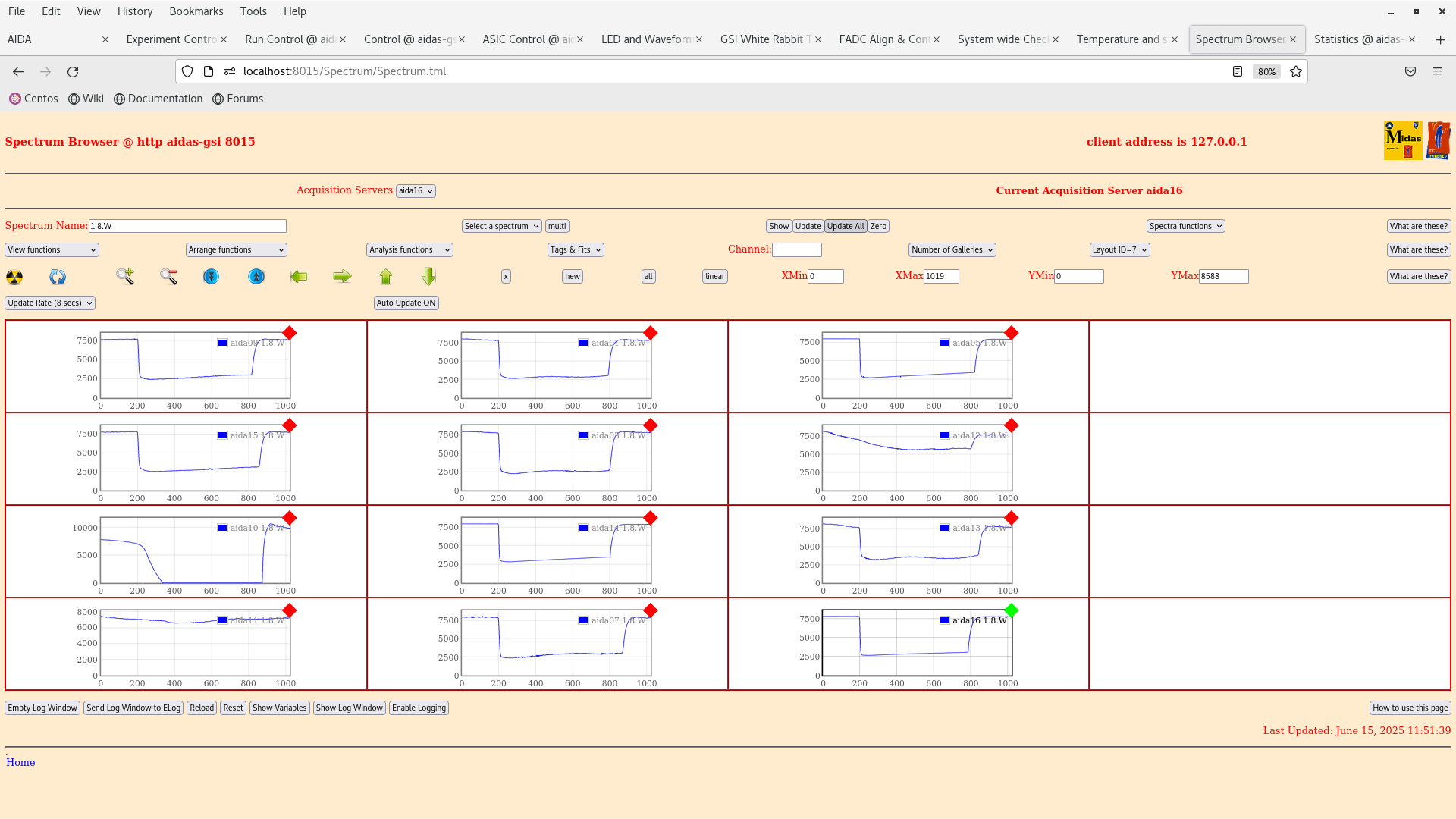

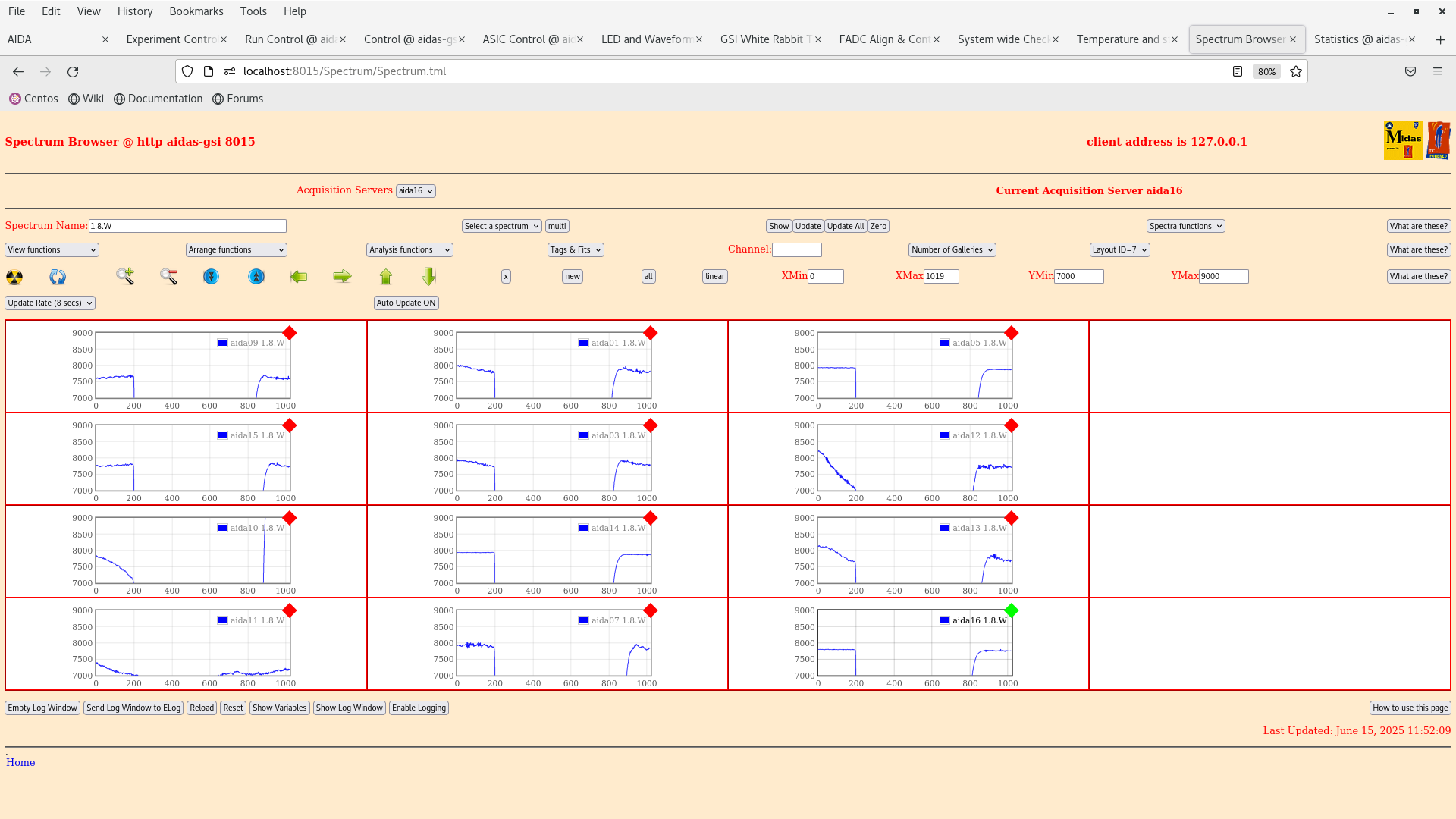

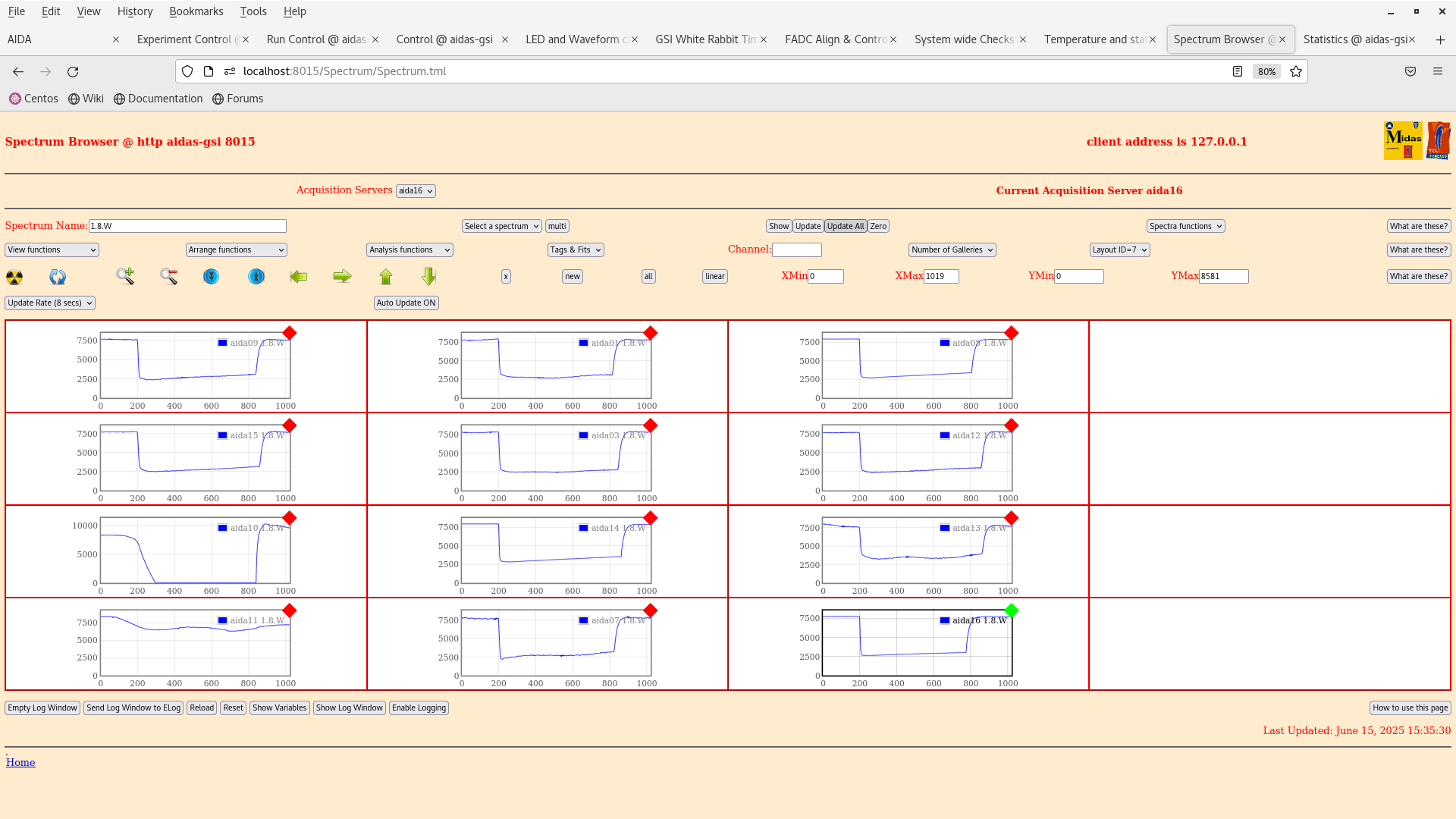

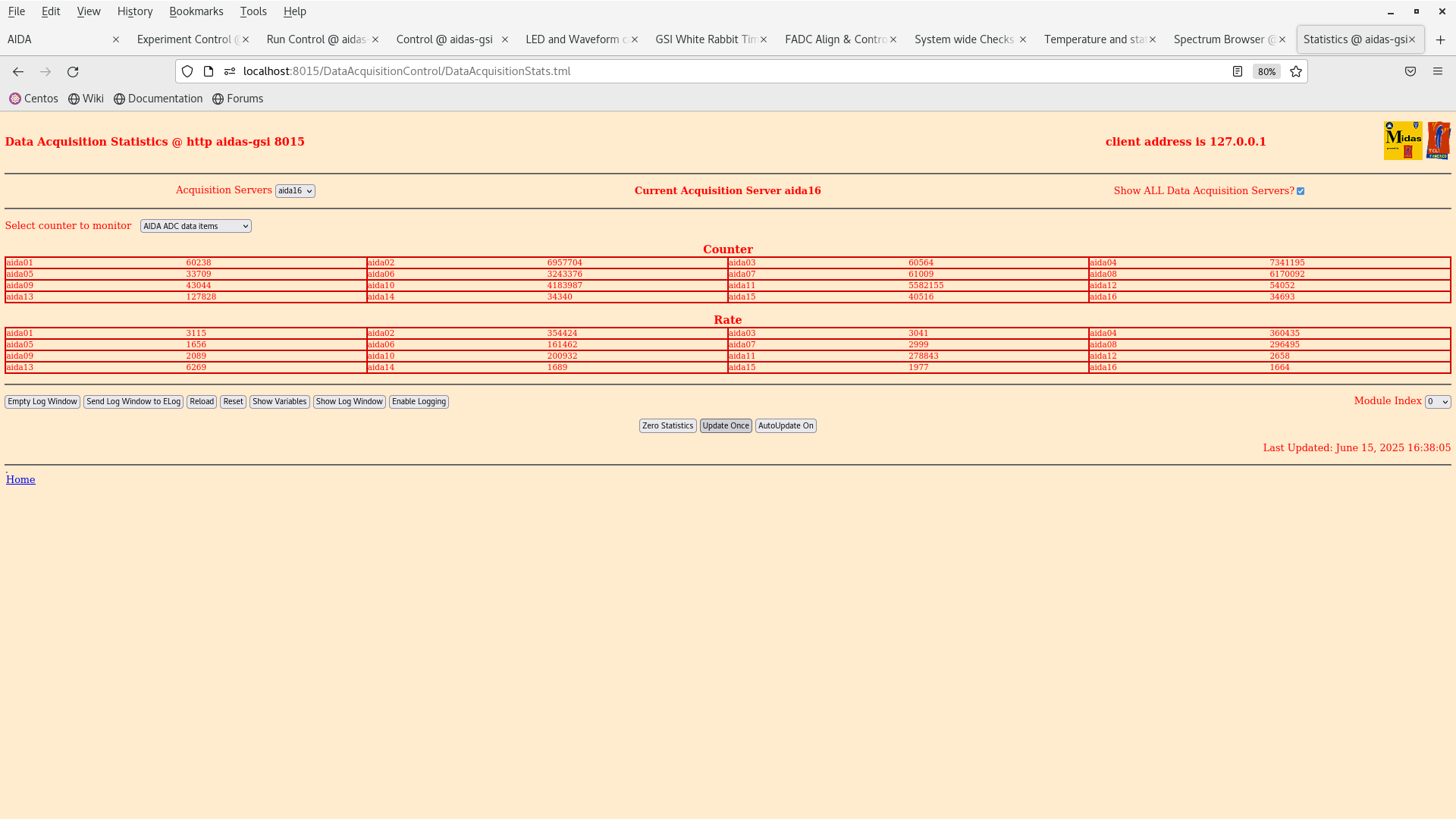

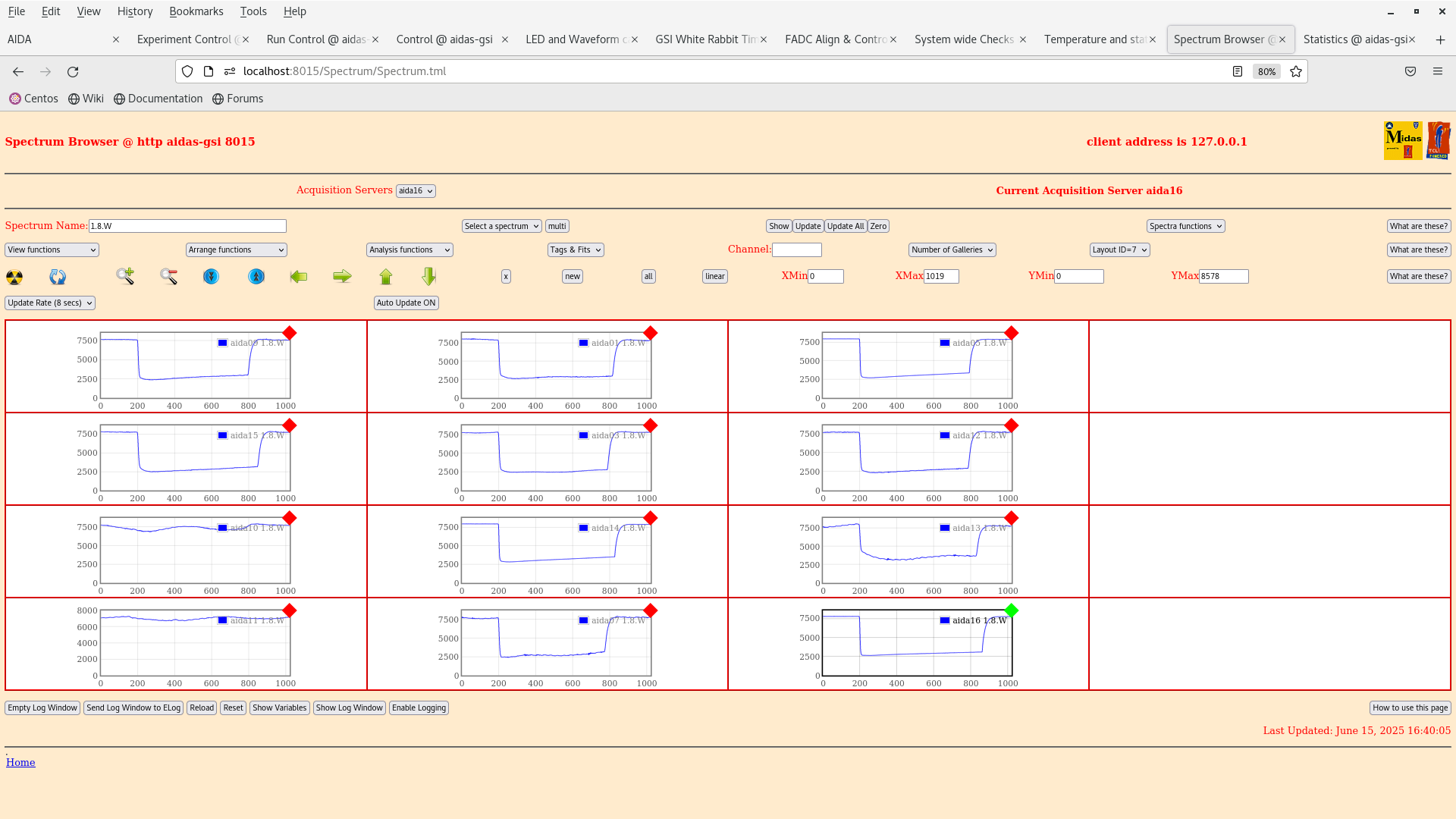

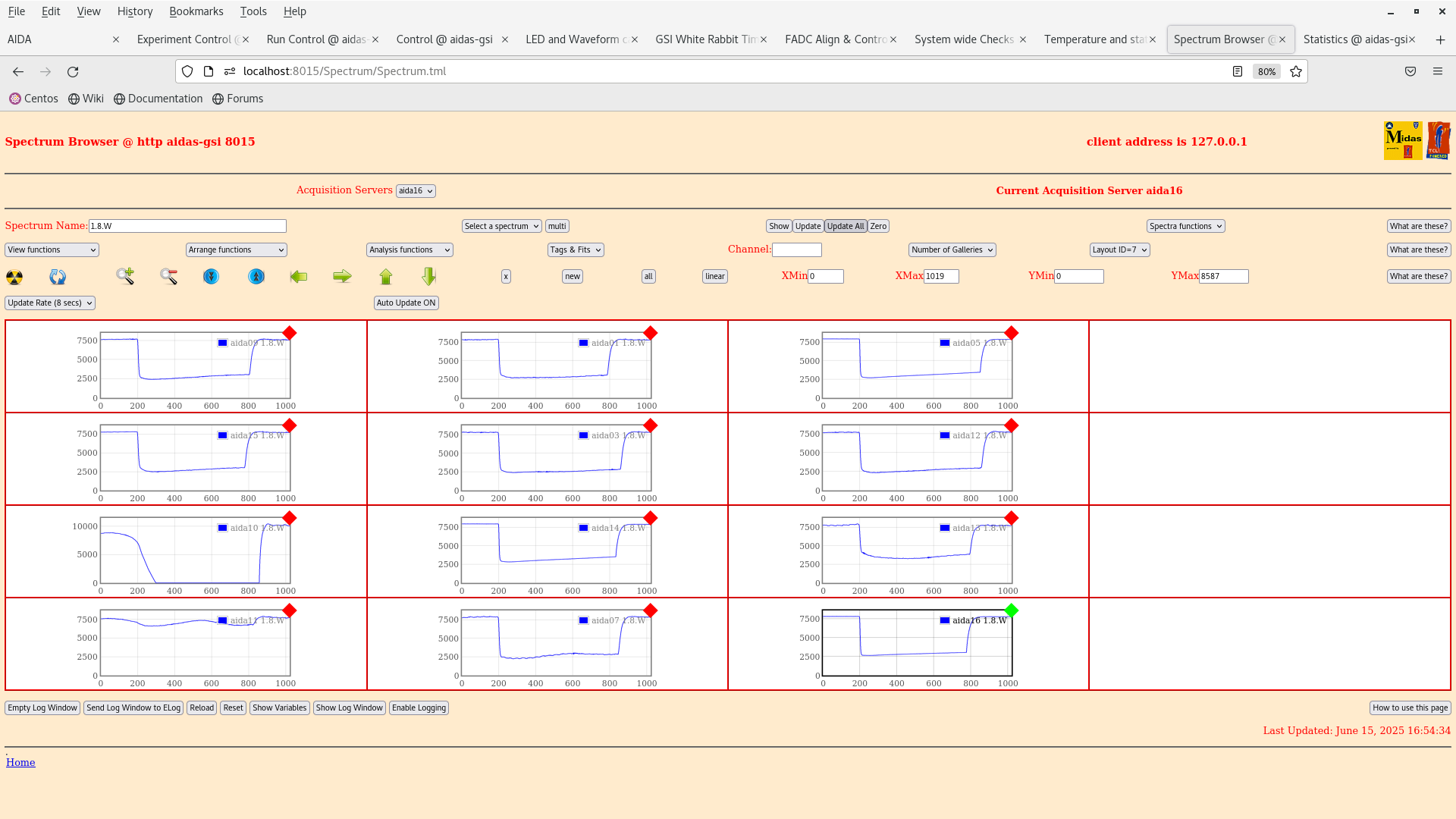

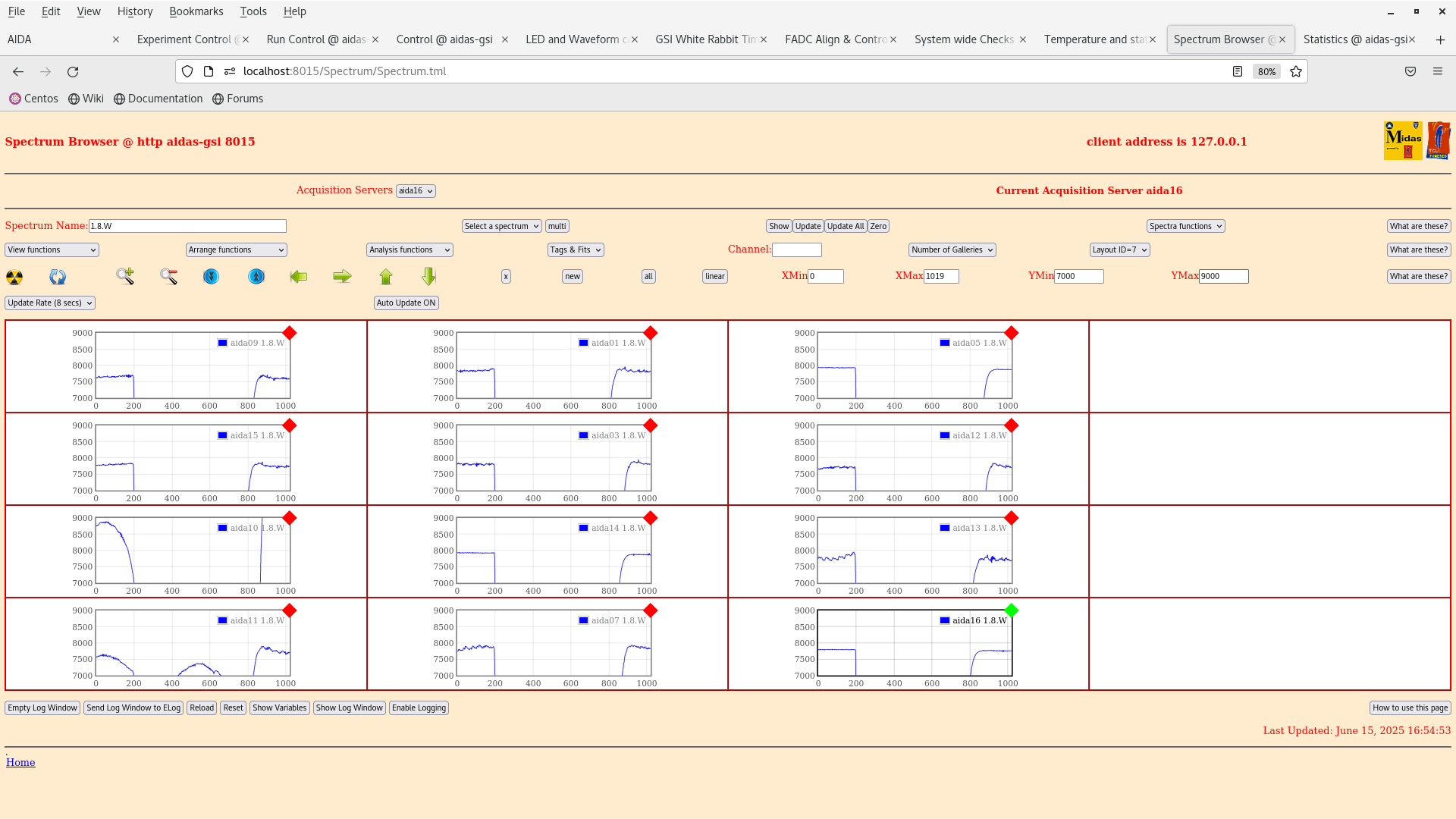

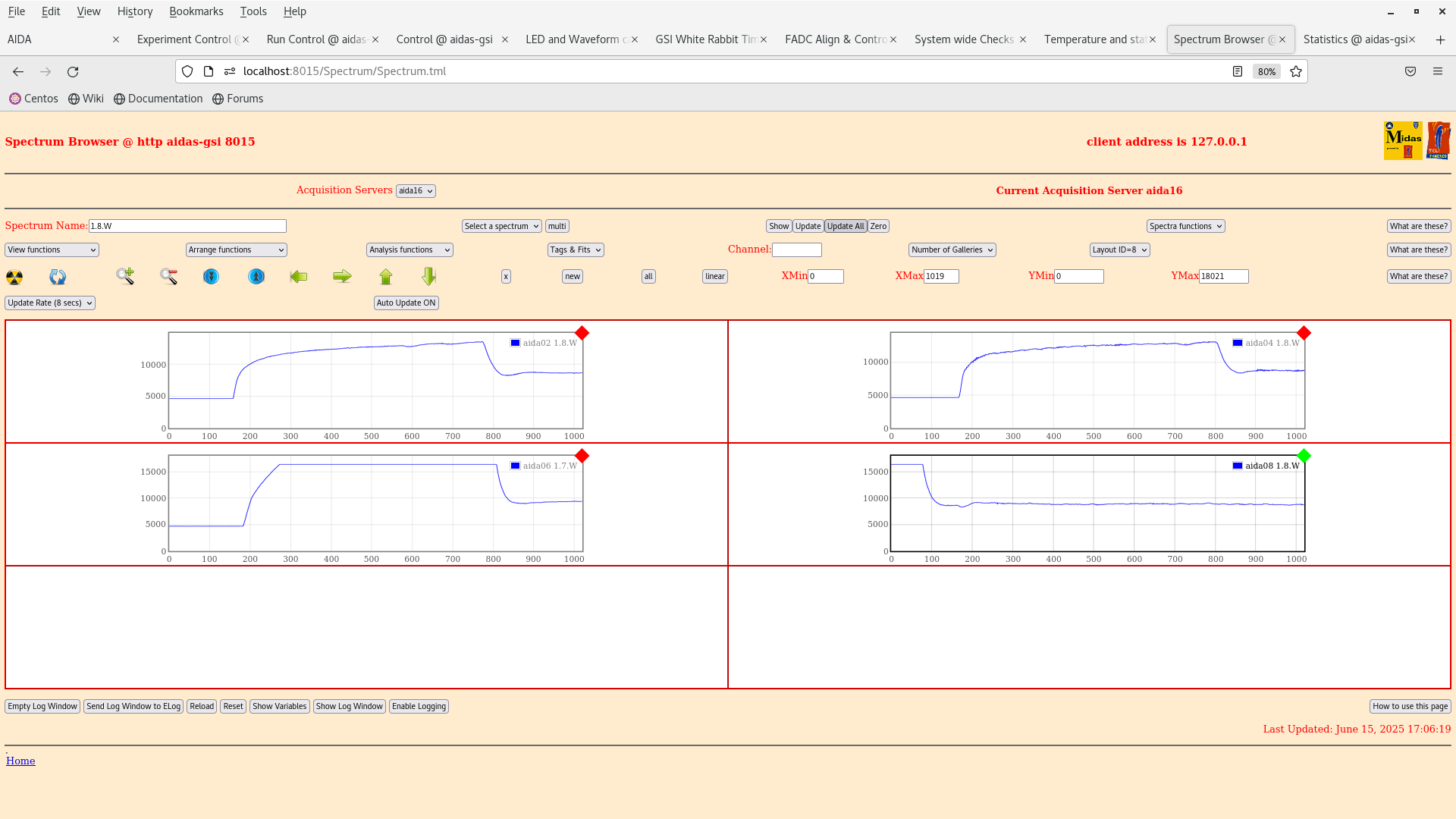

per p+n FEE64 1.8.W spectra - 20us FSR - attachments 10

per p+n FEE64 1.8.W spectra - 20us FSR - expanded y-scale = 2000 x 122uV/LSB = 0.244V FSR - attachment 11

per n+n FEE64 1.8.W spectra - 20us FSR - attachments 12

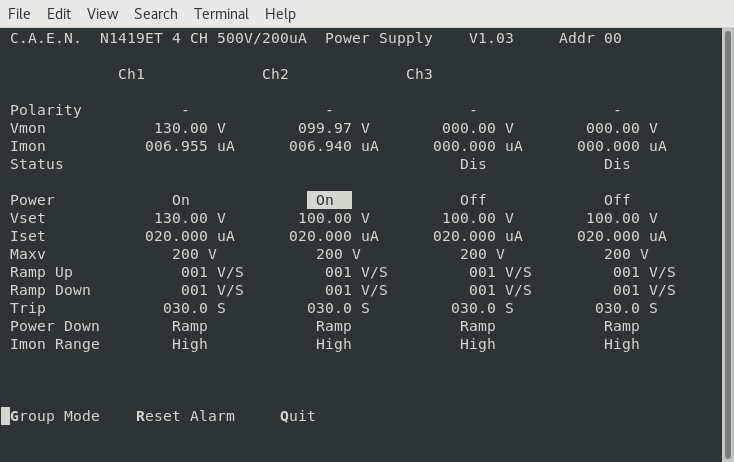

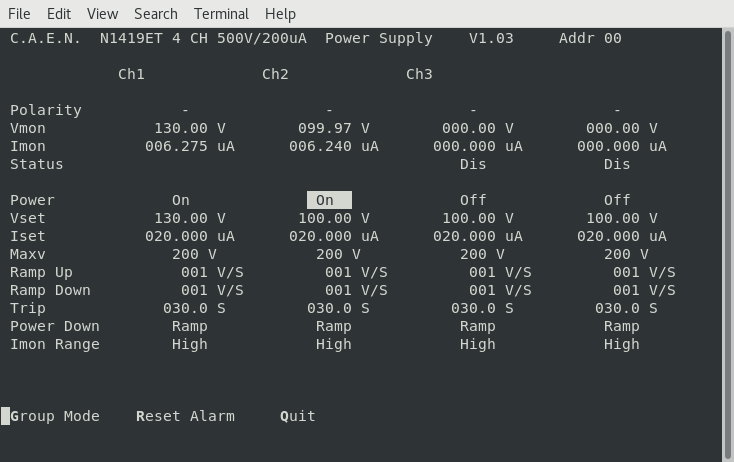

15.20 Data suggests 2x (of 6x) Si wafers are not biased - aida11 & aida05-aida12 - J2 cable disconnected

Switch from negative to positive bias polarity

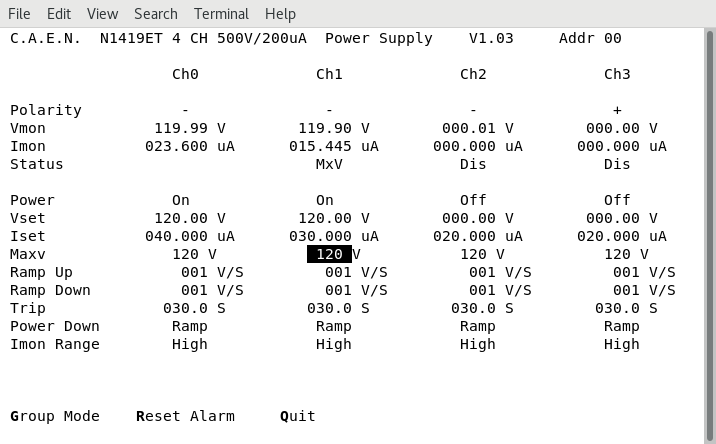

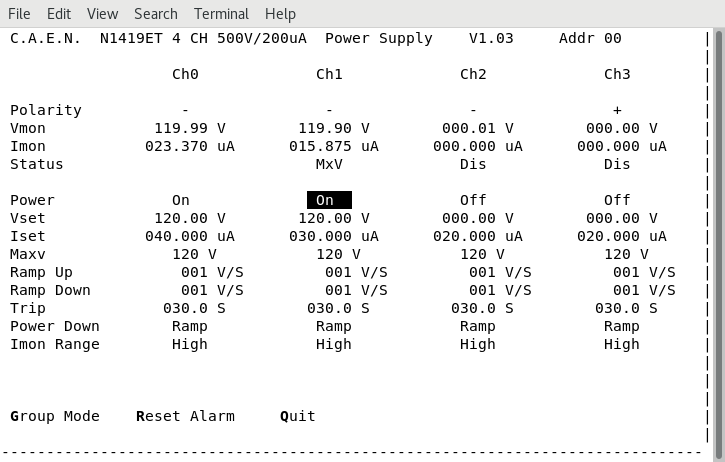

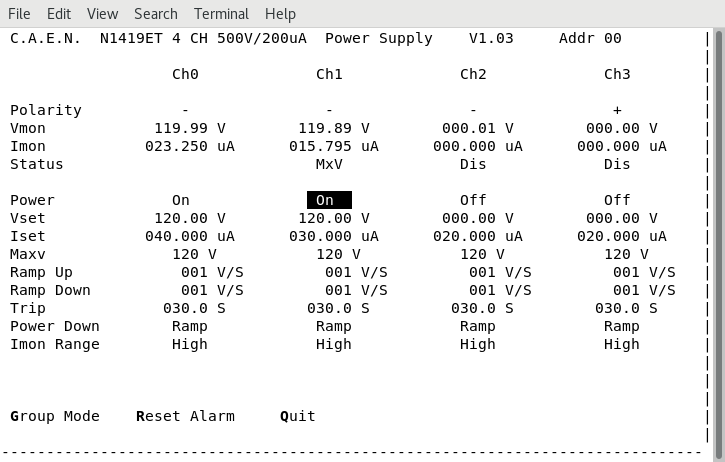

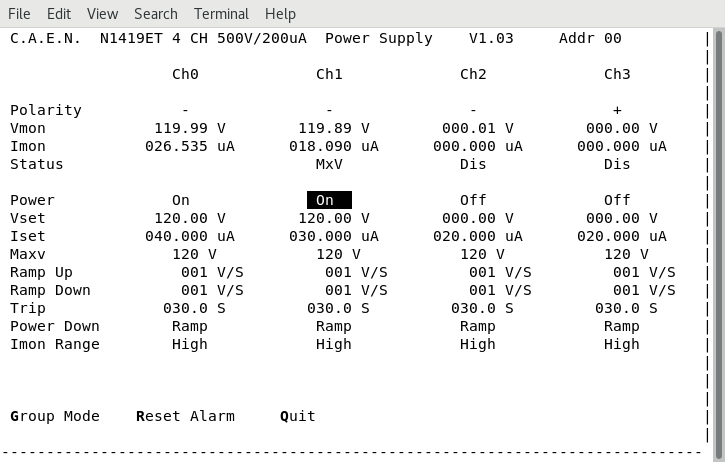

CAEN N1419ET channels 1 and 2 switched from negative to positive polarity

Note internal LK fitted - HV outputs *not* floating

Channel 1 -> DSSSD#0 from aida12 to aida04 (HV daisy chain aida12-aida03-aida15 *not* removed)

Channel 2 -> DSSSD#1 from aida16 to aida08 (HV daisy chain aida16-aida07-aida11 *not* removed)

LK1 removed from adaptor PCBs for aida02. aida04, aida06, aaida08

LK1 fitted aida05, aida13, aida10, aida09, aida15, aida11

LK3 *no* change

DSSSD bias & leakage current - attachment 13

note increase in leakage current for DSSSD#0 but not DSSSD#1

- indicating DSSSD#0 has all Si wafers biased

- all wafers of DSSSD#1 not biased => damaged adaptor PCB and/or cabling, misaligned ribbon cable/Kapton PCB connection within snout

FEE64 temps OK - attachment 14

ADC data item stats - attachment 15

per FEE64 Rate spectra - attachments 16-17

note ASICs with per channel rates of 22Hz (pulser)

note *all* FEE64 slow comparator 0x64

note ignore aida10 - connected to MSL type BB7 - not biased yet

per p+n FEE64 1.8.L spectra - attachment 18-19

pulser peak widths

aida05, aida14, aida16 c. 15-20 ch FWHM ( c. 10-15keV FWHM ) - cable from DSSSD not connected to adaptor PCB

aida15 c. 108 ch FWHM - electronic noise c. 2x worse than configuration used for 2023/4 tests

per p+n FEE64 1.8.W spectra - 20us FSR - attachments 20

per p+n FEE64 1.8.W spectra - 20us FSR - expanded y-scale = 2000 x 122uV/LSB = 0.244V FSR - attachment 21

per n+n FEE64 1.8.W spectra - 20us FSR - attachments 22

16.40 Add LK1 to aida03, aida07

DSSSD bias & leakage current - attachment 23

no change

ADC data item stats - attachment 24

per p+n FEE64 1.8.L spectra - attachment 25-26

pulser peak widths

aida05, aida14, aida16 c. 15-20 ch FWHM ( c. 10-15keV FWHM ) - cable from DSSSD not connected to adaptor PCB

aida15 c. 117 ch FWHM - electronic noise c. 2x worse than configuration used for 2023/4 tests

per p+n FEE64 1.8.W spectra - 20us FSR - attachments 27

no change

16.50 Increase DSSSD#0 bias from +100V to +120V

DSSSD bias & leakage current - attachment 28

per p+n FEE64 1.8.L spectra - attachment 29-30

pulser peak widths

aida05, aida14, aida16 c. 15-20 ch FWHM ( c. 10-15keV FWHM ) - cable from DSSSD not connected to adaptor PCB

aida15 c. 70 ch FWHM - electronic noise c. 1.2-2x worse than configuration used for 2023/4 tests

per FEE64 Rate spectra - attachments 31-32

per FEE64 1.8.W spectra - 20us FSR - attachments 33-36

aida02 & aida04 stabilised but still very noisy

Switch BNC PB-5 Pulser polarity + to - and connect test- test daisy chain

ADC data item stats - attachment 37

per FEE64 Rate spectra - attachments 38-39

aida02 & aida04 rates significantly lower but not 25Hz expected

per n+n FEE64 1.8.L spectra - attachment 40

pulser peak width aida02 c. 700 ch FWHM - very noisy!

per n+n FEE64 1.8.W spectra 20us FSR - attachment 41

*** Summary

DSSSD#0

3x Si wafers biased OK

p+n junction side electronic noise c. 1.2-2x 2023/4 configuration

n+n Ohmic side very noisy - increased detector HV to stabilise => increased capacitative load cf. 2023/4 configuration?

DSSSD#1

2x Si wafers biased OK, 1x probably not biased

p+n junction side electronic noise > 4x 2023/4 configuration

n+n Ohmic side very noisy/unstable - increased detector HV not attempted due to issues with biasing all 3x Si wafers

MSL type BB7

not biased yet

To Do

Complete connection and grounding of Bplas detectors |

| Attachment 1: Screenshot_from_2025-06-15_11-45-34.png

|

|

| Attachment 2: Screenshot_from_2025-06-15_11-45-50.png

|

|

| Attachment 3: Screenshot_from_2025-06-15_11-46-01.png

|

|

| Attachment 4: Screenshot_from_2025-06-15_11-46-29.png

|

|

| Attachment 5: Screenshot_from_2025-06-15_11-46-45.png

|

|

| Attachment 6: Screenshot_from_2025-06-15_11-47-05.png

|

|

| Attachment 7: Screenshot_from_2025-06-15_11-47-11.png

|

|

| Attachment 8: Screenshot_from_2025-06-15_11-48-00.png

|

|

| Attachment 9: Screenshot_from_2025-06-15_11-48-06.png

|

|

| Attachment 10: Screenshot_from_2025-06-15_11-51-44.png

|

|

| Attachment 11: Screenshot_from_2025-06-15_11-52-19.png

|

|

| Attachment 12: Screenshot_from_2025-06-15_11-52-47.png

|

|

| Attachment 13: Screenshot_from_2025-06-15_15-19-56.png

|

|

| Attachment 14: Screenshot_from_2025-06-15_15-20-14.png

|

|

| Attachment 15: Screenshot_from_2025-06-15_15-30-29.png

|

|

| Attachment 16: Screenshot_from_2025-06-15_15-31-20.png

|

|

| Attachment 17: Screenshot_from_2025-06-15_15-31-37.png

|

|

| Attachment 18: Screenshot_from_2025-06-15_15-32-39.png

|

|

| Attachment 19: Screenshot_from_2025-06-15_15-33-02.png

|

|

| Attachment 20: Screenshot_from_2025-06-15_15-35-33.png

|

|

| Attachment 21: Screenshot_from_2025-06-15_15-36-17.png

|

|

| Attachment 22: Screenshot_from_2025-06-15_15-36-54.png

|

|

| Attachment 23: Screenshot_from_2025-06-15_16-41-02.png

|

|

| Attachment 24: Screenshot_from_2025-06-15_16-38-08.png

|

|

| Attachment 25: Screenshot_from_2025-06-15_16-39-34.png

|

|

| Attachment 26: Screenshot_from_2025-06-15_16-39-46.png

|

|

| Attachment 27: Screenshot_from_2025-06-15_16-41-30.png

|

|

| Attachment 28: Screenshot_from_2025-06-15_16-52-15.png

|

|

| Attachment 29: Screenshot_from_2025-06-15_16-52-47.png

|

|

| Attachment 30: Screenshot_from_2025-06-15_16-53-00.png

|

|

| Attachment 31: Screenshot_from_2025-06-15_16-54-00.png

|

|

| Attachment 32: Screenshot_from_2025-06-15_16-54-08.png

|

|

| Attachment 33: Screenshot_from_2025-06-15_16-54-40.png

|

|

| Attachment 34: Screenshot_from_2025-06-15_16-54-58.png

|

|

| Attachment 35: Screenshot_from_2025-06-15_16-55-14.png

|

|

| Attachment 36: Screenshot_from_2025-06-15_16-55-31.png

|

|

| Attachment 37: Screenshot_from_2025-06-15_17-03-49.png

|

|

| Attachment 38: Screenshot_from_2025-06-15_17-04-00.png

|

|

| Attachment 39: Screenshot_from_2025-06-15_17-04-15.png

|

|

| Attachment 40: Screenshot_from_2025-06-15_17-04-40.png

|

|

| Attachment 41: Screenshot_from_2025-06-15_17-06-24.png

|

|

|

198

|

Sun Mar 14 07:04:30 2021 |

OH | Sunday 14th March 2021 |

08:07 Realised the correlation scalers hadn't been enabled again. Have enabled them now. R56_151

Looking through the merger messages from the nightshift we see bad timestamps in FEE 11. This FEE does not have any scalers going into it.

It is also the least noisy FEE in the back DSSD

MERGE Data Link (20510): bad timestamp 10 3 0xc2b77eff 0x037a3b92 0x000017f7f37a3b92 0x166c17f7f37a3b92 0x166c17f7f3877262

MERGE Data Link (20510): bad timestamp 10 3 0xc2827f3a 0x037aa122 0x000017f7f37aa122 0x166c17f7f37aa122 0x166c17f7f3877262

09:01 System wide checks

Base Current Difference

aida07 fault 0x8c74 : 0x8c77 : 3

White Rabbit error counter test result: Passed 11, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

Base Current Difference

aida07 fault 0x2 : 0x5 : 3

FPGA Timestamp error counter test result: Passed 11, Failed 1

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

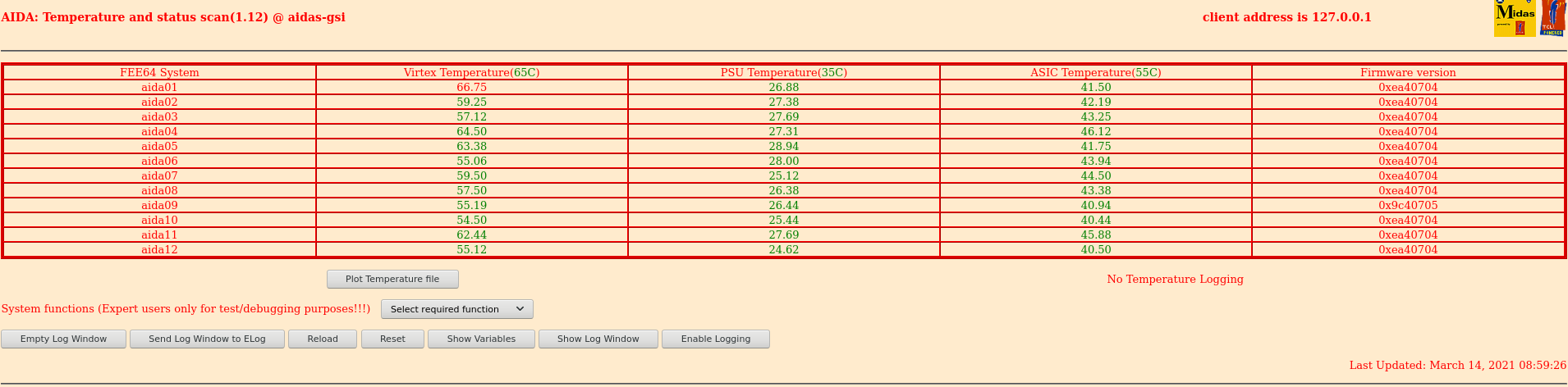

Statistics - attachment 1

Temperature - attachment 2

Bias and leakage current - attachment 3

11:18 System wide checks

Base Current Difference

aida07 fault 0x8c77 : 0x8c78 : 1

White Rabbit error counter test result: Passed 11, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

Statistics - attachment 4

Temperatures - attachment 5

Bias and leakage - attachment 6

13.14 DAQ continues OK - file R56_285

ASIC settings 2019Dec19-16.19.51

DSSSD#1 slow comparator 0xa

DSSSD#2 slow comparator 0xa

DSSSD#3 slow comparator 0xd

BNC PB-5 Pulser

Amplitude1.0V

Attenuation x1

Frequency 2Hz

tau_d 1ms

- polarity

Delay 250ns, tail pulse

13.18 System wide checks

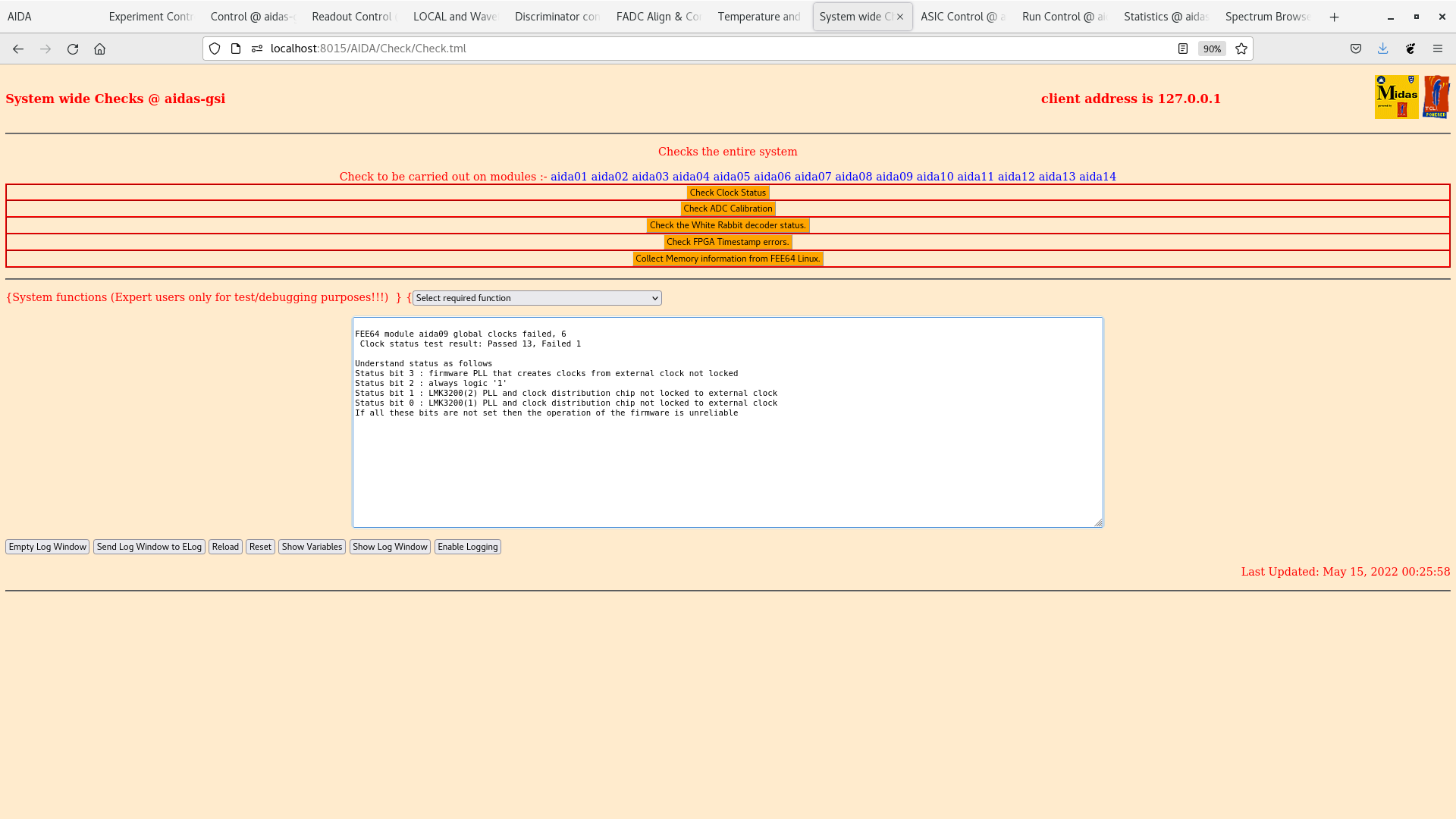

FEE64 module aida09 global clocks failed, 6

Clock status test result: Passed 11, Failed 1

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

FEE64 module aida07 failed

FEE64 module aida09 failed

Calibration test result: Passed 10, Failed 2

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

Base Current Difference

aida07 fault 0x8c77 : 0x8c78 : 1

White Rabbit error counter test result: Passed 11, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

FPGA Timestamp error counter test result: Passed 12, Failed 0

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 27 8 3 4 2 2 2 2 3 4 10 : 54492

aida02 : 0 2 3 0 2 3 2 3 3 3 6 : 36416

aida03 : 18 9 1 2 0 4 1 3 3 3 6 : 36320

aida04 : 2 3 3 3 1 4 3 2 2 4 15 : 74224

aida05 : 26 72 72 54 53 49 22 18 7 4 7 : 72104

aida06 : 7 5 5 10 0 2 2 4 3 2 5 : 30932

aida07 : 2 4 2 1 1 3 2 3 2 3 7 : 39464

aida08 : 25 9 4 2 1 2 1 4 3 3 6 : 36716

aida09 : 4 11 3 5 2 4 1 2 3 3 6 : 36024

aida10 : 18 5 2 1 0 5 2 2 3 3 6 : 36144

aida11 : 25 10 4 1 1 4 2 3 2 3 6 : 35668

aida12 : 26 7 1 1 1 3 2 3 3 3 6 : 36496

13.19 FEE64 temperatures OK - attachment 7

Good events stats OK - attachment 8

Bias & leakage currents OK - attachment 9

Merger 4.5M items/s

Tape Server 14Mb/s

No Merger warning/error messages since last report. No MBS relay warning/error/messages since last restart.

All histograms zero'd

16.00 DAQ contiues R56_361

System wide checks

FEE64 module aida09 global clocks failed, 6

Clock status test result: Passed 11, Failed 1

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

FEE64 module aida07 failed

FEE64 module aida09 failed

Calibration test result: Passed 10, Failed 2

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

Base Current Difference

aida07 fault 0x8c77 : 0x8c79 : 2

White Rabbit error counter test result: Passed 11, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

FPGA Timestamp error counter test result: Passed 12, Failed 0

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 23 8 6 4 2 2 2 2 3 4 10 : 54524

aida02 : 1 3 4 2 1 2 1 4 3 3 6 : 36572

aida03 : 2 3 2 3 1 3 2 2 3 3 6 : 35936

aida04 : 19 7 2 3 1 4 3 3 1 4 15 : 73796

aida05 : 34 68 72 54 53 49 22 18 7 4 7 : 72104

aida06 : 11 10 4 10 0 2 2 4 3 2 5 : 30972

aida07 : 1 3 2 2 2 2 2 3 2 3 7 : 39420

aida08 : 24 10 5 2 1 3 1 4 3 3 6 : 36864

aida09 : 20 8 3 5 2 3 2 3 3 3 6 : 36704

aida10 : 2 3 2 3 1 3 3 2 3 3 6 : 36192

aida11 : 17 10 4 0 1 4 2 3 2 3 6 : 35604

aida12 : 20 6 3 2 1 3 2 2 2 4 6 : 37040

15.05 FEE64 temperatures OK - attachment 10

Good events stats OK - attachment 11

Bias & leakage currents OK - attachment 12

Merger 4.6M items/s

Tape Server 14Mb/s

No Merger warning/error messages since last report. No MBS relay warning/error/messages since last restart.

Rate spectra - attachments 13 & 14

p+n junction HEC spectra - attachment 15

17.33 end of S452 run file R56_397

No Merger warning/error messages since last report. No MBS relay warning/error/messages since last restart.

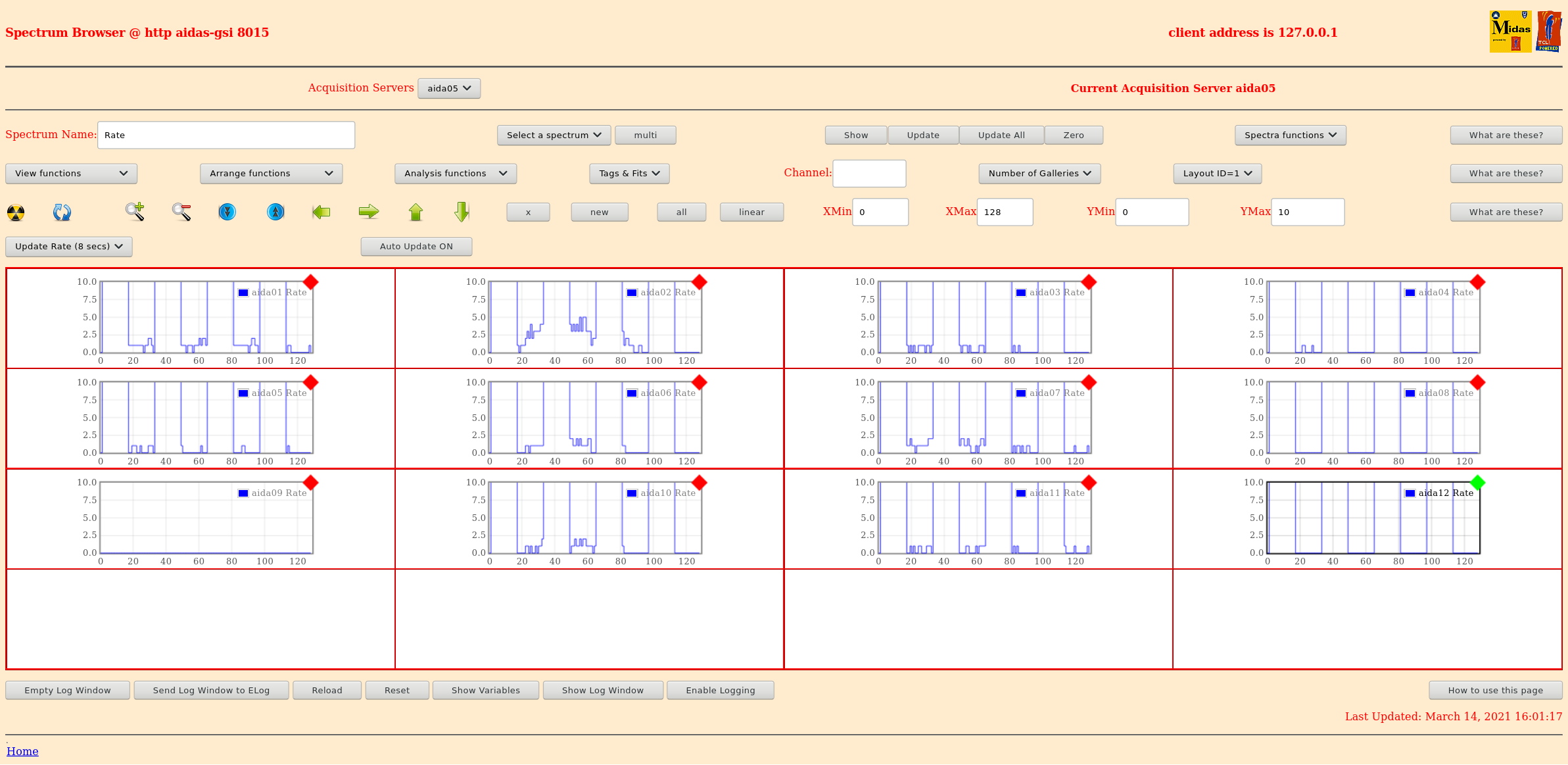

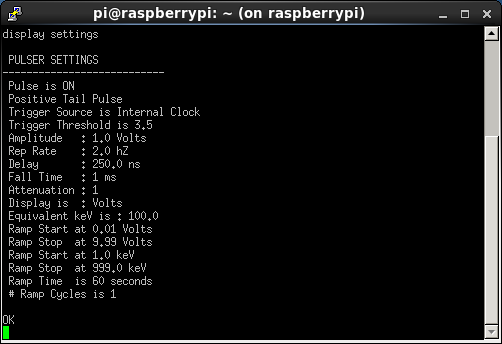

BNC PB-5 config - attachment 16

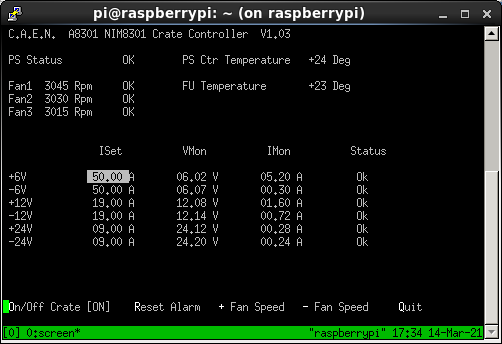

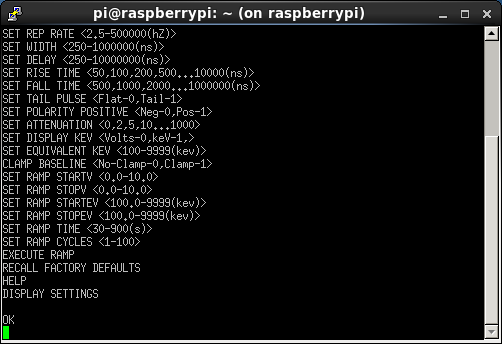

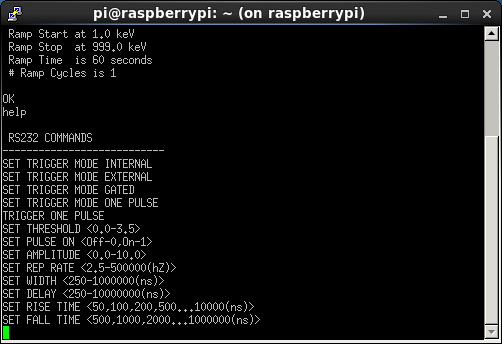

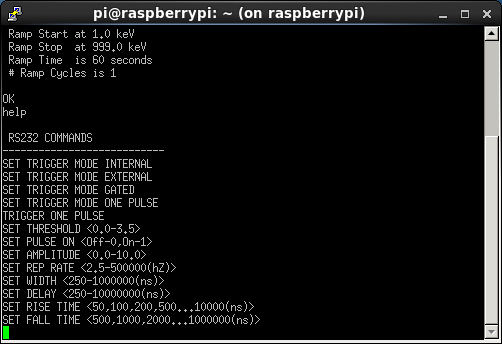

CAEN 8xxx NIM bin config - attachment 17 |

| Attachment 1: 210314_0858_Stats.png

|

|

| Attachment 2: 210314_0859_Temp.png

|

|

| Attachment 3: 210314_0900_Bias.png

|

|

| Attachment 4: 210314_1116_Stats.png

|

|

| Attachment 5: 210314_1116_Temp.png

|

|

| Attachment 6: 210314_1117_Bias.png

|

|

| Attachment 7: Screenshot_2021-03-14_Temperature_and_status_scan_aidas-gsi.png

|

|

| Attachment 8: Screenshot_2021-03-14_Statistics_aidas-gsi.png

|

|

| Attachment 9: 34.png

|

|

| Attachment 10: Screenshot_2021-03-14_Temperature_and_status_scan_aidas-gsi(1).png

|

.png.png)

|

| Attachment 11: Screenshot_2021-03-14_Statistics_aidas-gsi(1).png

|

.png.png)

|

| Attachment 12: 35.png

|

|

| Attachment 13: Screenshot_2021-03-14_Spectrum_Browser_aidas-gsi.png

|

|

| Attachment 14: Screenshot_2021-03-14_Spectrum_Browser_aidas-gsi(1).png

|

.png.png)

|

| Attachment 15: Screenshot_2021-03-12_Spectrum_Browser_aidas-gsi(1).png

|

.png.png)

|

| Attachment 16: 40.png

|

|

| Attachment 17: 41.png

|

|

| Attachment 18: 51.png

|

|

| Attachment 19: 52.png

|

|

| Attachment 20: Screenshot_2021-03-14_Spectrum_Browser_aidas-gsi(3).png

|

.png.png)

|

|

199

|

Sun Mar 14 08:16:00 2021 |

OH PJCS | Sunday 14th March 2021 |

> 08:07 Realised the correlation scalers hadn't been enabled again. Have enabled them now. R56_151

>

> Looking through the merger messages from the nightshift we see bad timestamps in FEE 11. This FEE does not have any scalers going into it.

> It is also the least noisy FEE in the back DSSD

>

> MERGE Data Link (20510): bad timestamp 10 3 0xc2b77eff 0x037a3b92 0x000017f7f37a3b92 0x166c17f7f37a3b92 0x166c17f7f3877262

> MERGE Data Link (20510): bad timestamp 10 3 0xc2827f3a 0x037aa122 0x000017f7f37aa122 0x166c17f7f37aa122 0x166c17f7f3877262

>

> 09:01 System wide checks

>

> Base Current Difference

> aida07 fault 0x8c74 : 0x8c77 : 3

> White Rabbit error counter test result: Passed 11, Failed 1

>

> Understand the status reports as follows:-

> Status bit 3 : White Rabbit decoder detected an error in the received data

> Status bit 2 : Firmware registered WR error, no reload of Timestamp

> Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

>

> Base Current Difference

> aida07 fault 0x2 : 0x5 : 3

> FPGA Timestamp error counter test result: Passed 11, Failed 1

> If any of these counts are reported as in error

> The ASIC readout system has detected a timeslip.

> That is the timestamp read from the time FIFO is not younger than the last

>

> Statistics - attachment 1

> Temperature - attachment 2

> Bias and leakage current - attachment 3

It might be worth considering decreasing the time between the flushing of slower FEEs. Is the Merger waiting for the slower data and causing �deadtime� in the faster ones. Perhaps consider this as a

balancing across the system? |

|

200

|

Sun Mar 14 17:35:05 2021 |

TD, OH | Sunday 14 March - Pulser Walkthrough |

18.01 Pulser walkthrough at end of run S452 file S452/R57_0 ... R57_28

ASIC settings 2019Dec19-16.19.51

DSSSD#1 slow comparator 0xa

DSSSD#2 slow comparator 0xa

DSSSD#3 slow comparator 0xd

BNC PB-5 Pulser

Amplitude1.0V

Attenuation x1

Frequency 2Hz

tau_d 1ms

- polarity

Delay 250ns, tail pulse

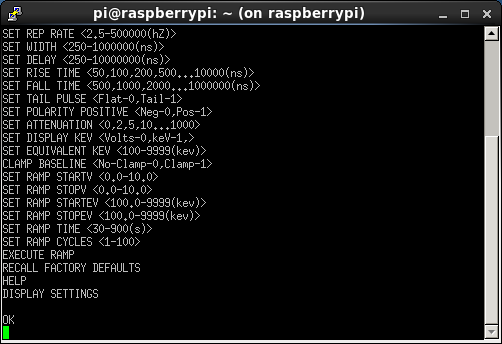

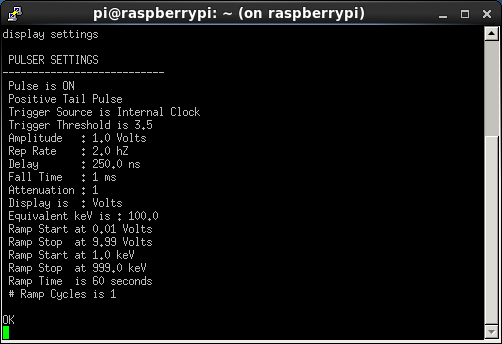

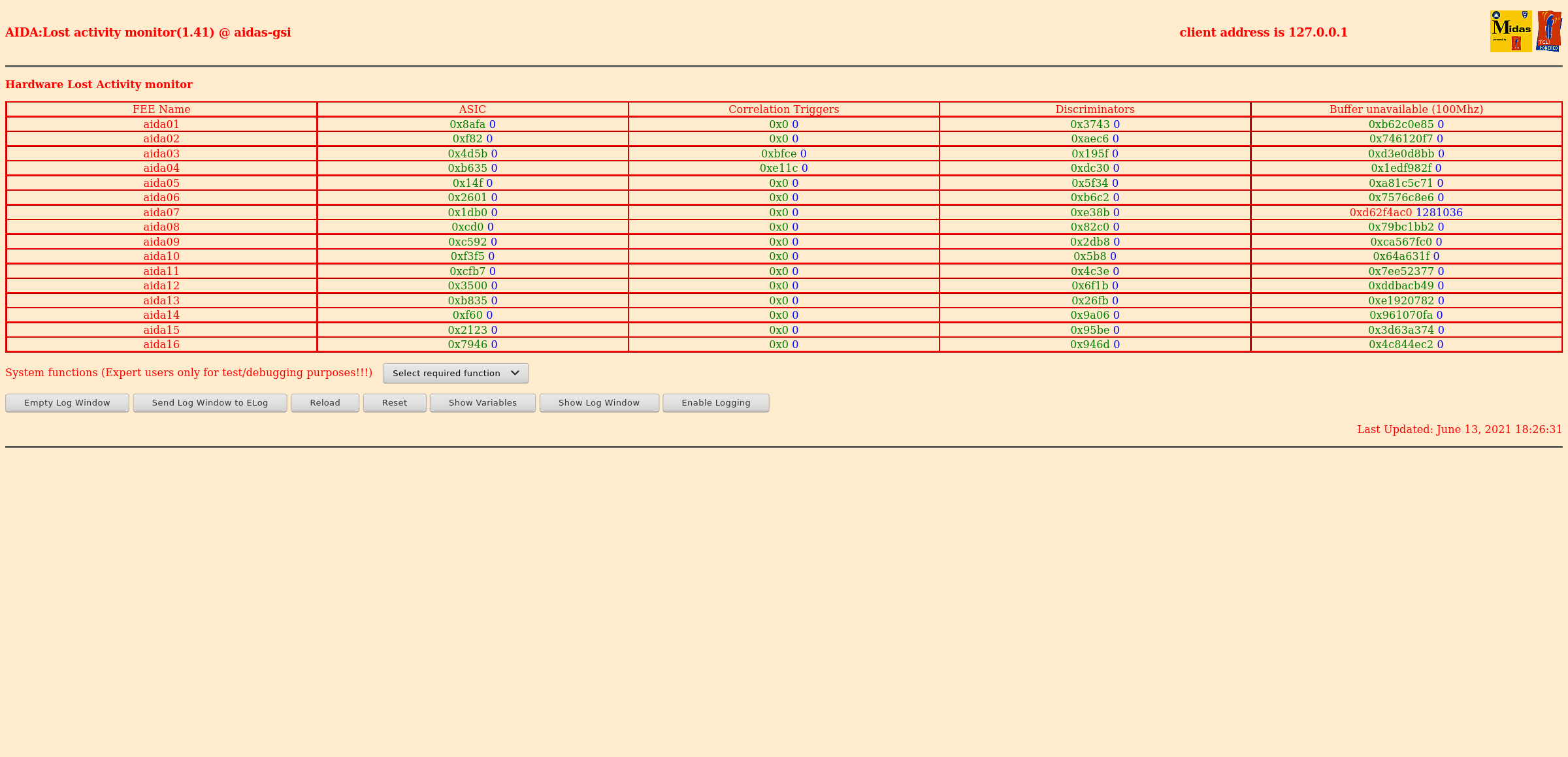

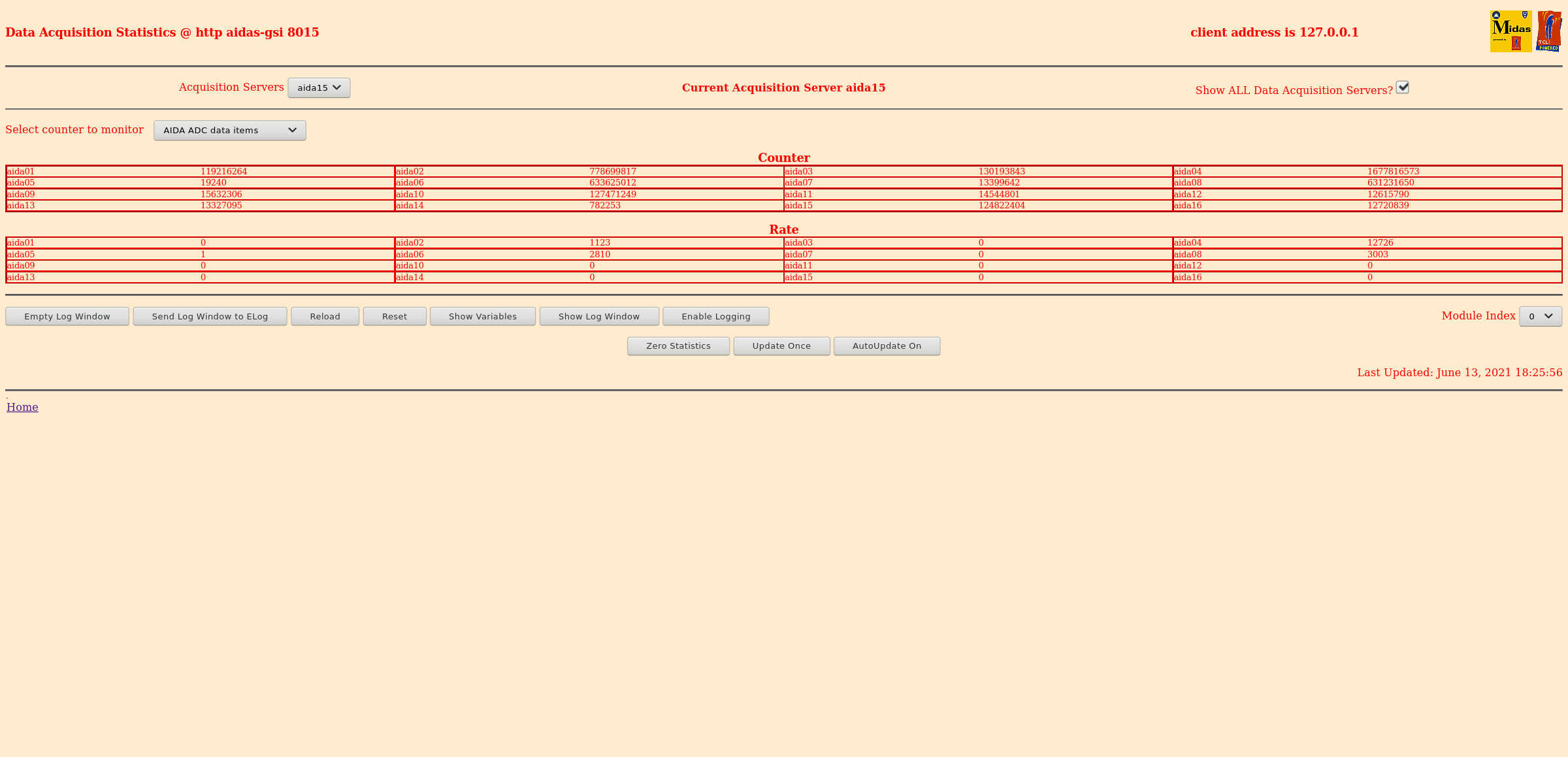

BNC PB-5 settings changed by terminal command line (see attachments 1, 2 & 3)