| |

ID |

Date |

Author |

Subject |

|

|

171

|

Thu Mar 4 11:16:13 2021 |

OH | Further cases of possible database issues |

During testing for the S452 experiment yesterday we were running through the steps of a restart.

The FEEs were not powercycled at this stage but the MIDAS server was restarted.

Initial setup went smoothly and no issues were encountered during setup.

NewMerger and TapeServer were both setup and set to going.

Upon ''Going'' the run control the data transfer for aida09 dropped out.

Going to the NewMerger it could be seen that data was making it through and data items were being merged.

The tapeserver however was seeing no data and neither was the MBS dataspy.

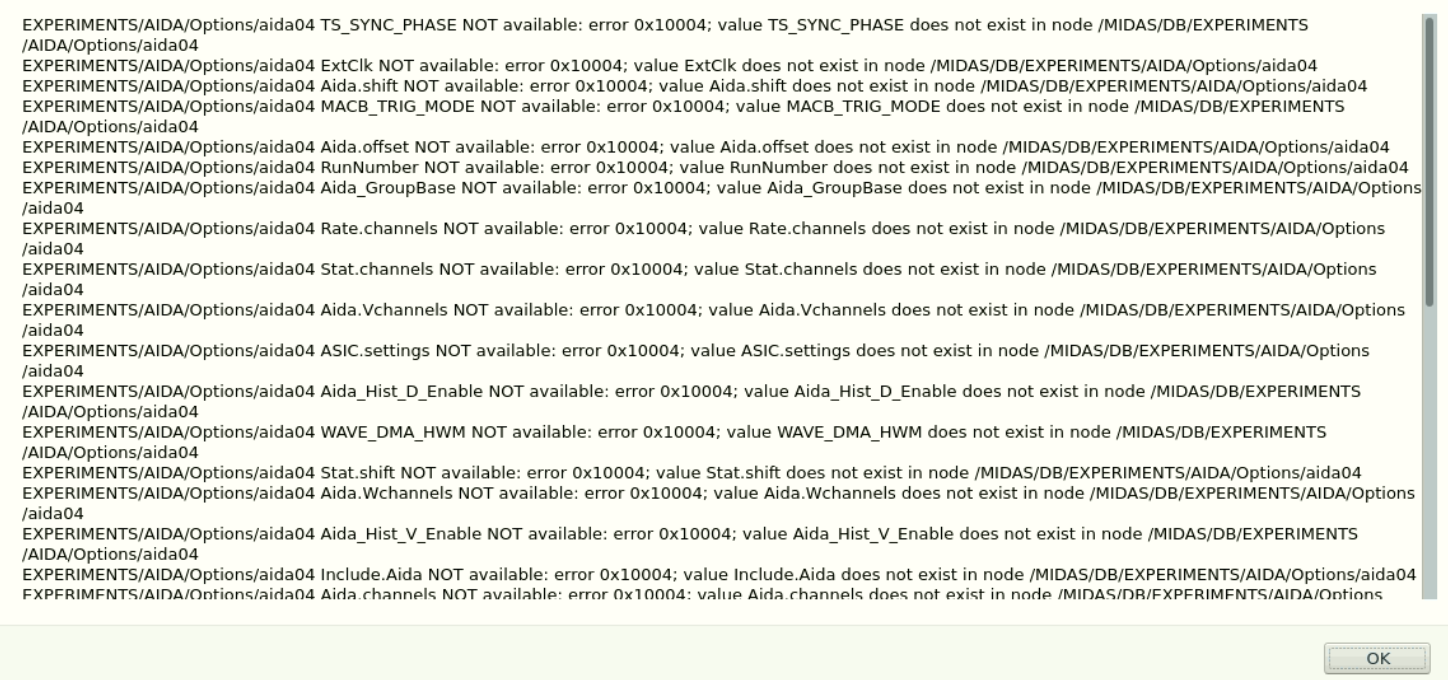

During this time the FEEs became unresponsive likely as their buffers filled. Trying to reset gave the attached errors.

Checking the folder manually it could be seen that the Options file was there.

At this point a powercycle was pewrformed but upong 'Going' the DAQ the same issue was again encountered.

This time we were able to recover control access to the FEEs by running multiple NewMerger sessions which helped clear the buffers.

During our search for the problem we looked at the Options from within MIDAS and could not see anything out of the ordinary.

We also tried restoring the Options from within MIDAS.

We again reached the same issue with the tapeserver.

At this point we restored the Options folder from by copying manually within terminal.

Following this we were able to start the DAQ normally. |

| Attachment 1: ErrorMessage.PNG

|

|

| Attachment 2: errorMessage.txt

|

EXPERIMENTS/AIDA/Options/aida04 TS_SYNC_PHASE NOT available: error 0x10004; value TS_SYNC_PHASE does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 ExtClk NOT available: error 0x10004; value ExtClk does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Aida.shift NOT available: error 0x10004; value Aida.shift does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 MACB_TRIG_MODE NOT available: error 0x10004; value MACB_TRIG_MODE does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Aida.offset NOT available: error 0x10004; value Aida.offset does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 RunNumber NOT available: error 0x10004; value RunNumber does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Aida_GroupBase NOT available: error 0x10004; value Aida_GroupBase does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Rate.channels NOT available: error 0x10004; value Rate.channels does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Stat.channels NOT available: error 0x10004; value Stat.channels does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Aida.Vchannels NOT available: error 0x10004; value Aida.Vchannels does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 ASIC.settings NOT available: error 0x10004; value ASIC.settings does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Aida_Hist_D_Enable NOT available: error 0x10004; value Aida_Hist_D_Enable does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 WAVE_DMA_HWM NOT available: error 0x10004; value WAVE_DMA_HWM does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Stat.shift NOT available: error 0x10004; value Stat.shift does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Aida.Wchannels NOT available: error 0x10004; value Aida.Wchannels does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Aida_Hist_V_Enable NOT available: error 0x10004; value Aida_Hist_V_Enable does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Include.Aida NOT available: error 0x10004; value Include.Aida does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Aida.channels NOT available: error 0x10004; value Aida.channels does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 DataAcqPgm NOT available: error 0x10004; value DataAcqPgm does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Aida_Hist_H_Enable NOT available: error 0x10004; value Aida_Hist_H_Enable does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 DataFormat NOT available: error 0x10004; value DataFormat does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 ASIC_DMA_HWM NOT available: error 0x10004; value ASIC_DMA_HWM does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

EXPERIMENTS/AIDA/Options/aida04 Aida_Hist_L_Enable NOT available: error 0x10004; value Aida_Hist_L_Enable does not exist in node /MIDAS/DB/EXPERIMENTS/AIDA/Options/aida04

STATE for aida01 returned with an error

error: SOAP http transport timed out after 20000 ms

NONE

error: SOAP http transport timed out after 20000 ms

while executing

"$transport $procVarName $url $req"

(procedure "::SOAP::invoke" line 18)

invoked from within

"::SOAP::invoke ::SOAP::_DataAcquisitionControlClient__GetState"

("eval" body line 1)

invoked from within

"eval ::SOAP::invoke ::SOAP::_DataAcquisitionControlClient__GetState $args"

(procedure "DataAcquisitionControlClient__GetState" line 1)

invoked from within

"DataAcquisitionControlClient__GetState"

|

|

|

414

|

Fri Apr 8 08:59:42 2022 |

OH, NH | Friday 8th April |

09:59 Noticed that the right hand ribbon cable for aida07 was offset vertically by 1. i.e. Only 1 of the 2 rows of pins in. Unbiassed detectors and reconnected.

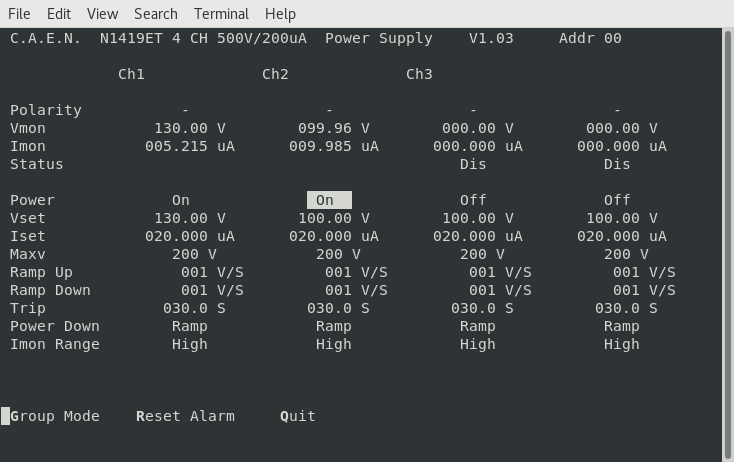

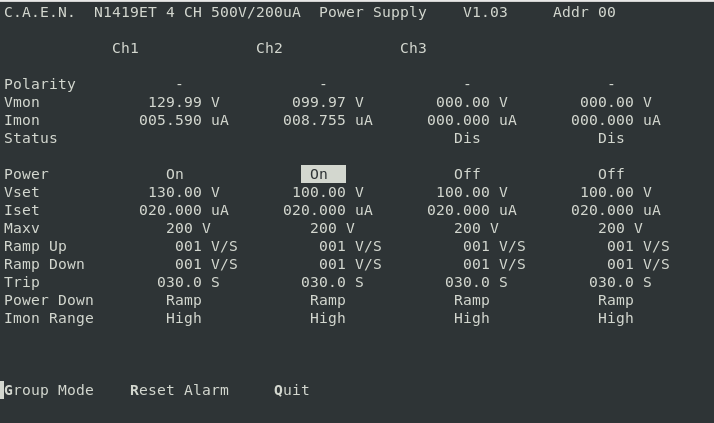

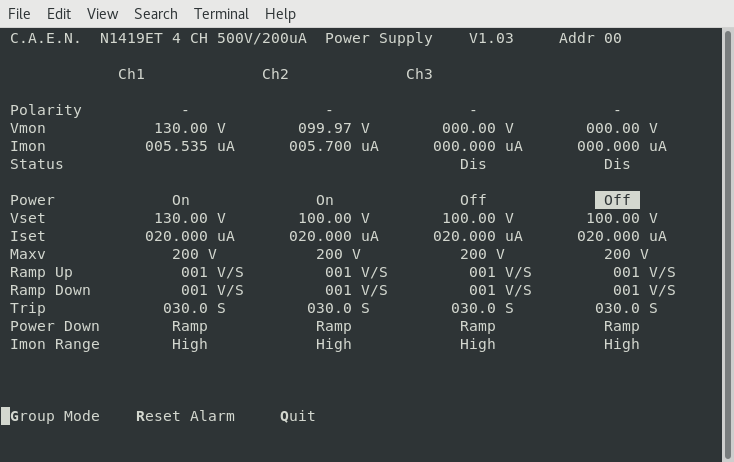

Rebiassed detectors - leakage current on DSSD2 increased to 9.96uA - Attachment 1

Power cycling FEEs

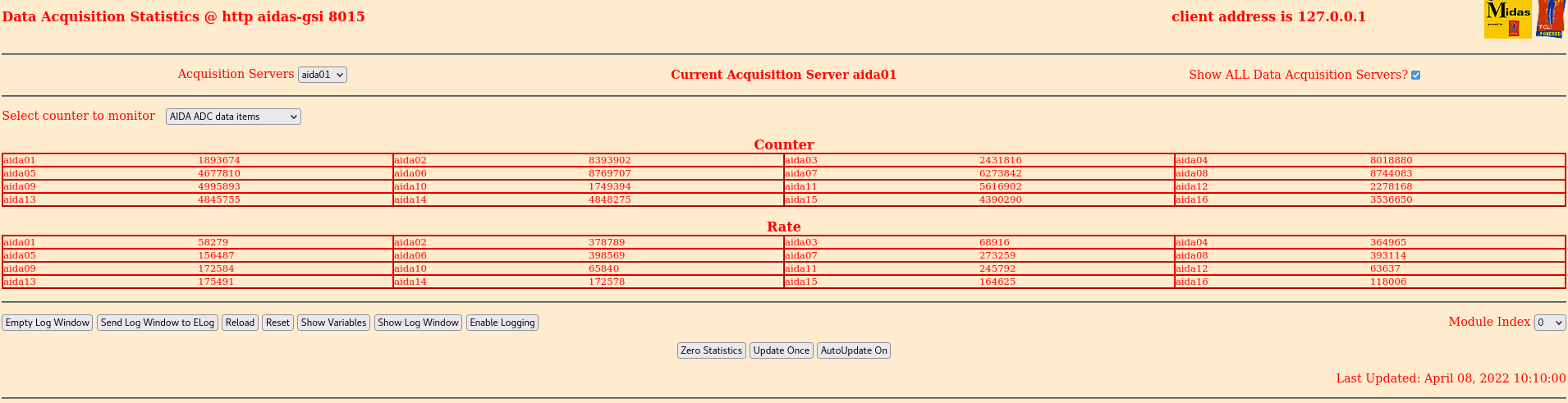

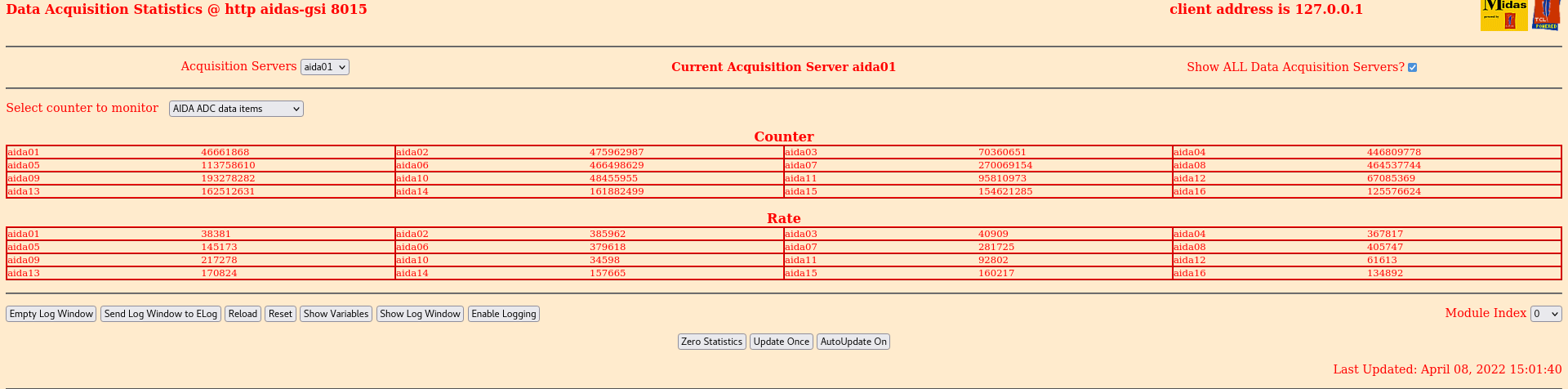

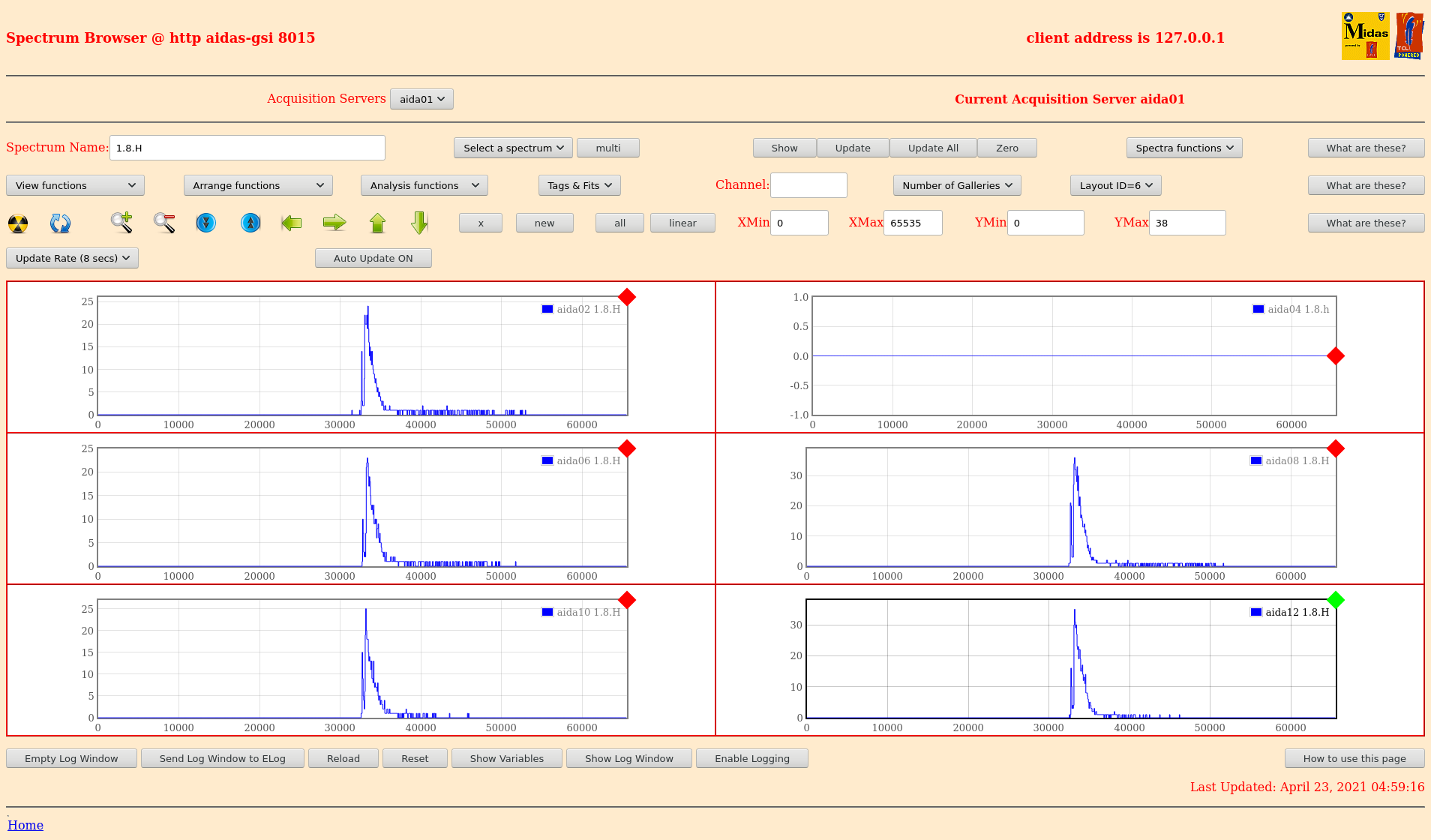

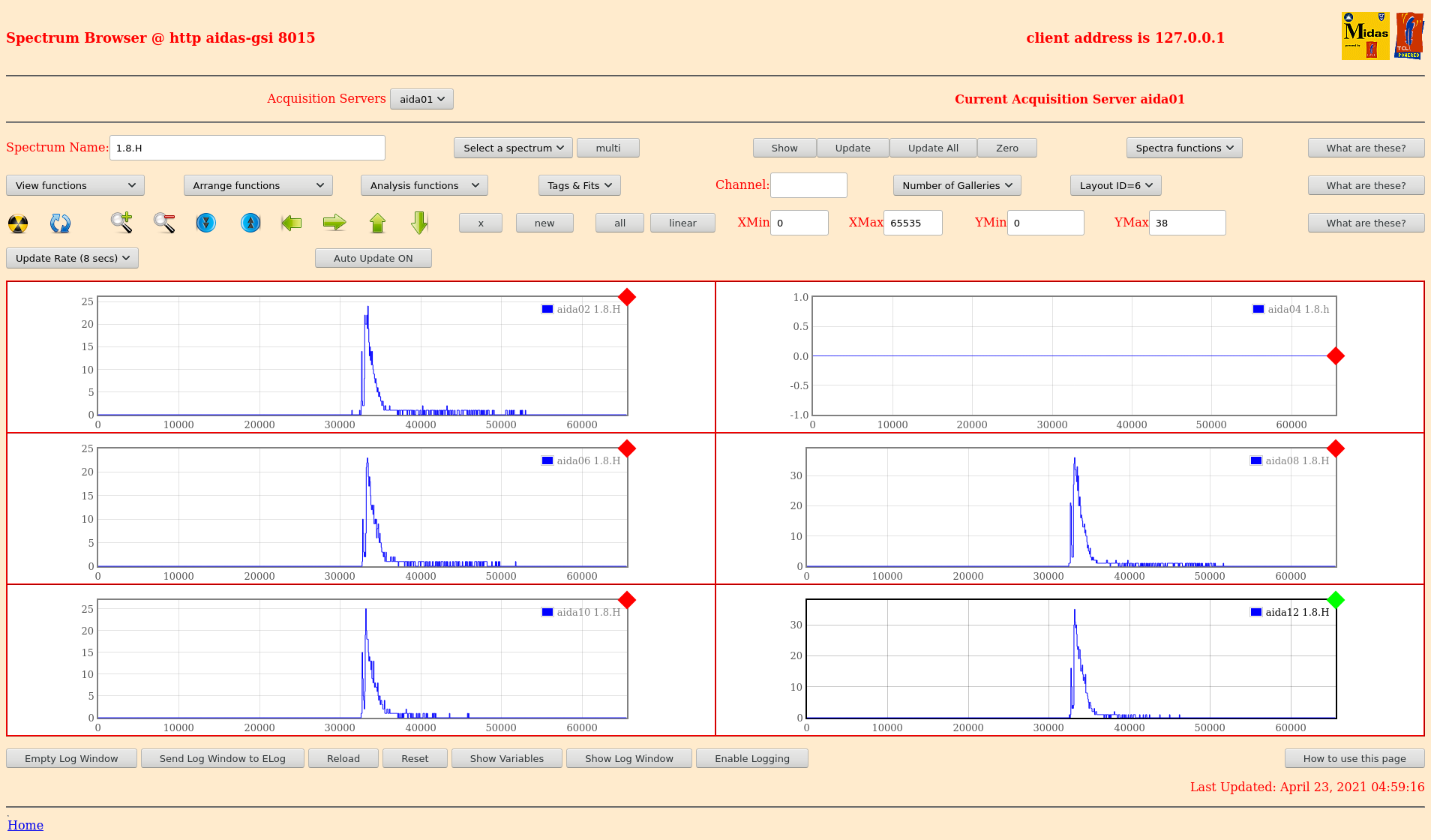

Following restart the FEEs show some improvement in rates - attachment 2

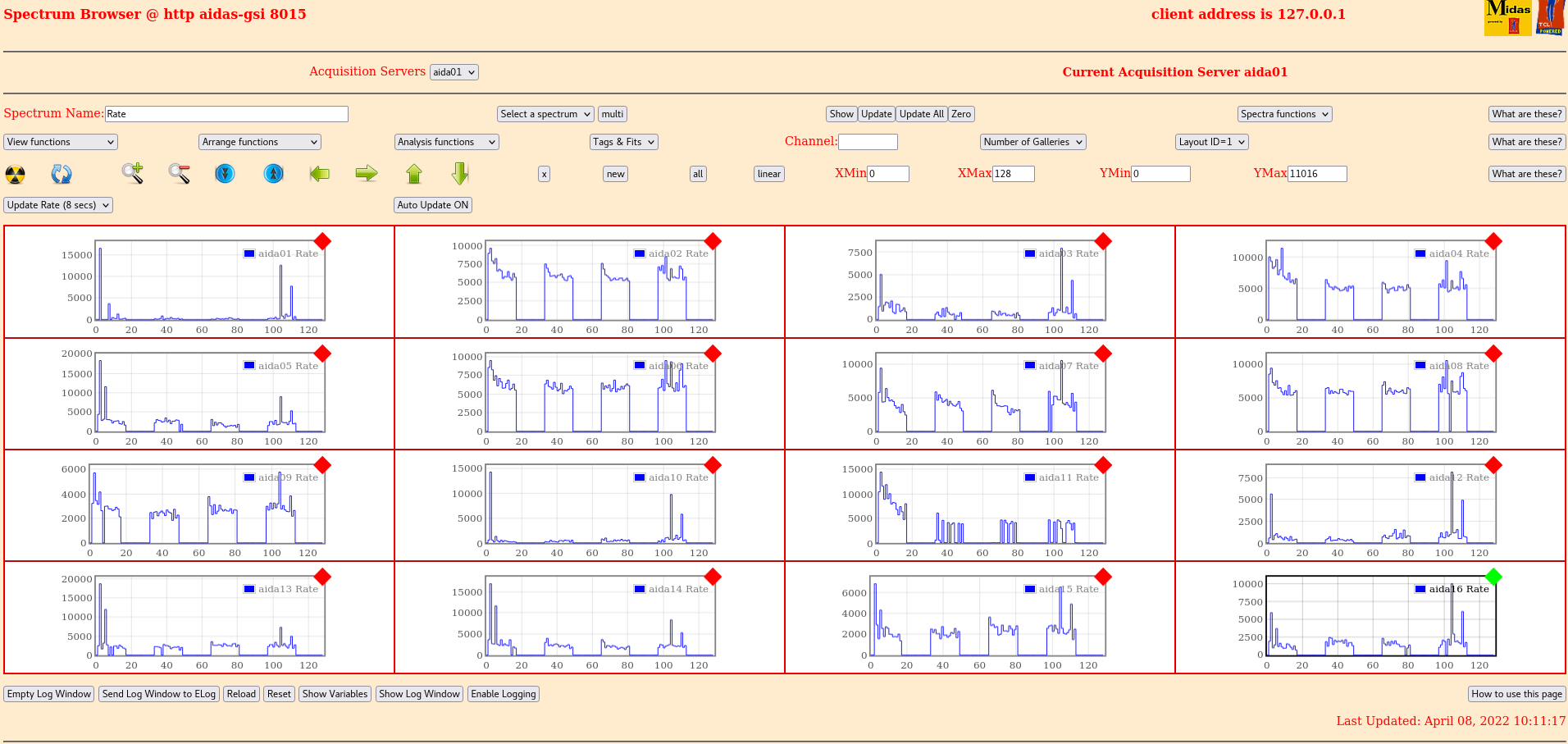

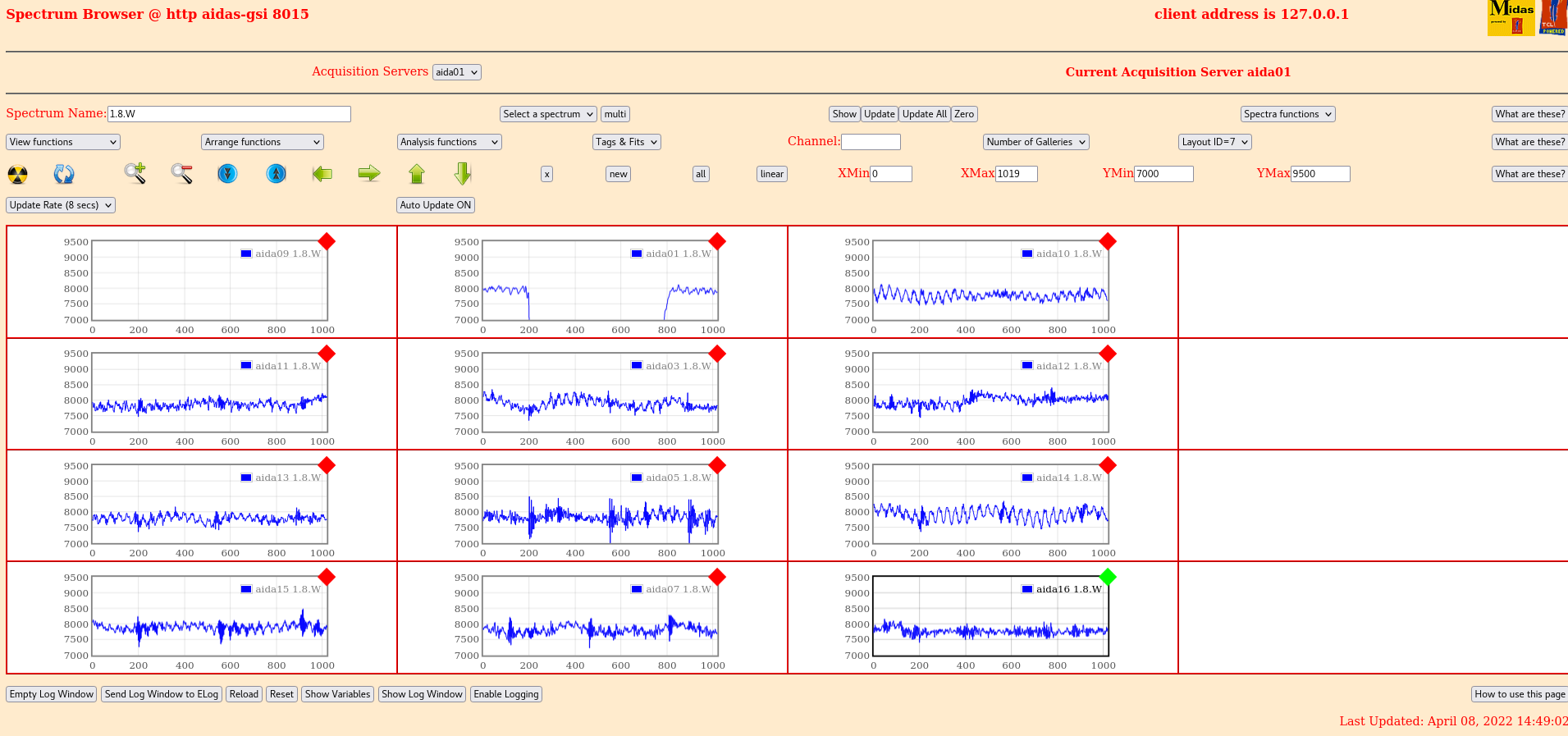

Rate spectra - attachment 3

Still issues with aida11 in the rate spectra (Likely a misaligned ERNI connector)

Pulser on rate spectra - attachment 4

Pulser off rate spectra - attachment 5

We can see that with the pulser on there are events in the channels in aida01 and aida11

With the pulser off these channels disappear.

ERNI connector is then likely aligned the issue is more likely the DSSD ribbon cable is misaligned.

Taking bias off to investigate.

10:39 Could not observe anything out of alignement about either the connectors or the adaptor boards

Note that after pushing on the connector AIDA01 had largely recovered

13:30 Top of snout taken off while mounted in S4. It was observed that one of the ribbon cables for aida11 was off by 1 row.

This was corrected in situ and the snout was put back together and made light tight again.

Oddly leakage current still the same - DSSD2 has come down though - attachment 6

FEEs powercycled for new tests

Half the channels in aida11 had appeared again

Took apart once more and found the other header also off by one row which has been corrected

FEEs powercycled for new test

All of aida11 now showing - attachment 7

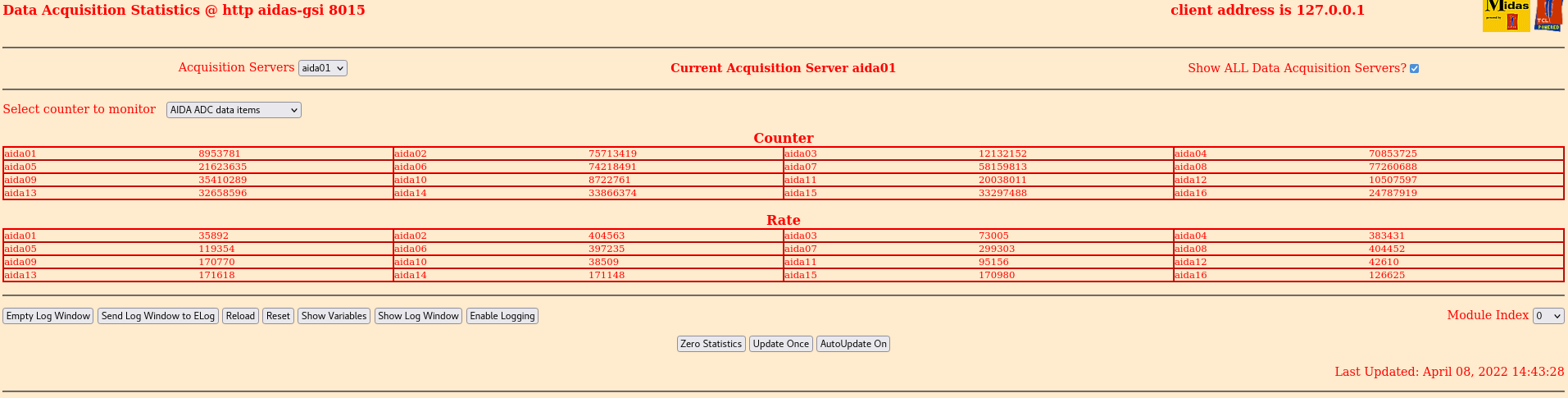

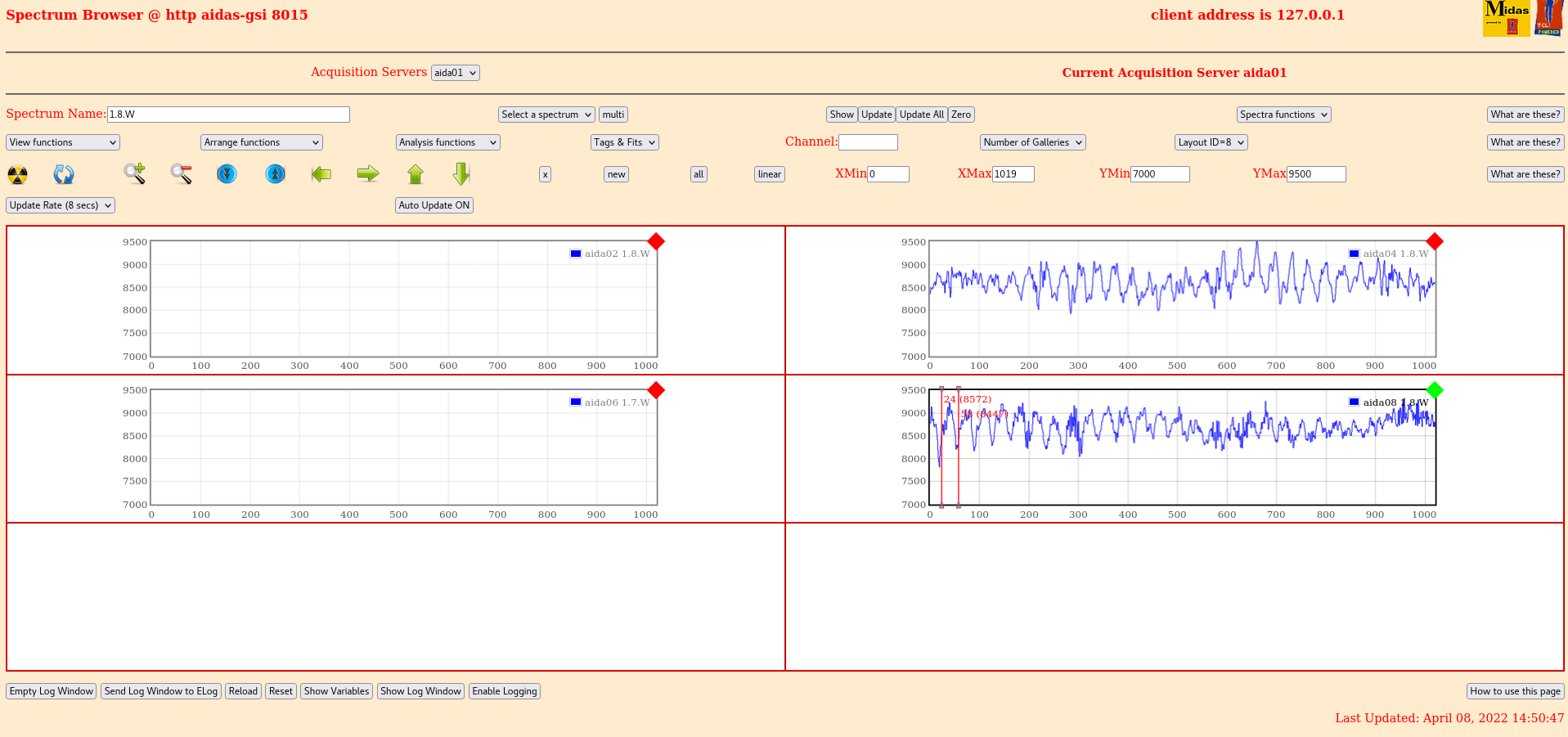

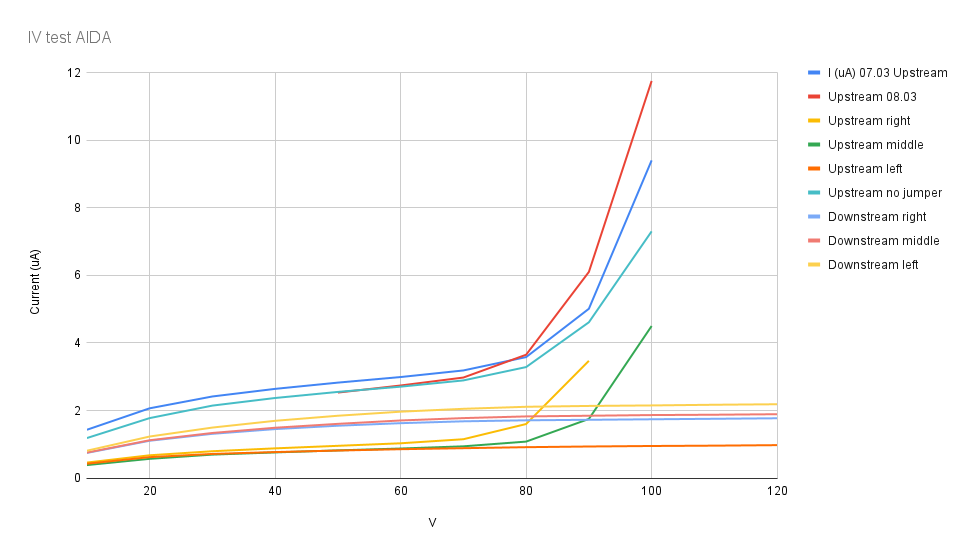

Statistics at 0xa shown in attachment 8

All p+n for DSSD1 are good (aida01, 03, 09, 10, 11 and 12)

p+n for DSSD2 are so so (aida05, 07, 13, 14, 15 and 16)

All n+n 2, 4, 6 and 8 are poor still

14:50 p+n waveforms - attachment 9

n+n waveforms - attachment 10

Current jumper configuration

LK1 (Bias ground) on FEEs 6 and 8

LK2&4 on all p+n

LK3 on aida03 and aida07 (Bottom middle)

15:00 Investigated whether there was a light leak. Placed black material over snout.

Leakage on DSSD2 dropped to 5.6 - attachment 11

There was a light leak

Stats have decreased slightly - attachment 12

16:00 Move raspberry pis atop 5mm alminimum plate to keep away from FEE64 PSUs

No change

16:30 Remove pulser network from all FEEs

Rates get noticably worse in many FEEs... why?

Stats - attachment 13

Possible ideas include braid touching things it shouldn't (Adapter PCBs?) |

| Attachment 1: 220408_1000_bias.png

|

|

| Attachment 2: 220409_1010_Stats.png

|

|

| Attachment 3: 220409_1011_rate.png

|

|

| Attachment 4: 220408_1358_bias.png

|

|

| Attachment 5: 220408_1444_rate.png

|

|

| Attachment 6: 220408_1444_stats.png

|

|

| Attachment 7: 220408_1449_layout7.png

|

|

| Attachment 8: 220408_1451_layout8.png

|

|

| Attachment 9: 220308_1459_bias.png

|

|

| Attachment 10: 220408_1503_stats_post_light.png

|

|

| Attachment 11: 2022-04-08_16-26-30_Stats_No_Pulser.png

|

|

|

|

531

|

Fri Mar 8 16:05:57 2024 |

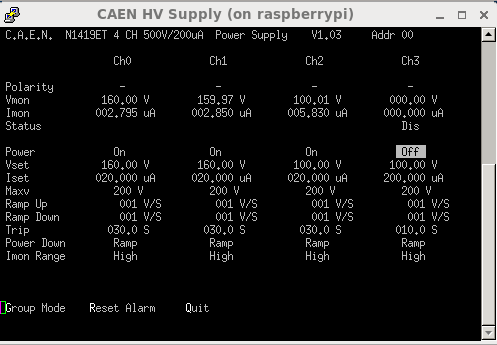

JB, CC, TD, NH | Friday 8 March |

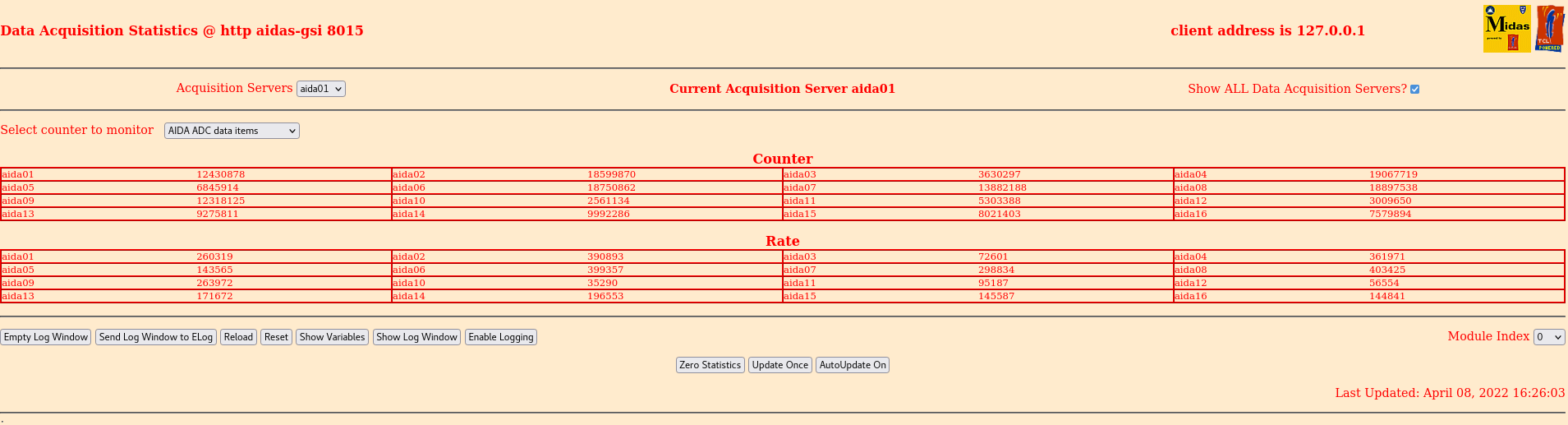

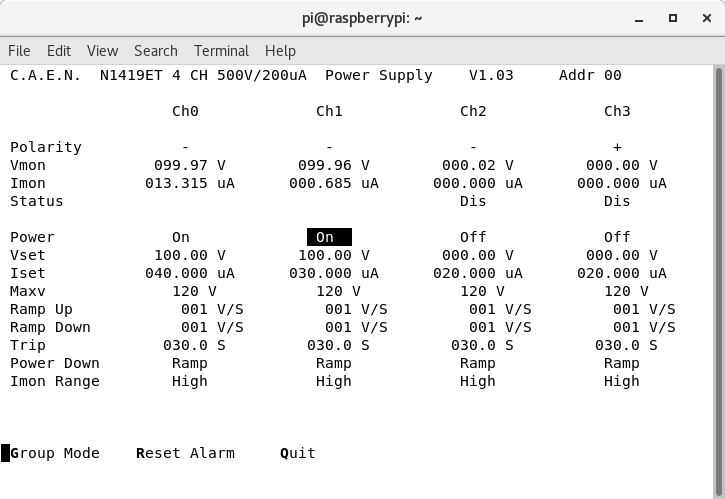

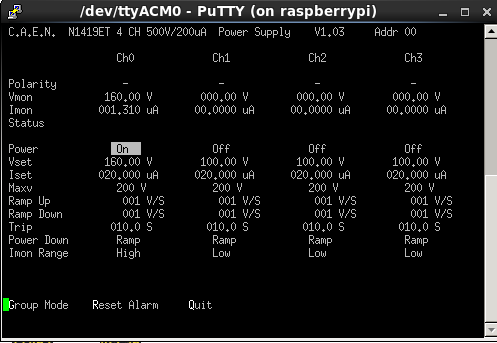

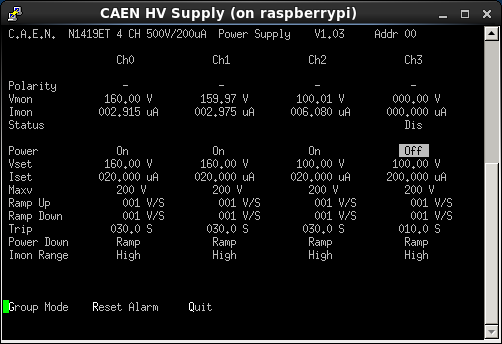

Bias tests of AIDA on individual wafers and in parallel. Spreadsheet can be found in attachment 1, and graphic results can be seen in Attachment 2. Summary: Upstream detector cannot be biased in parallel nor individually. Downstream detector can be biased with positively and each wafer can individually be biased negatively. In parallel, it was not possible to bias the downstream detector negatively as indicated by the tests below.

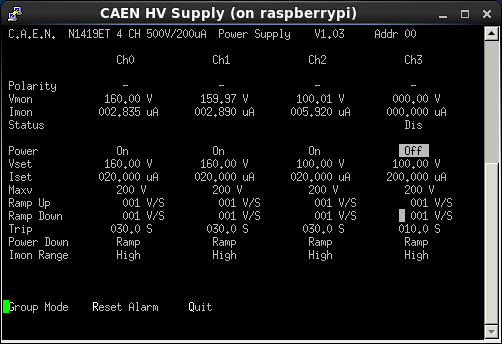

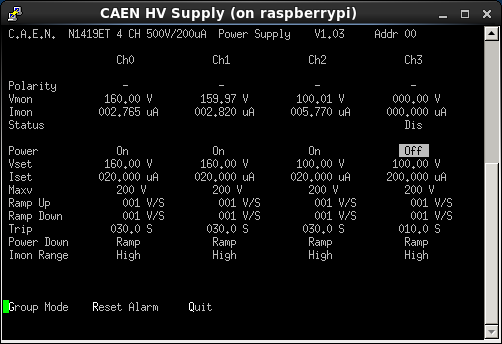

Test downstream DSSSD with positive polarity bias

Configuration as follows:

CAEN N1419ET ch #3 connected to LHS FEE64 adaptor PCB ( looking upstream ) - LK1 *not* fitted LK1 fitted to 3x ( top )

FEE64 adaptor PCBs Lemo 00.250 jumper cables from/to GND terminals of 3x ( top )

FEE64 adaptor PCBs *and* LHS FEE64 adaptor PCB 1x ( bottom, middle )

FEE64 adaptor PCB connected to ribbon cables but not otherwise connected to anything, LK3 fitted Total 5x adaptor PCBs installed

No other LKs fitted

| Bias Voltage (V) |

Current (uA) |

| +10 |

2.150 |

| +20 |

3.300 |

| +30 |

4.035 |

| +40 |

4.550 |

| +50 |

4.955 |

| +60 |

5.255 |

| +70 |

5.490 |

| +80 |

5.650 |

| +90 |

5.730 |

| +100 |

5.780 |

| +110 |

5.825 |

| +120 |

5.860 |

Nominal V-I curve, stable leakage current. Attachment 3.

Following this success we attempted to repeat test using negative polarity bias

Configuration as follows:

CAEN N1419ET ch #1 connected to ( top, left )

FEE64 adaptor PCB ( looking upstream ) LHS

FEE64 adaptor PCB ( looking upstream ) - LK1 fitted Lemo 00.250 jumper cables from/to BIAS terminals of 3x ( top )

FEE64 adaptor PCBs Lemo 00.250 jumper cable from/to GND terminals of LHS and ( top, left )

FEE64 adaptor PCBs 1x ( bottom, middle )

FEE64 adaptor PCB connected to ribbon cables but not otherwise connected to anything,

LK3 fitted Total 5x adaptor PCBs installed No other LKs fitted With detector bias

-20V we continue to observe the leakage current cycling between 0 and ~2uA with a frequency ~1Hz ( as before )

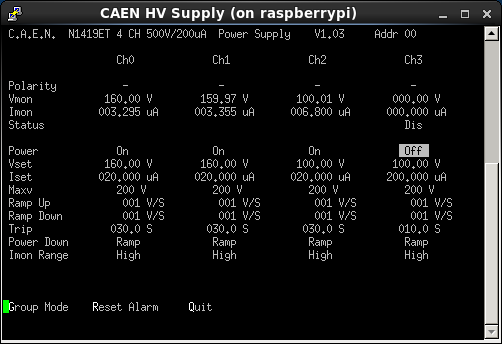

Copy configuration used for upstream DSSSD test ( which was successful albeit there was detector breakdown at bias voltages > c. 90V )

CAEN N1419ET ch #1 connected to ( bottom, left )

FEE64 adaptor PCB ( looking upstream ) LHS

FEE64 adaptor PCB ( looking upstream ) - LK1 fitted Lemo 00.250 jumper cables from/to BIAS terminals of 3x ( bottom )

FEE64 adaptor PCBs Ground cable jumpered from/to GND terminals LHS, ( left, bottom ), RHS and all 3x top FEE64 adaptor PCBs ( bottom, middle )

FEE64 adaptor PCB LK3 fitted Total 8x adaptor PCBs installed

No other LKs fitted With detector bias -20V we observe leakage current of ~2-3uA.

Current unstable - variations 10-100nA over periods of several seconds Although the leakage current is unstable this is an improvement over previous tests with negative bias. The duplication of upstream and downstream configurations suggests that for some unknown reason it is necessary to connect all 8x FEE64 adaptor PCBs whereas our expectation was that only 4x were necessary.

Summary: Upstream DSSSD Si wafers 1 & 2 breakdown for bias > c. 90V Si wafer 3 OK to 120V Positive bias - not tested Negative bias OK - leakage current stable to c. 90V Downstream DSSSD Si wafers 1, 2 & 3 OK to 120V Positive bias OK Negative bias - leakage current unstable

To do:

1) Disconnect ribbon cables from p+n junction FEE64 adaptor PCBs of upstream DSSSD, apply c. 100V bias and check leakage current is zero i.e. eliminate shorts in PCBs

2) Check that all ribbon cables are properly seated in the adaptor PCBs

3) Check all adaptor PCB connector pins are OK: will need to remove ribbon cables

4) If/when you open check seating of all Kapton PCBs in the DSSSD connectors *and* carefully check that ribbon cable and Kapton PCB connectors are aligned and not out by 1 or 2 rows say.

|

| Attachment 1: IV_test_AIDA.xlsx

|

| Attachment 2: chart.png

|

|

| Attachment 3: Downstream_positive_bias_vs._Current_(uA).png

|

.png.png)

|

|

|

299

|

Fri May 7 13:11:22 2021 |

NH | Friday 7th May |

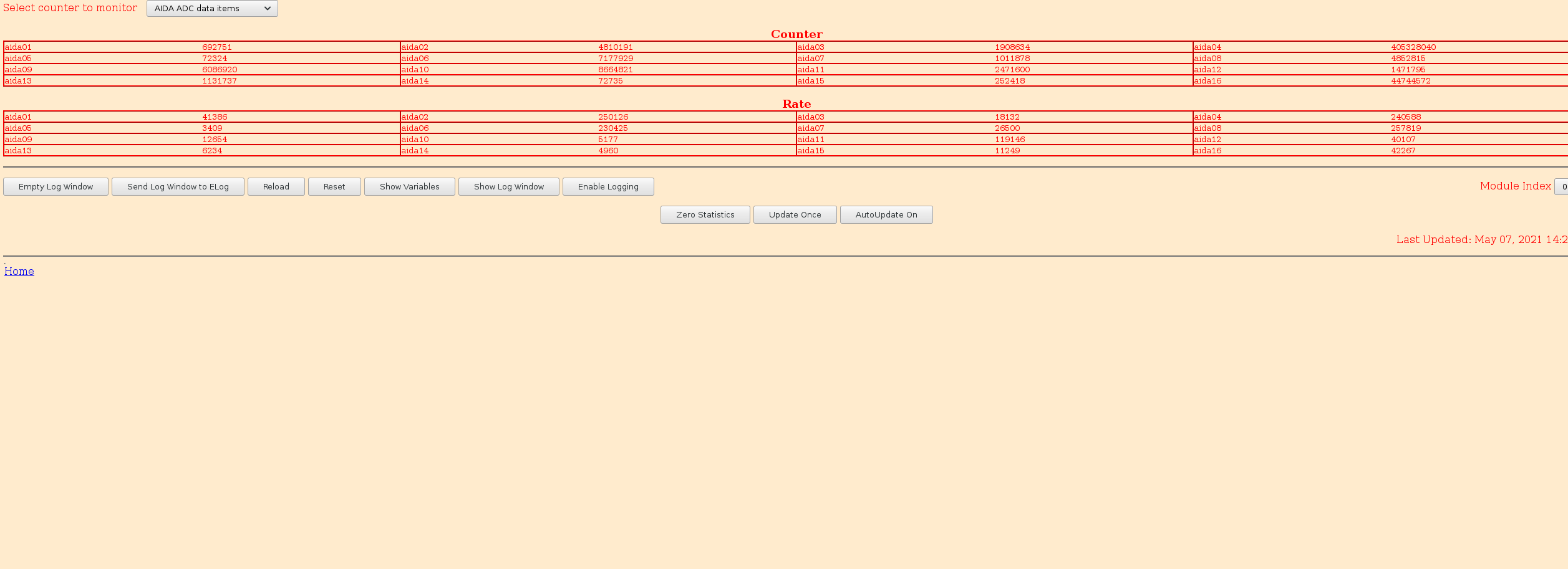

14:11 - Alpha has been running most of morning

Just saw rates in tape spike to 6 MB/s...

Stop output to tape and look:

ASIC check & load... all rates except aida04 back to 0

Start output to tape

Back to ~300 KB/s

R6_49 will be affected by this.

Others seem OK

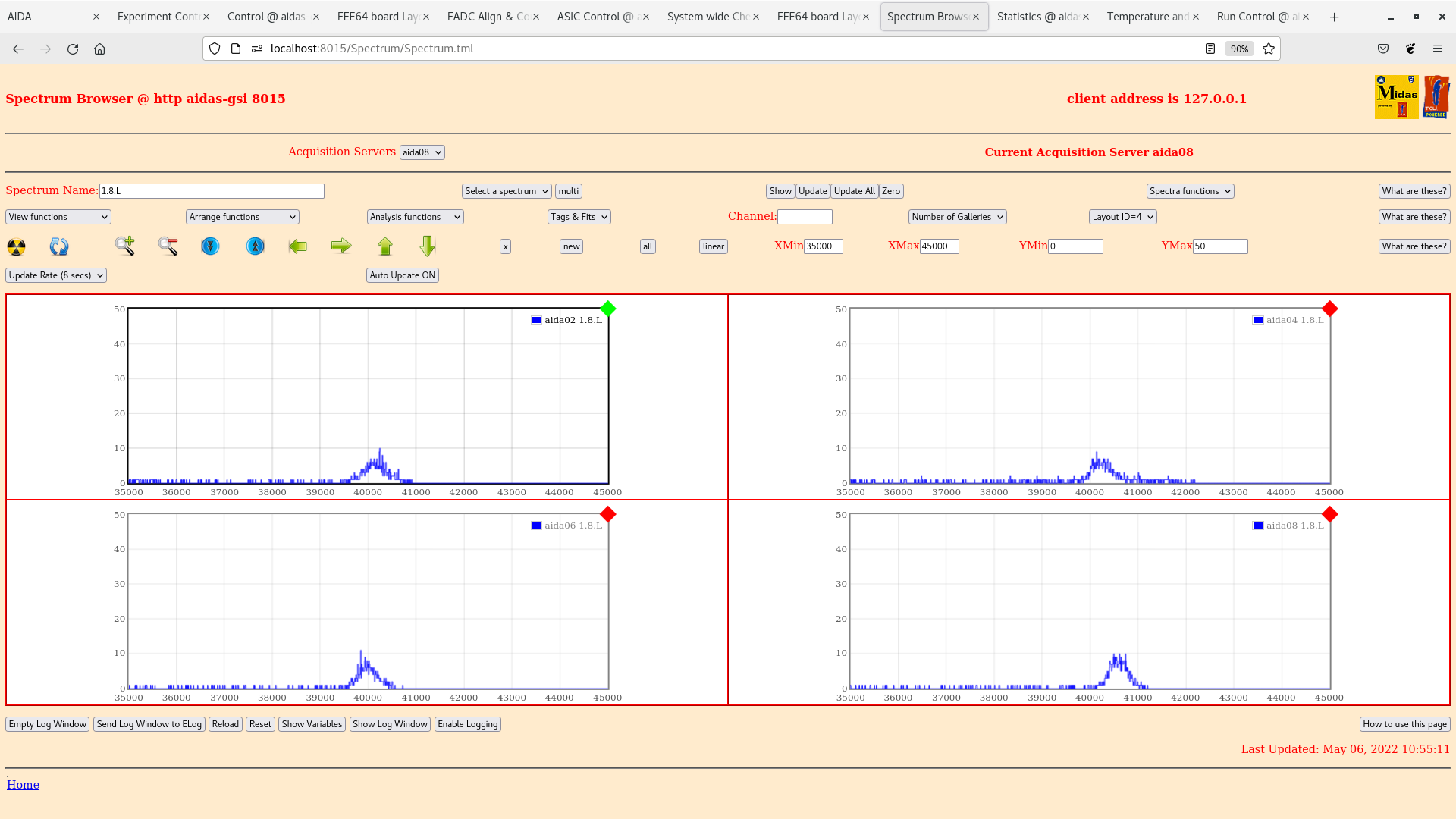

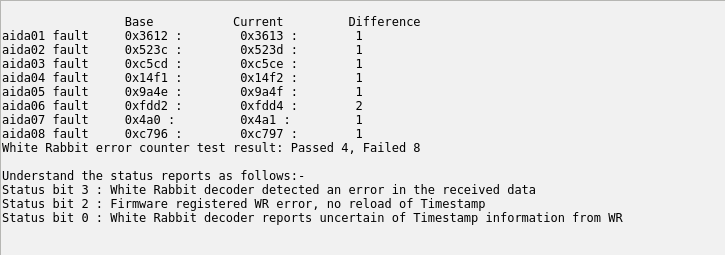

System wide check failures:

Base Current Difference

aida01 fault 0xb405 : 0xb406 : 1

aida02 fault 0xefc7 : 0xefc8 : 1

aida03 fault 0xdaab : 0xdaac : 1

aida04 fault 0x8f7c : 0x8f7d : 1

aida05 fault 0xb5bd : 0xb5be : 1

aida06 fault 0xeff1 : 0xeff2 : 1

aida07 fault 0x8f57 : 0x8f58 : 1

aida08 fault 0xbef7 : 0xbef8 : 1

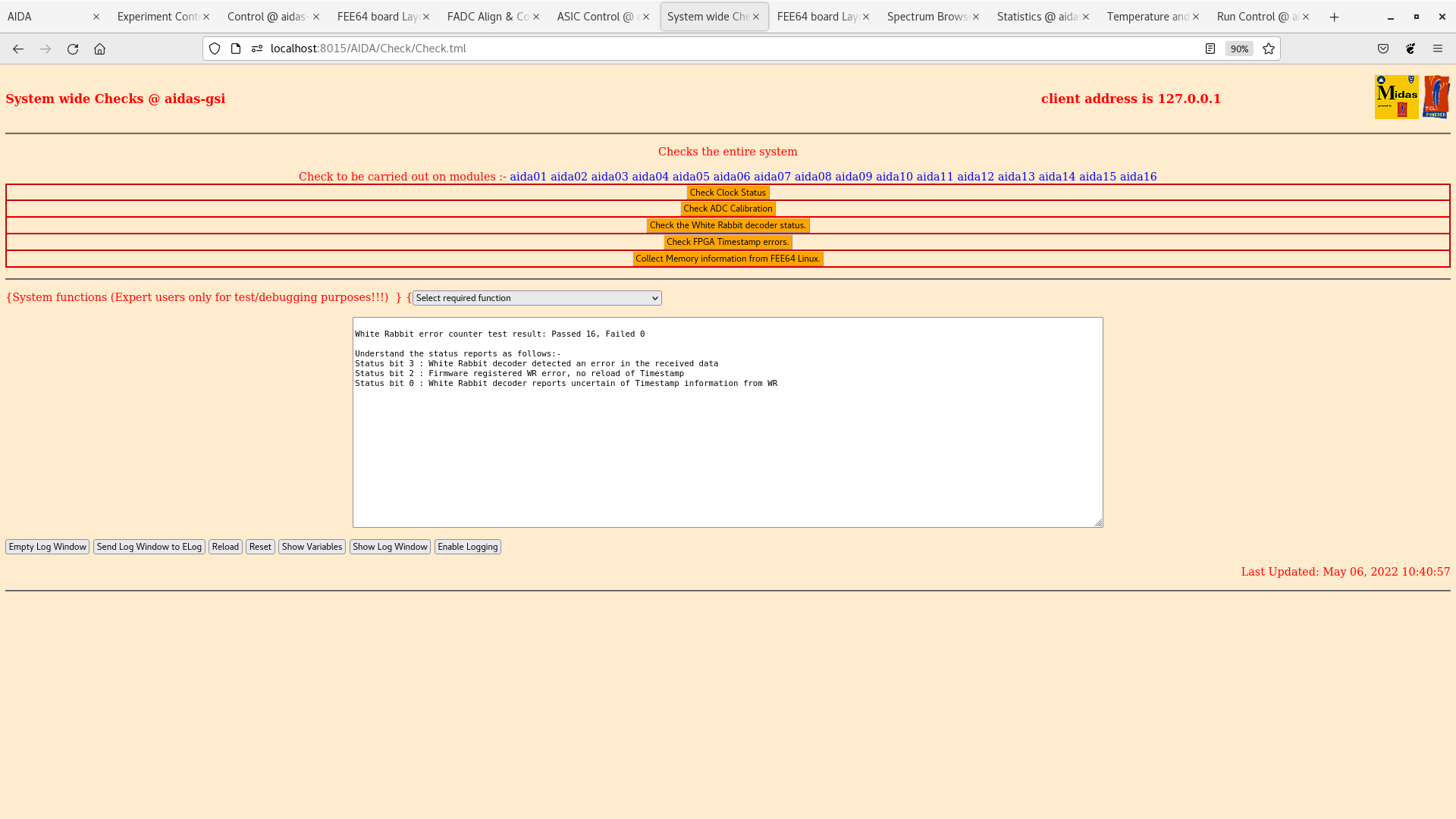

White Rabbit error counter test result: Passed 8, Failed 8

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

Base Current Difference

aida12 fault 0x0 : 0x200 : 512

aida13 fault 0x0 : 0x61 : 97

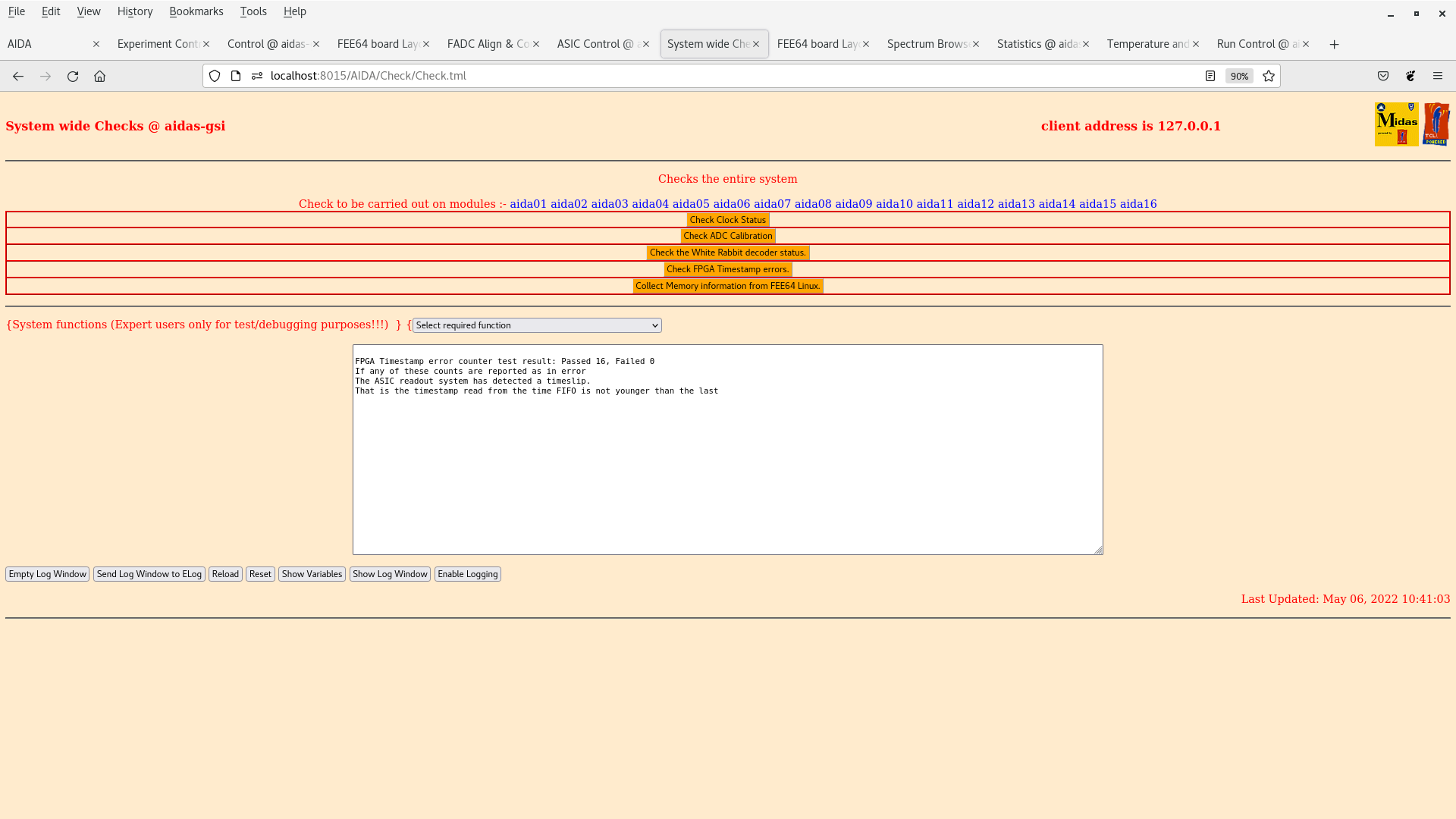

FPGA Timestamp error counter test result: Passed 14, Failed 2

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

The FPGA errors seem to come on FEEs with no WR errors or clock errors (including Lock/PLL page)

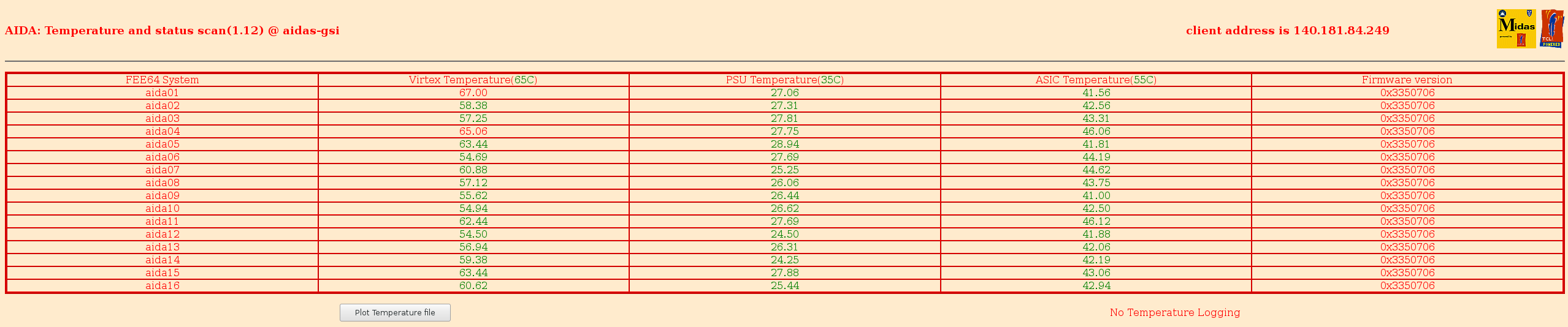

Temps & Rates OK

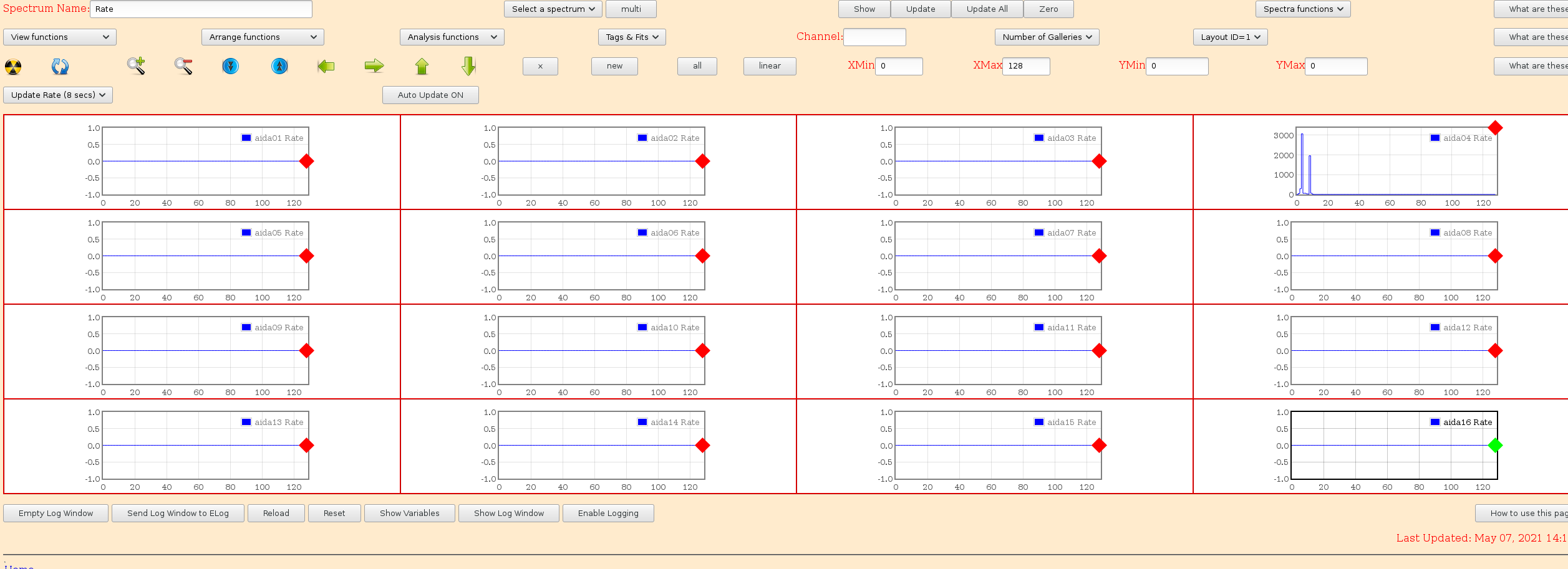

Will now stop Alpha run and check noise situation

Run stopped at R6_49

Switching to nostorage (NOTAPE/R2)

Set ASICs to threshold 0xa, Rates OK

Rate to Tape/MBS ca 9 MB/s

No change to situation since yesterday... good sign

During MBS test aida13 rebooted... crash log from ttyUSB5 attached

It was later noticed connector half off in aida05, reseated and after some time got noise levels OK again...

cables on top very sensitive, indicative of issues inside maybe(?). We avoid touching AIDA for now :)

A power cycle of all FEEs was performed after aida13's reboot to make sure things are good.

All systems check OK |

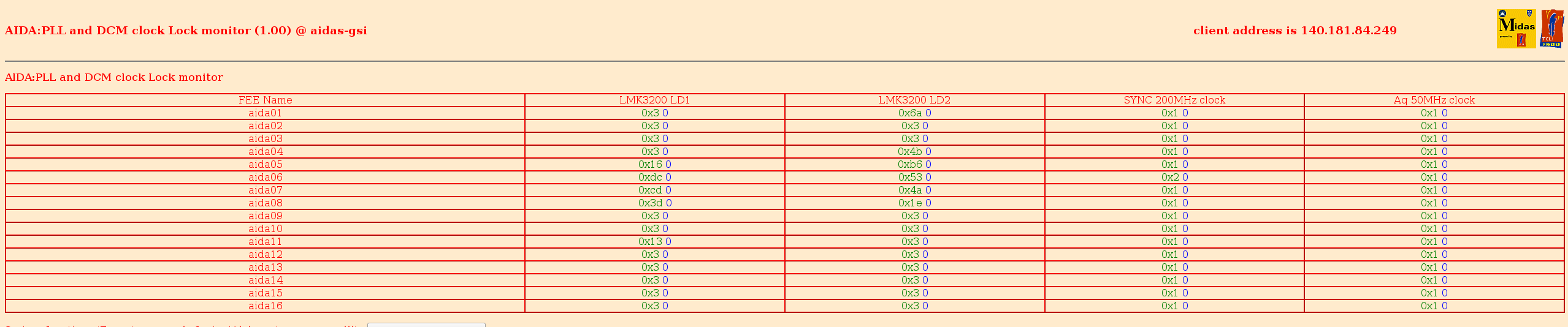

| Attachment 1: elog_locks.png

|

|

| Attachment 2: elog_temps.png

|

|

| Attachment 3: elog_rates.png

|

|

| Attachment 4: elog_rates1.png

|

|

| Attachment 5: aida13.txt

|

06/19:25:39|Data Acquisition Statistics counters now cleared^M

06/19:25:55|Clear Statistics (1)^M

06/19:25:55|------------[ cut here ]------------^M

07/15:23:58|kernel BUG at mm/slab.c:2974!^M

07/15:23:58|Oops: Exception in kernel mode, sig: 5 [#1]^M

07/15:23:58|PREEMPT Xilinx Virtex440^M

07/15:23:59|Modules linked in: aidamem xdriver xh_spidev_register^M

07/15:23:59|NIP: c009211c LR: c00920b0 CTR: 00000007^M

07/15:23:59|REGS: c0391bf0 TRAP: 0700 Not tainted (2.6.31)^M

07/15:23:59|MSR: 00021000 <ME,CE> CR: 24022048 XER: 00000000^M

07/15:23:59|TASK = c036e318[0] 'swapper' THREAD: c0390000^M

07/15:23:59|GPR00: 00000001 c0391ca0 c036e318 c680daf0 c694003c 0000000a c6940020 00000009 ^M

07/15:23:59|GPR08: 0000001b c680dae0 00000cf0 c680dae0 24008042 00005aa8 c03a0000 00000020 ^M

07/15:23:59|GPR16: c0390000 c03a069c c03a0000 c038c384 c038cc18 00000020 00000000 00200200 ^M

07/15:23:59|GPR24: 00100100 c0390000 00000000 c680dae8 c680dae0 c680ae00 00000006 c680e400 ^M

07/15:23:59|NIP [c009211c] cache_alloc_refill+0x130/0x608^M

07/15:23:59|LR [c00920b0] cache_alloc_refill+0xc4/0x608^M

07/15:23:59|Call Trace:^M

07/15:23:59|[c0391ca0] [c00920b0] cache_alloc_refill+0xc4/0x608 (unreliable)^M

07/15:23:59|[c0391d00] [c00927d8] kmem_cache_alloc+0xc4/0xcc^M

07/15:23:59|[c0391d20] [c0042420] __sigqueue_alloc+0x50/0xb8^M

07/15:23:59|[c0391d40] [c0042938] __send_signal+0x78/0x260^M

07/15:23:59|[c0391d70] [c0042f78] group_send_sig_info+0x70/0x9c^M

07/15:24:00|[c0391da0] [c00438a8] kill_pid_info+0x48/0x8c^M

07/15:24:00|[c0391dc0] [c0038e8c] it_real_fn+0x1c/0x30^M

07/15:24:00|[c0391dd0] [c0050c40] hrtimer_run_queues+0x184/0x240^M

07/15:24:00|[c0391e30] [c0040ba8] run_local_timers+0x10/0x2c^M

07/15:24:00|[c0391e40] [c0040bf4] update_process_times+0x30/0x70^M

07/15:24:00|[c0391e60] [c005a000] tick_periodic+0x34/0xe8^M

07/15:24:00|[c0391e70] [c005a0d4] tick_handle_periodic+0x20/0x120^M

07/15:24:00|[c0391eb0] [c000af70] timer_interrupt+0xa4/0x10c^M

07/15:24:00|[c0391ed0] [c000e9c4] ret_from_except+0x0/0x18^M

07/15:24:00|[c0391f90] [c0006fac] cpu_idle+0xcc/0xdc^M

07/15:24:00|[c0391fb0] [c000172c] rest_init+0x70/0x84^M

07/15:24:00|[c0391fc0] [c0341854] start_kernel+0x230/0x2ac^M

07/15:24:00|[c0391ff0] [c0000204] skpinv+0x194/0x1d0^M

07/15:24:00|Instruction dump:^M

07/15:24:00|2f1e0000 409900f4 387c0010 3b7c0008 80dc0000 7f9c3000 419e014c 81060010 ^M

07/15:24:00|801d001c 7c004010 38000000 7c000114 <0f000000> 81260010 801d001c 7f804840 ^M

07/15:24:00|Kernel panic - not syncing: Fatal exception in interrupt^M

07/15:24:00|Call Trace:^M

07/15:24:00|[c0391a40] [c0005de8] show_stack+0x44/0x16c (unreliable)^M

07/15:24:00|[c0391a80] [c00345bc] panic+0x94/0x168^M

07/15:24:01|[c0391ad0] [c000bd44] die+0x178/0x18c^M

07/15:24:01|[c0391af0] [c000c000] _exception+0x164/0x1b4^M

07/15:24:01|[c0391be0] [c000e978] ret_from_except_full+0x0/0x4c^M

07/15:24:01|[c0391ca0] [c00920b0] cache_alloc_refill+0xc4/0x608^M

07/15:24:01|[c0391d00] [c00927d8] kmem_cache_alloc+0xc4/0xcc^M

07/15:24:01|[c0391d20] [c0042420] __sigqueue_alloc+0x50/0xb8^M

07/15:24:01|[c0391d40] [c0042938] __send_signal+0x78/0x260^M

07/15:24:01|[c0391d70] [c0042f78] group_send_sig_info+0x70/0x9c^M

07/15:24:01|[c0391da0] [c00438a8] kill_pid_info+0x48/0x8c^M

07/15:24:01|[c0391dc0] [c0038e8c] it_real_fn+0x1c/0x30^M

07/15:24:01|[c0391dd0] [c0050c40] hrtimer_run_queues+0x184/0x240^M

07/15:24:01|[c0391e30] [c0040ba8] run_local_timers+0x10/0x2c^M

07/15:24:01|[c0391e40] [c0040bf4] update_process_times+0x30/0x70^M

07/15:24:01|[c0391e60] [c005a000] tick_periodic+0x34/0xe8^M

07/15:24:01|[c0391e70] [c005a0d4] tick_handle_periodic+0x20/0x120^M

07/15:24:01|[c0391eb0] [c000af70] timer_interrupt+0xa4/0x10c^M

07/15:24:01|[c0391ed0] [c000e9c4] ret_from_except+0x0/0x18^M

07/15:24:01|[c0391f90] [c0006fac] cpu_idle+0xcc/0xdc^M

07/15:24:01|[c0391fb0] [c000172c] rest_init+0x70/0x84^M

07/15:24:01|[c0391fc0] [c0341854] start_kernel+0x230/0x2ac^M

07/15:24:02|[c0391ff0] [c0000204] skpinv+0x194/0x1d0^M

07/15:24:02|Rebooting in 180 seconds..

07/15:27:02|^MISOL Version 1.00 Date 9th January 2017

|

|

|

641

|

Fri Jun 7 16:08:37 2024 |

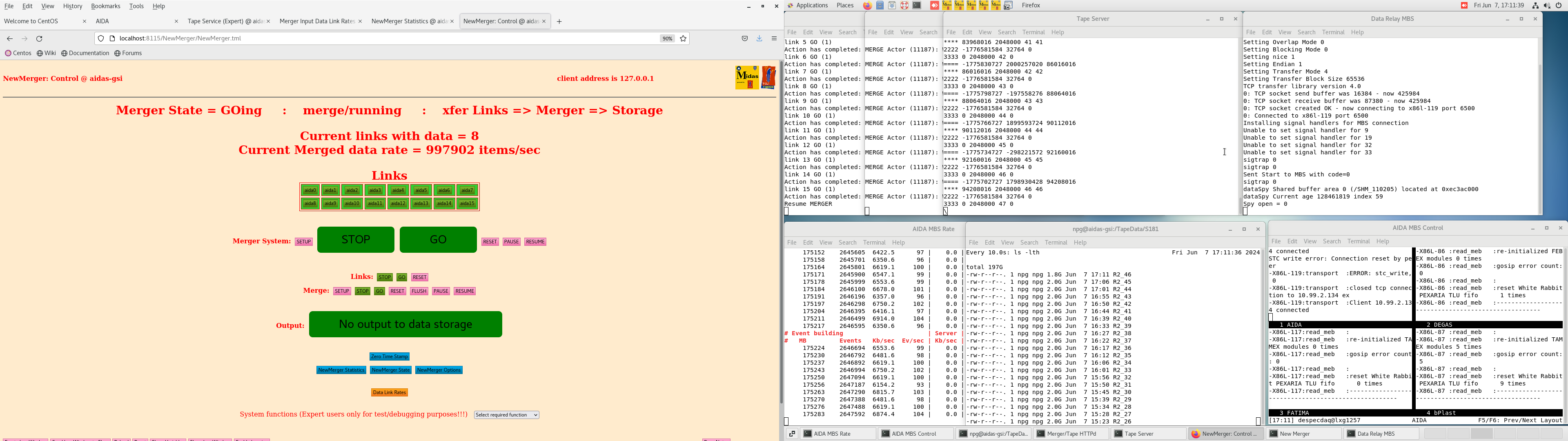

TD | Friday 7 June |

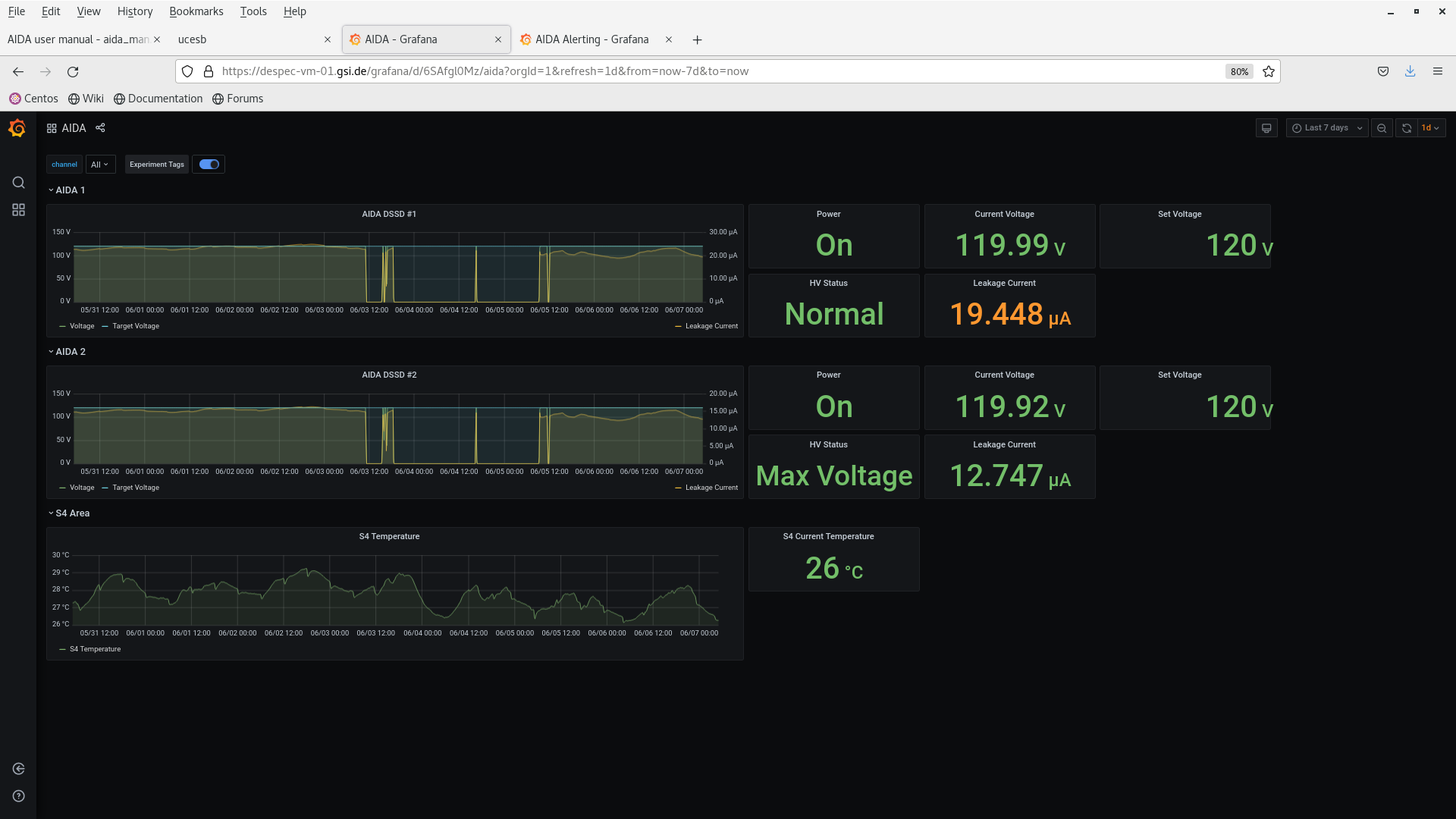

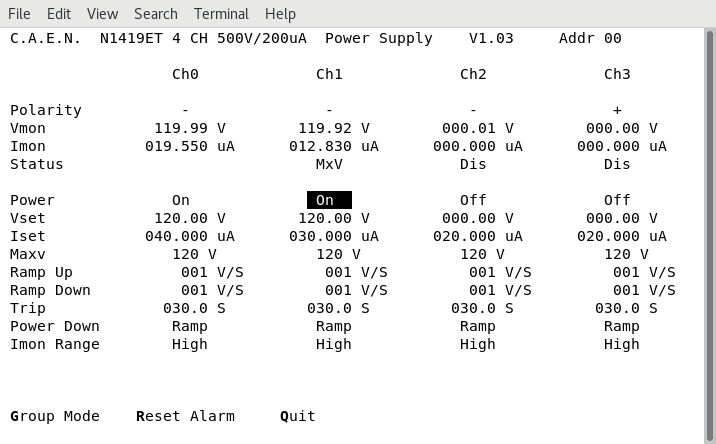

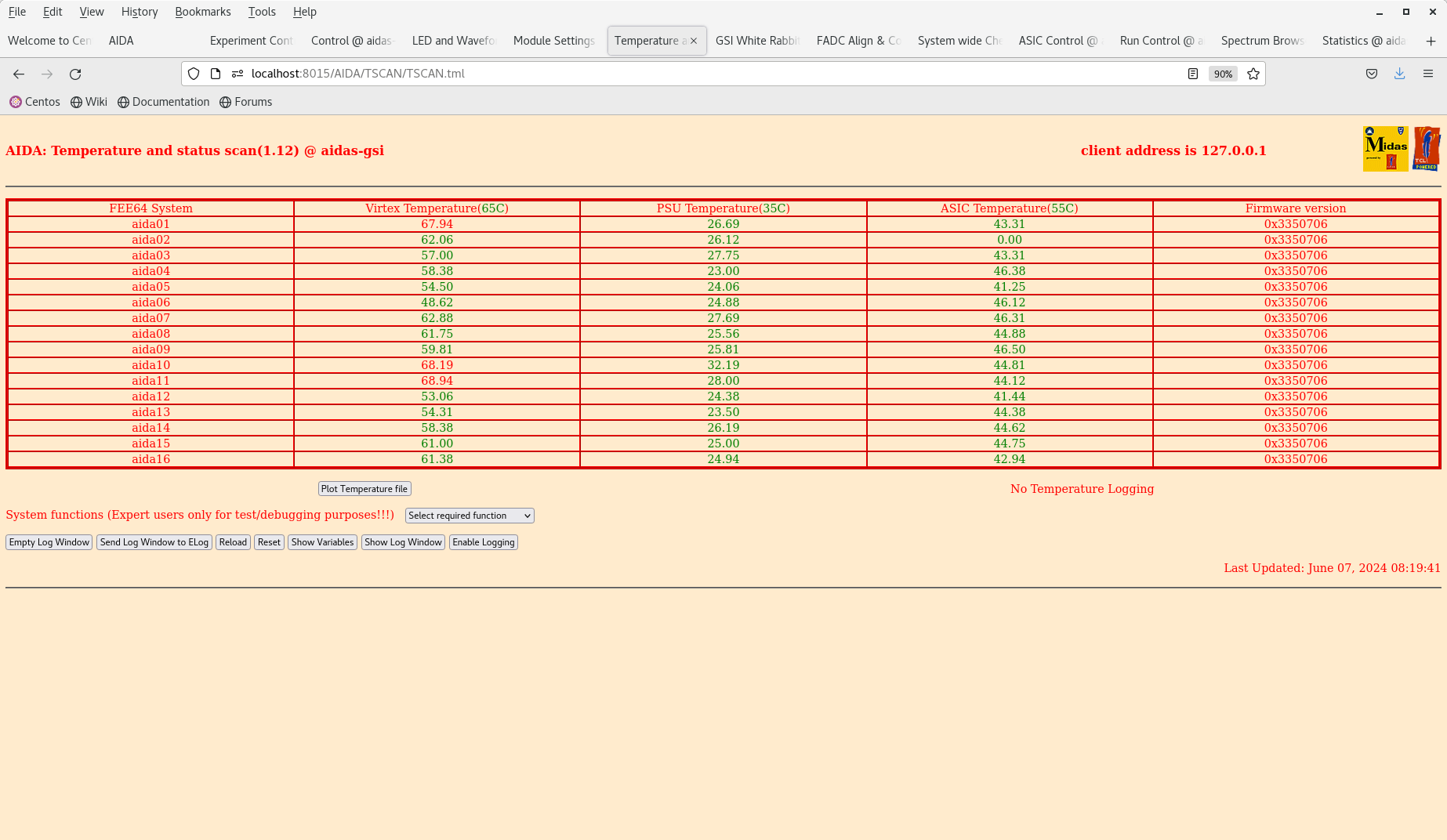

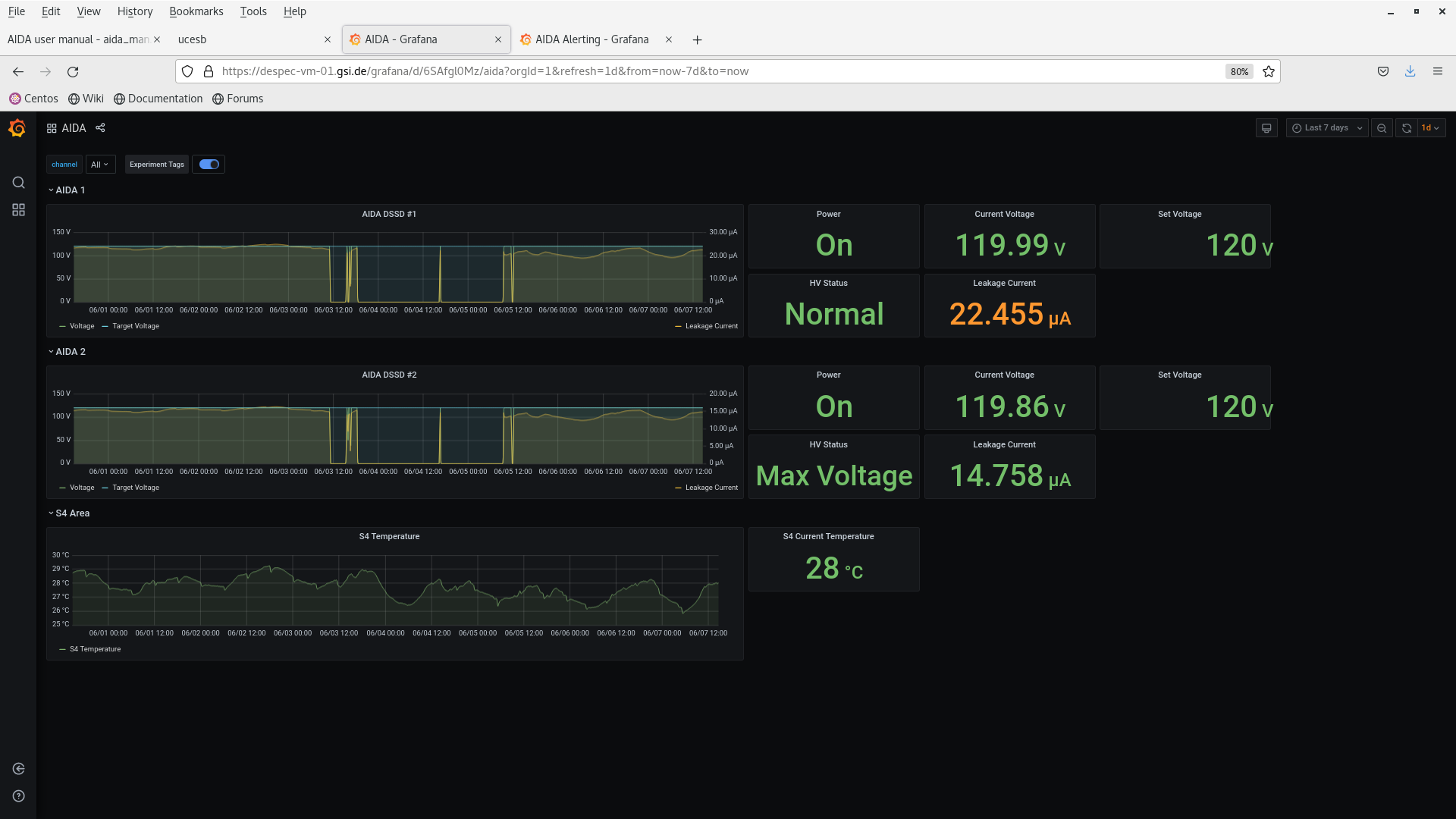

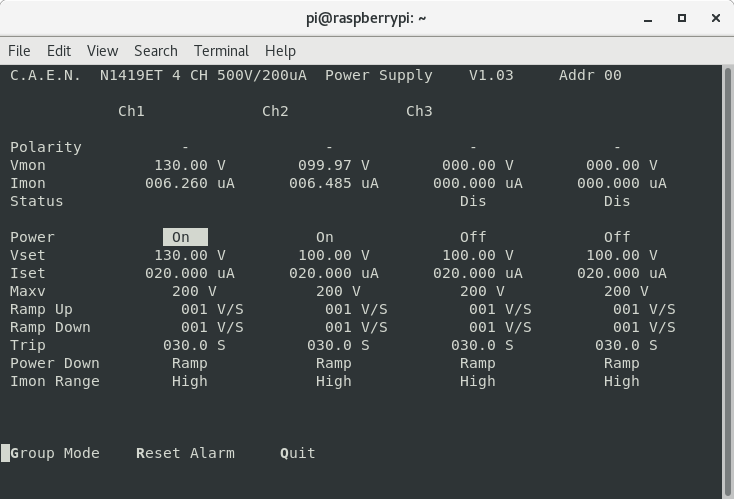

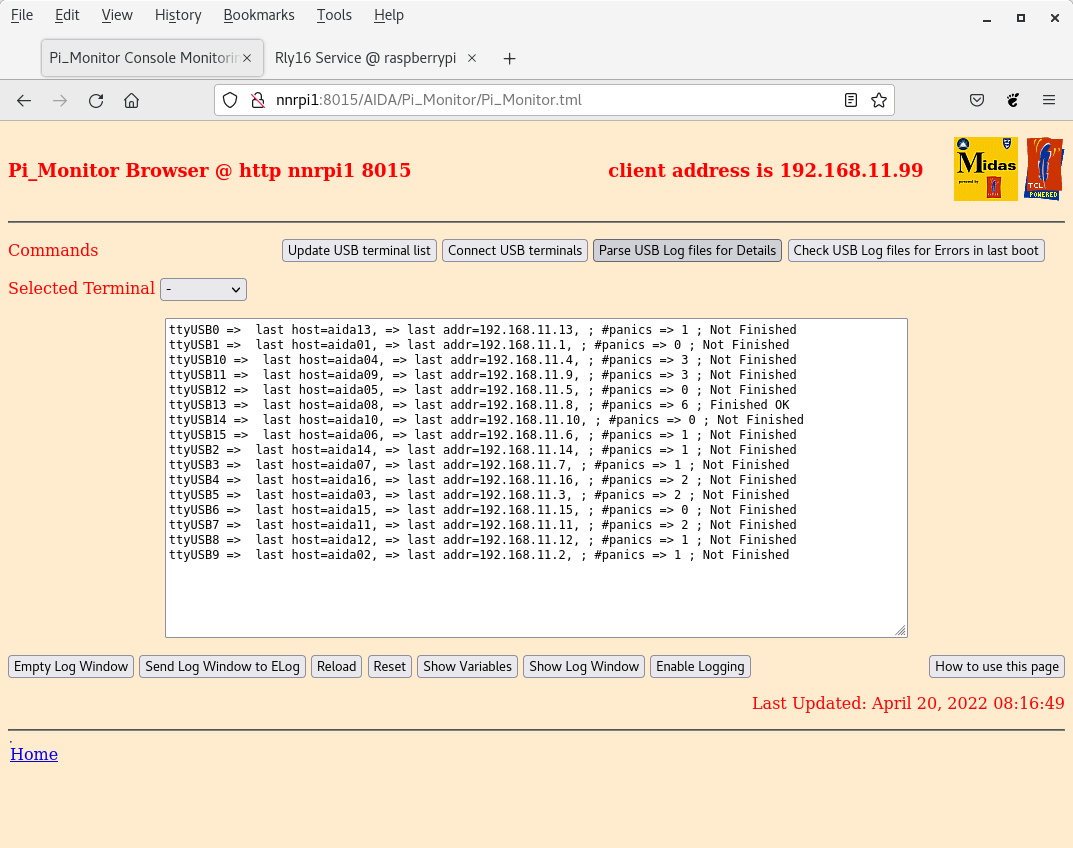

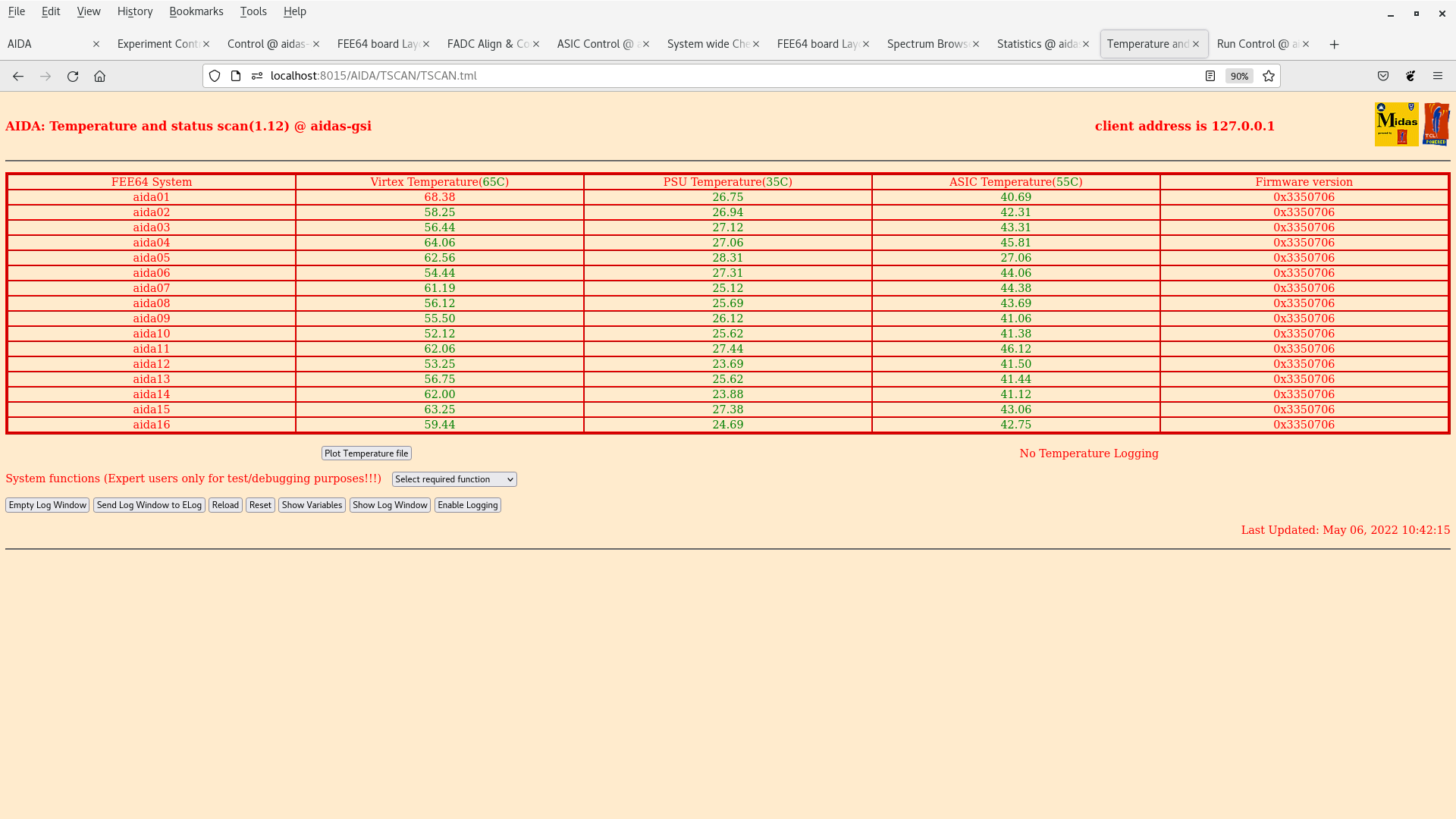

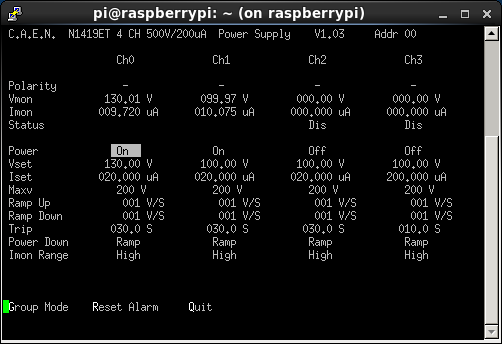

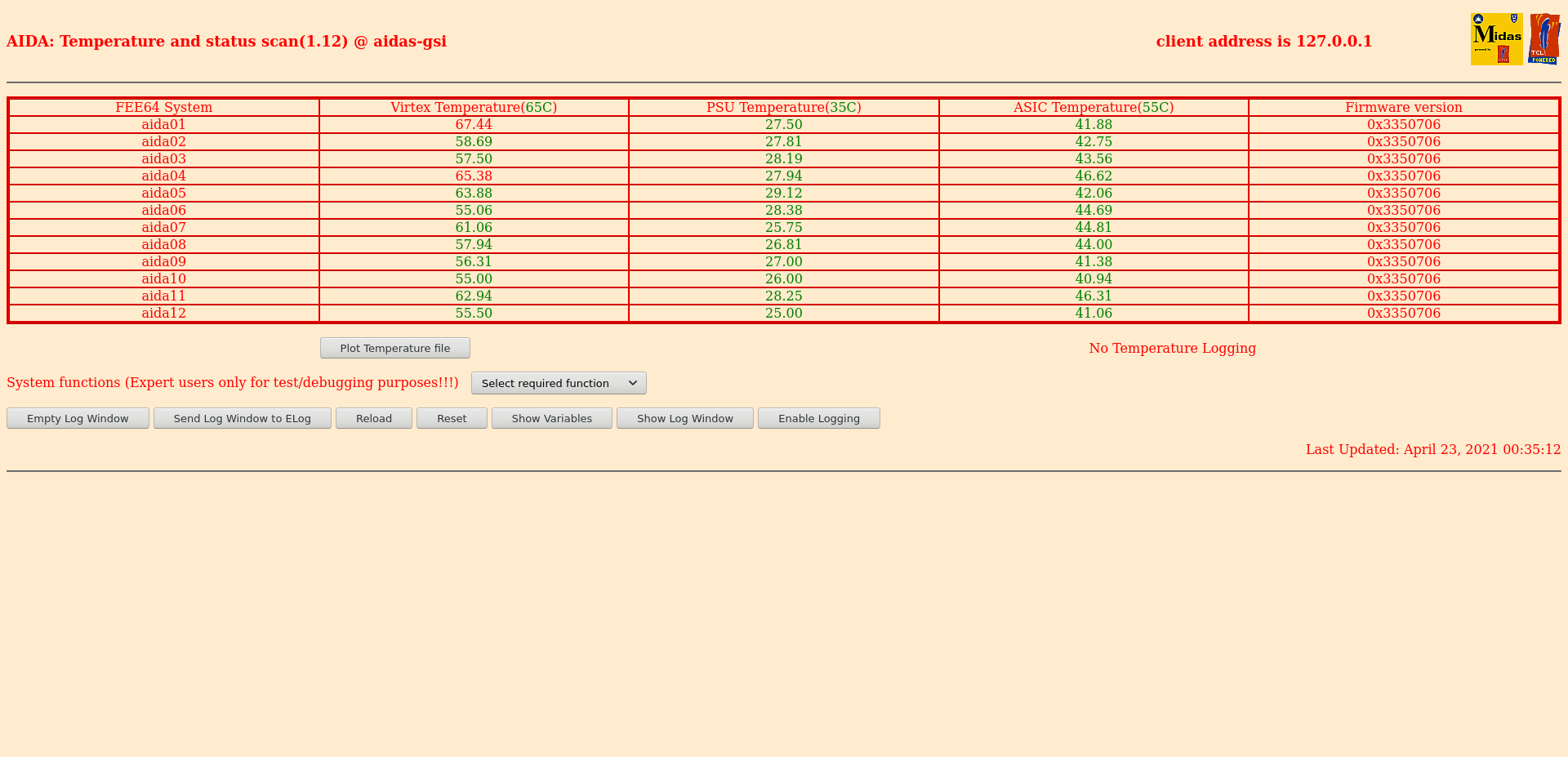

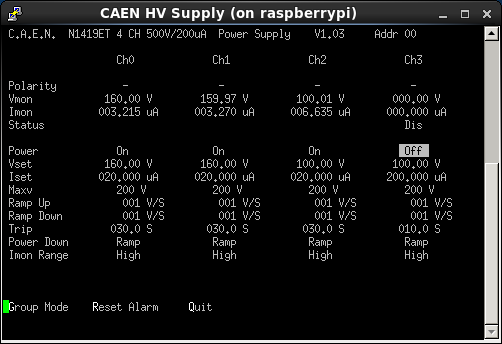

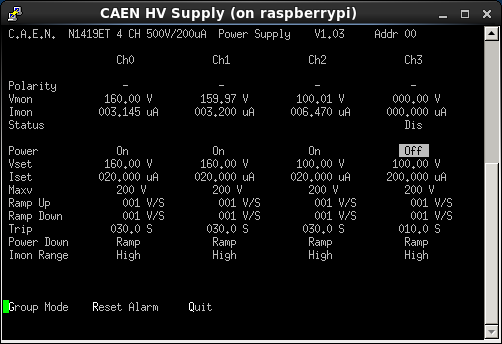

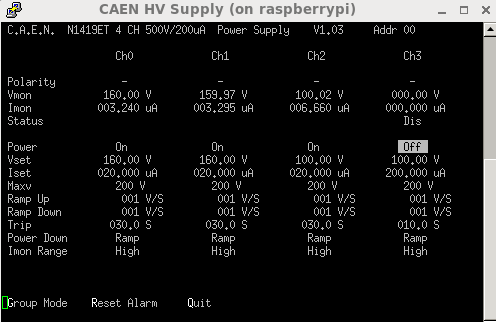

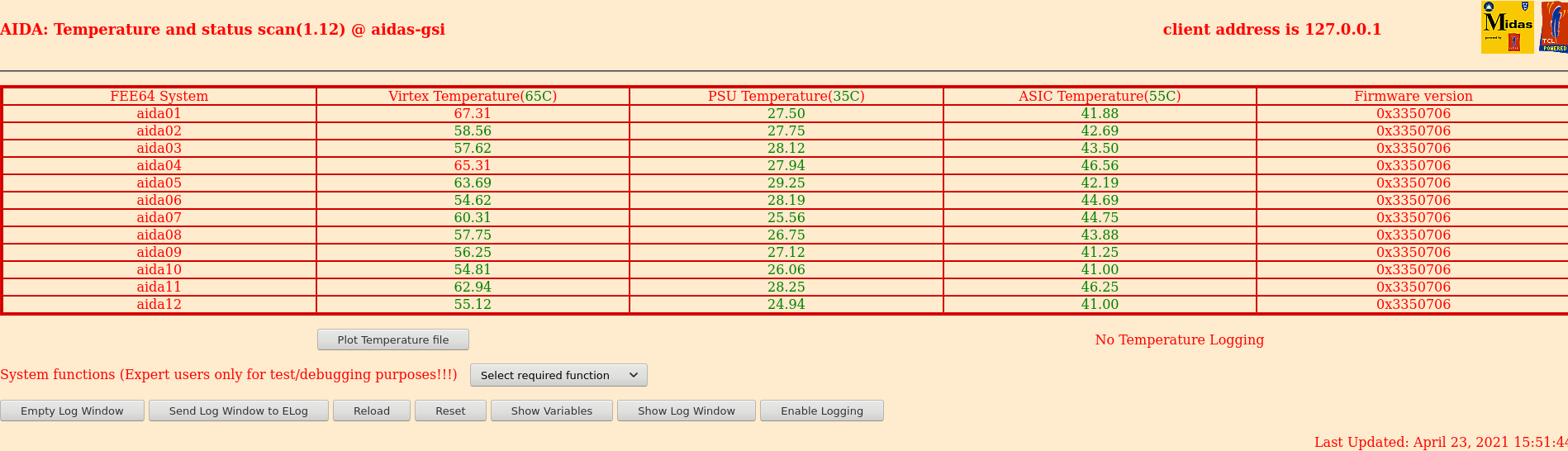

05.01 DSSSD bias & leakage current - attachment 1

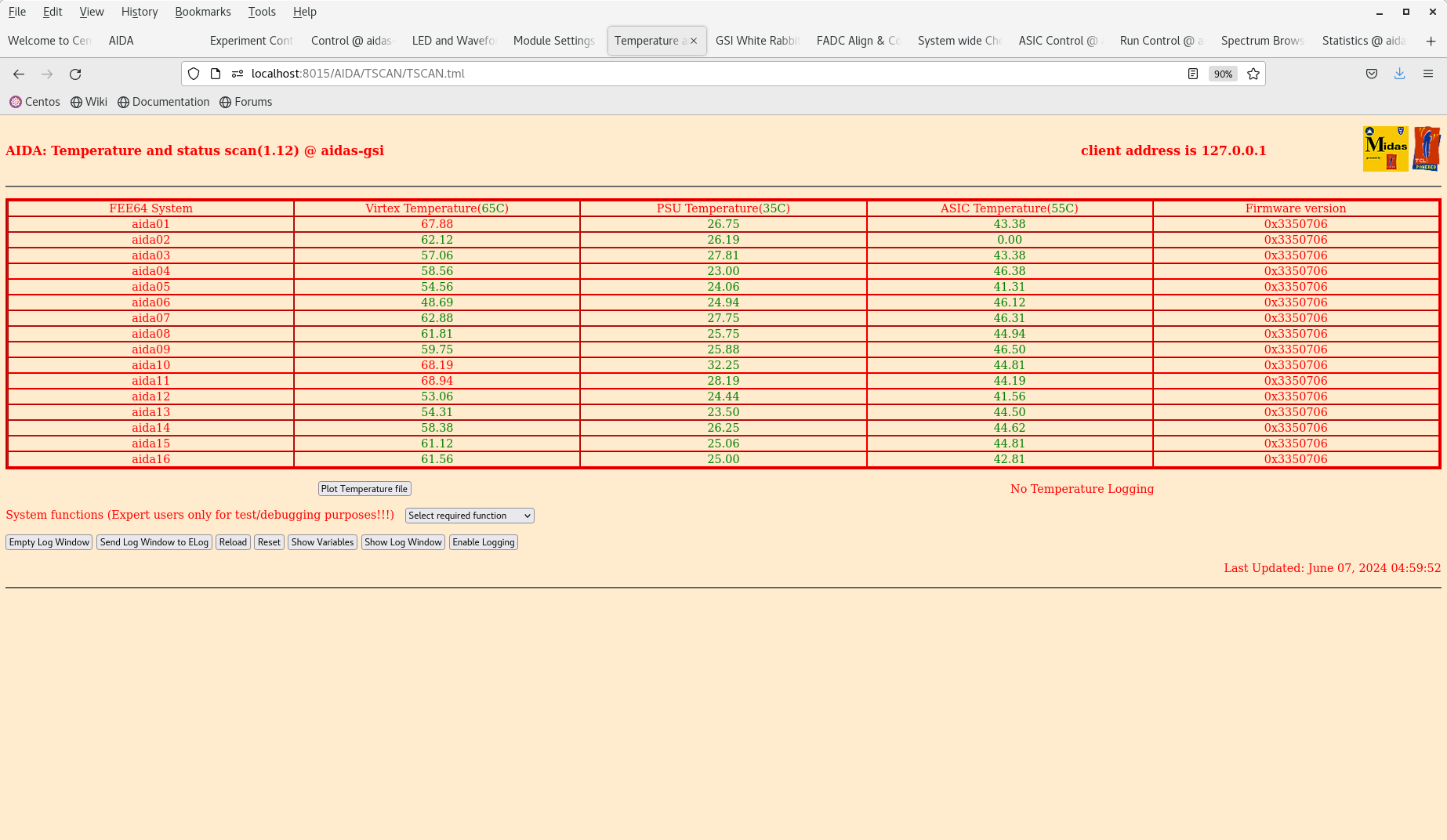

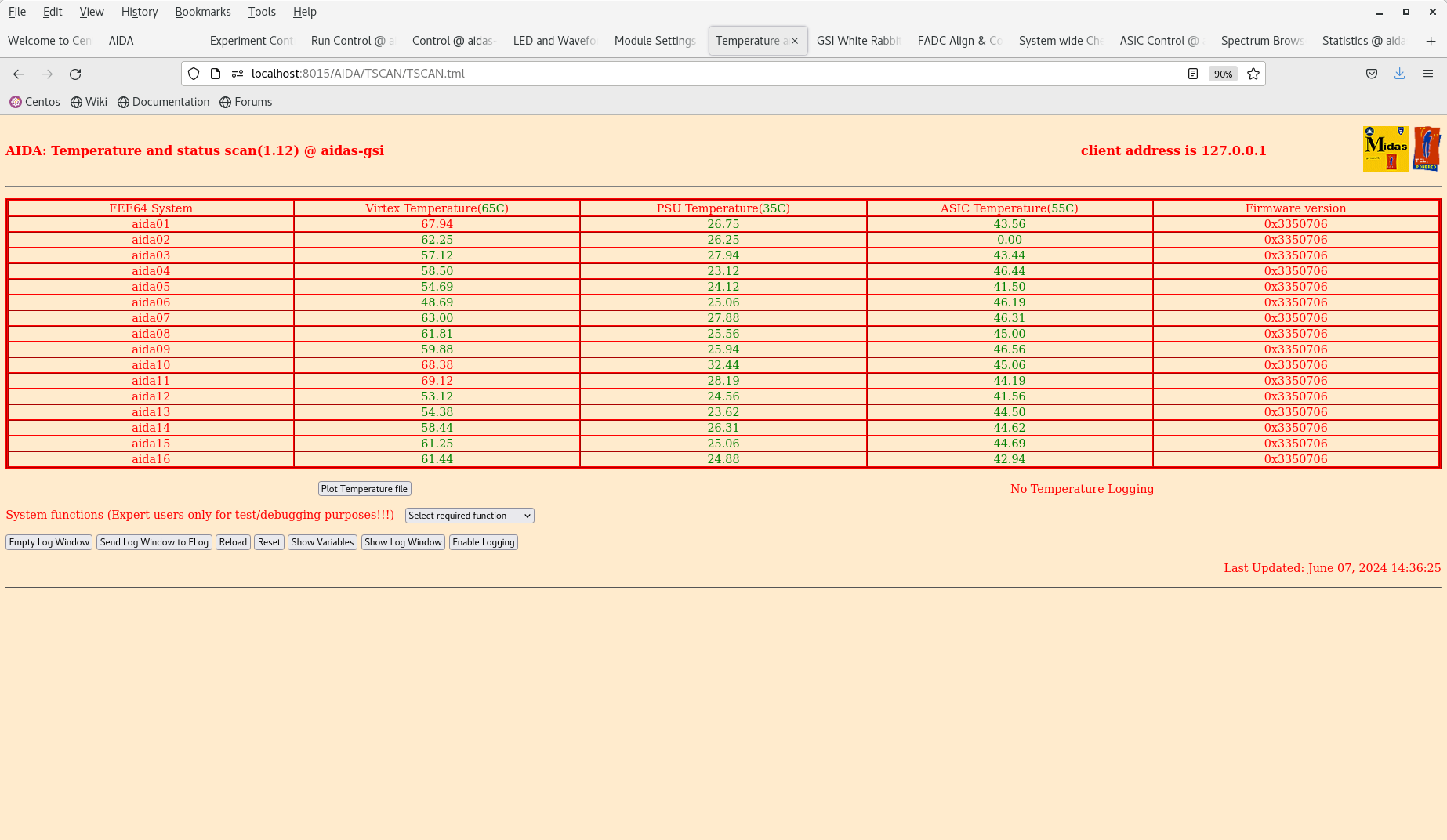

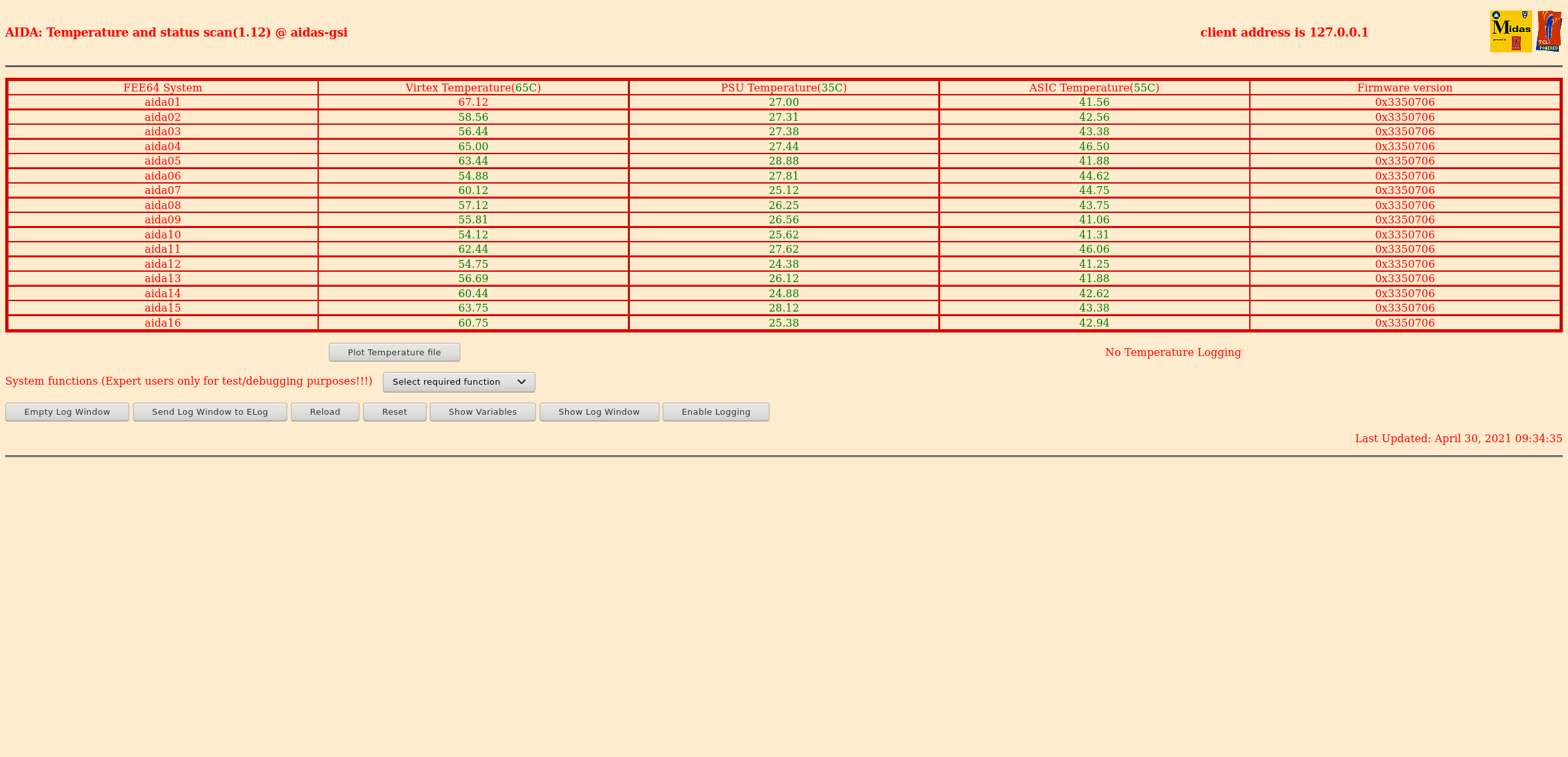

FEE64 temperatures OK - attachment 2

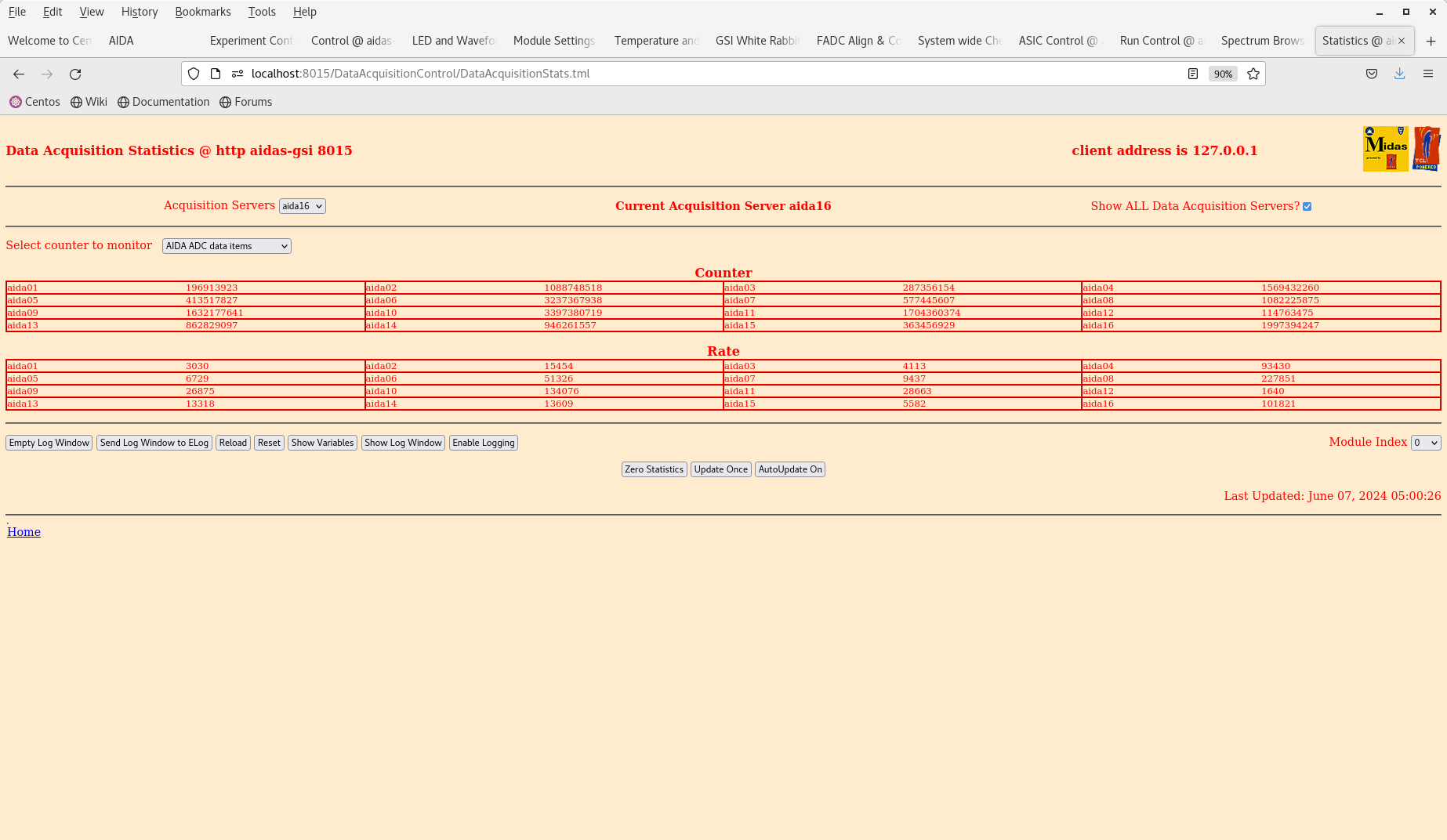

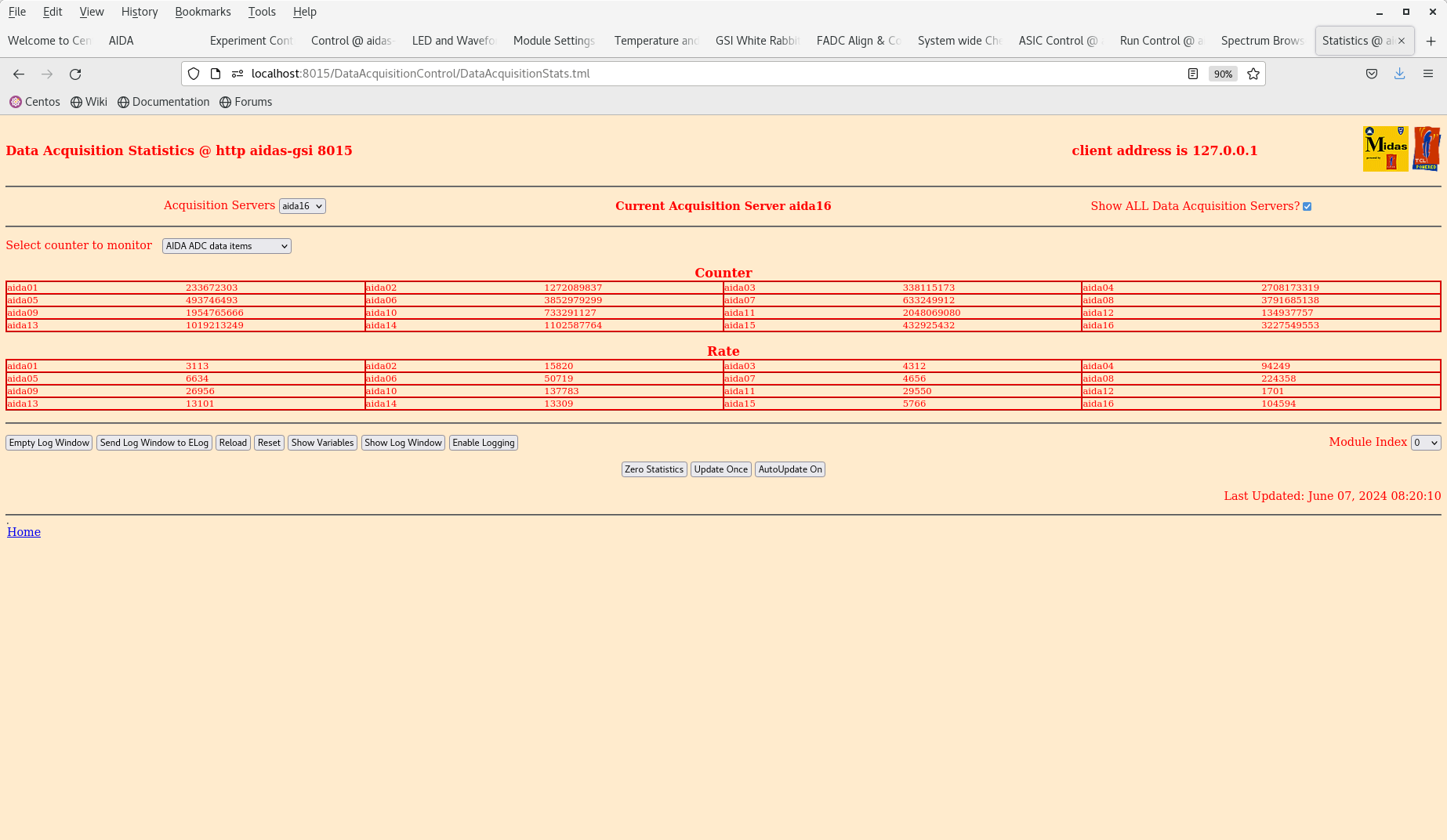

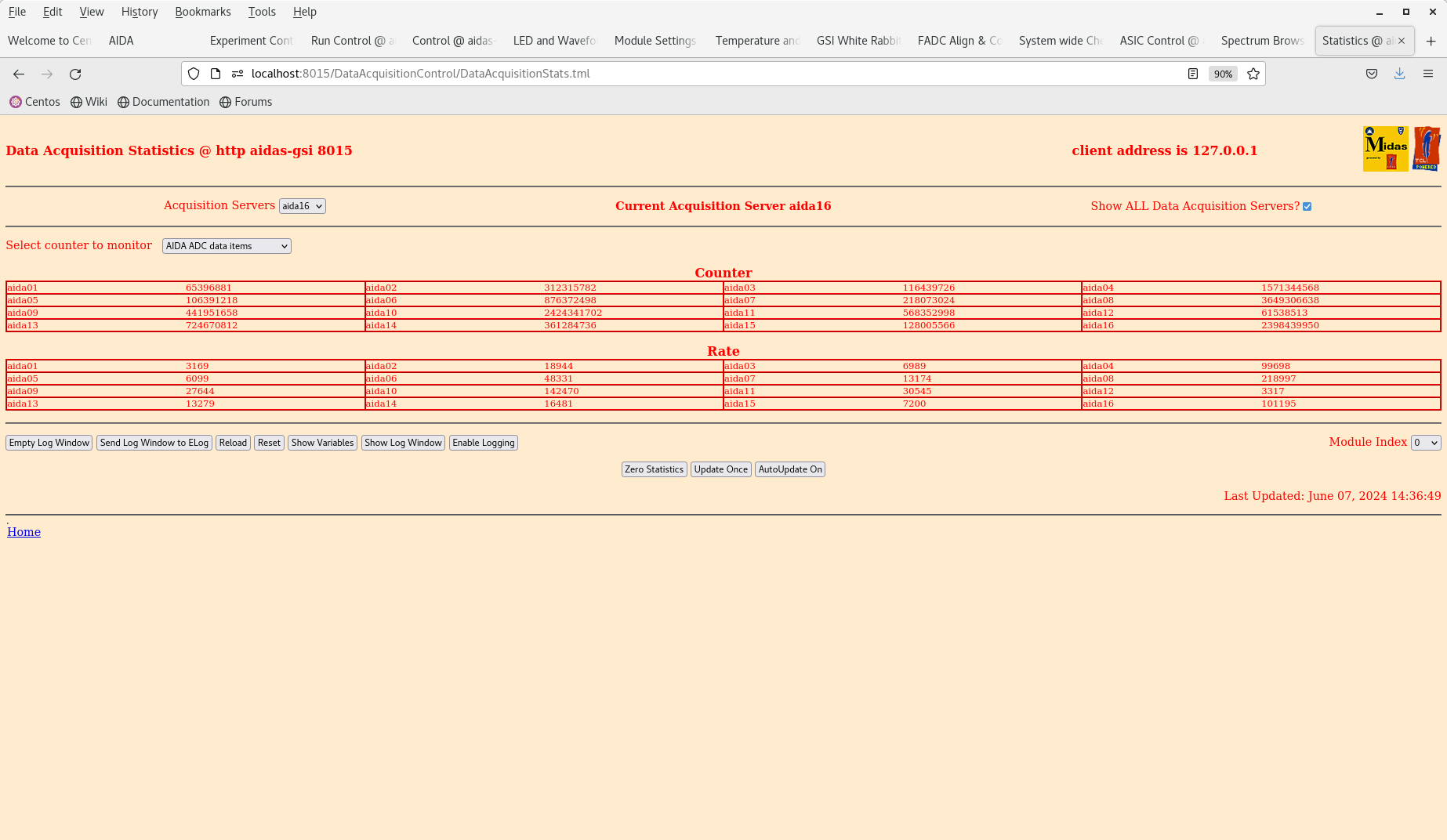

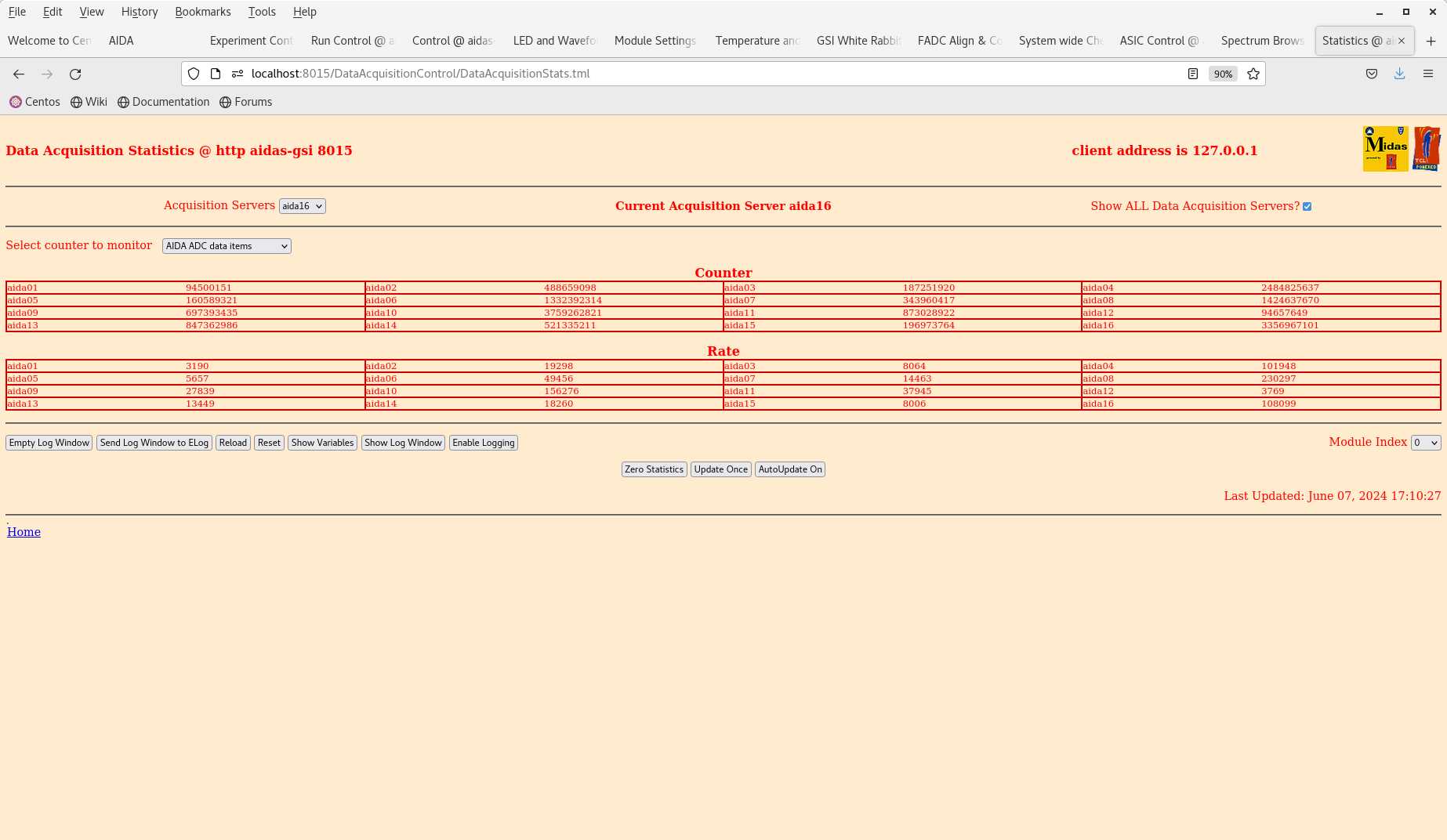

ADC data item stats - attachment 3

9x < 20k, max 228k aida08

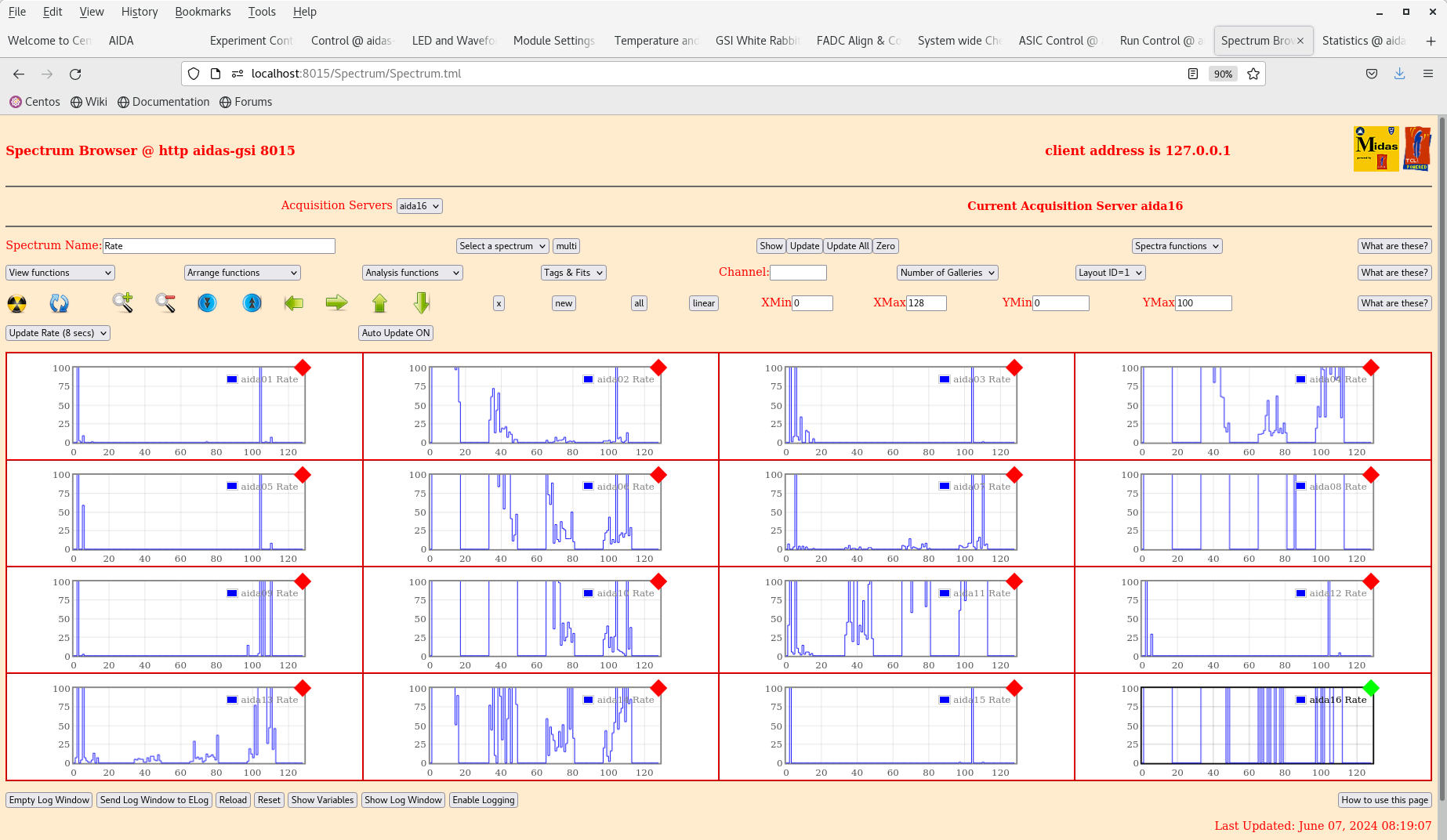

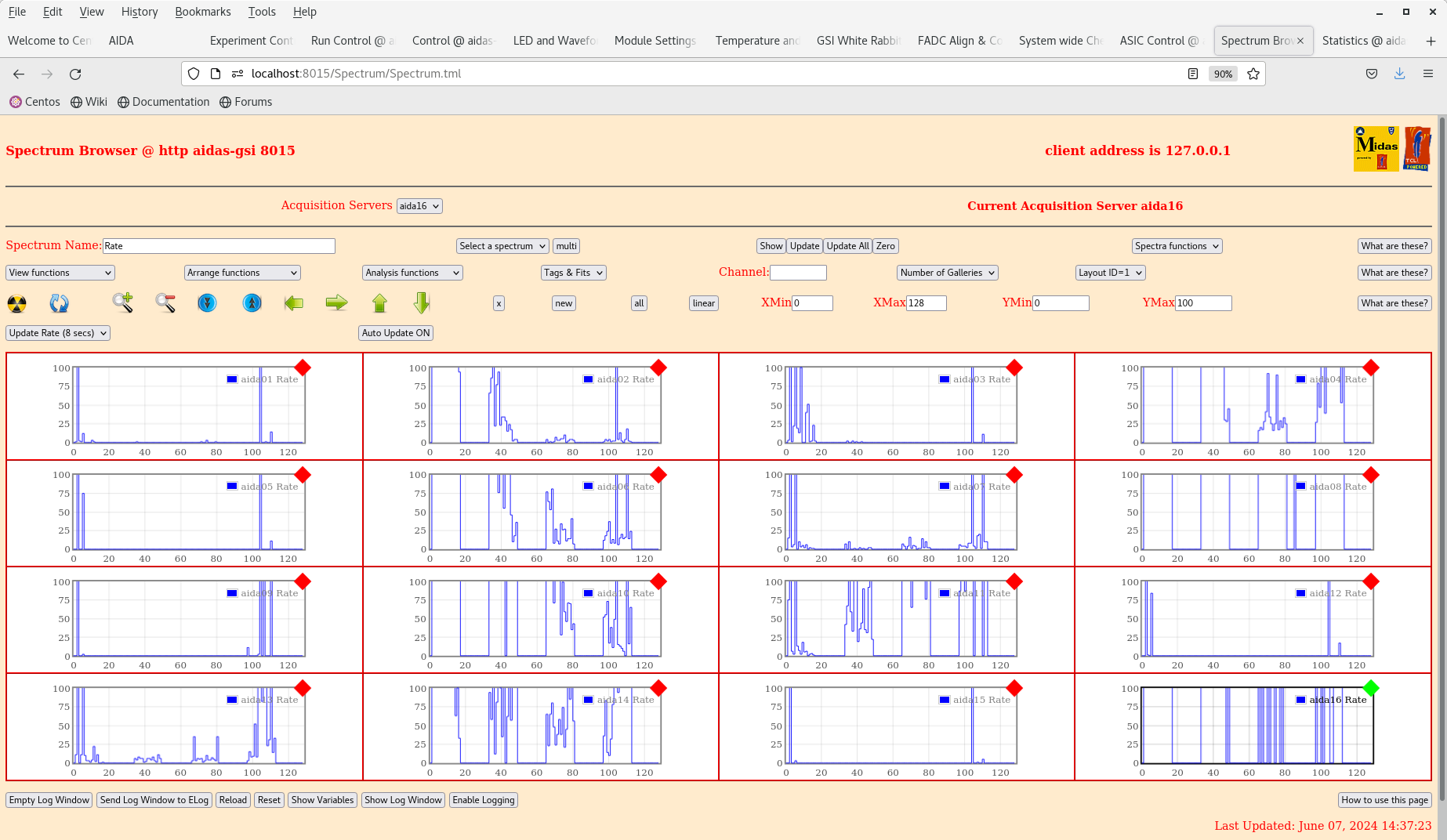

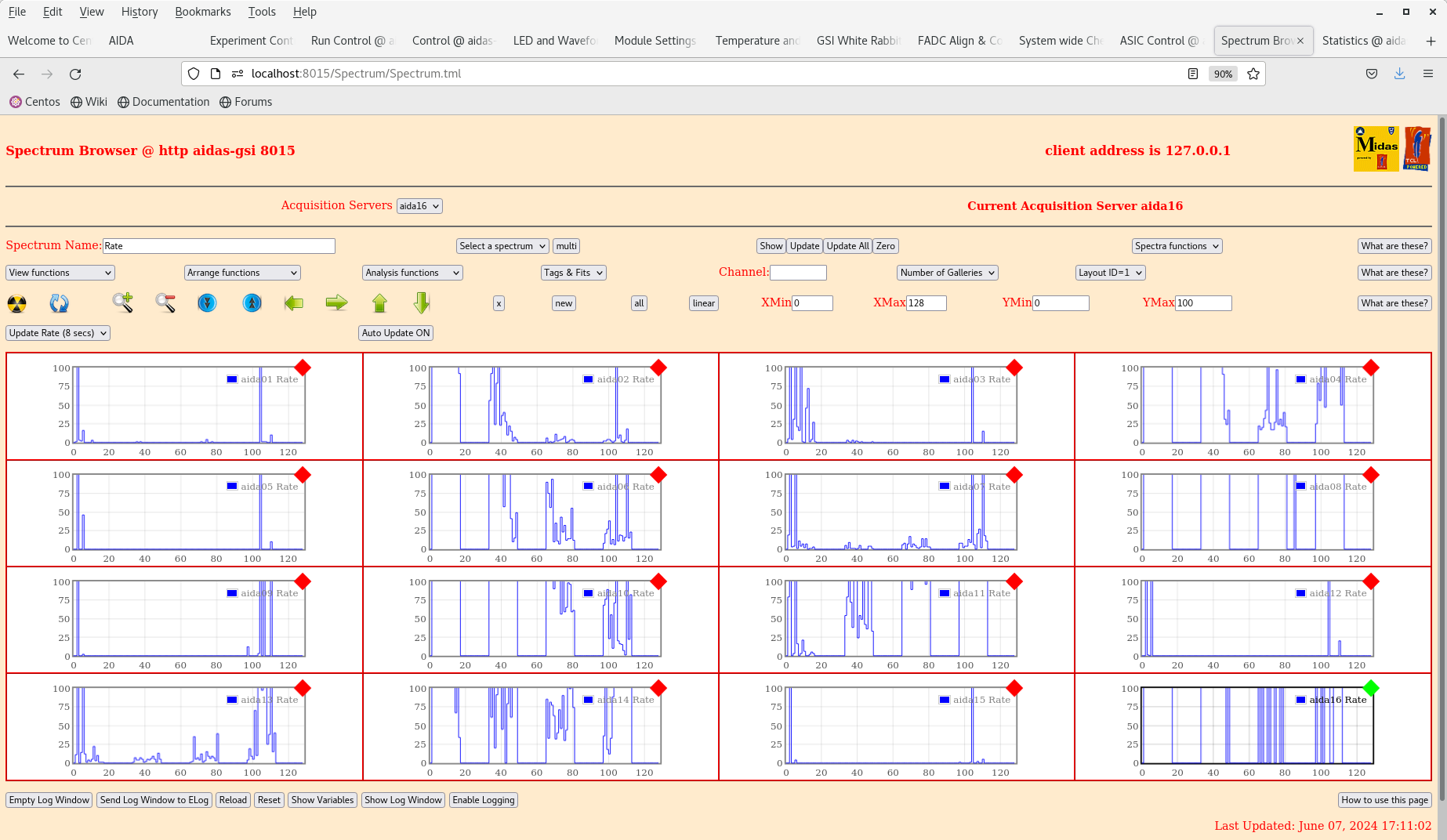

per FEE64 Rate spectra - attachment 4

08.18 DSSSD bias & leakage current - attachment 5

FEE64 temperatures OK - attachment 6

ADC data item stats - attachment 7

9x < 20k, max 224k aida08

per FEE64 Rate spectra - attachment 8

14.37 DSSSD bias & leakage current - attachment 9

FEE64 temperatures OK - attachment 10

ADC data item stats - attachment 11

9x < 20k, max 224k aida08

per FEE64 Rate spectra - attachment 12

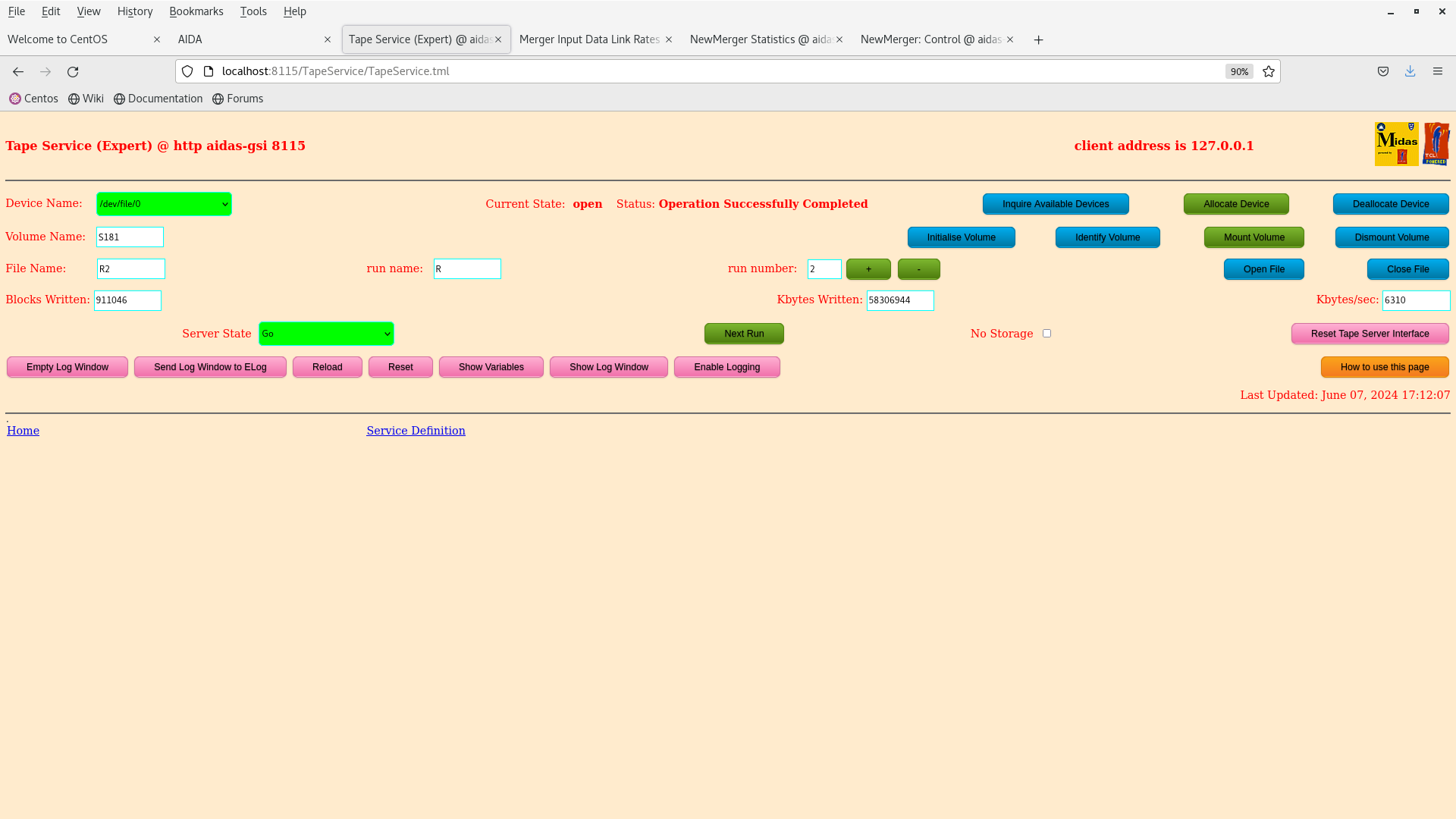

Writing to disk file S181/R1 (continuing alpha background file)

14.38 End run S181/R1 and start new run file S181/R2

17.09 08.18 DSSSD bias & leakage current - attachment 13

FEE64 temperatures OK - attachment 14

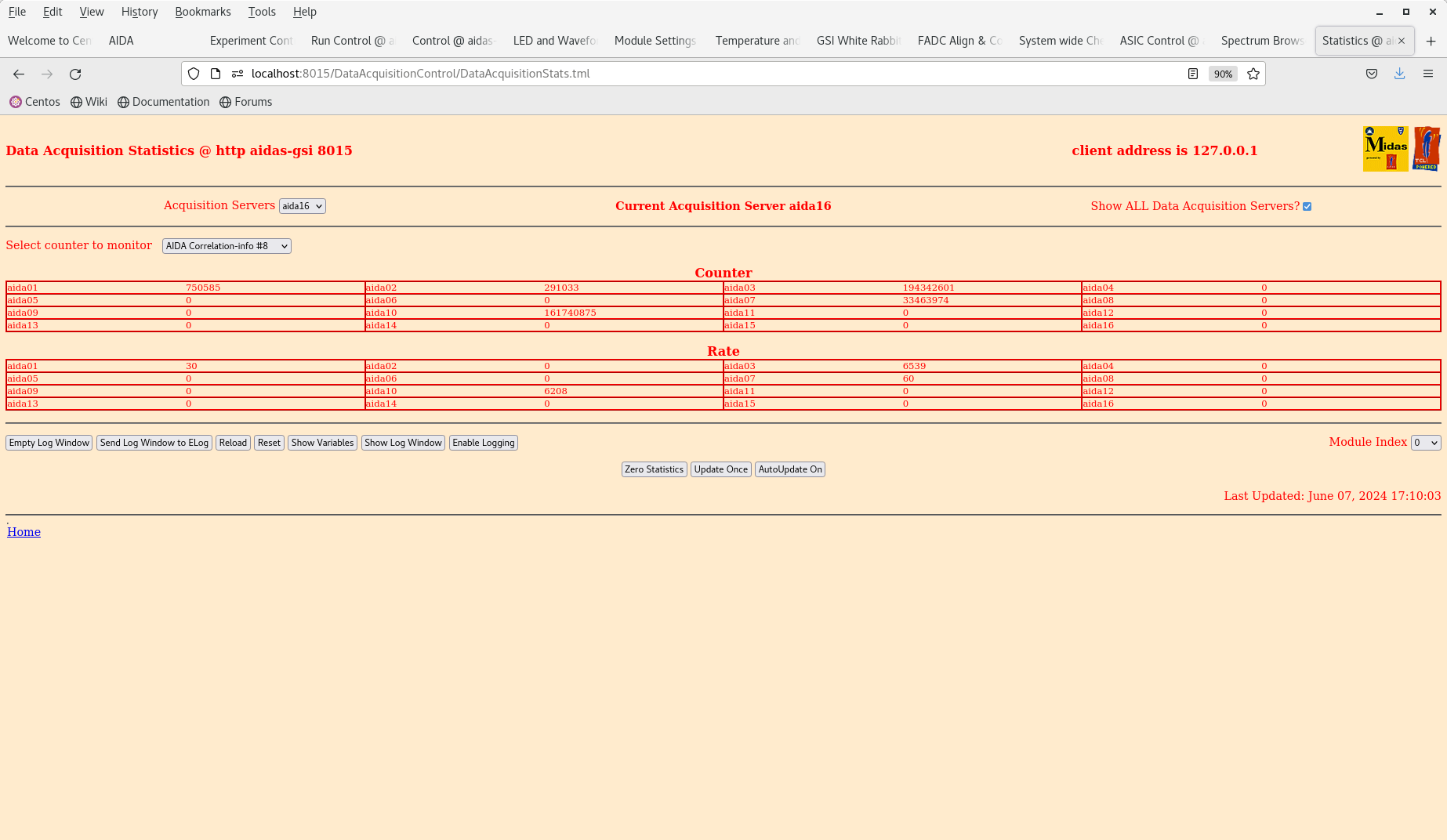

MBS correlation scaler data - attachment 15

data to aida01, aida02, aida03 and aida10

ADC data item stats - attachment 16

9x < 20k, max 230k aida08

per FEE64 Rate spectra - attachment 17

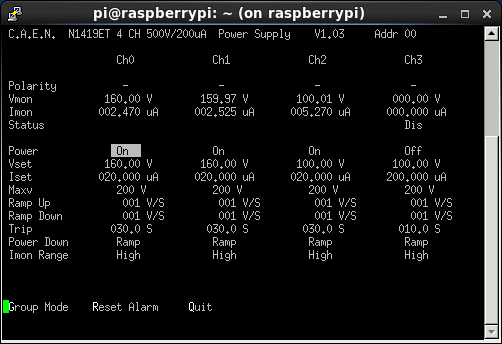

Merger/TapeServer etc - attachments 18-19 |

| Attachment 1: Screenshot_from_2024-06-07_05-01-53.png

|

|

| Attachment 2: Screenshot_from_2024-06-07_05-00-13.png

|

|

| Attachment 3: Screenshot_from_2024-06-07_05-00-49.png

|

|

| Attachment 4: Screenshot_from_2024-06-07_05-01-23.png

|

|

| Attachment 5: Screenshot_from_2024-06-07_08-18-34.png

|

|

| Attachment 6: Screenshot_from_2024-06-07_08-19-54.png

|

|

| Attachment 7: Screenshot_from_2024-06-07_08-20-21.png

|

|

| Attachment 8: Screenshot_from_2024-06-07_08-19-22.png

|

|

| Attachment 9: Screenshot_from_2024-06-07_14-38-06.png

|

|

| Attachment 10: Screenshot_from_2024-06-07_14-36-36.png

|

|

| Attachment 11: Screenshot_from_2024-06-07_14-37-12.png

|

|

| Attachment 12: Screenshot_from_2024-06-07_14-37-42.png

|

|

| Attachment 13: Screenshot_from_2024-06-07_17-09-16.png

|

|

| Attachment 14: Screenshot_from_2024-06-07_17-09-46.png

|

|

| Attachment 15: Screenshot_from_2024-06-07_17-10-10.png

|

|

| Attachment 16: Screenshot_from_2024-06-07_17-10-52.png

|

|

| Attachment 17: Screenshot_from_2024-06-07_17-11-15.png

|

|

| Attachment 18: Screenshot_from_2024-06-07_17-11-40.png

|

|

| Attachment 19: Screenshot_from_2024-06-07_17-12-21.png

|

|

|

|

421

|

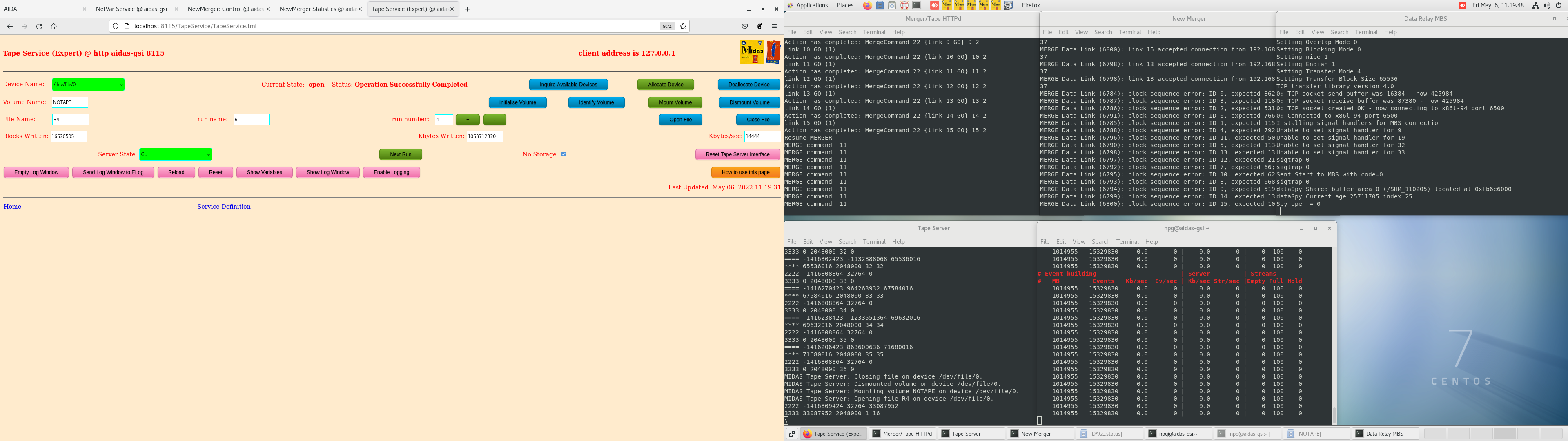

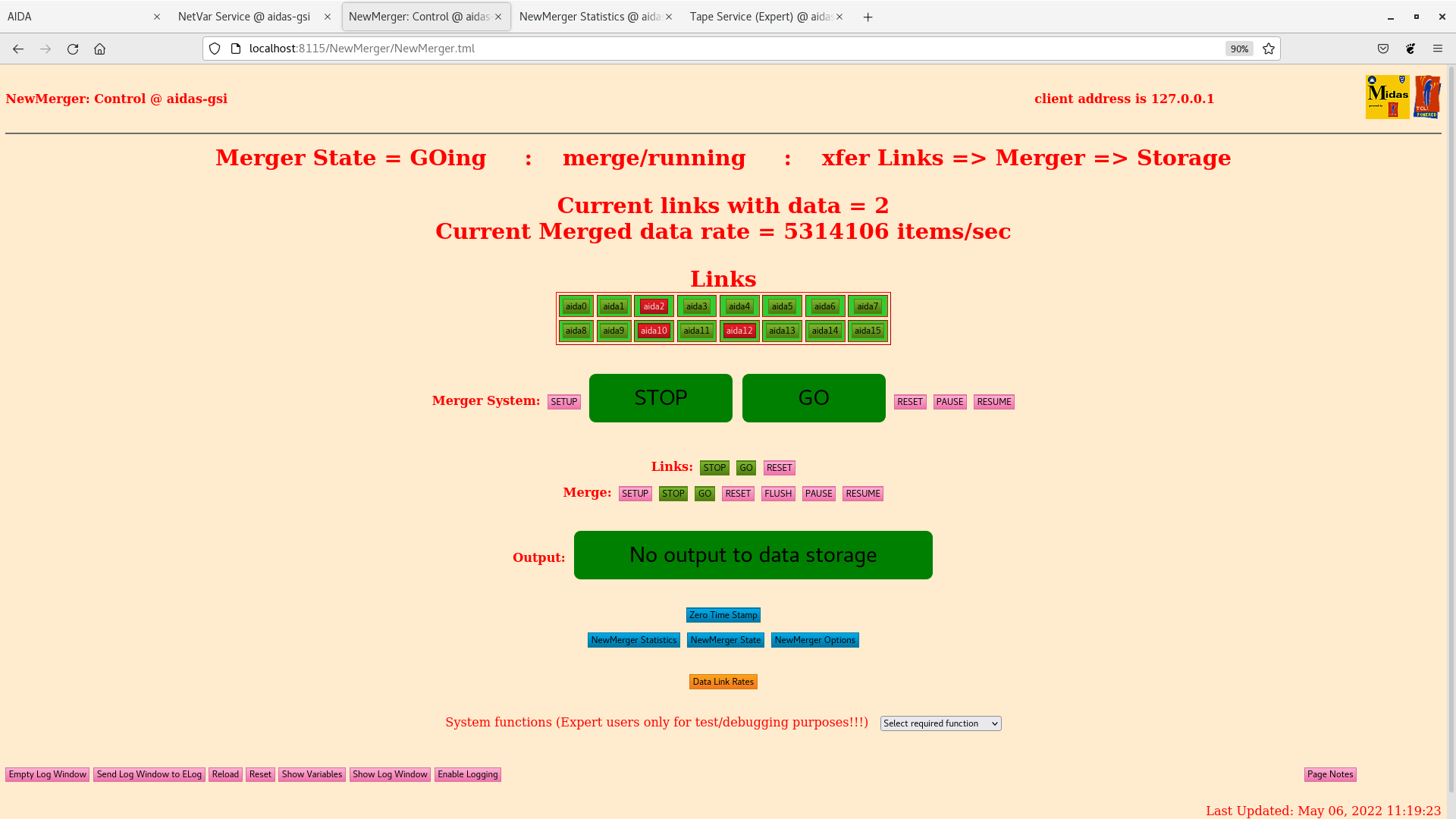

Fri May 6 09:31:41 2022 |

TD NH | Friday 6 May |

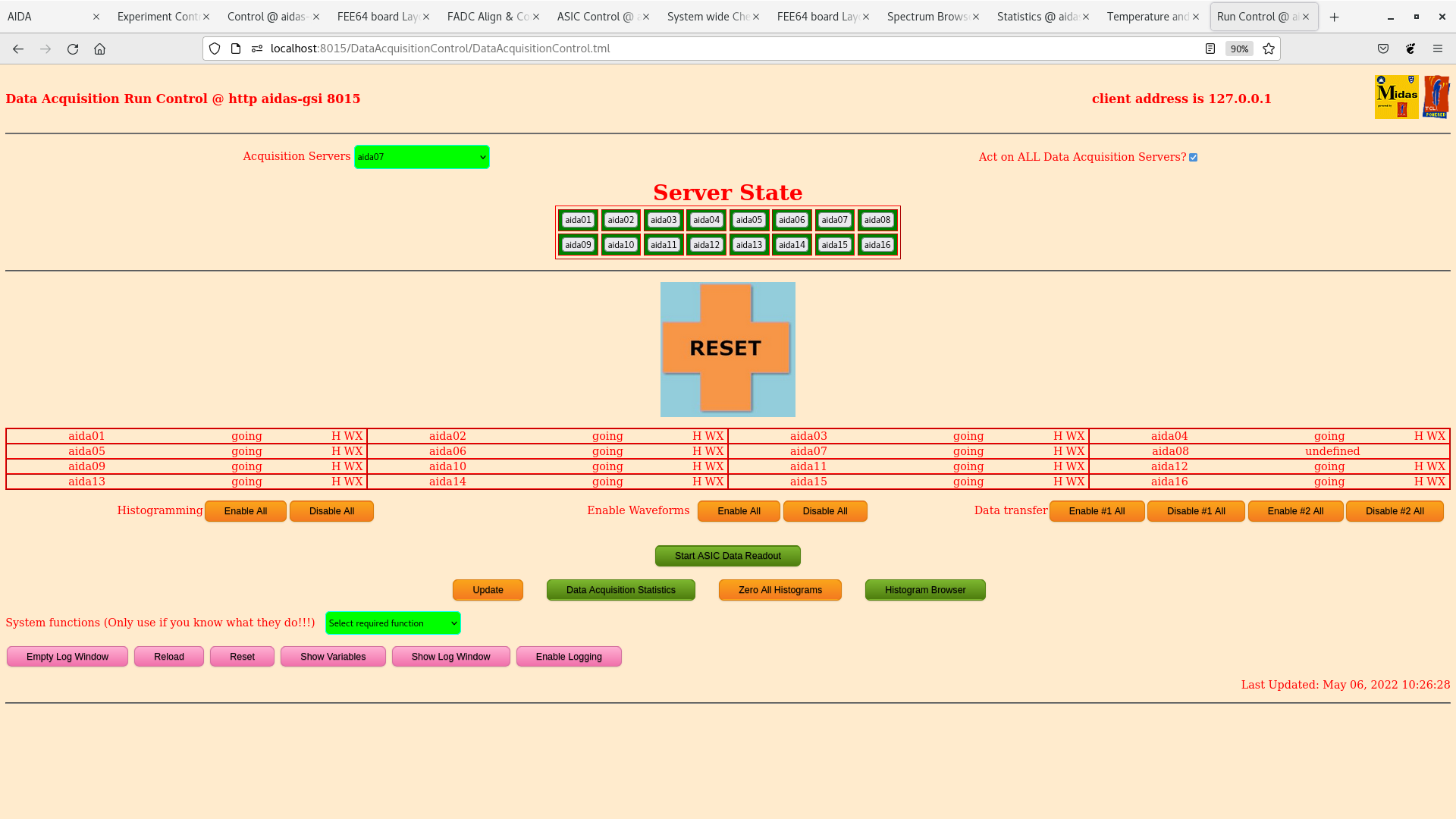

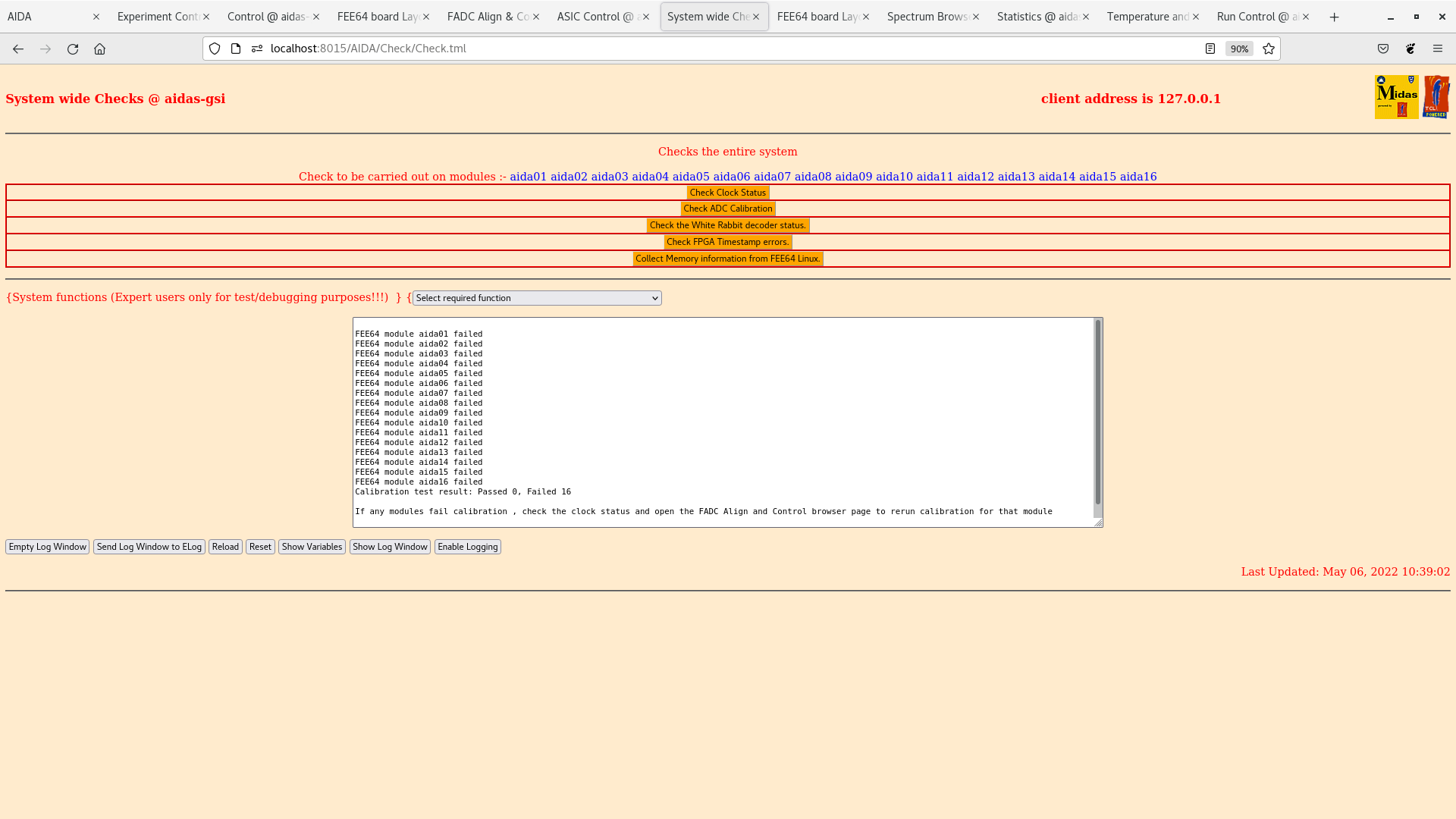

10:30 DAQ appears to have stopped

Attachment 2 - DSSSD bias and leakage current OK

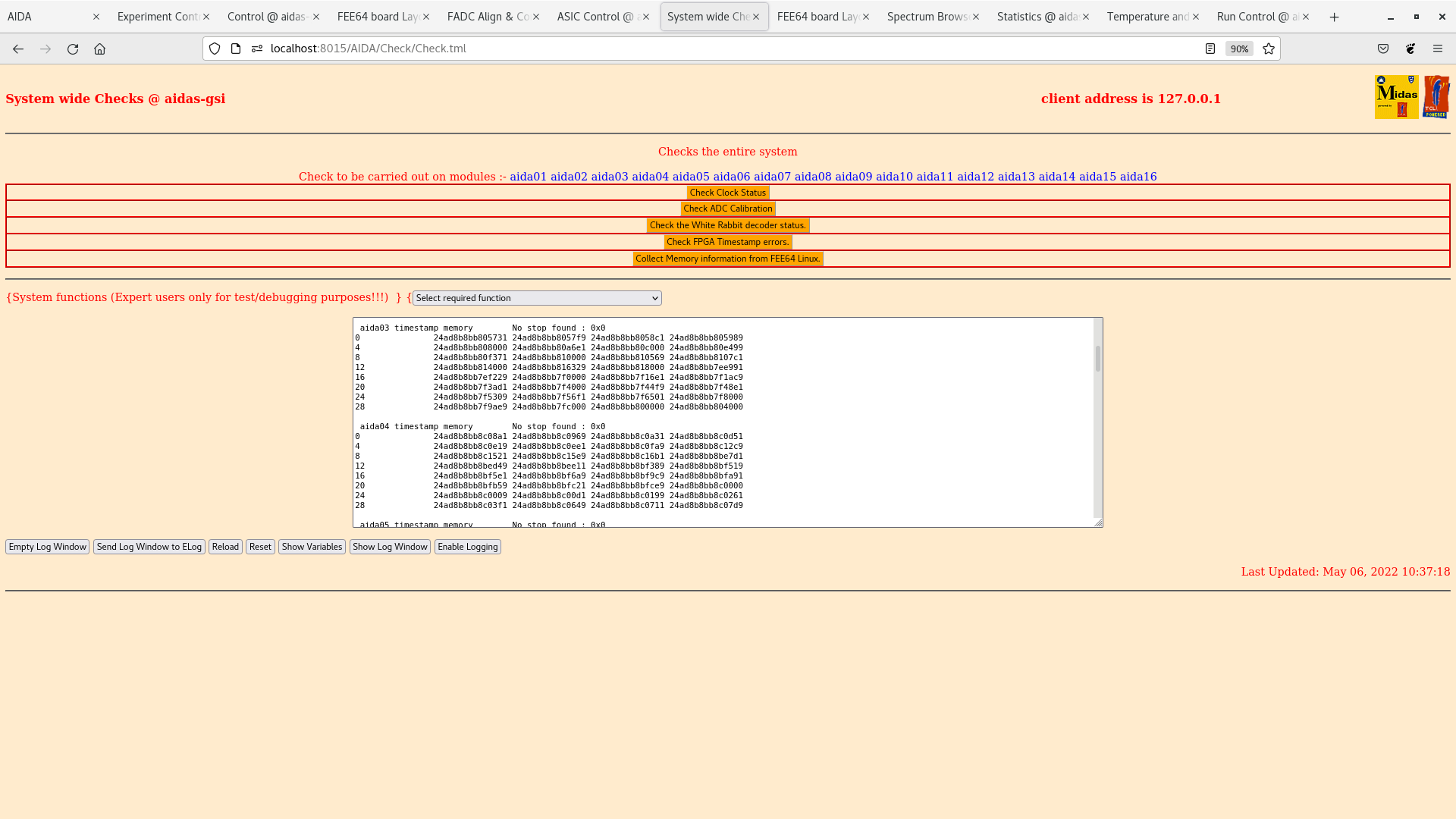

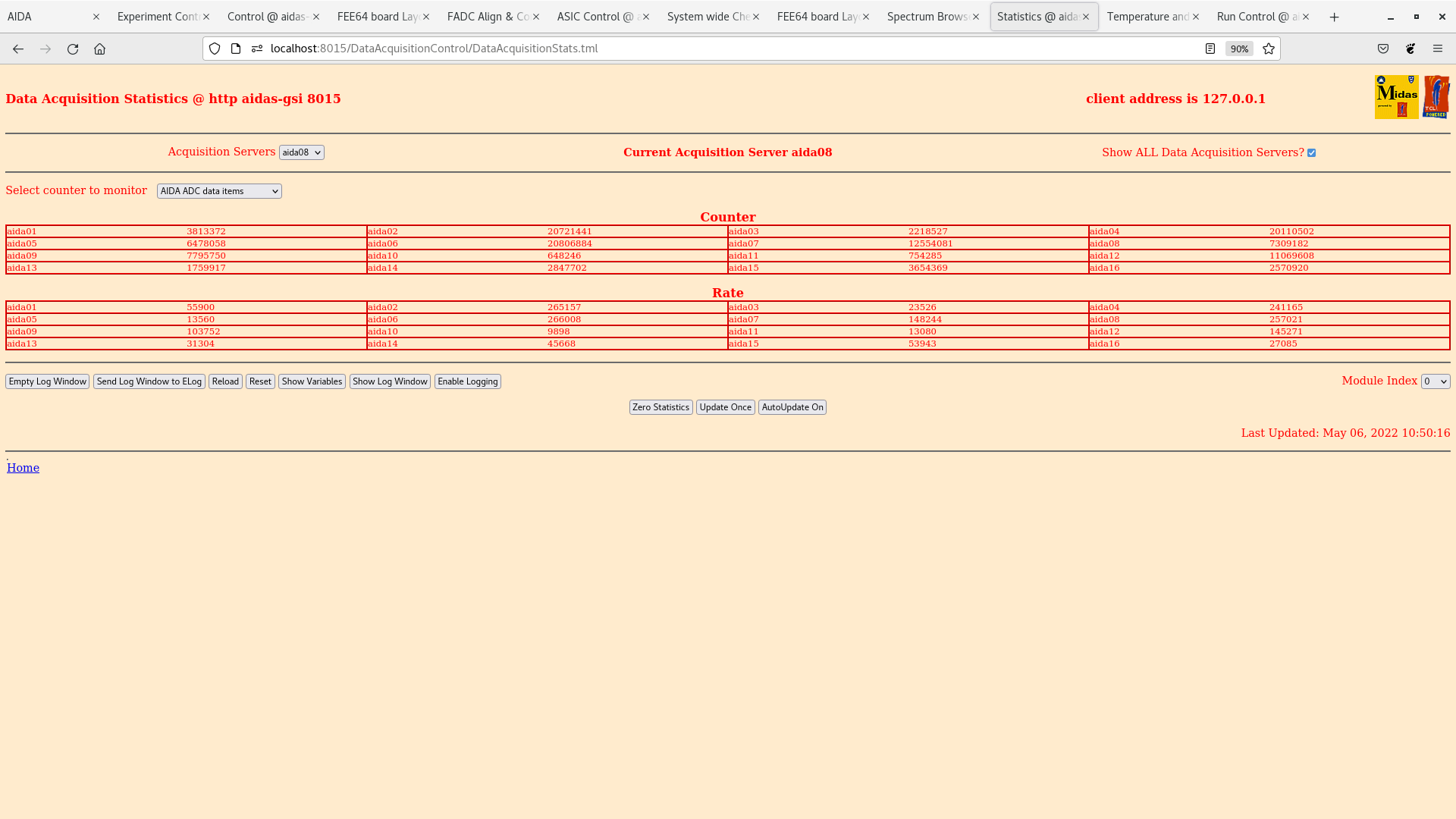

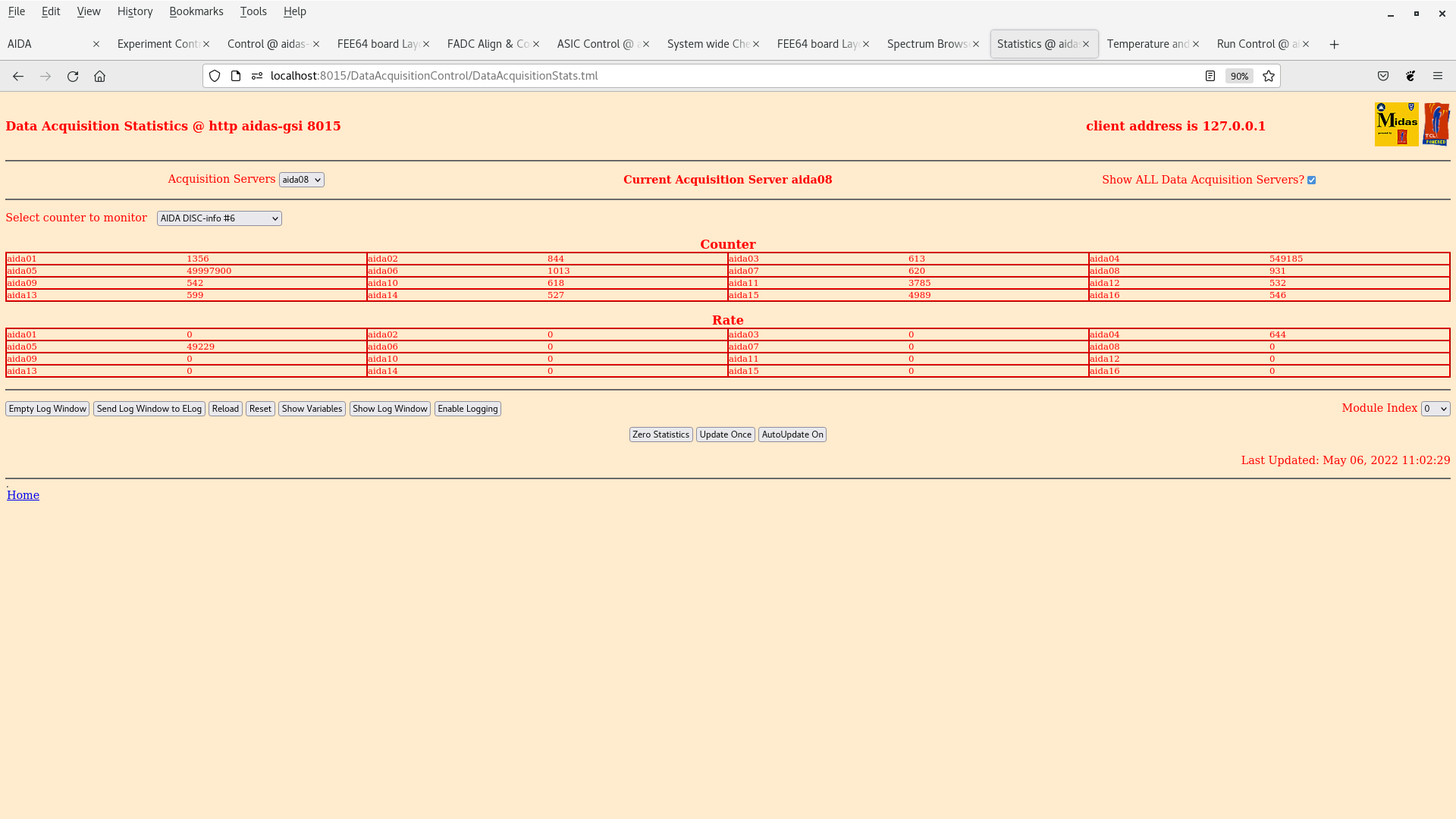

Attachments 1, 3-5 - zero rate adc data items all FEE64s - note aida08 adc data item counter zero

RESET/SETUP/GO aida08 *only*

DAQ STOP *all* FEE64s

Attachment 6 - FEE64 temperatures OK

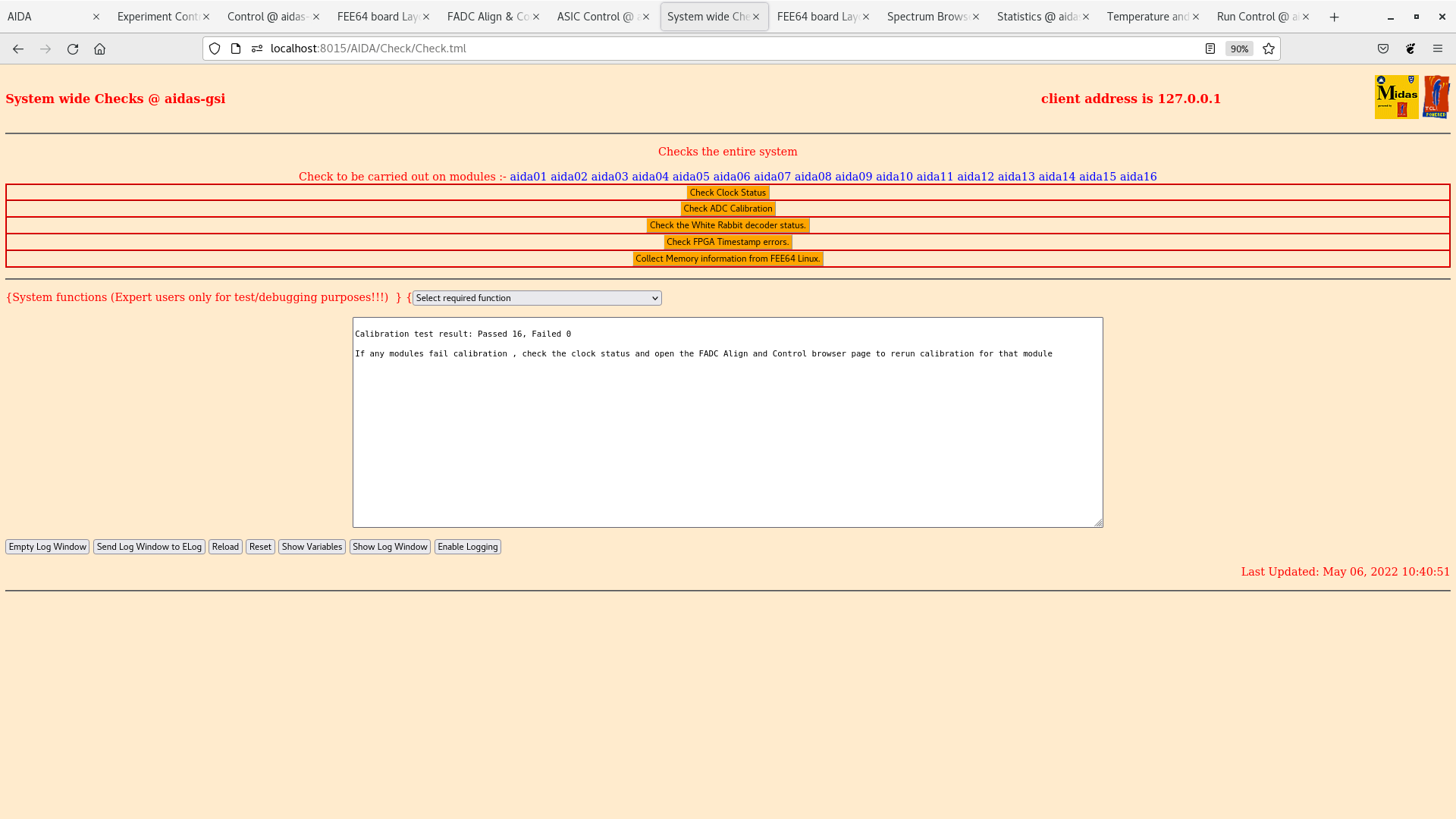

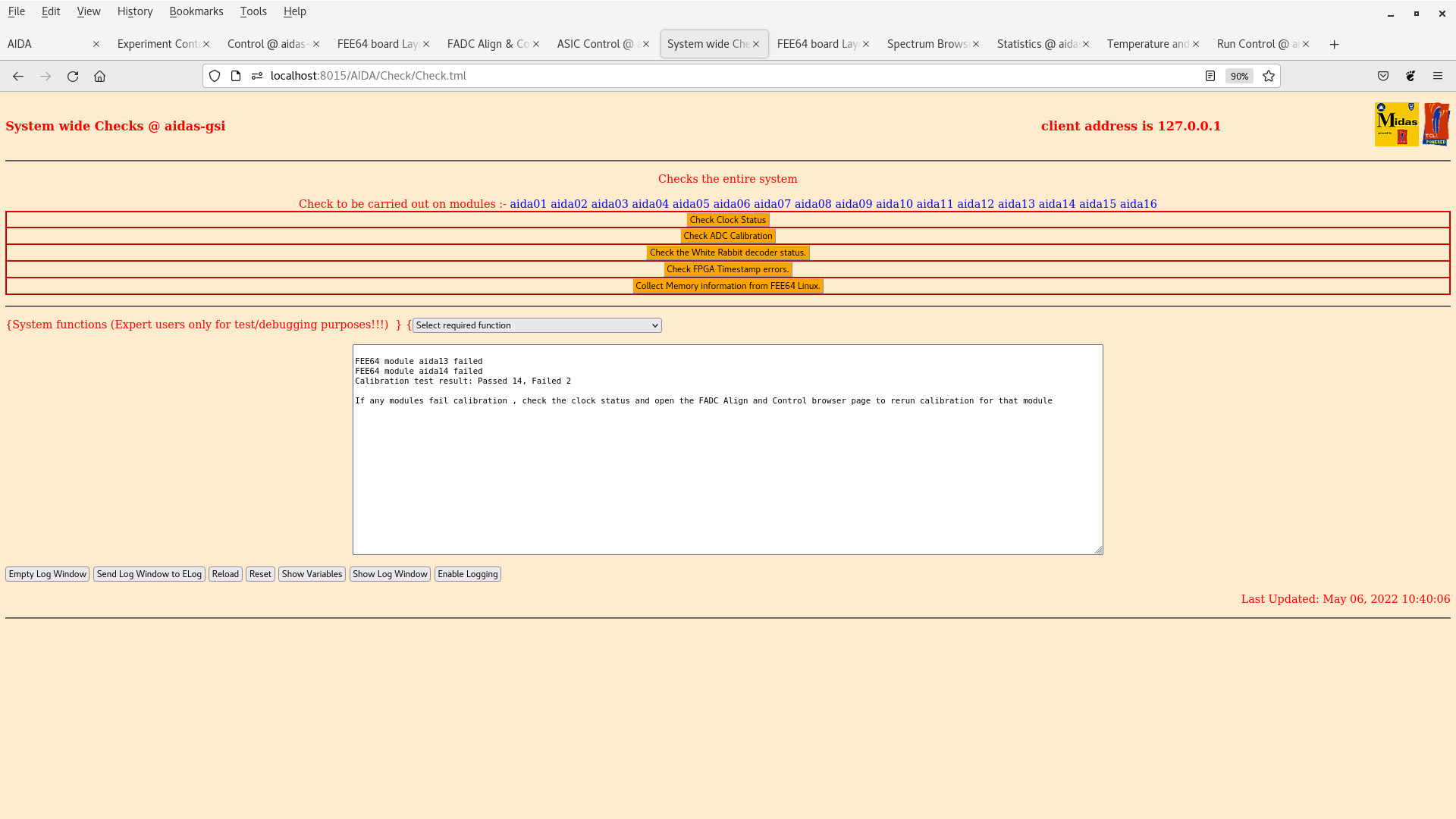

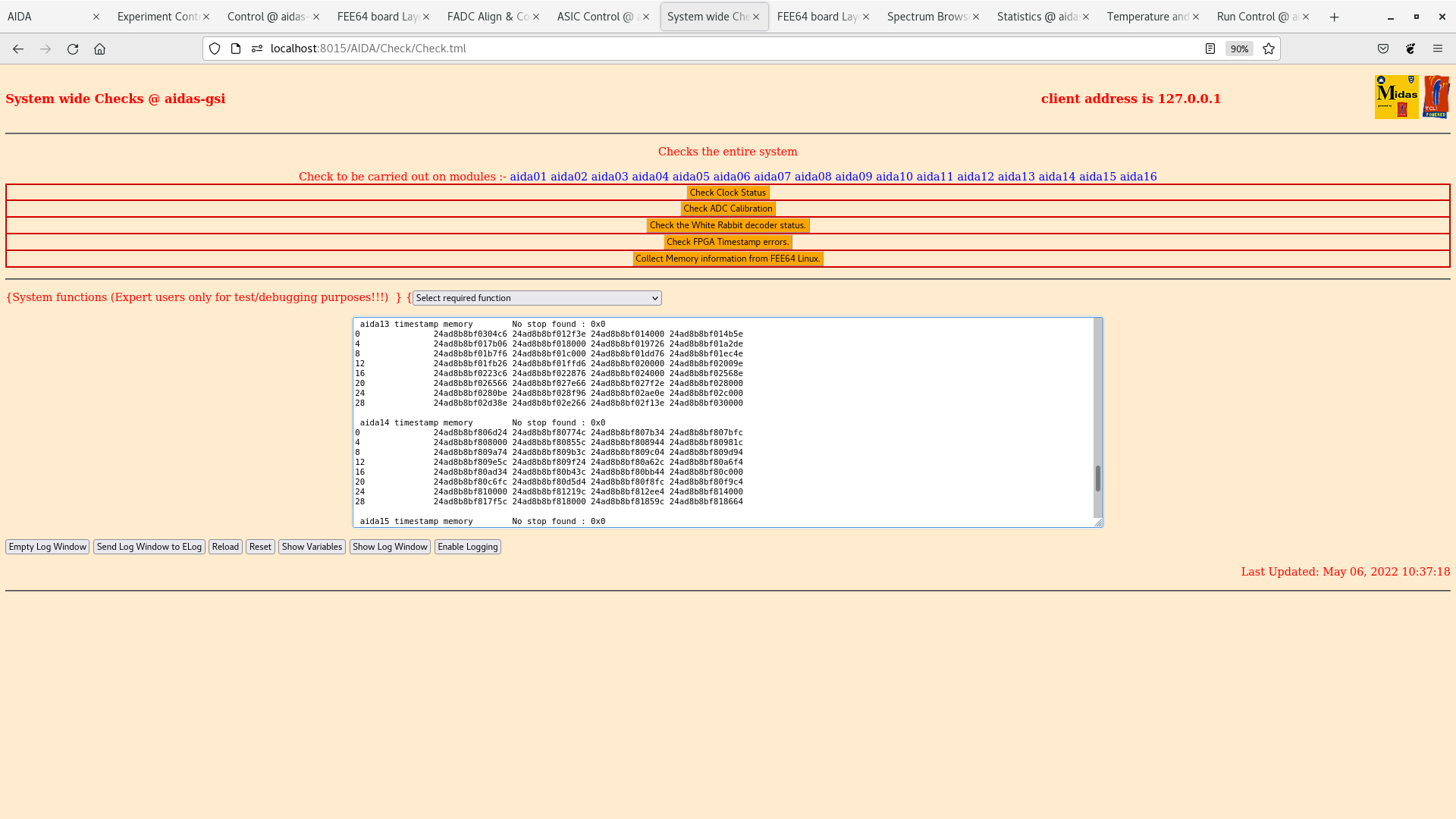

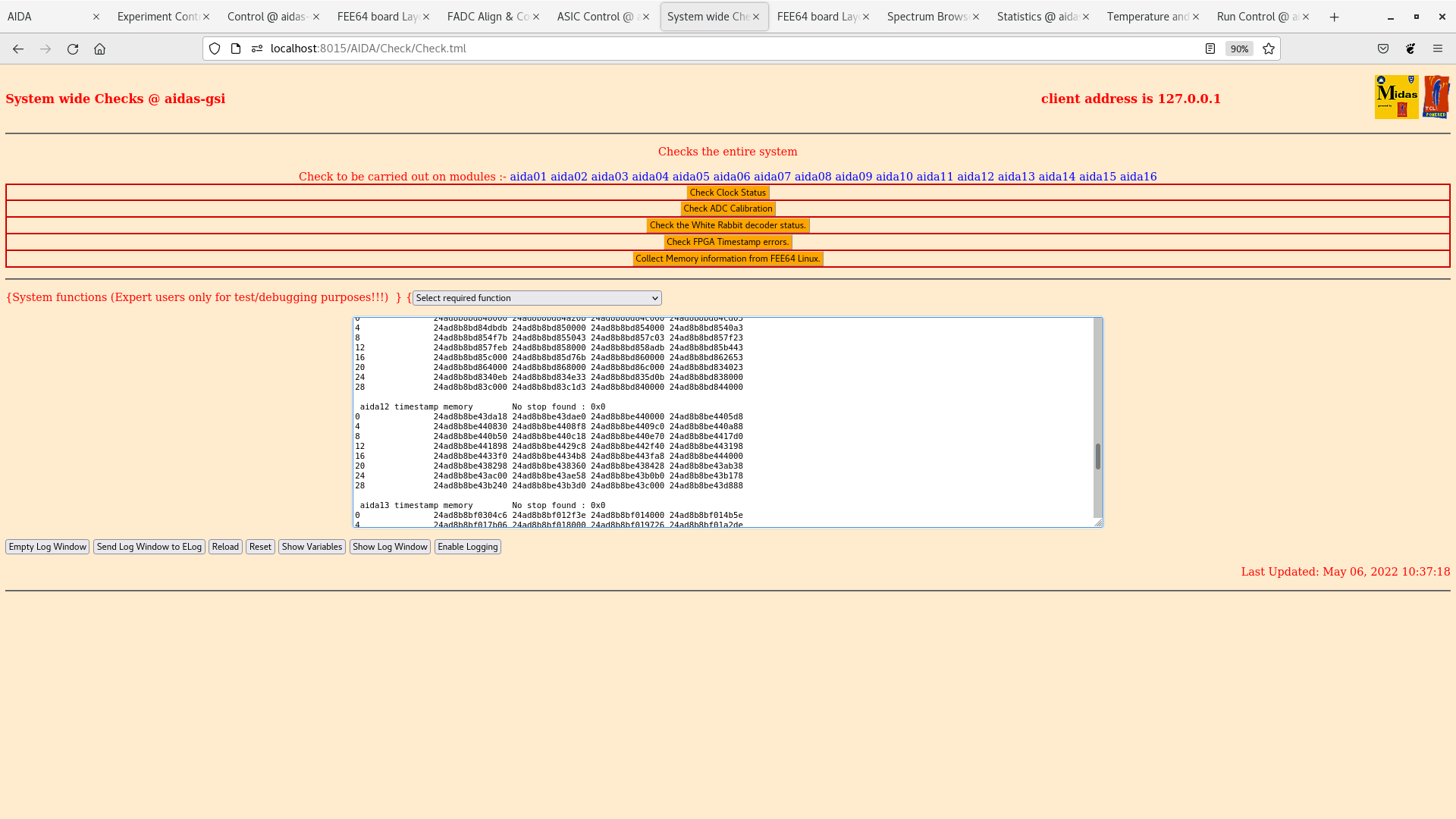

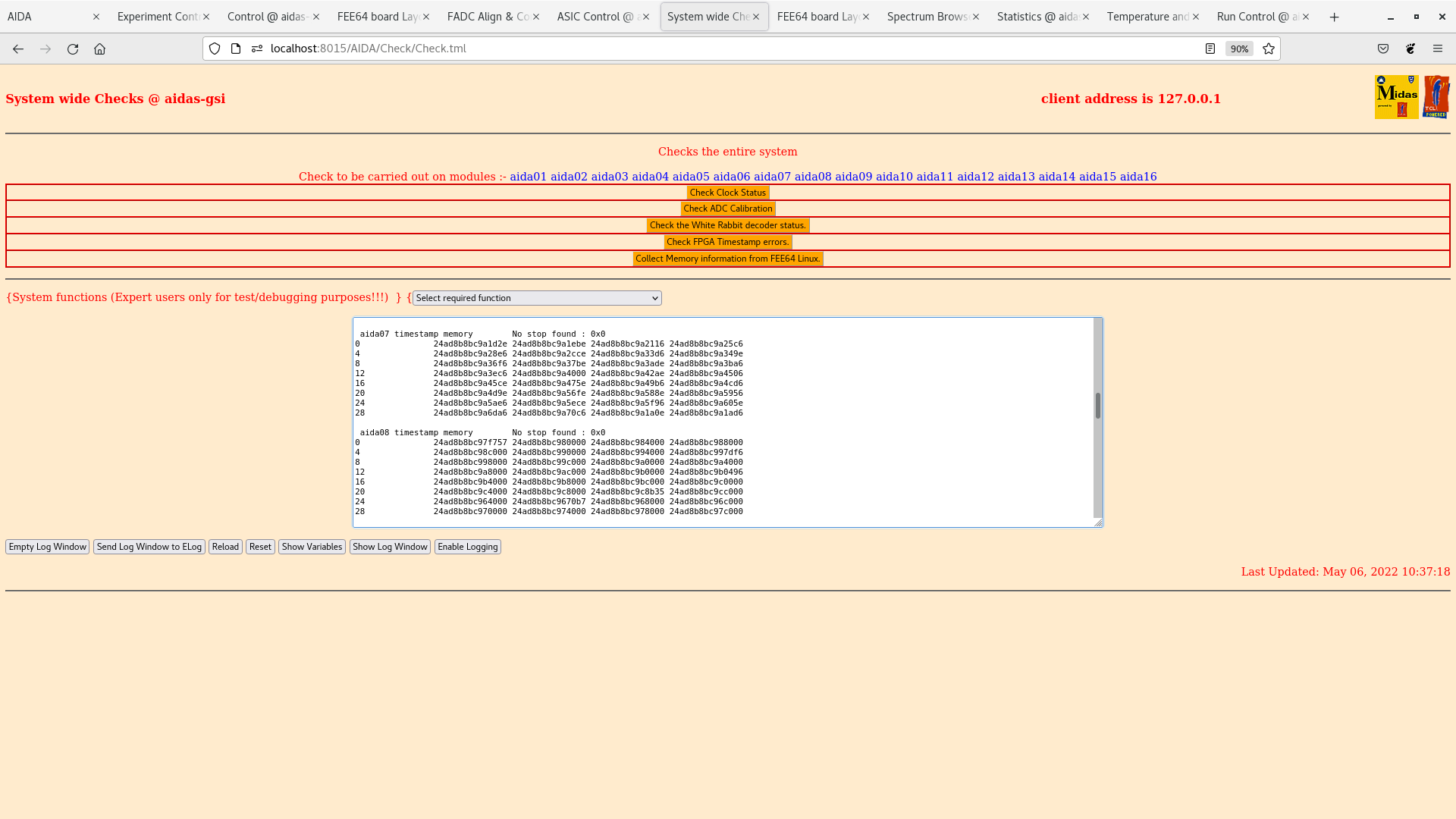

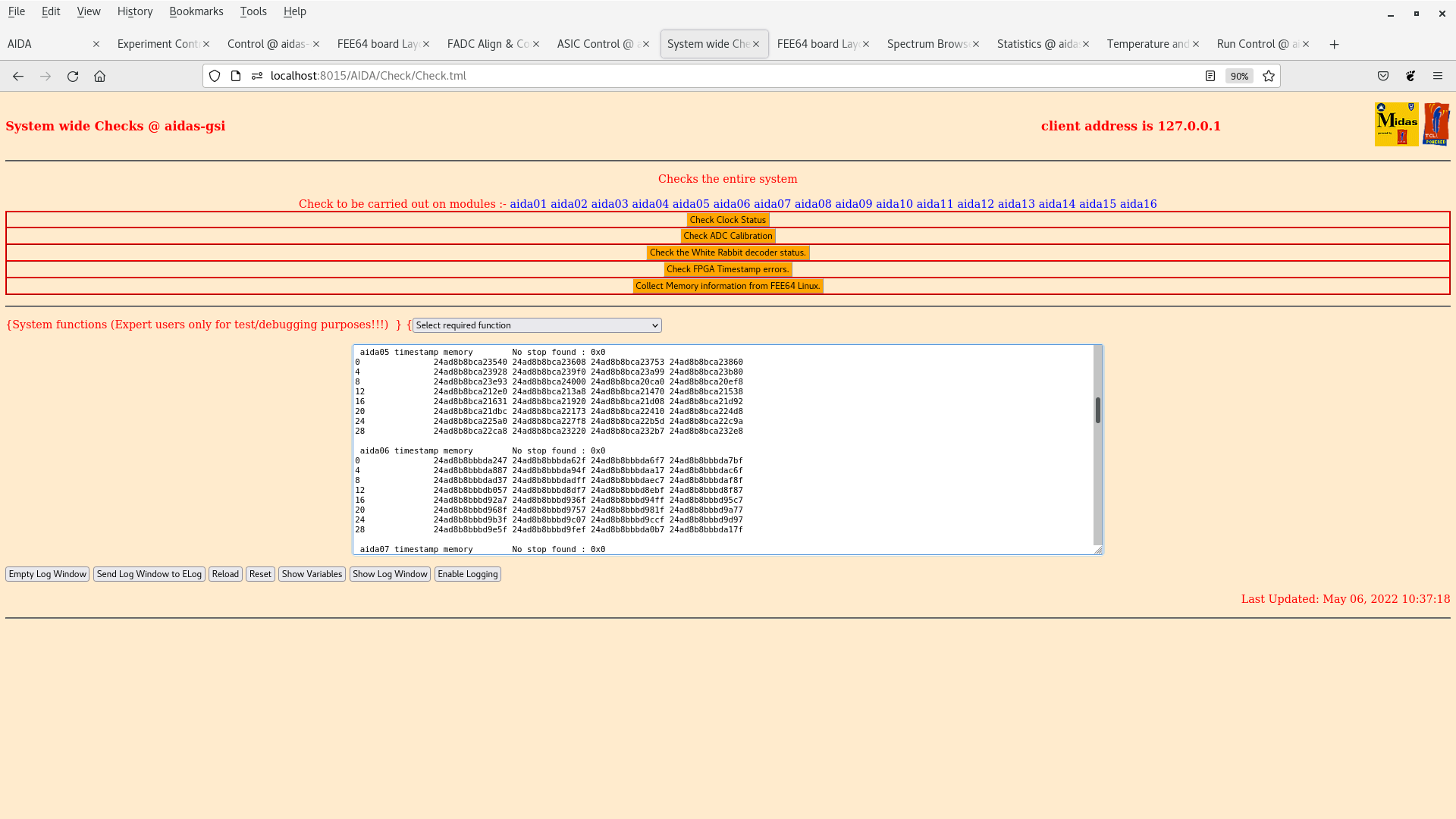

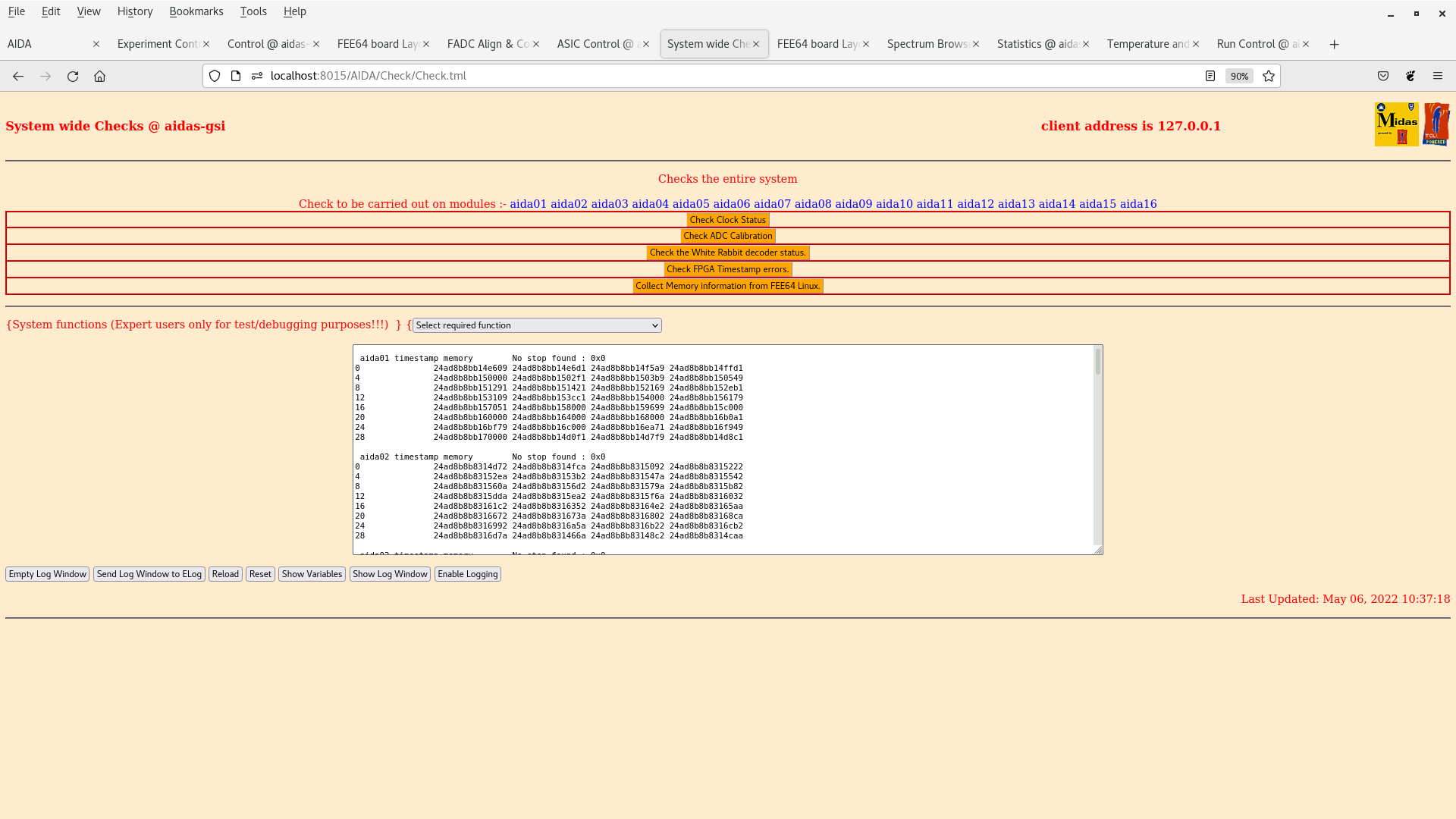

Attachments 7-23 - system wide checks - all OK

10:48 DAQ GO *all* FEE64s

all spectra zero'd

attachment 29 - ADC data items

n+n FEE64s aida02, 4, 6 & 8 c. 250k

p+n FEE64s aida07, 9 & 12 c. 100-150k, all other FEE64s < 100k

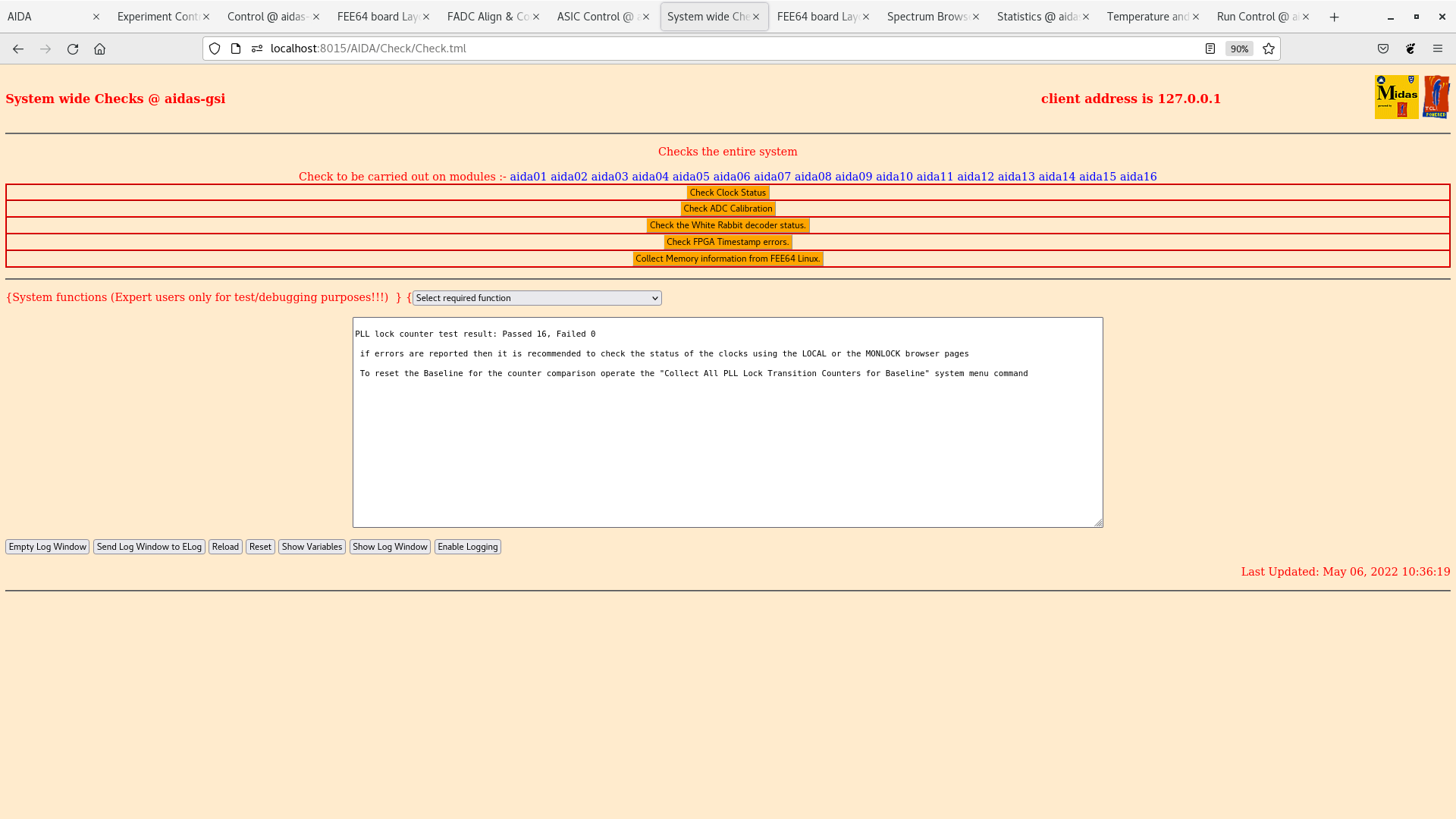

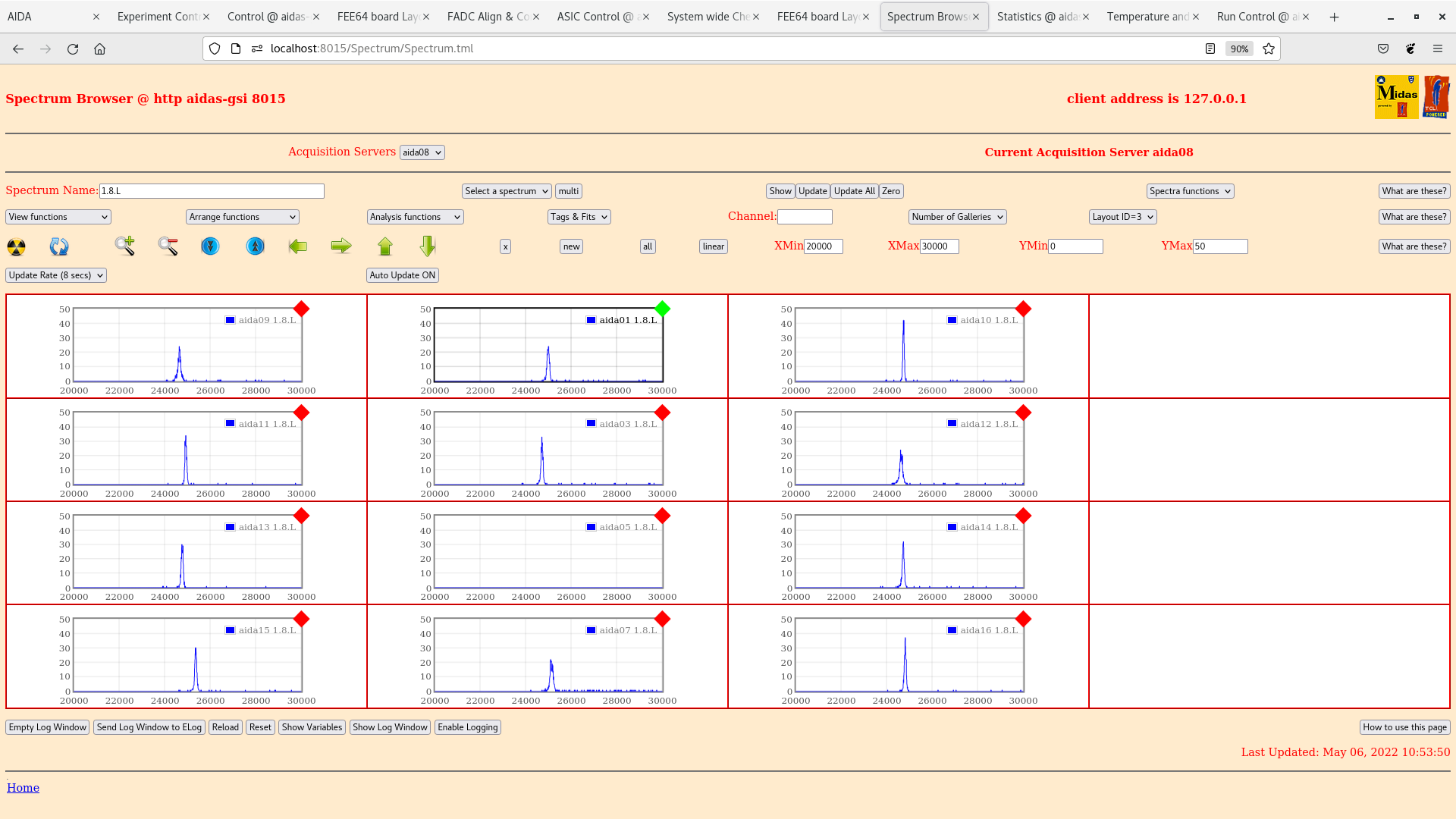

attachments 26 & 27 1.8.L spectra

aida01 peak width 112ch FWHM

aida02 peak width 485 ch FWHM

attachments 24 & 25 1.8.W spectra 20us FSR

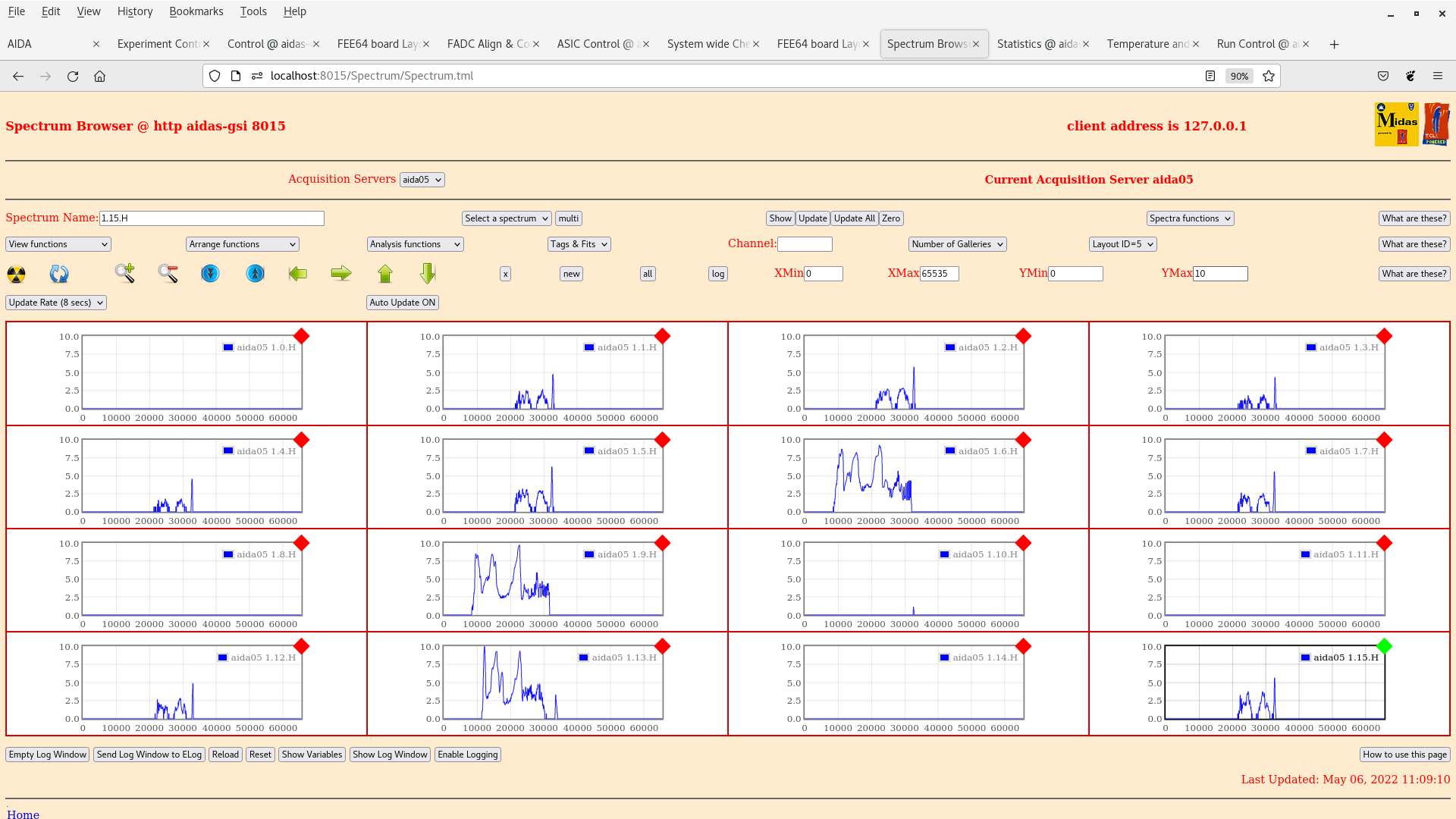

attachment 30 - aida05 1*H spectra - aida05 asic#1 is producing HEC data

attachment 31 - aida05 also producing disc data

attachments 32 & 33 merger and tape server OK - 14MB/s to disk - no data to MBS currently?

18.36 Disconnect ribbon cabling from adaptor PCB - continue to observe HEC events from aida05 asic#1

Disconnect test inputs from adaptor PCB - continue to observe HEC events from aida05 asic#1

Conclude aida05 asic#1 has probably failed in operation and should be replaced. Other FEE64s are currently in CRYRING hall and measurement is in progress - ML says we should be able to access Monday. |

| Attachment 1: Screenshot_from_2022-05-06_10-27-27.png

|

|

| Attachment 2: Screenshot_from_2022-05-06_10-26-59.png

|

|

| Attachment 3: Screenshot_from_2022-05-06_10-26-33.png

|

|

| Attachment 4: Screenshot_from_2022-05-06_10-25-44.png

|

|

| Attachment 5: Screenshot_from_2022-05-06_10-24-54.png

|

|

| Attachment 6: Screenshot_from_2022-05-06_10-42-18.png

|

|

| Attachment 7: Screenshot_from_2022-05-06_10-41-06.png

|

|

| Attachment 8: Screenshot_from_2022-05-06_10-41-00.png

|

|

| Attachment 9: Screenshot_from_2022-05-06_10-40-54.png

|

|

| Attachment 10: Screenshot_from_2022-05-06_10-40-09.png

|

|

| Attachment 11: Screenshot_from_2022-05-06_10-39-07.png

|

|

| Attachment 12: Screenshot_from_2022-05-06_10-38-58.png

|

|

| Attachment 13: Screenshot_from_2022-05-06_10-38-35.png

|

|

| Attachment 14: Screenshot_from_2022-05-06_10-38-21.png

|

|

| Attachment 15: Screenshot_from_2022-05-06_10-38-16.png

|

|

| Attachment 16: Screenshot_from_2022-05-06_10-38-10.png

|

|

| Attachment 17: Screenshot_from_2022-05-06_10-38-02.png

|

|

| Attachment 18: Screenshot_from_2022-05-06_10-37-52.png

|

|

| Attachment 19: Screenshot_from_2022-05-06_10-37-46.png

|

|

| Attachment 20: Screenshot_from_2022-05-06_10-37-39.png

|

|

| Attachment 21: Screenshot_from_2022-05-06_10-37-31.png

|

|

| Attachment 22: Screenshot_from_2022-05-06_10-36-24.png

|

|

| Attachment 23: Screenshot_from_2022-05-06_10-35-52.png

|

|

| Attachment 24: Screenshot_from_2022-05-06_10-56-31.png

|

|

| Attachment 25: Screenshot_from_2022-05-06_10-55-56.png

|

|

| Attachment 26: Screenshot_from_2022-05-06_10-55-13.png

|

|

| Attachment 27: Screenshot_from_2022-05-06_10-53-53.png

|

|

| Attachment 28: Screenshot_from_2022-05-06_10-51-00.png

|

|

| Attachment 29: Screenshot_from_2022-05-06_10-50-25.png

|

|

| Attachment 30: Screenshot_from_2022-05-06_11-09-15.png

|

|

| Attachment 31: Screenshot_from_2022-05-06_11-02-33.png

|

|

| Attachment 32: Screenshot_from_2022-05-06_11-19-48.png

|

|

| Attachment 33: Screenshot_from_2022-05-06_11-19-27.png

|

|

|

|

355

|

Fri Jun 4 08:40:52 2021 |

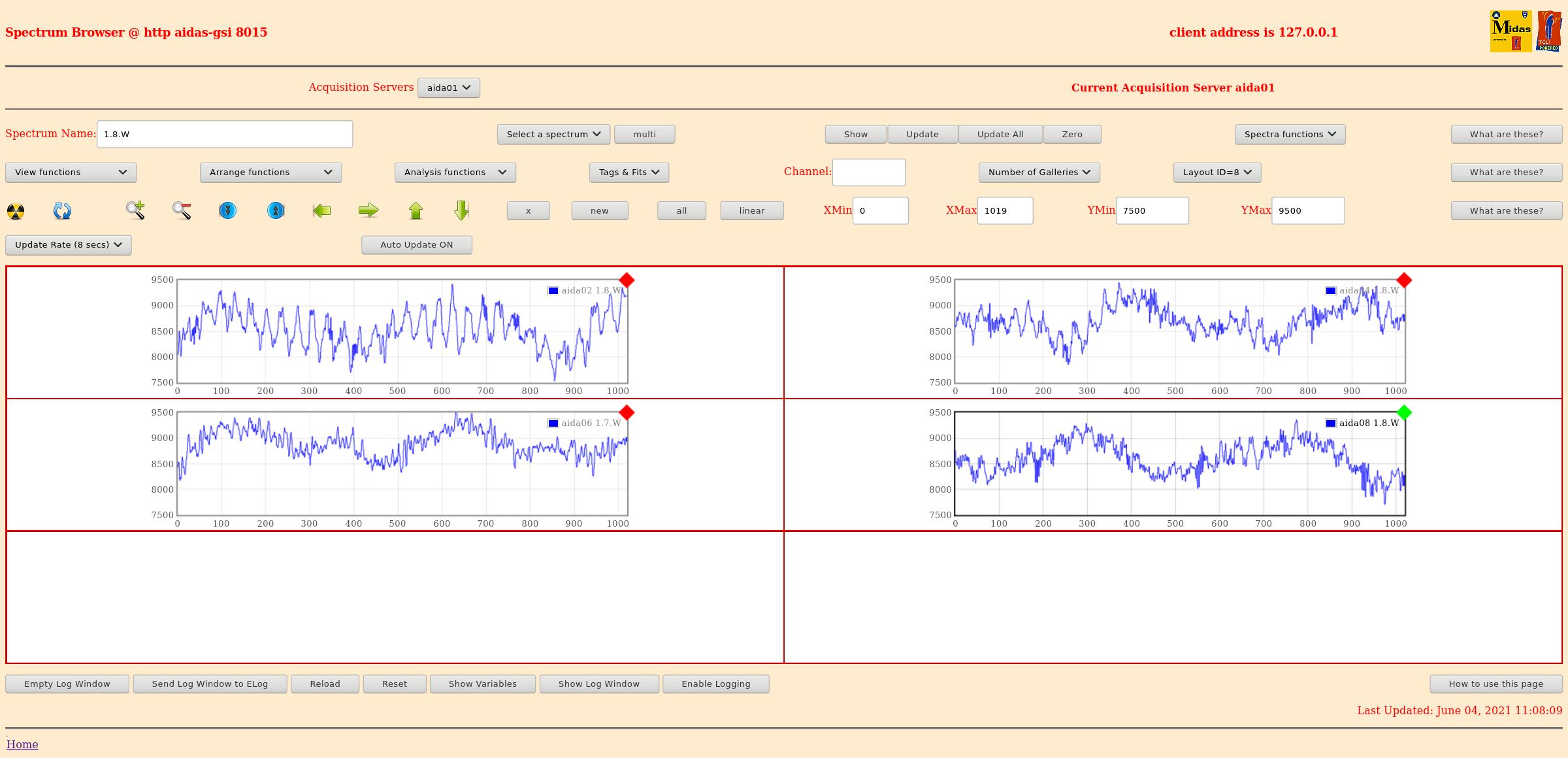

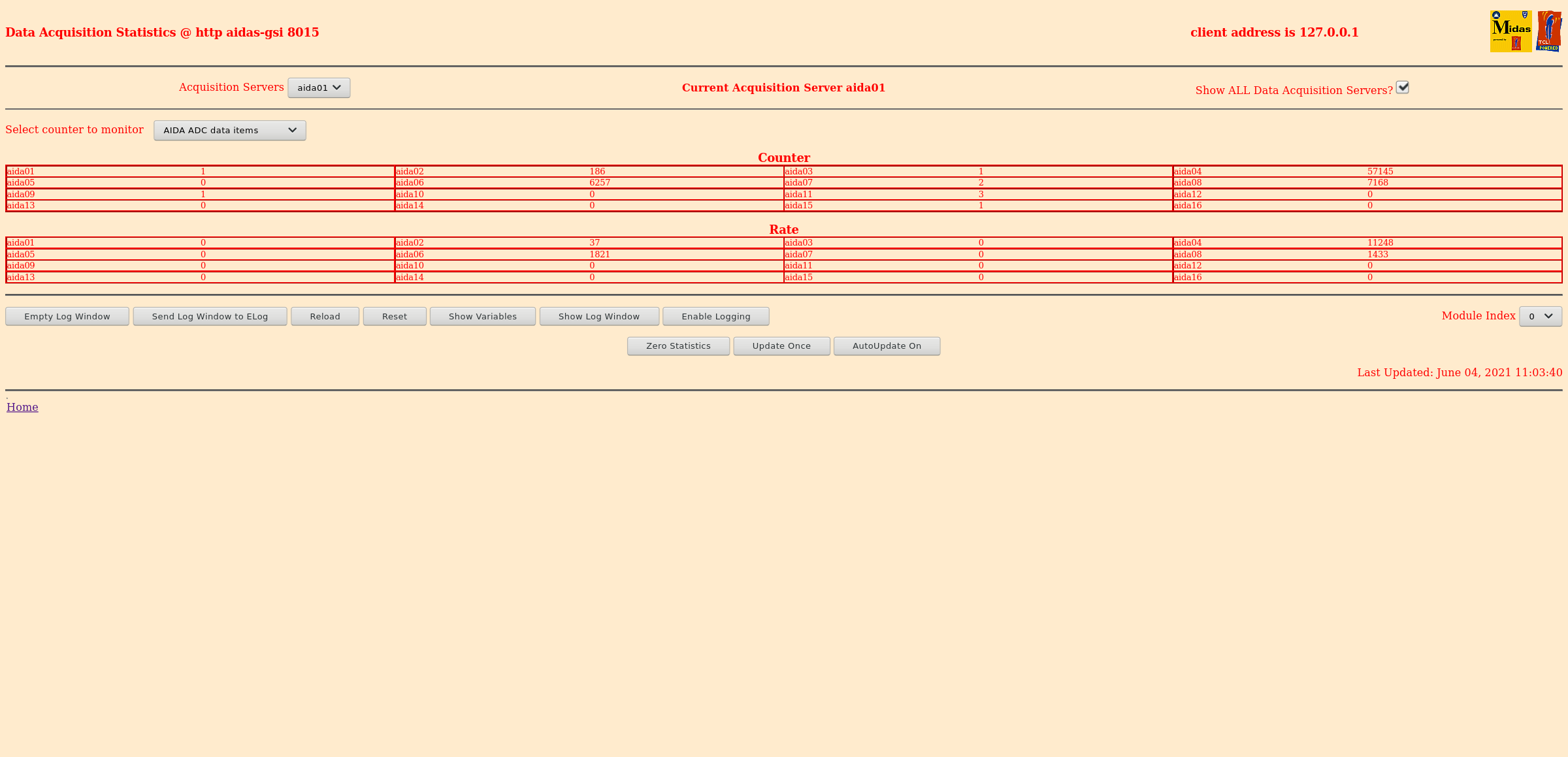

TD | Friday 4 June |

09.20 DAQ found stopped

files in /TapeData/S496 indicate increased data rate yesterday evening from c. 18.00 until data stopped at c. midnight

aida15 rebooted at 00.02

regained control of DAQ and issued DAQ STOP by restarting NewMerger *twice*

11.00 DAQ reset and setup

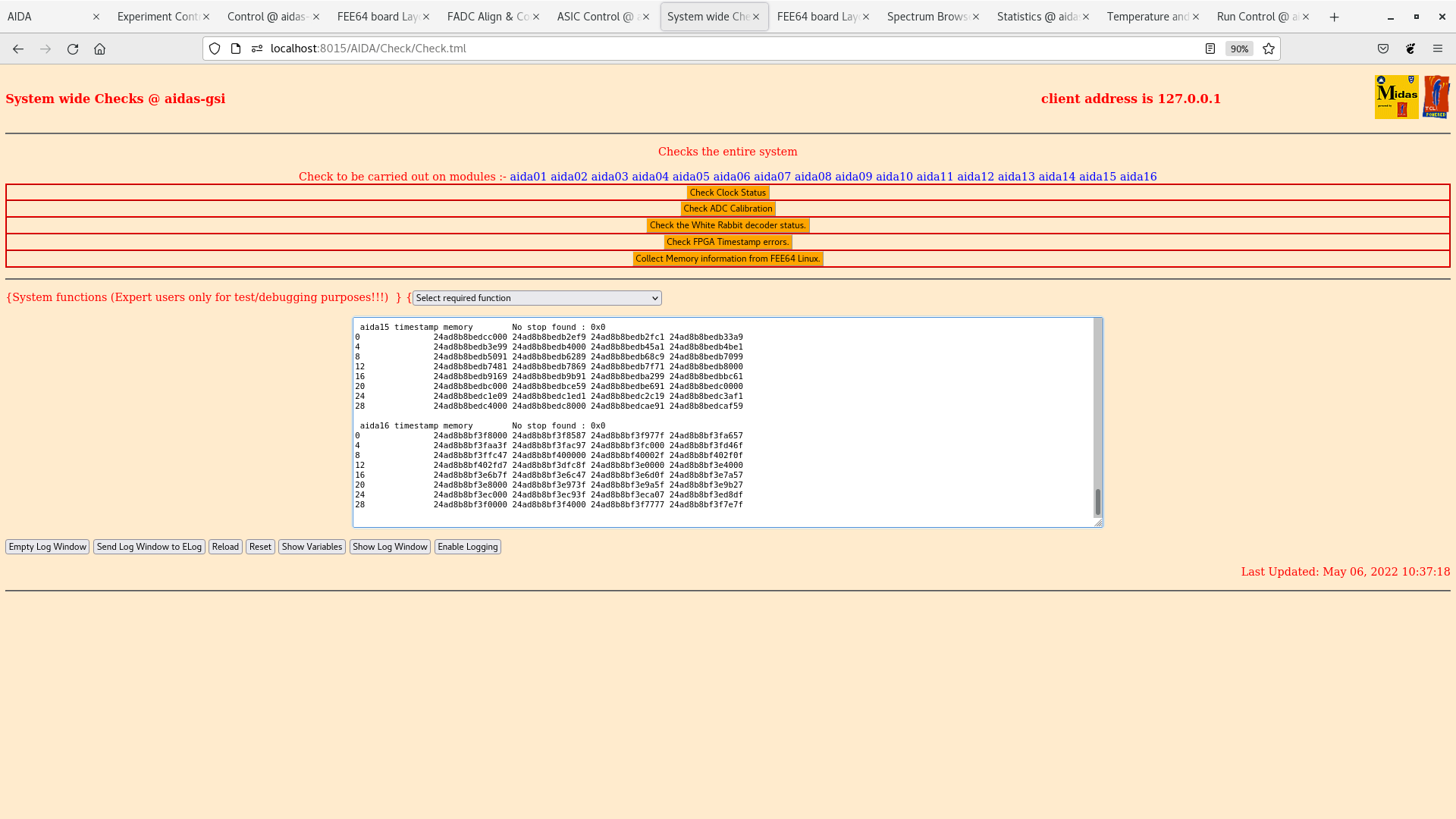

All system wide checks OK *except*

Base Current Difference

aida05 fault 0x4d3c : 0x4d3c : 0

aida05 : WR status 0x10

White Rabbit error counter test result: Passed 15, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

Returned 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 2 4 2 8 5 4 1 2 2 4 7 : 41352

aida02 : 0 3 3 6 6 4 1 2 2 4 7 : 41352

aida03 : 2 4 2 12 1 3 2 2 2 4 7 : 41352

aida04 : 2 2 1 7 4 3 2 2 2 4 7 : 41352

aida05 : 2 3 1 5 3 2 3 2 2 4 7 : 41360

aida06 : 2 4 2 6 4 3 2 2 2 4 7 : 41352

aida07 : 1 5 2 9 4 2 4 3 1 4 7 : 41324

aida08 : 0 3 1 7 4 3 4 3 1 4 7 : 41352

aida09 : 3 3 0 8 2 2 3 2 2 4 7 : 41380

aida10 : 1 2 2 11 3 2 3 3 3 3 7 : 41044

aida11 : 2 3 1 6 6 4 2 3 3 3 7 : 41072

aida12 : 4 2 1 8 3 3 3 3 1 4 7 : 41072

aida13 : 2 4 1 8 4 4 2 3 3 3 7 : 41016

aida14 : 1 4 1 9 4 4 2 3 3 3 7 : 41044

aida15 : 0 5 1 2 2 1 2 4 3 4 7 : 42872

aida16 : 1 3 2 9 4 4 4 4 2 3 7 : 41052

Collecting the file size of each FEE64 Options CONTENTS file to check they are all the same

FEE : aida01 => Options file size is 1026 Last changed Fri Jun 04 09:30:42 CEST 2021

FEE : aida02 => Options file size is 1025 Last changed Sun May 23 00:19:21 CEST 2021

FEE : aida03 => Options file size is 1014 Last changed Thu Apr 29 14:43:50 CEST 2021

FEE : aida04 => Options file size is 1025 Last changed Fri May 14 16:54:56 CEST 2021

FEE : aida05 => Options file size is 1025 Last changed Mon May 17 06:25:41 CEST 2021

FEE : aida06 => Options file size is 1014 Last changed Thu Apr 29 14:43:59 CEST 2021

FEE : aida07 => Options file size is 1014 Last changed Thu Apr 29 14:44:02 CEST 2021

FEE : aida08 => Options file size is 1025 Last changed Sun May 23 00:16:54 CEST 2021

FEE : aida09 => Options file size is 1014 Last changed Thu Apr 29 14:44:08 CEST 2021

FEE : aida10 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida11 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida12 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida13 => Options file size is 1025 Last changed Fri May 07 19:40:34 CEST 2021

FEE : aida14 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida15 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida16 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

11.03 DAQ resumes file S496/R32

alpha background

slow comparator 0x64

BNC PB-5 pulser OFF

11.09 1.8.W spectra - 20us FSR - attachments 1 & 2

Grafana - DSSSD bias & leakage current - most recent 7 days - attachment 3

ADC data items - attachment 4

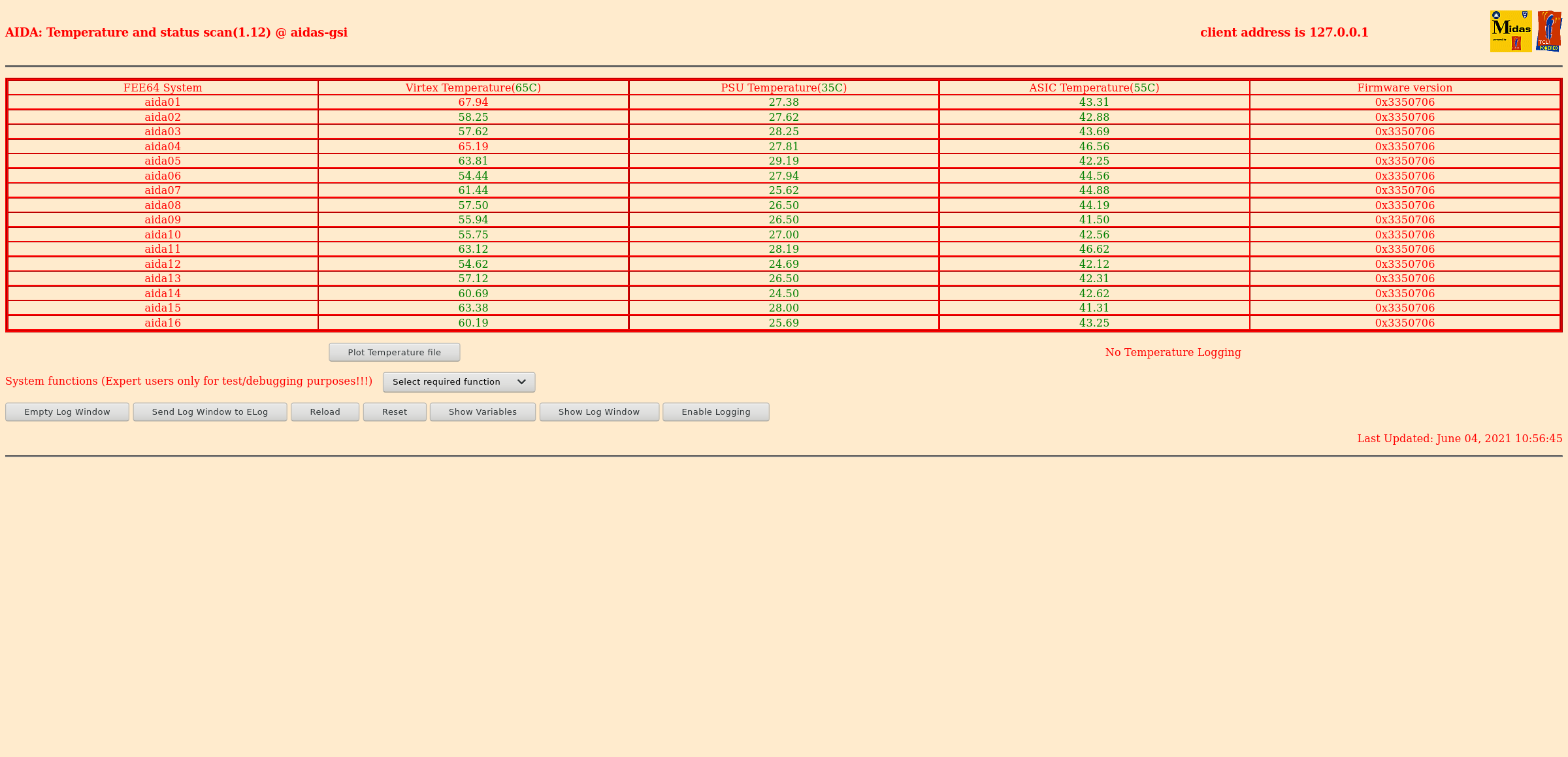

FEE64 temperatures OK - attachment 5

DSSSD bias & leakage currents OK - attachment 6

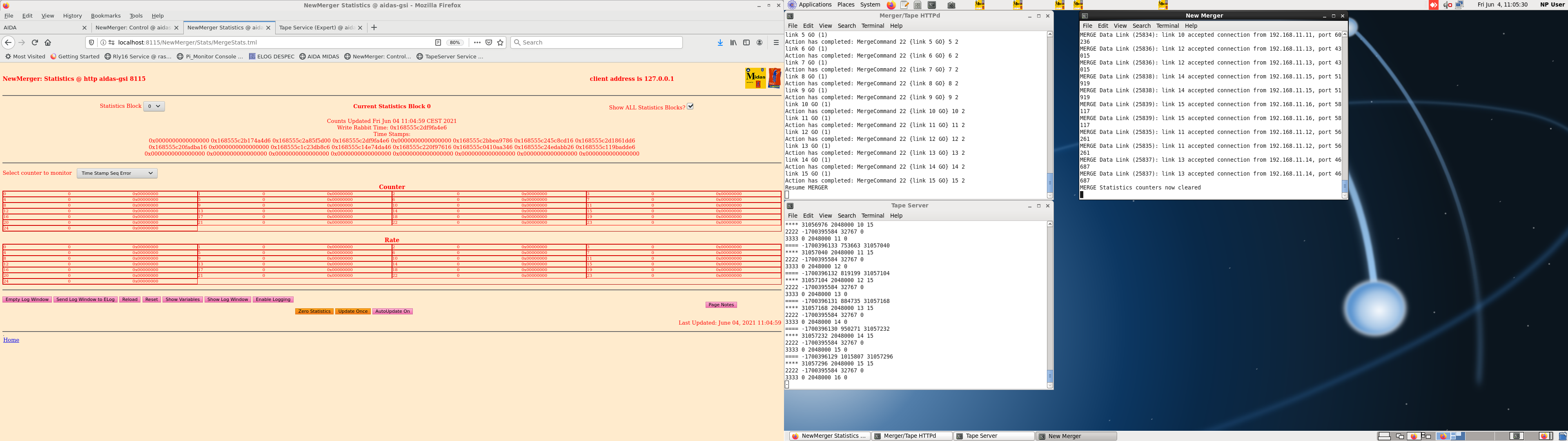

Merger/Tape Server/Merger statistics - attachment 7

no merger errors reported since previous restart

13.07 analysis of file S496/R32_16 - attachment 8

max deadtime 0.18% aida04 |

| Attachment 1: Screenshot_2021-06-04_Spectrum_Browser_aidas-gsi(1).png

|

.png.png)

|

| Attachment 2: Screenshot_2021-06-04_Spectrum_Browser_aidas-gsi.png

|

|

| Attachment 3: Screenshot_2021-06-04_AIDA_Alerting_-_Grafana.png

|

|

| Attachment 4: Screenshot_2021-06-04_Statistics_aidas-gsi.png

|

|

| Attachment 5: Screenshot_2021-06-04_Temperature_and_status_scan_aidas-gsi.png

|

|

| Attachment 6: 980.png

|

|

| Attachment 7: 981.png

|

|

| Attachment 8: R32_16

|

*** TDR format 3.3.0 analyser - TD - May 2021

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 49166189 ( 17465.0 Hz)

Other data format: 212753815 ( 75575.1 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 137 ( 0.0 Hz)

RESUME: 137 ( 0.0 Hz)

SYNC100: 42486 ( 15.1 Hz)

WR48-63: 42486 ( 15.1 Hz)

FEE64 disc: 1037793 ( 368.6 Hz)

MBS info: 211630776 ( 75176.2 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 0 ( 0.0 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 2815.130 s

FEE elapsed dead time(s) elapsed idle time(s)

0 0.000 0.000

1 0.000 2759.088

2 0.741 0.000

3 4.946 0.000

4 0.000 0.000

5 0.000 2173.993

6 0.000 0.000

7 0.000 2104.432

8 0.000 0.000

9 0.000 0.000

10 0.000 0.000

11 0.000 0.000

12 0.000 0.000

13 0.000 0.000

14 0.000 0.000

15 0.000 0.000

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 184 0 0 0 0 0 0 0 0 0 0 0

1 115458 62 0 0 0 0 31 31 0 0 0 0

2 444 105932150 0 0 36 36 18754 18754 0 105894570 0 0

3 39683483 106817705 0 0 101 101 21752 21752 1037793 105736206 0 0

4 154 0 0 0 0 0 0 0 0 0 0 0

5 4413391 1852 0 0 0 0 926 926 0 0 0 0

6 586 0 0 0 0 0 0 0 0 0 0 0

7 4948958 2044 0 0 0 0 1022 1022 0 0 0 0

8 489 0 0 0 0 0 0 0 0 0 0 0

9 77 0 0 0 0 0 0 0 0 0 0 0

10 1172 0 0 0 0 0 0 0 0 0 0 0

11 163 2 0 0 0 0 1 1 0 0 0 0

12 754 0 0 0 0 0 0 0 0 0 0 0

13 94 0 0 0 0 0 0 0 0 0 0 0

14 605 0 0 0 0 0 0 0 0 0 0 0

15 177 0 0 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time: 29.027s ( 1102.409 blocks/s, 68.901 Mb/s)

|

|

|

697

|

Fri Jan 31 17:26:47 2025 |

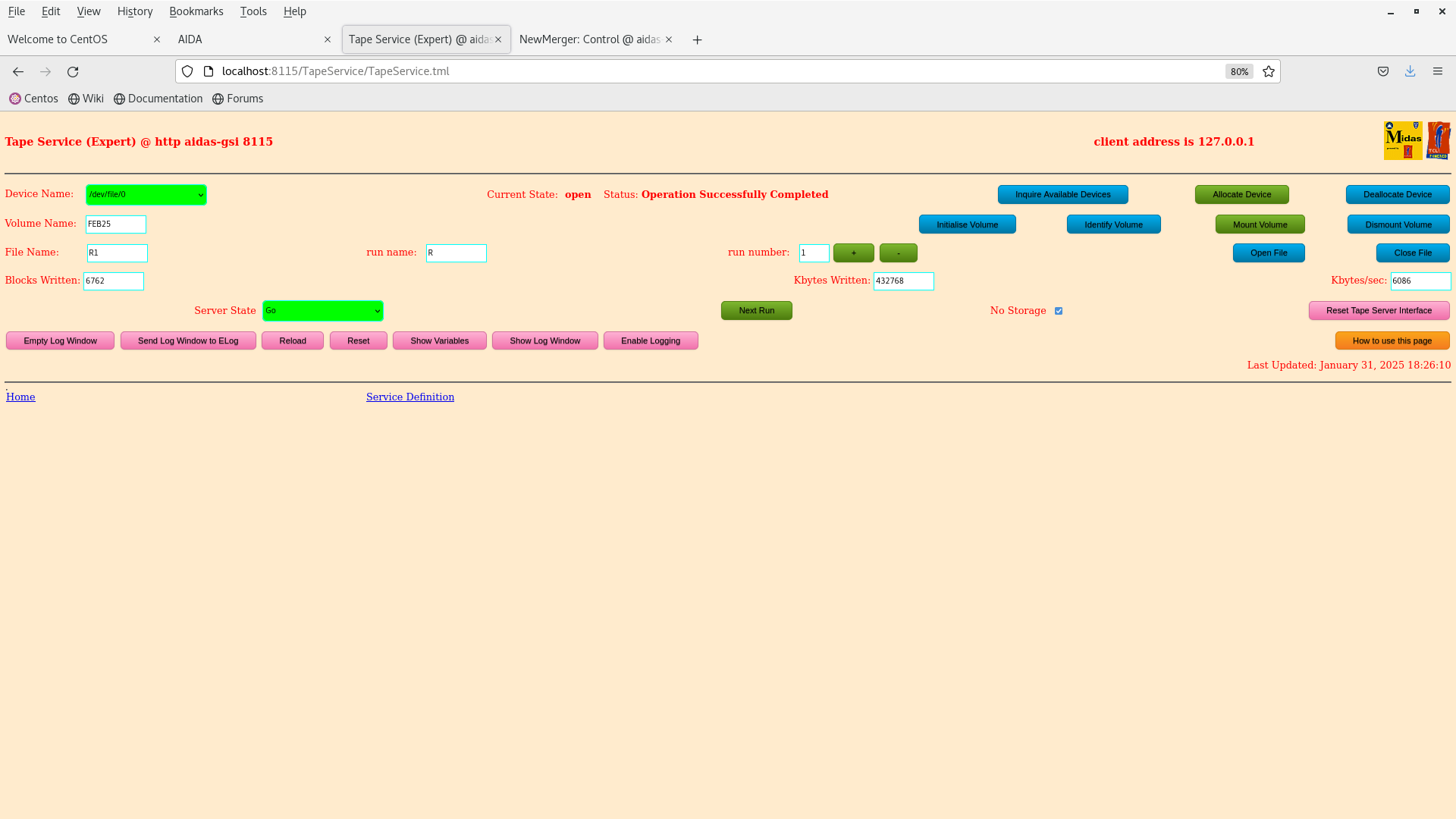

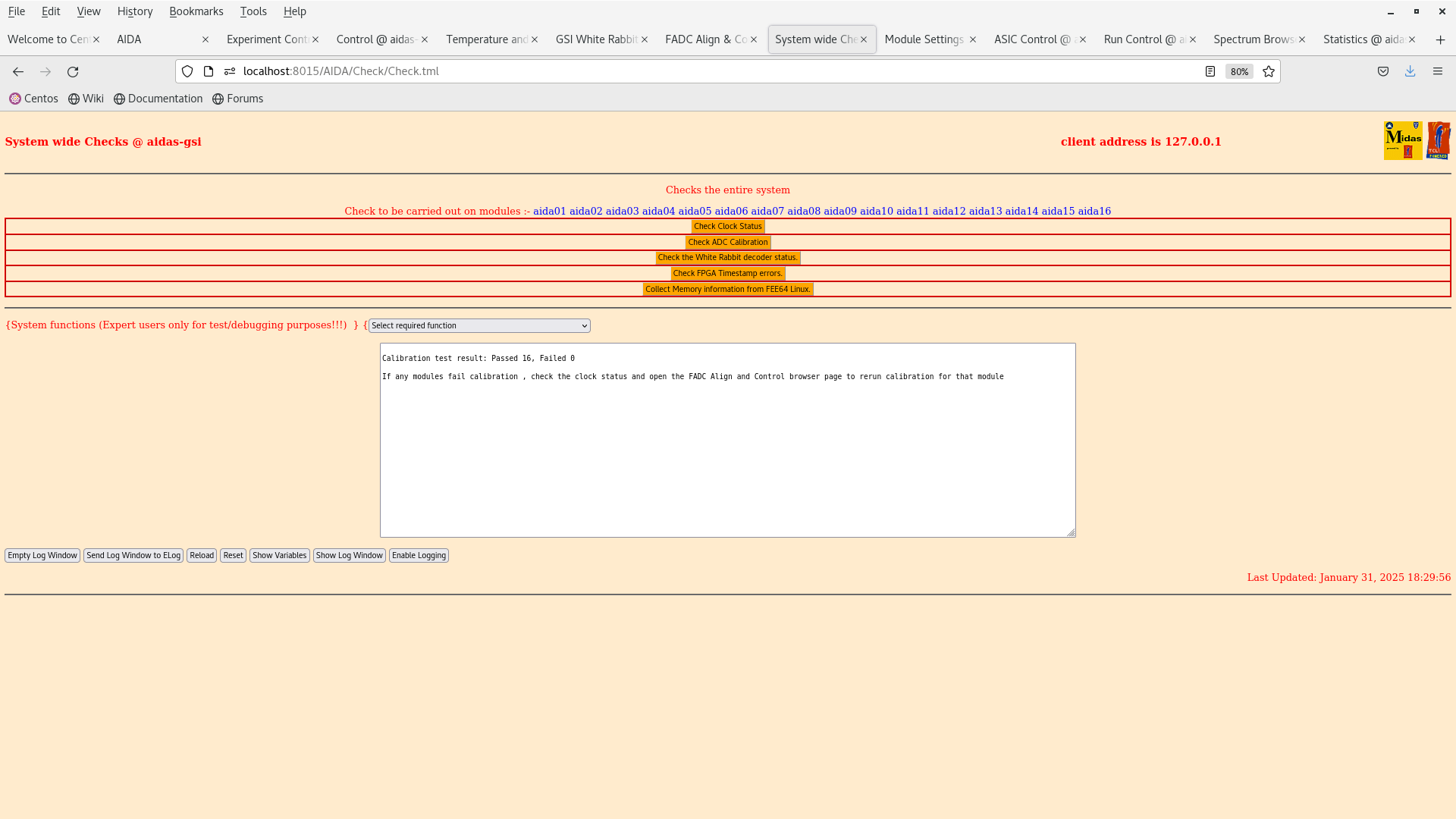

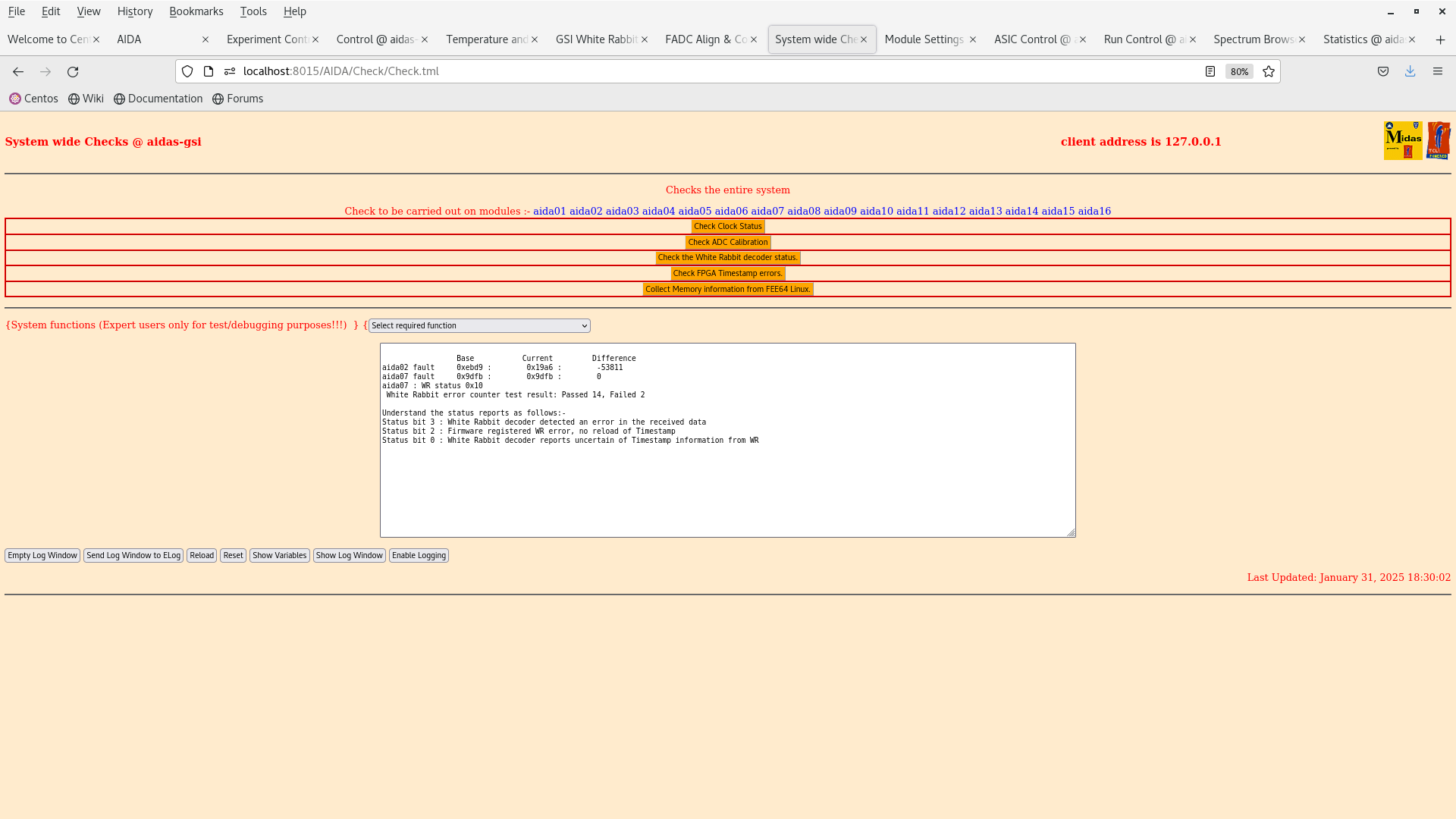

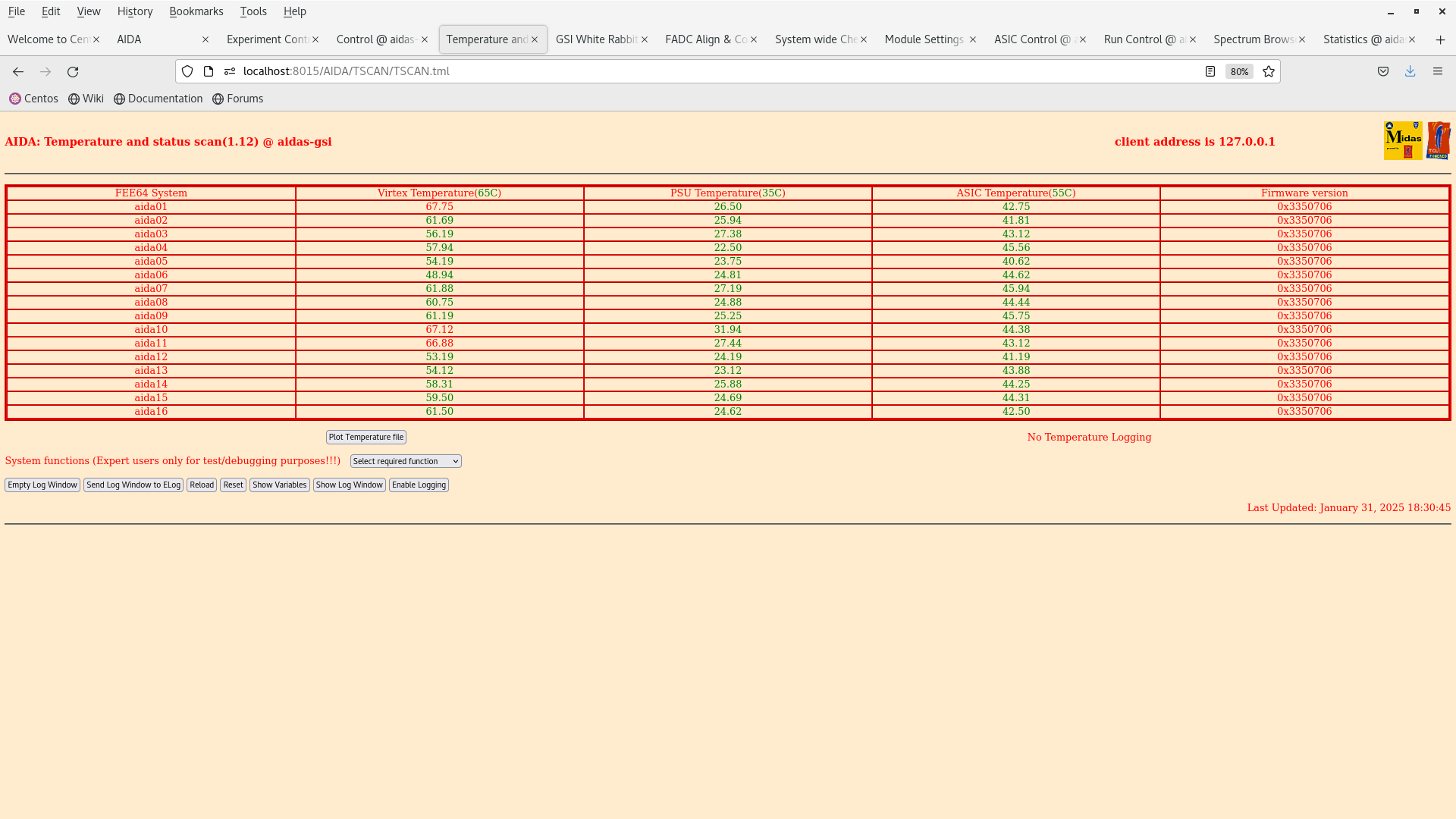

CC, TD, MP | Friday 31 January contd. |

18.18 bPlas and BB7 installs complete

Restart AIDA DAQ, Merger, Tape Server and re-test

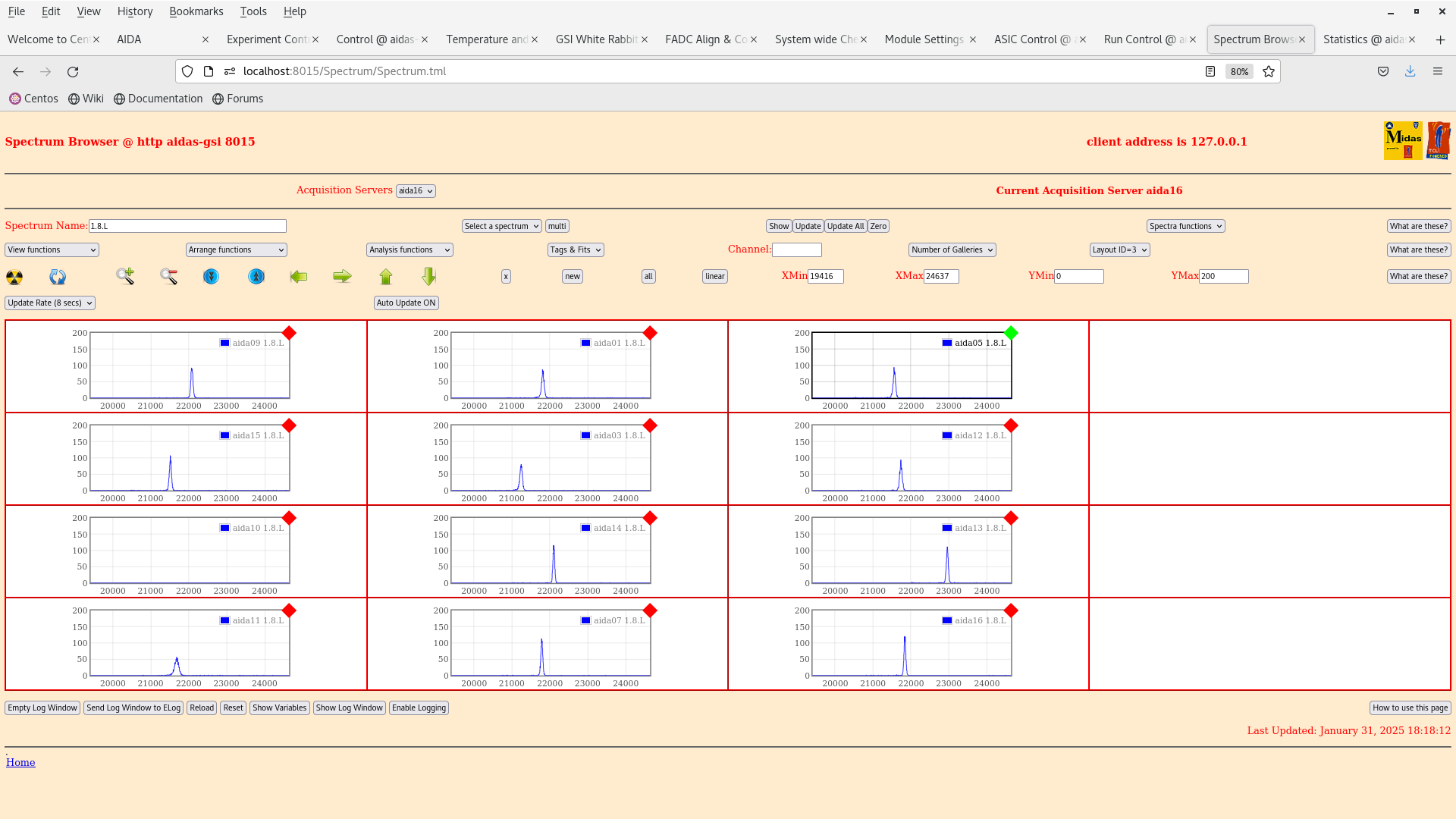

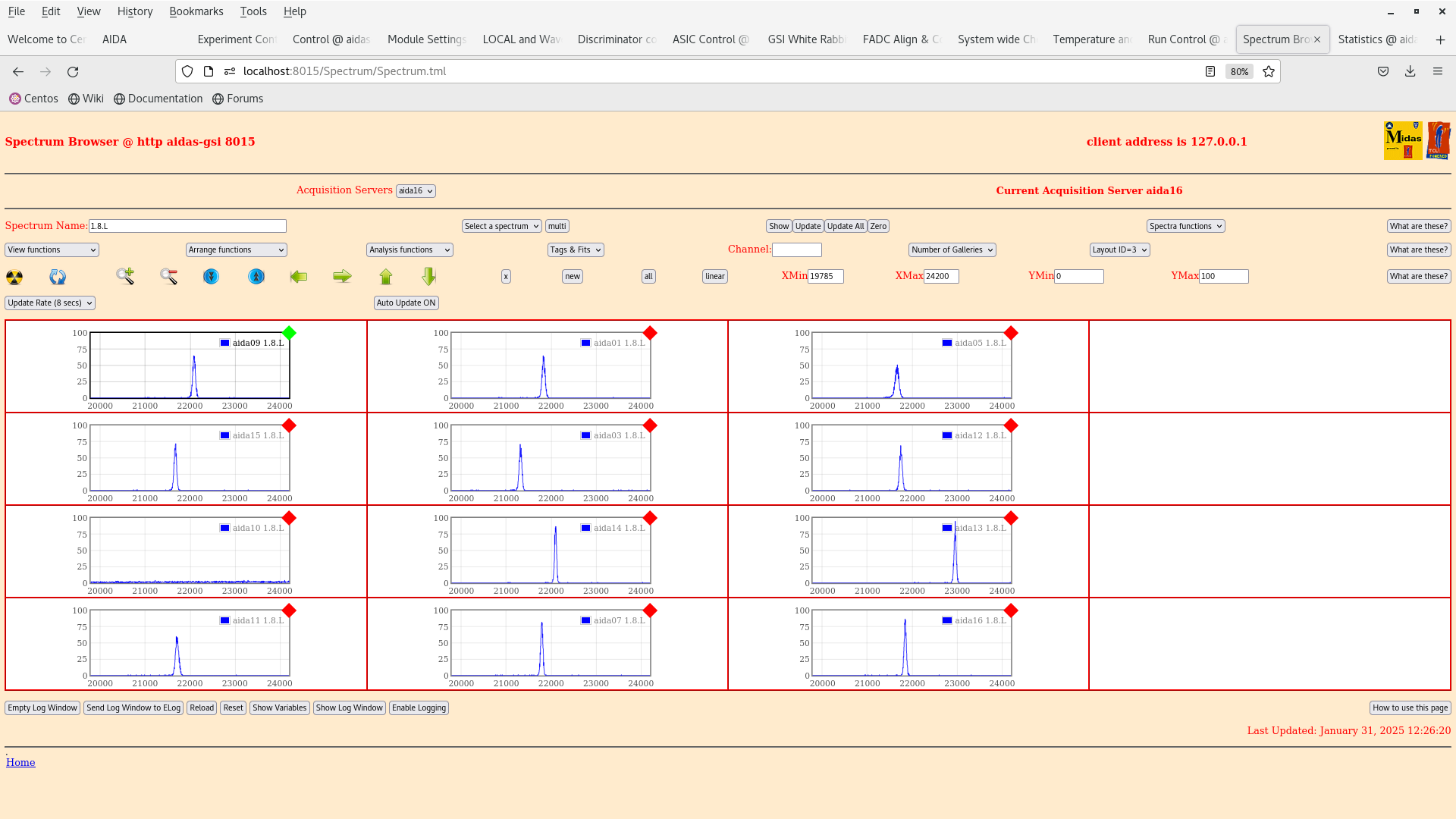

per p+n FEE64 1.8.L spectra - attachment 1

aida09 pulser peak width 69 ch FWHM = 42keV FWHM

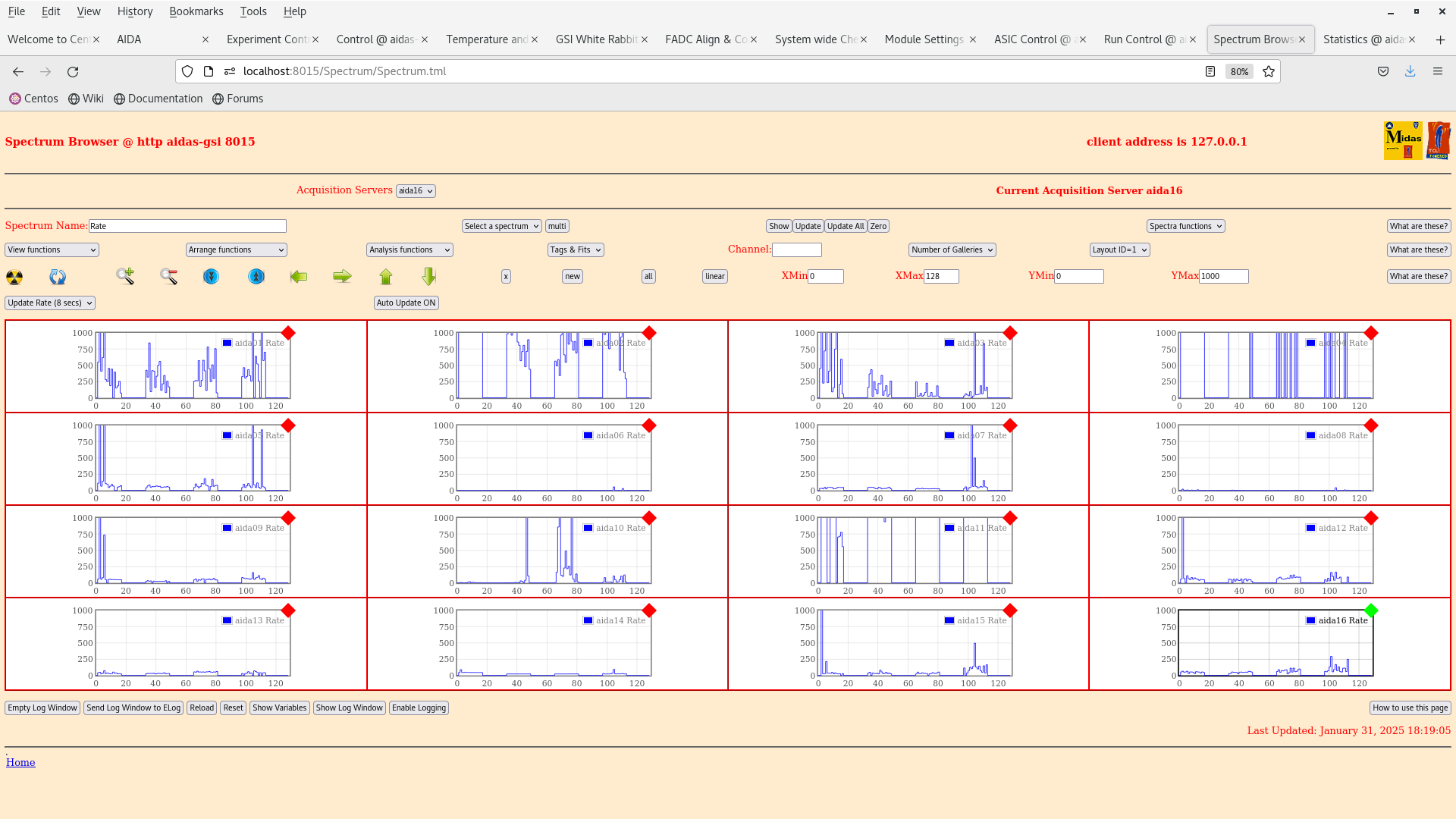

per FEE64 Rate Spectra - attachment 2

BB18 p+n FEE64s very good/good, n+n FEE64s OK - could be improved

BB7 aida10 p+n asics good, n+n asics 1x good, 1x OK

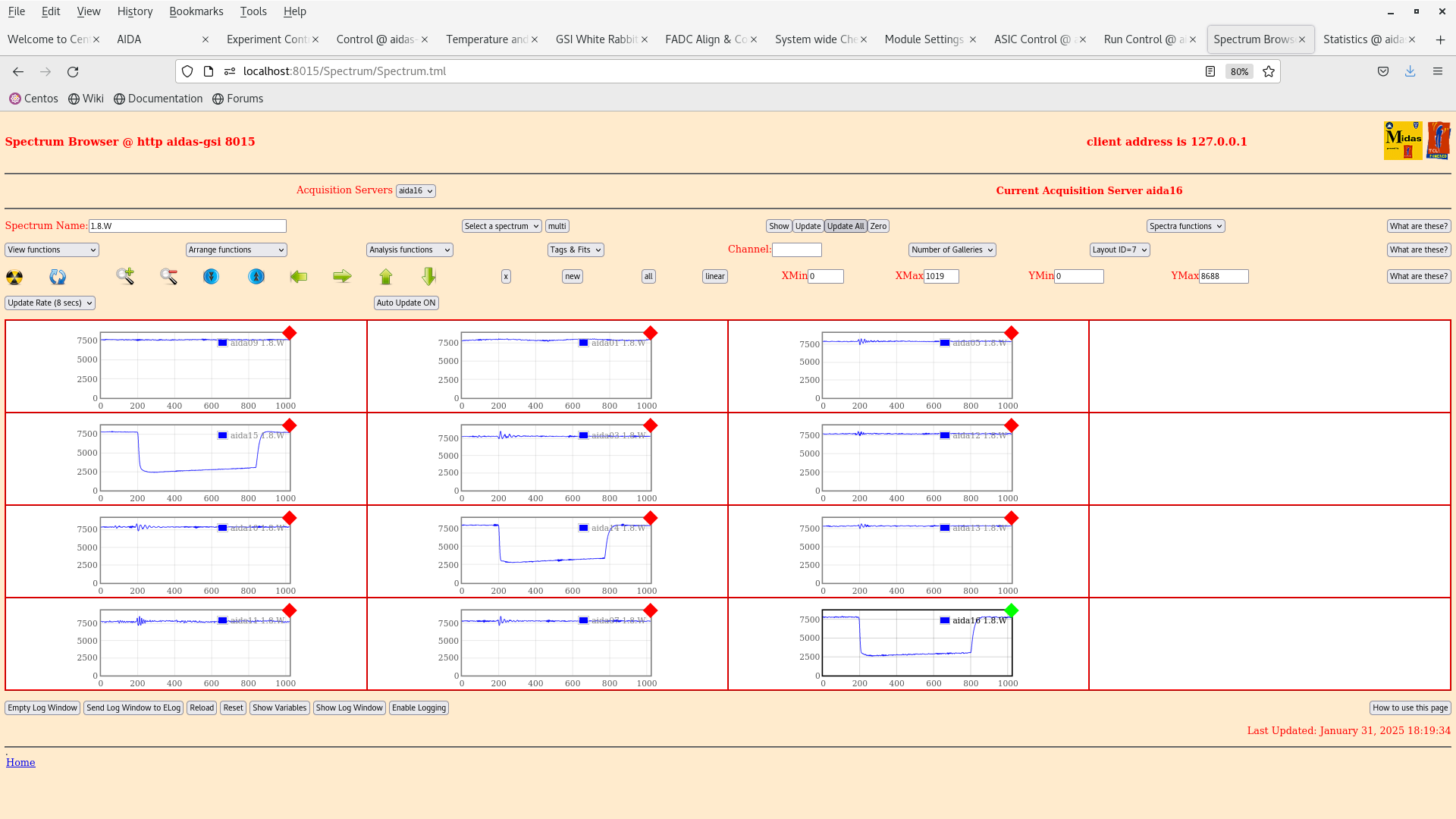

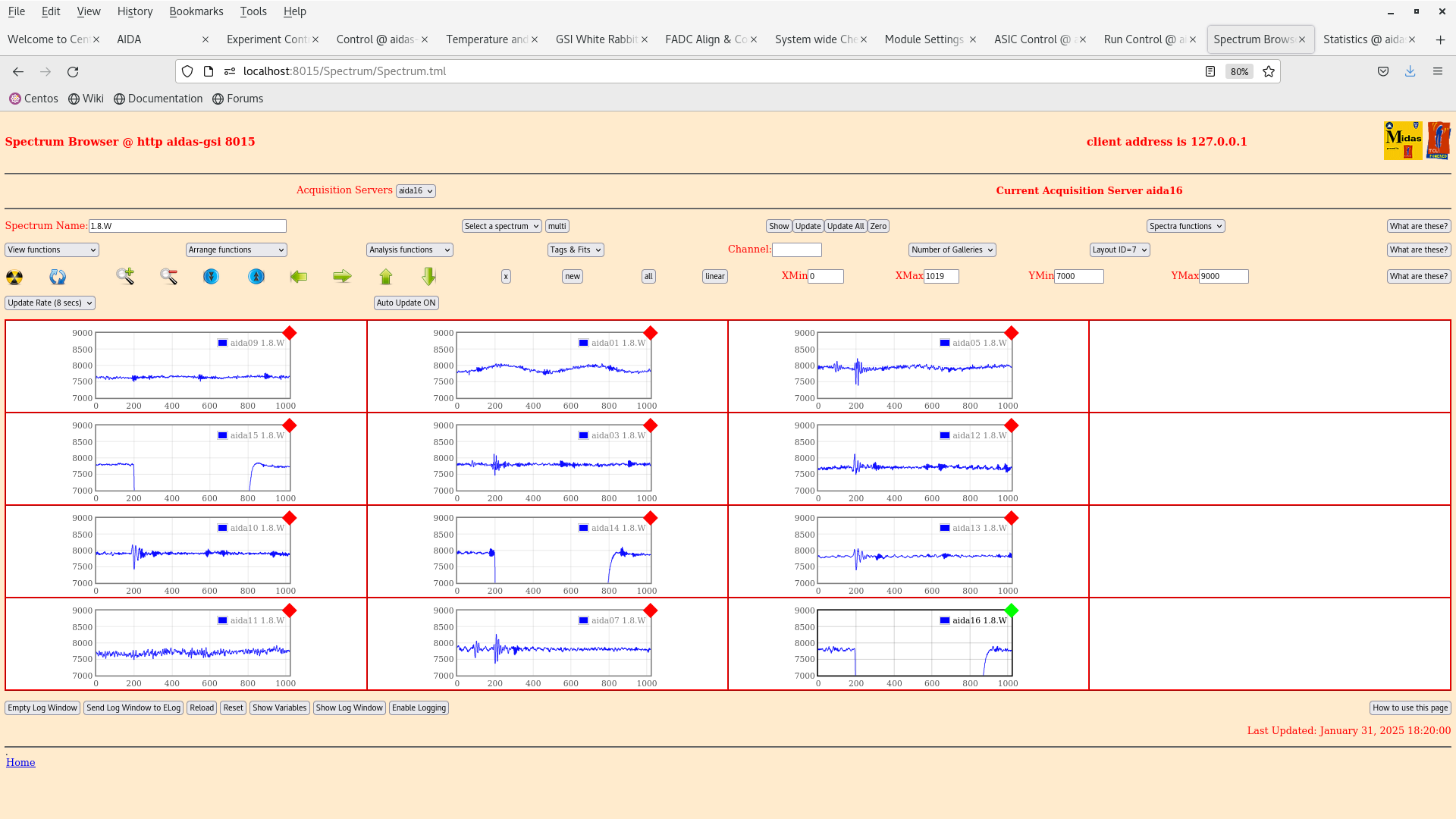

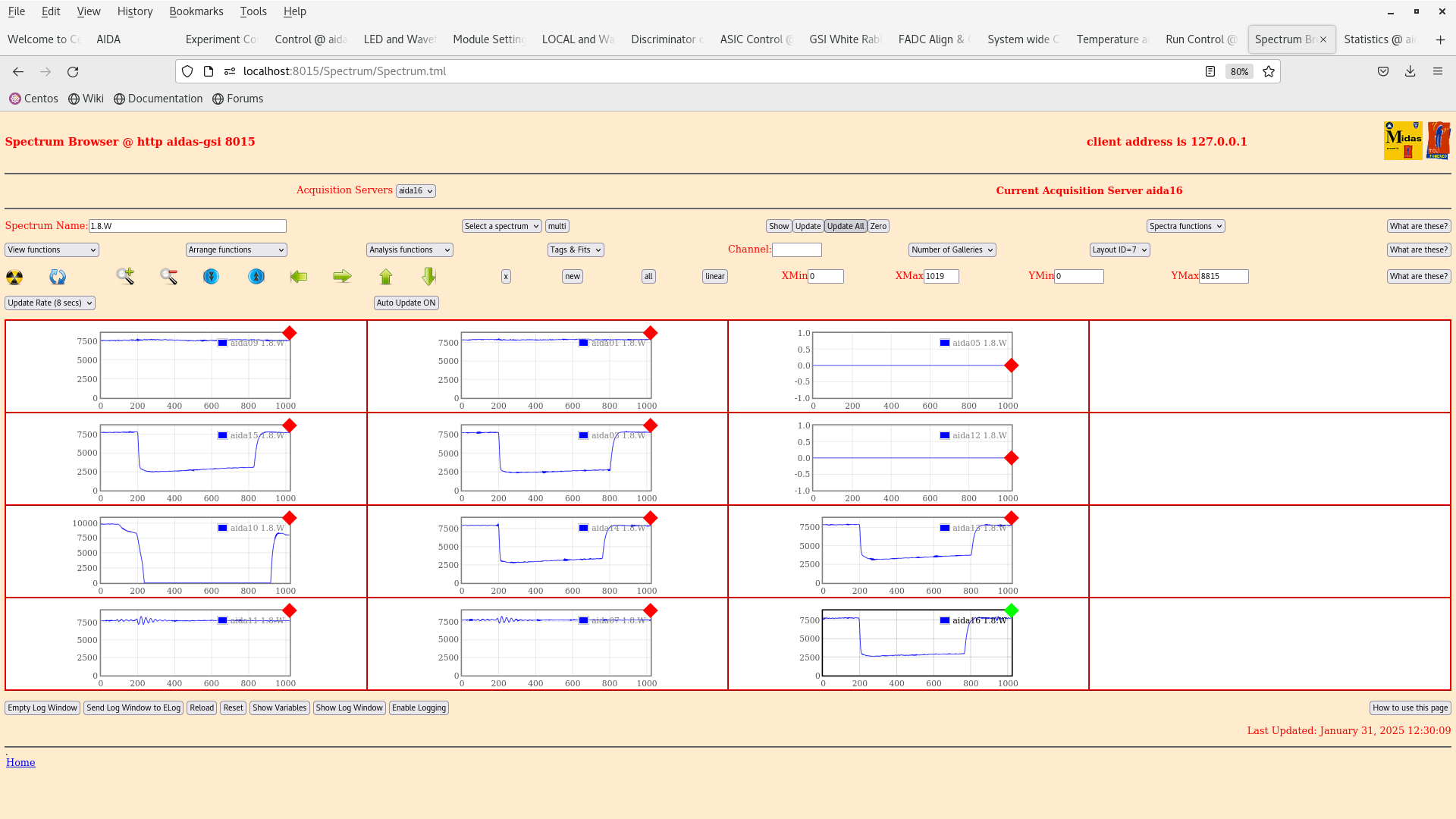

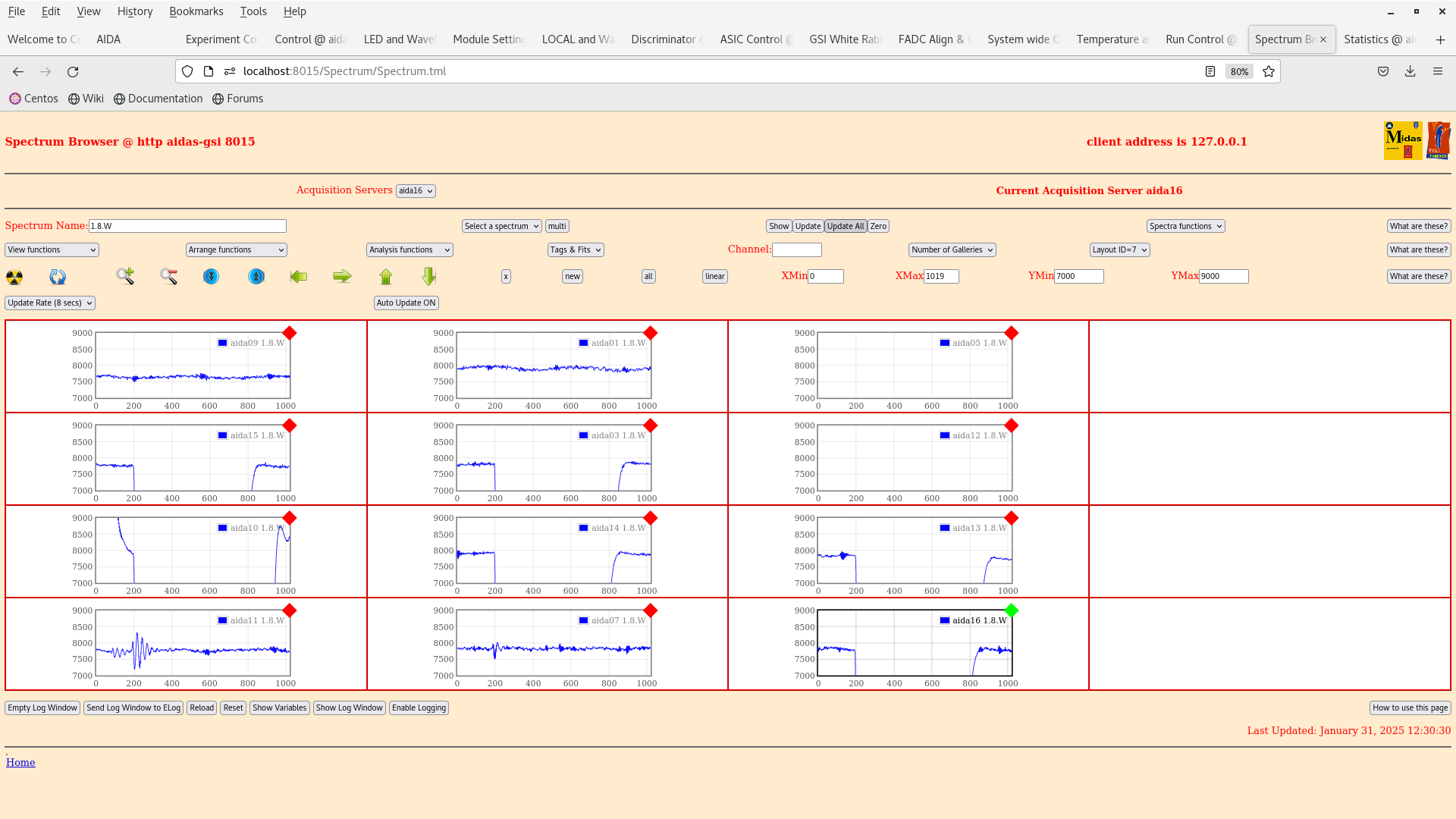

per FEE64 1.8.W spectra - 20us FSR - attachments 3-5

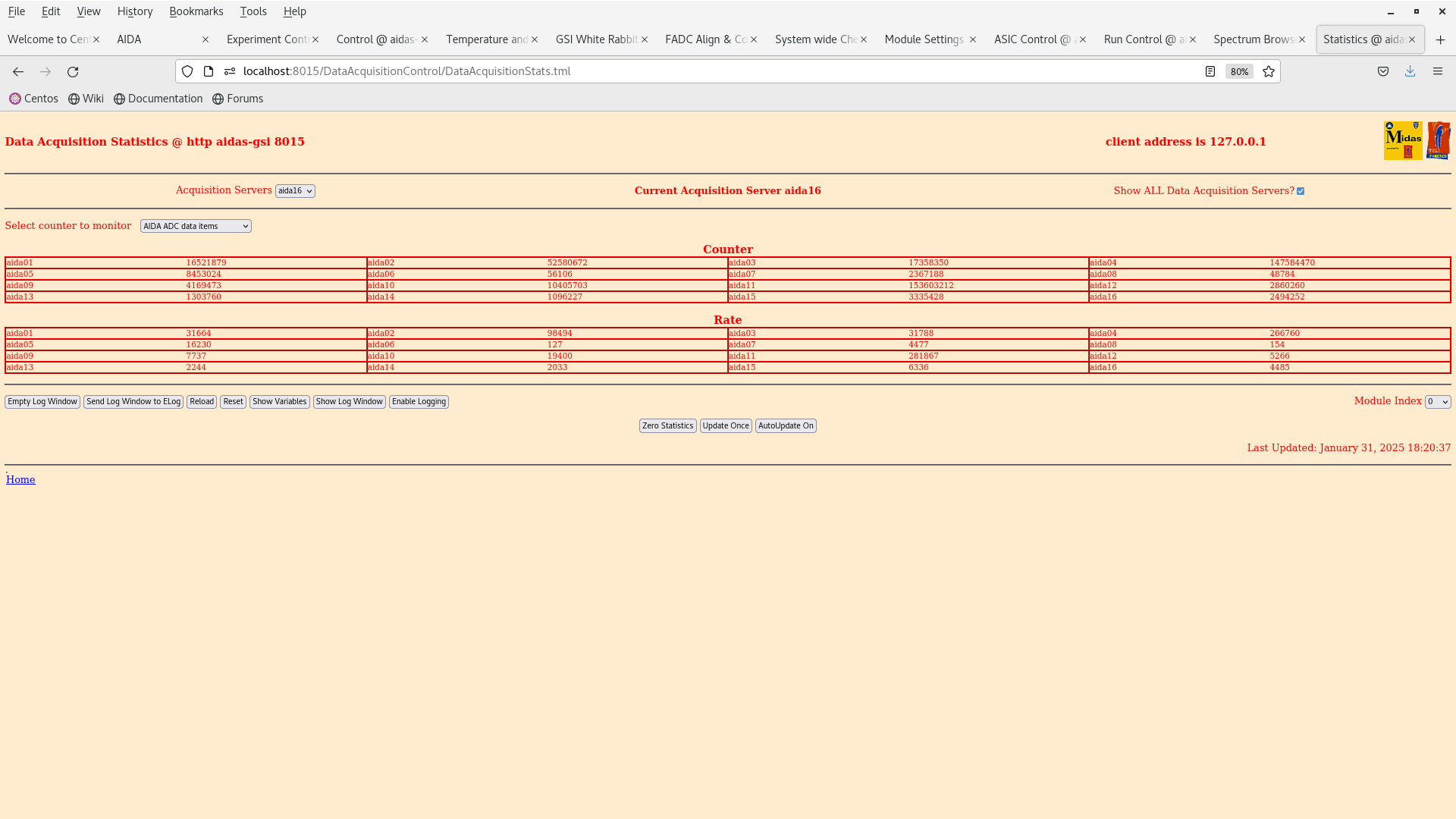

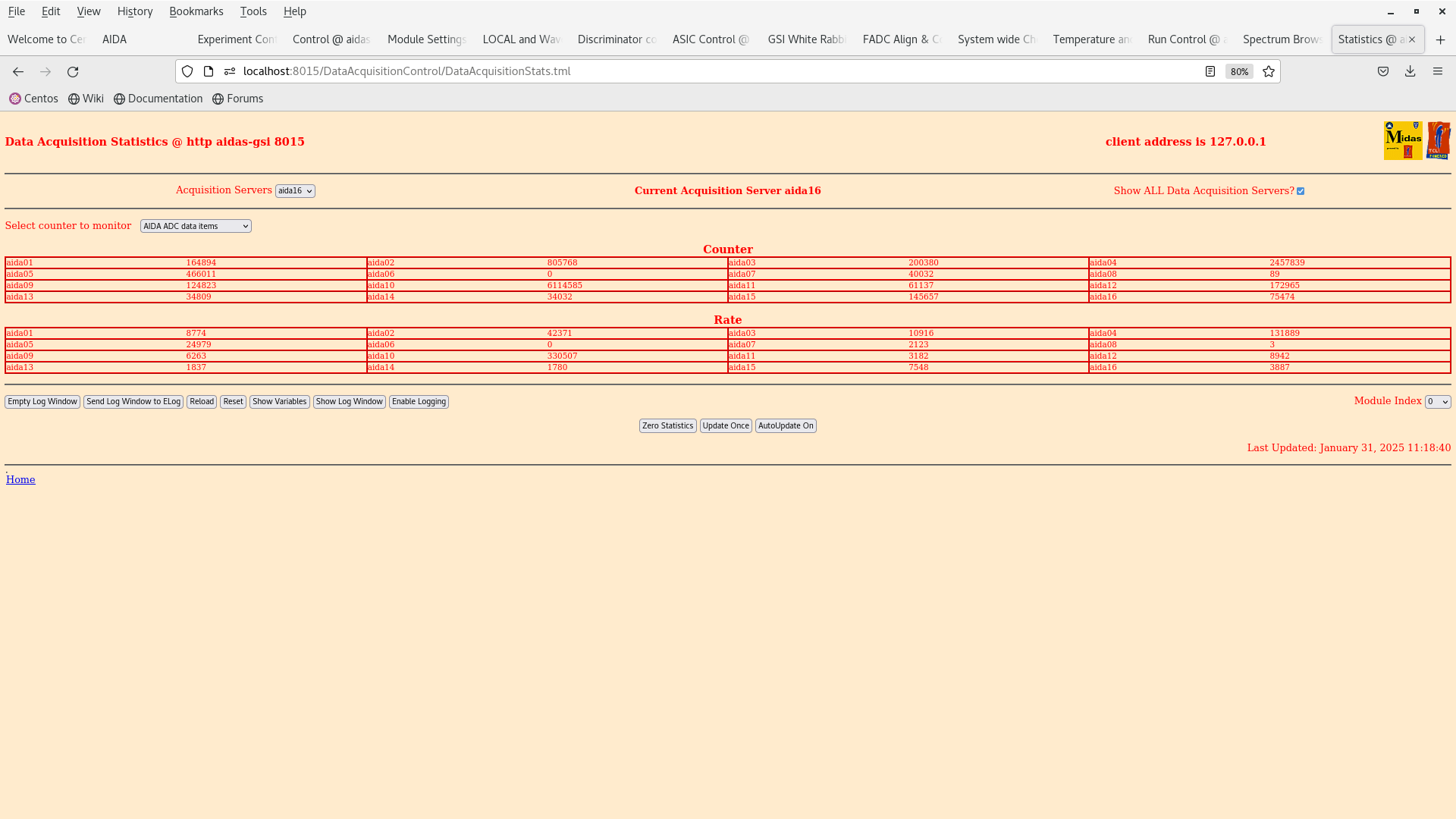

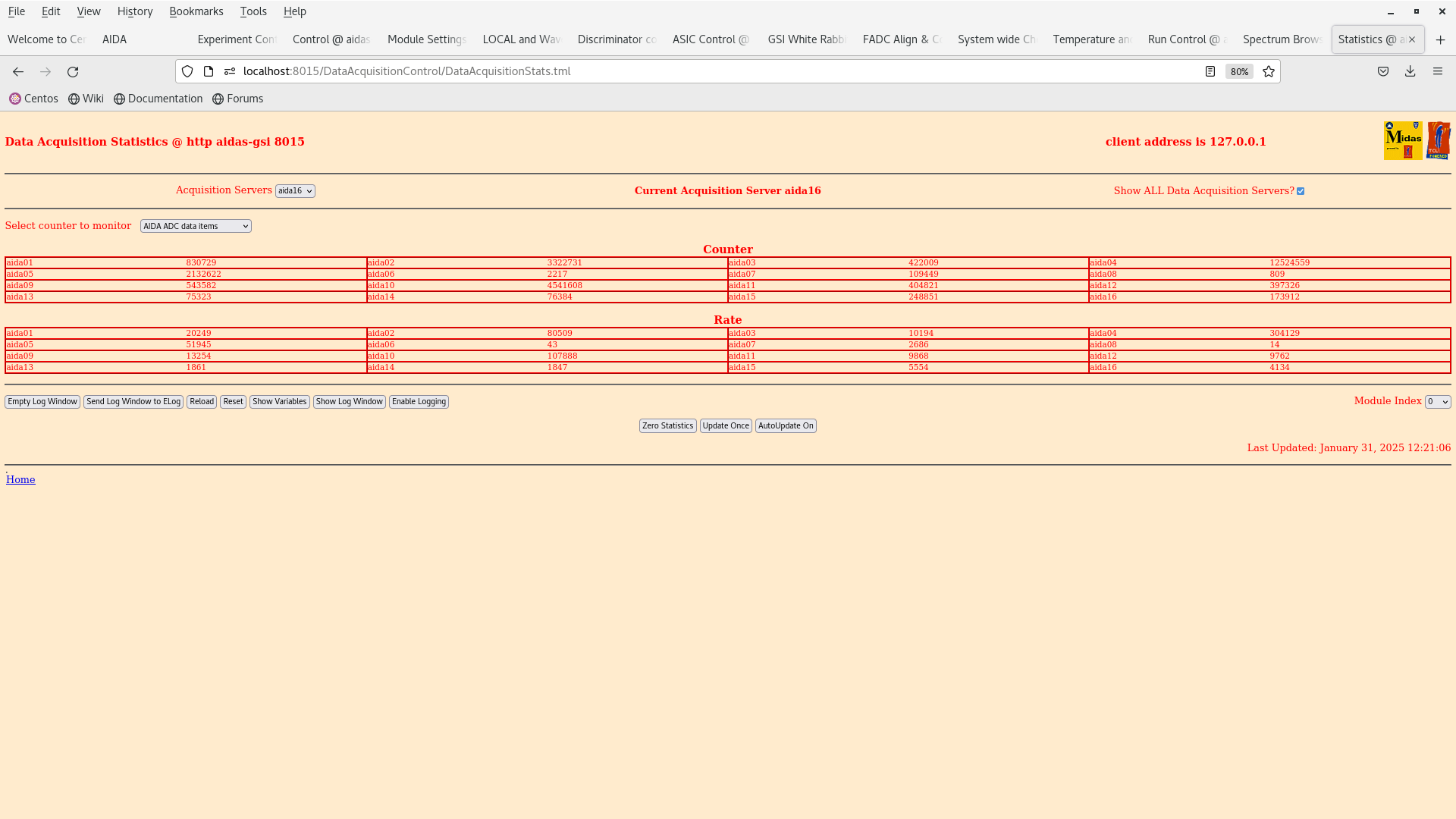

ADC data item stats - attachment 6

aida01 aida03 30k, all other BB18 p+n FEE64s < 20k, n+n FEE64s 100/270k

BB7 aida10 19k

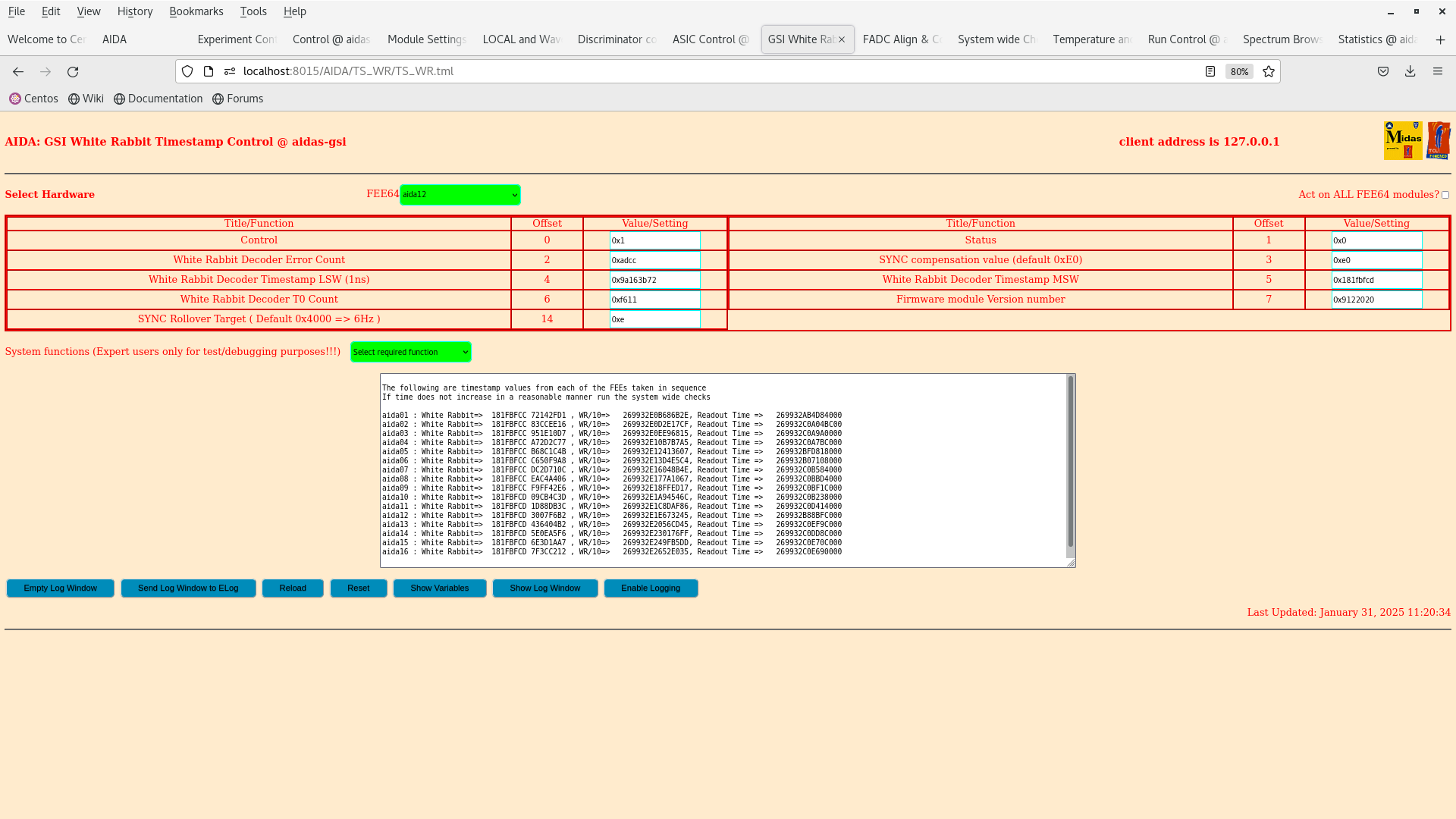

WR timestamps OK - attachment 7

Merger, TapeSever etc - attachments 8-9

disk directpry /TapeData/FEB25

working OK

DSSSD bias & leakage current OK - attachment 10

System wide checks OK - attachment 11-15

note global clock status 6 errors reported earlier today have now gone

FEE64 temperatures OK - attachment 16

18.38 Transition to safe state

DAQ STOP

disable data transfer 1

detector bias OFF

FEE64 power OFF

Can restart as follows

1) FEE64 power ON

2) DAQ RESET

3) DAQ SETUP

4) Enable histogramming

5) Enable waveforms

6) Detector bias ON

7) Restore ASIC settings

8) ASIC Control

9) FEE64 temperatures

10) System wide checks

sync ASIC clocks

11) FADC control - calibrate ADCS for *all* FEE64s

12) System wide checks contd.

13) DAQ GO

14) Check ADC data item stats

15) Check WR timestamps

If all OK can re-connect to Merger/TapeServer as follows

1) DAQ STOP

2) enable data transfer 1

3) DAQ GO

Can disconnect from Merger/TapeServer as follows

1) DAQ STOP

2) disable data transfer 1

|

| Attachment 1: Screenshot_from_2025-01-31_18-18-17.png

|

|

| Attachment 2: Screenshot_from_2025-01-31_18-19-19.png

|

|

| Attachment 3: Screenshot_from_2025-01-31_18-19-37.png

|

|

| Attachment 4: Screenshot_from_2025-01-31_18-20-04.png

|

|

| Attachment 5: Screenshot_from_2025-01-31_18-20-30.png

|

|

| Attachment 6: Screenshot_from_2025-01-31_18-20-42.png

|

|

| Attachment 7: Screenshot_from_2025-01-31_18-21-01.png

|

|

| Attachment 8: Screenshot_from_2025-01-31_18-25-58.png

|

|

| Attachment 9: Screenshot_from_2025-01-31_18-26-13.png

|

|

| Attachment 10: Screenshot_from_2025-01-31_18-29-38.png

|

|

| Attachment 11: Screenshot_from_2025-01-31_18-29-52.png

|

|

| Attachment 12: Screenshot_from_2025-01-31_18-29-58.png

|

|

| Attachment 13: Screenshot_from_2025-01-31_18-30-06.png

|

|

| Attachment 14: Screenshot_from_2025-01-31_18-30-12.png

|

|

| Attachment 15: Screenshot_from_2025-01-31_18-30-30.png

|

|

| Attachment 16: Screenshot_from_2025-01-31_18-30-48.png

|

|

|

|

695

|

Fri Jan 31 09:37:47 2025 |

CC, TD, MP | Friday 31 January |

Implantation stack mounted - BB18(DS)-1000 + bPlas + bPlas + 3x BB7(DS)-1000

N.B. aida02, aida09 & aida15 have grounded copper screen (3M 1245 - aluminimum braid to copper screen of ribbon cables) for Kapton PCBs connecting the Samtec ribbon cables to the BB18 DSSSD.

n+n FEE64s aida02, aida04, aida06 and aida08 LK1 fitted

p+n FEE64s aida03 and aida07 LK3 fitted

BB7 aida10 (asics #1-2 p+n, #3-4 n+n)

BB18 p+n FEE64s 9-15, 1-3, 5-12 - n+n FEE64s 2-4 (L-R looking downstream)

10.30 FEE64 power ON

DSSSD bias ON (BB18 only) - attachment 1

leakage current OK

ASIC settings 2024Dec13-17.02.45 restored

p+n FEE64 slow comparator 0xa, n+n FEE64 slow comparator 0xf

Attachments 2-7 WR timestamp aida05 & aida12, system wide check

aida12 & aida05 global clock status 6 - to be checked - OK for initial tests without merger

WR decoder status aida02

per FEE64 Rate spectra - attachment 8

aida10 high rate - BB7 not biased

rates OK for p+n FEE64s, rates high for n+n FEE64s - to be checked

BNC PB-5 pulser ON to p+n FEE64s - no obvious adaptor PCB misalignments

ADC data item stats - attachment 9

rates generally OK

aida10 high - BB7 not biased

aida02 & aida04 n+n FEE64s - rates high - to be checked when bPlas install complete

all p+n FEE64s connected to BB18 <10K except aida05 25k - very good!

BNC PB-5 settings - attachment 10

WR timestamps OK - attachment 11

FEE64 temperatures OK - attachment 12

12.15 bPlas driver PCB installed, bPlas cabling and grounds *not* connected yet

ADC data item stats - attachment 13

all rates higher cf. attachment 9

per FEE64 Rate spectra - attachment 14

per p+n FEE64 1.8.L spectra - attachment 15

aida09 pulser peak width 69 ch FWHM = 49keV FWHM

aida14 pulser peak width 50 ch FWHM = 35keV FWHM

per p+n FEE64 1.8.W spectra - 20us FSR - attachments 16-17

per n+n FEE64 1.8W spectra - 20us FSR - attachment 18

DSSSD bias & leakage current OK - attachment 19

ambient temperature +21.6 deg C, d.p. +0.4 deg C, RH 24.4%

FEE64 temperatures OK - attachment 20

DSSSD bias volatge & leakage current OK - attachment 21

CAEN N1419ET ch#0 BB18, ch#1 BB7

Install of bPlas drivers, cabling, grounds complete

ADC data item stats - attachment 22

per FEE64 Rate spectra - attachment 23

all BB18 p+n FEE64s *except* aida05 show very low rates of noise

per p+n FEE64 1.8.L spectra - attachment 24

aida09 pulser peak width 62 ch FWHM = 42keV FWHM

BB18 p+n FEE64s better electronic noise cf. p+n FEE64s not connected to a DSSSD

per FEE64 1.8.W spectra - 20us FSR - attachments 25-26 |

| Attachment 1: Screenshot_from_2025-01-31_10-39-16.png

|

|

| Attachment 2: Screenshot_from_2025-01-31_10-58-48.png

|

|

| Attachment 3: Screenshot_from_2025-01-31_10-58-59.png

|

|

| Attachment 4: Screenshot_from_2025-01-31_10-59-11.png

|

|

| Attachment 5: Screenshot_from_2025-01-31_10-59-11.png

|

|

| Attachment 6: Screenshot_from_2025-01-31_10-59-52.png

|

|

| Attachment 7: Screenshot_from_2025-01-31_11-00-02.png

|

|

| Attachment 8: Screenshot_from_2025-01-31_11-17-59.png

|

|

| Attachment 9: Screenshot_from_2025-01-31_11-18-43.png

|

|

| Attachment 10: Screenshot_from_2025-01-31_11-18-50.png

|

|

| Attachment 11: Screenshot_from_2025-01-31_11-21-05.png

|

|

| Attachment 12: Screenshot_from_2025-01-31_11-21-29.png

|

|

| Attachment 13: Screenshot_from_2025-01-31_12-21-09.png

|

|

| Attachment 14: Screenshot_from_2025-01-31_12-21-55.png

|

|

| Attachment 15: Screenshot_from_2025-01-31_12-26-26.png

|

|

| Attachment 16: Screenshot_from_2025-01-31_12-30-13.png

|

|

| Attachment 17: Screenshot_from_2025-01-31_12-30-34.png

|

|

| Attachment 18: Screenshot_from_2025-01-31_12-31-25.png

|

|

| Attachment 19: Screenshot_from_2025-01-31_12-41-33.png

|

|

| Attachment 20: Screenshot_from_2025-01-31_12-42-08.png

|

|

| Attachment 21: Screenshot_from_2025-01-31_15-59-26.png

|

|

| Attachment 22: Screenshot_from_2025-01-31_16-07-21.png

|

|

| Attachment 23: Screenshot_from_2025-01-31_16-07-31.png

|

|

| Attachment 24: Screenshot_from_2025-01-31_16-08-39.png

|

|

| Attachment 25: Screenshot_from_2025-01-31_16-10-48.png

|

|

| Attachment 26: Screenshot_from_2025-01-31_16-11-30.png

|

|

|

|

288

|

Fri Apr 30 08:38:12 2021 |

TD | Friday 30 April |

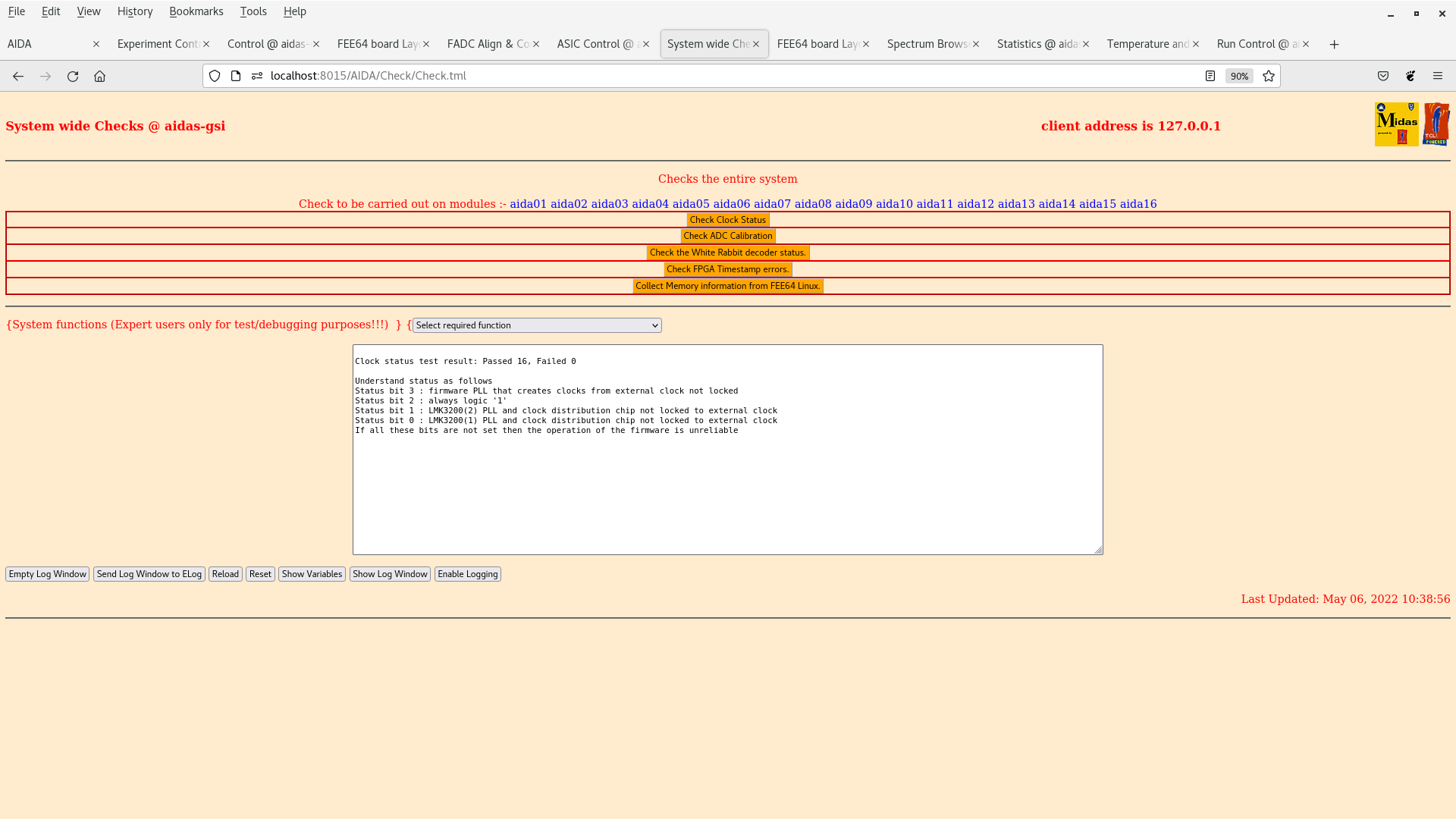

09.40 All system wide checks OK *except*

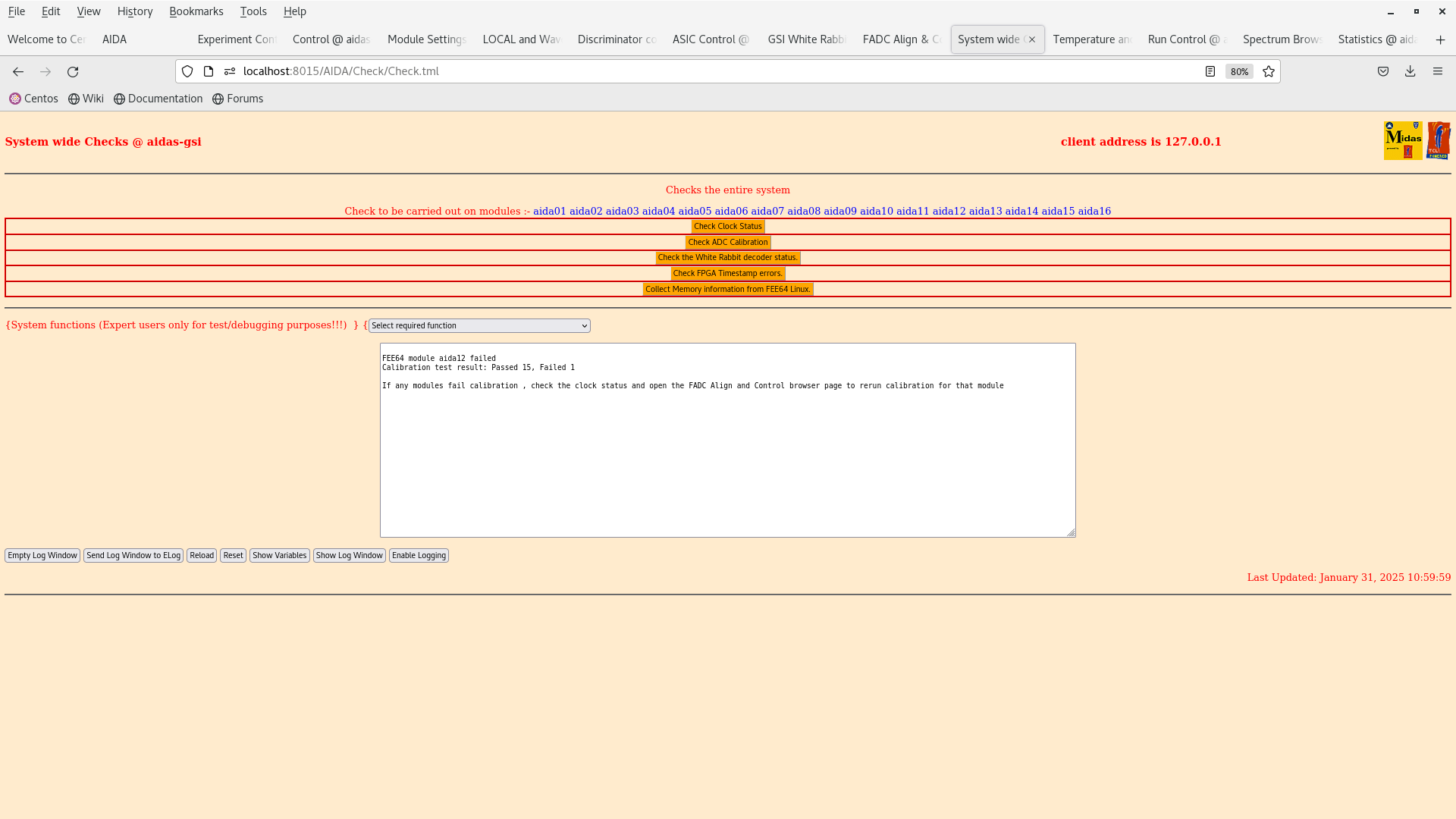

FEE64 module aida07 failed

Calibration test result: Passed 15, Failed 1

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

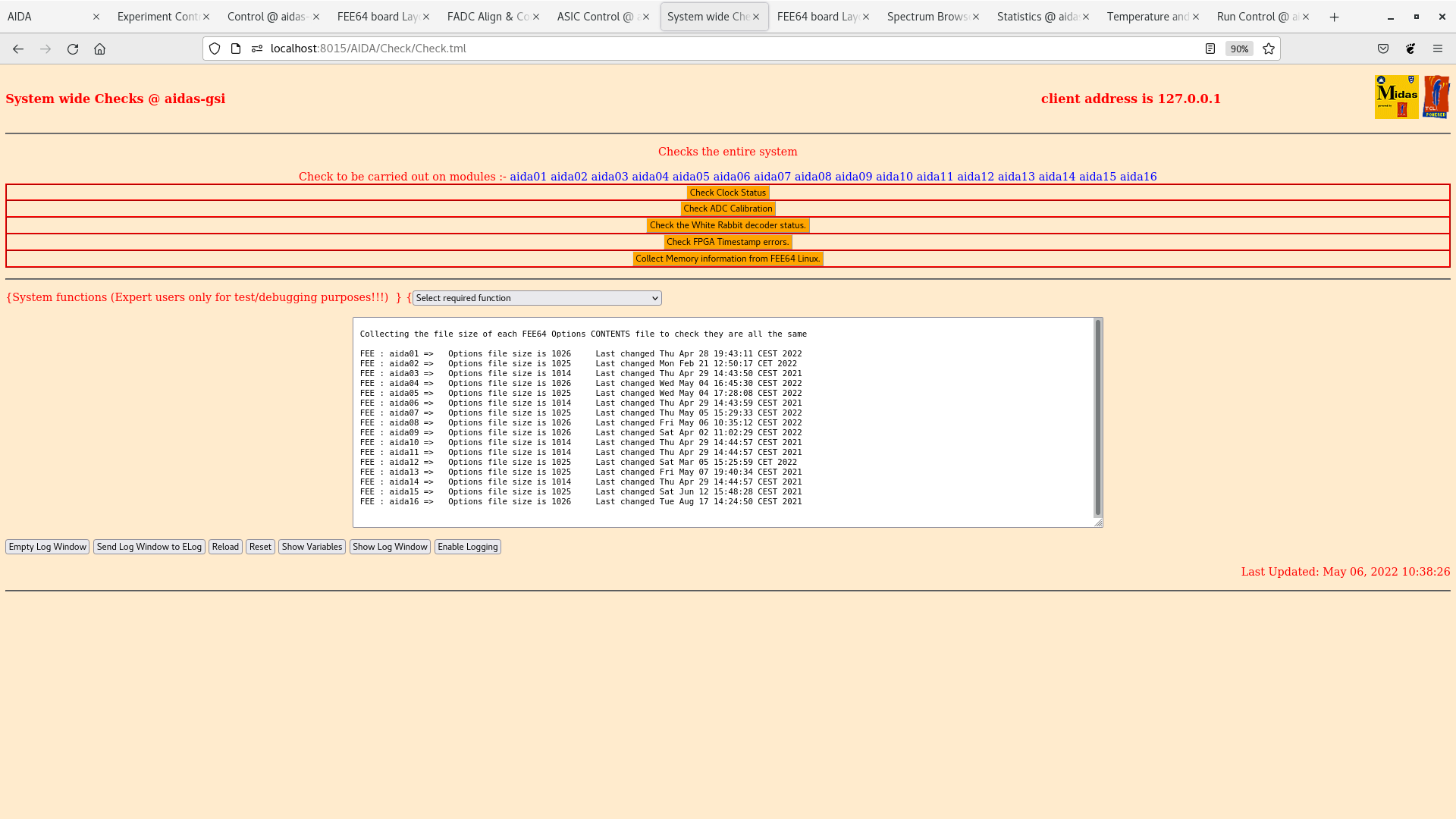

Collecting the file size of each FEE64 Options CONTENTS file to check they are all the same

FEE : aida01 => Options file size is 1025 Last changed Thu Apr 29 17:50:06 CEST 2021

FEE : aida02 => Options file size is 1014 Last changed Thu Apr 29 14:43:46 CEST 2021

FEE : aida03 => Options file size is 1014 Last changed Thu Apr 29 14:43:50 CEST 2021

FEE : aida04 => Options file size is 1014 Last changed Thu Apr 29 14:43:53 CEST 2021

FEE : aida05 => Options file size is 1014 Last changed Thu Apr 29 14:43:55 CEST 2021

FEE : aida06 => Options file size is 1014 Last changed Thu Apr 29 14:43:59 CEST 2021

FEE : aida07 => Options file size is 1014 Last changed Thu Apr 29 14:44:02 CEST 2021

FEE : aida08 => Options file size is 1014 Last changed Thu Apr 29 14:44:05 CEST 2021

FEE : aida09 => Options file size is 1014 Last changed Thu Apr 29 14:44:08 CEST 2021

FEE : aida10 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida11 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida12 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida13 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida14 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida15 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida16 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

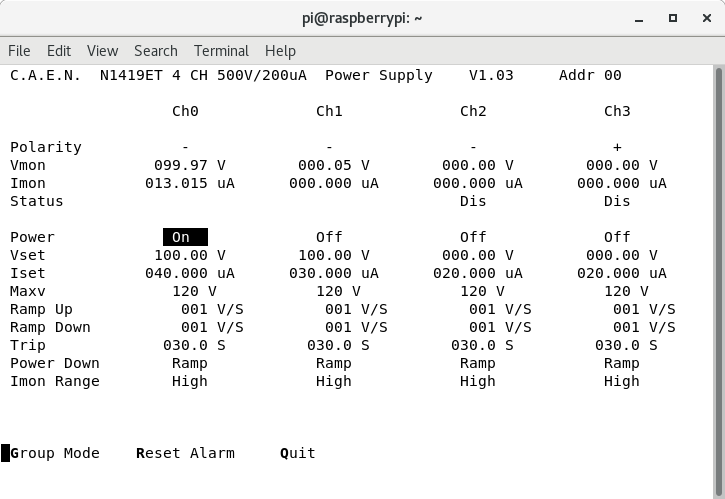

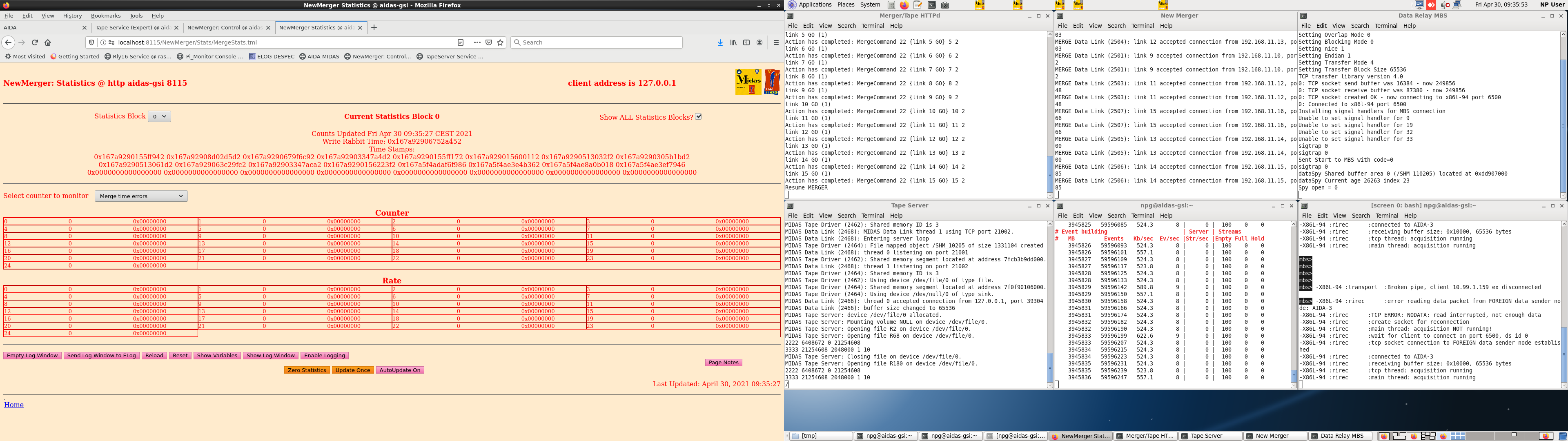

09.44 DSSSD bias & leakage currents Ok - attachment 1

Merger time seq errors - attachment 2

no merger errors since restart yesterday

FEE64 temps OK - attachment 3

good event stats - attachment 4

Merger/Tape Server server consoles - attachment 5

Grafana DSSSD bias |& leakage currents for previous 7 days - attachment 6

DAQ continues OK - no data storage |

| Attachment 1: 310.png

|

|

| Attachment 2: 311.png

|

|

| Attachment 3: Screenshot_2021-04-30_Temperature_and_status_scan_aidas-gsi.png

|

|

| Attachment 4: Screenshot_2021-04-30_Statistics_aidas-gsi.png

|

|

| Attachment 5: Screenshot_2021-04-30_NewMerger_Statistics_aidas-gsi.png

|

|

| Attachment 6: Screenshot_2021-04-30_AIDA_Alerting_-_Grafana.png

|

|

|

|

626

|

Thu May 2 23:08:43 2024 |

TD | Friday 3 May |

00.05 FEE64 temperatures OK

ADC data item stats OK

09.31 FEE64 temperatures OK

ADC data item stats OK

13.15 FEE64 temperatures OK

ADC data item stats OK

9/16 <20k max aida16 164k

20.15 FEE64 temperatures OK

ADC data item stats

aida02 & aida03 no data - DAQ reset

9/16 <20k max aida16 158k

23.15 FEE64 temperatures OK

ADC data item stats

aida03 no data - DAQ reset

10/16 <20k max aida16 153k |

|

|

39

|

Mon Apr 1 10:14:09 2019 |

CA, NH, TD | Friday 29th March 2019 |

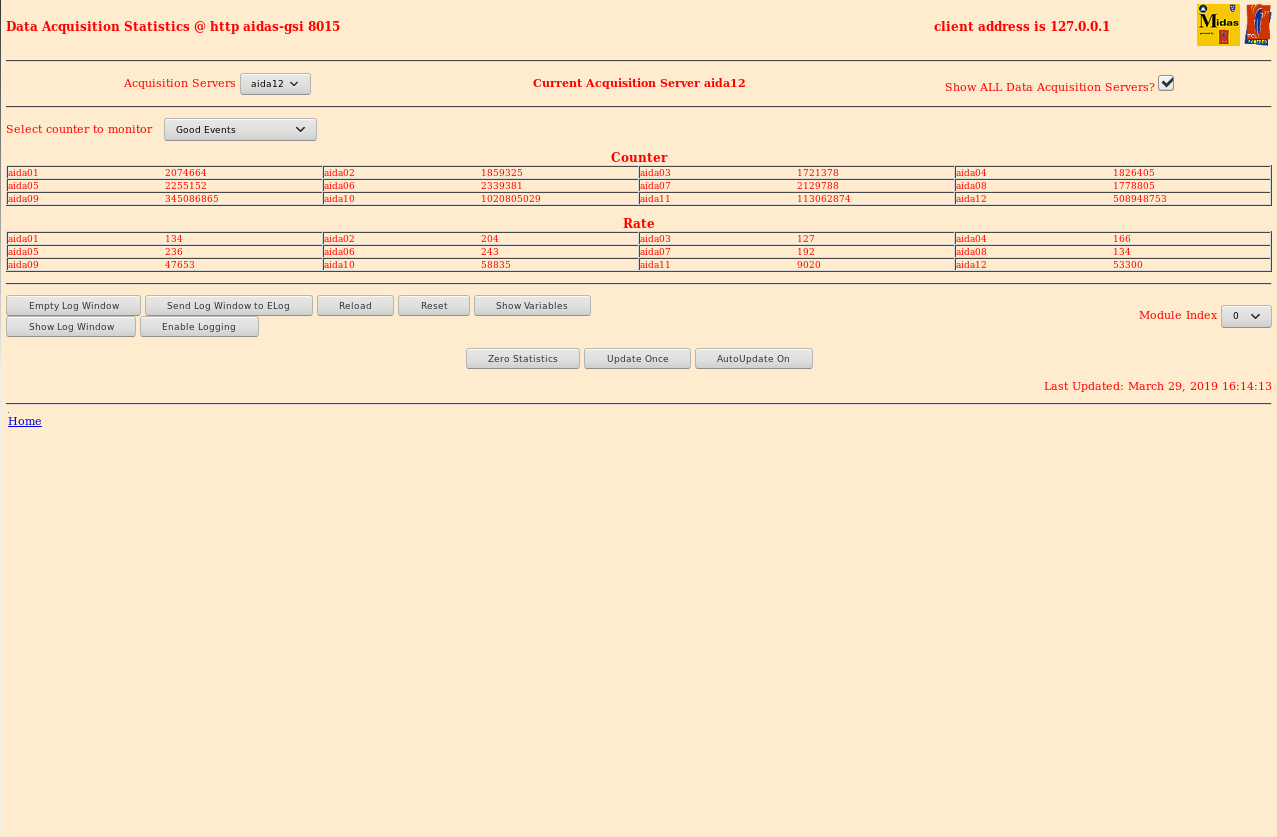

16:30 good event statistics ok, with 9,10,11,12 running faster (detector FEE64s) (attachment 1)

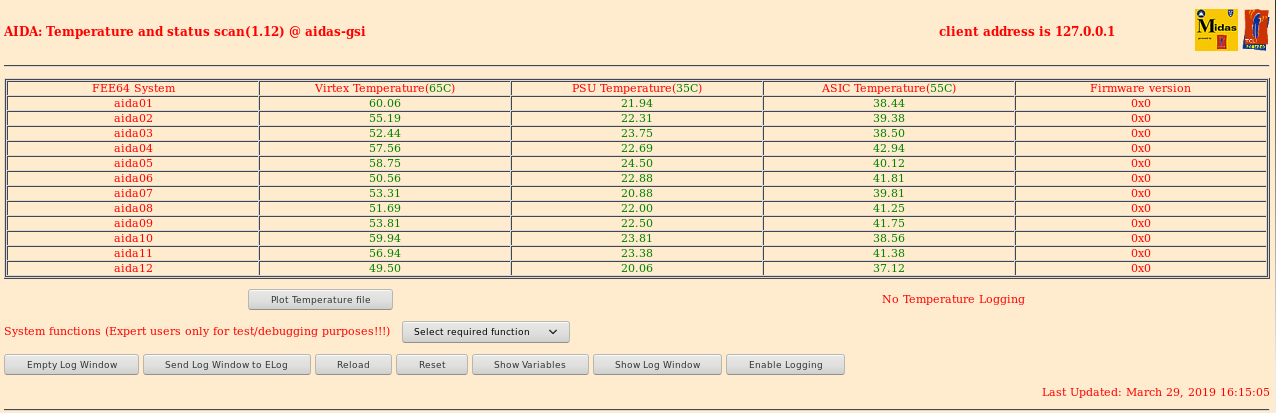

FEE temperatures ok (attachment 2)

detector bias/leakage currents ok (attachment 3)

system wide checks ok *except* FEE64 Linux memory information check causes script error,

WR decoder status returns errors

DAQ & Merger running ok

slow comparator threshold raised to 0x64

|

| Attachment 1: 290319_stats.png

|

|

| Attachment 2: 290319_temp.png

|

|

| Attachment 3: 290913_bias.png

|

|

|

|

350

|

Fri May 28 10:29:07 2021 |

TD | Friday 28 May |

11.30 DAQ continues - file S496/R18_472

alpha background

All system wide checks OK *except*

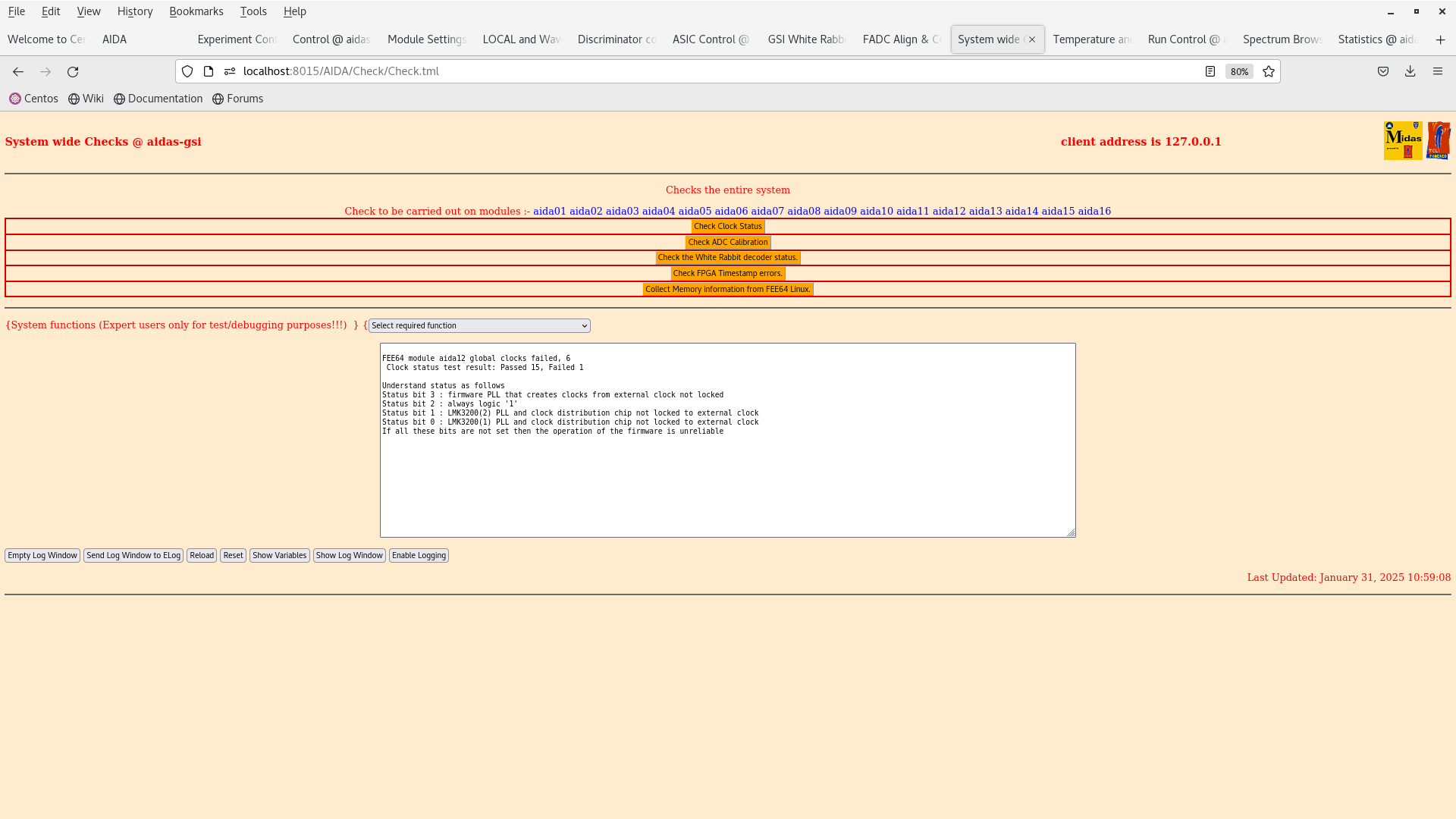

FEE64 module aida06 global clocks failed, 6

Clock status test result: Passed 15, Failed 1

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

Base Current Difference

aida01 fault 0x82b0 : 0x82b2 : 2

aida02 fault 0xfe72 : 0xfe74 : 2

aida03 fault 0x97f4 : 0x97f6 : 2

aida04 fault 0x950 : 0x952 : 2

aida05 fault 0x8e93 : 0x8e95 : 2

aida06 fault 0x545a : 0x545c : 2

aida07 fault 0xc04d : 0xc04f : 2

aida08 fault 0xa0f7 : 0xa0f9 : 2

White Rabbit error counter test result: Passed 8, Failed 8

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

Returned 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 1 4 7 1 3 2 2 2 2 4 6 : 36980

aida02 : 3 1 5 1 2 4 3 3 2 4 6 : 37892

aida03 : 8 8 6 6 3 3 2 3 3 3 6 : 36800

aida04 : 37 12 5 6 3 4 2 3 3 3 6 : 37060

aida05 : 11 5 6 4 2 2 2 2 2 4 6 : 37044

aida06 : 4 3 3 3 2 2 2 3 3 4 6 : 38456

aida07 : 1 12 3 2 0 3 3 2 2 4 6 : 37204

aida08 : 13 8 1 2 3 4 3 3 2 4 6 : 38020

aida09 : 7 7 5 1 1 3 2 2 2 4 6 : 36996

aida10 : 12 7 9 2 1 3 3 3 1 4 6 : 36856

aida11 : 2 9 3 1 2 3 3 3 1 4 6 : 36768

aida12 : 11 4 3 3 2 4 2 3 2 4 6 : 37724

aida13 : 10 8 6 2 2 3 2 2 2 4 6 : 37128

aida14 : 16 7 7 1 0 4 2 2 2 4 6 : 37128

aida15 : 12 6 2 2 1 3 3 4 2 4 6 : 38272

aida16 : 9 4 10 1 2 3 2 2 2 4 6 : 37124

Collecting the file size of each FEE64 Options CONTENTS file to check they are all the same

FEE : aida01 => Options file size is 1026 Last changed Sun May 23 12:04:25 CEST 2021

FEE : aida02 => Options file size is 1025 Last changed Sun May 23 00:19:21 CEST 2021

FEE : aida03 => Options file size is 1014 Last changed Thu Apr 29 14:43:50 CEST 2021

FEE : aida04 => Options file size is 1025 Last changed Fri May 14 16:54:56 CEST 2021

FEE : aida05 => Options file size is 1025 Last changed Mon May 17 06:25:41 CEST 2021

FEE : aida06 => Options file size is 1014 Last changed Thu Apr 29 14:43:59 CEST 2021

FEE : aida07 => Options file size is 1014 Last changed Thu Apr 29 14:44:02 CEST 2021

FEE : aida08 => Options file size is 1025 Last changed Sun May 23 00:16:54 CEST 2021

FEE : aida09 => Options file size is 1014 Last changed Thu Apr 29 14:44:08 CEST 2021

FEE : aida10 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida11 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida12 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida13 => Options file size is 1025 Last changed Fri May 07 19:40:34 CEST 2021

FEE : aida14 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida15 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

FEE : aida16 => Options file size is 1014 Last changed Thu Apr 29 14:44:57 CEST 2021

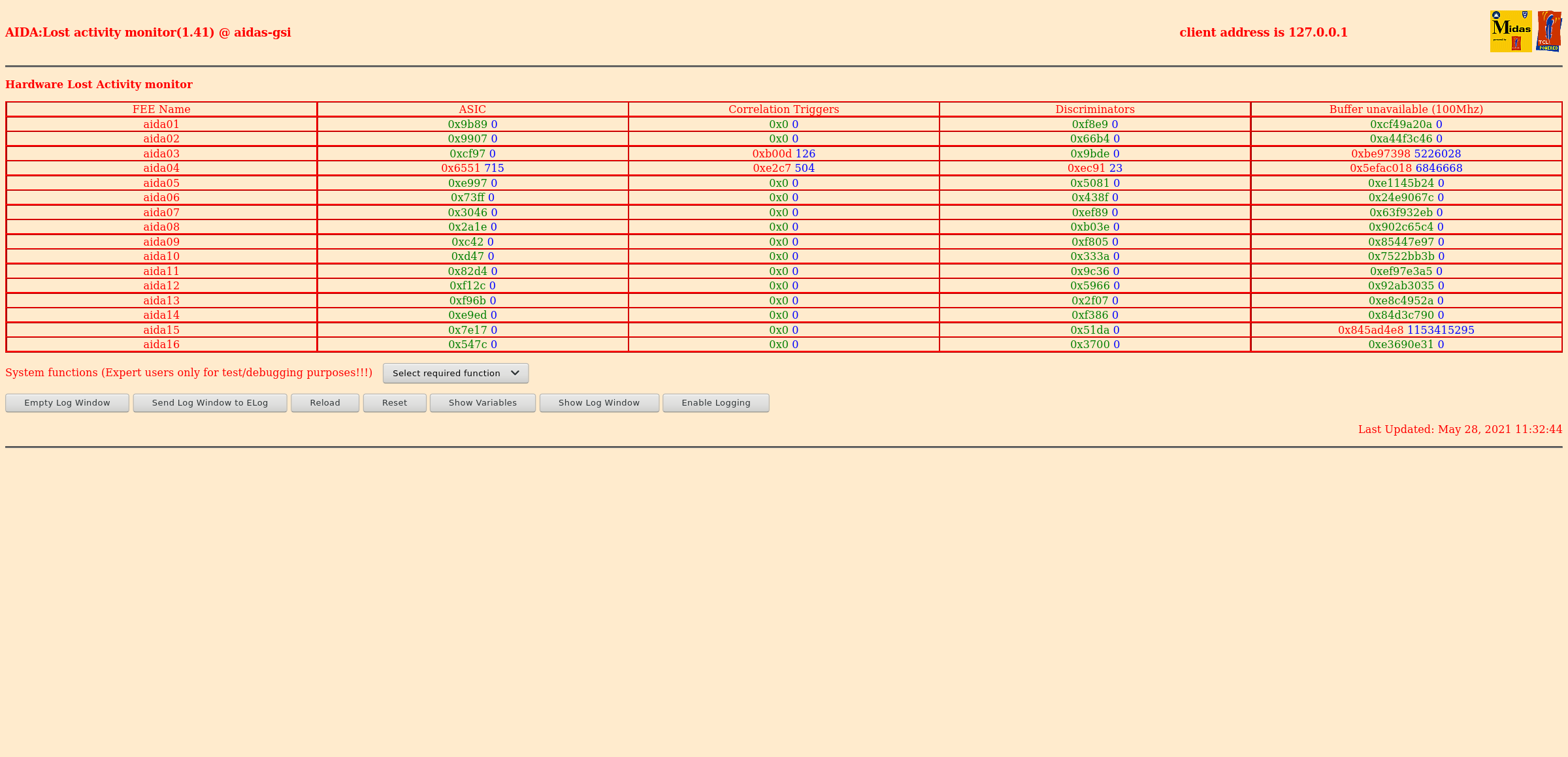

Grafana - DSSSD bias & leakage current - most recent 7 days - attachment 1

Lost activity monitor - attachment 2

1.8.W spectra - attachments 3 & 4

ADC data item stats - attachment 5

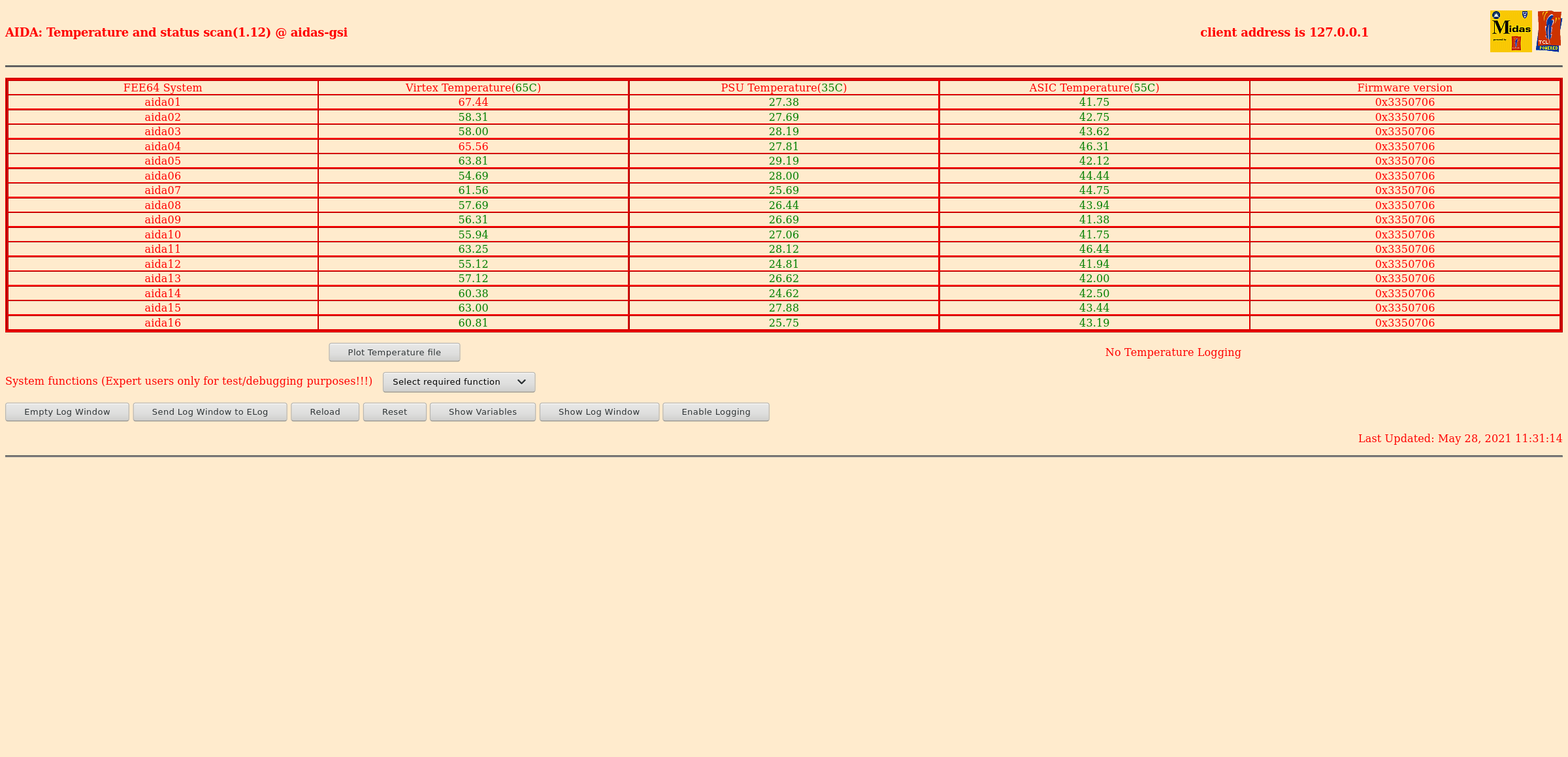

FEE64 temps OK - attachment 6

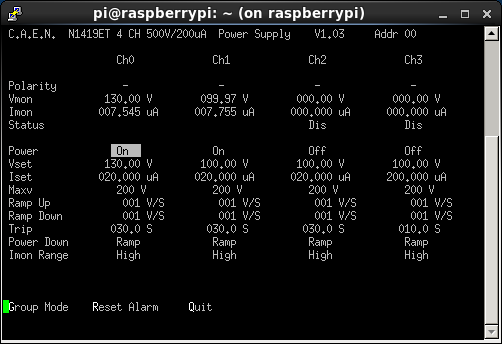

DSSSD bias & leakage current OK - attachment 7

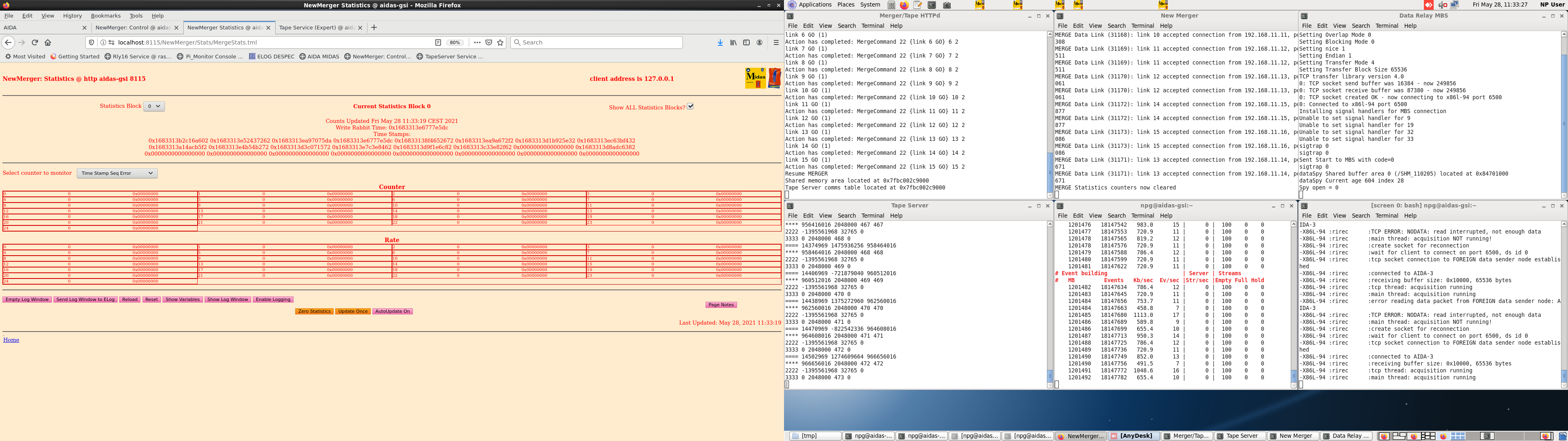

Merger/Tape Server/Merger stats - attachment 8

no merger errors reported since previous restart

14.30 analysis of file S496/R18_471 - attachment 9

max deadtime 0.18% aida04 |

| Attachment 1: Screenshot_2021-05-28_AIDA_Alerting_-_Grafana.png

|

|

| Attachment 2: Screenshot_2021-05-28_Lost_activity_monitor_aidas-gsi.png

|

|

| Attachment 3: Screenshot_2021-05-28_Spectrum_Browser_aidas-gsi(1).png

|

.png.png)

|

| Attachment 4: Screenshot_2021-05-28_Spectrum_Browser_aidas-gsi.png

|

|

| Attachment 5: Screenshot_2021-05-28_Statistics_aidas-gsi.png

|

|

| Attachment 6: Screenshot_2021-05-28_Temperature_and_status_scan_aidas-gsi.png

|

|

| Attachment 7: 940.png

|

|

| Attachment 8: 941.png

|

|

| Attachment 9: R18_471

|

*** TDR format 3.3.0 analyser - TD - May 2021

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 57407666 ( 20753.5 Hz)

Other data format: 204512336 ( 73933.4 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 116 ( 0.0 Hz)

RESUME: 116 ( 0.0 Hz)

SYNC100: 42303 ( 15.3 Hz)

WR48-63: 42303 ( 15.3 Hz)

FEE64 disc: 1160567 ( 419.6 Hz)

MBS info: 203266931 ( 73483.1 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 109 ( 0.0 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 2766.172 s

FEE elapsed dead time(s) elapsed idle time(s)

0 0.000 0.000

1 0.000 2700.364

2 0.332 0.000

3 4.856 0.000

4 0.000 0.000

5 0.000 1685.309

6 0.000 0.000

7 0.000 1567.327

8 0.000 0.000

9 0.000 0.000

10 0.000 0.000

11 0.000 0.000

12 0.000 0.000

13 0.000 0.000

14 0.000 0.000

15 0.000 0.000

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 181 23 0 0 0 0 0 0 23 0 0 13

1 838470 386 0 0 0 0 166 166 54 0 0 0

2 162 101753181 0 0 19 19 17931 17931 15 101717266 0 5

3 42392398 102752755 0 0 97 97 21331 21331 1160234 101549665 0 12

4 211 21 0 0 0 0 0 0 21 0 0 10

5 6478076 2740 0 0 0 0 1337 1337 66 0 0 0

6 260 17 0 0 0 0 0 0 17 0 0 4

7 7695649 3163 0 0 0 0 1537 1537 89 0 0 28

8 132 14 0 0 0 0 1 1 12 0 0 10

9 368 5 0 0 0 0 0 0 5 0 0 4

10 173 18 0 0 0 0 0 0 18 0 0 5

11 303 5 0 0 0 0 0 0 5 0 0 5

12 186 1 0 0 0 0 0 0 1 0 0 7

13 585 2 0 0 0 0 0 0 2 0 0 2

14 0 0 0 0 0 0 0 0 0 0 0 0

15 512 5 0 0 0 0 0 0 5 0 0 4

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time: 31.742s ( 1008.122 blocks/s, 63.008 Mb/s)

|

|

|

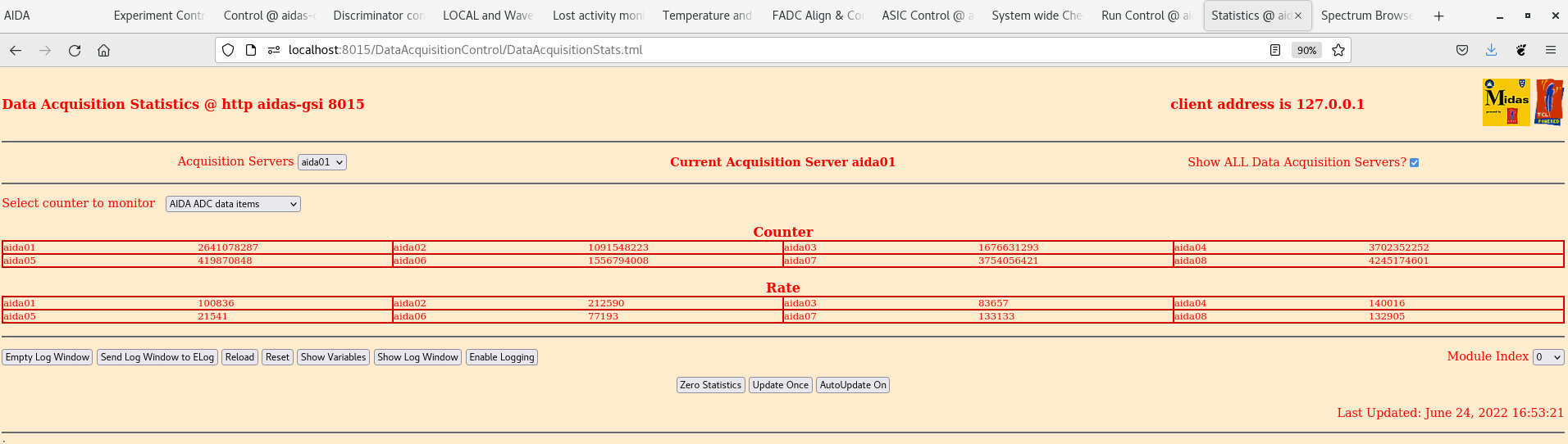

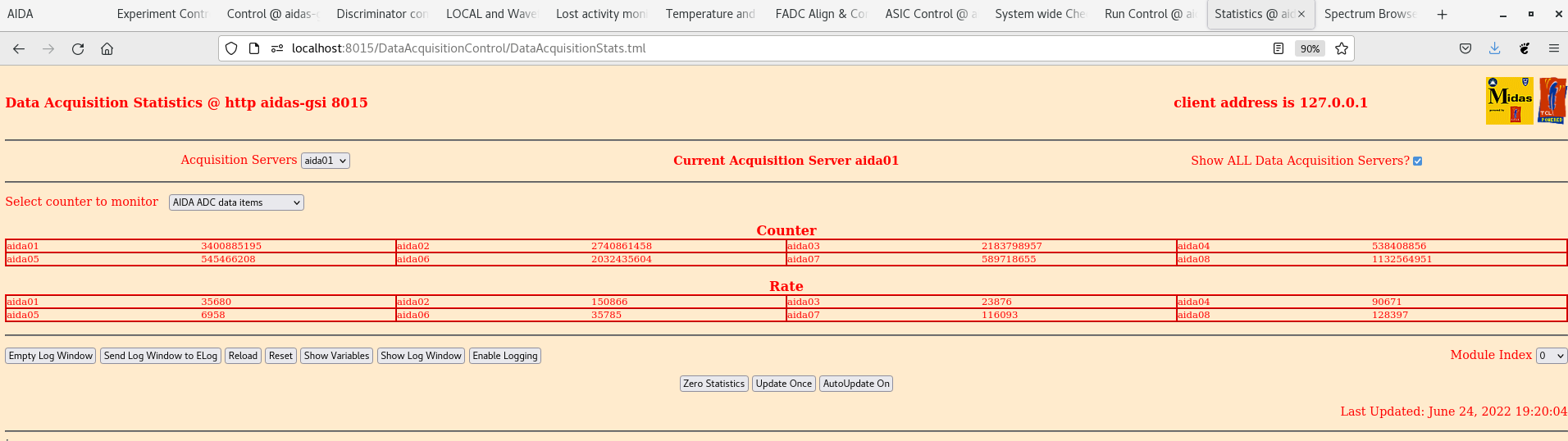

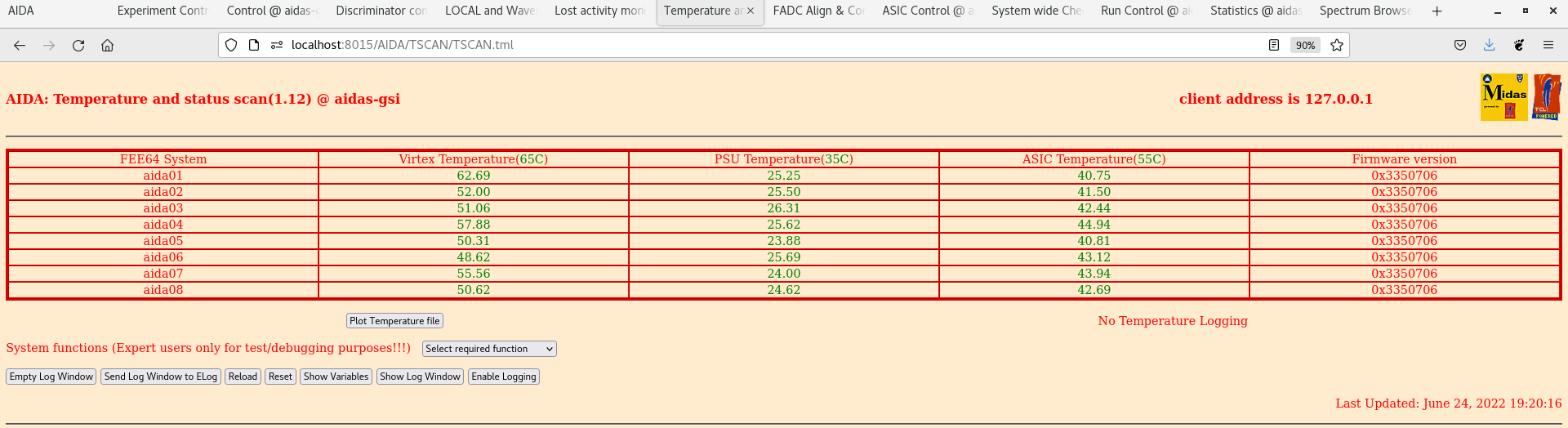

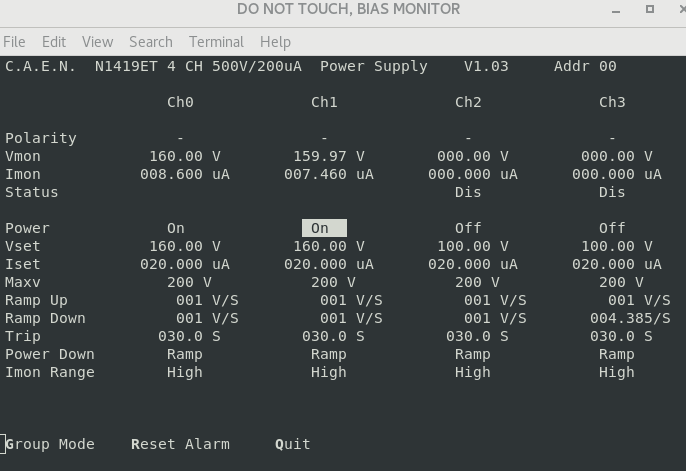

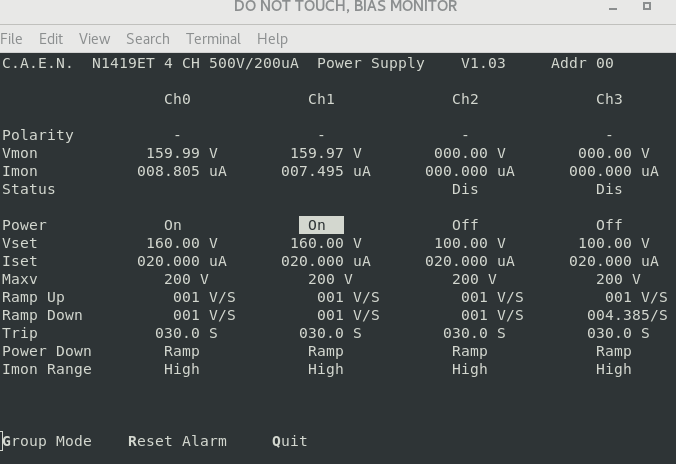

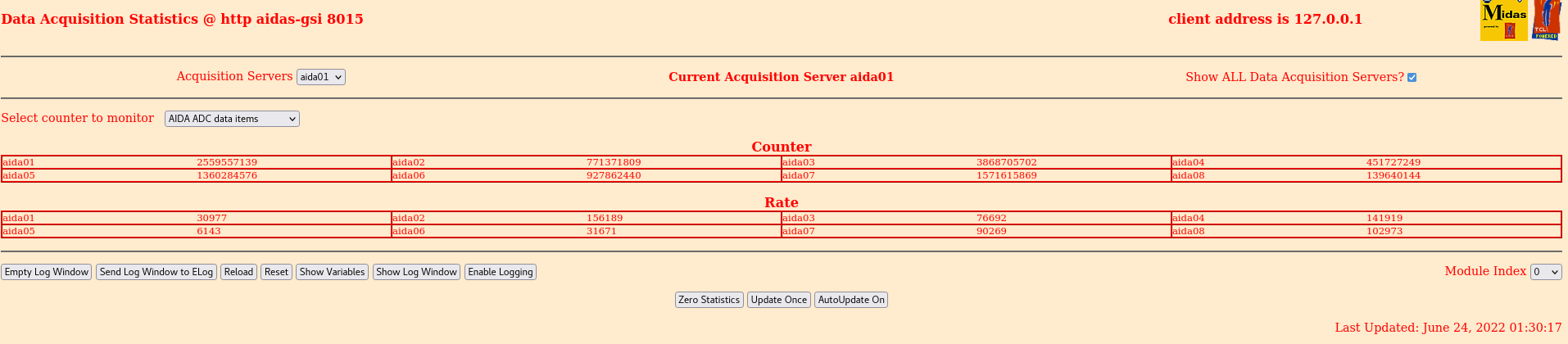

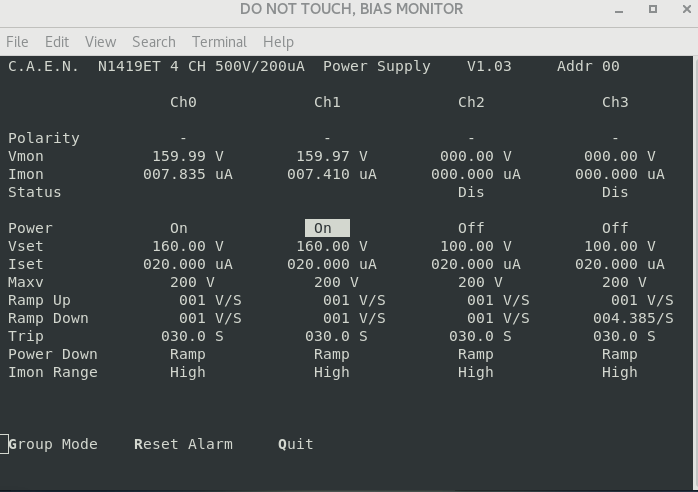

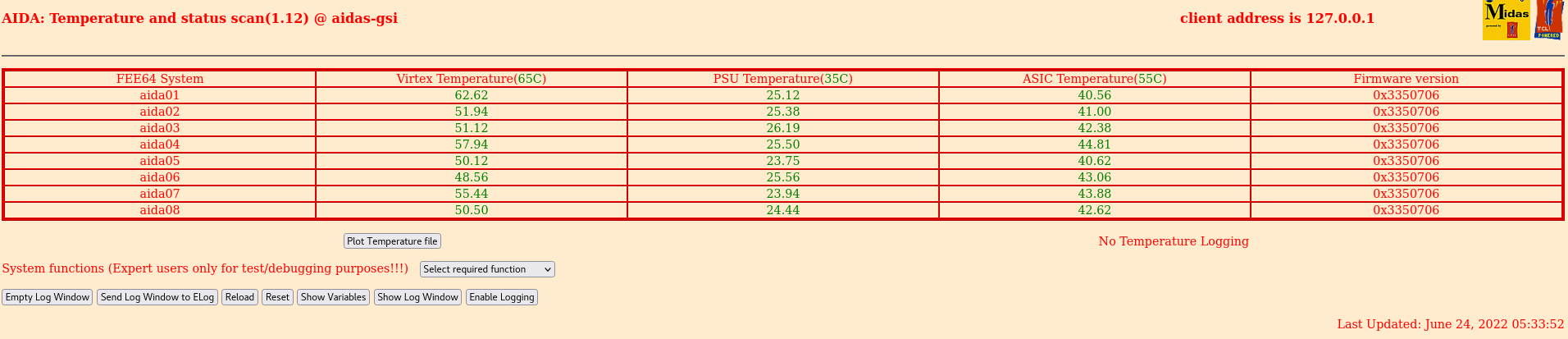

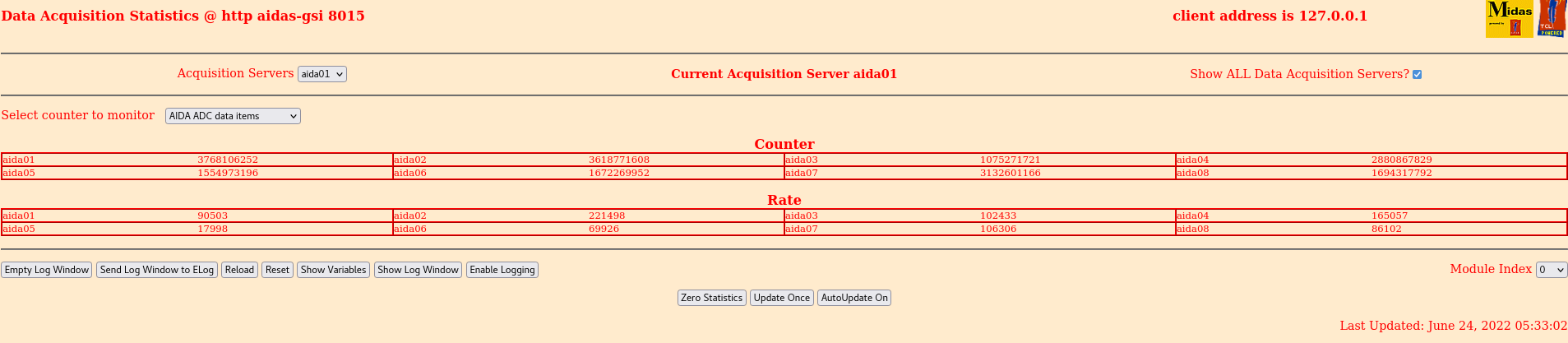

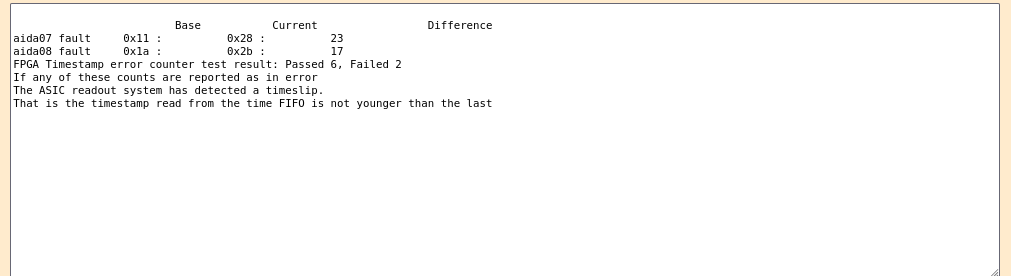

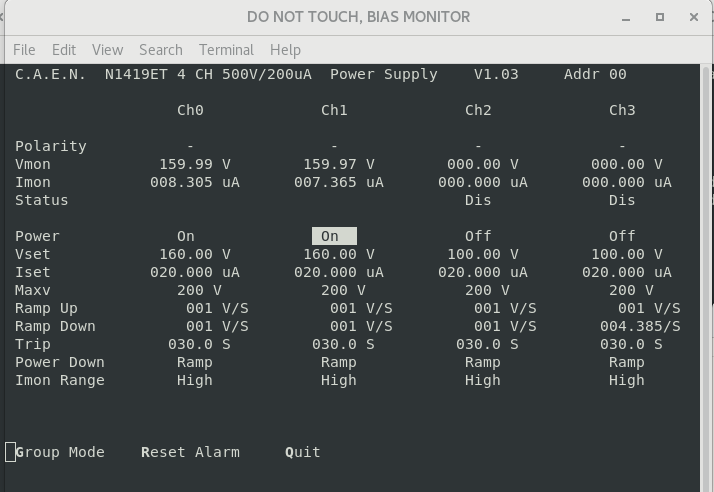

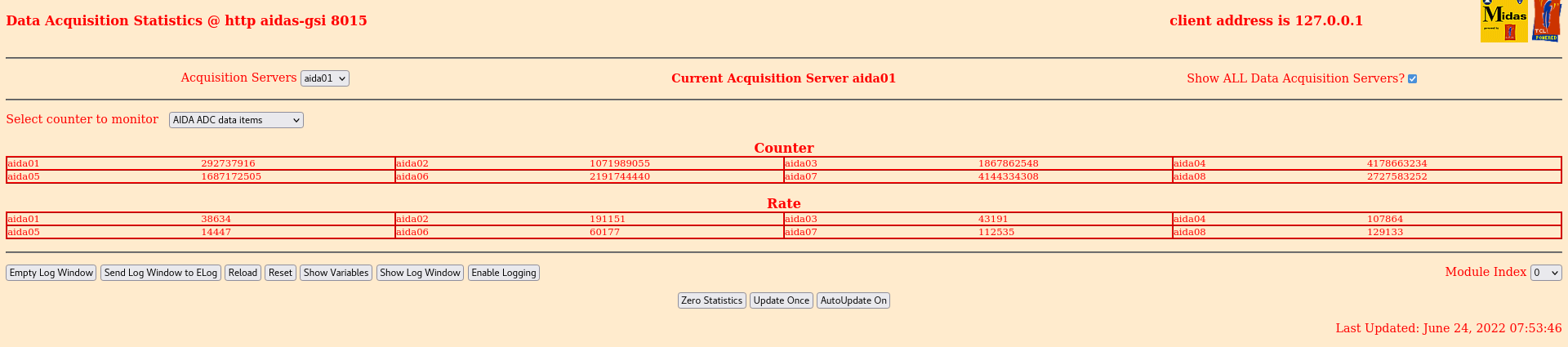

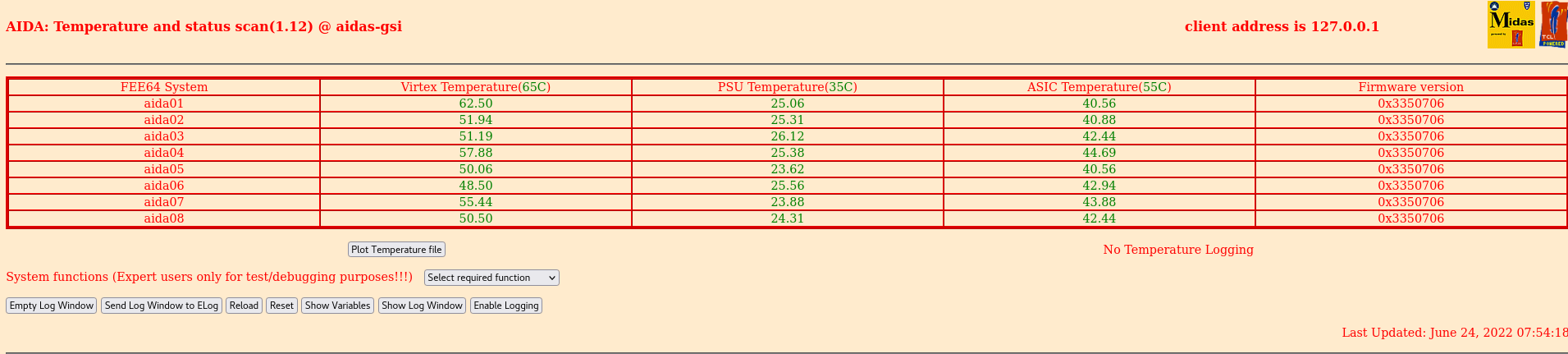

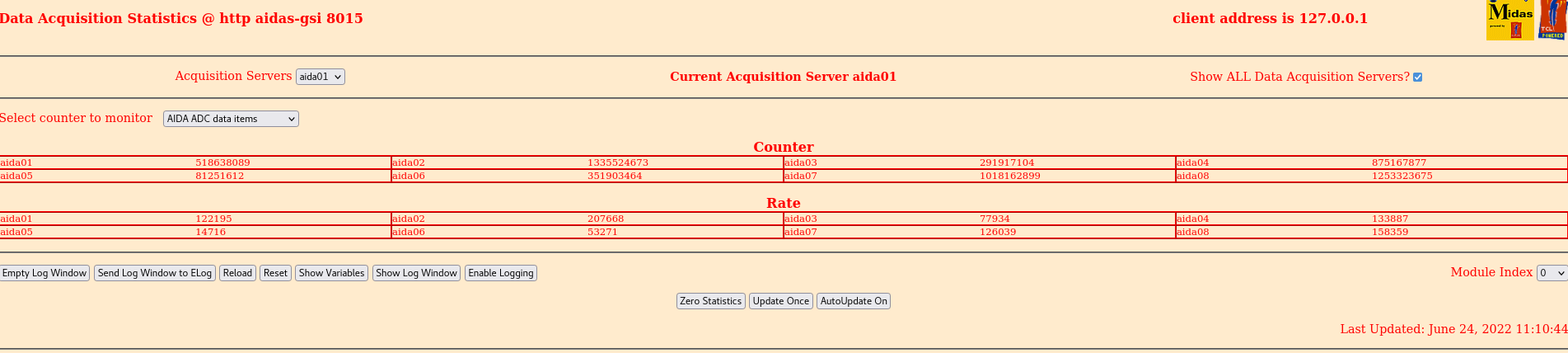

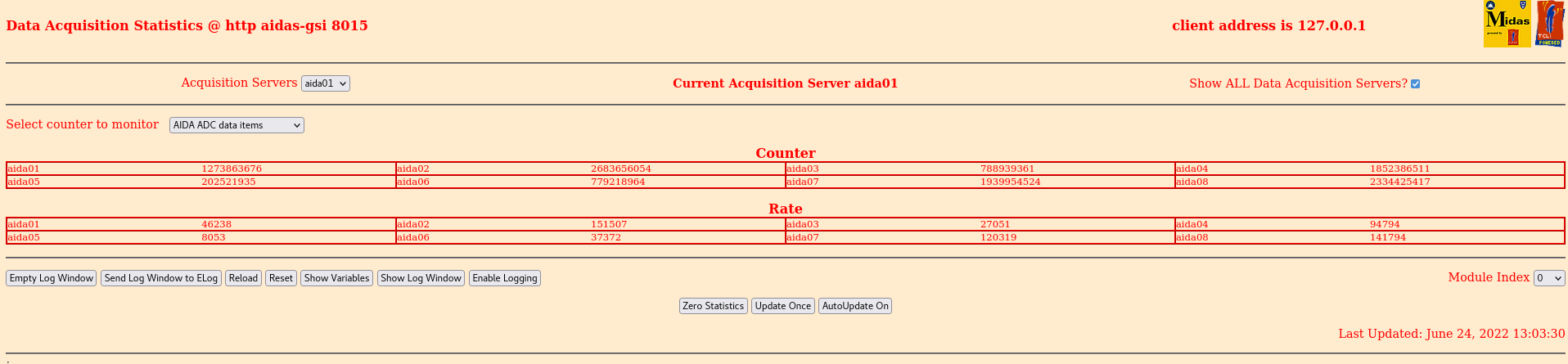

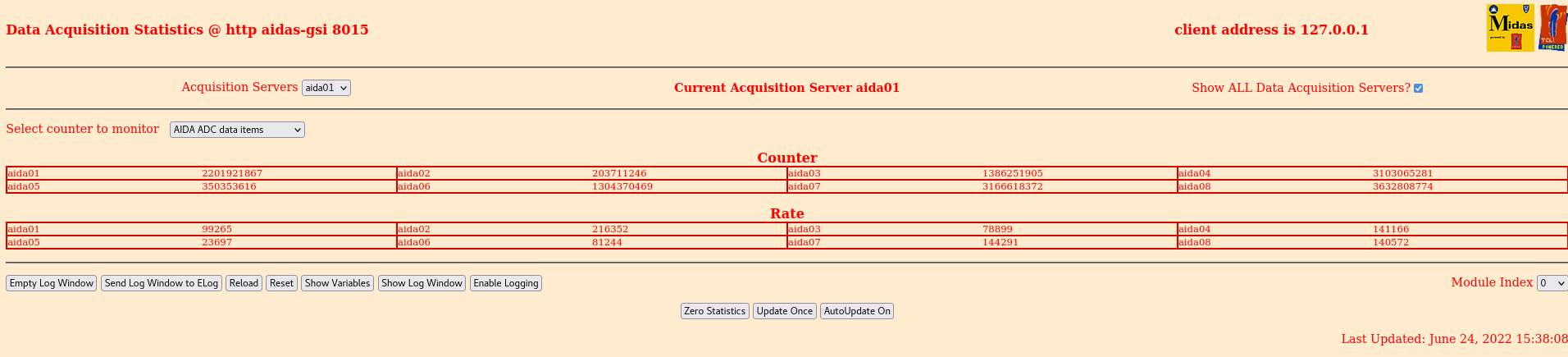

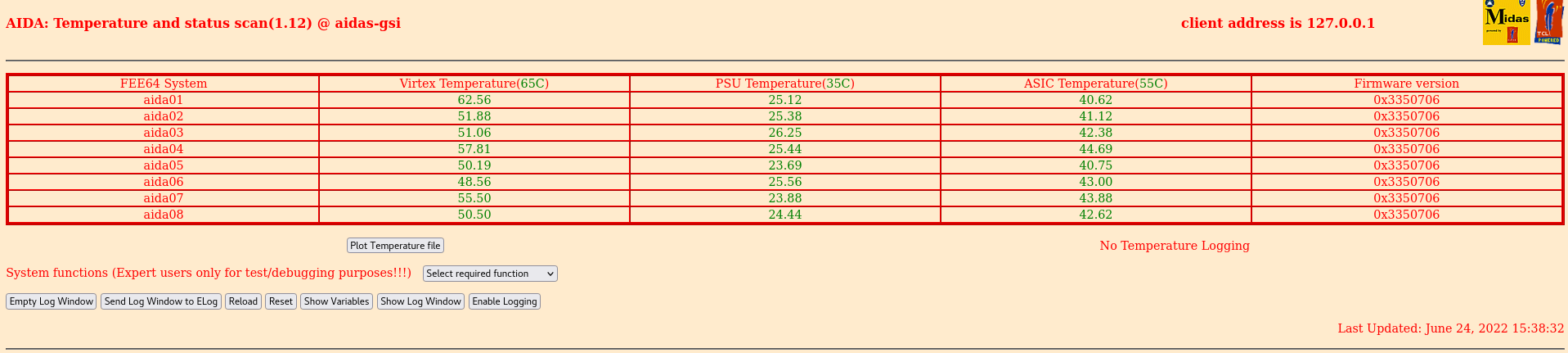

497

|

Fri Jun 24 15:04:06 2022 |

Marc | Friday 24th June - evening shift |

16:05 - Last checked was at 15:30. (see previous entry. All running smoothly.

Next wide check will be in about an hour.

17:00

Stats -ok - attachment 1

Temperatures ok - attachement 2

Leakage current ok but - attachment 3

ucesb screen-shot - attachment 4

Wide check completed. Nothing different.

WR status decoder status:

Base Current Difference

aida07 fault 0xc53d : 0xc547 : 10

aida08 fault 0xf1be : 0xf1e9 : 43

White Rabbit error counter test result: Passed 6, Failed 2

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

FPGA timestamp::

Base Current Difference

aida07 fault 0x2a : 0x2c : 2

FPGA Timestamp error counter test result: Passed 7, Failed 1

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

Note that the leakage current is ok but has increased since yesterday , See graphana - attachement 5 - Prossibly due to higher beam intensity.

19:20 -

Stats ok - attachment 6

Temp ok - attachment 7

Leakage current ok - attachement 8

Wide check completed and same output as above.

22:00

Stats ok - attachment 9

Temp ok - attachment 10

Leakage current ok - attachement 11

Wide check completed and same output as above.

|

| Attachment 1: Stats-Screenshot_from_2022-06-24_16-53-47.png

|

|

| Attachment 2: Temp-Screenshot_from_2022-06-24_16-52-58.png

|

|

| Attachment 3: HV_LC-Screenshot_from_2022-06-24_16-51-39.png

|

|

| Attachment 4: ucesb-Screenshot_from_2022-06-24_16-57-32.png

|

|

| Attachment 5: GraphanaAIDA-Screenshot_from_2022-06-24_17-48-41.png

|

|

| Attachment 6: Stats-Screenshot_from_2022-06-24_19-21-32.png

|

|

| Attachment 7: Temp-Screenshot_from_2022-06-24_19-20-48.png

|

|

| Attachment 8: HV-LC-Screenshot_from_2022-06-24_19-19-43.png

|

|

| Attachment 9: Stats-Screenshot_from_2022-06-24_22-01-09.png

|

|

| Attachment 10: Temp-Screenshot_from_2022-06-24_22-01-50.png

|

|

| Attachment 11: HV_LC-Screenshot_from_2022-06-24_21-58-33.png

|

|

|

|

495

|

Fri Jun 24 00:34:55 2022 |

AM | Friday 24 June 00:00-08:00 |

01:30 Attachments 1-5, white rabbit and fpga timestamp failures, otherwise all good

03:30 Attachments 11-15, white rabbit and fpga timestamp failures, otherwise all good

05:30 Attachments 6-10, white rabbit and fpga timestamp failures, otherwise all good

07:30 Attachments 16-20, white rabbit and fpga timestamp failures, otherwise all good |

| Attachment 1: 220624_0130_fpgatime.png

|

|

| Attachment 2: 220624_0130_whiterabbit.png

|

|

| Attachment 3: 220624_0130_temps.png

|

|

| Attachment 4: 220624_0130_stats.png

|

|

| Attachment 5: 220624_0130_bias.png

|

|

| Attachment 6: 220624_0530_fpgatime.png

|

|

| Attachment 7: 220624_0530_whiterabbit.png

|

|

| Attachment 8: 220624_0530_temps.png

|

|

| Attachment 9: 220624_0530_stats.png

|

|

| Attachment 10: 220624_0530_bias.png

|

|

| Attachment 11: 220624_0330_fpgatime.png

|

|

| Attachment 12: 220624_0330_whiterabbit.png

|

|

| Attachment 13: 220624_0330_temps.png

|

|

| Attachment 14: 220624_0330_stats.png

|

|

| Attachment 15: 220624_0330_bias.png

|

|

| Attachment 16: 220624_0730_fpga.png

|

|

| Attachment 17: 220624_0730_whiterabbit.png

|

|

| Attachment 18: 220624_0730_temps.png

|

|

| Attachment 19: 220624_0730_stats.png

|

|

| Attachment 20: 220624_0730_bias.png

|

|

|

|

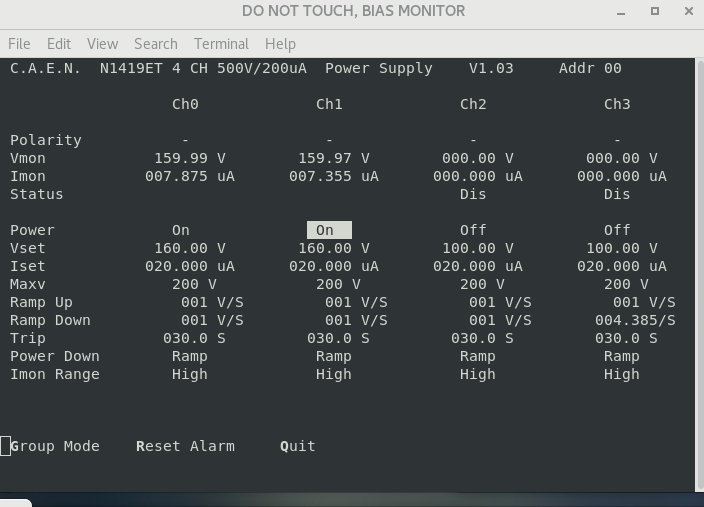

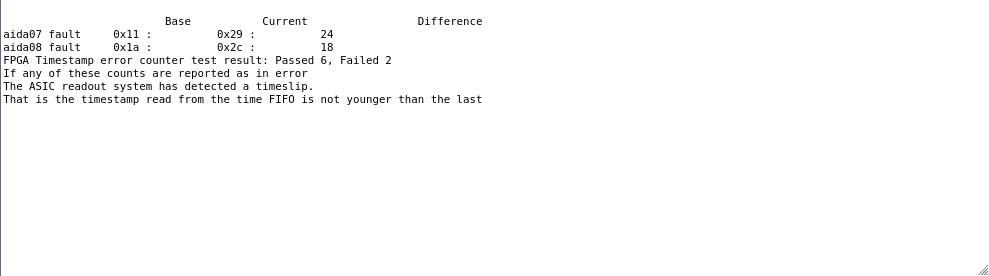

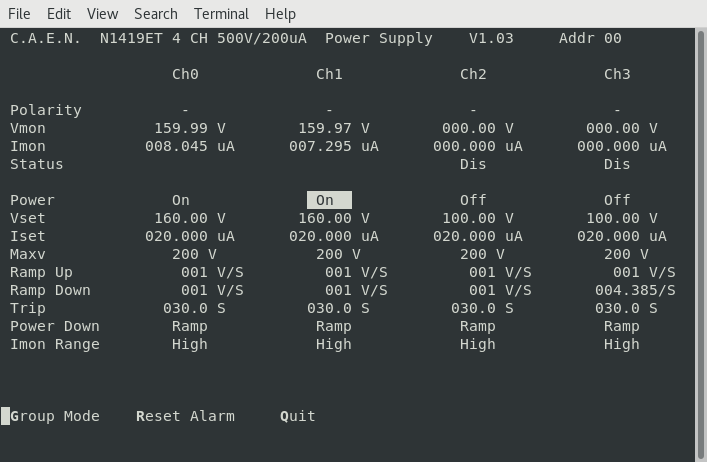

496

|

Fri Jun 24 06:56:06 2022 |

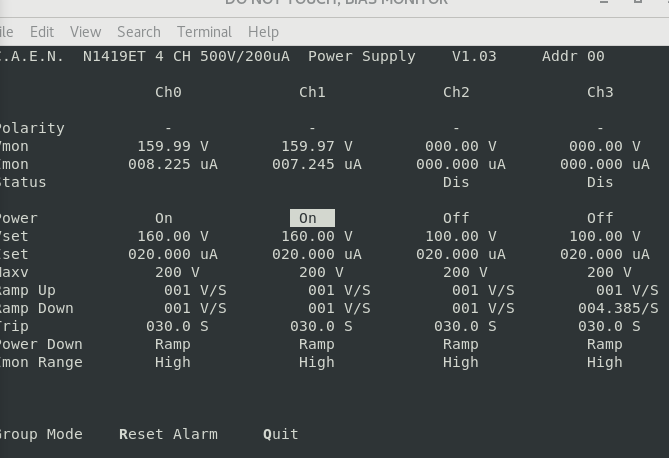

OH | Friday 24 June 008:00-16:00 |

07:56 Took over from AM. No issues reported overnight

Stats ok - attachment 1

Temperature ok - attachment 2

Bias and leakage current ok - attachment 3

System wide checks:

Clocks ok

WR

Base Current Difference

aida07 fault 0xc4fe : 0xc53b : 61

aida08 fault 0xf0e9 : 0xf1b7 : 206

White Rabbit error counter test result: Passed 6, Failed 2

FPGA Errors

Base Current Difference

aida07 fault 0x11 : 0x29 : 24

aida08 fault 0x1a : 0x2c : 18

FPGA Timestamp error counter test result: Passed 6, Failed 2

Analysis of R3_359 - attachment 4

Dead time still around 15.9%

Merger item rate around 2E6-4E6

Tape server rate at 7750 kB/s

Current HDD free space 1.7 TB

Time left in HDD 2.59 days

Will run out of space at some point on Sunday

Have started compression of uncompressed raw data on the HDD. Using nice +10

08:45 AIDA07 dropped out from the merger at some point in the preceeding 5-10 minutes. - attachment 5

Am regularly checking the statistics

Was able to stop the DAQ by relaunching the merger.

Reset the FEEs and recovered without a powercylce

Started R4 following this stop

08:58 They have taken the beam to change the ion source for maybe 2 hours

Will stop writing data but continue forwarding to MBS

No storage ticked. Following break will be on R5

11:10 Beam is starting to come back R5 started

Stats ok - attachment 6

Temps ok - attachment 7

Bias and leakage currents ok - attachment 8

13:05 Statistics ok - attachment 9

Temps ok - attachment 10

Bias and leakage curents ok - attachment 11

System wide checks:

WR

Base Current Difference

aida07 fault 0xc53d : 0xc540 : 3

aida08 fault 0xf1be : 0xf1d0 : 18

White Rabbit error counter test result: Passed 6, Failed 2

FPGA

Base Current Difference

aida07 fault 0x2a : 0x2b : 1

FPGA Timestamp error counter test result: Passed 7, Failed 1

Analysis of R5_33 - attachment 12

15:28 Statistics ok - attachment 13

Temperature ok - attachment 14

Bias and leakage current ok - attachment 15

System wide checks:

Base Current Difference

aida07 fault 0xc53d : 0xc546 : 9

aida08 fault 0xf1be : 0xf1e0 : 34

White Rabbit error counter test result: Passed 6, Failed 2

Base Current Difference

aida07 fault 0x2a : 0x2b : 1

FPGA Timestamp error counter test result: Passed 7, Failed 1

Analysis of R5_63 - attachment 16 |

| Attachment 1: 220624_0753_stats.png

|

|

| Attachment 2: 220624_0754_Temp.png

|

|

| Attachment 3: 220624_0755_Bias.png

|

|

| Attachment 4: R3_359_analysis.txt

|

*** TDR format 3.3.0 analyser - TD - May 2021

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 260715255 ( 897318.9 Hz)

Other data format: 1204745 ( 4146.4 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 1323 ( 4.6 Hz)

RESUME: 1323 ( 4.6 Hz)

SYNC100: 33082 ( 113.9 Hz)

WR48-63: 33082 ( 113.9 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 1135935 ( 3909.6 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 353220 ( 1215.7 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 290.549 s

FEE elapsed dead time(s) elapsed idle time(s)

0 10.171 0.000

1 46.409 0.000

2 1.006 0.000

3 4.601 0.000

4 0.000 37.574

5 0.031 0.000

6 0.191 0.000

7 0.254 0.000

8 0.000 0.000

9 0.000 0.000

10 0.000 0.000

11 0.000 0.000

12 0.000 0.000

13 0.000 0.000

14 0.000 0.000

15 0.000 0.000

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 30903987 28078 0 0 236 236 4023 4023 0 19560 0 86851

1 61208192 17252 0 0 718 718 7908 7908 0 0 0 52897

2 26785987 291397 0 0 72 72 3425 3425 0 284403 0 56573

3 43119726 289440 0 0 153 153 5319 5319 0 278496 0 29859

4 4604412 1194 0 0 0 0 597 597 0 0 0 28791

5 18336996 4656 0 0 16 16 2312 2312 0 0 0 34152

6 36059875 277258 0 0 42 42 4514 4514 0 268146 0 48935

7 39696080 295470 0 0 86 86 4984 4984 0 285330 0 15162

8 0 0 0 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time: 34.877s ( 917.511 blocks/s, 57.344 Mb/s)

|

| Attachment 5: 220624_0842_Stats_Stop.png

|

|

| Attachment 6: 220624_1111_Stats.png

|

|

| Attachment 7: 220624_1111_Temp.png

|

|

| Attachment 8: 220624_1112_Bias.png

|

|

| Attachment 9: 220624_1303_stats.png

|

|

| Attachment 10: 220624_1303_Temp.png

|

|

| Attachment 11: 220624_1304_Bias.png

|

|

| Attachment 12: R5_33_analysis.txt

|

*** TDR format 3.3.0 analyser - TD - May 2021

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 260717099 ( 869523.1 Hz)

Other data format: 1202901 ( 4011.8 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 1344 ( 4.5 Hz)

RESUME: 1344 ( 4.5 Hz)

SYNC100: 33117 ( 110.4 Hz)

WR48-63: 33117 ( 110.4 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 1133979 ( 3782.0 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 354749 ( 1183.1 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 299.839 s

FEE elapsed dead time(s) elapsed idle time(s)

0 11.504 0.000

1 42.102 0.000

2 0.275 0.000

3 6.677 0.000

4 0.000 31.976

5 0.051 0.000

6 0.250 0.000

7 0.412 0.000

8 0.000 0.000

9 0.000 0.000

10 0.000 0.000

11 0.000 0.000

12 0.000 0.000

13 0.000 0.000

14 0.000 0.000

15 0.000 0.000

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 31758241 28867 0 0 238 238 4156 4156 0 20079 0 87480

1 58453105 16104 0 0 635 635 7417 7417 0 0 0 53128

2 20104679 289945 0 0 41 41 2565 2565 0 284733 0 56849

3 41709424 287290 0 0 188 188 5262 5262 0 276390 0 29572

4 5133297 1264 0 0 0 0 632 632 0 0 0 29278

5 17857346 4470 0 0 22 22 2213 2213 0 0 0 34539

6 40732502 278221 0 0 59 59 5175 5175 0 267753 0 48740

7 44968505 296740 0 0 161 161 5697 5697 0 285024 0 15163

8 0 0 0 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time: 34.742s ( 921.070 blocks/s, 57.567 Mb/s)

|

| Attachment 13: 220624_1538_Stats.png

|

|

| Attachment 14: 220624_1538_Temp.png

|

|

| Attachment 15: 220624_1538_Bias.png

|

|

| Attachment 16: R5_63_analysis.txt

|

*** TDR format 3.3.0 analyser - TD - May 2021

*** ERROR: READ I/O error: 5002

blocks: 32000

ADC data format: 260796374 ( 834020.0 Hz)

Other data format: 1123626 ( 3593.3 Hz)

Sample trace data format: 0 ( 0.0 Hz)

Undefined format: 0 ( 0.0 Hz)

Other data format type: PAUSE: 1191 ( 3.8 Hz)

RESUME: 1191 ( 3.8 Hz)

SYNC100: 33165 ( 106.1 Hz)

WR48-63: 33165 ( 106.1 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 1054914 ( 3373.6 Hz)

Other info: 0 ( 0.0 Hz)

ADC data range bit set: 350507 ( 1120.9 Hz)

Timewarps: ADC: 0 ( 0.0 Hz)

PAUSE: 0 ( 0.0 Hz)

RESUME: 0 ( 0.0 Hz)

SYNC100: 0 ( 0.0 Hz)

WR48-63: 0 ( 0.0 Hz)

FEE64 disc: 0 ( 0.0 Hz)

MBS info: 0 ( 0.0 Hz)

Undefined: 0 ( 0.0 Hz)

Sample trace: 0 ( 0.0 Hz)

*** Timestamp elapsed time: 312.698 s

FEE elapsed dead time(s) elapsed idle time(s)

0 7.889 0.000

1 39.498 0.000

2 0.306 0.000

3 5.270 0.000

4 0.000 26.707

5 0.036 0.000

6 0.217 0.000

7 0.175 0.000

8 0.000 0.000

9 0.000 0.000

10 0.000 0.000

11 0.000 0.000

12 0.000 0.000

13 0.000 0.000

14 0.000 0.000

15 0.000 0.000

16 0.000 0.000

17 0.000 0.000

18 0.000 0.000

19 0.000 0.000

20 0.000 0.000

21 0.000 0.000

22 0.000 0.000

23 0.000 0.000

24 0.000 0.000

25 0.000 0.000

26 0.000 0.000

27 0.000 0.000

28 0.000 0.000

29 0.000 0.000

30 0.000 0.000

31 0.000 0.000

32 0.000 0.000

*** Statistics

FEE ADC Data Other Data Sample Undefined Pause Resume SYNC100 WR48-63 Disc MBS Other HEC Data

0 30903831 29785 0 0 188 188 4074 4074 0 21261 0 87155

1 61666403 16932 0 0 646 646 7820 7820 0 0 0 55280

2 20140383 267008 0 0 42 42 2575 2575 0 261774 0 55290

3 41652352 266495 0 0 164 164 5306 5306 0 255555 0 28879

4 4871487 1204 0 0 0 0 602 602 0 0 0 28340

5 17605547 4430 0 0 11 11 2204 2204 0 0 0 33538

6 41056242 264471 0 0 55 55 5126 5126 0 254109 0 47278

7 42900129 273301 0 0 85 85 5458 5458 0 262215 0 14747

8 0 0 0 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0 0 0 0

*** Timewarps

FEE ADC Pause Resume SYNC100 WR48-63 Disc MBS Undefined Samples

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

2 0 0 0 0 0 0 0 0 0

3 0 0 0 0 0 0 0 0 0

4 0 0 0 0 0 0 0 0 0

5 0 0 0 0 0 0 0 0 0

6 0 0 0 0 0 0 0 0 0

7 0 0 0 0 0 0 0 0 0

8 0 0 0 0 0 0 0 0 0

9 0 0 0 0 0 0 0 0 0

10 0 0 0 0 0 0 0 0 0

11 0 0 0 0 0 0 0 0 0

12 0 0 0 0 0 0 0 0 0

13 0 0 0 0 0 0 0 0 0

14 0 0 0 0 0 0 0 0 0

15 0 0 0 0 0 0 0 0 0

16 0 0 0 0 0 0 0 0 0

17 0 0 0 0 0 0 0 0 0

18 0 0 0 0 0 0 0 0 0

19 0 0 0 0 0 0 0 0 0

20 0 0 0 0 0 0 0 0 0

21 0 0 0 0 0 0 0 0 0

22 0 0 0 0 0 0 0 0 0

23 0 0 0 0 0 0 0 0 0

24 0 0 0 0 0 0 0 0 0

25 0 0 0 0 0 0 0 0 0

26 0 0 0 0 0 0 0 0 0

27 0 0 0 0 0 0 0 0 0

28 0 0 0 0 0 0 0 0 0

29 0 0 0 0 0 0 0 0 0

30 0 0 0 0 0 0 0 0 0

31 0 0 0 0 0 0 0 0 0

32 0 0 0 0 0 0 0 0 0

*** Program elapsed time: 41.305s ( 774.730 blocks/s, 48.421 Mb/s)

|

|

|

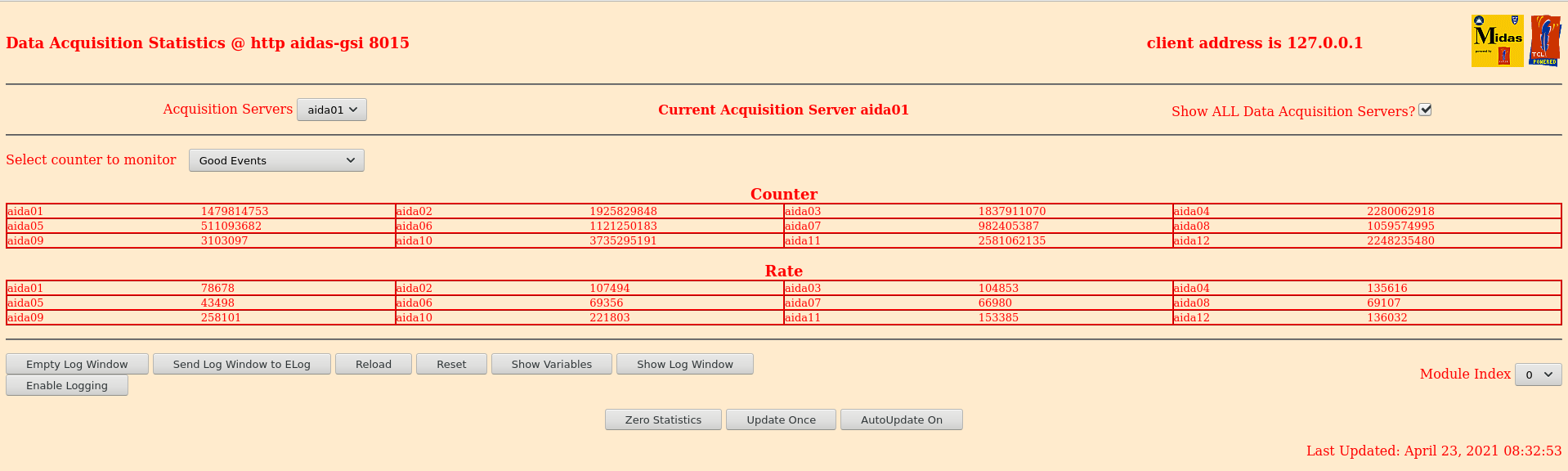

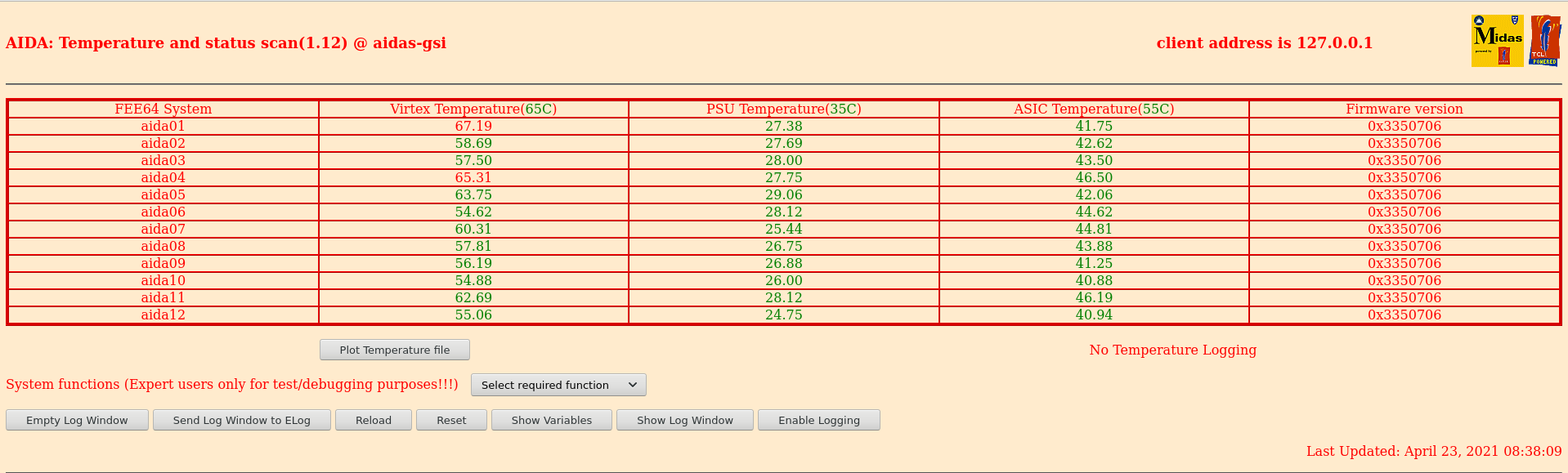

264

|

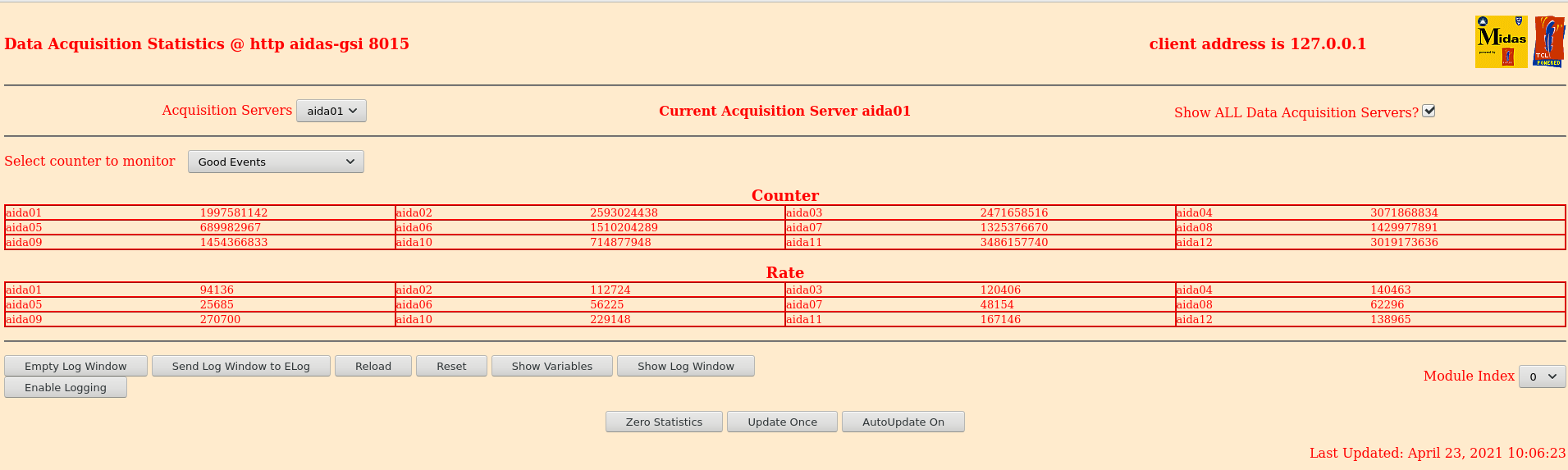

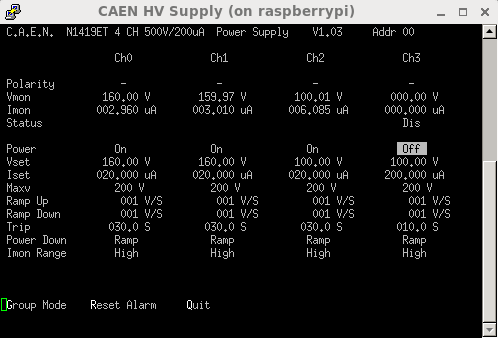

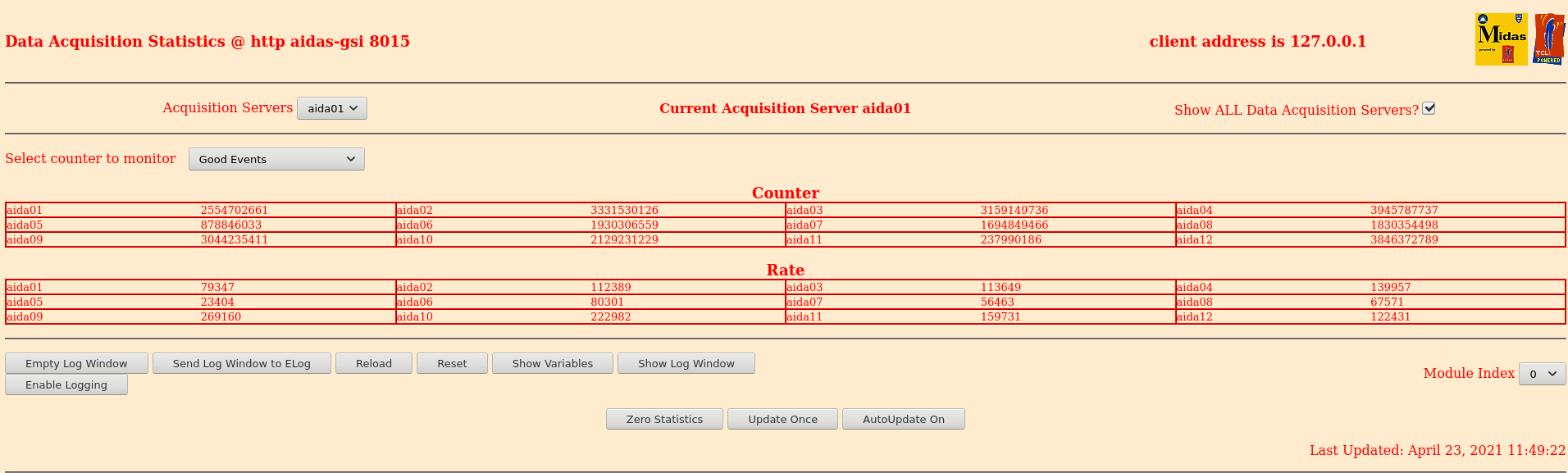

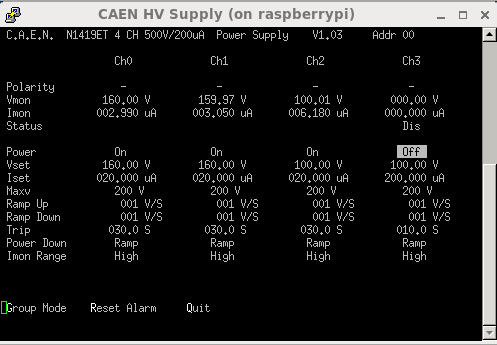

Fri Apr 23 07:09:57 2021 |

LJW | Friday 23rd April 08:00-12:00 |

08:30

System Checks

Clock Status error:

FEE64 module aida06 global clocks failed, 6

Clock status test result: Passed 11, Failed 1

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

ADC Calibration error:

FEE64 module aida06 failed

FEE64 module aida07 failed

FEE64 module aida12 failed

Calibration test result: Passed 9, Failed 3

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

White Rabbit Decoder Status error:

Base Current Difference

aida06 fault 0x679f : 0x67a2 : 3