| ID |

Date |

Author |

Subject |

|

242

|

Sun Apr 18 21:43:01 2021 |

ML-OH | system wide checks |

New System wide check 10pm CET

Clock status test result: Passed 12, Failed 0

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

ADC calibration check:

FEE64 module aida06 failed

FEE64 module aida07 failed

FEE64 module aida10 failed

Calibration test result: Passed 9, Failed 3

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

Base Current Difference

aida01 fault 0x7686 : 0x768a : 4

aida02 fault 0x941d : 0x9421 : 4

aida03 fault 0x7cd7 : 0x7cdb : 4

aida04 fault 0xb86d : 0xb871 : 4

aida05 fault 0x1a59 : 0x1a61 : 8

aida06 fault 0x4f45 : 0x4f4d : 8

aida07 fault 0x3bfc : 0x3c1d : 33

aida08 fault 0xc7ce : 0xc7d5 : 7

aida09 fault 0xb33b : 0xb33c : 1

White Rabbit error counter test result: Passed 3, Failed 9

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

FPGA timestamp error checks:

Base Current Difference

aida09 fault 0x1 : 0x2 : 1

aida12 fault 0xa : 0xf : 5

FPGA Timestamp error counter test result: Passed 10, Failed 2

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

Memory from FEE64:

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 22 19 6 4 2 3 2 4 2 3 6 : 36304

aida02 : 23 9 3 3 1 3 1 4 2 3 6 : 35828

aida03 : 15 5 6 3 2 3 3 3 2 3 6 : 35876

aida04 : 20 8 18 1 1 3 4 3 2 3 6 : 36240

aida05 : 21 7 1 2 1 2 4 3 2 3 6 : 35868

aida06 : 18 8 4 1 3 4 1 3 3 3 6 : 36520

aida07 : 4 9 3 4 2 3 2 2 3 3 6 : 36104

aida08 : 15 5 2 4 2 1 3 4 2 3 6 : 36100

aida09 : 2 23 8 1 2 3 2 4 2 3 6 : 36192

aida10 : 10 7 8 5 2 1 3 3 2 3 6 : 35712

aida11 : 1 9 5 1 2 3 1 4 2 3 6 : 35772

aida12 : 14 8 6 3 3 4 1 3 3 3 6 : 36600 |

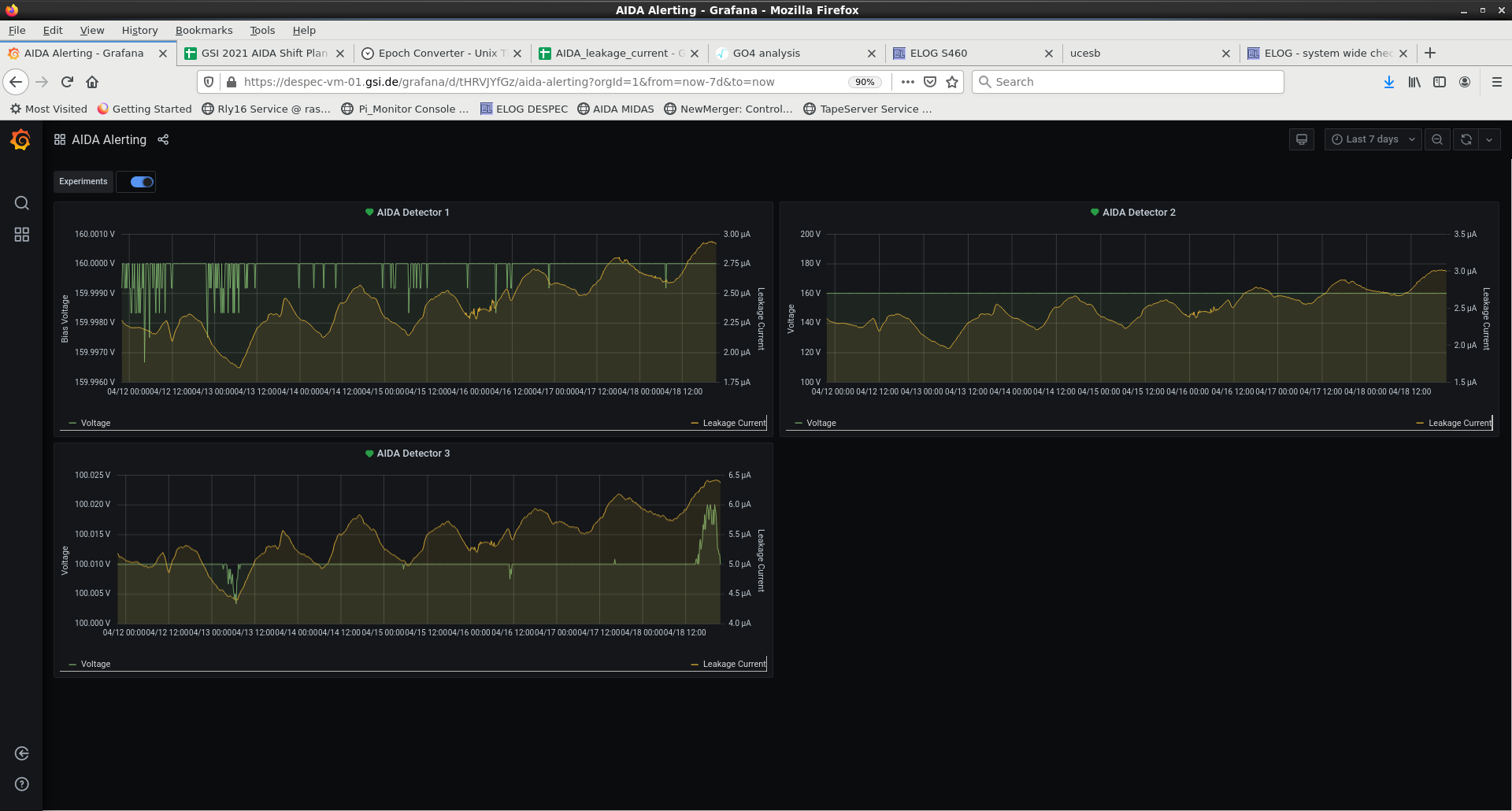

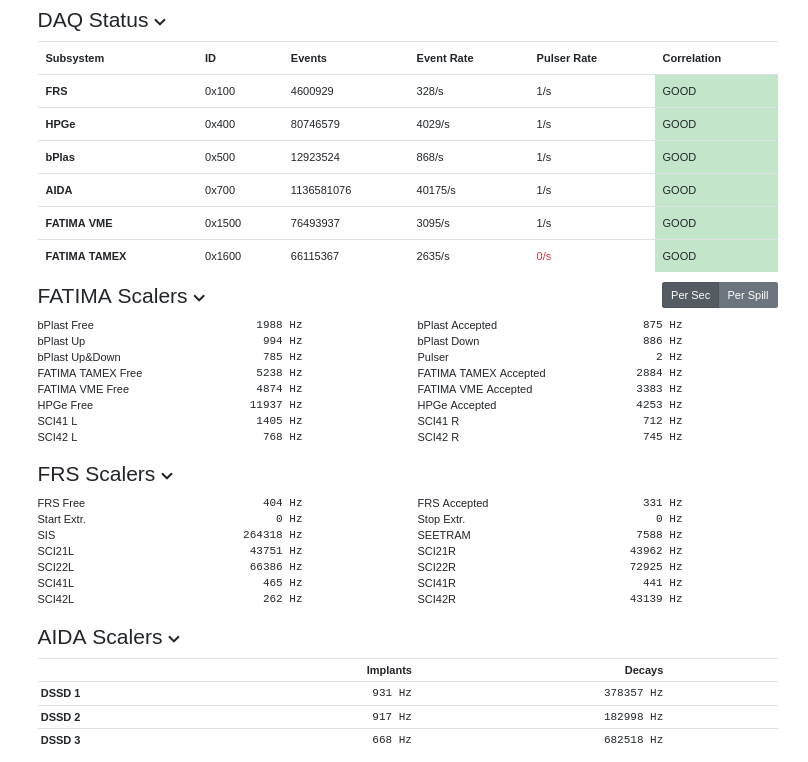

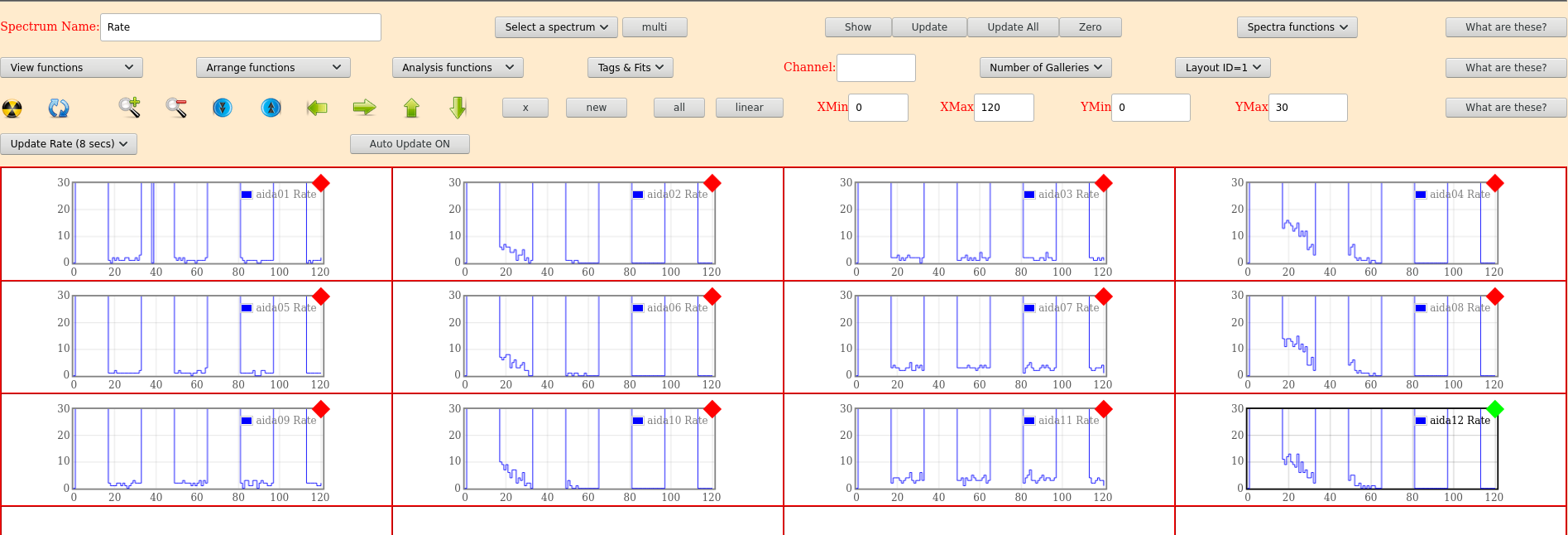

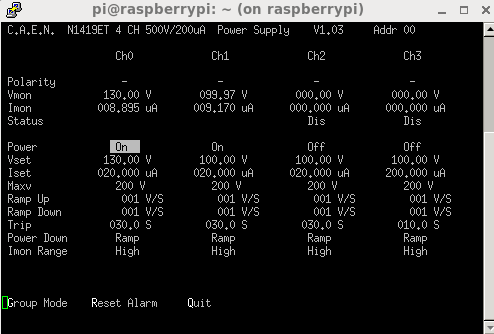

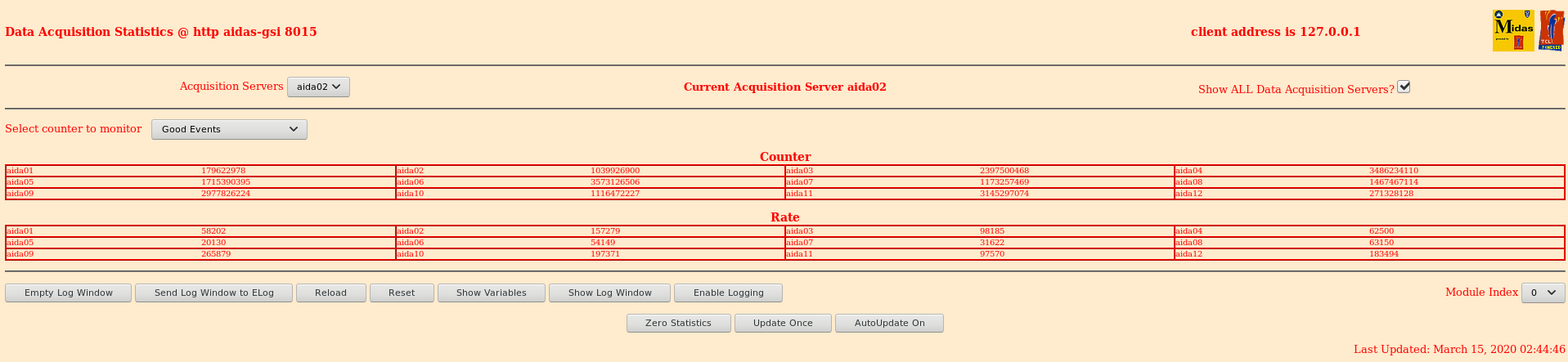

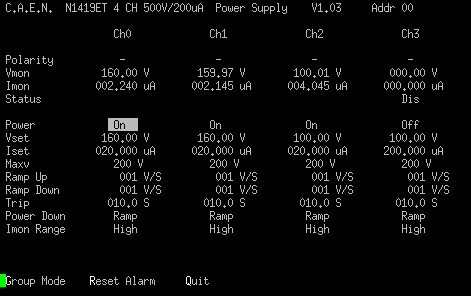

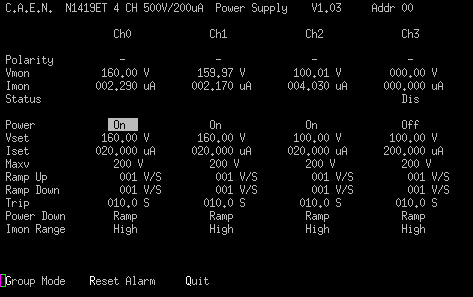

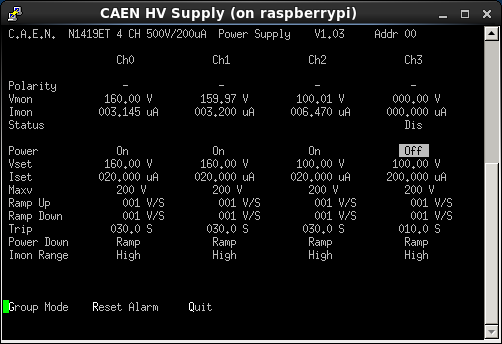

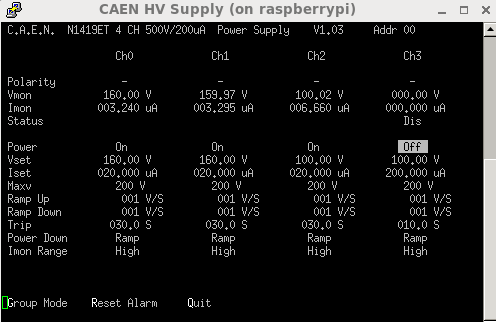

| Attachment 1: 18-04-2021_10pm_HV.png

|

|

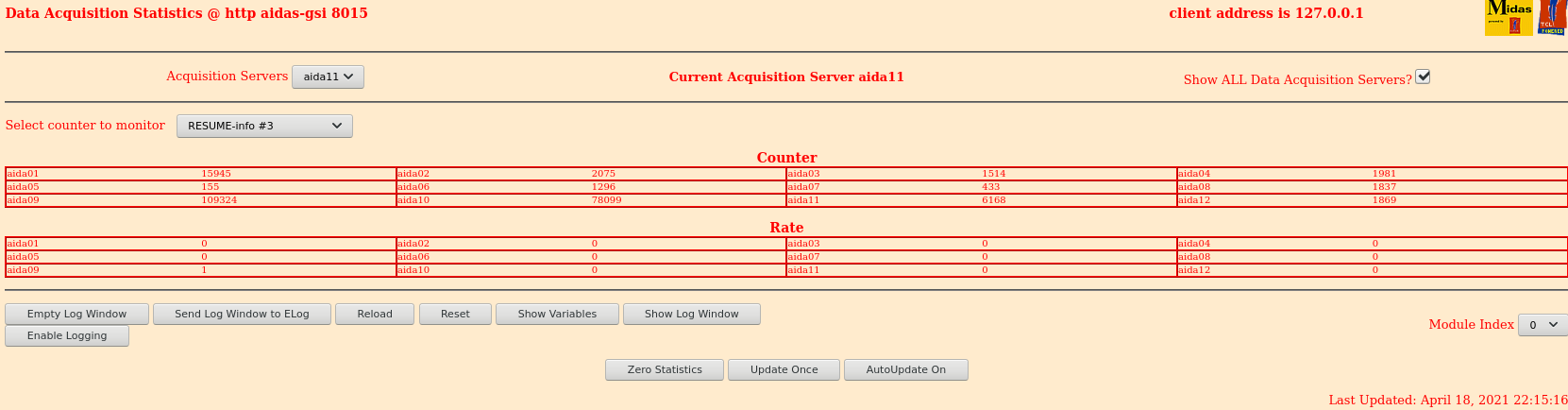

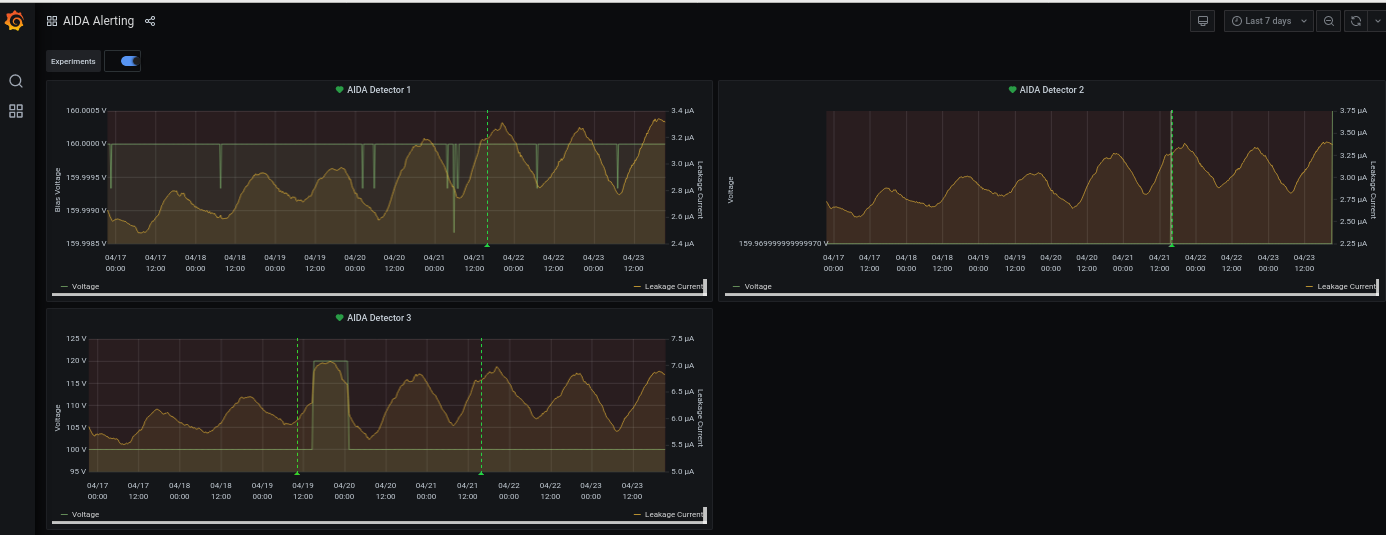

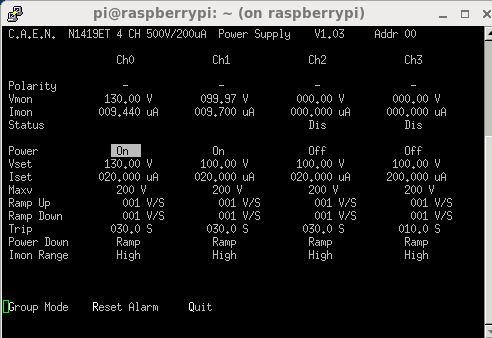

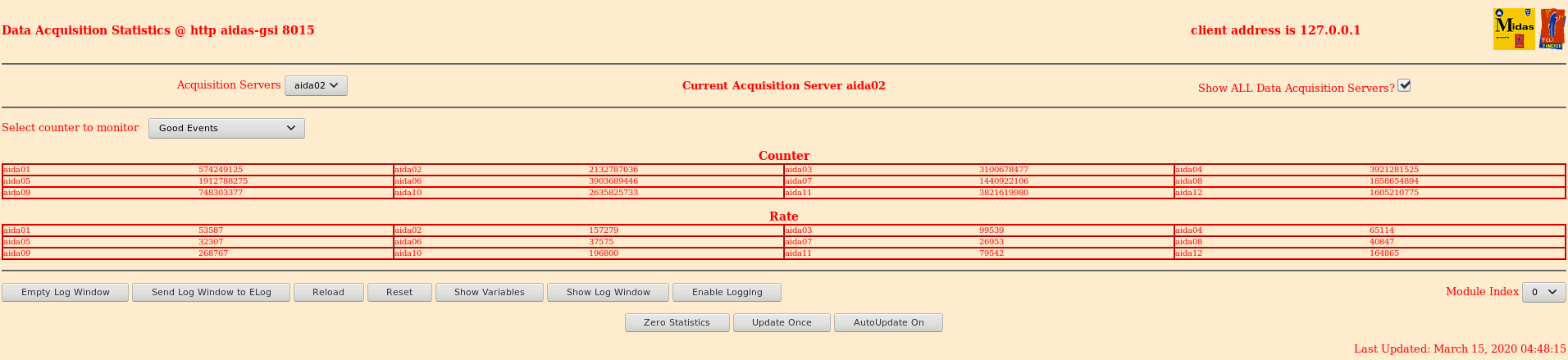

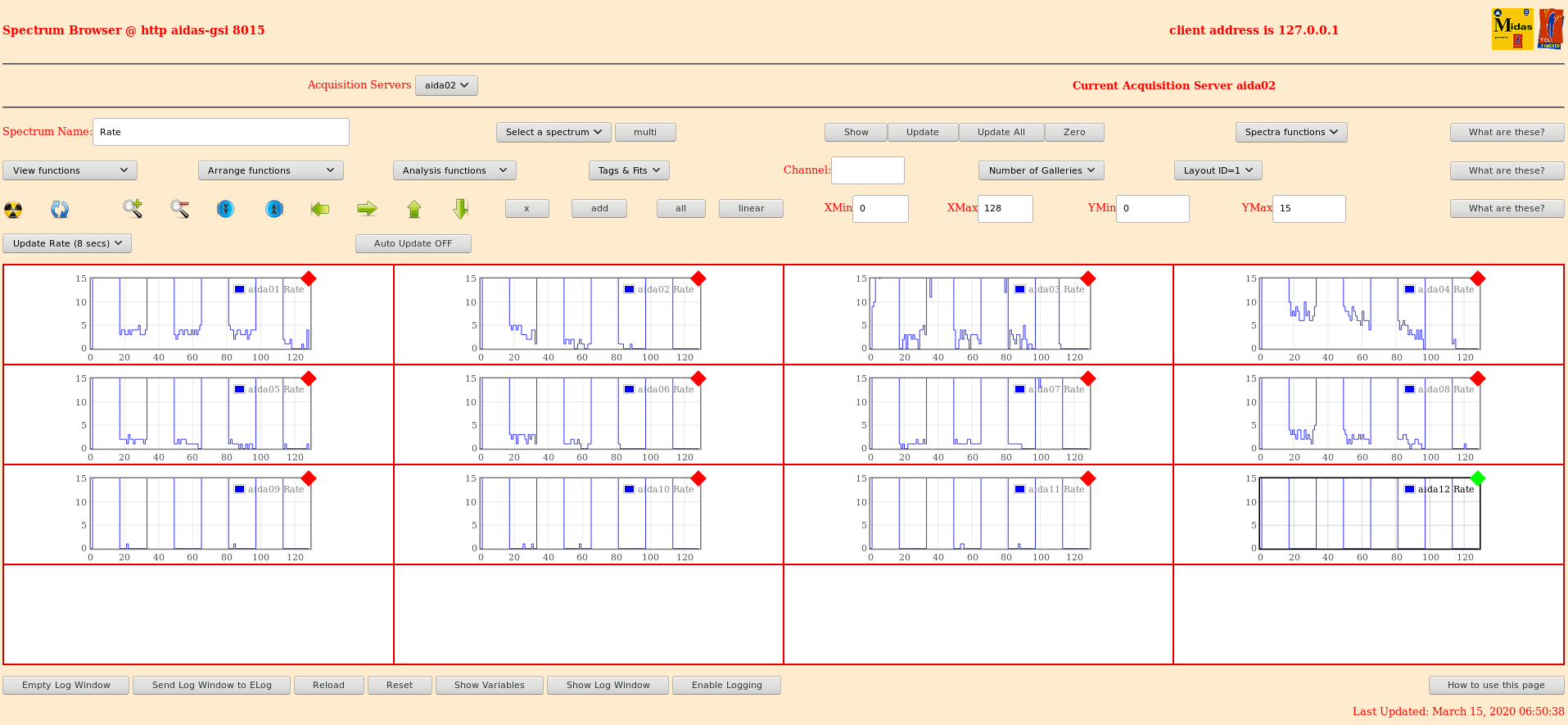

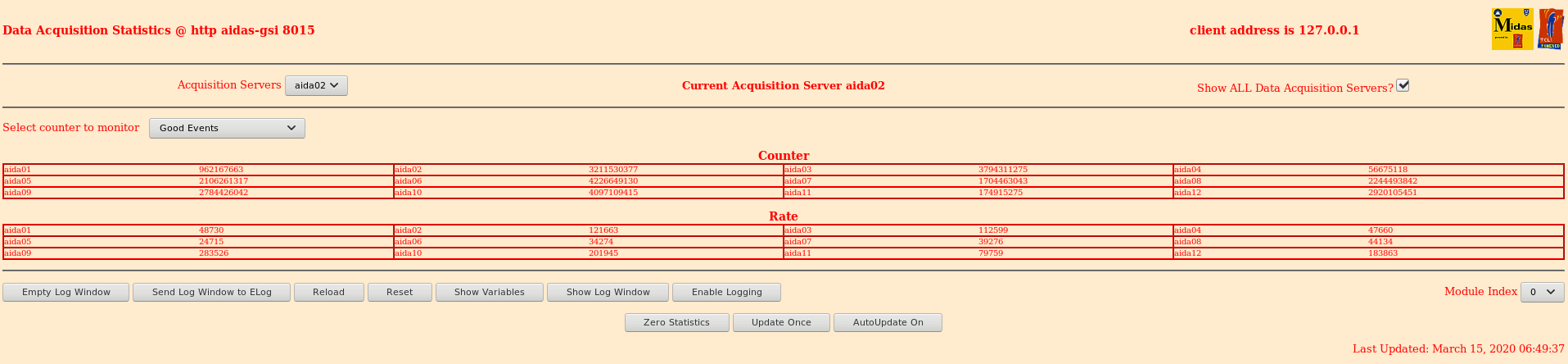

| Attachment 2: 18-04-2021_10pm_StatGoodEvt.png

|

|

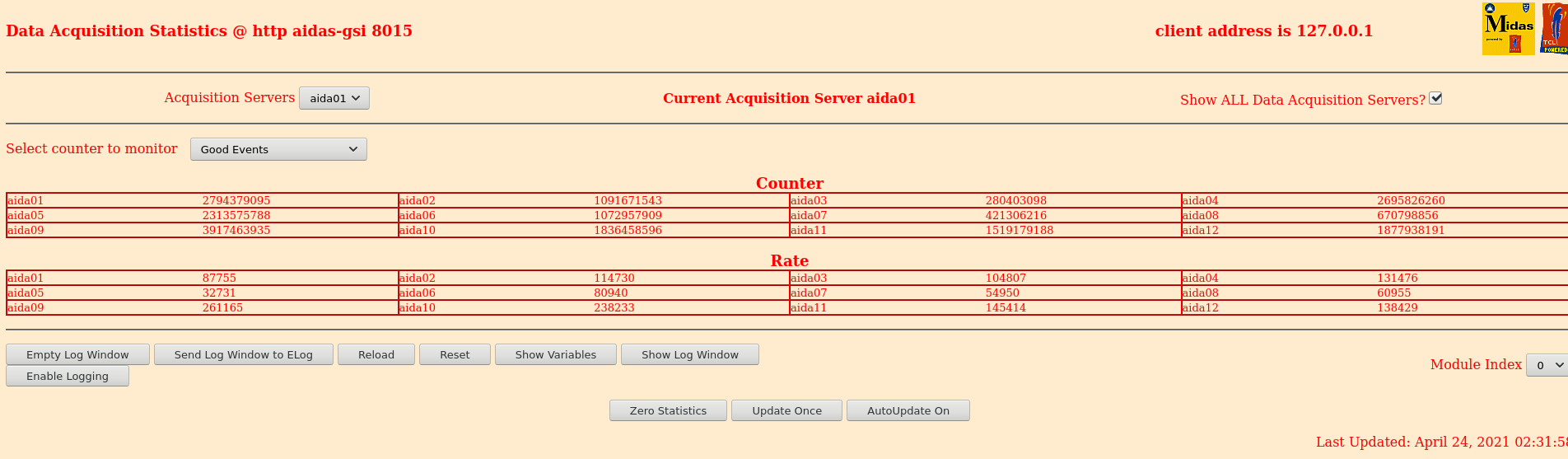

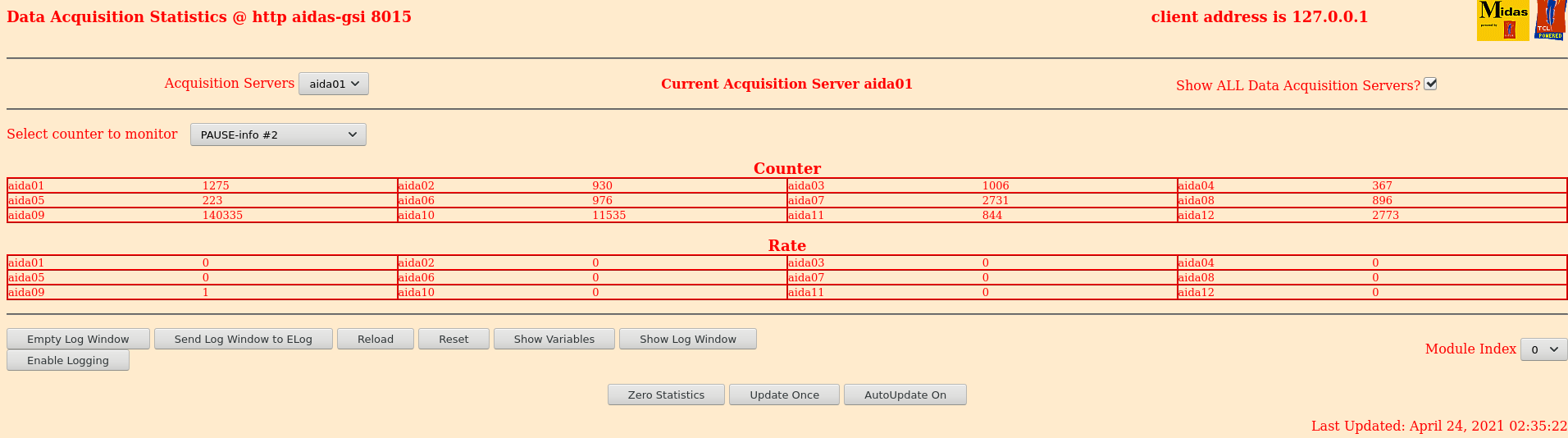

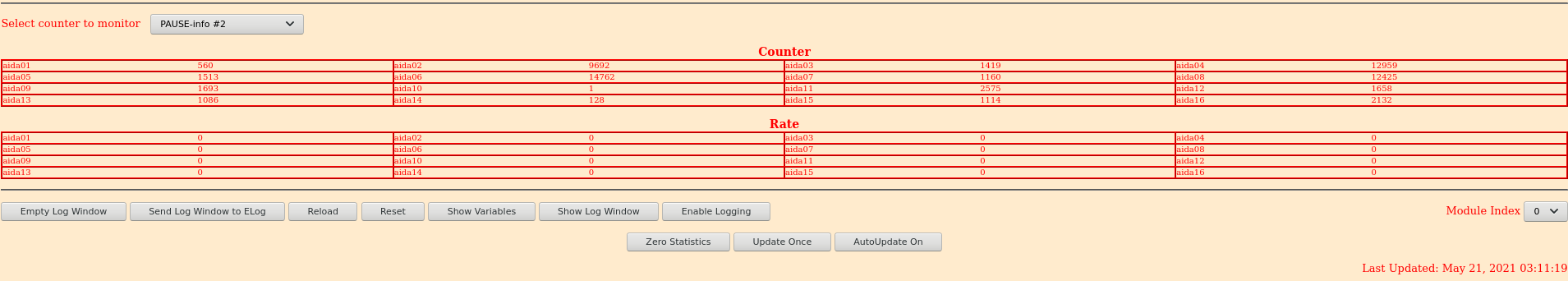

| Attachment 3: 18-04-2021_10pm_PAUSE.png

|

|

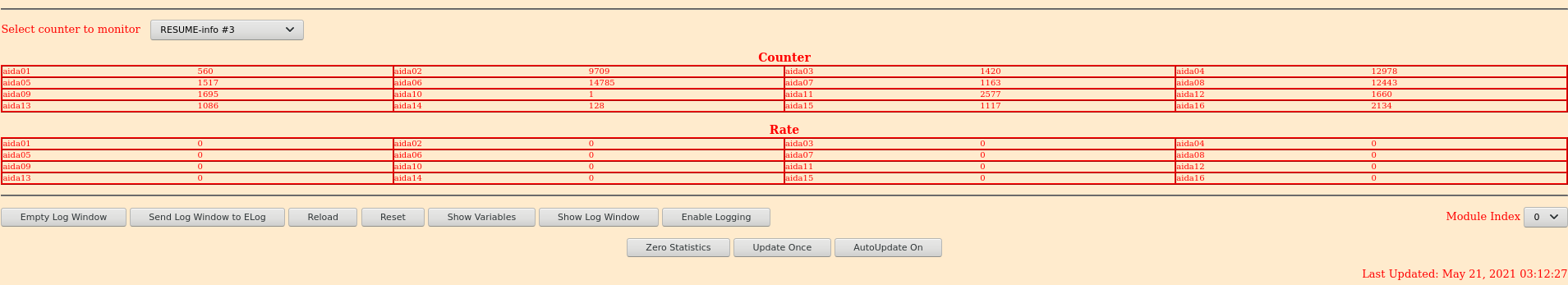

| Attachment 4: 18-04-2021_10pm_RESUME.png

|

|

| Attachment 5: 18-04-2021_10pm_ADCdataItem.png

|

|

| Attachment 6: 18-04-2021_10pm_DISC.png

|

|

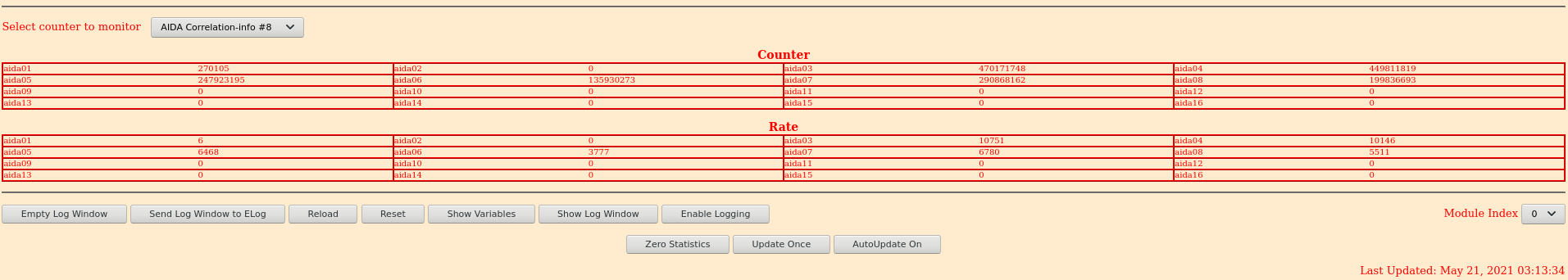

| Attachment 7: 18-04-2021_10pm_correlations.png

|

|

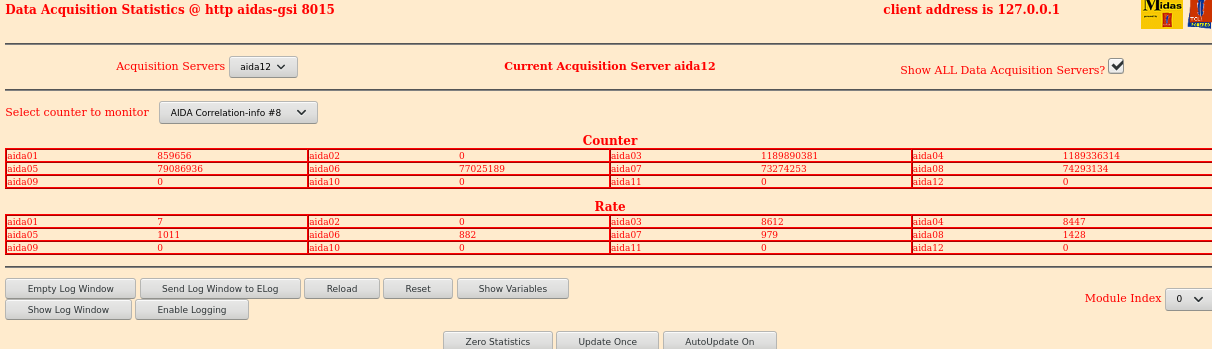

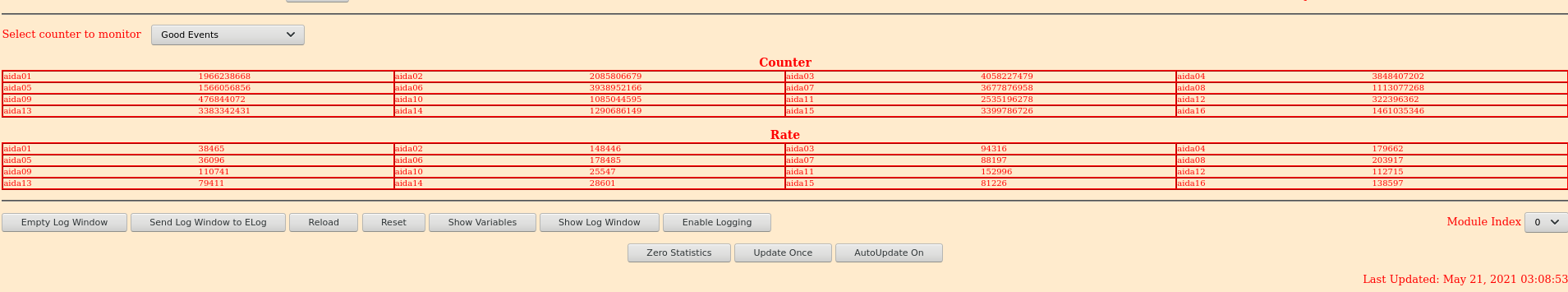

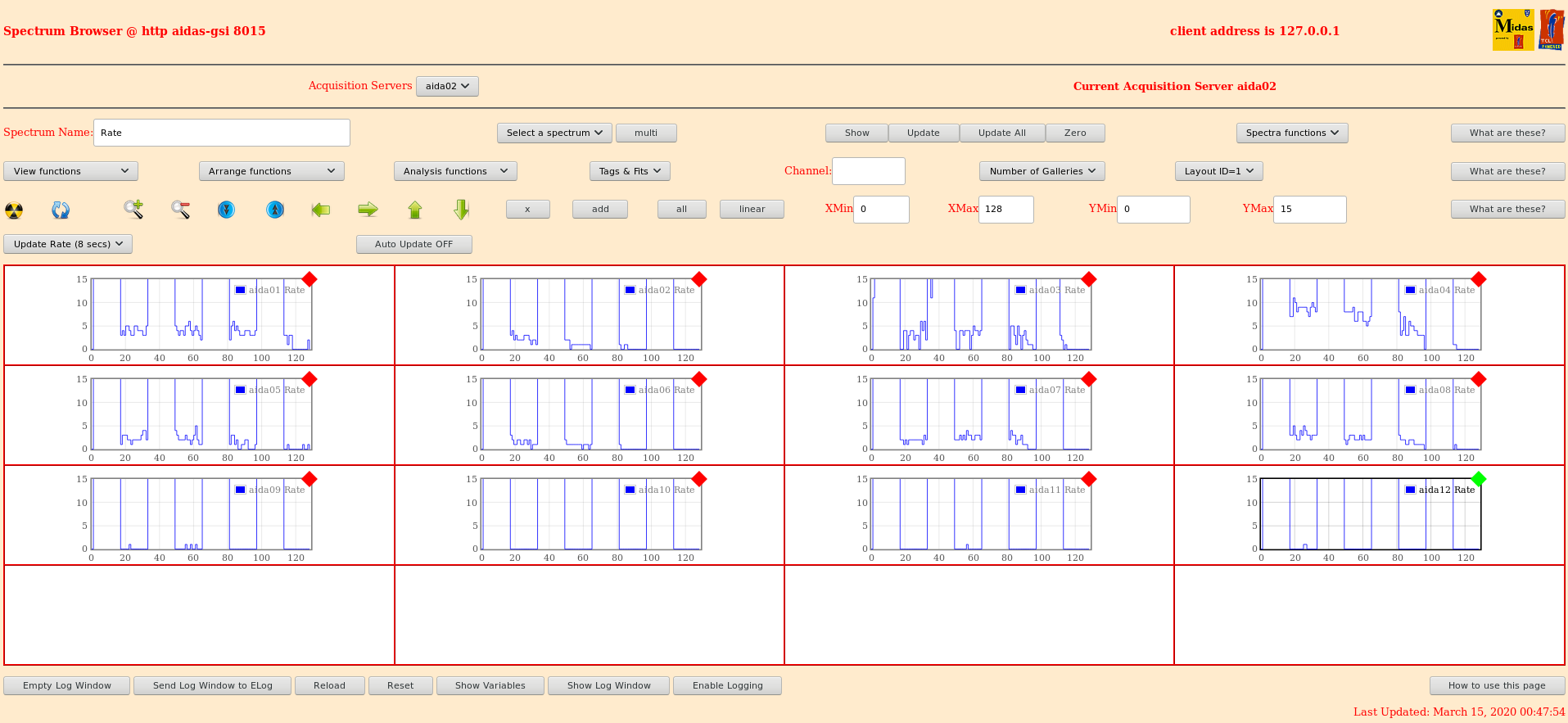

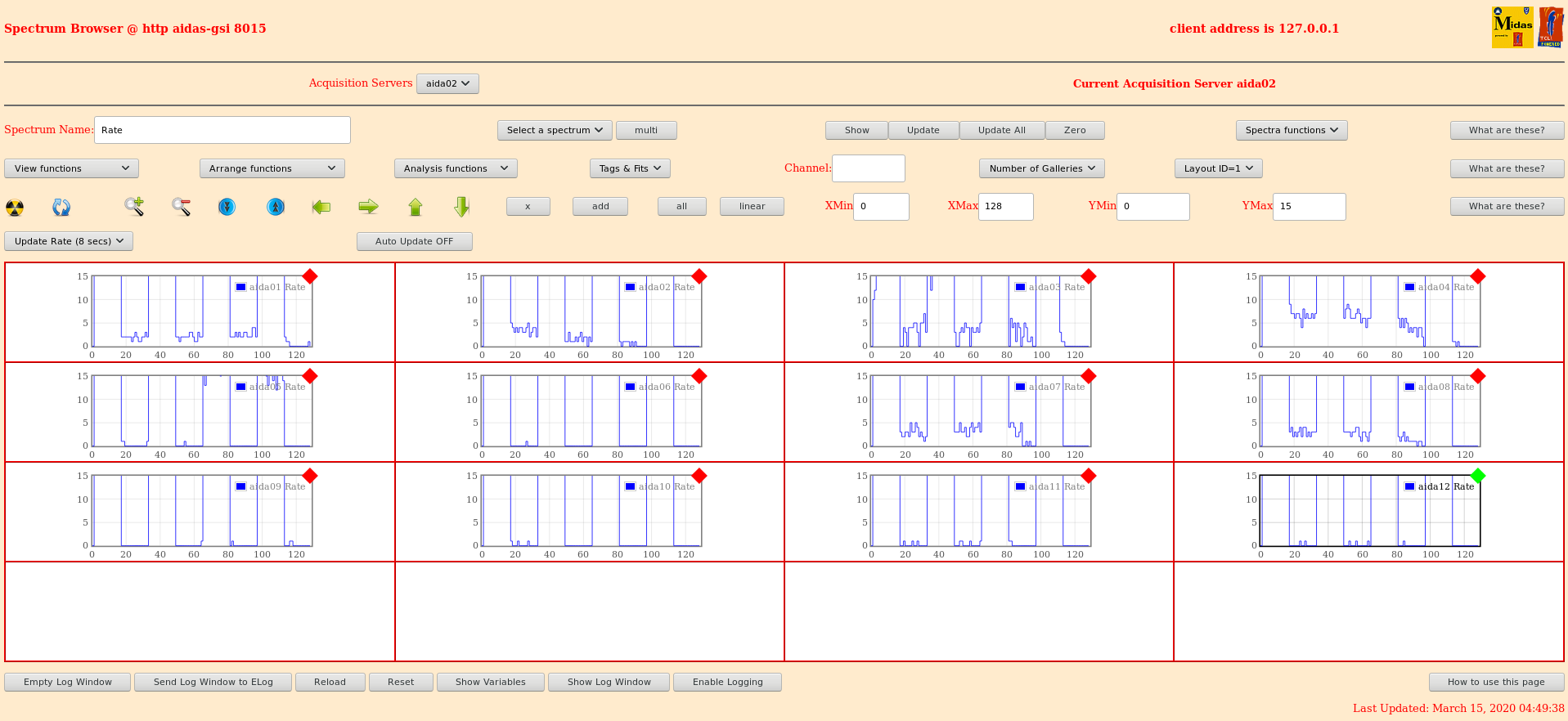

| Attachment 8: 18-04-2021_10pm_SpecRate.png

|

|

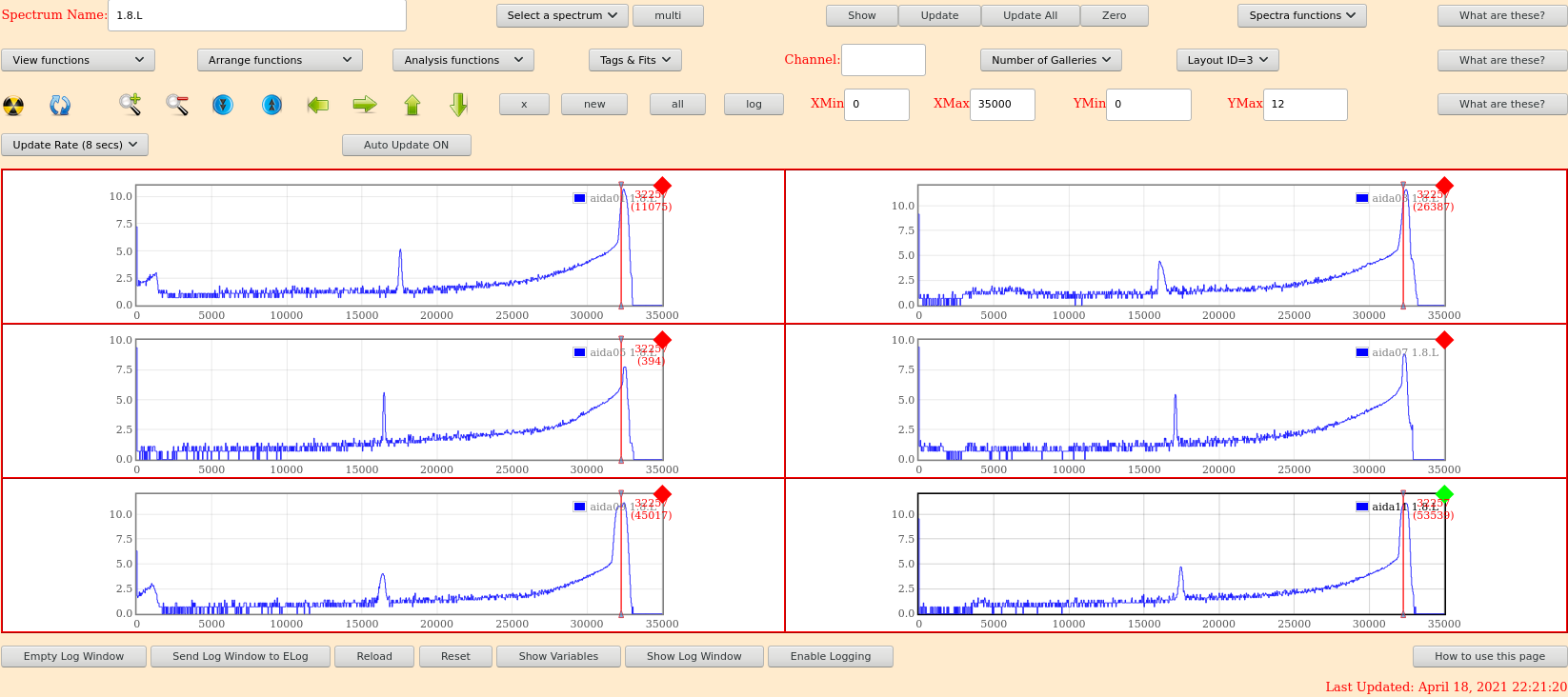

| Attachment 9: 18-04-2021_10pm_Spec1-8H.png

|

|

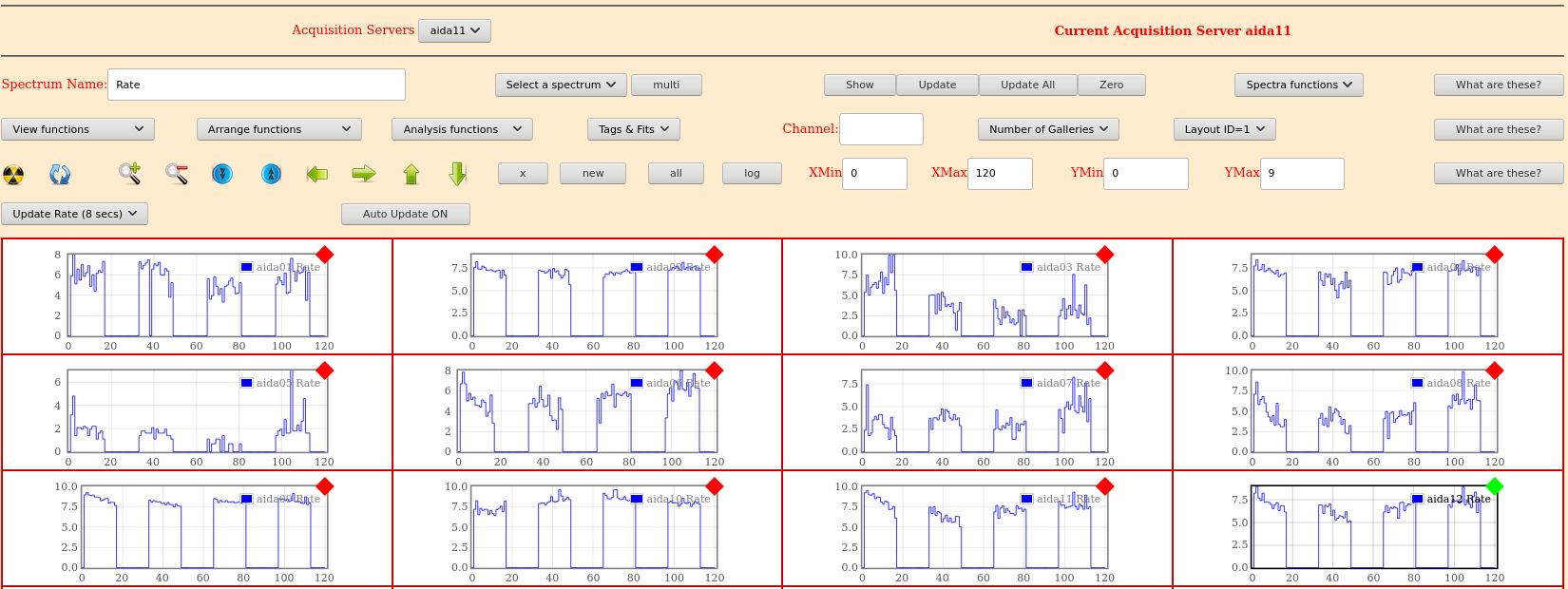

| Attachment 10: 18-04-2021_10pm_Spec1-8HlayoutID6.png

|

|

| Attachment 11: 18-04-2021_10pm_Spec1-8L.png

|

|

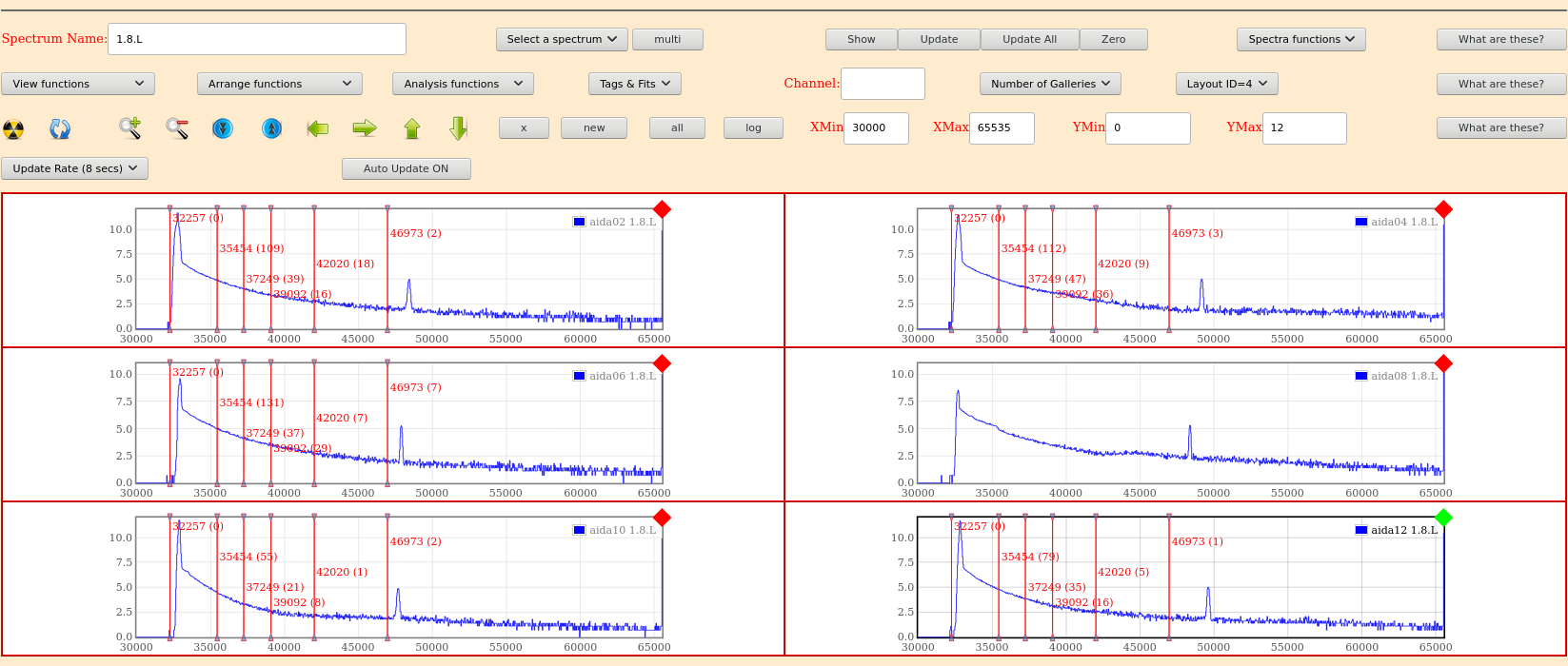

| Attachment 12: 18-04-2021_10pm_Spec1-8L_layoutid4.png

|

|

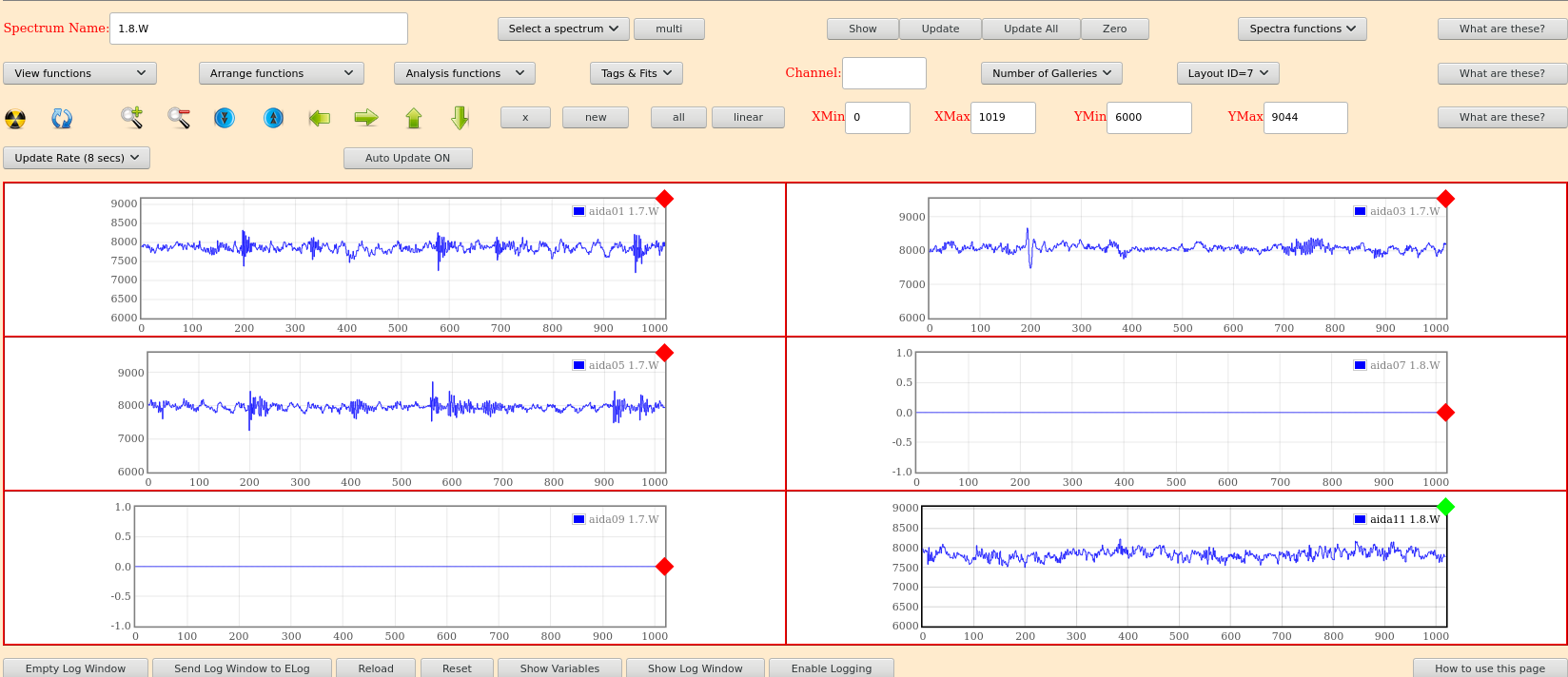

| Attachment 13: 18-04-2021_10pm_Spec1-8W.png

|

|

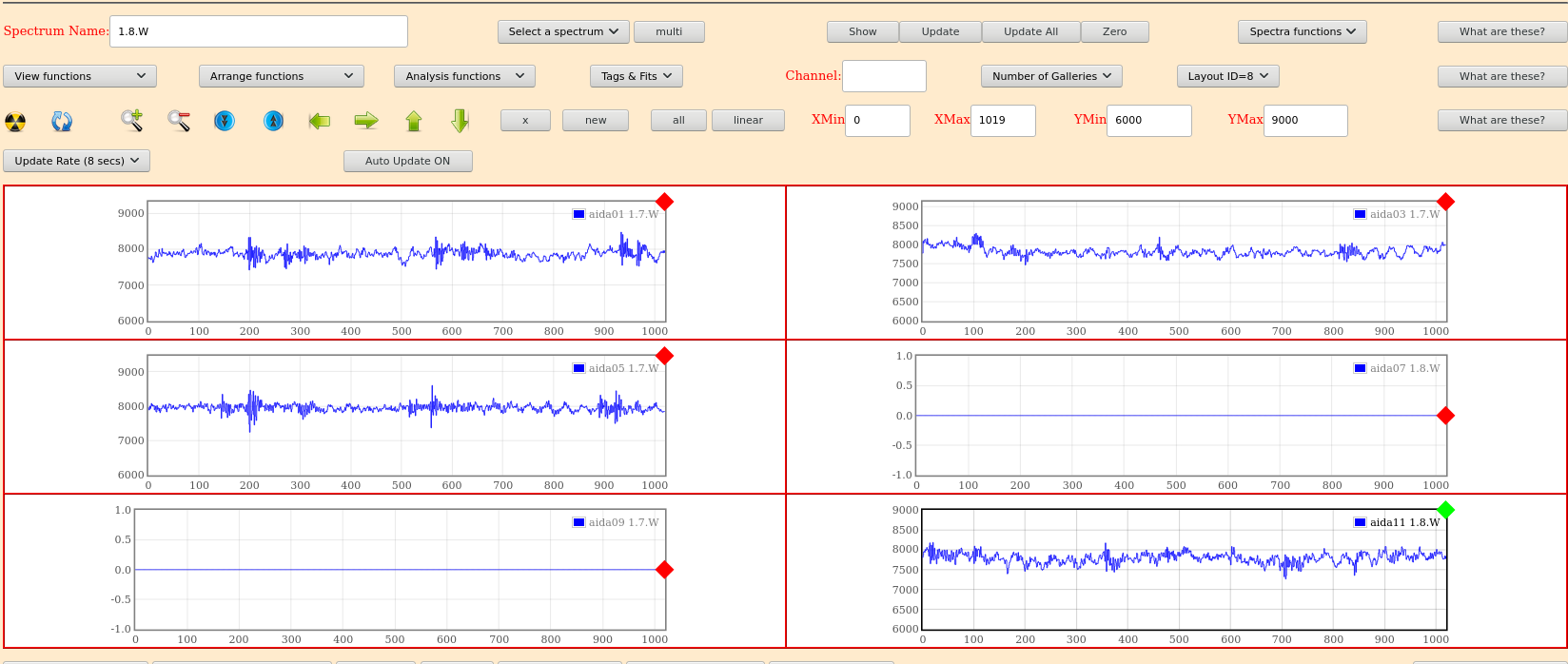

| Attachment 14: 18-04-2021_10pm_SpecLayoutID8.png

|

|

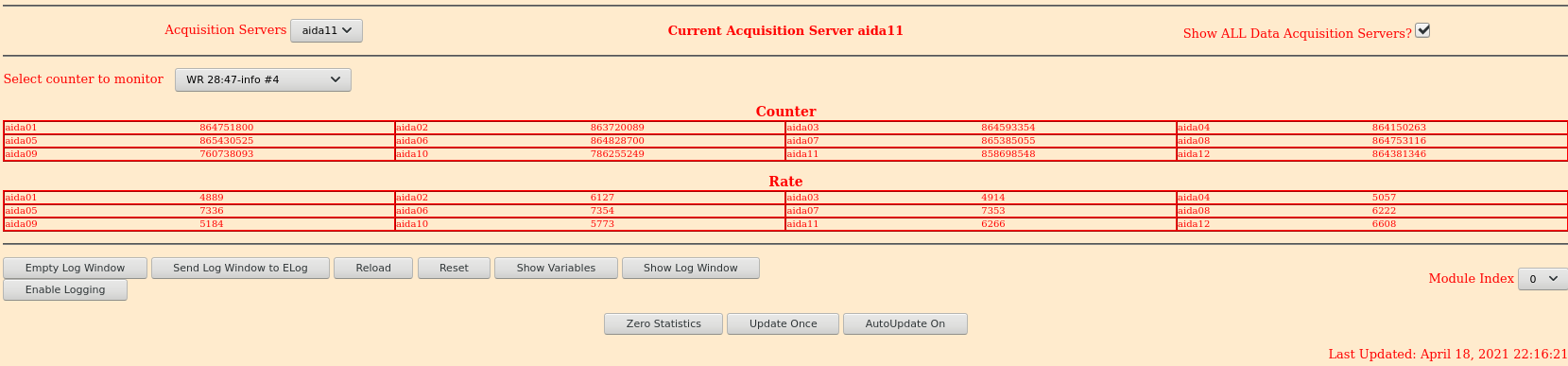

| Attachment 15: 18-04-2021_10pm_WR28-47.png

|

|

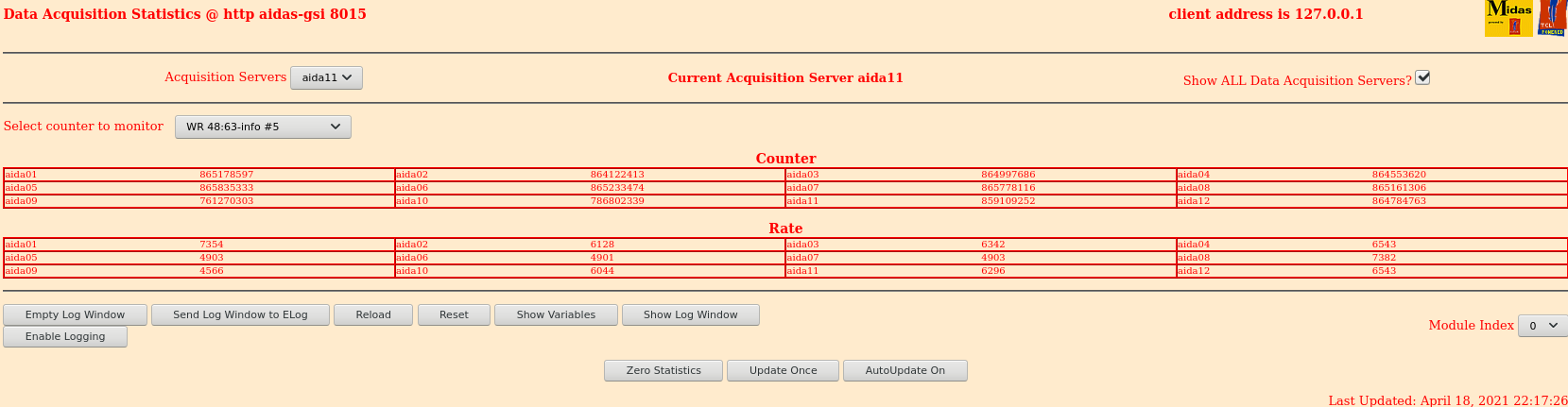

| Attachment 16: 18-04-2021_10pm_WR48-63.png

|

|

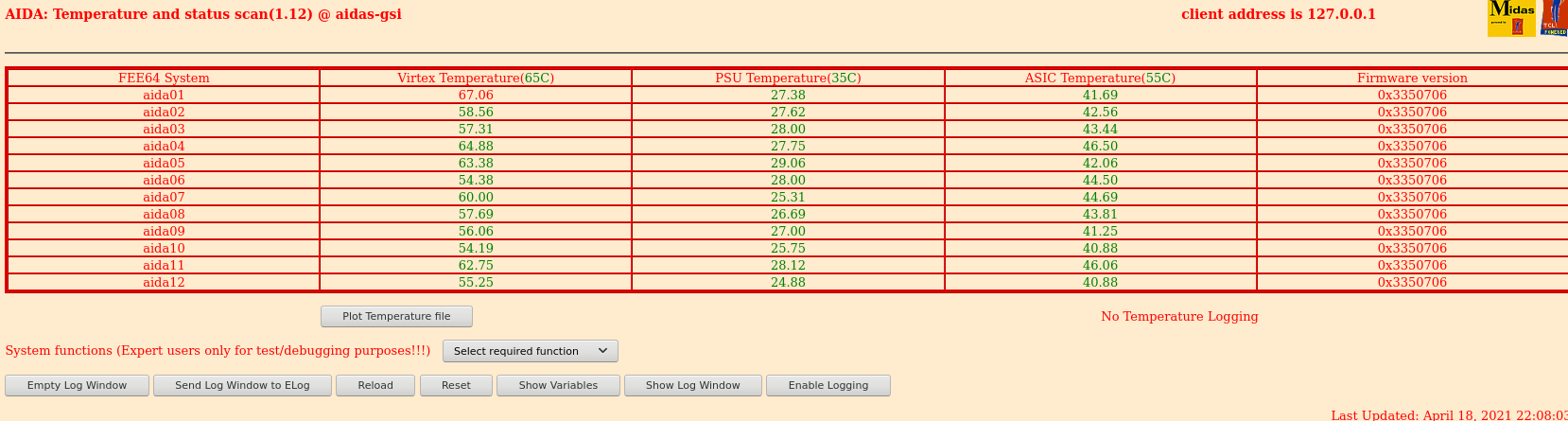

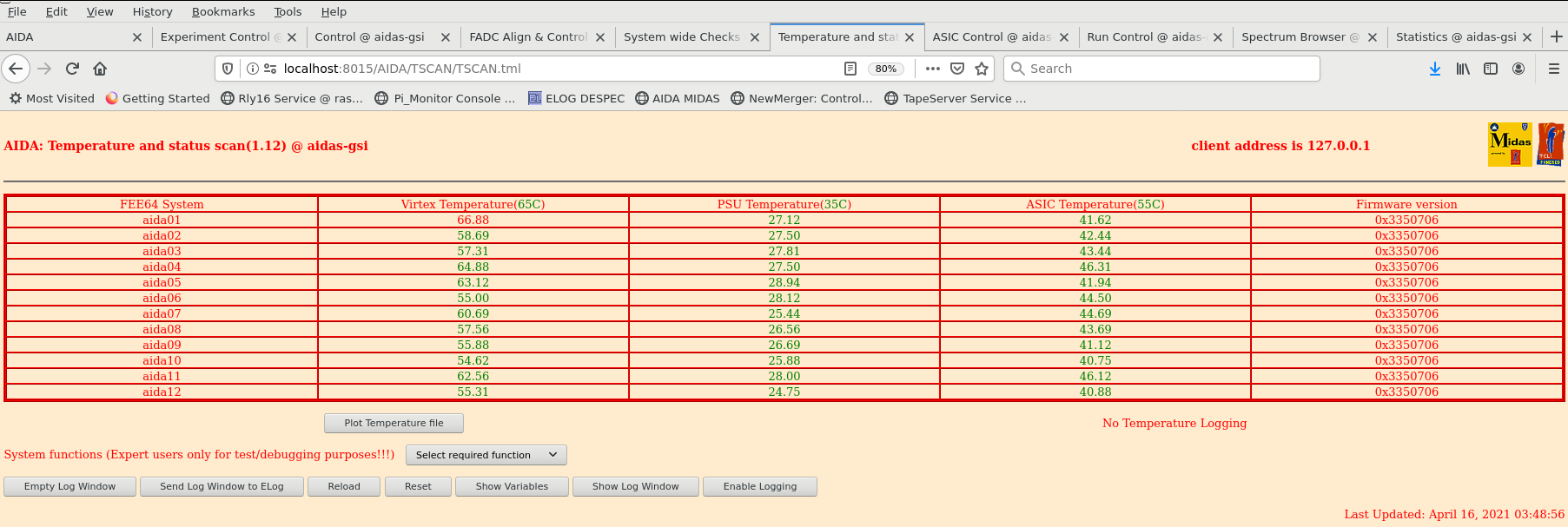

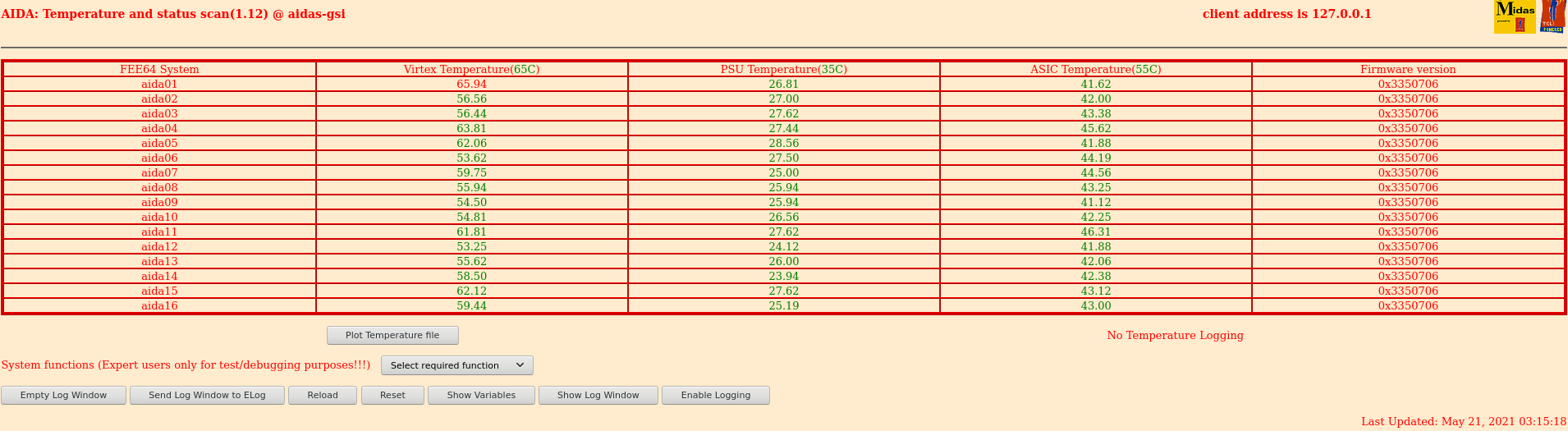

| Attachment 17: 18-04-2021_10pm_temp.png

|

|

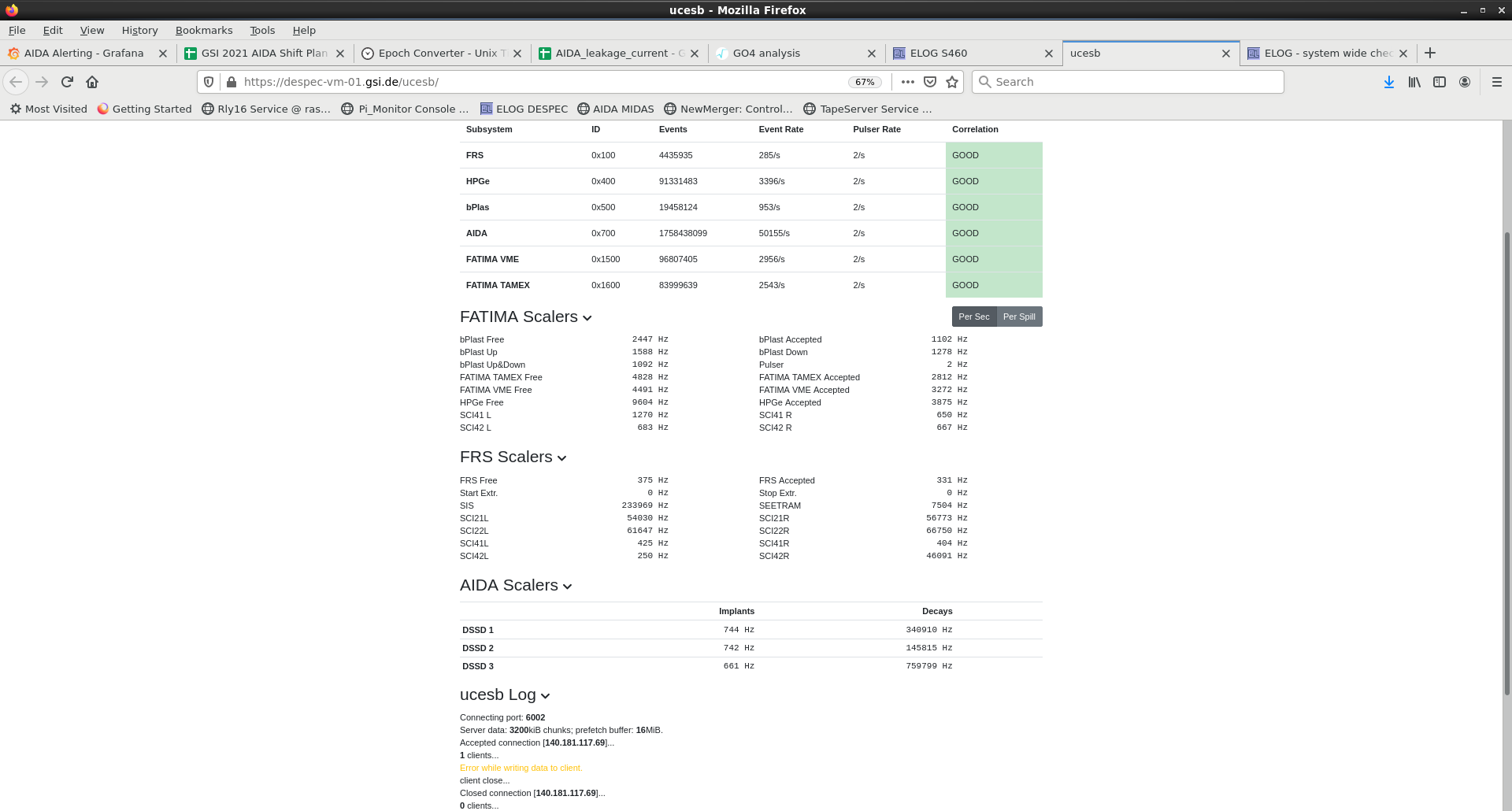

| Attachment 18: 18-04-2021_10pm_ucesb_monitor.png

|

|

| Attachment 19: 18-04-2021_10pm-AIDA_Alerting_-_Grafana.png

|

|

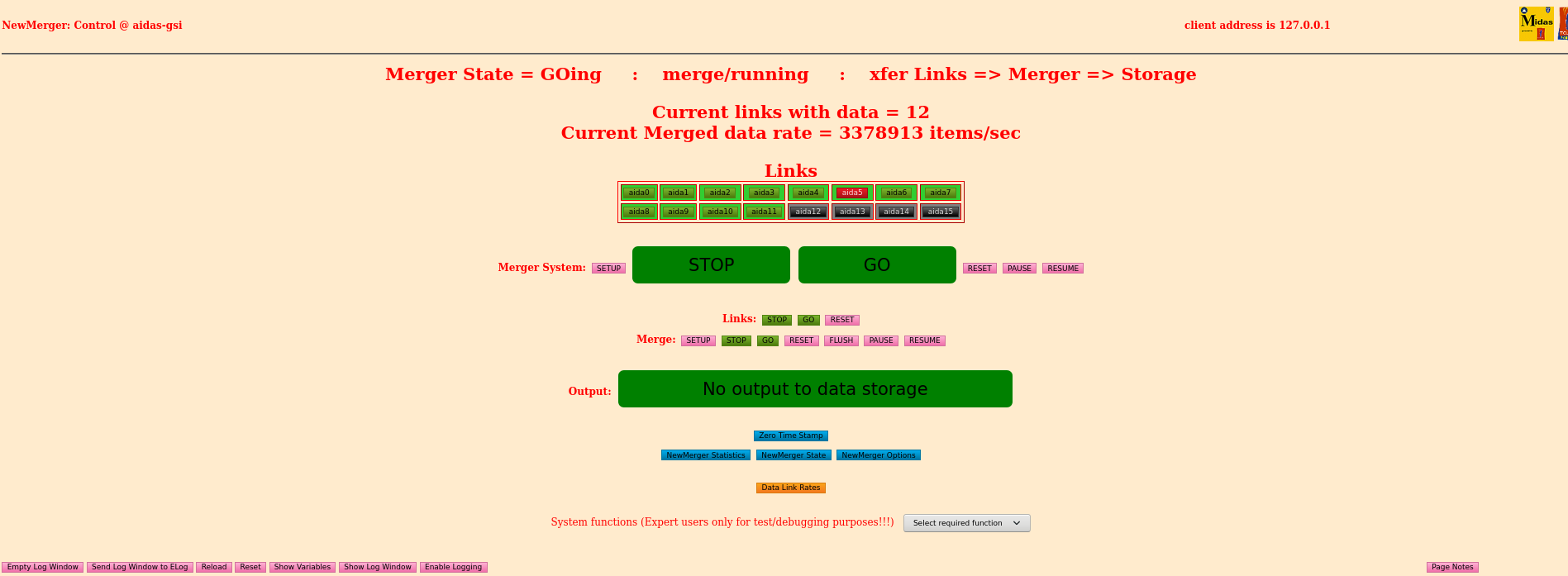

| Attachment 20: 18-04-2021_10pm_NewMerger.png

|

|

|

228

|

Fri Apr 16 05:13:09 2021 |

ML | system wide checks |

system wide checks:

Done around 4am.

#################################

To be noted:

-1- White rabbit and FPGA checks failed for 1 FEE and passed for 11

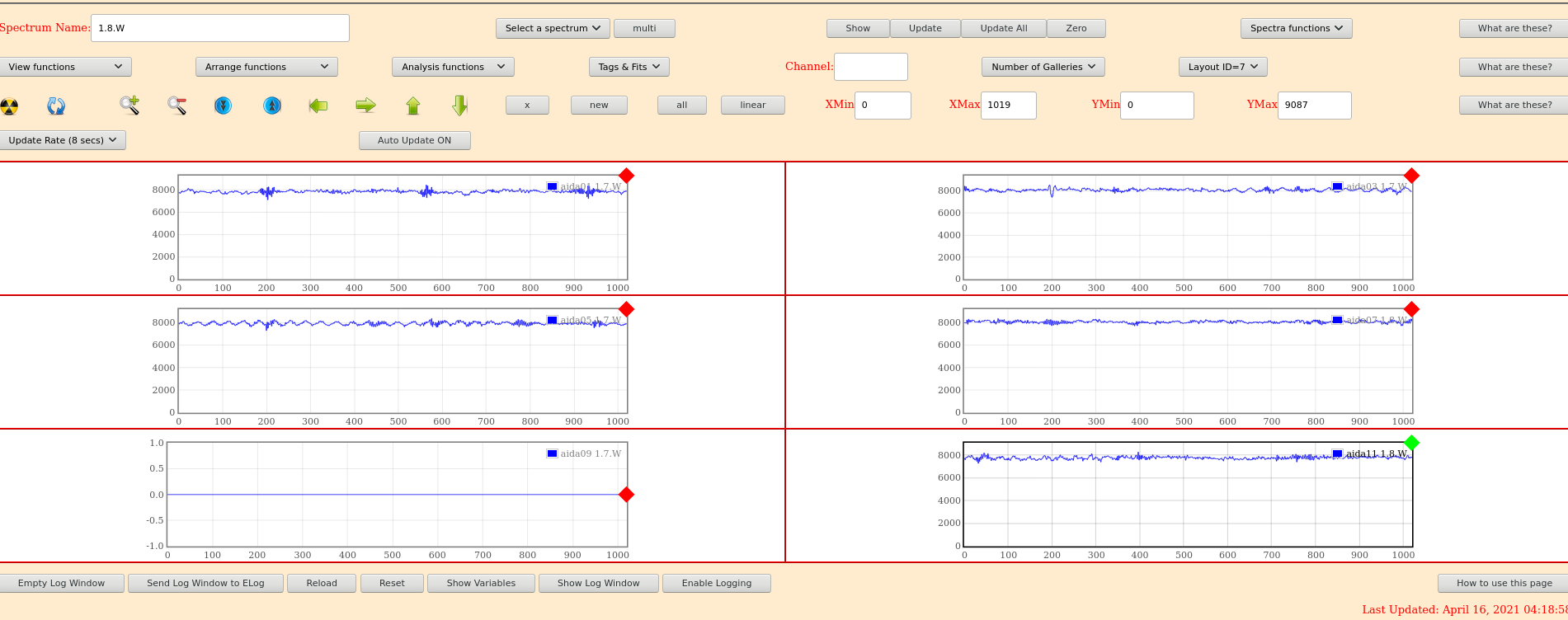

-2- No waveform for AIDA09 in 1.8.L spectrum

-3- AIDA 7 is red in the NewMerger control window (?)

#################################

Details:

Clock status test result: Passed 12, Failed 0

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

Calibration test result: Passed 12, Failed 0

White Rabbit checks:

Base Current Difference

aida07 fault 0xfa8c : 0xfb37 : 171

White Rabbit error counter test result: Passed 11, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

FPGA timestamp check:

Base Current Difference

aida07 fault 0x0 : 0xe : 14

FPGA Timestamp error counter test result: Passed 11, Failed 1

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

Memory check:

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 45 9 7 3 4 3 2 3 3 3 6 : 36940

aida02 : 23 9 6 7 4 3 2 3 3 3 6 : 36964

aida03 : 40 8 5 4 5 3 2 3 3 3 6 : 36976

aida04 : 37 13 7 3 4 3 4 2 3 3 6 : 36940

aida05 : 35 11 6 3 4 4 2 3 2 4 6 : 38052

aida06 : 42 8 2 3 4 4 2 3 3 3 6 : 36968

aida07 : 42 10 5 5 5 3 2 3 3 3 6 : 37032

aida08 : 40 8 1 6 3 4 2 3 3 3 6 : 36976

aida09 : 18 18 14 8 5 5 5 4 3 2 6 : 36728

aida10 : 1 8 9 6 3 3 1 4 2 3 6 : 36052

aida11 : 24 11 14 6 2 2 4 2 3 3 6 : 36824

aida12 : 17 13 8 5 5 4 2 3 2 3 6 : 36108 |

| Attachment 1: 16-04-2021_3h45am_HV.png

|

|

| Attachment 2: 48_temperature.png

|

|

| Attachment 3: 16-04-2021_3h51_StatGoodEvt.png

|

|

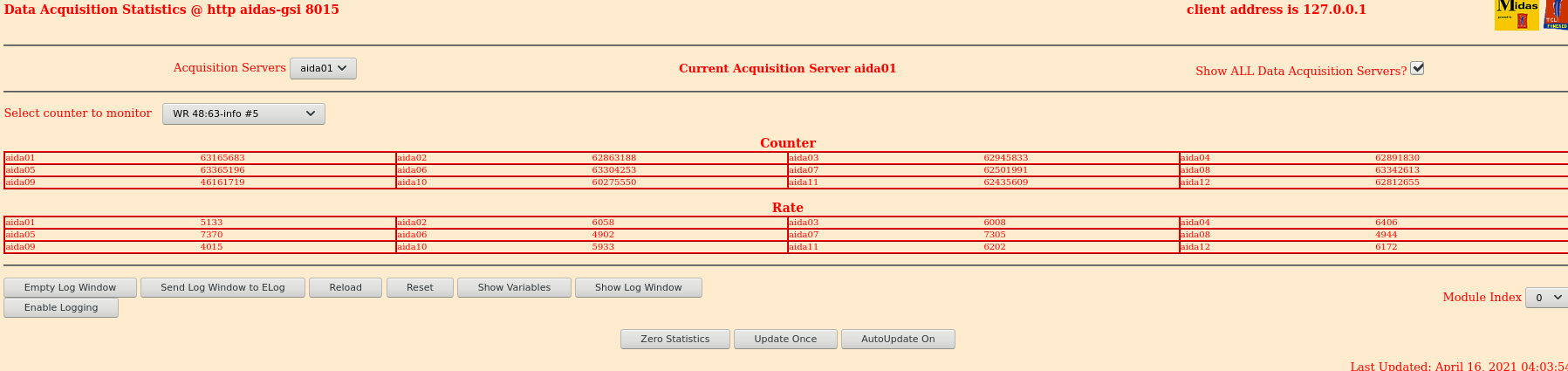

| Attachment 4: 16-04-2021_3h53_StatADCdataItem.png

|

|

| Attachment 5: 16-04-2021_3h58_StatWR#4.png

|

|

| Attachment 6: 16-04-2021_4h04_StatWR#5.png

|

|

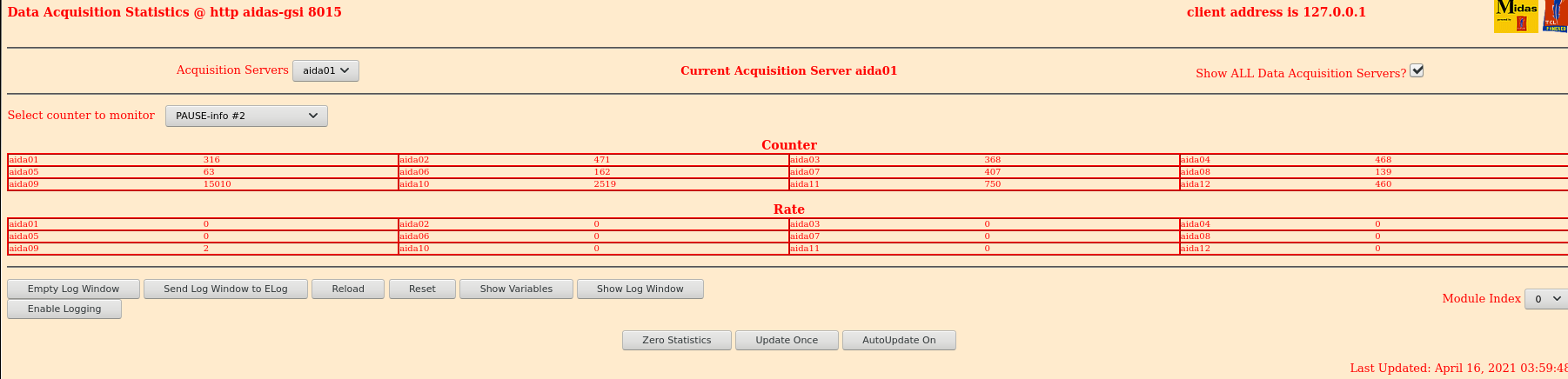

| Attachment 7: 16-04-2021_3h59_StatPause#2.png

|

|

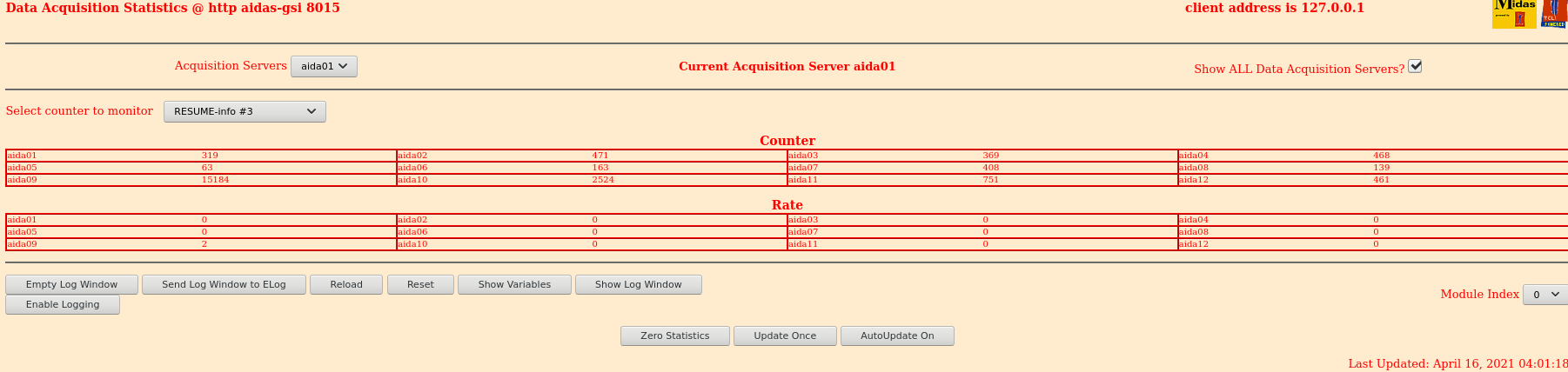

| Attachment 8: 16-04-2021_4h01_StatResume#3.png

|

|

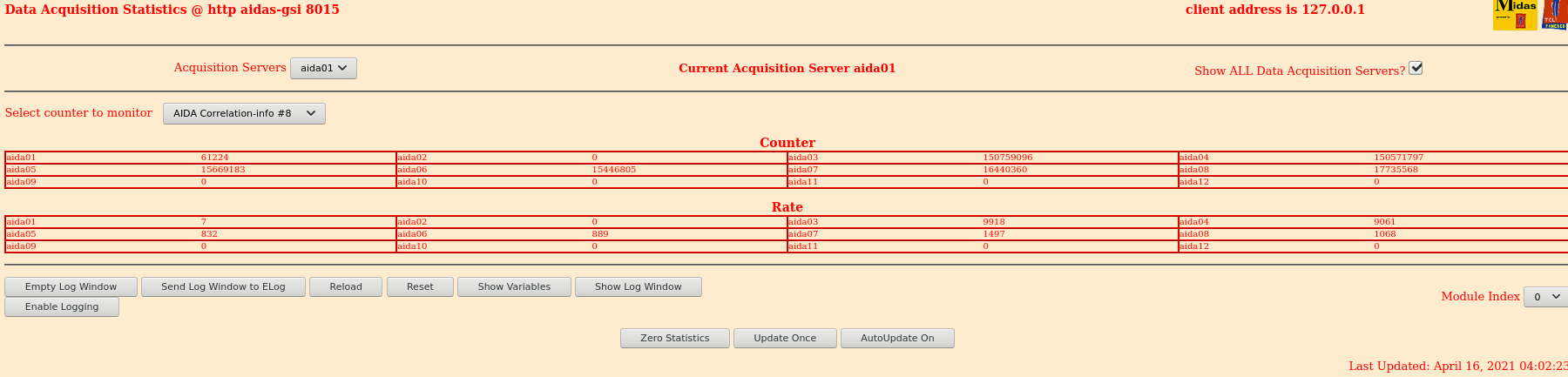

| Attachment 9: 16-04-2021_4h02_StatCorrelation#8.png

|

|

| Attachment 10: 16-04-2021_4h06_SpecRate.png

|

|

| Attachment 11: 16-04-2021_4h08_SpecRate2.png

|

|

| Attachment 12: 16-04-2021_4h17_Spec1.8L.png

|

|

| Attachment 13: 16-04-2021_4h29_Spec1.8L_id4.png

|

|

| Attachment 14: 16-04-2021_4h20_Spec1.8W_id7.png

|

|

| Attachment 15: 25_Spec1.8W_id8.png

|

|

| Attachment 16: 16-04-2021_4h48_NewMergerControl.png

|

|

|

269

|

Sat Apr 24 01:44:09 2021 |

ML | system wide checks |

system wide checks:

Clock status:

FEE64 module aida06 global clocks failed, 6

Clock status test result: Passed 11, Failed 1

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

ADC calibration:

FEE64 module aida06 failed

FEE64 module aida07 failed

FEE64 module aida12 failed

Calibration test result: Passed 9, Failed 3

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

White Rabbit

Base Current Difference

aida06 fault 0x679f : 0x67a4 : 5

White Rabbit error counter test result: Passed 11, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

FPGA timestamp error page not working !!

Memory information:

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 19 15 4 6 4 3 2 4 2 3 6 : 36420

aida02 : 36 25 24 6 0 4 2 3 2 3 4 : 28056

aida03 : 17 7 4 3 3 5 2 2 3 3 6 : 36444

aida04 : 4 5 4 5 3 4 2 3 3 3 6 : 36824

aida05 : 23 9 4 2 3 3 1 3 3 3 6 : 36452

aida06 : 26 8 5 1 3 4 2 2 3 3 6 : 36312

aida07 : 21 9 3 3 4 5 1 2 3 3 6 : 36268

aida08 : 27 9 2 2 2 4 1 3 3 3 6 : 36500

aida09 : 13 4 3 3 1 2 4 2 3 3 6 : 36388

aida10 : 1 10 0 3 1 2 3 3 2 3 6 : 35572

aida11 : 23 13 8 3 3 4 3 3 2 3 6 : 36196

aida12 : 19 7 4 3 2 3 2 3 3 3 6 : 36644

|

| Attachment 1: 24-04-2021_230am_AIDA_HV.png

|

|

| Attachment 2: 24-04-2021_230am_ucesbStat.png

|

|

| Attachment 3: 24-04-2021_230am_grafana.png

|

|

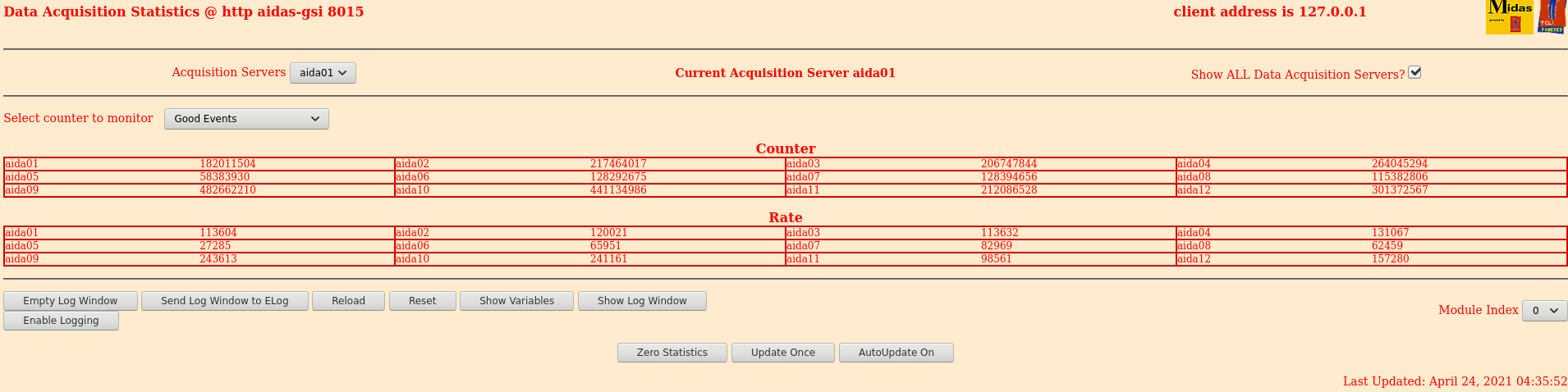

| Attachment 4: 24-04-2021_230am_AidaGoodEvent.png

|

|

| Attachment 5: 24-04-2021_230am_Correlation#8.png

|

|

| Attachment 6: 24-04-2021_230am_RESUME#3.png

|

|

| Attachment 7: 24-04-2021_230am_PAUSE#2.png

|

|

|

270

|

Sat Apr 24 03:13:05 2021 |

ML | AIDA DAQ Reset |

AIDA PC crashe completely at ~3:30am CET.

Tom was called and he Restarted the AIDA system at ~4am with Run 52.

Not sure what cause the crash but AnyDesk remote connection was suddenly lost and once reconnected all Terminal sessions were gone.

|

|

272

|

Sat Apr 24 03:32:11 2021 |

ML | quick checks |

Quick system checks after crash

Temperature ok.

Still cannot connect remotely to /ucesb with my gsi web login and password (?).

Clock status test result: Passed 12, Failed 0

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

Calibration test result: Passed 12, Failed 0

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

Base Current Difference

aida05 fault 0x31a2 : 0x31a2 : 0

aida05 : WR status 0x10

White Rabbit error counter test result: Passed 11, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 9 3 4 2 3 2 1 4 2 3 7 : 39804

aida02 : 29 4 2 3 0 3 1 4 2 3 7 : 39828

aida03 : 20 6 1 2 2 3 1 4 2 3 7 : 39888

aida04 : 19 5 4 2 1 3 1 4 2 3 7 : 39860

aida05 : 27 5 4 1 2 3 2 3 1 4 7 : 40692

aida06 : 17 10 3 2 1 3 1 4 2 3 7 : 39876

aida07 : 22 7 2 2 2 3 1 4 2 3 7 : 39920

aida08 : 12 6 5 1 3 2 1 4 2 3 7 : 39824

aida09 : 0 9 1 3 1 3 1 4 2 3 7 : 39800

aida10 : 2 2 2 3 3 2 3 2 2 3 7 : 39256

aida11 : 21 7 4 3 0 3 2 3 2 3 7 : 39596

aida12 : 18 8 3 0 2 3 2 3 2 3 7 : 39608

|

| Attachment 1: 24-04-2021_430am_GoodEvent.png

|

|

|

273

|

Sat Apr 24 04:07:23 2021 |

ML | ucesb scalers |

ucesb is back - see attachment |

| Attachment 1: 24-04-2021_5am_ucesb.png

|

|

|

274

|

Sat Apr 24 04:50:01 2021 |

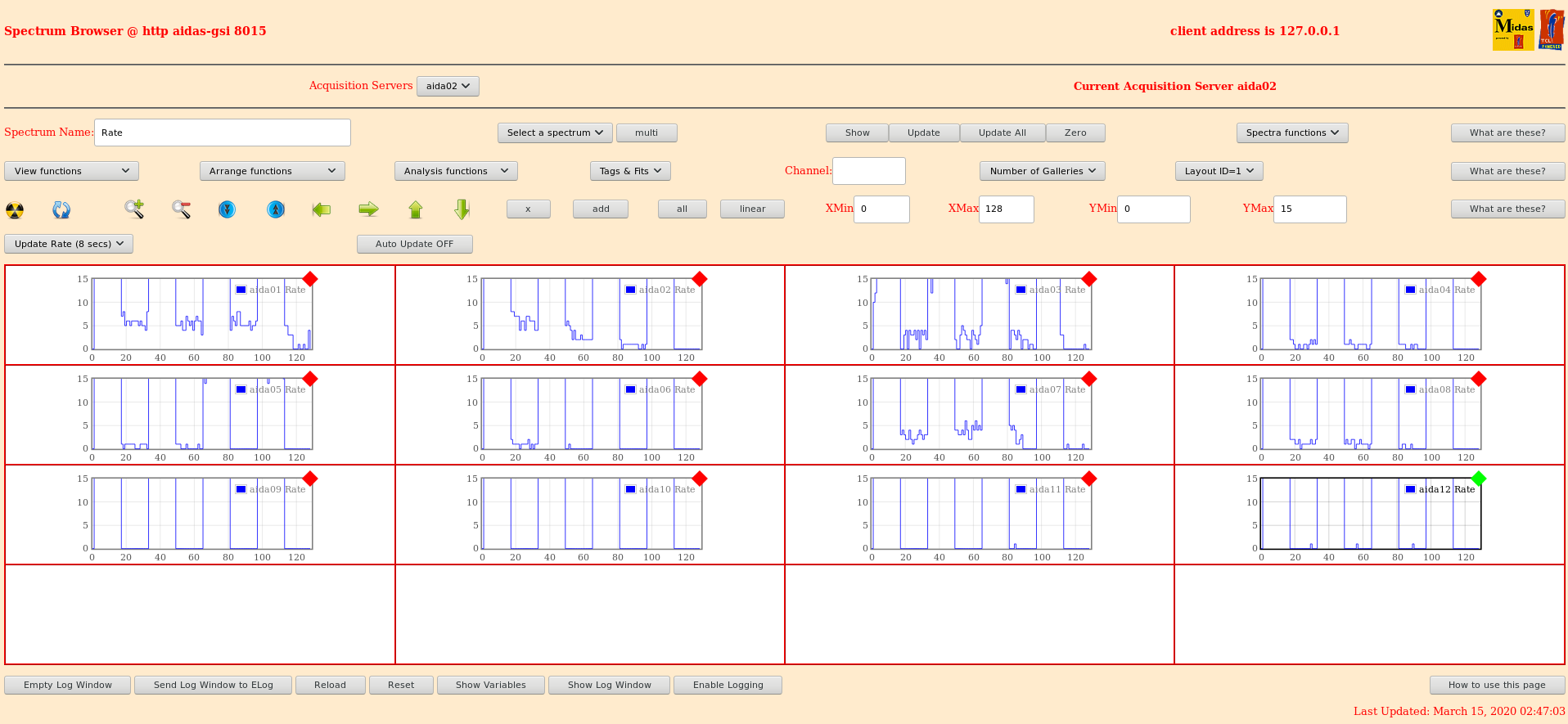

ML | Spectra |

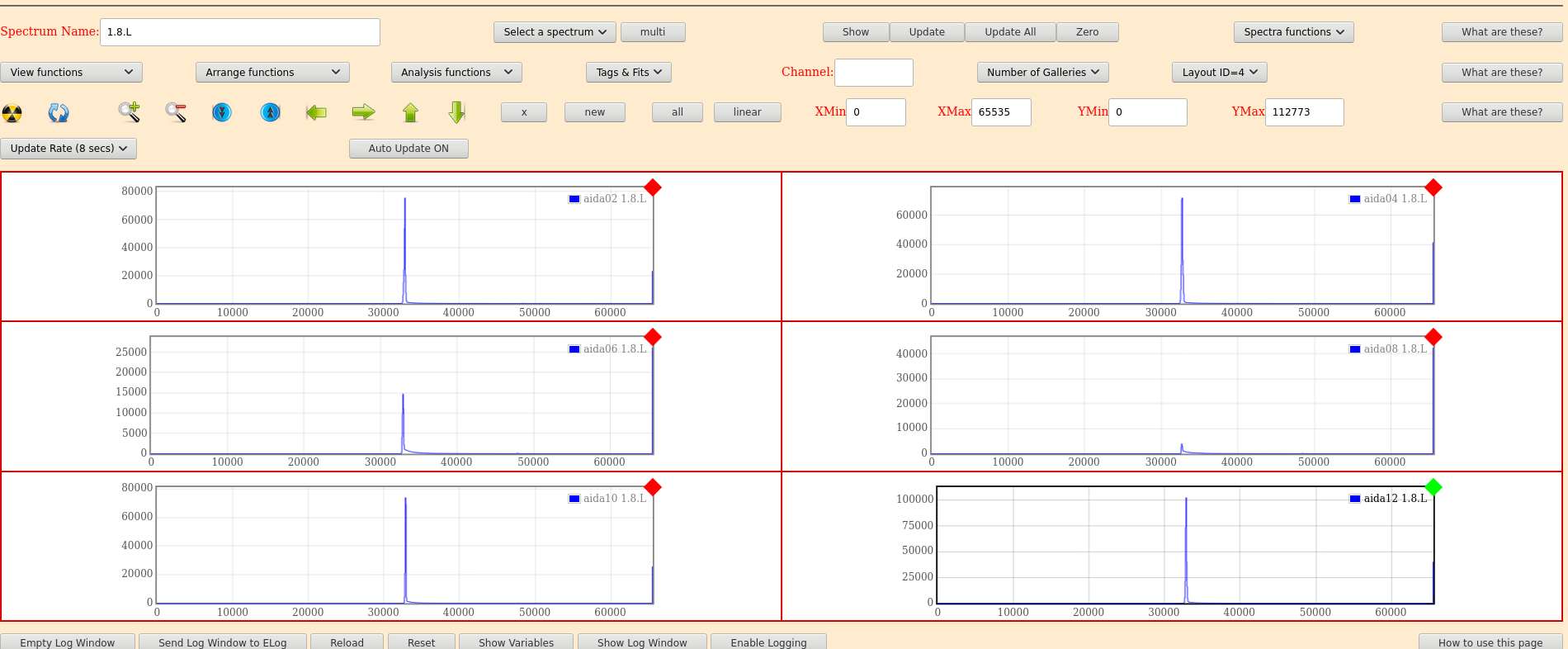

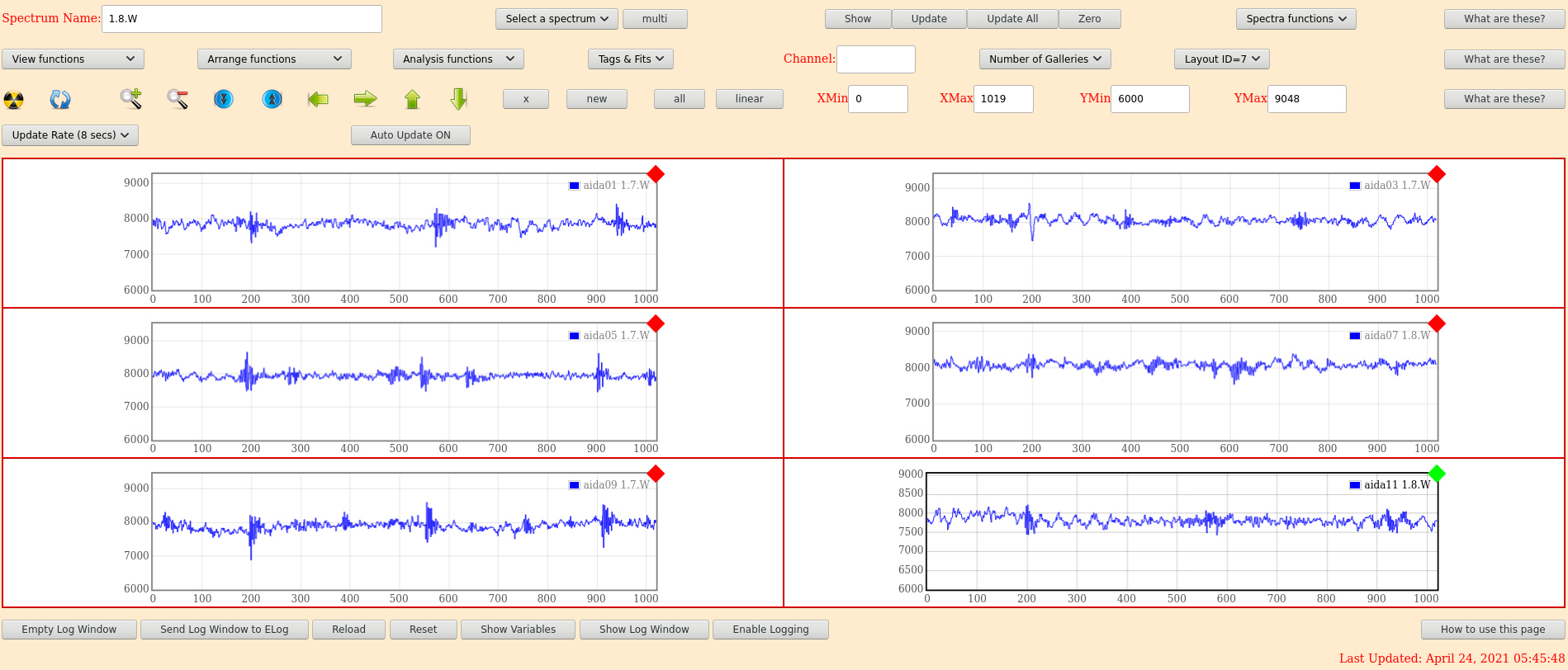

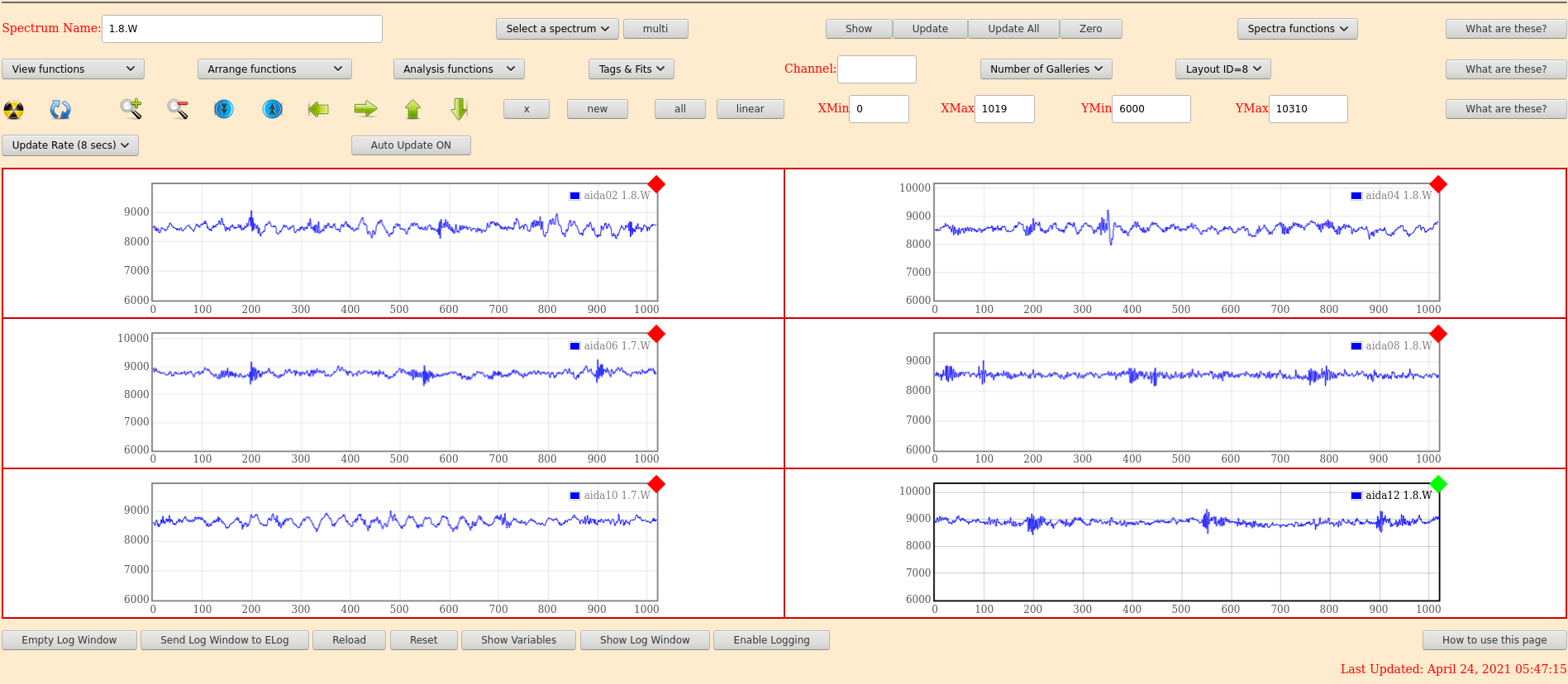

Some screenshot of spectra attached |

| Attachment 1: 24-04-2021_540am_SpecLayoutId3.png

|

|

| Attachment 2: 24-04-2021_540am_SpecLayId4.png

|

|

| Attachment 3: 24-04-2021_540am_SpecLayId5.png

|

|

| Attachment 4: 24-04-2021_540am_SpecLayId6.png

|

|

| Attachment 5: 24-04-2021_540am_SpecLayId7.png

|

|

| Attachment 6: 24-04-2021_540am_SpecLayId8.png

|

|

| Attachment 7: 24-04-2021_540am_SpecLayId1.png

|

|

| Attachment 8: 24-04-2021_540am_SpecLayId2.png

|

|

|

275

|

Sat Apr 24 05:17:51 2021 |

ML | End of beam |

Beam has now stopped (end of expriment) and background measurements starts. |

|

339

|

Fri May 21 02:17:47 2021 |

ML | system wide checks |

Wide check at 3am -

All fine.

Same output as at the beginning of the shift (see my previous entry) and attachments.

|

| Attachment 1: 2021-05-21_3h05_Leakcurrent.png

|

|

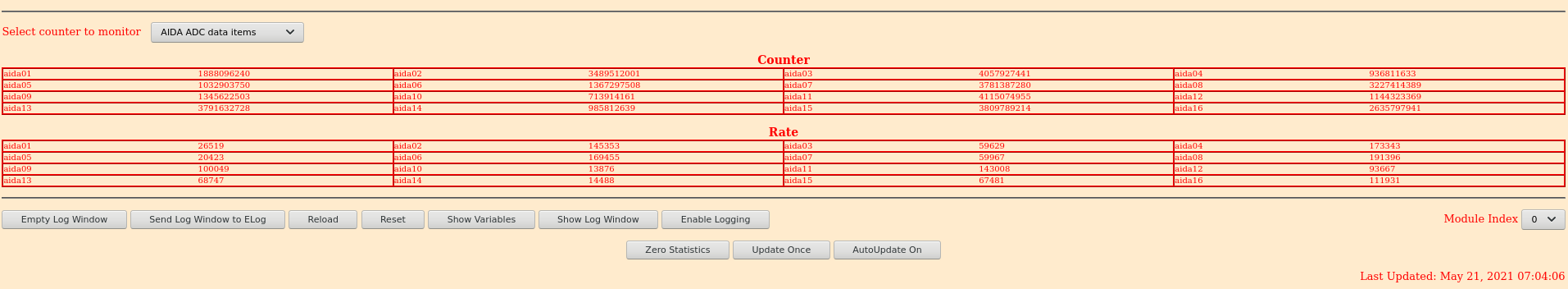

| Attachment 2: 2021-05-21_3h05_stats_adcItem.png

|

|

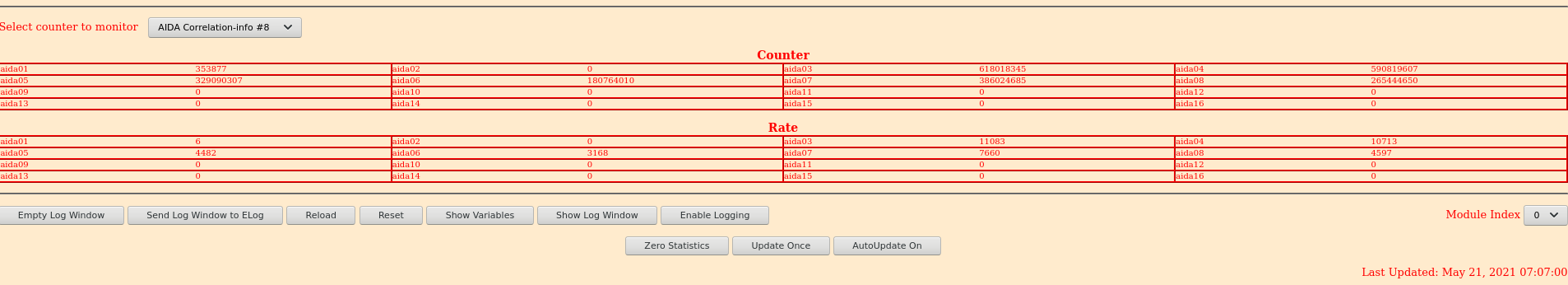

| Attachment 3: 2021-05-21_3h05_stats_Correlation.png

|

|

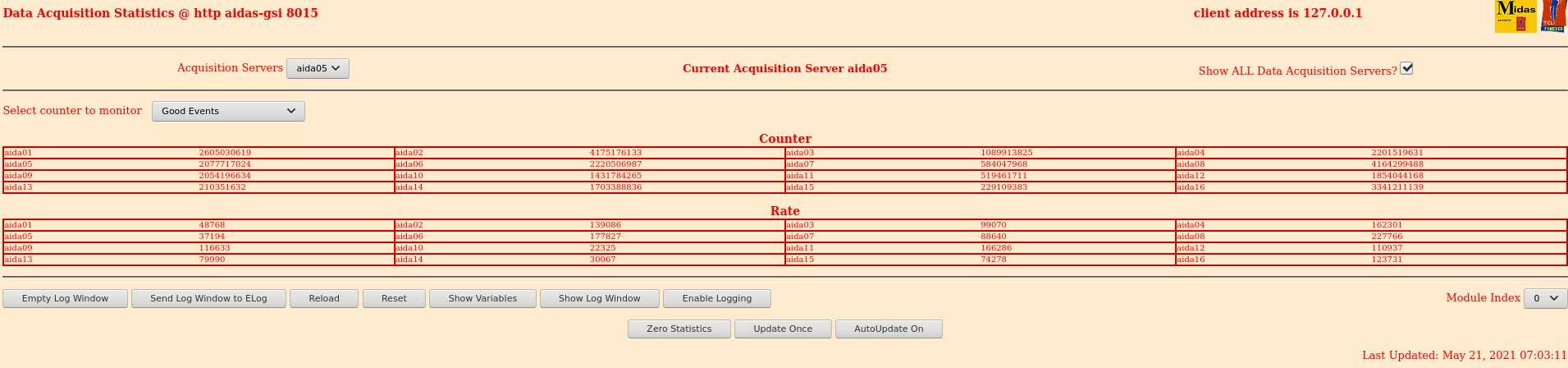

| Attachment 4: 2021-05-21_3h05_stats_GoodEvents.png

|

|

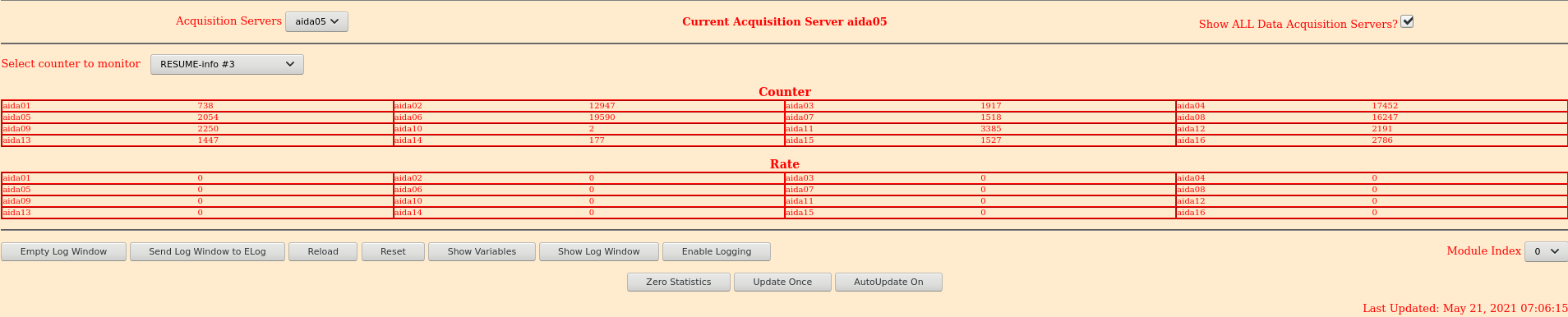

| Attachment 5: 2021-05-21_3h05_stats_PAUSE.png

|

|

| Attachment 6: 2021-05-21_3h05_stats_RESUME.png

|

|

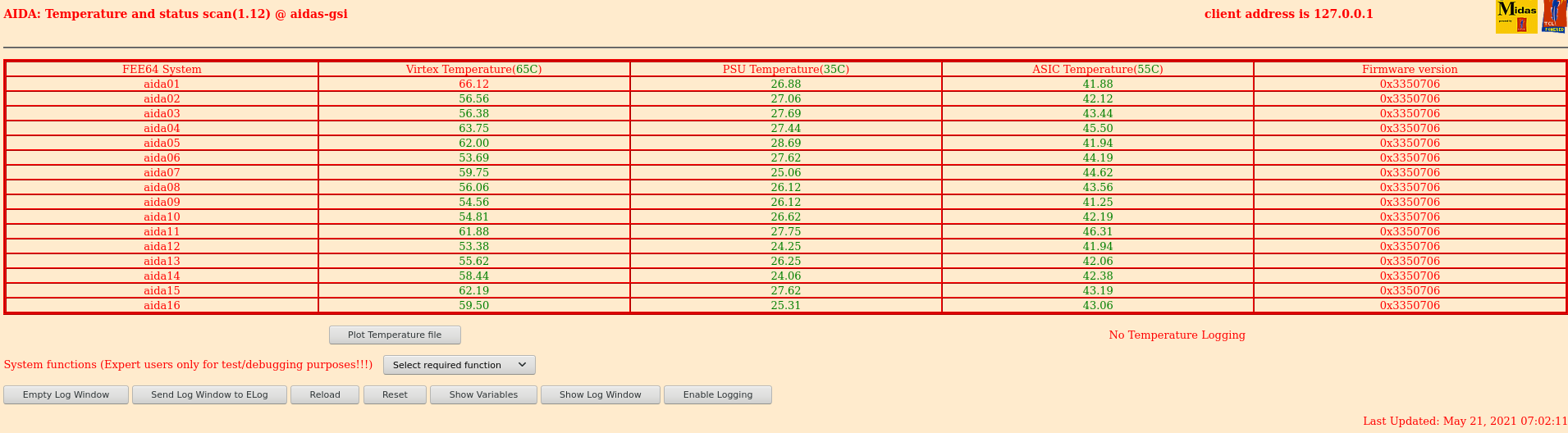

| Attachment 7: 2021-05-21_3h05_temperature.png

|

|

| Attachment 8: 2021-05-21_3h05_ucesb.png

|

|

| Attachment 9: 2021-05-21_3h05_aidaGrafana.png

|

|

|

340

|

Fri May 21 06:09:28 2021 |

ML | system wide checks |

System wide checks at 7am CET

All seems fine, nothing significant to report

Slight increase of dead time noted in FEE 3, 5 and 7.

-----

Clock status test result: Passed 16, Failed 0

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

-----

ADC calibration

FEE64 module aida01 failed

FEE64 module aida02 failed

FEE64 module aida03 failed

FEE64 module aida04 failed

FEE64 module aida05 failed

FEE64 module aida06 failed

FEE64 module aida07 failed

FEE64 module aida08 failed

FEE64 module aida09 failed

FEE64 module aida10 failed

FEE64 module aida11 failed

FEE64 module aida12 failed

FEE64 module aida13 failed

FEE64 module aida14 failed

FEE64 module aida15 failed

FEE64 module aida16 failed

Calibration test result: Passed 0, Failed 16

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

-----

White Rabbit:

Base Current Difference

aida05 fault 0x500 : 0x56e : 110

White Rabbit error counter test result: Passed 15, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

-----

FPGA Timestamp error counter test result: Passed 16, Failed 0

If any of these counts are reported as in error

The ASIC readout system has detected a timeslip.

That is the timestamp read from the time FIFO is not younger than the last

-----

Returned 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 23 5 6 5 0 4 1 3 3 3 6 : 36484

aida02 : 10 3 3 2 3 2 2 2 3 3 6 : 35952

aida03 : 2 5 1 4 5 2 2 3 3 3 6 : 36608

aida04 : 1 3 4 0 4 3 2 3 3 3 6 : 36572

aida05 : 19 9 3 2 2 3 1 3 4 3 6 : 37380

aida06 : 13 11 1 5 3 4 4 2 3 3 6 : 36860

aida07 : 12 2 4 3 3 2 1 3 2 2 7 : 37280

aida08 : 25 5 7 1 1 3 3 3 3 3 6 : 36828

aida09 : 22 5 6 4 1 3 2 3 3 3 6 : 36640

aida10 : 23 8 6 3 2 3 2 2 2 4 6 : 37212

aida11 : 24 14 7 3 3 2 3 3 3 3 6 : 36960

aida12 : 16 10 5 3 1 2 1 2 4 3 6 : 36736

aida13 : 23 6 4 2 2 3 2 3 3 3 6 : 36620

aida14 : 22 7 8 4 3 4 1 2 2 4 6 : 37200

aida15 : 10 12 9 2 1 3 1 3 3 3 6 : 36376

aida16 : 18 5 6 2 0 3 2 4 3 3 6 : 37008

|

| Attachment 1: 2021-05-21_7h00_LeakCurrent.png

|

|

| Attachment 2: 2021-05-21_7h00_Stats_GoodEvents.png

|

|

| Attachment 3: 2021-05-21_7h00_Stats_ADCitems.png

|

|

| Attachment 4: 2021-05-21_7h00_stats_Correlation.png

|

|

| Attachment 5: 2021-05-21_7h00_Stats_PAUSE.png

|

|

| Attachment 6: 2021-05-21_7h00_Stats_RESUME.png

|

|

| Attachment 7: 2021-05-21_7h00_temperature.png

|

|

| Attachment 8: 2021-05-21_7h00_ucesb.png

|

|

|

436

|

Fri May 13 00:50:16 2022 |

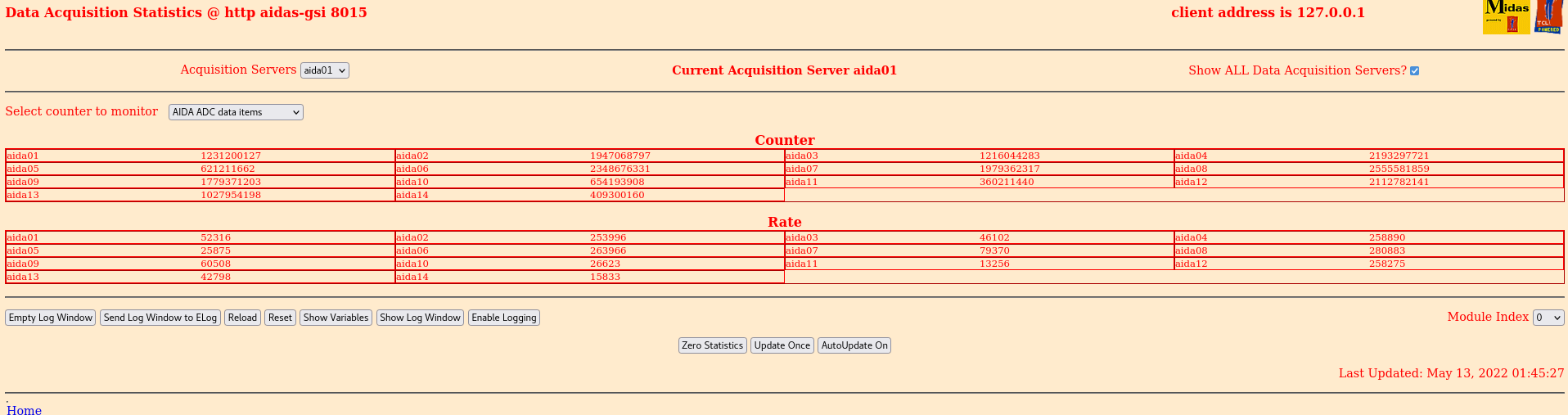

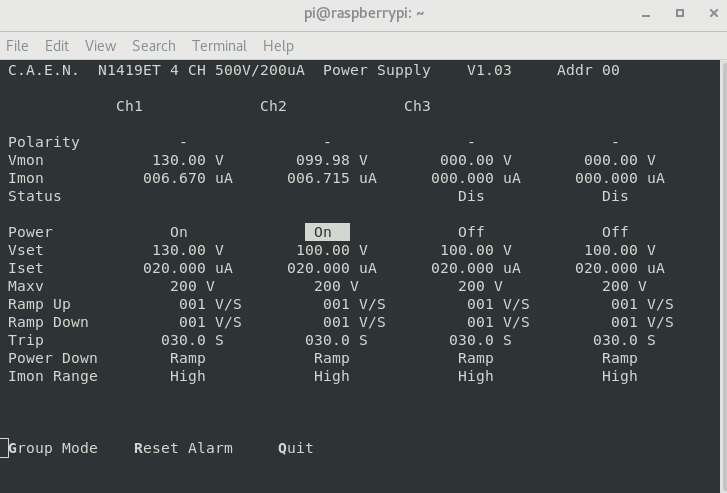

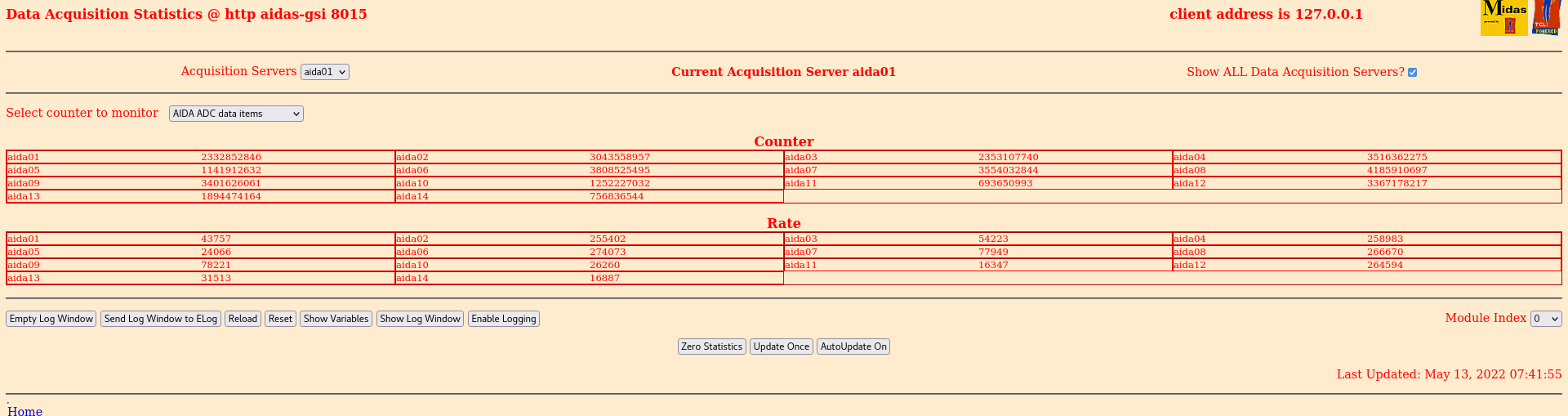

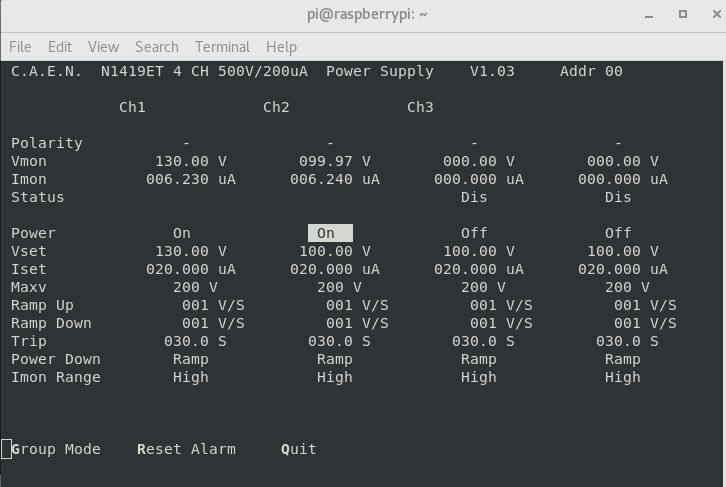

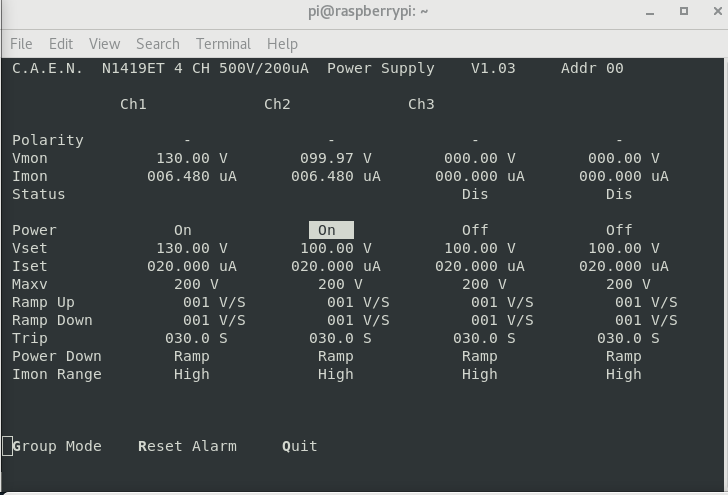

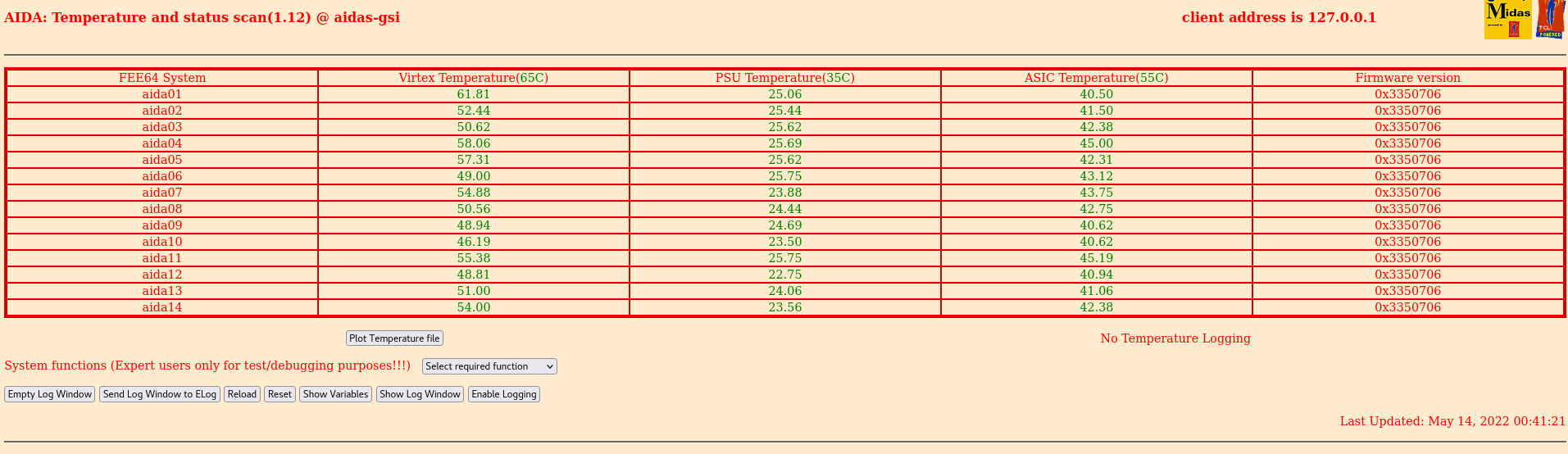

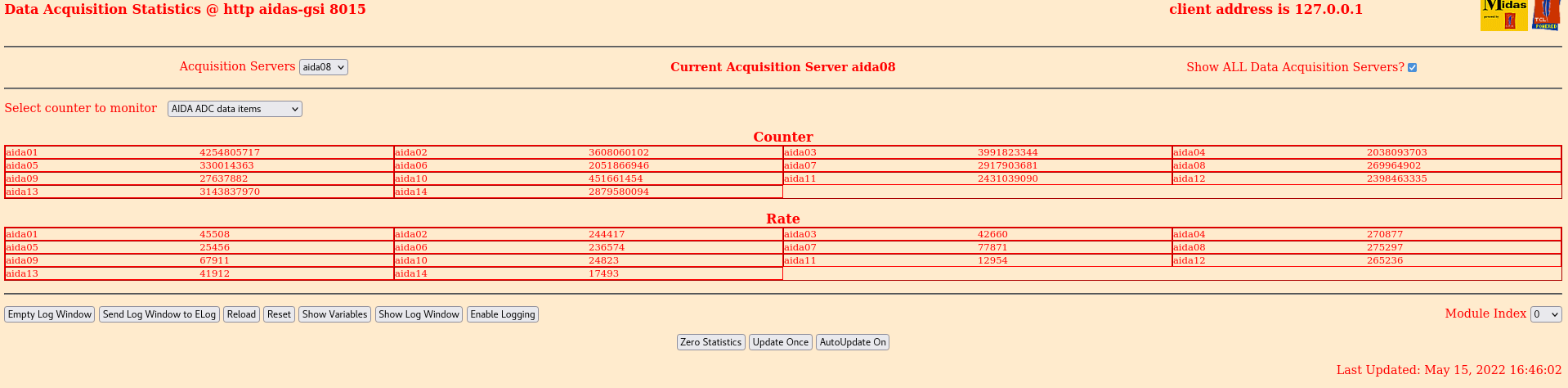

ML | 2h-Shift Checks |

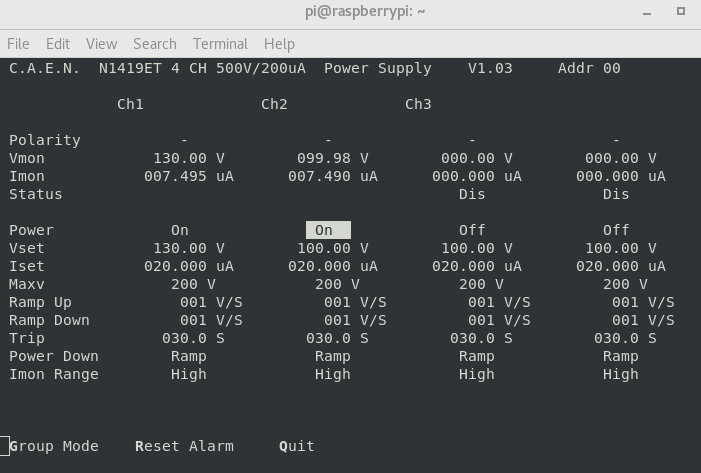

All seems ok (apart for my virgin network connection usually quite reliable but not so tonight !?!).

Statistics seems ok.

Temperatures appears stable

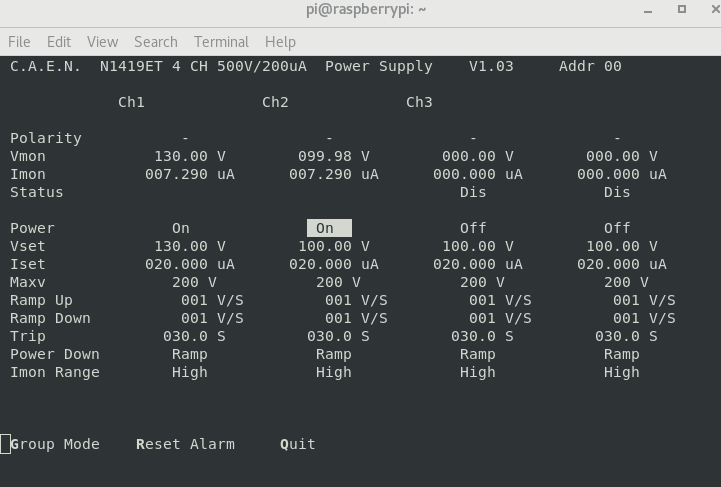

Leakage current ok.

System Wide Checks:

Clock check: Passed= 14: - Failed=: 0

ADC calibration check:

FEE64 module aida01 failed

FEE64 module aida04 failed

FEE64 module aida06 failed

FEE64 module aida13 failed

Calibration test result: Passed=10 ; Failed= 4

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module -> DID THAT BUT NO CHANGES

White rabbit decode status: Passed=14 ; Failed=0

FPGA timestamp check: Passed=14 ; Failed=0

Memory information: Page loading failed with the error message below:

Got the error Server Internal Error

while trying to obtain /AIDA/Check/Check.tml.

could not read "/Embedded/XilinxLinux/ppc_4xx/rfs/aida01/tmp/mybuddy.txt": no such file or directory while executing "file size $mybuddy " (procedure "do_collect_info" line 16) invoked from within "do_collect_info " ("COLLECTINFO" arm line 1) invoked from within "switch -glob $w { RESET {set started 0} CLEAR {EmptyLog} ELOG {PrintLog} ..." (procedure "do_click" line 23) invoked from within "do_click" invoked from within "if {$started != 0} { variable JS "" variable LogFlag if {$LogFlag == 1} {InsertLog "Last Updated: [clock format [clock seconds] -form..." (file "Check.tcl" line 8) invoked from within "source Check.tcl" (in namespace eval "::Check" script line 6) invoked from within "namespace eval Check { global env source [file join $env(MIDASBASE) TclHttpd tcl Common common.tcl] source [file join $env(MIDASB..." invoked from within "subst { [Doc_Dynamic] <! [global Httpd; upvar #0 Httpd[set Httpd(currentSocket)] data; set ClientIPAddress $data(ipaddr); set MyInfo $data(self)] >..." ("uplevel" body line 1) invoked from within "uplevel #0 [list subst $script]" (procedure "SubstFile" line 12) invoked from within "SubstFile /home/npg/MIDAS_Releases/23Jan19/MIDAS_200119/TclHttpd/Html/AIDA/Check/Check.tml {}" ("uplevel" body line 1) invoked from within "uplevel 1 [list SubstFile $path $interp]" (procedure "Subst_File" line 7) invoked from within "Subst_File $template $interp" invoked from within "TemplateInstantiate $sock $path {} $suffix {} $Template(templateInterp)" (procedure "Doc_application/x-tcl-template" line 9) invoked from within "$cmd $path $suffix $sock" (procedure "Doc_Handle" line 20) invoked from within "Doc_Handle $prefix $path $suffix $sock" (procedure "DocDomain" line 44) invoked from within "DocDomain / /MIDAS/TclHttpd/Html sock8 AIDA/Check/Check.tml" ("eval" body line 1) invoked from within "eval $Url(command,$prefix) [list $sock $suffix]" |

| Attachment 1: Stats_Screenshot_from_2022-05-13_01-45-56.png

|

|

| Attachment 2: Temp_Screenshot_from_2022-05-13_01-47-31.png

|

|

| Attachment 3: HV_LC_Screenshot_from_2022-05-13_01-48-21.png

|

|

|

437

|

Fri May 13 02:28:36 2022 |

ML | beam dropped |

We see less counts in AIDA implant DSSD1 (~1Hz) than at the beginning of the night shift (~10Hz).

This seems to be beam related as the count rates in DESPEC & FRS Scalers seems to have dropped too. |

|

438

|

Fri May 13 02:56:36 2022 |

ML | 2h-Shift Checks |

All seemnormal on AIDA side.

Stats as before

Temperatures stable

HV-LV ok

System wide check : all results as in the previous checks |

| Attachment 1: Stats_Screenshot_from_2022-05-13_03-43-34.png

|

|

| Attachment 2: Temp_Screenshot_from_2022-05-13_03-44-41.png

|

|

| Attachment 3: HV_LC_Screenshot_from_2022-05-13_03-41-28.png

|

|

|

439

|

Fri May 13 04:45:23 2022 |

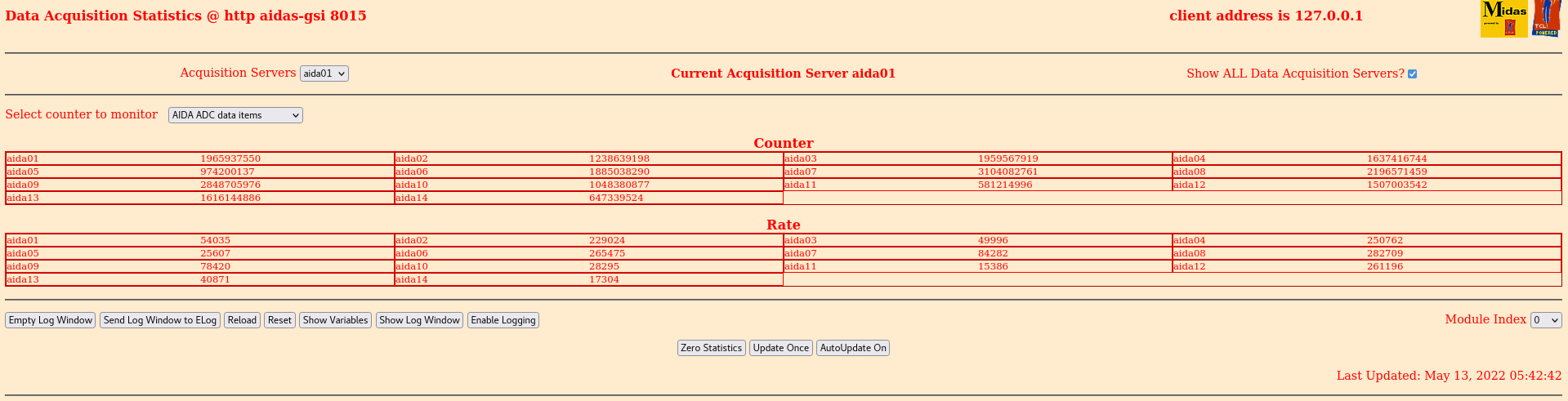

ML | 2h-Shift Checks |

AIDA is running ok. Note that, in the last hour or so, the rate of implant in DSSD1 is back to higher rate ~10 Hzto 15 Hz as at the beginning of this shift.

Stats seems ok

Temperatures stable

Leakage current: ok

A systwm wide check gives same result as for the fist check on this shift at ~1am |

| Attachment 1: Stats_Screenshot_from_2022-05-13_05-43-14.png

|

|

| Attachment 2: Temp_Screenshot_from_2022-05-13_05-42-10.png

|

|

| Attachment 3: HV_LC_Screenshot_from_2022-05-13_05-41-23.png

|

|

|

440

|

Fri May 13 06:47:33 2022 |

ML | 2h-Shift Checks |

It has been a quiet night. AIDA has been stable.

Stats appears stable appear

Temperature also stable

Leakage current slowly dropping still.

System wide checks done. Status quo here again. |

| Attachment 1: Stats_Screenshot_from_2022-05-13_07-43-54.png

|

|

| Attachment 2: Temp_Screenshot_from_2022-05-13_07-43-13.png

|

|

| Attachment 3: HV_LC_Screenshot_from_2022-05-13_07-42-38.png

|

|

|

444

|

Fri May 13 23:37:59 2022 |

ML | 2h-Shift Checks |

Took over remotely from CB about an hour ago

At 0h40 (CET):

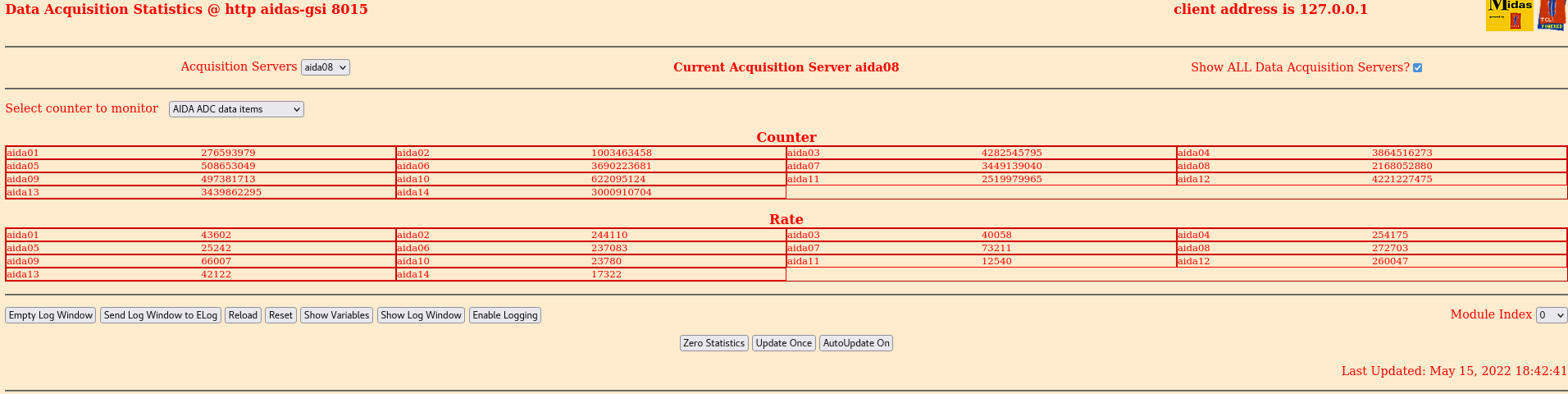

Stats still ok - attach 1

Leakage still OK - Attach 2

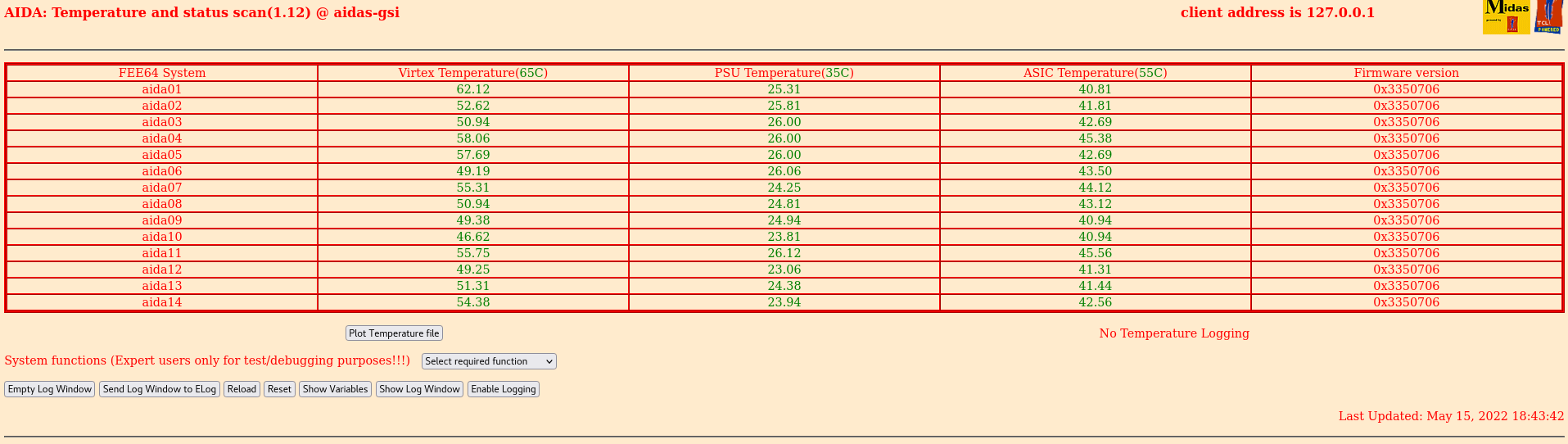

Temps - attach 3

Grafana OK

UCESB rates ok - attach 5

System-wide checks: aida09 fails clock (1), aida02 06 09 10 13 fail ADC calibration, all pass WR |

| Attachment 1: Stats_Screenshot_from_2022-05-14_00-40-56.png

|

|

| Attachment 2: HV_LC_Screenshot_from_2022-05-14_00-39-51.png

|

|

| Attachment 3: temp_Screenshot_from_2022-05-14_00-41-44.png

|

|

| Attachment 4: UCESB_Screenshot_from_2022-05-14_01-00-00.png

|

|

|

445

|

Sat May 14 01:52:03 2022 |

ML | 2h-Shift Checks |

AIDA stats ok

Leakage current ok

Temperatires ok

grafana ok

ucesb rates dropped a bit in all scalers so beam intensity must have dropped a bit.

System wide check done and same results as earlier:

aida09 fails clock (1), aida02 06 09 10 13 fail ADC calibration, all pass WR |

| Attachment 1: Stats_Screenshot_from_2022-05-14_02-48-14.png

|

|

| Attachment 2: Temp_Screenshot_from_2022-05-14_02-47-31.png

|

|

| Attachment 3: HV_LC_Screenshot_from_2022-05-14_02-46-42.png

|

|

| Attachment 4: ucesb_rates_Screenshot_from_2022-05-14_02-50-36.png

|

|

| Attachment 5: Grafana_Screenshot_from_2022-05-14_03-50-00.png

|

|

|

457

|

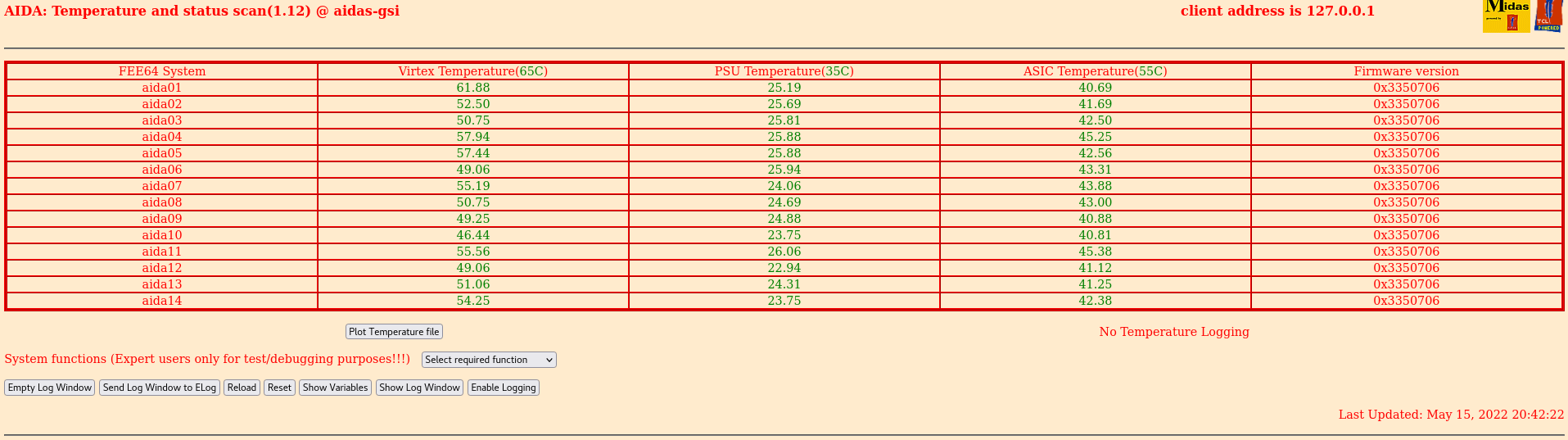

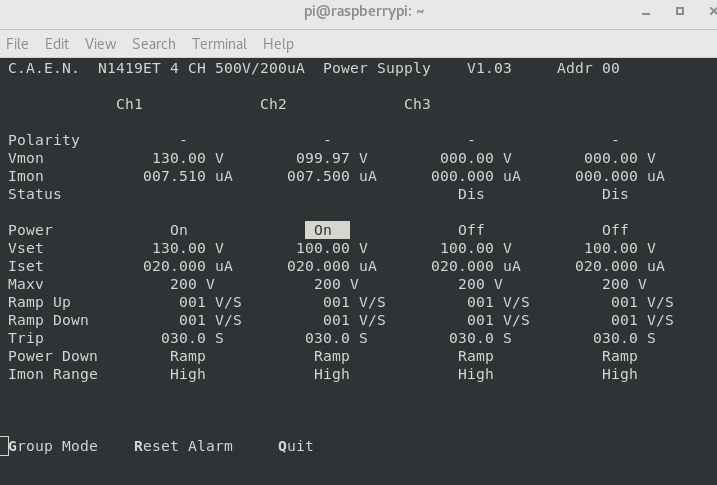

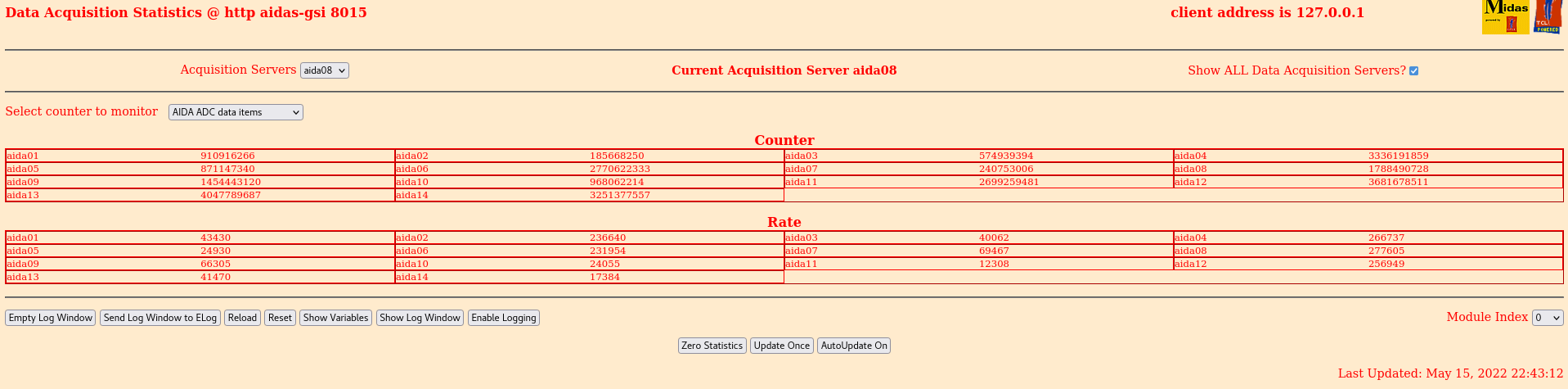

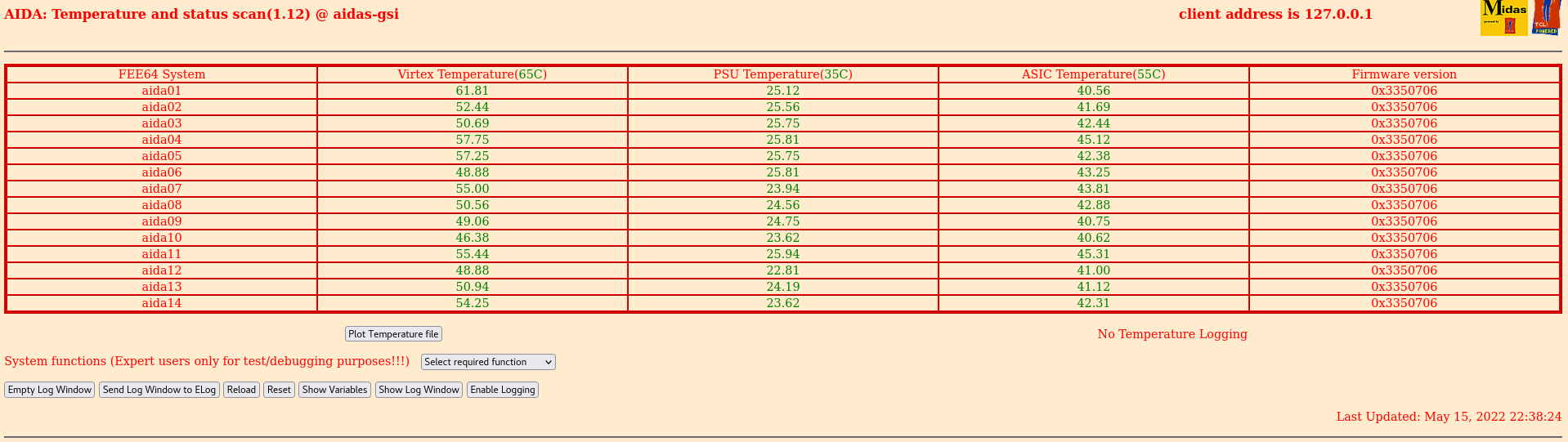

Sun May 15 15:51:49 2022 |

ML | Sunday 15th May 16:00-0:00 |

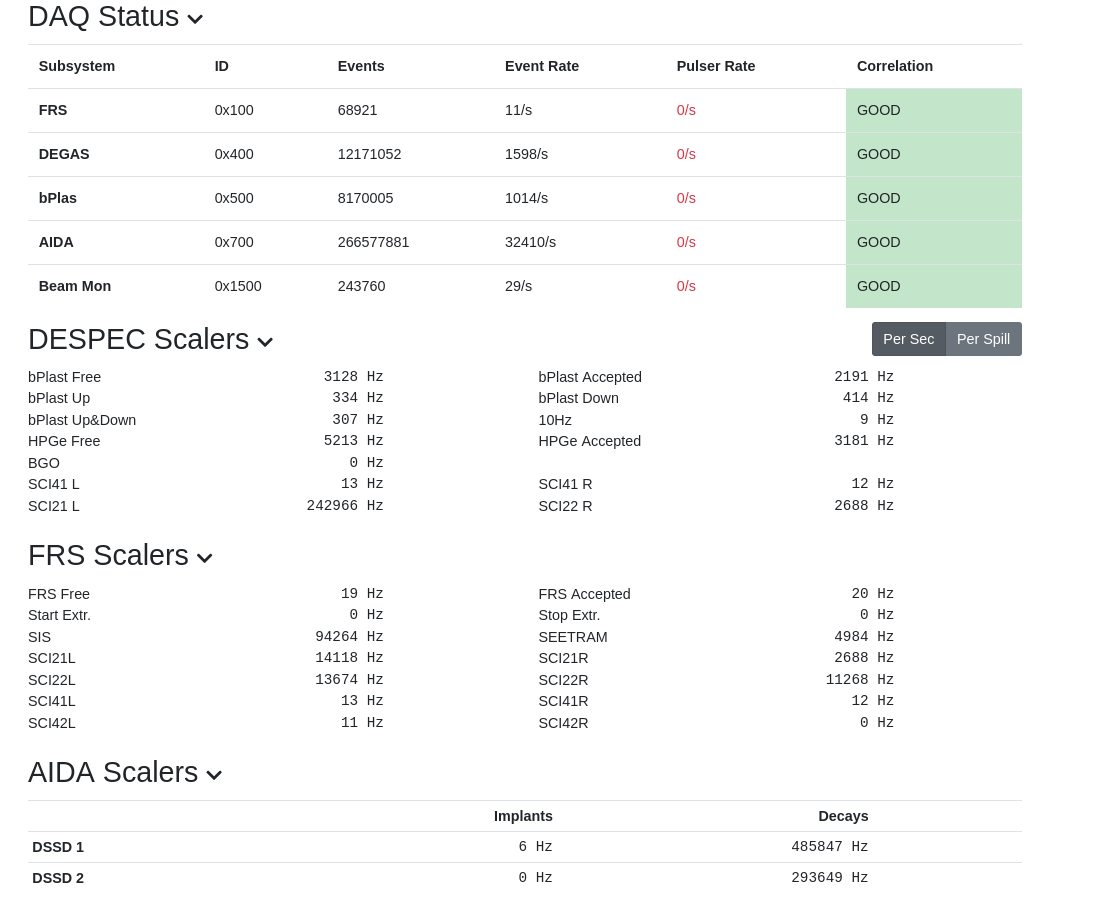

Status at 16:45 (CET)

The expreiment continues to run smoothly.

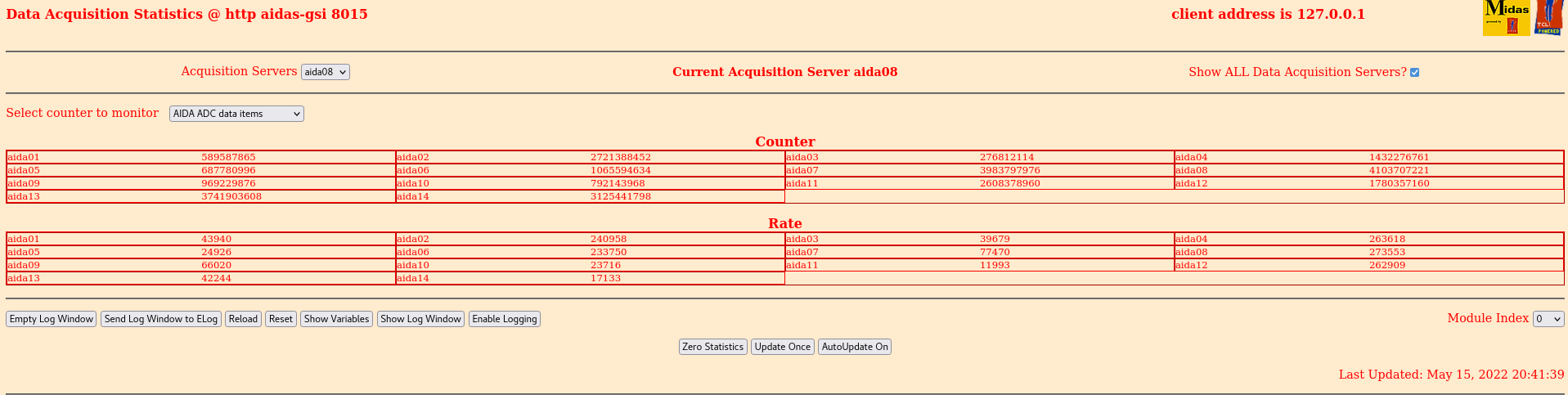

AIDA Stats look ok - Attachment 1

AIDA Temperature ok - Attachment 2

AIDA Leakage current: ok - Attachment 3

System wide check:

Clock: 13 passed, 1 failed (aida09)

ADC Calibration: 9 passed, 5 fialed (aida2,6,9,10,13)

White rabbit decoder: 14 passed, 0 failed.

FPGA timestamp: 14 passed, 0 failed.

Status at 18:45 (CET):

All rates ok on ucesb.

AIDA Stats ok - Attachment 4

AIDA Temperature ok - Attachment 5

AIDA Leakage current: increase slightly - Attachment 6

System wide check: No changes, same as above

Status at 20:45 (CET):

All rates ok on ucesb.

AIDA Stats ok - Attachment 7

AIDA Temperature ok - Attachment 8

AIDA Leakage current: increase slightly - Attachment 9

System wide check: No changes, same as above

Status at 22:45 (CET):

All rates ok on ucesb.

AIDA Stats ok - Attachment 10

AIDA Temperature ok - Attachment 11

AIDA Leakage current: increase slightly - Attachment 12

System wide check: No changes, same as above |

| Attachment 1: Stats_Screenshot_from_2022-05-15_16-49-06.png

|

|

| Attachment 2: Temp_Screenshot_from_2022-05-15_16-48-31.png

|

|

| Attachment 3: HV_LC_Screenshot_from_2022-05-15_16-47-44.png

|

|

| Attachment 4: Stats_Screenshot_from_2022-05-15_18-43-16.png

|

|

| Attachment 5: Temp_Screenshot_from_2022-05-15_18-44-06.png

|

|

| Attachment 6: HV_LC_Screenshot_from_2022-05-15_18-42-23.png

|

|

| Attachment 7: Stats_Screenshot_from_2022-05-15_20-42-03.png

|

|

| Attachment 8: Temp_Screenshot_from_2022-05-15_20-42-42.png

|

|

| Attachment 9: HV_LC_Screenshot_from_2022-05-15_20-36-28.png

|

|

| Attachment 10: Stats_Screenshot_from_2022-05-15_22-43-37.png

|

|

| Attachment 11: Temp_Screenshot_from_2022-05-15_22-44-20.png

|

|

| Attachment 12: HV_LC_Screenshot_from_2022-05-15_22-42-36.png

|

|

|

152

|

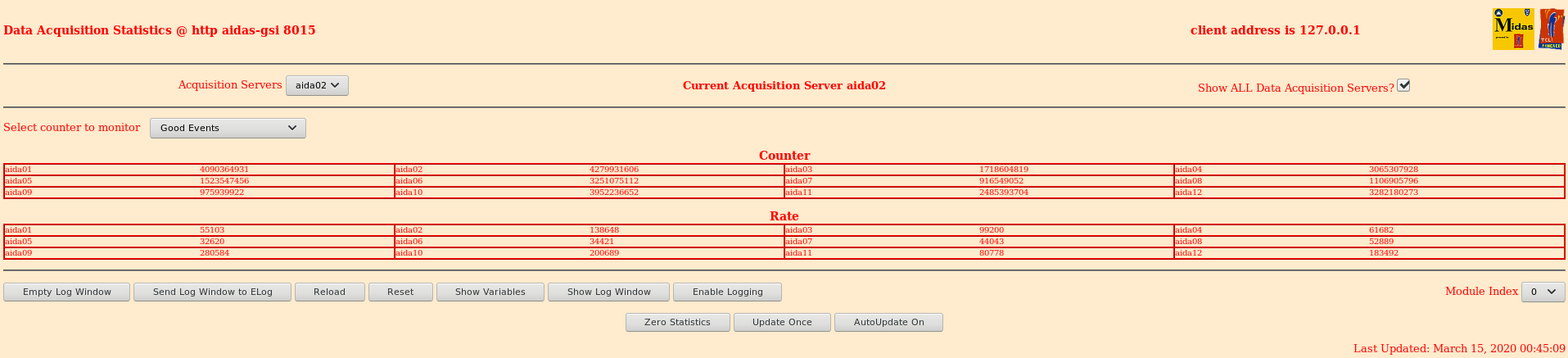

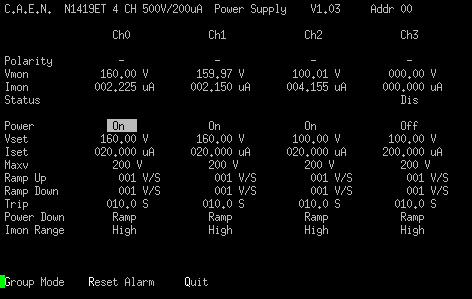

Sat Mar 14 23:09:28 2020 |

MB, SJ, MR | Sunday 15th March 0:00-8:00 |

AIDA ELog filled out by DESPEC night shift members Matthew Brunet (MB), Shaheen Jazrawi (SJ), and Matthias Rudiger (MR).

0:05-0:08 Beam operators altering settings, beam off/sporadic during this period.

0:46

All system wide checks passed

Leak currents lower than previous measurement - attachment #1

Implants look as previously - attachment #2

Stats about where they have been - attachment #3

FEE temperatures fine - attachment #4

Merger fine, 3 Mega items / sec

TapeServer writing about 25 MB/s

2:46

All system wide checks passed

Leak currents similar to previous - attachment #5

Implants look as previously - attachment #6

Stats about where they have been - attachment #7

FEE temperatures fine - attachment #8

Merger fine, 3 Mega items / sec

TapeServer writing about 27 MB/s

4:49

All system wide checks passed

Leak currents similar to previous - attachment #9

Implants look as previously - attachment #10

Stats good - attachment #11

FEE temperatures fine - attachment #12

Merger fine, 3 Mega items / sec

TapeServer writing about 27 MB/s

6:49

All system wide checks passed

Leak currents no significant change - attachment #13

Implants look as previously - attachment #14

Stats good - attachment #15

FEE temperatures fine - attachment #16

Merger fine, 3 Mega items / sec

TapeServer writing about 25 MB/s |

| Attachment 1: Matt-15-BiasesA.png

|

|

| Attachment 2: Matt-15-HistosA.png

|

|

| Attachment 3: Matt-15-StatsA.png

|

|

| Attachment 4: Matt-15-TempsA-.png

|

|

| Attachment 5: Matt-15-BiasesB.png

|

|

| Attachment 6: Matt-15-HistosB.png

|

|

| Attachment 7: Matt-15-StatsB.png

|

|

| Attachment 8: Matt-15-TempsB.png

|

|

| Attachment 9: Matt-15-BiasesC.png

|

|

| Attachment 10: Matt-15-HistosC.png

|

|

| Attachment 11: Matt-15-StatsC.png

|

|

| Attachment 12: Matt-15-TempsC.png

|

|

| Attachment 13: Matt-15-BiasesD.png

|

|

| Attachment 14: Matt-15-HistosD.png

|

|

| Attachment 15: Matt-15-StatsD.png

|

|

| Attachment 16: Matt-15-TempsD.png

|

|

|

266

|

Fri Apr 23 13:13:46 2021 |

MA, TD | Friday 23 April 12.00-16.00 |

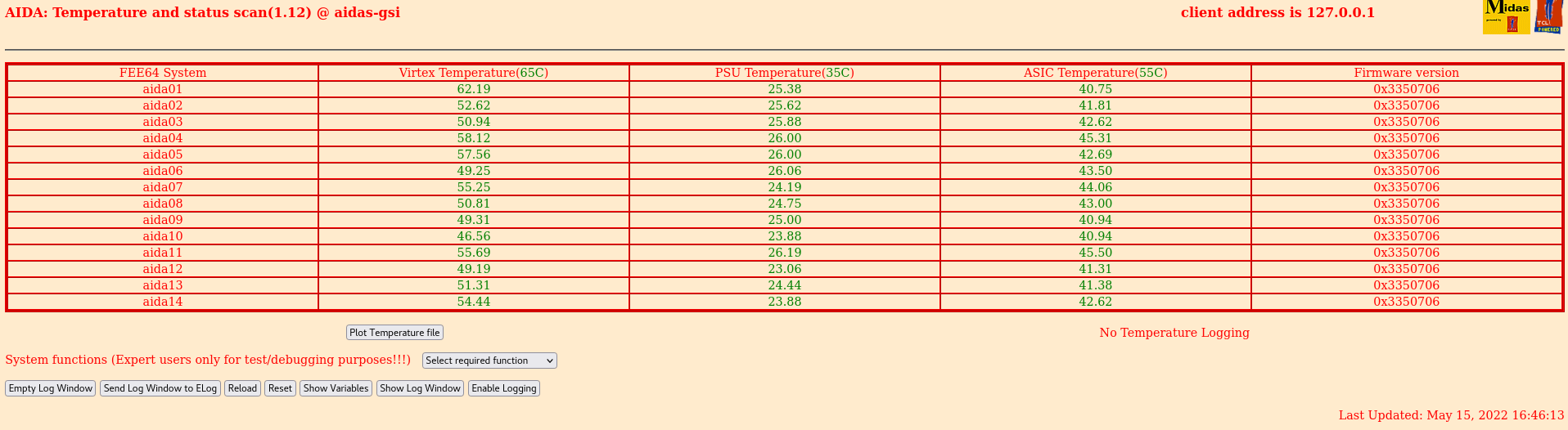

14.15 System wide checks

FEE64 module aida06 global clocks failed, 6

Clock status test result: Passed 11, Failed 1

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

FEE64 module aida06 failed

FEE64 module aida07 failed

FEE64 module aida12 failed

Calibration test result: Passed 9, Failed 3

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

Base Current Difference

aida06 fault 0x679f : 0x67a2 : 3

White Rabbit error counter test result: Passed 11, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

FPGA timestamp errors - reports 'server internal error'

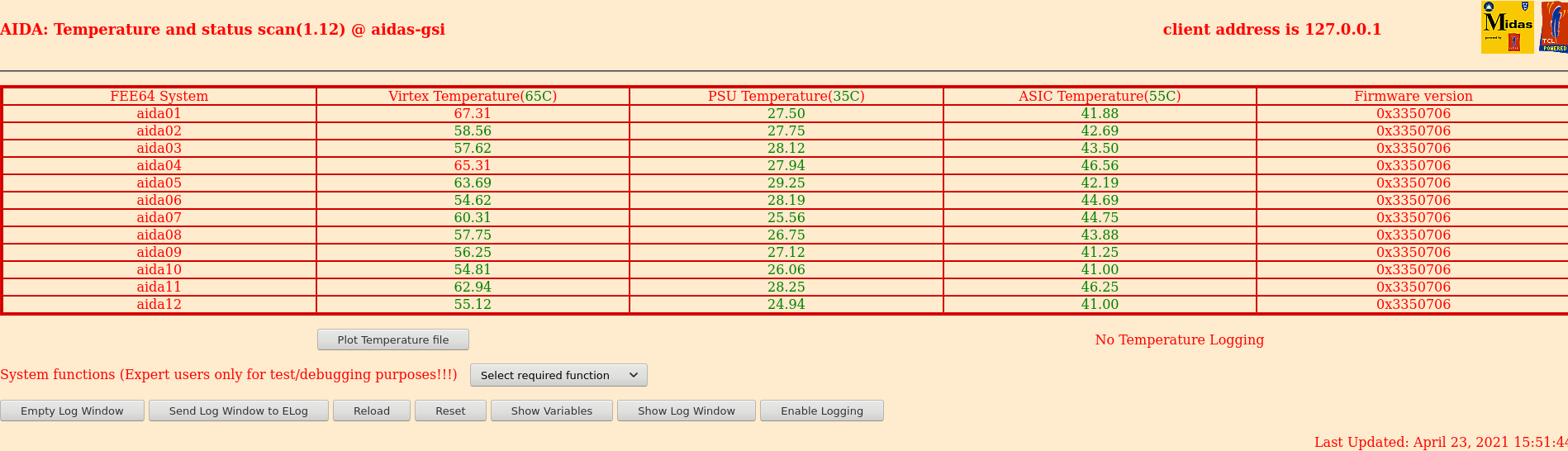

14.16 DSSSD bias & leakage currents OK - attachment 1

FEE64 temps OK - attachment 2

good events stats - attachment 3

14.22 DAQ continues file S460/R51_205

beam intensity 2.2e+09/s

15:53 system check

Rates, Temperatures, Voltages are ok and attached 4,5,6

Clock check

FEE64 module aida06 global clocks failed, 6

Clock status test result: Passed 11, Failed 1

Understand status as follows

Status bit 3 : firmware PLL that creates clocks from external clock not locked

Status bit 2 : always logic '1'

Status bit 1 : LMK3200(2) PLL and clock distribution chip not locked to external clock

Status bit 0 : LMK3200(1) PLL and clock distribution chip not locked to external clock

If all these bits are not set then the operation of the firmware is unreliable

ADC check

FEE64 module aida06 failed

FEE64 module aida07 failed

FEE64 module aida12 failed

Calibration test result: Passed 9, Failed 3

If any modules fail calibration , check the clock status and open the FADC Align and Control browser page to rerun calibration for that module

White Rabbit

Base Current Difference

aida06 fault 0x679f : 0x67a2 : 3

White Rabbit error counter test result: Passed 11, Failed 1

Understand the status reports as follows:-

Status bit 3 : White Rabbit decoder detected an error in the received data

Status bit 2 : Firmware registered WR error, no reload of Timestamp

Status bit 0 : White Rabbit decoder reports uncertain of Timestamp information from WR

FPGA

Loge page error!

Memory check

Returned 0 0 0 0 0 0 0 0 0 0 0 0

Mem(KB) : 4 8 16 32 64 128 256 512 1k 2k 4k

aida01 : 23 6 2 1 2 3 2 4 2 3 6 : 36044

aida02 : 15 3 2 2 0 3 2 3 2 3 4 : 27188

aida03 : 29 4 0 3 2 4 2 2 3 3 6 : 36212

aida04 : 4 6 4 4 2 3 3 3 3 3 6 : 36864

aida05 : 19 5 4 2 3 3 1 3 3 3 6 : 36404

aida06 : 24 9 5 2 3 3 3 2 3 3 6 : 36472

aida07 : 20 4 9 0 2 3 2 2 3 3 6 : 36096

aida08 : 22 9 4 3 1 3 1 3 3 3 6 : 36352

aida09 : 20 7 3 2 2 3 3 2 3 3 6 : 36344

aida10 : 25 9 9 5 2 3 2 3 3 3 6 : 36828

aida11 : 24 11 2 0 1 3 1 3 3 3 6 : 36248

aida12 : 26 5 4 2 1 3 2 2 3 3 6 : 36048 |

| Attachment 1: 200.png

|

|

| Attachment 2: Screenshot_2021-04-23_Temperature_and_status_scan_aidas-gsi(4).png

|

.png.png)

|

| Attachment 3: Screenshot_2021-04-23_Statistics_aidas-gsi(4).png

|

.png.png)

|

| Attachment 4: 210423_1550_Voltages.png

|

|

| Attachment 5: 210423_1550_Stats.png

|

|

| Attachment 6: 210423_1550_Temp.png

|

|